Category:SVG logic gates

Jump to navigation

Jump to search

Media in category "SVG logic gates"

The following 83 files are in this category, out of 83 total.

-

7400 Circuit tristated.svg 319 × 372; 36 KB

-

Ampel Muster Grob.svg 600 × 160; 12 KB

-

AND DIN.svg 100 × 80; 5 KB

-

And-inverter-graph.svg 511 × 316; 19 KB

-

ApplicationSimplificationd'uncircuitlogiquePage14Image3.svg 600 × 400; 136 KB

-

Buffer DIN.svg 100 × 80; 5 KB

-

Buffer gate.svg 120 × 74; 1,019 bytes

-

BUT DIN.svg 100 × 80; 5 KB

-

Circuit elements es.svg 477 × 260; 17 KB

-

Circuit elements mk.svg 418 × 260; 16 KB

-

Circuit elements.svg 400 × 260; 17 KB

-

CPT-logic-gate conversion (A.¬B)+(C).svg 428 × 173; 15 KB

-

CPT-logic-gate conversion NOR-(-A.B).svg 424 × 140; 20 KB

-

CPT-logic-gate ex1 Answer.svg 342 × 106; 31 KB

-

CPT-logic-gate ex1.svg 313 × 106; 34 KB

-

CPT-logic-gate ex3.svg 379 × 88; 36 KB

-

CPT-logic-gate ex4 - Answers.svg 320 × 73; 42 KB

-

CPT-logic-gate ex4.svg 291 × 73; 6 KB

-

CPT-logic-gate ex5 - Answers.svg 445 × 80; 7 KB

-

CPT-logic-gate ex5.svg 414 × 72; 42 KB

-

CPT-logic-gate example.svg 419 × 527; 11 KB

-

CurrentSwitchLogic.svg 1,052 × 744; 132 KB

-

Differential-Current-Switch.svg 1,197 × 1,061; 127 KB

-

DMR Schnitt.svg 184 × 364; 14 KB

-

Dont-care-timing.svg 350 × 150; 13 KB

-

ISN-combi-portes1.svg 1,239 × 410; 10 KB

-

Logic-gate-and-de.svg 640 × 282; 5 KB

-

Logic-gate-buf-de.svg 640 × 282; 4 KB

-

Logical and.svg 200 × 75; 5 KB

-

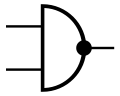

Logical or.svg 200 × 75; 5 KB

-

LogicGates mk.svg 771 × 1,155; 46 KB

-

Logik-materiell-impl.svg 345 × 230; 15 KB

-

Logikplan.svg 213 × 106; 6 KB

-

Logique74ls51.svg 714 × 934; 15 KB

-

MFrey (A and B) or (A and C).svg 1,600 × 700; 7 KB

-

MFrey (A and B) or (C and D) 000.svg 220 × 120; 22 KB

-

MFrey (A and B) or (C and D) 001.svg 220 × 120; 23 KB

-

MFrey (A and B) or (C and D) 002.svg 220 × 120; 22 KB

-

MFrey (A and B) or (C and D) 003.svg 220 × 120; 19 KB

-

MFrey (A and B) or (C and D) 004.svg 220 × 120; 15 KB

-

MFrey (A nor B) and C 001.svg 220 × 90; 19 KB

-

MFrey (A nor B) and C.svg 220 × 90; 18 KB

-

MFrey (A or B) and C 000.svg 220 × 90; 19 KB

-

MFrey (A or B) and C 001.svg 220 × 90; 19 KB

-

MFrey (A or B) and C 002.svg 220 × 90; 15 KB

-

MFrey (A or B) and C 003.svg 220 × 90; 14 KB

-

MFrey (A or B) and C 004.svg 220 × 90; 12 KB

-

MFrey (A or B) and C.svg 220 × 90; 18 KB

-

MFrey (A or E or C) and B 000.svg 220 × 120; 11 KB

-

MFrey (A or E or C) and B 001.svg 220 × 120; 12 KB

-

MFrey (A or E or C) and B 002.svg 220 × 120; 7 KB

-

MFrey A and (B or C).svg 1,600 × 700; 6 KB

-

MFrey A and 0.svg 1,200 × 400; 6 KB

-

MFrey A and B or C and D.svg 220 × 110; 22 KB

-

MFrey A and B or C.svg 220 × 90; 18 KB

-

MFrey A and Not A.svg 1,200 × 400; 5 KB

-

MFrey A or (B and C).svg 220 × 90; 18 KB

-

MFrey A or 1.svg 1,200 × 700; 6 KB

-

MFrey A or Not A.svg 1,200 × 700; 5 KB

-

MFrey B or (C and A).svg 220 × 90; 18 KB

-

MFrey Not A and B 000.svg 150 × 60; 17 KB

-

MFrey Not A and B.svg 150 × 60; 16 KB

-

NAND DIN.svg 100 × 80; 5 KB

-

NBUT DIN.svg 100 × 80; 5 KB

-

NOR DIN.svg 100 × 80; 5 KB

-

NOR-Gate DIN40900.svg 330 × 200; 9 KB

-

NOT DIN.svg 100 × 80; 5 KB

-

NOT gate.svg 120 × 74; 99 KB

-

NOT-Gate DIN40900.svg 58 × 30; 6 KB

-

OR DIN.svg 100 × 80; 5 KB

-

Portes Logiques.svg 280 × 260; 11 KB

-

Static CMOS inverter VTC.svg 654 × 610; 111 KB

-

Tristate buffer.svg 343 × 73; 6 KB

-

Unused Inputs Connected To Rails.svg 350 × 150; 17 KB

-

Unused Inputs Connected Together.svg 350 × 150; 19 KB

-

Very short Pulse-Pulsegenerator.svg 174 × 66; 6 KB

-

XNOR DIN 2.svg 100 × 80; 7 KB

-

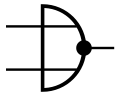

XNOR DIN.svg 100 × 80; 6 KB

-

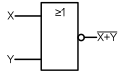

Xnor-gate-en.svg 500 × 180; 5 KB

-

XOR DIN 2.svg 100 × 80; 6 KB

-

XOR DIN.svg 100 × 80; 7 KB

-

Мажоритарный элемент.svg 230 × 150; 18 KB

-

ЭСЛ (переключатель тока).svg 320 × 210; 33 KB