# Communications of **HUAWEI RESEARCH**

June 2024 Issue <mark>6</mark>

AI for Science and Industry **p02**

Spatial Computing: Scalable Computing Systems Based on Computational Graphs **p12**

Exploration of Hybrid Optical-Electrical Switching Networks in AI Training Clusters **p42**

# **Editorial Note**

In this *Huawei Research* issue, we explore AI's transformative power in industrial and scientific modeling and computing. Our focus encompasses a broad spectrum of topics, including computing architectures, data types, the intricacies of hardware-software co-design, the development of algorithm models and architectures, and the exploration of various theories. Our objective is to offer an in-depth yet easily understandable analysis of the prevailing challenges and opportunities in AI technologies.

We systematically explain how AI can be effectively applied in industrial and scientific modeling and computing to address problems that have remained unsolved for over 200 years and are challenging to solve using existing AI statistical modeling. We explore how computer graphics and multimedia technologies can be integrated to create holographic media representations and non-geometric 3D scenario modeling. Additionally, we discuss the development of intelligent devices that can work in harmony with humans and complex environments. We also delve into the development of robotics without the use of coordinate systems. Finally, we examine how nonlinear system signals can be processed in the signal and system domain, leading to more accurate modeling methods. We aim to provide valuable insights and guidance for the next generation of AI technologies to tackle complex challenges.

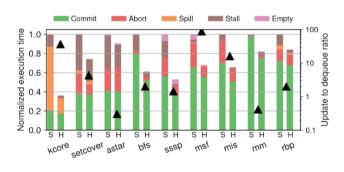

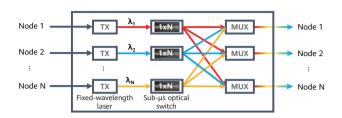

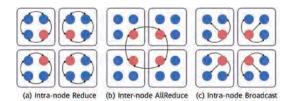

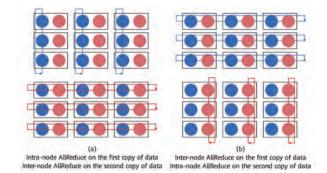

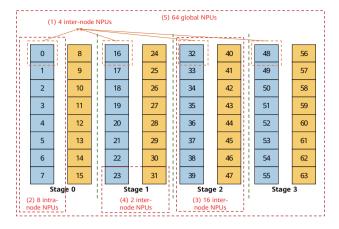

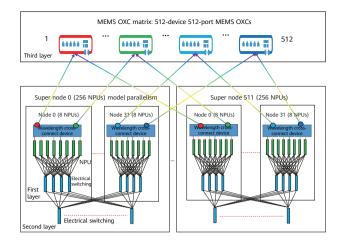

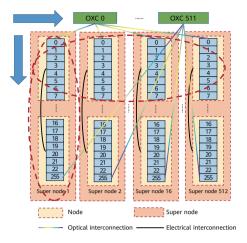

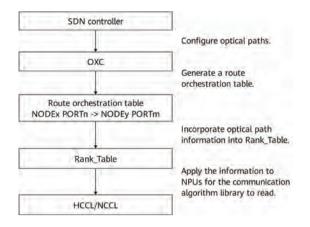

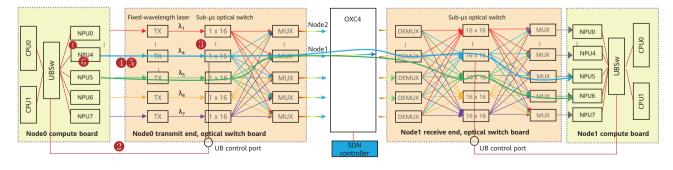

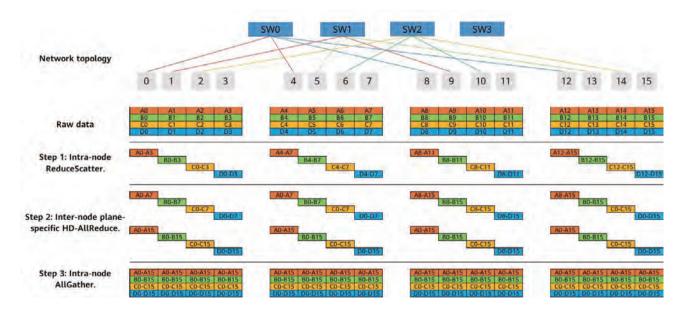

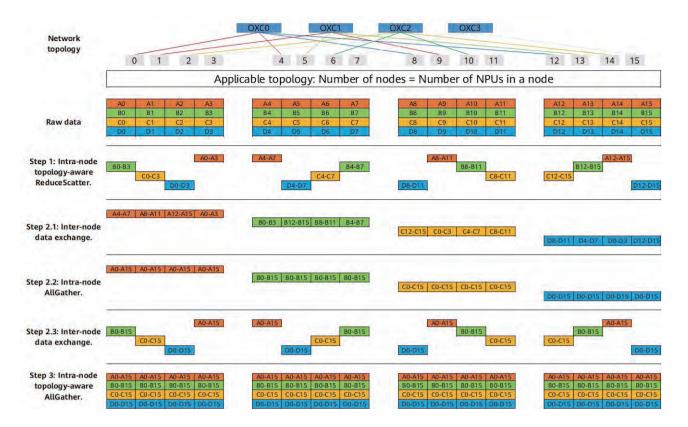

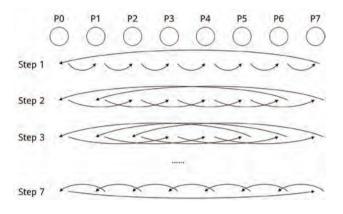

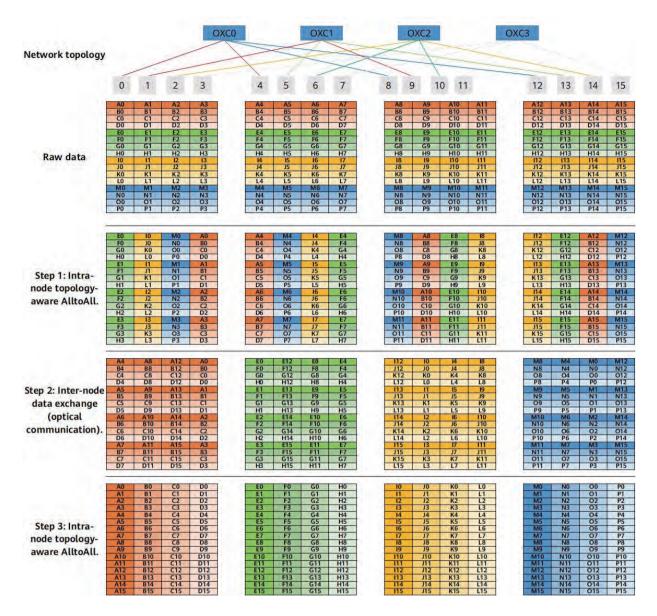

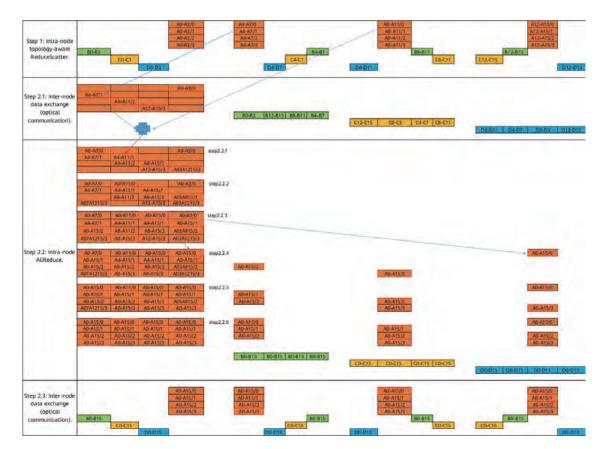

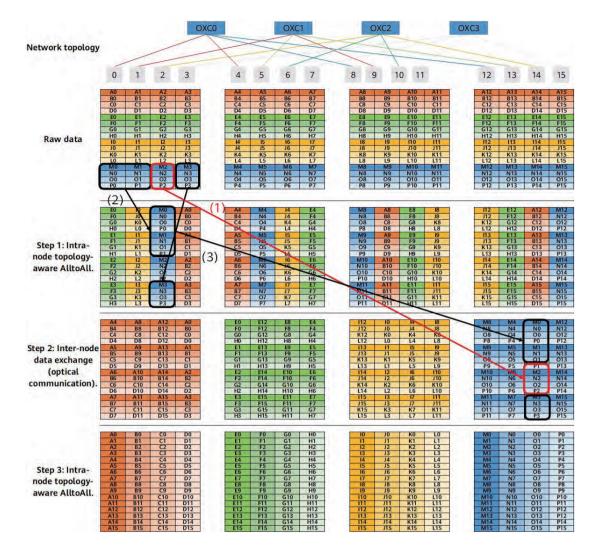

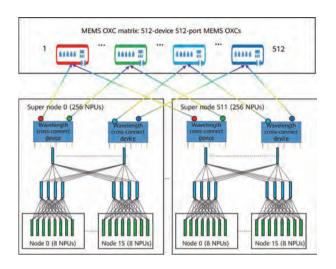

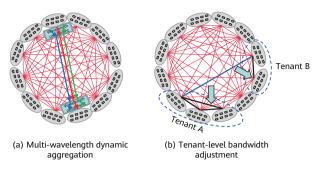

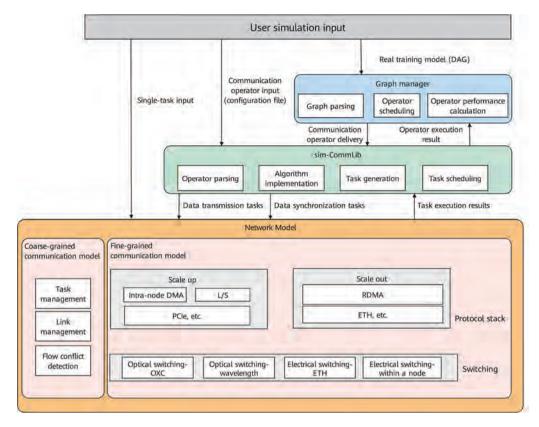

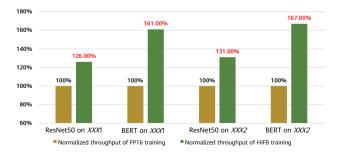

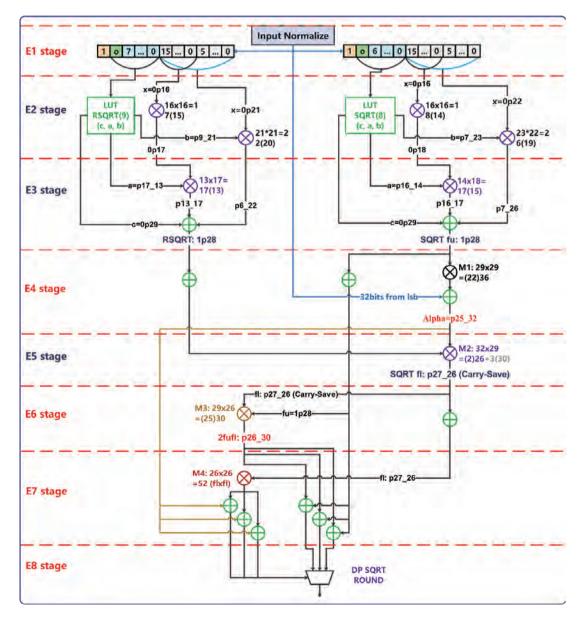

Spatial Computing introduces a novel, highly scalable architecture that transcends the conventional von Neumann model, designed to cater to the exponential computing power demands essential for AI advancements. Reprioritizing Speculative Task-Level Parallelism presents Hive, a cutting-edge task-based execution model and multicore architecture that enhances performance and optimizes energy efficiency. Hive leverages a wealth of fine-grained parallelism inherent in algorithms, employing dynamic priority updates to optimize execution. Hive ensures the integrity of speculative scheduling updates and prevents spurious task conflicts, establishing itself as an industry-leading hardware solution that significantly outperforms software-only parallel schedulers in efficiency and performance. Exploration of Hybrid Optical-Electrical Switching Networks in AI Training Clusters presents a groundbreaking hybrid optical-electrical switching network tailored for large-scale, high-bandwidth, and adaptable operations, addressing the challenges of cost and power consumption prevalent in computationally intensive scenarios such as AI and high-performance computing (HPC). Additionally, it introduces a novel collective communication algorithm optimized for this hybrid network, enhancing the efficiency of communication operations within AI training clusters. Ascend HiFloat8 AI Training and Inference doubles the computing power with a minimal increase in area by introducing an innovative 8-bit floating-point format, HiF8. This development, coupled with HiF8-based AI training and inference solutions, marks a substantial improvement in computing efficiency. To overcome hardware performance bottlenecks caused by complex CPU instructions for floatingpoint square root (FP SORT) computation, DP SQRT Computation Principle and Ultra-Low Latency Microarchitecture Design introduces an FP SQRT computation precision doubling method. This method segregates high and low bits and is paired with a corresponding microarchitecture design, enhancing computing precision and system performance.

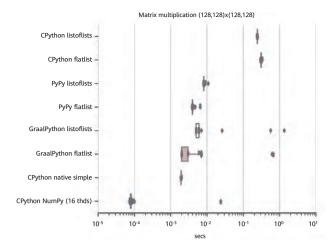

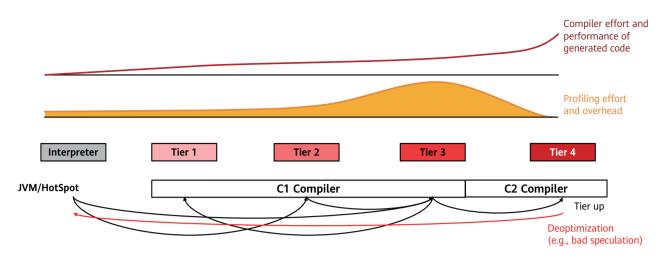

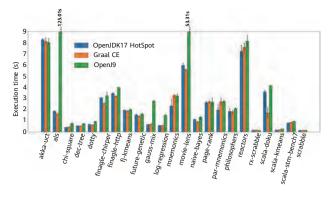

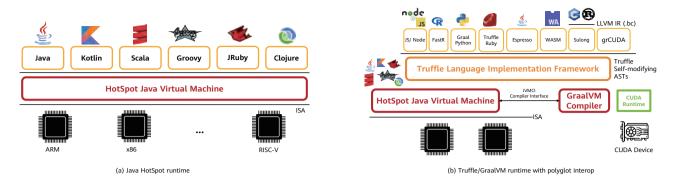

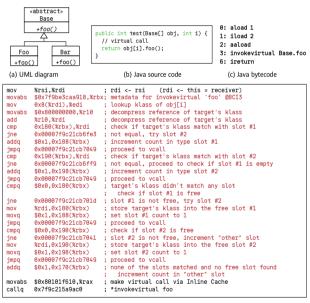

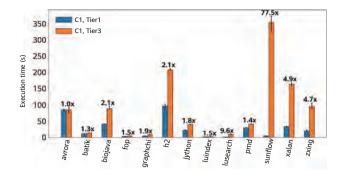

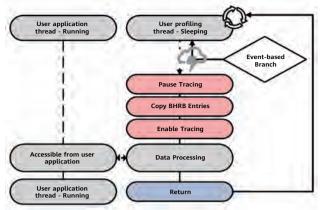

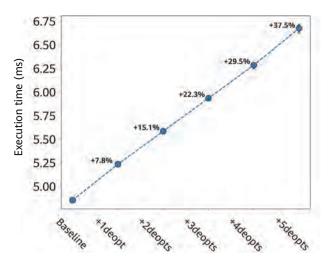

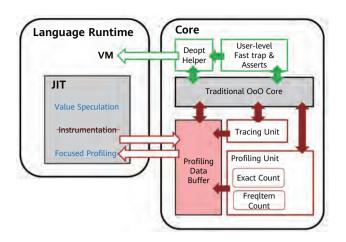

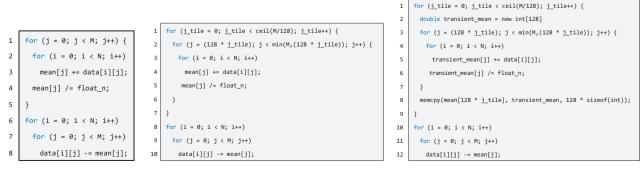

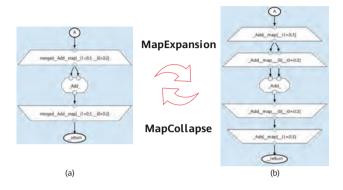

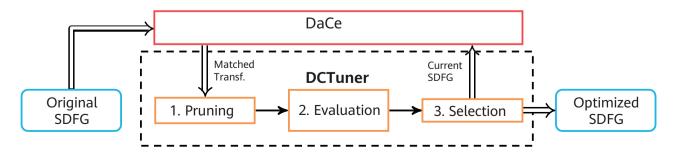

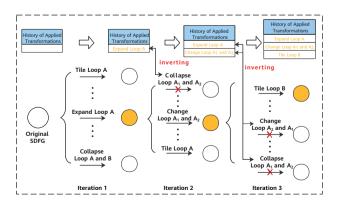

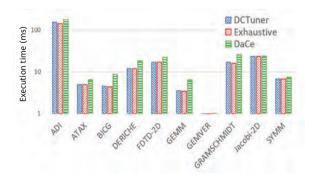

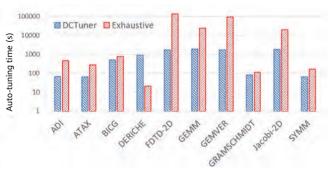

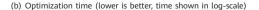

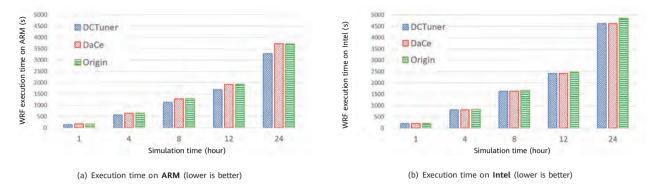

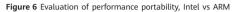

In hardware-software co-design and optimization, modern language implementations are increasingly leveraging dynamic or just-in-time (JIT) compilation techniques. This approach capitalizes on a unique opportunity to monitor and analyze the state of a program during its execution, allowing for real-time optimizations and enhancements that traditional compilation methods cannot offer. *Balancing the Yin and Yang of Dynamic Compilation and Execution* proposes innovative strategies for hardware-software co-design. It introduces software-directed narrowly focused profiling on hardware to more detailed profiles with minimal overhead. *Data-Centric Auto-Tuning of High-Performance Computing Applications* presents DCTuner, a novel auto-tuning method for optimizing HPC applications. DCTuner uses a data-centric representation, integrating a pruning strategy and a greedy exploration algorithm. This method enhances the performance of HPC applications beyond the current state-of-the-art benchmarks while ensuring high portability. *Humble Heroes* proposes a novel Algebraic Programming (ALP)/Pregel paradigm that scales well on a shared-memory parallel system and achieves speedups of up to 17.8x on common graph workloads, demonstrating that

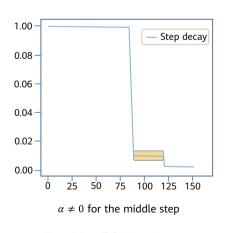

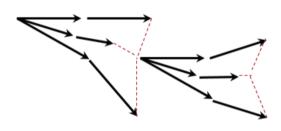

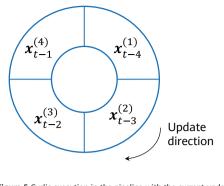

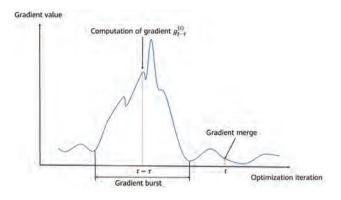

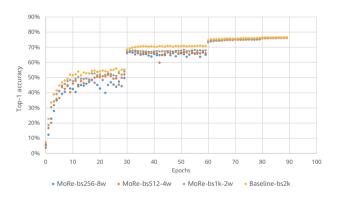

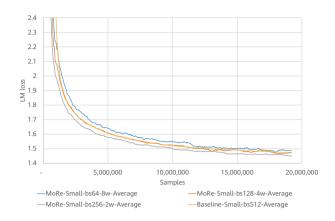

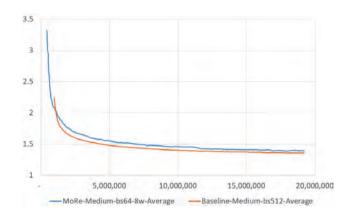

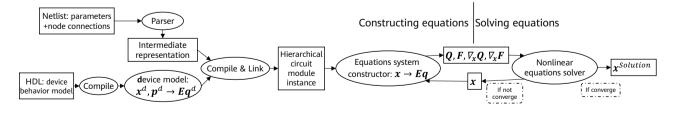

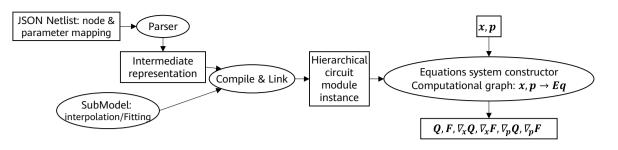

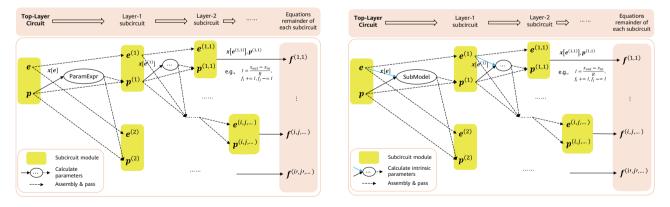

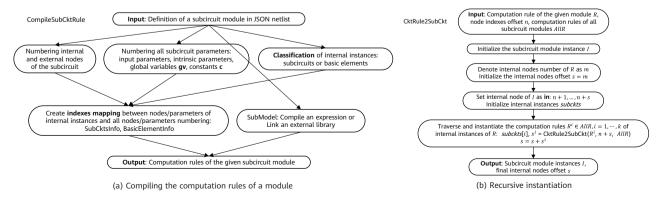

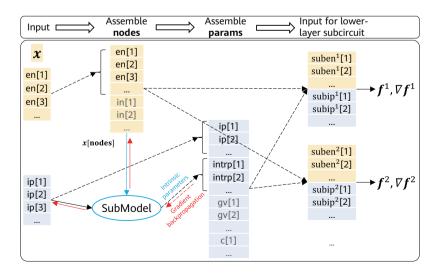

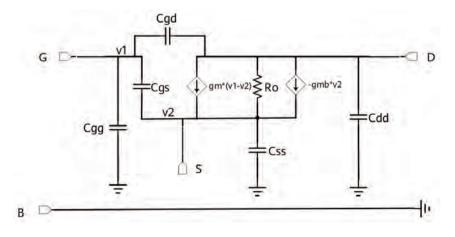

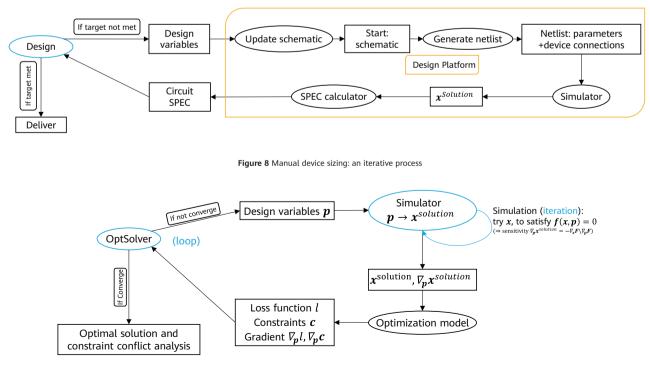

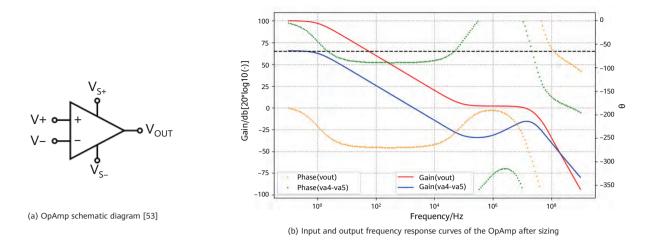

multiple humble programming models can be supported by a single software stack. *Asynchronous Training and MoRe* introduces the Momentum Reconstruction (MoRe) optimization technique, which achieves state-of-the-art convergence rates and generalization properties while reducing their memory requirements by a factor of two. *Computational Graph Representation of Equations System Constructors in Hierarchical Circuit Simulation* suggests using a computational graph representation to create an equations system constructor that supports dynamic parameters. This method, along with its JSON format netlist, simplifies the model development process and makes it easier to compute the gradients of equation remainders with respect to parameters.

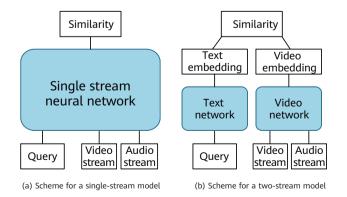

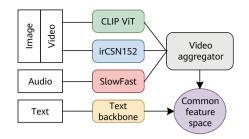

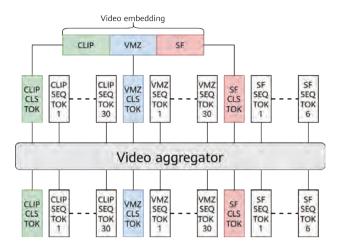

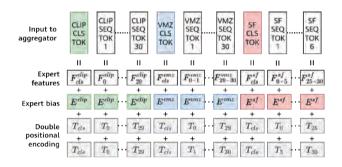

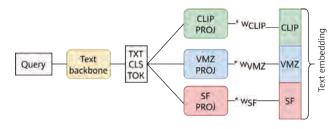

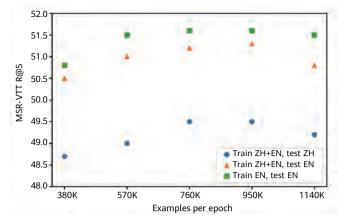

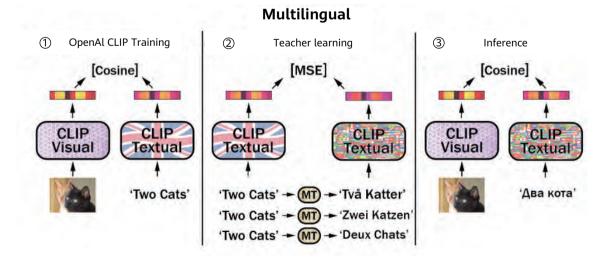

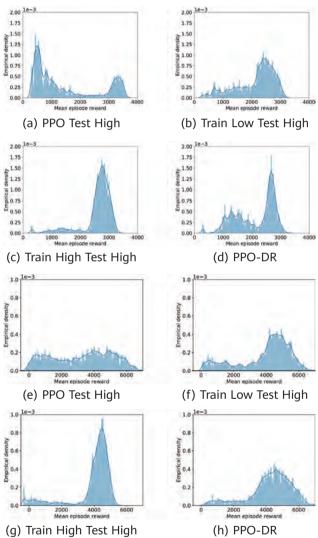

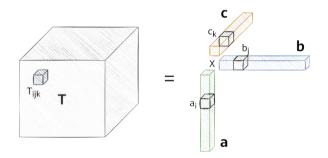

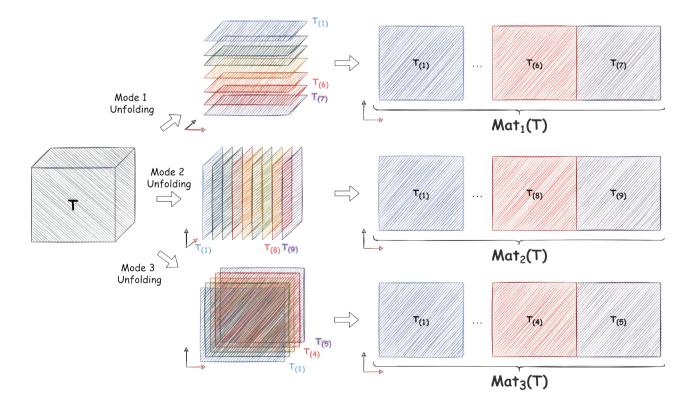

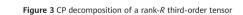

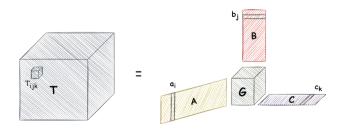

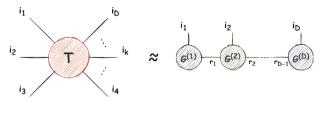

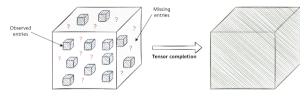

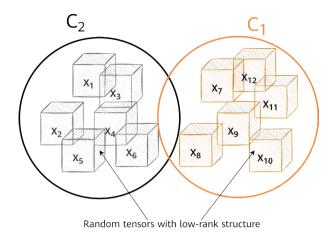

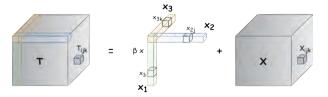

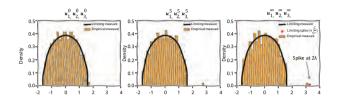

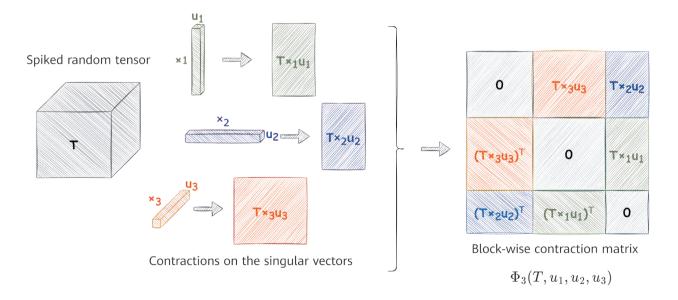

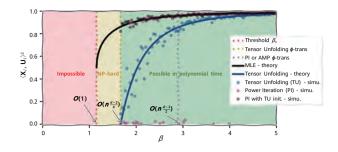

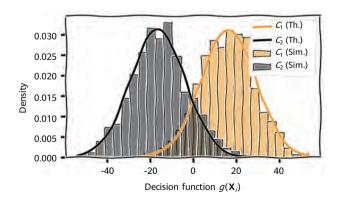

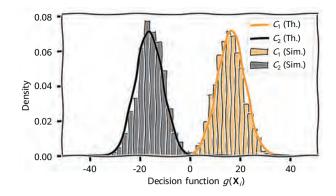

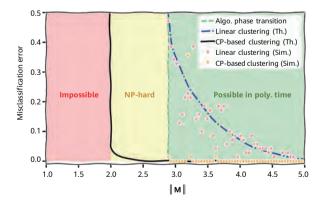

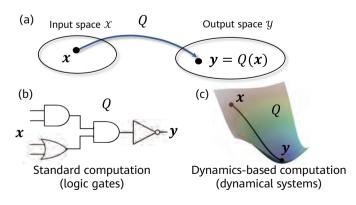

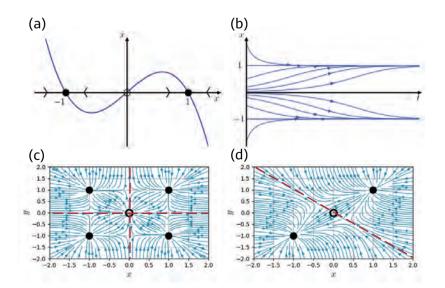

In multidomain multimodal AI algorithms, *MDMMT-2* delves into the analysis of datasets and training methodologies for text-image and text-video retrieval tasks. It introduces a sophisticated multistage training strategy for multilingual models, enhancing knowledge transfer efficiency and facilitating the use of noisy datasets during training without compromising prior knowledge integrity. *Wasserstein Robust Reinforcement Learning* proposes an innovative zero-order optimization method to address the max-min game in reinforcement learning, incorporating a constraint based on Wasserstein distance. This method demonstrates superior performance and efficiency in low- and high-dimensional MuJoCo environments. *Random Tensor Theory, Algorithms and Applications* comprehensively explores tensor properties and classical tensor decomposition methods. It examines the application of random tensor theory in evaluating the performance of supervised and unsupervised learning, highlighting the pivotal role of tensors in AI applications. *Dynamical Systems and Control Theory Perspective of Computation* presents a groundbreaking perspective, conceptualizing computation as a control system that transitions from an initial state to a desired output. This novel approach integrates dynamical systems and control theory. It offers a framework for designing hybrid physical systems that balance energy consumption and accuracy, paving the way for substantial energy savings in large-scale computational tasks.

fleng Liao

Heng Liao Chief Scientist of 2012 Labs

Editor-in-Chief: Heng Liao

**Executive Editor:** Heng Liao

#### **Editorial Board:**

Heng Liao, Wen Tong, Xinhua Xiao, Banghong Hu, Huihui Zhou, Feng Bao, Jeff Xu, Haibo Chen, Pinyan Lu, Jianbing Wang, Ruihua Li, Bo Bai

E-mail: HWResearch@huawei.com

### CONTENTS

# **Future Outlook**

Al for Science and Industry

02

Heng Liao, Linfeng Zhang, Lin Li

# **Technological Foundation**

| Spatial Computing: Scalable Computing Systems<br>Based on Computational Graphs                                                                                                      | 12 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tianqi Wang                                                                                                                                                                         |    |

| Reprioritizing Speculative Task-Level Parallelism                                                                                                                                   | 27 |

| Gilead Posluns, Yan Zhu, Guowei Zhang, Heng Liao, Mark C. Jeffrey                                                                                                                   |    |

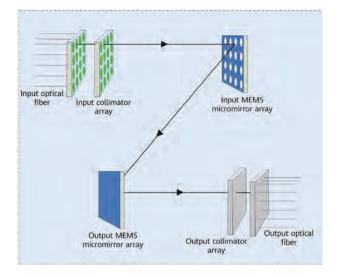

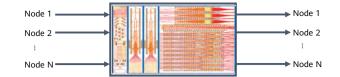

| Exploration of Hybrid Optical-Electrical Switching<br>Networks in AI Training Clusters                                                                                              | 42 |

| Shengyu Shen, Di Chen, Wenkai Ling, Jingyan Wang, Tianchi Hu,<br>Shanggang Xie, Tianxiang Chen, Yang Ren, Jifang He, Qihang Duan,<br>Zeshan Chang, Weibin Lin, Xin Liu, Guangcan Mi |    |

| Ascend HiFloat8 AI Training and Inference                                                                                                                                           | 76 |

| Yuanyong Luo, Richard Wu, Zhongxing Zhang, Minqi Chen,<br>Kai Zheng, Guanfu Chen, Chun Hang Lee, Sheng Yang                                                                         |    |

| DP SQRT Computation Principle and Ultra-Low<br>Latency Microarchitecture Design                                                                                                     | 99 |

Copyright © 2024 Huawei Technologies Co., Ltd. All rights reserved.

Yuanyong Luo, Zichao Long, Zhiyan Gu, Jianfeng Wang

# **Collaborative Optimization**

#### Balancing the Yin and Yang of Dynamic 113 Compilation and Execution

Maria Carpen-Amarie, Rene Mueller, Konstantinos Tovletoglou

| Data-Centric Auto-Tuning of High-<br>Performance Computing Applications | 133 |

|-------------------------------------------------------------------------|-----|

| Baicheng Yan, Giulio Stramondo, Zongyan Cao,<br>Zhe Wang, Long Wang     |     |

| Humble Heroes                                                           | 146 |

| A. N. Yzelman                                                           |     |

#### Asynchronous Training and MoRe: 171 Momentum Reconstruction for Reduced Memory Model Parallel Pipeline Training

Roman Talyansky, Zach Melamed, Pavel Kisilev, Ido Hakimi

# Computational Graph Representation191of Equations System Constructors inHierarchical Circuit Simulation

Zichao Long, Lin Li, Lei Han, Xianglong Meng, Chongjun Ding, Ruiyan Li, Wu Jiang, Fuchen Ding, Jiaqing Yue, Zhichao Li, Yisheng Hu, Ding Li, Heng Liao

# **Theory Frontiers**

| 207 |

|-----|

|     |

| 222 |

|     |

| 233 |

|     |

| 256 |

|     |

Jie Sun, Daniel Ebler, Leonarduzzi Roberto Fabio

# **AI for Science and Industry**

Heng Liao, Linfeng Zhang, Lin Li

#### Abstract

In practical terms, connectionist AI algorithms have — over the past decade — functioned as a more effective statistical modeling approach for non-physical modeling tasks such as image classification, image segmentation, and machine translation. The development of connectionist AI has given rise to many new industries and brought huge economic benefits to them and society as a whole. Al algorithms have quickly drawn wide attention from both academia and industry thanks to their ability to solve problems related to the aforementioned modeling tasks — such problems could not otherwise be solved by using physical (or rule-based) modeling methods, which had been a common practice over the past two centuries of scientific development. Throughout that time, though, many difficult yet important problems remain unsolved or have not been adequately addressed. Some of these problems cannot be solved using only traditional methods, and even directly applying AI-based statistical modeling methods fails to produce any practical outcome for most of them. Worse yet is the wide variety of applications in which these problems are involved: scientific and industrial problem modeling and solving; integration of computer graphics and multimedia technologies (e.g., building holographic multimedia representations and modeling 3D scenarios with a non-geometric approach); manufacturing intelligent devices that collaborate harmoniously with humans and complex environments, or developing robotics without using coordinate systems; using highly structured advanced knowledge systems to realize automatic Q&A for both open and closed domains, and automated theorem proving; and processing nonlinear system signals in the signal and system domain, and developing higher-accuracy modeling methods for doing so. In this article, we review existing research for these applications and provide further insights.

#### Keywords

high-performance computing, AI

# **1** Introduction

AI algorithms have created incredible economic value over the past decade thanks to their increasing applications in several key fields.

In the security protection field, AI algorithms have made significant strides in computer graphics — they are comparable to or even outperform humans in image classification, segmentation, compression, enhancement, and recognition. And thanks to improvements in massive data storage, reading, and retrieval, AI algorithms have had a major impact in not only facilitating but also enhancing security protection across society.

AI algorithms have also been instrumental in the field of mobile phone applications. Take the camera snapshot function of mobile phones as an example — AI-based image processing helps to effectively ensure the quality of photo snapshots.

Another field in which AI algorithms create significant value is the autonomous driving industry. Here, AI technologies are heavily utilized in modeling the environment of vehicles and road obstacles, as well as in performing sensing, prediction, decision-making, control, and battery management functions.

And in the Internet field, AI algorithms enable big data analytics to do a remarkably good job in user profiling, thereby allowing content to be more personalized in order to achieve a better Internet surfing experience for users.

Essentially, AI algorithms benefit immensely from a datadriven neural network architecture of deep learning and reinforcement learning where these algorithms are rooted. Unlike the analytical approach adopted by traditional computer algorithms, AI algorithms leverage big data statistics to solve problems in a much more effective way — this is even more noticeable when addressing certain types of problems that the traditional approach cannot solve. Nevertheless, the huge success of applying AI algorithms in the fields mentioned earlier also leads to a high homogeneity of research. So while researchers commit valuable resources to these key fields, they might inadvertently overlook other more important and difficult areas that require even larger investment.

This article focuses on several important areas where established science or existing AI technologies fail to fully solve certain problems. It will explore the following topics:

- A New Approach to Scientific Computing and Industrial Computing

- A Novel Method of Integrating Computer Graphics and Multimedia Technologies

- A Groundbreaking Paradigm of Developing Autonomous Robotics

- A Fresh Understanding on the Learning and Reasoning of Structured Knowledge

- Material Basis of AI

# 2 A New Approach to Scientific Computing and Industrial Computing

Experiments, theories, and computing have been and continue to be three of the most important factors in advancing human science, enabling us to obtain and expand our control over information, energy, and matter. Before big data analytics emerged, processing information reliably depended primarily on physical modeling that utilizes mathematical symbols. Physical models have been advantageous because they are simple and specific, allow deductive reasoning, partially support analytical and numerical computation, and — very importantly — some of them are quantitatively verifiable through experiments. For instance, once Newton defined the concepts of point mass, rigid body, and the like, he was able to derive his laws of motion using parameters (e.g., position and velocity) that originated from those defined concepts. In a complex system, however, what may first appear to be an advantage may actually be a disadvantage. To demonstrate this, assume we use an ideal, simplified model of "spherical chickens in a vacuum" to perform computation — this model cannot actually solve any real-world problems. Given that data acquisition, storage, and computing have all become exceptionally convenient today, is it now possible to further explore the value of information in a more effective and efficient way than if we were to use traditional physical modeling methods? We will explore this possibility by analyzing traditional applied mathematics - a subject that closely combines symbols and experiments. It is comprised of the following five main steps:

- Create a mathematical model for a domain problem.

- Find the analytical or numerical method for solving the problem.

- Convert the problem-solving process into a computer algorithm.

- Compile the algorithm as a software program.

- Optimize the algorithm and software iteratively, and implement large-scale parallelization.

# 2.1 Creating a Mathematical Model for a Domain Problem

Data is a product of "intelligence." But despite data storing the essence of intelligence information, it does so in quite a fragmented way. Due to the lack of effective methods for capturing salient information from data, human civilization has struggled throughout history. Traditional mathematical modeling primarily involves finding abstract equivalent representations of things, such as concept definitions, hypothetical conditions, and mathematical relations. Even though the study of mathematical relations attracts the attention of most scholars, concept definitions and hypotheses essentially determine the quality and significance of traditional mathematical modeling. Let's look at two typical examples — Kepler's Laws of Planetary Motion and Newton's Laws of Motion. Using a geometric language conceived by René Descartes, Kepler's Laws explain the motion of planetary bodies through the mathematical relations of several concepts such as planetary coordinates, time, and orbital parameters. Newton's Laws go one step further by coining the terms of mass, action relationship, and acceleration. Among them, the concept of "mass" unifies the measurement of all substances, meaning that all objects — from those as big as the Sun and the Moon to those as small as apples and oranges — can be measured by just one dimension, namely, their mass. Such symbolic abstractions, both mathematical and physical ones, are adopted by many scientific masterpieces, including Euclid's Elements written before antiquity, Newton's Mathematical Principles of Natural Philosophy in the 17th century, and Einstein's General Relativity in the 20th century. Similarly, Galois' group theory proposed in the 19th century unifies the algebraic structures with the concept of group. Later, quantum mechanics and quantum electrodynamics emerged to unify the action relationships between inorganic matters in nature through four fundamental interactions. This kind of representation, achieved in an "equivalent" or "unified" manner, has demonstrated remarkable advantages in the induction, deduction, and spreading of science throughout human civilization.

At the substance level, equivalent representation of action relationships has brought fundamental changes to society. Yet at the consciousness (or human intelligence) level, we still lack a unified representation that proves effective for modeling. On the one hand, it is impossible to acquire parameters from within the system — in this case, the human brain. On the other hand, rules summarized by humans do not perform well enough to address problems in open domains. For instance, in the early stages of development (in the 1950s), machine translation adopted a grammar rule-based approach (i.e., one based on expert knowledge) and consequently struggled to develop further due to the inefficiency of rule-based systems. It was not until data-driven statistical methods were employed in the 1990s that machine translation began to deliver satisfactory performance. Although such modeling methods drove breakthroughs in speech recognition and text recognition, their value was not fully realized at that time because the capabilities of storing, reading, and processing big data still needed to be perfected. Later in 2012, data-driven neural networks emerged and demonstrated compelling performance in classification. Since then, statistical modeling based on neural networks has been creating unprecedented value in many fields.

The rapid development of neural network methods leads us to ask ourselves: What makes AI technologies so special? And what are the advantages and disadvantages of AI methods with respect to their technical principles? The currently popular "Datasets + Neural network architecture + Gradient backpropagation" approach is actually an automated "Modeling + Training + Generalization & inference" framework designed for specific high-dimensional problems. The core philosophy of such a framework in terms of problem solving is "to make an assumption and verify it."

As an example, let's look at the modeling of an image classification problem. For a given set of images, the input dimensionality is d = 3 \* 224 \* 224, and an expectation function based on L1 loss is used as the target function. According to the universal approximation theorem, the approximation error of neural network fitting is independent of the input dimensionality. We can therefore use neural networks to model high-dimensional problems [1]. Weinan E et al. also analyzed in further detail the performance of two-layer neural networks and that of residual networks in Barron space and flow-induced function space separately [2].

Gradient disappearance and dispersion are two factors that we may encounter during the training of neural networks. However, we can address them by respectively selecting an appropriate activation function (e.g., the popular ReLU function) and normalizing parameters. For a neural network that has many layers, the training effect may not meet

expectations — in this case, we can use a residual neural network (ResNet) to ensure the relevance of gradients [3]. In the case of an *L*-laver network, the attenuation of gradient relevance in a PlainNet without residual representation is  $\frac{1}{2^L}$ , and that of a ResNet is only  $\frac{1}{\sqrt{L}}$  [4]. A ResNet is also more flexible in terms of its representation capability, and performs especially well in the selection and combined use of shallow and deep features. With these advantages, a ResNet is more suitable for learning from large datasets. From this, we can conclude that there is very little logical reasoning or deduction involved in the process of fixing training issues. Instead, theoretical analysis is often conducted on a solution that has been verified as valid through experiments. As such, we can determine that the ResNet representation of image classification problems provides us a better loss landscape [5] and considerably reduces the difficulty involved in gradient optimization. Even so, these advantages have yet to be theoretically proven in a strict sense.

Nevertheless, the main difficulty encountered in data-driven and AI-based statistical modeling lies in the generalization capability of models. Even if the previous training issues are addressed, the resulting models will still depend strongly on training data. Intuitively, we can see that the difficulty of generalizing a model goes up as the actual environment of inference and the training data become more and more dissimilar. The generalization predicament also occurs in traditional physical modeling — the most typical example of this is that Newtonian mechanics at the macro level does not apply to quantum mechanics at the micro level. Things become worse or even disastrous when we perform inference with an AI-based neural network model. This is because we cannot determine the scenario applicability (i.e., the generalization capability) of a model until the results of inference are verified. Theoretically, we can use the Rademacher complexity to describe a model's capability of fitting random noise on a given dataset. However, the bound provided by the Rademacher complexity can barely match real-world scenarios. Such difficulties are major factors that hinder the generalization of models. Is there a way to combine established science with big data-based AI technologies that are widely used today, so that we can find a "unified" information processing technology that brings higher efficiency and hence alleviate — to the largest degree practicable — the model generalization predicament of high-dimensional problems? Without a ready answer to this question, we can still study the following successful cases in industry to see whether they offer us some insights, either physically or mathematically.

- In what way is the Transformer architecture [6], which adopts a self-attention mechanism, similar to the action mechanism of universal gravitation and Coulomb force?

- How can we guarantee the equivariance of 3D rototranslations [7] during the training of a neural network?

- Using side length restrictions of triangles, can we improve the method of training agent models for protein structure generation [8], such that AlphaFold2 will reach a computational accuracy comparable to experimental results?

- Can momentum knowledge be leveraged to improve gradient optimization algorithms [9]?

Using implicit knowledge in big data to facilitate modeling remains an open and long-term undertaking. Now we explore several typical unsolved industrial problems, for which using the AI approach is expected to achieve breakthroughs.

#### **OPC Modeling**

To model the optical proximity correction (OPC) process of a lithography machine, for instance, the traditional method builds a physical model for each lens and then stacks these models. This method, while allowing us to obtain adequate results under relatively low accuracy requirements, is no longer effective when lenses approach their optical limits and the system becomes notably affected by factors such as temperature and lens imperfections. One possible approach of overcoming this issue is to construct a hybrid model that combines the deep neural network model and the traditional physical model. This approach has been preliminarily verified as effective — as such, it is fair to say that introducing AI methods in traditional modeling may bring very good results.

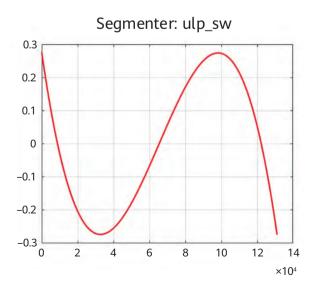

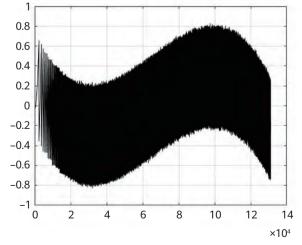

#### **Optical Communication Module Modeling**

In an optical-electrical conversion system used in optical communication, the presence of non-linear physical signals can cause dynamic damages and consequent coupling of the damages. As a result, the classical method of signal processing and modeling is unable to accurately model the signal conversion process and often produces a high bit error rate. Using AI technologies can help rectify the defects found in the physical models created for optical communication. With the novel AI approach, we can treat an optical-electrical conversion system as a non-linear waveform transformation function. By using it, we can directly predict waveform transformation and therefore parse specific resulting

#### 🛞 | Future Outlook

effects based on the predicted waveform. Furthermore, AI can detect non-linear signals in signal patterns during the early stages of simulation, making it possible to apply a compensation algorithm accordingly. AI detection is much more accurate and efficient than manual identification, especially when we consider the microscopic nature of non-linear signals and the difficulty in intuitively perceiving such signals.

#### Astronomical Phenomena Modeling

In astronomy, radio telescopes like China's FAST (Fivehundred-meter Aperture Spherical Telescope) have profound capabilities of receiving and collecting signals, enabling the discovery of many astronomical phenomena such as pulsars and radio storms. Despite this, the signal processing capability of these telescopes falls far behind the speed at which they gather information — a performance bottleneck. In traditional signal processing, a radio telescope builds a physical model in the form of a time-frequency spectrogram that involves an unknown distance parameter. Waves of different frequencies spread at varied speeds, and these waves present distinct slopes in spectrogram signals. Leveraging these characteristics, scientists are able to determine the astronomical distance through a grid traversal of dispersion values or downsampling values, or by performing Gaussian fitting on the time axis. Nevertheless, this approach involves very high computational costs and is extremely inefficient.

Today, AI technologies offer the prospect of solving this problem. By labeling deterministic astronomical signal samples and learning from the labeled samples, we can directly determine signal waveforms in a graphical manner, enabling us to solve the astronomical distance based on the waveforms. This kind of problems involve a large amount of unlabeled data, in which case semi-supervised AI learning has demonstrated good performance. For example, a "distillation learning" algorithm can learn and train on de-dispersed data, and then transfer the resulting model to learn on non-de-dispersed data in order to provide predictions. Because blind search becomes feasible without the need to consider dispersion, such an algorithm considerably speeds up searches and can even realize realtime search. Likewise, semi-supervised positive-unlabeled learning (or PU learning) algorithms can effectively explore a large amount of unlabeled data at a reasonably low training cost by mixing the unlabeled data with labeled samples. PU learning algorithms have yielded discoveries of valid pulse signals and achieve a higher detection efficiency.

### 2.2 Problem Solving

Even with accurate physical modeling, solving highdimensional problems can still be catastrophic due to the absence of efficient methods. For instance, a method as powerful as the Schrödinger equation can only solve hydrogen atom problems accurately. To address this issue, academics have developed many approximation algorithms, for example, the density functional theory. The tradeoff between accuracy and computational complexity is always a thorny issue because we can never have both. As such, applying neural networks to solve high-dimensional partial differential equation (PDE) problems has naturally become a hot subject of research. This research is being conducted in the following two main directions.

First, we can use the dataset obtained through a traditional numerical solver to train a deep neural network, and then use this network as an agent simulator to achieve higher solving performance [10]. However, this approach does not allow theoretical analysis on accuracy bounds or convergence of solutions. Consequently, it does not provide any theoretical guarantee. In other words, this method provides only speculations for certain tasks that traditional methods fail to solve [11-13].

Second, we can use neural networks to learn mapping relationships between functions, and then use these mappings as operators for solving PDE problems. The two most typical research efforts in this regard are DeepONet [14] and the Fourier neural operator [15]. Once they are learned for an entire category of PDEs, these operators can be used directly for different initializations or bounds, without the need for retraining to be performed. Nonetheless, the specific PDE categories to which such operators are applicable still depends on further theoretical analysis [16, 17].

# **3 A Novel Method of Integrating Computer Graphics and** Multimedia Technologies

In computer graphics, an image is constructed and rendered based on a 3D geometric model in a coordinate system. Pixels are generated to form a corresponding image within geometric surfaces and grids, from a certain point of view or under specific illumination conditions. In multimedia processing, however, an image is generated after information collected from the real world is processed by the color filter array and sensors, followed by a series of post-processing (such as de-mosaicization, white balance, and gamma correction). These two image generation methods have developed in parallel over the course of more than two decades. Only now though is it possible to integrate them thanks to the introduction and popularization of AI technologies.

Traditional computer graphics renders images on the basis of mathematical and physical modeling that utilizes the optical process (e.g., rasterization and ray tracing) of camera photographing. To approach this differently, the neural radiation field (NeRF) [18–20] and multiplane image (MPI) [21-23] techniques, along with many of their subsequent works, use deep learning for image rendering. In this case, the rendering process directly treats the model of 3D objects and their scenario as a function, which takes incident rays as input values and provides an output of reflected light rays with specific color, intensity, and direction information to represent an image. By learning functional mapping through AI, 3D models and images can be directly connected to each other without the use of geometric elements. This integrated approach creates new possibilities for further development of multimedia, graphics, and even metaverses.

# 4 A Groundbreaking Paradigm of Developing Autonomous Robotics

Given the enormous applications of AI, it is only natural for us to think how we can enable more intelligence for machines or robots. Today's robots possess only simple and limited intelligence — their level of autonomy is far too weak to even complete tasks independently. Traditionally, we control robots by modeling their states and the environment in which they work based on a precise coordinate system. To put it differently, by using a robot's position, action, and state information collected through sensors and sensing algorithms, we can train a model with high-dimensional coordinates. As such, we can then use the model to predict and plan the robot's actions and the exact way in which each action happens (i.e., the path, distance, angle of movement, and so on). The planned information (i.e., instructions for the robot's next action) is then passed to the PID (Proportional-Integral-Derivative) controller for execution, with collaboration from the motor controller. This inefficient control process drastically limits the capabilities of robots compared to humans and animals.

Now that AI has demonstrated its breakthroughs in computer graphics, we can also apply AI methods in robot control. In other words, we can train an end-to-end, graphbased control model that does not require the use of a coordinate system — similar to the case with computer graphics we mentioned earlier. Using this model, a robot can directly take actions based on what it has observed and learned, much the same as a living creature does. For example, if we want a robotic arm to strike a ball like a professional baseball player, we can train the arm by repeatedly throwing baseballs at it — with a certain degree of variation in how it is thrown — so that the arm learns how to hit each baseball perfectly. A robotic arm trained in this way can strike a baseball on par with a professional in real baseball games. Most importantly, such training has been preliminarily proved as being effective.

# 5 A Fresh Understanding on the Learning and Reasoning of Structured Knowledge

In the Internet age, big data usually comes in the form of dynamic, unstructured, but strongly correlated texts. Many experts renowned in the field of AI do not advocate adopting the structured approach of knowledge learning. Instead, they believe that demand-driven, fragmented information ingestion benefits AI learning better and can yield an optimal learning effect. That being said, the human race over several thousands of years of civilization has adopted a process of extracting and accumulating structured knowledge from fragmented information. In particular, the emergence of languages and characters — as a typical and well-known structured symbol system — has profoundly accelerated the transmission of information, virtually broken the limitations of time and space in knowledge transfer, and substantially pushed our ability to exponentially accumulate knowledge. Therefore, learning and reasoning of structured knowledge could be the ultimate problem of AI development.

The development of AI relies on data, algorithms, compute power, and applications. Among these four factors, data is usually sufficient, compute power is attainable, and AI application scenarios are broad enough to guarantee a promising future, whereas AI algorithms now turn out to be a major bottleneck. Learning and reasoning of structured knowledge can be leveraged to effectively address this bottleneck, helping us to achieve AI algorithm breakthroughs. A knowledge learning system can use a weighted mapping network to efficiently express structured knowledge, which maps to specific objects in real life. Such a system should possess some kind of "memory" and use this memory to continuously store new knowledge. Using the stored knowledge, the system should be able to perform repeated reasoning on new problems and eventually solve them.

In the industry, many ultra-large models were proposed on the basis of the Transformer architecture mentioned in Section 2.1. As an example, the GPT3 model [24] launched in 2020 adopted a new prompting approach and demonstrated human-level capabilities in many humanities areas, such as writing articles and even poetry. Yet even a model as large as GPT3 could not adequately understand certain structured knowledge, of which mathematics is a very typical subject. Performance evaluations of [25] showed that models had only near-random accuracy for most science, technology, engineering, and mathematics (STEM) tasks.

Just one year later, however, researches utilizing humanlike thinking (e.g., chain-of-thought prompting) emerged [26, 27], followed by works such as the Pathways Language Model (PaLM) [28] — a large language model that achieved scaling through the use of Pathways. Based on these works, the latest Minerva model [29] improved the accuracy of the MATH dataset (mathematics competition level for high school) [30] from 6.9% to 50.3% — compared to only 40% of an average high school student, after learning more than 1.2 million arXiv papers in LaTeX format and a large amount of mathematical knowledge in webpages.

Mathematical symbol-based calculation and theorem proving have been effectively contributing to improving AI's reasoning and prediction abilities. To learn the calculation of mathematical symbols and theorem proving, AI can adopt a human-like learning approach in order to solve problems with limited knowledge and complex reasoning skills. This ability, which extends limited knowledge to infinite applications, will enable AI to achieve automated exploration, learning, and prediction in many more open fields. Currently, AI has excelled in some simple calculation and theorem proving, such as symbolic calculation of trigonometric functions [31] and solving elementary schoollevel mathematical word problems. We expect that, in the future, AI will prove all theorems of advanced mathematics in a fully automated way. While this accomplishment will make AI capable of applying the knowledge it has learned, other optimization methods will take it to an even higher level. With theorem representation optimization through a hypertree [32], or with learning method optimization based on the GPT-f model [33] and Expert Iteration [34], Mathlib's tested inference accuracy for pass@1 has reached 63%, and a small number of International Mathematical Olympiad (IMO) contest questions have been successfully proved [34].

This AI approach based on structured knowledge also exhibits potential in solving open-domain problems. For example, an AI-based search engine can directly provide answers to some questions that require reasoning. This kind of search engine can actually be used as a chatbot [35], although such application may come at the expense of certain quality defects or sensitive issues. Such an AI approach kicks off the first yet critical step in solving opendomain problems.

# 6 Material Basis of AI

The development of AI naturally relies on a material foundation. Throughout the development of traditional CPUs, the material basis has involved a complete system of single-chip microcomputers, PCs, servers, and supercomputing centers. Likewise, humanity as a whole needs to work together and establish a full AI material system from 10-cent single-chip microcomputers to 1-billion-dollar supercomputing centers, in order to firmly sustain the rapid development of AI.

# References

- Y. Lu and J. Lu, "A universal approximation theorem of deep neural networks for expressing distributions," *CoRR*, vol. abs/2004.08867, 2020.

[Online]. Available: https://arxiv.org/abs/2004.08867

- [2] W. E, C. Ma, and L. Wu, "Barron spaces and the compositional function spaces for neural network models," *CoRR*, vol. abs/1906.08039, 2019. [Online]. Available: http://arxiv.org/abs/1906.08039

- [3] K. He, X. Zhang, S. Ren, and J. Sun, "Deep residual learning for image recognition," *CoRR*, vol. abs/1512.03385, 2015. [Online]. Available: http:// arxiv.org/abs/1512.03385

- [4] D. Balduzzi, M. Frean, L. Leary, J. P. Lewis, K. W. Ma, and B. McWilliams, "The shattered gradients problem: If ResNets are the answer, then what is the question?" *CoRR*, vol. abs/1702.08591, 2017. [Online]. Available: http://arxiv.org/abs/1702.08591

- [5] H. Li, Z. Xu, G. Taylor, and T. Goldstein, "Visualizing the loss landscape of neural nets," *CoRR*, vol. abs/1712.09913, 2017. [Online]. Available: http:// arxiv.org/abs/1712.09913

- [6] A. Vaswani, N. Shazeer, N. Parmar, J. Uszkoreit, L. Jones, A. N. Gomez, L. Kaiser, and I. Polosukhin, "Attention is all you need," CoRR, vol. abs/1706.03762, 2017. [Online]. Available: http:// arxiv.org/abs/1706.03762

- [7] F. Fuchs, D. E. Worrall, V. Fischer, and M. Welling, "SE(3)-Transformers: 3D roto-translation equivariant attention networks," in Advances in Neural Information Processing Systems 33: Annual Conference on Neural Information Processing Systems 2020, NeurIPS 2020, December 6-12, 2020, virtual, H. Larochelle, M. Ranzato, R. Hadsell, M. Balcan, and H. Lin, Eds., 2020. [Online]. Available: https://proceedings.neurips.cc/paper/2020/hash/152 31a7ce4ba789d13b722cc5c955834-Abstract.html

- [8] J. Jumper, R. Evans, A. Pritzel, T. Green, M. Figurnov, O. Ronneberger, K. Tunyasuvunakool, R. Bates, A. Žídek, A. Potapenko, A. Bridgland, C. Meyer, S. Kohl, A. Ballard, A. Cowie, B. Romera-Paredes, S. Nikolov, R. Jain, J. Adler, and D. Hassabis, "Highly accurate

protein structure prediction with AlphaFold," *Nature*, vol. 596, pp. 1–11, 08 2021.

- [9] D. P. Kingma and J. Ba, "Adam: A method for stochastic optimization," in 3rd International Conference on Learning Representations, ICLR 2015, San Diego, CA, USA, May 7-9, 2015, Conference Track Proceedings, Y. Bengio and Y. LeCun, Eds., 2015. [Online]. Available: http://arxiv.org/ abs/1412.6980

- [10] M. Raissi, P. Perdikaris, and G. E. Karniadakis, "Physics informed deep learning (part I): Datadriven solutions of nonlinear partial differential equations," *CoRR*, vol. abs/1711.10561, 2017. [Online]. Available: http://arxiv.org/abs/1711.10561

- [11] J. Han, A. Jentzen, and W. E, "Overcoming the curse of dimensionality: Solving high-dimensional partial differential equations using deep learning," *CoRR*, vol. abs/1707.02568, 2017. [Online]. Available: http://arxiv.org/abs/1707.02568

- [12] H. Wang, L. Zhang, J. Han, and W. E, "DeePMD-kit: A deep learning package for many-body potential energy representation and molecular dynamics," *CoRR*, vol. abs/1712.03641, 2017. [Online]. Available: http://arxiv.org/abs/1712.03641

- L. Fang, P. Ge, L. Zhang, H. Lei, and W. E, "DeepN<sup>2</sup>: A deep learning-based non-newtonian hydrodynamic model," *CoRR*, vol. abs/2112.14798, 2021. [Online]. Available: https://arxiv.org/abs/2112.14798

- [14] L. Lu, P. Jin, and G. E. Karniadakis, "DeepONet: Learning nonlinear operators for identifying differential equations based on the universal approximation theorem of operators," *CoRR*, vol. abs/1910.03193, 2019. [Online]. Available: http:// arxiv.org/abs/1910.03193

- [15] Z. Li, N. B. Kovachki, K. Azizzadenesheli, B. Liu, K. Bhattacharya, A. M. Stuart, and A. Anandkumar, "Fourier neural operator for parametric partial differential equations," in 9th International Conference on Learning Representations, ICLR 2021, Virtual Event, Austria, May 3-7, 2021. OpenReview. net, 2021. [Online]. Available: https://openreview. net/forum?id=c8P9NQVtmnO

- [16] S. Lanthaler, S. Mishra, and G. E. Karniadakis, "Error estimates for DeepONets: A deep learning framework in infinite dimensions," *CoRR*, vol. abs/2102.09618, 2021. [Online]. Available: https:// arxiv.org/abs/2102.09618

- [17] N. Kovachki, S. Lanthaler, and S. Mishra, "On universal approximation and error bounds for Fourier neural operators," *J. Mach. Learn. Res.*, vol. 22, pp. 290:1–290:76, 2021. [Online]. Available: http: //jmlr.org/papers/v22/21-0806.html

- [18] B. Mildenhall, P. P. Srinivasan, M. Tancik, J. T. Barron, R. Ramamoorthi, and R. Ng, "Nerf: Representing scenes as neural radiance fields for view synthesis," *Commun. ACM*, vol. 65, no. 1, pp. 99–106, 2022. [Online]. Available: https://doi.org/10.1145/3503250

- [19] T. Müller, A. Evans, C. Schied, and A. Keller, "Instant neural graphics primitives with a multiresolution hash encoding," *CoRR*, vol. abs/2201.05989, 2022. [Online]. Available: https://arxiv.org/abs/2201.05989

- [20] M. Tancik, V. Casser, X. Yan, S. Pradhan, B. Mildenhall, P. P. Srinivasan, J. T. Barron, and H. Kretzschmar, "Block-nerf: Scalable large scene neural view synthesis," *CoRR*, vol. abs/2202.05263, 2022. [Online]. Available: https://arxiv.org/abs/2202.05263

- [21] T. Zhou, R. Tucker, J. Flynn, G. Fyffe, and N. Snavely, "Stereo magnification: Learning view synthesis using multiplane images," *ACM Trans. Graph.*, vol. 37, no. 4, p. 65, 2018. [Online]. Available: https://doi. org/10.1145/3197517.3201323

- [22] B. Mildenhall, P. P. Srinivasan, R. O. Cayon, N. K. Kalantari, R. Ramamoorthi, R. Ng, and A. Kar, "Local light field fusion: Practical view synthesis with prescriptive sampling guidelines," *ACM Trans. Graph.*, vol. 38, no. 4, pp. 29:1–29:14, 2019. [Online]. Available: https://doi.org/10.1145/3306346.3322980

- J. Flynn, M. Broxton, P. E. Debevec, M. DuVall, G. Fyffe, R. S. Overbeck, N. Snavely, and R. Tucker, "DeepView: View synthesis with learned gradient descent," in *IEEE Conference on Computer Vision and Pattern Recognition, CVPR 2019, Long Beach, CA, USA, June 16-20, 2019.* Computer Vision Foundation / IEEE, 2019, pp. 2367–2376. [Online]. Available: http://openaccess.thecvf.com/content\\_

CVPR\\_2019/html/Flynn\\_DeepView\\_View\\_ Synthesis\\_With\\_Learned\\_Gradient\\_Descent\\_ CVPR\\_2019\\_paper.html

- [24] T. B. Brown, B. Mann, N. Ryder, M. Subbiah, J. Kaplan, P. Dhariwal, A. Neelakantan, P. Shyam, G. Sastry, A. Askell, S. Agarwal, A. Herbert-Voss, G. Krueger, T. Henighan, R. Child, A. Ramesh, D. M. Ziegler, J. Wu, C. Winter, C. Hesse, M. Chen, E. Sigler, M. Litwin, S. Gray, B. Chess, J. Clark, C. Berner, S. McCandlish, A. Radford, I. Sutskever, and D. Amodei, "Language models are few-shot learners," in *Advances in Neural Information Processing Systems 33: Annual Conference on Neural Information Processing Systems 2020, NeurIPS 2020, December 6-12, 2020, virtual*, H. Larochelle, M. Ranzato, R. Hadsell, M. Balcan, and H. Lin, Eds., 2020. [Online]. Available: https://proceedings.neurips.cc/paper/2020/hash/1457 c0d6bfcb4967418bfb8ac142f64a-Abstract.html

- [25] D. Hendrycks, C. Burns, S. Basart, A. Zou, M. Mazeika, D. Song, and J. Steinhardt, "Measuring massive multitask language understanding," in 9th International Conference on Learning Representations, ICLR 2021, Virtual Event, Austria, May 3-7, 2021. OpenReview.net, 2021. [Online]. Available: https://openreview.net/ forum?id=d7KBjml3GmQ

- [26] J. Wei, X. Wang, D. Schuurmans, M. Bosma, E. H. Chi, Q. Le, and D. Zhou, "Chain of thought prompting elicits reasoning in large language models," *CoRR*, vol. abs/2201.11903, 2022. [Online]. Available: https://arxiv.org/abs/2201.11903

- [27] X. Wang, J. Wei, D. Schuurmans, Q. V. Le, E. H. Chi, and D. Zhou, "Self-consistency improves chain of thought reasoning in language models," *CoRR*, vol. abs/2203.11171, 2022. [Online]. Available: https:// doi.org/10.48550/arXiv.2203.11171

- [28] A. Chowdhery, S. Narang, J. Devlin, M. Bosma,

G. Mishra, A. Roberts, P. Barham, H. W. Chung,

C. Sutton, S. Gehrmann, P. Schuh, K. Shi, S.

Tsvyashchenko, J. Maynez, A. Rao, P. Barnes, Y.

Tay, N. Shazeer, V. Prabhakaran, E. Reif, N. Du,

B. Hutchinson, R. Pope, J. Bradbury, J. Austin, M.

Isard, G. Gur-Ari, P. Yin, T. Duke, A. Levskaya, S.

Ghemawat, S. Dev, H. Michalewski, X. Garcia, V.

Misra, K. Robinson, L. Fedus, D. Zhou, D. Ippolito, D. Luan, H. Lim, B. Zoph, A. Spiridonov, R. Sepassi, D. Dohan, S. Agrawal, M. Omernick, A. M. Dai, T. S. Pillai, M. Pellat, A. Lewkowycz, E. Moreira, R. Child, O. Polozov, K. Lee, Z. Zhou, X. Wang, B. Saeta, M. Diaz, O. Firat, M. Catasta, J. Wei, K. Meier-Hellstern, D. Eck, J. Dean, S. Petrov, and N. Fiedel, "Palm: Scaling language modeling with pathways," CoRR, vol. abs/2204.02311, 2022. [Online]. Available: https:// doi.org/10.48550/arXiv.2204.02311

- [29] A. Lewkowycz, A. Andreassen, D. Dohan, E. Dyer, H. Michalewski, V. Ramasesh, A. Slone, C. Anil, I. Schlag, T. Gutman-Solo, Y. Wu, B. Neyshabur, G. Gur-Ari, and V. Misra, "Solving quantitative reasoning problems with language models," 2022.

- [30] D. Hendrycks, C. Burns, S. Kadavath, A. Arora, S. Basart, E. Tang, D. Song, and J. Steinhardt, "Measuring mathematical problem solving with the MATH dataset," in Proceedings of the Neural Information Processing Systems Track on Datasets and Benchmarks 1, NeurIPS Datasets and Benchmarks 2021, December 2021, virtual, J. Vanschoren and S. Yeung, Eds., 2021. [Online]. Available: https://datasets-benchmarksproceedings.neurips.cc/paper/2021/hash/ be83ab3ecd0db773eb2dc1b0a17836a1-Abstractround2.html

- [31] Z. Liu, Y. Li, Z. Liu, L. Li, and Z. Li, "Learning to prove trigonometric identities," arXiv e-prints, p. arXiv:2207.06679. Jul. 2022.

- [32] G. Lample, M. Lachaux, T. Lavril, X. Martinet, A. Hayat, G. Ebner, A. Rodriguez, and T. Lacroix, "Hypertree proof search for neural theorem proving," CoRR, vol. abs/2205.11491, 2022. [Online]. Available: https://doi.org/10.48550/arXiv.2205.11491

- [33] S. Polu and I. Sutskever, "Generative language modeling for automated theorem proving," CoRR, vol. abs/2009.03393, 2020. [Online]. Available: https://arxiv.org/abs/2009.03393

- [34] S. Polu, J. M. Han, K. Zheng, M. Baksys, I. Babuschkin, and I. Sutskever, "Formal mathematics statement curriculum learning," CoRR, vol. abs/2202.01344, 2022. [Online]. Available: https://arxiv.org/abs/2202.01344

[35] R. Thoppilan, D. D. Freitas, J. Hall, N. Shazeer, A. Kulshreshtha, H. Cheng, A. Jin, T. Bos, L. Baker, Y. Du, Y. Li, H. Lee, H. S. Zheng, A. Ghafouri, M. Menegali, Y. Huang, M. Krikun, D. Lepikhin, J. Qin, D. Chen, Y. Xu, Z. Chen, A. Roberts, M. Bosma, Y. Zhou, C. Chang, I. Krivokon, W. Rusch, M. Pickett, K. S. Meier-Hellstern, M. R. Morris, T. Doshi, R. D. Santos, T. Duke, J. Soraker, B. Zevenbergen, V. Prabhakaran, M. Diaz, B. Hutchinson, K. Olson, A. Molina, E. Hoffman-John, J. Lee, L. Aroyo, R. Rajakumar, A. Butryna, M. Lamm, V. Kuzmina, J. Fenton, A. Cohen, R. Bernstein, R. Kurzweil, B. Aguera-Arcas, C. Cui, M. Croak, E. H. Chi, and Q. Le, "Lamda: Language models for dialog applications," CoRR, vol. abs/2201.08239, 2022. [Online]. Available: https://arxiv.org/abs/2201.08239

# Spatial Computing: Scalable Computing Systems Based on Computational Graphs

Tianqi Wang

#### Abstract

Semiconductor manufacturing is still developing but results are being delivered at a slower pace. Emerging applications, like AI, are demanding exponentially more and more computing power. Processors based on the traditional von Neumann architecture are suffering from the constraints of the memory wall and power wall. And the overhead involved in maintaining the shared-memory model is increasing rapidly, making it more difficult to scale out computing systems. These factors make it impossible to meet the demand of applications for computing power. In terms of scalability, spatial computing — which uses the distributed memory system — is increasingly used to build high-performance computing systems. This paper summarizes the existing progress and challenges of spatial computing and briefly introduces HiSilicon's ongoing research on the applications, programming models, and computational graph partitioning and mapping of spatial computing.

#### Keywords

spatial computing, high performance computing, AI

# 1 Introduction

Research into computer architecture has continued to advance as semiconductor manufacturing processes and application algorithms evolve. And the advancement of semiconductor manufacturing processes following Moore's Law is facilitating transistor manufacturing. Moreover, growing application algorithms manage to convert the computing power of transistors into actual productivity. On top of that, research into computer architecture has led to the development of more efficient organization methods, paving the way for transistors to achieve more effective computing power.

Spatial computing is one of the most valuable research directions of computer architectures. This paper illustrates the necessity of application of "More than Moore" — a new paradigm for computing power growth — in the research of computing system architecture from the application algorithm and manufacturing process perspectives. It also dives into the potential of spatial computing, an architecture of "More than von Neumann" that might provide extra computing power in the future. The paper then summarizes the current work and challenges in spatial computing architecture, and outlines the spatial computing research of the HiSilicon research team in fields such as application scenario analysis, programming model, and computational graph deployment.

# 1.1 More Than Moore

Moore's Law observes a virtuous cycle of economy where user consumption drives investment, which then fuels technological progress, and then the resulting product improvements and upgrades attract further user consumption. However, the development of semiconductor manufacturing processes lacks fuel. As such, the virtuous cycle is on the brink of collapse. That is, the slowdown of technological progress attracts fewer new users, making it difficult to draw enough investment in technological progress, and this in turn results in slower technological progress. Figure 1 illustrates these virtuous and vicious cycles.

As mentioned earlier. Moore's Law is essentially a commitment to stable growth that attracts continuous investment from social resources. What unequivocally attracts continuous social investment is not the growth of nominal parameters, but that of available computing power essentially, the better life it brings. Thus, computing power is facing mounting challenges in cutting-edge fields related to the national economy and people's livelihoods. This is evident in numerous cases. For example, materials and drug design relies on the computational processing of molecular dynamics or computational chemistry to simulate system evolution [2]. The design and control of internal combustion engines depend on accurate hydrodynamics and structural mechanics modeling [3]. Accurate weather forecast and earthquake warning cannot be divorced from fast and precise geophysical simulation [4]. And accurate simulation and real-time control of electromagnetic fields make controlled nuclear fusion possible [5].

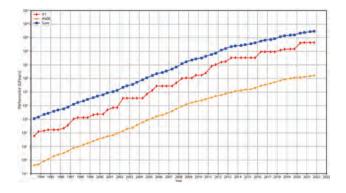

Numerical solutions of partial differential equations, such as the finite element method, have made outstanding achievements in scientific computing. But today, these conventional methods are not advanced enough to handle sophisticated issues, such as simulating complex chemical reactions or phenomena of turbulence and shock waves, and modeling phase transition processes. They fail to generate accurate computing results for large-scale systems and even get stuck during the initial stages. The major obstacle lies in the complex system and physical process as they depend on too many variables. When high-dimensional functions are used to represent the system, the curse of dimensionality arises, resulting in the inability to solve problems. As shown in Figure 2, the performance of the top 500 supercomputers has improved 1000-fold in the space of 10 years, from 2005 to 2015. If three-dimensional grids had been used to solve partial differential equations, only a tenfold increase of the grid resolution could have been achieved over the same 10-year period, not to mention the complex algorithm of the equation solver, which could further lower the final resolution improvement. The curse of dimensionality is substantially rooted in function approximation, a

Figure 1 Virtuous cycle and vicious cycle of Moore's Law [1]

Figure 2 Computing power survey of the top 500 supercomputers [6]

conventional method to handle issues with high complexity and low generalization based on polynomial functions and piecewise functions.

The AI method has been successfully applied in extensive fields such as image classification and natural language processing. At the same time, the AI method has been widely introduced into the scientific computing fields mentioned earlier and achieved a series of remarkable achievements. From the point of view of computational mathematics, the AI method provides an effective tool to solve high-dimensional mathematical problems. Given that the target approximation error is  $\epsilon$ , the dimension of the problem to be solved is d, and the total number of parameters required for approximate modeling is m. The convergence rate of the traditional polynomial approximation will be  $\epsilon \sim m^{-1/d}$ . That is, when the error  $\epsilon \sim 0.1$ , the total number of parameters required is  $m \sim 10^d$ . However, the convergence rate of AI modeling based on neural networks is  $\epsilon \sim m^{-1/2}$ . That is, when the error  $\epsilon \sim 0.1$ , the total number of parameters required is only  $m \sim 10^2$ .

The application scope of the AI method is limited due to its intrinsic nature of inexplicability. However, the AI method can contribute to solving some highly complex problems that other methods cannot solve. For example, analytical methods cannot simulate the scale of meaningful problems (such as first-principle simulation of organic chemical reactions) [2] within an acceptable period of time. Another example is that current analytical methods provide unstable solutions, requiring the introduction of many phenomenological methods (such as simulation of turbulent flows and phenomenological theory in high energy physics) [3]. These phenomenological methods depend on the experience or intuition of scientists, while the contemporary AI method can systematically improve the expression capability of empirical phenomenological models. In addition, the AI method is widely used in

engineering practices that need to control the experimental system in real time. For example, in a magnetic confinement fusion experiment that mandates accurate control of the magnetic field position, the conventional high-precision electromagnetic field solution cannot achieve real-time control. Consequently, phenomenological models of many empirical parameters are used [5].

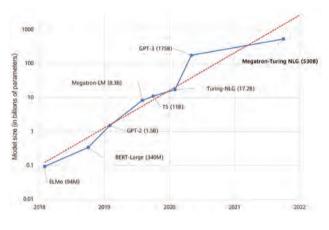

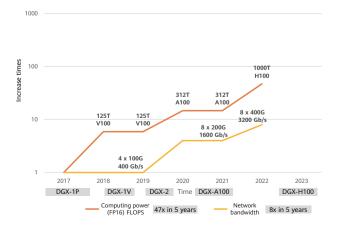

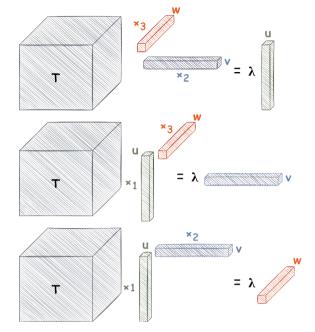

No pain, no gain, as the saying goes. Although the AI method has the potential to solve cutting-edge problems in science and engineering, it requires that larger-scale AI networks be built for complex systems such as natural language processing (NLP) and multiphysics. As shown in Figure 3, AI model sizes have increased by nearly four orders since 2018, posing new challenges to inference and training systems of AI networks. *This drives computing system designers to adopt "More than Moore" — a computing power growth paradigm much faster than Moore's Law based on existing semiconductor manufacturing processes.*

Figure 3 AI model size growth by time [7]

### 1.2 More Than von Neumann

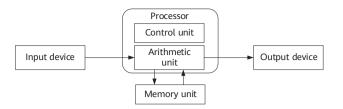

Turing's paper in 1936 gave a precise mathematical description of the Turing machine and explored the boundary of the computable problem of the Turing machine [8]. As shown in Figure 4, the Turing machine consists of seven basic elements: a group of architectural states Q, a

Figure 4 Basic elements of a general-purpose Turing machine

Figure 5 Traditional von Neumann architecture

set of input characters  $\Sigma$ , a set of paper tape characters  $\Gamma$ , a set of state transition functions  $\delta$ , an initial state q0 within Q, an acceptance state  $q_{accept}$ , and a rejection state  $q_{reject}$ .

However, Turing did not dive into the implementation strategy of the Turing machine. It was von Neumann who proposed a realizable architecture of the Turing machine. In Figure 5, the von Neumann architecture defines a basic architecture including a control unit, arithmetic unit, and memory unit, meaning that it defines a method for implementing the aforementioned seven basic elements such as the architecture state Q and the state transition function  $\delta$  in a Turing machine. This method has been highly applicable despite the constraints of the digital circuit technology and semiconductor technology at that time, and has become the cornerstone of traditional computer architecture research.

The success of Moore's Law stems from its commitment to stable growth. Accordingly, architecture designers must continuously improve the computing power of computing systems with a certain methodology. Based on the hardware processor of the von Neumann architecture, software developers have developed large and complex high-level software ecosystems, which are even more expensive than hardware systems. The traditional von Neumann architecture agrees on a set of interfaces for software and hardware, including the instruction set architecture (ISA) and shared

memory model, and separates their design. As such, hardware and software can be developed independently and smoothly inherit the existing software. Within this system, the compiler acts as a software-to-hardware mapping tool to design the controllable complexity, facilitating the success of the traditional architecture.

As modern semiconductor manufacturing processes and packaging technologies advance, obvious limitations are becoming apparent in the von Neumann architecture. Discrete memory and computing units lead to the memory and power consumption walls. Centralized control units also restrict system scalability. Assume that an application requires N transistors, the available transistor density is N, and the footprint of the computing system is *S*. Then,

$$N = \rho \times S \tag{1}$$

The growth rate of transistor scale *dN* is calculated based on those of transistor density  $d\rho$  and computing system footprint dS

$$dN = d\rho \times S + \rho \times dS \tag{2}$$

As mentioned earlier, the growth rate of unit transistor density resulting from Moore's Law is far from meeting the requirements of new applications such as AI ( $dN \gg d\rho$ ) x S). This requires computer architecture researchers to effectively and reliably organize transistors (in pursuit of a larger *dS*) in a larger footprint.

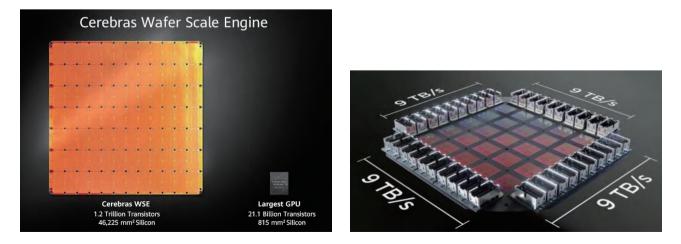

The rapid development of packaging technologies is an attempt to organize transistors in a larger footprint. In recent years, chiplet and wafer-scale technologies have been widely used by major chip enterprises in their own products. Traditional processor providers such as AMD, Intel, and NVIDIA have produced CPU and GPU chips based on

Figure 6 Cerebras CS-1 [9] (left) and Tesla DoJo [10] (right) based on the wafer-scale technology

#### 😹 | Technological Foundation

the chiplet technology. Some startups and cross-border enterprises have also developed exploratory products based on the wafer-scale technology, such as Cerebras CS-1/2 and Tesla DoJo in Figure 6.

The shared memory model of the traditional architecture can inherit the existing high-level software. A method of implementing shared storage is to maintain a logically shared memory model on physically distributed storage data by using a consistency protocol (e.g., the CHI protocol [11] of ARM and the TSO [12] of Intel). The synchronization of status information initiated by the consistency protocol should be performed without requiring programmer involvement, meaning that the synchronization must be completed *per unit time*. In a traditional architecture, the unit time is usually at the level of nanoseconds, which is the execution duration of instructions.

High-density transistors following the Moore's Law prediction can continuously improve the on-chip interconnect bandwidth. However, the on-chip interconnect latency cannot be continuously reduced due to the constraints of physical laws. *In order to enlarge the chip size while trying to maintain the coherence and consistency to inherit the existing software ecosystem, the traditional von Neumann architecture framework must be abandoned. That means it is necessary to ease the existing coherence protocol to some extent, and to increase the granularity from the instruction level to the task level per unit time.*

Although this change can open up a new path for continuous growth of computing power, it also implies a cost on the software stack. That is, programmers need to develop new applications based on a task-level programming model, or refactor existing code to adapt to new computing power. In addition, software architects are also facing new challenges in how to design and develop a set of tools based on new hardware abstraction or configurations to effectively schedule and manage computing tasks. High performance computing (HPC) has been challenging the potential of computing scalability, and some inspiring attempts have emerged in this field. Despite the difficulty involved in automatically converting existing codes into task-based descriptions, OmpSs/OpenMP has designed some task-based compiler directive statements to migrate codes successfully [13]. In areas where algorithms such as first principles and computational chemistry evolve rapidly for more computing power, scientists are willing to pay the cost of refactoring code. NAMD/NWChem is a typical task-based programming model of code refactoring [13].

# 2 From Spatial Computing to Computational Graphs

# 2.1 Spatial Computing in a Broader Sense

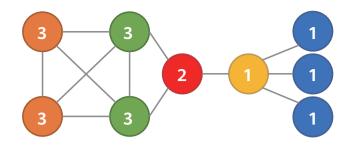

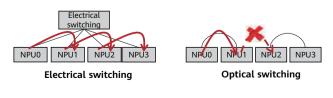

Figure 7a shows the processor architecture spectrum. Processors based on the conventional von Neumann architecture usually *use centralized control logic and shared memory or register files, exchange data between arithmetic logic units (ALUs) by accessing the shared memory*, and perform tasks in a time sequence of instruction fetching, data fetching, and execution, as shown in Figure 7b. In addition to the time dimension, the spatial computing architecture also considers the spatial dimension. That is, many processing engines (PEs) are integrated into a given space in order to execute tasks at the same time. They have *independent control logic and distributed memories, and data directly flows between these PEs*, as shown in Figure 7c.

Traditional spatial computing architectures use many simple PEs to form arrays in order to achieve a high degree of parallelism of application algorithms. These PEs can directly communicate with each other in a point-to-point manner without detouring from a shared memory. Each PE may be independently programmed, and dataflows are formed between PEs. CGRA and FPGA are typical

Figure 7 Processor system architecture spectrum [14]

examples of spatial computing architecture. Compared with the SIMD/SIMT architecture, the current spatial computing architecture processor is applicable to scenarios with significant producer-consumer dataflows (e.g., audio and video encoding and decoding, encryption, and communications).

As mentioned earlier, the decentralized control logic and distributed memory design of this architecture can fit into the physical implementation of hardware and achieve better scalability than the traditional von Neumann architecture does. However, in scenarios such as CGRA and FPGA, the PE granularity of a spatial computing processor is too small and lacks general programmability. It is difficult to carry a complex application with an obvious dynamic feature. Therefore, we attempt to expand the definition of spatial computing by replacing PEs with general-purpose processor cores in order to improve computing power and programmability. Our proposal ensures that multi-core processor clusters retain their dataflow design and work in pipeline mode. Spatial computing architectures such as CGRA and FPGA attempt to leverage fine-grained task-level parallelism in order to accelerate the computing process; the spatial computing architecture discussed in this paper aims to achieve better scalability using a similar distributed, decentralized design. This paper defines space computing in a broader sense — *it is dedicated to extending computing* tasks to a larger space at the architecture level. Therefore, this paper focuses on scenarios that require high scalability, such as high performance computing and AI training.

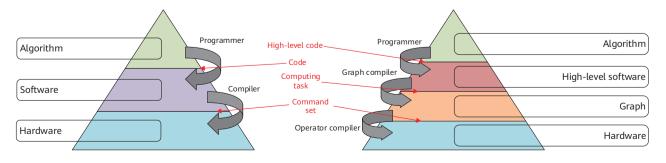

### 2.2 Abstract Layers of Computational Graphs

As shown on the left of Figure 8, research on the architecture is looking for a method M that maps a mathematical algorithm A to a physical implementation P, that is, P=M(A). The traditional architecture, however, adds an abstraction layer (/) of ISA to divide the mapping into two phases — the software compilation phase (SW) from algorithm to ISA, and the hardware implementation phase (HW) from ISA to physical implementation, that is, I =SW(M), and P = HW(I).

Based on the previous discussion, research into computer architecture is facing the following major challenges:

- Although the AI method provides new tools that can solve real-world problems, it significantly increases the complexity of algorithms.

- The growth rate of transistor density slows down and new packaging technologies such as chiplet and waferscale technologies are introduced.

- As the complexity of algorithm A and physical implementation *P* increases dramatically, the mapping *M* from the algorithm to physical implementation is facing a dimensional explosion in complexity.

Complexity is an inexhaustible objective presence caused only by defects in architecture design. As an aphorism of David Wheeler goes, "All problems in computer science can be solved by another level of indirection" [15]. As shown on the right of Figure 8, there is an attempt to add an abstraction layer of the computational graph G between the ISA and the algorithm layer. That is, the algorithm M is mapped to the computational graph *G* through the graph compiler GC. The computational graph is converted into the ISA by the operator compiler OC. The hardware architecture completes the physical implementation, that is, G = GC(M), I = OC(G), and P = HW(I).

In the new abstraction layer of computational graphs, the complexity of operators is shielded, and the dependencies between tasks as well as the input and output data are explicitly represented. Such a design coarsens the granularity of computation expressions of loads from the instruction level to the task level. In the traditional system architecture, the software compilation (SW) with dimensional explosion in complexity is divided into graph compilation (GC)

Figure 8 Abstract layers of the traditional system architecture (left) and spatial computing system (right)

#### 😹 | Technological Foundation

and operator compilation (OC). In the phase of graph compilation, higher load granularity and explicit information can help graph optimization tools achieve efficient computing load deployment over a larger space.

# 3 Research Progress in the Industry

The industry has been exploring the boundaries of scalability with HPC for decades, providing significant reference value. The traditional cluster-level parallelism solution based on the programming model of message passing interface (MPI) and open multi-processing (OpenMP) has the following limitations in the HPC field:

- Poor programmability: MPI requires programmers to manually process data segmentation and load balancing, meaning that programming is reliant on the experience of a minority of professional programmers.

- Poor performance portability: Different supercomputing clusters have different hardware architectures.

High scalability requires programmers to adapt an optimization solution to hardware.

- Difficult load balancing: Load imbalance, which causes low computing power utilization, occurs in strongly dynamic applications (such as sparse matrix computation, finite element analysis, and molecular dynamics simulation) when the process-thread model

(i.e., MPI-OpenMP model) can only express coarse parallel granularity and the scheduling policy is fixed.

Due to these limitations, a series of graph-based solutions are proposed in the HPC field to bridge the gap between programmability and performance, and achieve better load balancing. The methods used in this field also involve programming models, runtime systems, and hardware acceleration. This section discusses several successful practices.

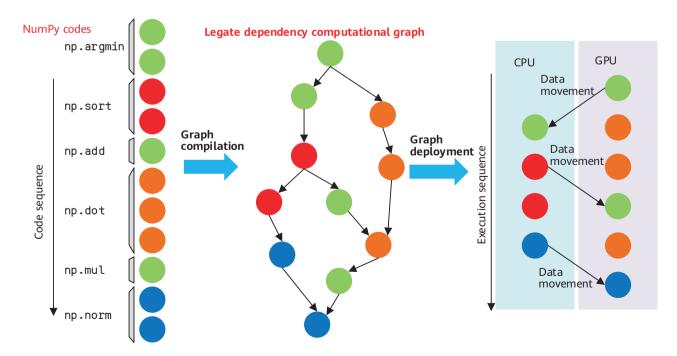

# 3.1 Legate

Legate, jointly developed by NVIDIA and Stanford University, can automatically deploy NumPy programs to heterogeneous distributed computing clusters. Legate is implemented on top of the Legion runtime system. Figure 9 [16] shows the Legate's rationale.

Programmers simply call NumPy to implement algorithms by means of serial programming. The compiler uses each NumPy function call as an operator to analyze data dependencies between NumPy function calls, and to generate a computational graph in order to show the dependencies. First, the computational graph is submitted to the Legion runtime system. Then, Legate Mapper maps the graph and makes it run on heterogeneous computing clusters of different scales. Experiment results show that although Legate significantly underperforms compared with the manually tuned MPI, programmers can leverage Legate

Figure 9 NumPy code sequence input by Legate (left), intermediate representation of Legate graph (middle), and physical deployment of Legate graph (right) [16]

to scale up from a single GPU to a cluster with multiple GPU enclosures, without needing to deal with complex parallel programming.

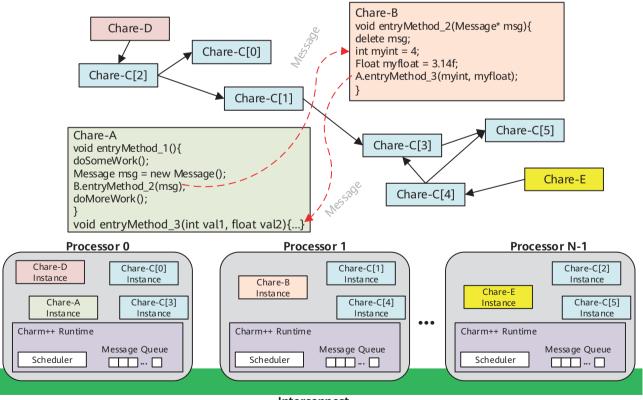

## 3.2 Charm++

Charm++ is a parallel programming framework developed by the University of Illinois Urbana-Champaign (UIUC). This object-oriented framework adopts the asynchronous messaging mechanism, as shown in Figure 10. Programmers can create a series of chare-objects that allow concurrent and asynchronous execution in Charm++. These objects can synchronize information by sending and receiving messages.

Implementations based on high-level semantics are compiled into computational graphs and submitted to the Charm++ runtime system, which deploys concurrent chare-objects (tasks) on multiple processors. Based on task status, the system automatically migrates each chareobject (task) among processors to achieve dynamic load balancing. A series of applications developed based on Charm++ have been widely used, especially NAMD, which is a molecular dynamics simulation software. Molecular dynamics simulations generally face dynamic load

imbalances, resulting in poor scalability. However, the Charm++ framework helps improve the scalability of NAMD, outperforming other competitors that are also developed based on the MPI and OpenMP architecture [13].

In addition, Charm++ frees programmers of distributed hardware awareness and has the runtime/toolchain capable of solving the parallelization problem. A high-linearity program (such as LeanMD written in Charm++) can be implemented on a cluster containing more than 10,000 cores with only a few hundred lines of code. It largely facilitates verification of new algorithms for scientists.

# 3.3 Anton

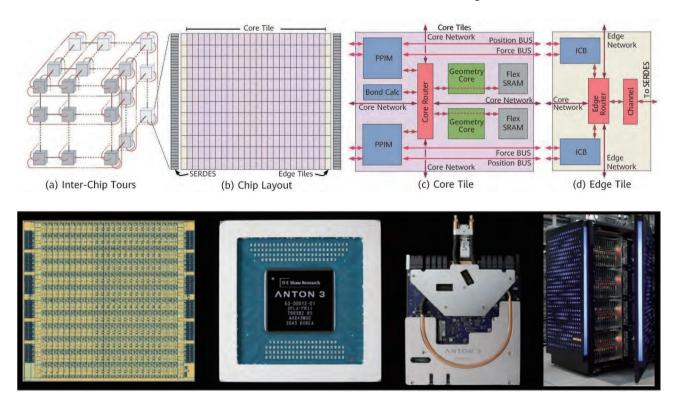

Anton is a tailored computing chip developed by D. E. Shaw Research for molecular dynamics simulations. The computing cluster built on this chip achieves performance far beyond Summit, a supercomputing cluster. Figure 11 [18] provides details about Anton.

For different kernels involved in molecular dynamics simulations, Anton integrates heterogeneous computing units, specifically, customized accelerator pairwise point

Interconnect

Figure 10 Charm++ programming model based on concurrent chare-objects (above) and Charm++ runtime software (below) [17]

#### 😹 | Technological Foundation

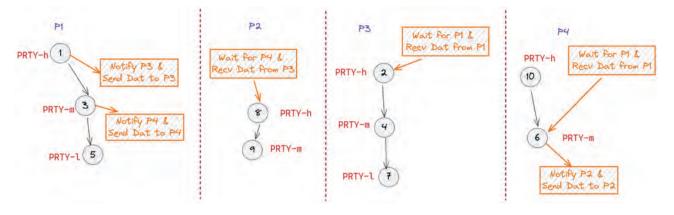

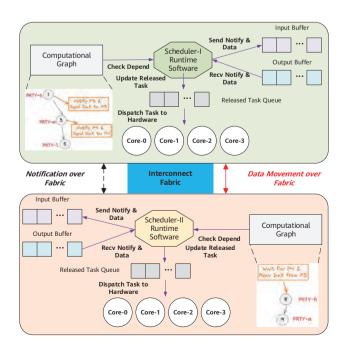

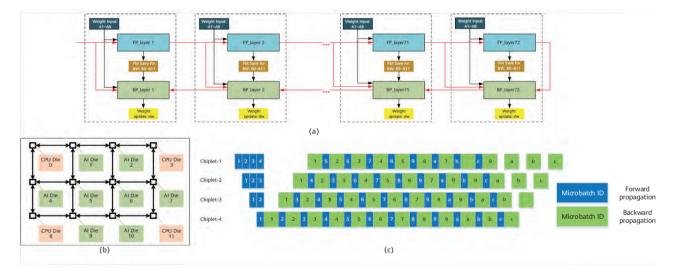

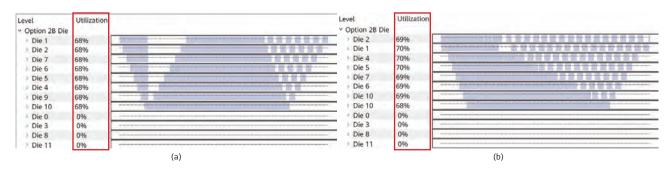

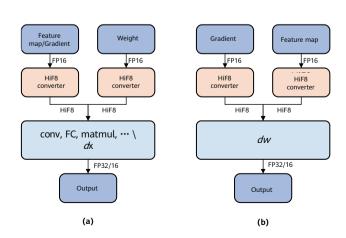

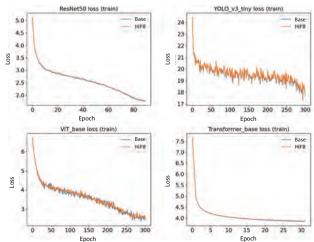

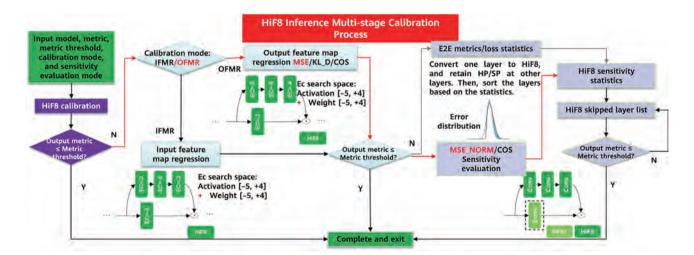

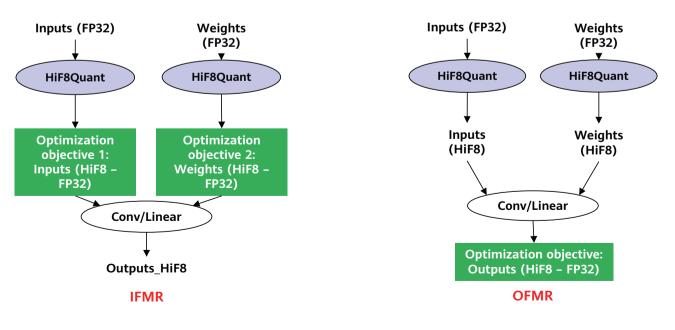

interaction modules (PPIMs) and programmable geometry cores. To effectively organize these computing units, Anton also customizes on-chip interconnect systems and interchip interconnect systems. Unlike classic server chips and AI chips, Anton focuses on low communication latency for better scalability. As shown in Figure 11, the cross-node end-to-end communication latency of the Anton system can reach as low as 90.1 ns. To achieve load balancing in molecular dynamics simulations, Anton also designs a task scheduler and an event-driven programming model that integrates hardware and software.