## POLITECNICO DI TORINO

Collegio di Ingegneria Elettronica, delle Telecomunicazioni e Fisica (ETF) Department of Electronics and Telecommunications (DET)

Master of Science in Telecommunications Engineering

Master of Science Degree

## **Remotized Control of Power Electronic Devices Exploiting a Plastic Optical Fiber Photonic Bus**

**Candidate:** Erasmo Vizzaccaro Advisor: Vittorio Curri (DET)

**Co-Advisors:** Eric Giacomo Armando (DENERG) Gianmario Pellegrino (DENERG) Paolo Savio (ISMB)

Academic Year 2017/2018

Erasmo Vizzaccaro: *Remotized Control of Power Electronic Devices Exploiting a Plastic Optical Fiber Photonic Bus* Telecommunications Engineering, © Politecnico di Torino 2018 ADVISOR: Vittorio Curri To my father and my mother Lovely parents and sources of inspiration in my life I love you

A mio padre e mia madre Genitori fantastici e fonti di ispirazione nella mia vita Vi voglio bene

#### ABSTRACT

Nowadays, a new energy revolution is in act. This trend can be noticed from the explosive growth of portable devices (smartphones, laptops, tablets) industry processes, hybrid cars and many others. Power Electronic assumes a fundamental role in this revolution, since it represents the technique with which the power is transferred from the source to the load. These developments are leading digital control into becoming the enabling technology for many engineering fields and Power Electronic Converters (PECs) into being used in several applications such as computer power supplies, energy conversion and motor drive control, suggesting the possibility of new and better integration of advanced power conversion and ICT services. Therefore, linking the Power Electronic world to the Information and Communication Technologies becomes extremely important and suggestive from the point of view of what we can achieve with this kind of technologies linked together.

In Chapter 1, the Power Electronic world is introduced with the description of the most important converters and their application in the motor control field by means Pulse Width Modulation. In Chapter 2, the major communication topologies and protocols are described. After, thesis goals and an overview of our work is presented. Finally, the world of optical communications is explained, focusing the attention on the differences between the glass and the plastic optical fiber.

In Chapter 3 our work is explained in detail. Traditionally the State of the Art about the control of PEC is mainly focused on the use of optical fibers in "one signal per fiber" manner. In this work we investigates a method to remotize the control of PEC by means of a plastic optical fiber, passing in this way from a centralized to a shared centralized control, and thus making PEC a black box compatible with any off-board controller. The scope of this thesis consists into defining a proper communication protocol for the photonic bus in order to link together PECs and their remote control and making possible the control and synchronization of several power converters, enabling real-time control and telemetry for diagnostics and prognostics. Also, a proof-of-concept demonstrator is presented and tested. Finally, in Chapter 4 the Internet of Power world is introduced. After a briefly introduction to the Internet of Things world, conclusion and further developments towards the Internet of Power by using a power electronic cloud enabling telemetry and remote management are presented.

First of all I would like to thank my advisor, Prof. Vittorio Curri, both for proposing this very stimulating thesis and for allowing me to carry out this work in absolute serenity, always putting myself in the best conditions to work through his passion and his help, giving me in addition, the possibility to participate in the drafting of two scientific articles on the project on which the thesis is based. I would also like to thank the Interdepartmental Center for Power Electronics (PEIC) of the Politecnico di Torino for allowing me to carry out this stimulating project from various points of view. I would like to thank my co-advisors, Prof. Eric Giacomo Armando and Prof. Gianmario Pellegrino of the Energy Department (DENERG), Ing. Paolo Savio of the Istituto Superiore Mario Boella (ISMB) and the Ph.D. student Anantaram Varatharajan (DENERG), for having supported me during these six months of work through their skills, always giving me the necessary contribution and always clarifying all my doubts. Finally, I would like to thank the people of ISMB, in particular the staff of the "Applied Photonics" research area for giving me the opportunity to carry on the thesis in their offices and for making me feel like one of them.

I thank you, Mum and Dad, for giving me the opportunity to study without ever putting pressure, always standing on my side, and for giving me the opportunity to study away from home allowing me to make life experiences that without your help I could never do. I want to thank you for always being next to me and for always urging me. Unfortunately I took a little longer to graduate, but only to continue to hear the most famous phrases of Dad as "open the book" or "study!", and now in fact I already miss them (even if in reality there are still Gemma and Albino). Thank you so much for never having let me miss anything, even though sometimes I was not the perfect child. I hope to give you back every day for a little bit of everything you have done for me, and to make you proud of me, as I am of you.

Thanks to Albino and Gemma, to be more than a simple brother and a simple sister. You have always been with me, you have always supported me with no ifs or buts. It is true that we do not often go out together, but I know very well that you will always be there for me as I am for you. I thank you because these 5 years away from home have not in any way scratched our beautiful relationship, and going back home and telling us about our experiences is always exciting. Finally I want to tell you, Mum, Dad, Albino and Gemma, that this distance that has lasted for 5 years, does not feel just for you, but it is hard to bear (even if I try to hide it) for me too. But we all know that it will not be a few kilometers to divide us: I love you!

Thanks to my beautiful extended family, grandmother Gemma, aunt Graziella, aunt Rita, uncle Chichino, Mario and Matteo (and even those who are not there anymore but it is as if they were always with us). I thank you because you have always believed in me, always giving me your support, even when this goal seemed unattainable.

I thank my love, Maria Chiara, because for two and a half years she supports me and constantly supports me. I know my character very well, sometimes I'm really unbearable (maybe in the family they know something) but despite this you never stopped believing in me and pulling me up when I wanted to send everything to the air, convincing me of the skills I have. Thank you because with your presence in my life, you made me discover new things, you made me understand what it means to always be there, you made me understand that to be well and be happy you do not have to do 5 a.m, but enough a bed, a blanket (of paaaail) and a television. I thank you because falling asleep and wake up by your side is something indescribably beautiful. I thank you, Maria Chiara, because you taught me what it means to LOVE.

Thanks to my friends, the new ones (terroni and polentoni), known in this experience, with whom I spent fantastic evenings around Turin or simply at home with a glass of wine and lots of laughter. I thank the Friends of all time that despite of distance have always been present and ready to support me, and every time I come home they make me feel as if I had never gone.

Thank my beautiful flatmates: Gerardo, Giulio, Luciano, Manuel, Pietro and Riccardo. Getting to know you was one of the best things about this Turin experience; tying with you was very easy, in fact, despite being new to the house you made me feel at ease immediately. I thank you because I know myself and I know how much I break the boxes for certain things, but despite this you have always given me your support, allowing the birth of a solid relationship and friendship.

My university career ends here. To thank everyone with a few words is never simple, so I hope I have succeeded and made you understand how important you are to me. Many thanks to everyone for always being on my side, without you nothing would have been possible.

Erasmo Vizzaccaro Turin, October 2018. Innanzitutto vorrei ringraziare il mio relatore, Prof. Vittorio Curri, sia per avermi proposto questa tesi molto stimolante sia per avermi permesso di svolgere questo lavoro in assoluta serenità, mettendomi sempre nelle migliori condizioni per poter lavorare attraverso la sua passione e il suo aiuto, dandomi inoltre la possibilità di partecipare alla stesura di due articoli scientifici sul progetto su cui si basa il lavoro di tesi. Ringrazio poi il Centro Interdipartimentale per la Power Electronics (PEIC) del Politecnico di Torino per avermi permesso di svolgere questo progetto stimolante sotto vari punti di vista. Vorrei ringraziare i miei correlatori, Prof. Eric Giacomo Armando e Prof. Gianmario Pellegrino del Dipartimento Energia (DENERG), l'Ing. Paolo Savio dell'Istituto Superiore Mario Boella (ISMB) e lo studente di dottorato Anantaram Varatharajan (DENERG), per avermi supportato durante questi sei mesi di lavoro attraverso le loro competenze, dandomi sempre l'apporto necessario e chiarendo sempre ogni mio dubbio. Infine vorrei ringraziare le persone dell'ISMB, in particolare il personale dell'area di ricerca "Applied Photonics" per avermi dato la possibilità di portare avanti il lavoro di tesi presso i loro uffici e per avermi fatto sentire come uno di loro.

Ringrazio voi Mamma e Papà per avermi dato la possibilità di studiare senza mai mettermi pressione stando sempre dalla mia parte, e per avermi dato la possibilità di studiare lontano da casa permettendomi di fare delle esperienze di vita che senza il vostro aiuto non avrei mai potuto fare. Voglio ringraziarvi per essermi sempre stati accanto e per avermi sempre spronato (alla fine tutti quei litigi sono serviti). Purtroppo ci ho messo un pò più del dovuto a laurearmi, ma solo per continuare a sentire le frasi più famose di papà come "apri il libro" o "studia!", e ora infatti già mi mancano (anche se in realtà ci sono ancora Gemma e Albino). Grazie infine per non avermi mai fatto mancare niente nonostante alle volte non sia stato il figlio perfetto. Spero di restituirvi giorno per giorno un pò di tutto quello che avete fatto per me, e rendervi orgogliosi si me, cosi come io lo sono di voi.

Ringrazio Albino e Gemma, per essere di pù di un semplice fratello e una semplice sorella. Siete sempre stati con me, mi avete sempre appoggiato senza se e senza ma. E' vero non usciamo spesso insieme, ma so benissimo che voi ci sarete sempre per me così come io per voi. Vi ringrazio perchè questi 5 anni lontano da casa non hanno minimamente scalfito il nostro bellissimo rapporto, e il tornare a casa e raccontarci le nostre esperienze è sempre emozionante. Voglio infine dirvi, Mamma, Papà, Albino e Gemma, che questa lontananza che ormai dura da 5 anni, non si fa sentire solo per voi, ma è dura da sopportare (anche se cerco di nasconderlo) anche per me. Ma sappiamo tutti che non sarà certo qualche kilometro a dividerci: vi voglio bene!

Ringrazio la mia bellissima famiglia allargata, nonna Gemma, zia Graziella, zia Rita, zio Chichino, Mario e Matteo (e anche chi non c'è più ma è come se fosse sempre con noi). Vi ringrazio perchè avete sempre creduto in me, dandomi sempre il vostro sostegno, anche quando questo traguardo sembrava irraggiungibile.

Ringrazio il mio amore, Maria Chiara, perchè da 2 anni e mezzo mi supporta e mi sopporta costantemente. Conosco bene il mio carattere, alle volte sono proprio insopportabile (forse in famiglia ne sanno qualcosa) ma tu nonostante questo non hai mai smesso di credere in me e di tirarmi su quando volevo mandare tutto all'aria, convincendomi delle capacità che ho. Ti ringrazio perchè con la tua presenza nella mia vita, mi hai fatto scoprire cose nuove, mi hai fatto capire cosa significa esserci sempre, mi hai fatto capire che per stare bene ed essere felici non bisogna fare per forza le 5 del mattino, ma basta un letto, una coperta (di paaaail) e una televisione. Ti ringrazio perchè addormentarmi e svegliarmi al tuo fianco è qualcosa di indescrivibilmente bello. Ti ringrazio, Maria Chiara, perchè mi hai insegnato cosa significa AMARE.

Ringrazio i miei Amici, quelli nuovi (terroni e polentoni), conosciuti in questa esperienza da fuori sede, con cui ho passato serate fantastiche in giro per Torino o semplicemente a casa tra un bicchiere di vino e tante risate. Ringrazio poi gli Amici di sempre che nonostante la lontananza sono sempre stati presenti e pronti a supportarmi, ed ogni volta che torno a casa mi fanno sentire come se non me ne fossi mai andato.

Ringrazio i miei bellissimi coinquilini: Gerardo, Giulio, Luciano, Manuel, Pietro e Riccardo. Conoscervi è stata una delle cose più belle di questa esperienza torinese; legare con voi è stato facilissimo, infatti nonostante fossi nuovo della casa mi avete fatto sentire subito a mio agio. Vi ringrazio perchè mi conosco e so quanto rompo le scatole per determinate cose, ma nonostante questo mi avete sempre dato il vostro sostegno, permettendo la nascita di un rapporto solido e di amicizia.

Finisce qui il mio percorsi di studi. Ringraziare tutti con poche parole non è mai semplice, quindi spero di esserci riuscito e di avervi fatto capire quanto siete importanti per me. Grazie di cuore a tutti per essere sempre stati dalla mia parte, senza di voi niente di tutto questo sarebbe stato possibile.

Erasmo Vizzaccaro Torino, Ottobre 2018.

## CONTENTS

| 1 | ром  | ER ELI                     | ECTRONICS: INTRODUCTION AND BACKGROUND            | 1  |

|---|------|----------------------------|---------------------------------------------------|----|

|   | 1.1  | The ne                     | eed for Power Electronics                         | 1  |

|   | 1.2  | What i                     | is Power Electronics?                             | 2  |

|   | 1.3  | Power                      | Electronic Converters and their Applications      | 7  |

|   |      | 1.3.1                      | DC-DC Converter                                   | 9  |

|   |      | 1.3.2                      | DC-AC Converter                                   | 10 |

|   |      | 1.3.3                      | AC-DC Converter                                   | 13 |

|   |      | 1.3.4                      | AC-AC Converter                                   | 13 |

|   |      | 1.3.5                      | Voltage Regulator and Power Supply                | 14 |

|   | 1.4  | Power                      | Electronic Converters for Electric Motor Drives   | 18 |

|   |      | 1.4.1                      | Brushless DC Motor                                | 19 |

|   |      | 1.4.2                      | Motor Control Overview                            | 21 |

|   | 1.5  | A met                      | hod to control a Brushless DC motor: Pulse Width  |    |

|   |      | Modu                       | lation                                            | 24 |

|   |      | 1.5.1                      | Pulse Width Modulation                            | 26 |

| 2 | FIBE | R-POW                      | ER: APPLICATION OF OPTIC FIBERS TO POWER          |    |

|   | ELE  | CTRON                      | ICS                                               | 29 |

|   | 2.1  | Power                      | Electronics Control Architecture                  | 29 |

|   |      | 2.1.1                      | Design of PEBB based Power Electronics Systems    | 30 |

|   |      | 2.1.2                      | Distributed digital controller in motion control  |    |

|   |      |                            | system                                            | 31 |

|   | 2.2  | Comm                       | nunication topologies                             | 34 |

|   |      | 2.2.1                      | Star Structure                                    | 35 |

|   |      | 2.2.2                      | Bus Structure                                     | 36 |

|   |      | 2.2.3                      | Ring Structure                                    | 36 |

|   |      | 2.2.4                      | Daisy-chain Structure                             | 36 |

|   | 2.3  | An ov                      | erview of communication protocols for Power       |    |

|   |      | Conve                      | rters                                             | 37 |

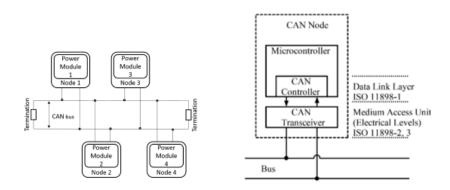

|   |      | 2.3.1                      | Controller Area Network (CAN)                     | 38 |

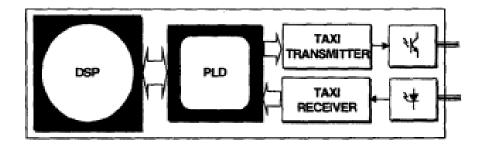

|   |      | 2.3.2                      | Serial Real-time Communication System (SERCOS)    | 39 |

|   |      | 2.3.3                      | Motion And Control Ring Optical (MACRO)           | 39 |

|   |      | 2.3.4                      | Power Electronic System Network (PESNet)          | 40 |

|   | 2.4  | Thesis                     | purpose                                           | 41 |

|   |      | 2.4.1                      | Example: Control of a PWM power converter .       | 42 |

|   | 2.5  | 2.5 Optical Communications |                                                   | 47 |

|   |      | 2.5.1                      | Description and characteristics of optical fibers | 47 |

|   |      | 2.5.2                      | Behavior                                          | 50 |

|   |      | 2.5.3                      | Attenuation                                       | 51 |

|   |      | 2.5.4                      | Glass Optical Fiber                               | 52 |

|   |      | 2.5.5                      | Plastic Optical Fiber                             | 54 |

|   |      | 2.5.6                      | Transmission Windows for Plastic and Glass Op-    |    |

|   |      |                            | tical Fibers                                      | 55 |

|   |      | 2.5.7                                                      | State of the Art of Plastic Optical Fibers   | 59 |

|---|------|------------------------------------------------------------|----------------------------------------------|----|

| 3 | SHA  | RED C                                                      | ONTROL OF PECS THROUGH A PHOTONIC BUS        | 61 |

|   | 3.1  | Introduction                                               |                                              |    |

|   | 3.2  | 3.2 Data Communication in PECs and Design of S             |                                              |    |

|   |      | Control Architecture                                       |                                              |    |

|   | 3.3  | An overview about FPGA and VHDL                            |                                              |    |

|   |      | 3.3.1                                                      | Field Programmable Gate Array                | 65 |

|   |      | 3.3.2                                                      | Very-High-Speed-Integrated-Circuit Hardware  |    |

|   |      |                                                            | Description Language                         | 68 |

|   | 3.4  | Photo                                                      | nic bus: Implementation and Protocol         | 71 |

|   |      | 3.4.1                                                      | Protocol Description                         | 72 |

|   |      | 3.4.2                                                      | Implementation                               | 76 |

|   | 3.5  | Demonstrator Setup                                         |                                              | 78 |

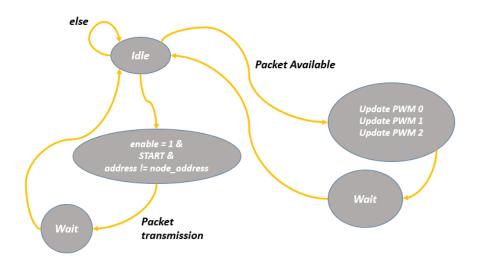

|   |      | 3.5.1                                                      | Finite State Machine                         | 84 |

|   |      | 3.5.2                                                      | Experimental Results                         | 85 |

| 4 | тои  | VARDS                                                      | THE INTERNET OF POWER: CONCLUSION AND        |    |

|   | FUR  | URTHER DEVELOPMENTS                                        |                                              |    |

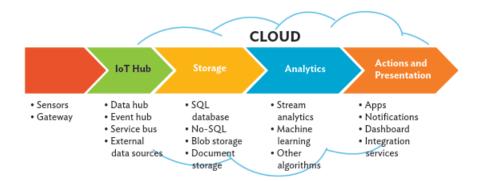

|   | 4.1  | Intern                                                     | et of Things: An Overview                    | 90 |

|   | 4.2  | .2 Internet of Energy: Internet of Things in Power Sectors |                                              |    |

|   |      | 4.2.1                                                      | State of the Art of Internet of Energy       | 92 |

|   | 4.3  | Further Developments                                       |                                              | 93 |

|   |      | 4.3.1                                                      | A cloud approach for controlling Power Elec- |    |

|   |      |                                                            | tronic Converters                            | 94 |

|   | 4.4  | Conclusion                                                 |                                              | 96 |

|   | BIBL | IOGRA                                                      | РНҮ                                          |    |

### LIST OF FIGURES

| Figure 1.1  | Power Electronics as interface between the source  |    |

|-------------|----------------------------------------------------|----|

| C           | and the load                                       | 2  |

| Figure 1.2  | Power Electronics World                            | 4  |

| Figure 1.3  | Power Electronics Applications                     | 5  |

| Figure 1.4  | Power Semiconductor Devices and their Appli-       |    |

| 0           | cations                                            | 6  |

| Figure 1.5  | Ideal Switch: Circuit and Characteristic           | 7  |

| Figure 1.6  | Power electronics and electrical energy genera-    |    |

| C           | tion transmission, storage, and distribution       | 8  |

| Figure 1.7  | DC-DC Converter                                    | 9  |

| Figure 1.8  | DC-AC Converter                                    | 11 |

| Figure 1.9  | AC-DC Converter                                    | 13 |

| Figure 1.10 | AC-AC Converter                                    | 14 |

| Figure 1.11 | Motor Classification                               | 18 |

| Figure 1.12 | Comparative analysis of motors                     | 19 |

| Figure 1.13 | Brushless DC motors                                | 20 |

| Figure 1.14 | Construction of Brushless DC motor                 | 20 |

| Figure 1.15 | Block diagram of a motor drive system              | 22 |

| Figure 1.16 | A periodic pulse train                             | 24 |

| Figure 1.17 | Three pulses with different Duty Cycle             | 24 |

| Figure 1.18 | Pulse Width Modulation technique                   | 26 |

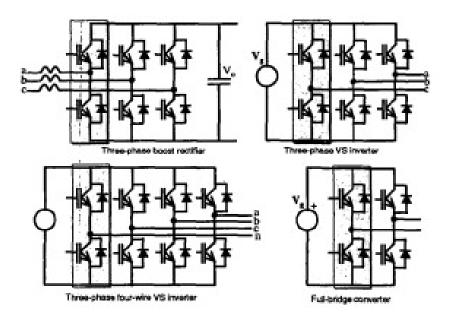

| Figure 2.1  | Common converter topologies, (Celanovic 2000)      | 32 |

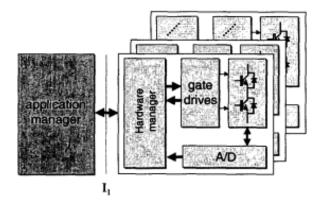

| Figure 2.2  | New system architecture, ( <i>Celanovic 2000</i> ) | 33 |

| Figure 2.3  | Application Manager, ( <i>Celanovic 2000</i> )     | 33 |

| Figure 2.4  | Communication topologies: Structure and fea-       |    |

|             | tures, ( <i>Vaidya 2017</i> )                      | 35 |

| Figure 2.5  | CAN configuration for power converters and         |    |

|             | its node structure, ( <i>Vaidya 2017</i> )         | 39 |

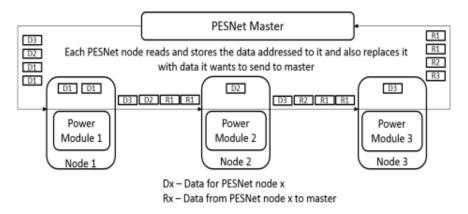

| Figure 2.6  | PESNet topology and functioning of data cycle,     |    |

|             | (Vaidya 2017)                                      | 40 |

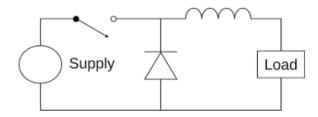

| Figure 2.7  | DC-DC Buck Converter                               | 43 |

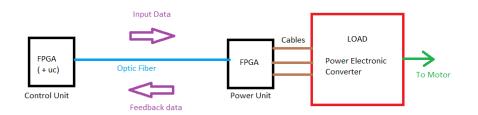

| Figure 2.8  | System layout with optic fiber communication       | 44 |

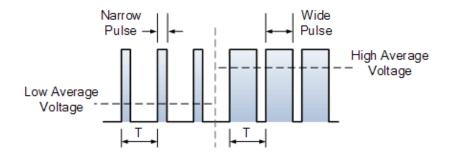

| Figure 2.9  | A typical PWM modulation                           | 44 |

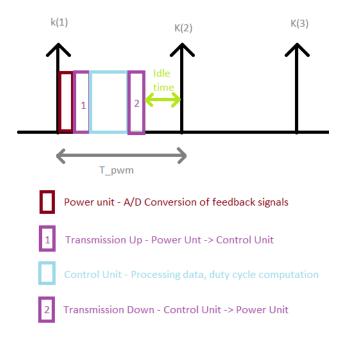

| Figure 2.10 | Sampling time scale                                | 45 |

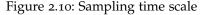

| Figure 2.11 | Synchronization of sampling and PWM output         |    |

|             | update                                             | 46 |

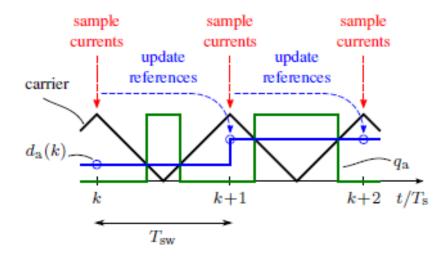

| Figure 2.12 | Electromagnetic Spectrum                           | 48 |

| Figure 2.13 | Optical Fiber                                      | 49 |

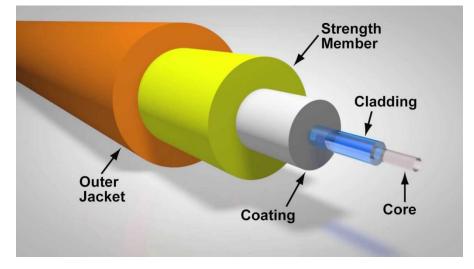

| Figure 2.14 | Structure of a typical single-mode fiber           | 50 |

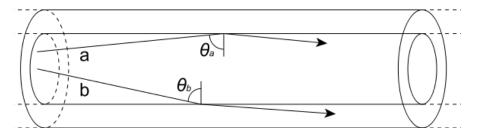

| Figure 2.15 | Total internal reflection (a) and external reflec- |    |

|             | tion ( <b>b</b> )                                  | 51 |

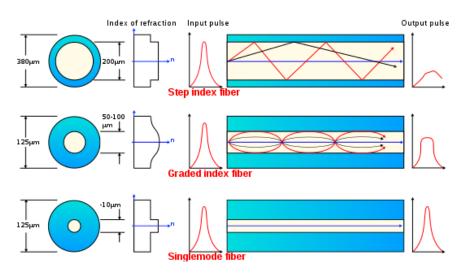

| Figure 2.16 | Optical fibers comparison                                | 53 |

|-------------|----------------------------------------------------------|----|

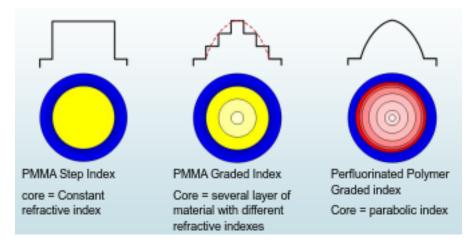

| Figure 2.17 | Index profiles for plastic optical fibers                | 54 |

| Figure 2.18 | Comparison between core/cladding of plastic              |    |

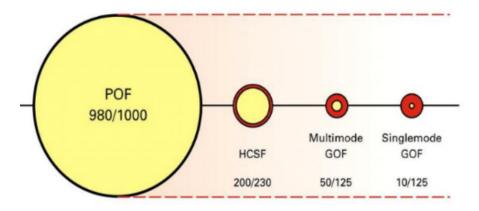

|             | and glass optical fiber                                  | 55 |

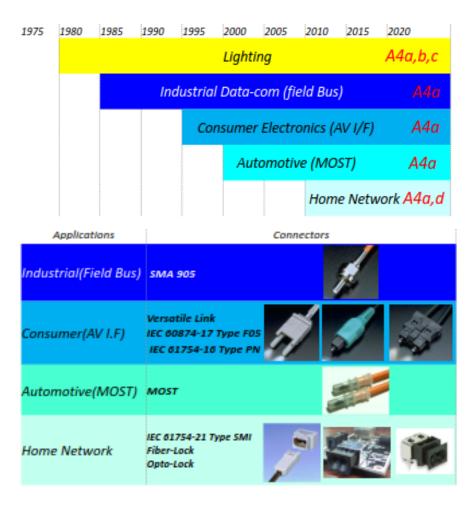

| Figure 2.19 | Expansion of Data applications for POF and               |    |

|             | connector interfaces for A4a POF                         | 56 |

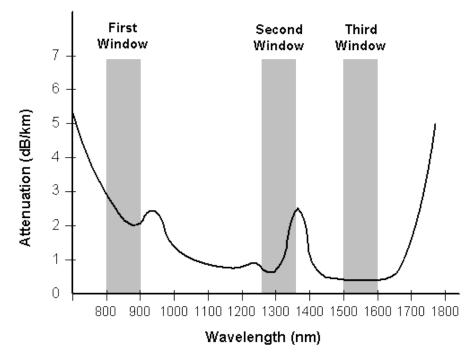

| Figure 2.20 | Transmission windows for a silica optical fiber          | 58 |

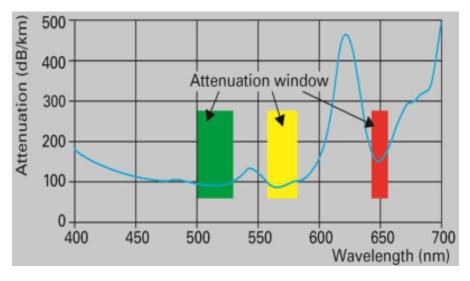

| Figure 2.21 | PMMA-SI-POF attenuation spectrum                         | 58 |

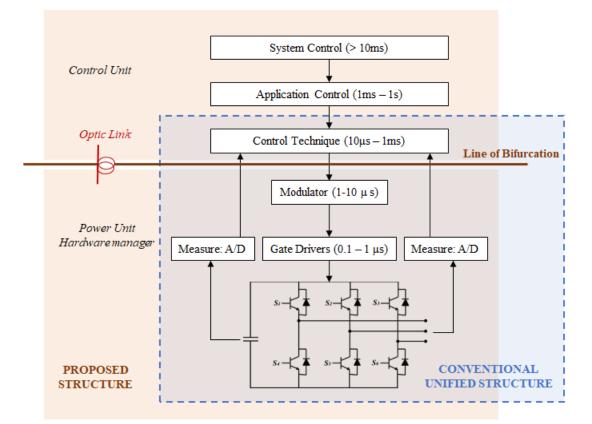

| Figure 3.1  | Common control layers for a PEC. Conventional            |    |

|             | and proposed are highlighted                             | 64 |

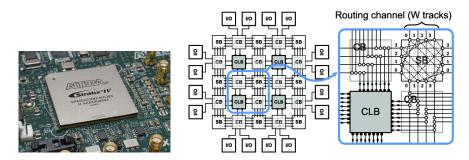

| Figure 3.2  | FPGA and its CLB rapresentations                         | 66 |

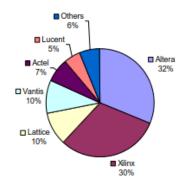

| Figure 3.3  | FPGAs market                                             | 67 |

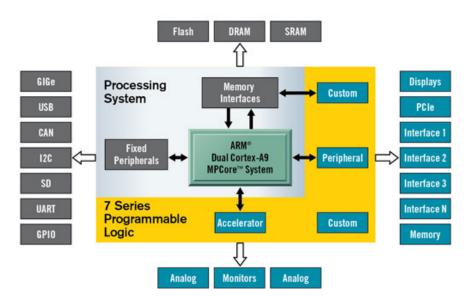

| Figure 3.4  | Xilinx Zynq-7000 structure                               | 68 |

| Figure 3.5  | A generic Vivado window with the Flow Navi-              |    |

|             | gator on the left                                        | 70 |

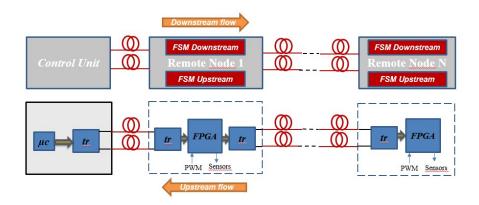

| Figure 3.6  | Scheme for the proposed TDM control setup                |    |

|             | based on a daisy-chain connected by POF links            | 71 |

| Figure 3.7  | Communication cycle timing diagram of the                |    |

|             | proposed optical link                                    | 73 |

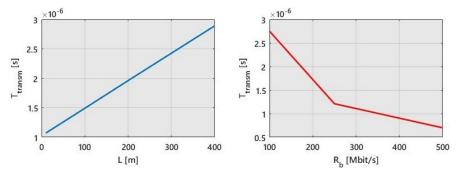

| Figure 3.8  | Sensitivity of $T_{transm}$ to fiber length and bit-rate |    |

|             | in a one-way transmission between two nodes              | 74 |

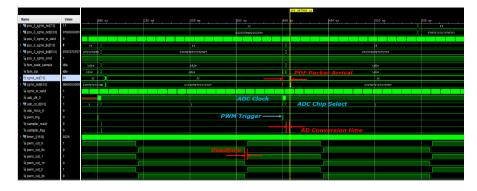

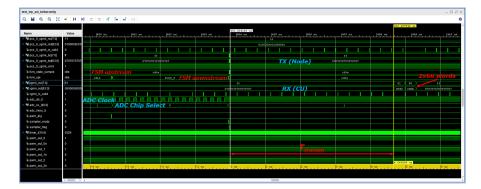

| Figure 3.9  | Simulation timing diagram with Vivado                    | 74 |

| Figure 3.10 | Example of packet flow                                   | 76 |

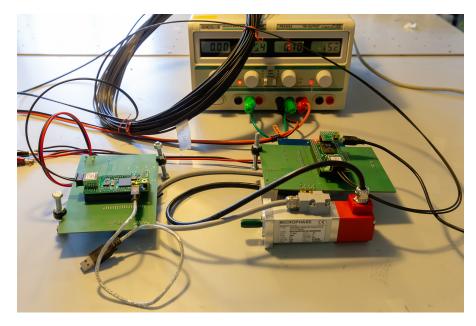

| Figure 3.11 | Demonstrator Setup                                       | 79 |

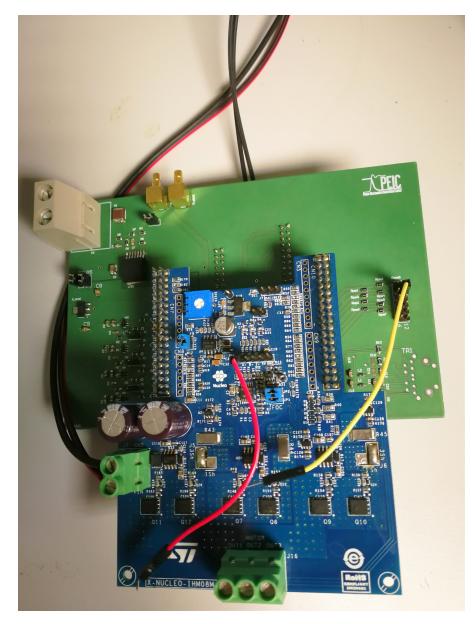

| Figure 3.12 | Developed PCB with the X-Nucleo-IHM08M1                  | 80 |

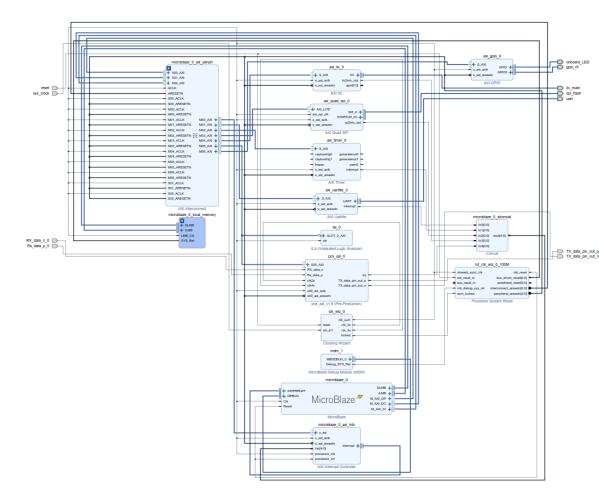

| Figure 3.13 | Control Unit scheme by Vivado Design Suite .             | 82 |

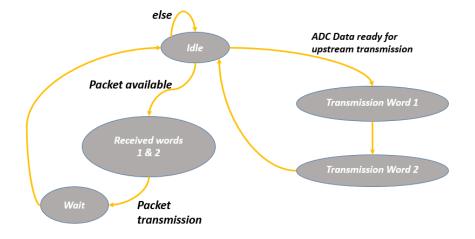

| Figure 3.14 | Finite State Machine - Upstream flow                     | 85 |

| Figure 3.15 | Finite State Machine - Downstream flow                   | 85 |

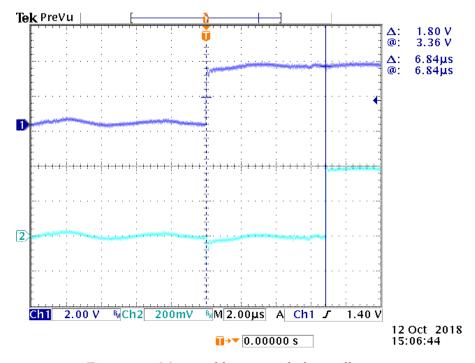

| Figure 3.16 | Measured latency with Vivado simulator                   | 87 |

| Figure 3.17 | Measured latency with the oscilloscope                   | 87 |

| Figure 4.1  | Components of the IoT cloud                              | 91 |

| Figure 4.2  | IoE Architecture                                         | 92 |

| Figure 4.3  | The daisy chain control scheme (on the right)            |    |

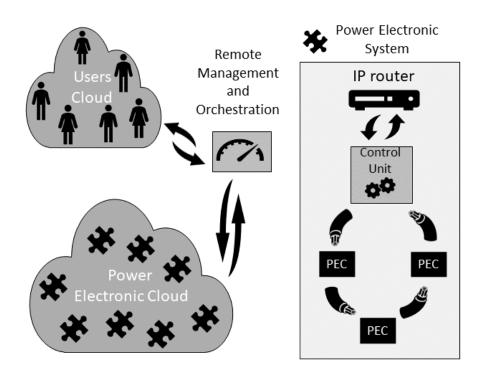

|             | as an element of the power electronic cloud              | 95 |

# POWER ELECTRONICS: INTRODUCTION AND BACKGROUND

This chapter gives an overview about the power electronics world. Firstly, the need and the meaning of power electronics are explained. Then, different power converters are described with particular attention to the converters used in the electric motor drives. Finally, a method to control a power electronic converter is described, i.e Pulse Width Modulation.

#### 1.1 THE NEED FOR POWER ELECTRONICS

Electricity has changed everything and it will again, completely changing the way people live and work. Today, we are in the early stages of a new energy revolution, and we can see it in the explosive growth of portable devices, industry processes, in hybrid cars on the road, in jetliners that are moving to all-electric, and much of the revolution is based on using electronic circuits to process energy. Nowadays, since people don't use "directly" electricity but light, heat, information and other more palpable types of energy, power electronic and energy conversion are becoming more and more important for our lives.

Everything started when a British scientist, Michael Faraday, in 1821 explained the conversion of electrical energy into mechanical energy by placing a current carrying conductor in a magnetic field, which resulted in the rotation of the conductor due to the torque produced by the mutual action of electrical current and magnetic field. Based on his principles, the most primitive DC motor began to be developed. So, it is undoubtedly true that electrical energy plays a very important role in our daily life for a lot of reasons, such as:

- Facility of transport, in fact a city can be fed with few metal wires carrying energy;

- It can be converted back and forth into mechanical energy or other energy forms with high efficiency;

Unfortunately, there are also some drawbacks since it has several different forms such as DC batteries, AC lines, 5v or 3.3v logic levels, single-phase or three-phase circuits. Therefore, since these diverse forms have their own purposes, an adjustment is needed to match each electrical application to a particular type of source.

#### 1.2 WHAT IS POWER ELECTRONICS?

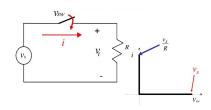

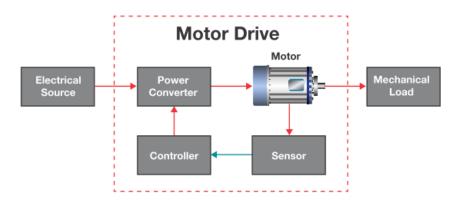

Today, lots of electronic devices, like smartphones and tablets, are used in our daily lives, and clearly the battery of these devices has to be charged to make the device work. Moreover, our daily activities are driven by a plug or an energy source like a battery. Hence, we do not only utilize power but we rely on it. An example can be our morning routine: turn off the alarm clock, turn on the lights in your room, check the e-mails on the smartphone and so on. From an electronic point of view, a source and a load are needed during the usage of an electronic device. The source is something that generates power, for example it could be a battery or the wall power, while the load is something that consumes power, that is the device itself like a computer, TV or any other type of device. The power electronics is the technology in between them, namely the circuitry that takes power from the source and delivers it to the load to feed it, as depicted in Figure 1.1.

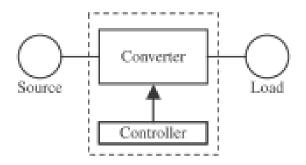

Figure 1.1: Power Electronics as interface between the source and the load.

In particular, the previous figure illustrates a power electronic system, where beyond the source and the load, there is the power converter that contains switches, lossless storage elements and magnetic transformers, while the control circuit is used to define how the switches work to reach the desired conversion, based on information given by the source, load and designer.

In other words, power electronics is the application of electronics to control the conversion of electric power where the electronic circuit takes care of changing the wall power into power that can be used from the load, makes sure that power is delivered safely to the device, so that it doesn't break or over heat. Some examples of power electronic converters (PECs) are:

- A notebook charge: it is made of a source, that is the AC power grid and of a load that could be the laptop connected with a wire to the power pack;

- A portable battery pack, where the source is the USB power, maybe from computer, and the load is the battery pack itself, where is located the power electronic;

- A photovoltaics (PV) solar panel that feeds an AC grid. In this case, the PV solar panel is the source, while the power grid is the load. So the power electronic is in between them to convert the power from the PV panel into something that can be delivered to the power grid;

- Electric motors require appropriate voltages and currents to operate in a suitable way, ie. maintaining torque speed;

- Microcontrollers and FPGAs, common in embedded application because they support activities of washing machines, microwave ovens and automobiles, requires low voltages and high input currents.

Whereas, some examples of power electronics requirements in the light and heavy industries are:

- Industrial controls: motor and motion control applications; Power sensing and measurement; Advanced power electronic AC motor controls that should supplant almost all existing DC motor systems over the next two decades;

- Electric power industry: emergency backup power supplies; Alternative energy source conversion; HVDC transmission;

- Computer industry: need for lots of power at a different of low DC voltages; Backup power is also important;

- Electronic equipment industry: power supplies for instruments, consumer electronics, portable and remote measurement devices, and many other products;

- Automobile industry: electric actuators and energy control; Electric traction systems;

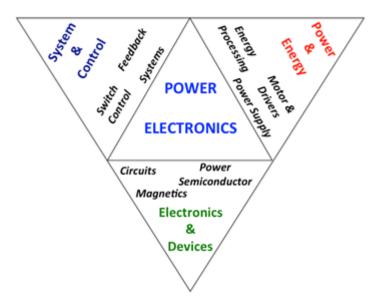

So, power electronics' framework is concerned with the conversion among different forms of electricity by designing proper circuits in order to control the flow of electrical energy. In fact, as it can be seen from the Figure 1.2, control, energy and electronics are always interrelated, and power electronics represents the median point that links all the topics together.

Figure 1.2: Power Electronics World

Of course, since the power converter is between the source and the load, it must only manage the flow and at the same time should not dissipate energy, otherwise the energy used by the converter is lost to the overall system. As a result, the most important features for a power converter are high input to output energy efficiency and the reliability, because a failure in the power converter means also a failure for the user (the load).

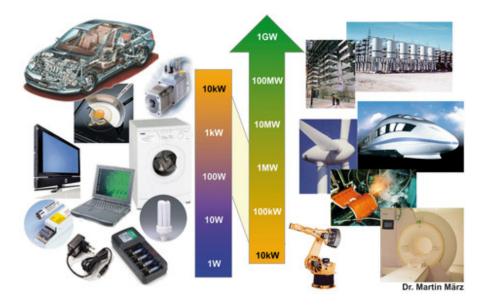

Thanks to the big developments in the field of electronics, the new power electronic components and systems allow customers to develop smaller and more energy-efficient power system that make an important contribution to reducing global energy consumption. For example, e-Mobility is one of the fastest growing markets of the future, and power electronic is used both in fast charging stations and in vehicles at the interface between the motor and the battery. In addition, it helps to control the output power of the motors of long distance and urban electric trains and supplies energy to auxiliary units such as lighting ventilation and air conditioning systems. Some of the largest application areas for power electronics can be found in industrial and commercial applications, such as motors, electric drives for robots, pumps and fans, or in the renewable energies field like photovoltaics (PV) solar panel and wind turbine. In general, the field of power electronic, can be divided in six different areas:

- Power supplies for computers (needs for lots of current at a variety of low DC voltages);

- Power semiconductor;

- Electronic motor drives (Power sensing and measurements);

5

- Energy processing such as power networks, high voltage-direct current (HVDC) systems;

- Electrical mobility such as electric cars and railways;

- Telecommunications field (needs power for transmission, signal processing);

Figure 1.3: Power Electronics Applications

Some years ago the process of energy conversion was not so easy as today. One of the first methods (in 1902) of high power rectification was the mercury arc rectifier, that was used to convert alternating current (AC) into direct current (DC). Thanks to this method it was possible to charge storage batteries and power DC motors for trams and subway systems. Clearly, this method was extremely expensive, inefficient and required an high cost for the maintenance of the system.

Over the time, thanks to the development of new of electronic components, new kinds of converters were invented. The first important invention was around 1950 with the bipolar junction transistor (BJT) that brought improvements in terms of stability, performance and reduced cost. Next, high power semiconductor diodes were invented and took the place of the vacuum tubes (used to control electric current between electrodes) being more efficient, smaller, cheaper, more reliable and durable. After that, with the introduction of the silicon controlled rectifier (SRC) and the increase of the switching speed of the BJTs, the range of the power electronics application started to increase rapidly. Finally, with the development of the MOSFETs in 1976 and the IGBT in 1982 the market of power electronics applications had an enormous expansion that still continues. In recent years there has been an increasing attention in the high-voltage Silicon Carbide(SiC) based semiconductor power devices and their applications such as medium voltage drives and power converters for renewable energy integration. In the meanwhile, IGBTs and FETs have been broadly used in the application of electric motor drives, switching supplies and other power conversion systems.

Another important benefit of power electronic conversion, is that nowadays the demand for integrated monitoring of industrial facilities in order to expand safety as well as efficiency is growing. In order to meet the power demand of the new applications, features of the power semiconductor devices must be improved into support higher operating switching frequencies and current densities using new materials and manufacturing techniques. Clearly, this has an immediate impact on the dynamic performance of the devices and the increase of the temperature of operation since losses are dissipated as heat. Consequently, the design of power electronics circuits requires precise information about the junction temperature of the switches, since it determines its lifetime and reliability.

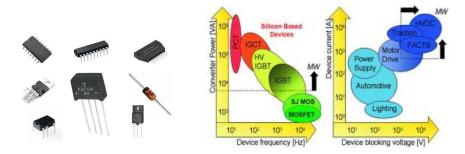

Figure 1.4: Power Semiconductor Devices and their Applications

The characteristics and the limitations of active devices, like BJT and FET, that act as a switch, are a key element in the design of power electronics systems.

In particular, an ideal switch, Figure 1.5, does not consume or dissipate any power. When the switch is closed, the current flow through the switch is equal to the current absorption by the load; the voltage across the switch terminal is equal to zero. When the switch is open, there is no current flow to the load, so the voltage across the switch is equal to the voltage source. So, an ideal switch dissipates no power. Obviously, the real behavior if different from the ideal one, but thanks to the huge advancements of the technology, semiconductor devices such as BJT and MOSFET, that are used as switches, approximate the behavior of the ideal switch, showing high efficiency and a very little amount of power wasted mainly during the switch. This is the reason for which nearly all power electronics applications are based on switching devices.

The benefits of using switching circuits are so important that is common to associate power electronics with the study of the switching power converters. In fact, power electronics is a branch of electronics in

7

Figure 1.5: Ideal Switch: Circuit and Characteristic

which devices will be operating only in saturation and cut-off regions, unlike linear electronics in which devices will be dealing when they are in active mode. This implies that a linear device dissipates energy to control the output voltage while a power switch stays either "on" or "off" and control the output voltage with the percentage "on" Vs "off", i.e. the duty cycle of the generated waveform.

Thence, power semiconductor devices can be classified based on their switching speed. For example, diodes with a frequency up to a few kilohertz are suited for slow speed while MOSFETs and BJTs work with frequencies that go from tens of kilohertz up to a few megahertz in power applications. Devices with high switching speed, reduce the energy lost in the transitions from ON to OFF and back, but introduce also some problems with radiated electromagnetic interference (EMI).

#### 1.3 POWER ELECTRONIC CONVERTERS AND THEIR APPLICATIONS

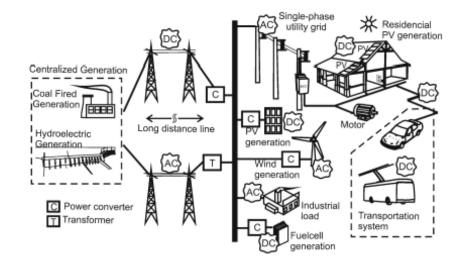

As explained in the previous section, power electronics had huge growth after the development of the silicon controlled rectifier (SCR), the first solid-state power switch, in 1957; in fact, today almost all of the technologies that require control of power use power electronics technology. So, with the incoming of microelectronic control, it is possible apply the modern control theory to power electronics and this makes very complex circuit functions feasible. This kind of switching technology allows power electronics systems to operate in the range from a few watts up to GW, with frequency range from some 100 Hz up to some 100 kHz, depending on the power handled. Figure 1.6 shows how electrical energy generation is distributed for the end-user, showing transmission, distribution, storage, renewable energy sources and users. As a result, the application area of power electronics is now extremely wide and is a key technology for all the following sub-systems:

- For high power level, power electronics deals with static and rotating equipment for generation, transmission, and distribution handling large amount of power;

- For consumer electronic applications, power electronics is fundamental for information processing, employing analog and digital circuits, or microprocessors including micro-controllers, digital

signal processors (DSP), and field programmable gate arrays (FPGAs).

• In the area of control, power electronics deals with stability and response characteristics in systems with feedback loops, based on classical or modern control.

Figure 1.6: Power electronics and electrical energy generation transmission, storage, and distribution

Thus, the introduction of devices and equipment able to convert effectively electric energy from AC to DC, DC to DC, DC to AC, and AC to AC together with the important developments in electrical power engineering has resulted in broad diffusion of power electronics in a ample spectrum of applications, such as:

- Residential: heaters, home appliances, electronic lighting, equipment sources;

- Commercial: heaters, fans, elevators, Uninterruptible Power Supply (UPS), AC and DC breakers, battery chargers;

- Industrial: pumps, blowers, robots, inductive heaters, welding, machine drive, portable sources;

- Transportation: electrical and hybrid vehicles, battery chargers, railroad electric system;

- Utility systems: high voltage direct current, generators, interface for photovoltaic, wind, fuel cells systems, Flexible AC Transmission System equipment;

- Aerospace: sources for spacecrafts, satellites, planes;

- Communication: sources, RF amplifiers, audio-amplifiers;

So, since each electronic device and application needs different voltages and has different requirements, a converter has to be used to give the right voltage level to the load. For example, as described in Section 1.2 of Chapter 1, starting from the wall AC power, a change in the voltage waveform, from AC to DC, is needed since most of the electric devices, like laptops and smartphone, require DC voltage. In general, in electrical and power engineering, power conversion is converting electric energy from one form to another such as converting between AC and DC, or changing the voltage or frequency, or some combination of these. This goal can be reached with the use of a power converter, that is an electrical or electro-mechanical device for converting electrical energy. There are four kinds of power converters, based on the input and output power:

#### DC CONVERSION

- DC-DC Converter (DC source, DC load)

- DC-AC Converter (DC source, AC load)

#### AC CONVERSION

- AC-DC Converter (AC source, DC load)

- AC-AC Converter (AC source, AC load)

#### 1.3.1 DC-DC Converter

It is an electronic circuit that converts the input DC voltage, that can range from a very few watts to hundreds of MW, from one level into another based on the requirements of the load. As shown in Figure 1.7 , it is made of at least two semiconductors and at least one energy storage element.

Figure 1.7: DC-DC Converter

This converter finds applications in a lot of portable devices such as computers and smartphone, which are fed with power from battery; in particular it is used to keep the voltage at a knows value independently from the voltage level of the battery. They are also used in the renewable energy field, to maximize the energy collected by photovoltaic systems or by wind turbines. This kind of conversion,

common in battery-based systems and in telecommunications systems, is becoming more and more significant in a much wider range of applications, since a lot of circuits use DC power at several different voltage levels. An example is power supplies that is having great result from home appliances to industrial controllers. In the past, major part of DC power supplies obtained energy from an AC line source, modified its voltage level with a transformer and finally rectified the result. Clearly, this method was relatedly inefficient and big expensive, while today the development of power semiconductors and ICs (integrated circuits) makes it economically viable: small cheaper power supplies are built using DC-DC converters. In this kind of converter, energy is periodically stored within and released from a magnetic field in an inductor or a transformer, typically within a frequency range of 300 kHz to 10 MHz. In particular there are two main topologies, *Flyback*, when energy is stored in the magnetic field and *Forward* when energy is transferred through the magnetic field. Moreover, the most common converters are:

- Buck or Step-Down converter (Forward topology), where the output voltage is lower than the input voltage;

- Boost or Step-Up Converter (Flyback topology), where the output voltage is higher than the input voltage;

- Boost-Buck Converter (Forward topology), that is capable of converting to a higher or lower voltage;

#### 1.3.2 DC-AC Converter

Despite a lot of our appliances are made to work with AC, small-scale power generators often generate DC. That means if you want to run something like an AC-powered device from a DC car battery in a mobile home, you need a device that will convert DC to AC. This kind of electronic device is called *inverter*. Today they have taken a prominent role in the modern technological world due to the sudden rise of electric cars and renewable energy technologies; they are also used in uninterruptible power supplies (UPS), HDVC power transmission, power grid and solar inverter. It needs a stable DC power as input in order to supply sufficient current for the designed load. The input voltage depends on the requirement of the designed device, for example 12 V DC for small battery powered consumer inverters or 400 V DC if power is from photovoltaic solar panels. Moreover, since power can be transferred both in single-phase and in three-phase, inverters can operate in single-phase or in three-phase. Single-phase inverter are used for power supplies and single-phase UPSs, while three-phase inverter are used for adjustable speed drives (ASDs) applications and for high power applications such as HVDC power transmission. Topologies for these converters can be separated into two main classes:

Figure 1.8: DC-AC Converter

- 1. Voltage Source Inverter (VSI): it has rigid DC source voltage that is the DC voltage has limited or zero impedance at the inverter input terminals; the independently controlled output is a voltage waveform; have practical uses in both single-phase and three-phase applications.

- 2. Current Source Inverter (CSI): It is supplied with a variable current from a DC source that has high impedance. The resulting current waves are not influenced by the load; this kind of inverter has practical for three-phase applications in which high-quality voltage waveforms are demanded.

As of the output waveform, an inverter can produce different waves like square wave, modified sine wave, pulsed sine wave and pulse width modulation. The output frequency is usually 50 or 60 hertz (the same as standard power line frequency), while the output voltage is regulated to be the same as the grid line voltage, that is 120 or 240 VAC.

#### 1.3.2.1 *Output waveform*

A technique called pulse width modulation (PWM) is used to produce a pure sinusoidal output and it is explained more in detail in the Section 1.5. The logic of PWM is simple, it generates the DC voltage in the form of pulses of different widths, that is in regions where you need higher amplitudes it will generate pulses of larger width. The shape of the averaged pulses looks very similar to the sine curve, the finer the pulse is used the better shape the sine curve will be. To implement the PWM in an actual inverter a comparator is used. Comparators compare a sine wave with triangular waves. In the case of a pure sinusoidal output, one comparators uses a normal sine wave, while the other uses an inverted sine wave. As a result, a PWM is obtained. Moreover, to implement the averaging, that is to make it exactly sinusoidal, energy storage elements (passive filters) such as inductors ( that smooth current) and capacitors (that smooth voltage) are used to smooth the power flow. If one more voltage level is introduced, it will give better approximation of the sine wave and can reduce instantaneous errors. Such multi-level inverter technology is used in high precision applications like wind turbines and electric car. To sum up, with an inverter bridge, a good PWM technique and a passive filter, the desired voltage can be produced for all the home appliances.

Generally speaking, the appliances we use in our homes (like electric heaters, incandescent lamps, kettles) that use raw power, don't care much about the shape of the wave they receive; all they want is energy and lots of it. Electronic devices, on the other hand, prefer the smoother input they get from a sine wave. This explains why inverters come in two distinct topologies:

- Pure Sine Wave inverters (PSW), they use a toroidal transformer and electronic circuits to transform direct current into a smoothly varying alternating current very similar to the kind of genuine sine wave normally supplied to our homes. They can be used to power any kind of AC appliance from a DC source, including TVs, computers, video games, radios and stereos;

- 2. *Modified Sine Wave inverters* (MSW), use relatively inexpensive electronics ( thyristors, diodes, and other simple components) to generate a kind of "rounded-off" square wave (a much rougher approximation of a sine wave) and while they're fine for delivering power to hefty electric appliances, they can and do cause problems with delicate electronics (or anything with an electronic or microprocessor controller). Also, their rounded-off square waves are delivering more power to the appliance overall than a pure sine wave (in fact there's more area under a square than a curve), so there's some risk of overheating with MSW inverters.

#### 1.3.3 AC-DC Converter

It is an electrical device that derives DC power from an AC supply, for this reason it is also called *rectifier*. It converts alternating current, which flow changes during the transmission, into direct current, whose flow in only one direction. This kind of converters can be found in different applications such as radio, television and computer, and in high-voltage direct current power transmission systems. The output of the rectifier is firstly smoothed by an electronic filter and possibly followed by a voltage regulator to produce steady current. In particular, consumer electronics usually include an AC adapter (type of power supply) to convert mains-voltage AC current to low-voltage DC suitable for consumption by microchips while consumer voltage converters (also known as "travel converters") are used when traveling between countries that use ĩ20 V versus ĩ40 V AC mains power.

Figure 1.9: AC-DC Converter

Circuit that use these types of converters can be single-phase or multiphase. In general, single-phase circuit are used for power supplies in home appliances (low power rectifiers) while three-phase circuit are used for industrial and high-power applications and for transmission of energy.

#### 1.3.4 AC-AC Converter

It is an electronic circuit that converts the alternating current waveforms having a certain magnitude and certain frequency into another alternating current waveform of different magnitude and frequency, allowing the control of the voltage, frequency, and phase of the waveform applied to a load from a supplied AC system. Even if it is not common in home appliances like the converters described above, this kind of conversion in principally necessary for speed controlling of machines, for low frequency and variable voltage magnitude applications. Hence, for example, by adjusting AC voltage using the AC to AC converter it is possible to regulate the speed of induction motors.

There are different kinds of AC to AC converters:

• Cycloconverters (also called *frequency changers*), are used in high power applications driving induction and synchronous motors.

Figure 1.10: AC-AC Converter

They are usually phase-controlled and they traditionally use thyristors due to their ease of phase commutation. Moreover in a cycloconverter, unlike other converters, there are no storage devices like inductors or capacitors. For this reason, the instantaneous input and output power are equal. In general, that are preferred for avoiding DC conversion and to limitate the number of stages like AC to DC to AC, since they are expensive and cause more losses. Some applications of cycloconverter are: cement mill drives, rolling mill drives and mind winders.

- DC link based AC to AC converter (aka AC/DC/AC converter), make use of a DC link, that is a rectifier is used to convert AC to DC and then an inverter is used to get AC from DC. As a result, an output with a different voltage and variable (higher or lower) frequency is obtained. Due to their wide area of application, these converters are the most common contemporary solution. Moreover they are stable in overload and no-load conditions as well as they can be disengaged from a load without damage.

- Matrix converters, the newer form of cycloconversion. This method removes the storage element in the DC-link, at the cost of a larger number of semiconductors. Matrix converters are often seen as a future concept for variable speed drives technology, but in spite of deep research over the decades they are not popular yet in the industrial market.

#### 1.3.5 Voltage Regulator and Power Supply

Voltage regulators or stabilizers are used in home appliances, like computer power supplies where they stabilize the DC voltages used by the processor and other components, to compensate for voltage fluctuations in mains power, i.e. in order to protect them from fluctuating input voltage. In this way, they hold up a constant AC or DC voltage that is independent of the load properties. There exist different techniques to stabilize AC voltage like electromechanical regulator and PWM static voltage regulator. This is the newest technique, and provides real time control of voltage variation, while to stabilize the voltage DC power supplies either series or shunt regulators are used. Power supplies are used in different range of application being a basic component of several electronic devices:

- Aircraft power supply: Both commercial and military avionic systems require a DC-DC power supply to convert energy into usable voltage;

- Electric Vehicle power supply: a power supply is needed to convert the high voltage coming from vehicle battery power;

- Computer power supply: it is a SMPS that converts the power from the mains supply to the several DC voltages needed internally. In particular, for their high efficiency (more than 90%), these converters are useful for task like convert a computer's main supply voltage (usually 12 V) down to the lower voltages needed by electronic components such as CPU or RAM, which need voltages on the order of 1.8 V or less;

Based on the voltage regulator used, power supplies can be broadly divided in two main types:

- 1. *Linear regulated power supplies,* based on devices that operate in their linear region and process the input power directly; they act as a variable resistance causing a voltage drop.

- 2. *Switching regulated power supplies,* based on a device forced to act as an on/off switch, that is providing output voltage by switching ideally lossless elements.

Both of them have some advantages depending on the applications and its requirements. For example, linear regulator are suitable if low EMI (Electromagnetic interference) and low noise are required; moreover at low drop level they are cheaper and occupy less PCB space, while switching regulator are suitable if power efficiency is critical or if the only power supply is a low DC voltage and a higher output voltage is required. It is true that the most important advantage of a SMPS is their efficiency, that is much higher that the efficiency of a linear power supply, since they dissipate a very little amount of power switching their output to keep the L/C output section at the correct voltage.

#### 1.3.5.1 Linear regulated power supplies

Linear power supplies, in order to produce the desired voltage, continually dissipate excess power in ohmic loss like a resistor, in the form of heat. In fact, they gain their name from the fact that they use linear, i.e. non-switching techniques to regulate the voltage output from the power supply. The main elements of linear power supply are:

- Input transformer (that determine size and weight of the device): As many power supplies get their source power from an AC mains input, it is common for linear power supplies to have a step down transformer to get lower voltage. This also serves to isolate the power supply from the mains input for safety.

- Rectifier: As the input from an AC supply is alternating, this needs to be converted to a DC format.

- Smoothing: Once rectified from an AC signal, the DC waveform needs to be smoothed to remove the varying voltage level, so large capacitors are used.

- Linear regulator: The smoothed supply is applied to the linear regulator, that provides a properly regulated output, since each load has different voltage requirement.

These devices are largely used since they offer a lot of benefits in terms of overall performance, and are especially used when the line regulation and removal of noise, coming from the AC line, is extremely important. So, even if it may not be as efficient as SMPS, often audio amplifiers and many other items of electronic equipment use linear power supplies to obtain the best performance. *Advantages*

- Low noise due to the use of the linear technology;

- No complexity: simpler circuit and simpler feedback loop stability criteria;

- Low risk of equipment damage;

#### Disadvantages

- Low efficiency, on the order of 30-40%.

- Size and weight: These devices result large and heavy due to the use of the input transformer and the capacitors;

- Losses in the regulator and the transformer;

#### 1.3.5.2 Switching regulated power supplies

In these devices the input power is converted to pulses before processing, by components that operate predominantly in non-linear modes (i.e. transistors that spend most of their time in cut-off or saturation). More in detail, the AC mains input is directly rectified and then filtered to obtain a DC voltage. The resulting DC voltage is then switched on and off at a high frequency by electronic switching circuitry, thus producing a sums of pulses that will pass through a high-frequency transformer or inductor and a capacitor. Switching occurs at a very high frequency (typically 10 kHz — 1 MHz), thereby enabling the use of transformers and filter capacitors that are smaller, lighter, and less expensive than those found in linear power supplies operating at mains frequency. After the inductor or secondary transformer, the high frequency AC is rectified and filtered to produce the DC output voltage. In particular, to keep the output voltage constant, the power supply employs a feedback controller that monitors current drawn by the load. The duty cycle of the switch determines how much charge is transferred to the load, and it increases as power output requirements increase. The output current flow depends on the input power signal, the storage elements and circuit topologies used, and also on the pattern used (i.e. PWM with an adjustable duty cycle) to drive the switching elements. Moreover, if a SMPS uses an adequately insulated high-frequency transformer, the output will be electrically isolated from the mains; it is an essential feature for safety. Advantages

## Invantages

- Reduced losses thanks to the use of a transformer operating at high frequencies;

- Smaller and lighter than a linear regulator;

- High efficiency: In the range of 70-90%, in fact almost all the power is transmitted to the load thanks to the little amount of wasted power;

### Disadvantages

- Greater complexity: They consists of a integrated controller, one or more power transistors and diodes as well as a power transformer, inductors and filter capacitors;

- Electromagnetic interference (EMI), due to the high switching frequency ;

#### 1.4 POWER ELECTRONIC CONVERTERS FOR ELECTRIC MOTOR DRIVES

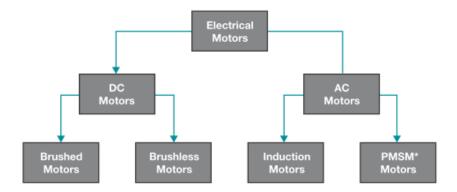

The primitive electric motors, since their first appearance (1886) more than a century ago with the American scientist Frank J. Sprague, have gone through a process of continuous evolution to achieve the goals of cost, size, and performance, and this evolution will continue into the future. All electric motors are governed by the laws of electromagnetism and are undergo to the same constraints forced by the materials (copper and iron) from which they are made. In particular, an electric motor is a device that converts electrical energy into mechanical energy, acting as a workhorse in a variable-speed drive system. Generally, an electric motor can be powered by direct current or by alternating current which leads to the two main classifications: AC motors and DC motors. Traditionally, AC machines, particularly induction motors, have been used in constant-speed applications, while DC machines were used in variable-speed applications. Furthermore, based on the two main classification there are multiple varieties of electric motor differentiated by structure and signal type., as depicted in Figure 1.11. Actually AC motors can be further classified in synchronous and asyn-

Figure 1.11: Motor Classification

chronous motors, that is whether or not the rotor runs at the same frequency as the stator.

In particular, the motor that we have used in this work is a *brushless DC motor*, depicted in Figure 1.13 and Figure 1.14, a synchronous motor powered by DC electricity with a SMPS which produces an AC electric current to drive each phase of the motor via a closed loop controller. For this reason only the brushless DC motor will be described in detail in the following; for reference a comparison between different motors is represented in Figure 1.12, showing the use of motors in terms of voltage and power levels, along with the pros and cons of each.

| Motor Type   | Voltage Levels | Power Levels   | Applications                                | Advantages                                                             | Disadvantages                                                                  |

|--------------|----------------|----------------|---------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Brushed DC   | <100V          | <100W          | Toys, coffee machine, gate openers, etc.    | Easy to spin, low cost                                                 | Brushes wear out,<br>Inefficient                                               |

| Brushless DC | <600V          | Up to a few kW | Household appliances,<br>white goods, pumps | Long life/reliable,<br>high efficiency                                 | Cost, complicated<br>control                                                   |

| AC induction | >600V          | >750 W         | Industrial and factory<br>automation        | Low cost, less maintenance,<br>rugged, reliable in wide<br>power range | Starting issues, low-<br>power factor correction,<br>complicated speed control |

Figure 1.12: Comparative analysis of motors

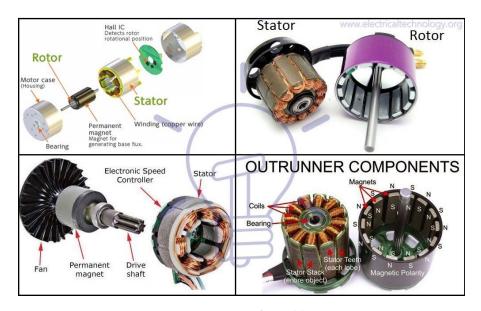

#### 1.4.1 Brushless DC Motor

The expansion of solid state power semiconductor electronics in the 1970s enabled the commutator and brushes to be removed in DC motors and the consequent growth of brushless motors. Today brushed motors are only used in low power applications or where only DC is available. The reasons that have brought to the elimination of the commutator and the decline of brushed motors are different:

- The friction of the brushes sliding along the rotating commutator segments causes torque losses that can be significant in a low power motor.

- The repeated abrupt switching of the current through the inductance of the windings causes sparks at the commutator contacts. These are a fire hazard in explosive atmospheres and can cause electromagnetic interference in nearby microelectronic circuits.

- Maintenance of the brushes;

Hence, thanks the advancement in the semiconductor technology, an electronic servo system replaces the mechanical commutator contacts, detecting the angle of the rotor, and accordingly controls semiconductor switches. The disposal of the sliding contact allows brushless motors to have less friction and longer life, making that their working life is only limited by the lifetime of their bearings. The BLDC motor is largely used in applications such as computer peripherals (disk drives, printers), appliances, automotive, aerospace, medical and automated industrial equipment. Since it is electrically commutated by power switches instead of brushes, it offers many advantages over traditional brushed DC and AC motors, such as:

- Smaller and lighter

- Lower materials costs

- Lower EMI

- Higher efficiency and reliability, largely due to the frequency at which the electricity is switched determined by the position sensor feedback

- Higher speed range

- Longer life

- Better speed versus torque characteristics

Another important advantage is that BLDC motor commutation can be implemented in software using a micro-controller or in digital firmware using an FPGA. In this way, as can be seen in our work, controller software can be customized to the specific motor being used in the application, resulting in greater efficiency.

Figure 1.13: Brushless DC motors

Figure 1.14: Construction of Brushless DC motor

However, since brushless motors do not self commutate, torque control, which is fundamental to the successful operation of any servo system, presents a more complex challenge. Several techniques have developed for controlling torque in brushless motors in order to produce the maximum torque, like sinewave control and Field Oriented Control (or Vector Control).

In particular, in this thesis a determinate application of BLDC motors has been analyzed, namely *Motion Control System*. Brushless DC motors are largely used in the industry, above all for motion control, actuation system and positioning thanks to the advantages above described. The most popular applications of BLDC motors in industrial engineering are linear motors, servomotors for machine tool servo drives, actuators drive motors for industrial robots.

To sum up, in the course of the last two decades the field of controlled electrical drives had spread fast thanks principally to the advances of semiconductors in power and signal electronics. In particular, these advancements have allowed the growth of motor drive control with ever lower power dissipation and ever more accurate control structures, that is not only are the DC current and voltage controlled but also the three phase currents and voltages are managed with vector controls. Thanks to this kind of control, the AC machine obtains each benefit of the DC machine and frees itself from the mechanical commutation disadvantages, achieving a very accurate steady state and transient control and leading to high dynamic performance in terms of response times and power conversion.

Everyday we see systems in motion all around us. What actually drives these movements are motors. Additionally, most household appliances such as refrigerators, air-conditioners, ventilation fans, washers, driers and so many others all require electric motors: the goal of this section is to discuss the role of power electronics in the motor drives of the applications that we use and encounter in household and industrial environments.

#### 1.4.2 Motor Control Overview

Motor control demands three fundamentals elements: a motor, a drive, and one or more feedback devices. The drive regulates current (in order to produce torque), knowing velocity and position. In nearly all control systems, multiple axes of motion must be controlled in synchronization. Usually a separate multiaxis controller provides coordination for the machine while the drives are left to implement the control associated with individual motors, but sometimes the application is so well defined that the drive and controller are integrated into one device, like a computer hard-disk controller. In brushless motors the torque command and the motor position are used to calculate multiple current commands in a process called commutation, whereas for brush motors, commutation is mechanical. As described formerly, motion control systems are among the most used in BLDC motors, such as pumps and fans. Additionally, they can be comfortably automated for remote control. The reason why brushless motors are preferred over stepper motors is that they are based upon a closed loop control system that produces closely controlled and stable operation, while DC stepper motors, for example, work with open loop control exhibiting torque pulsations.

#### 1.4.2.1 What is a drive?

An electric motor can be seen as a device that moves energy from an electrical source to a mechanical load. The system in which the motor is situated and makes it rotate is called the *drive*, and is shown in the Figure 1.15. The task of the motor drive is to get electrical energy from the source and provide electrical energy to the motor, such that the wanted mechanical output (speed of the motor, torque and the position of the motor shaft) is reached. Power converter have different

Figure 1.15: Block diagram of a motor drive system

tasks in the motor drive, such as:

- Transfer electrical energy from a source that could be of a given voltage, current at a certain frequency and phase as the input, to an electrical output of desired voltage, current, frequency and phase to the motor such that the required mechanical output of the motor is achieved to drive the load;

- Controller adjusts energy flow through feedback coming from the sensor block;

- Controller tells the converter what it needs to be doing. This is a closed-loop feedback system, that is the method of comparing what is actually happening to what the motor should be outputting, then adjusting the output accordingly to maintain the target output;

Enhancing the efficiency of systems motor-drive based could possibly come out in an important decrease in global electricity consumption, in fact a lot of researches show that electric motors represent about 50% of the whole electrical energy consumption across all applications. So, with the increasing demand of electricity due to the industrialization and urbanization across the world, the capability to provide energy is becoming even more challenging. The goal is to reduce energy consumption and carbon emissions on the environment by using an efficient power converter, that as it has explained in the previous sections, consist in the use of switched-mode power supplies (SMPS) that yields 100% efficiency in an ideal situation.

## 1.4.2.2 What is a servo system?

Nowadays, electronic motion control is a multi-billion-dollar industry. Servo motion is a fraction of that industry, sharing it with non-servo motion, such as stepper motors and variable-frequency systems. A servo system is defined as the drive, motor, and feedback device that enable accurate control of position, velocity, or torque using feed-back loops.

However, the lack of a separate feedback device does not mean the system is not a servo. This is because the feedback device may be present but may not be easily identified. For example, head-positioning servos of a hard-disk drive use feedback signals built into the disk platter rather than a separate feedback sensor; in addition, some applications use electrical signals from the motor itself to indicate speed. So, a servo motor is a sort of all-in-one device that has an electric motor, any integrated circuits required and a potentiometer included on the device.

Even if also stepper motors permit accurate regulation of motion, they are not servos, being based on "open-loop" systems without the need for stability analysis. One of the most important properties is the capacity to regulate position with fast response to changing commands and noise. Applications based on servo motor, generally cycle a motor from one position to another at high rates. However, there exist also servo applications that do not need fast acceleration, such as web-handling applications, which process rolled material such as tape, do not command large accelerations during normal operation.

## 1.5 A METHOD TO CONTROL A BRUSHLESS DC MOTOR: PULSE WIDTH MODULATION

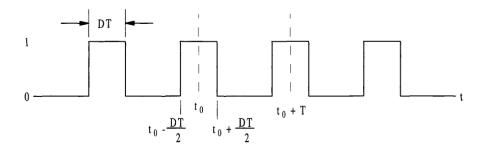

In order to understand the behavior of PWM, we need to understand how switching devices are represented in mathematics. To analyze the behavior of switching devices the Fourier Series of a switching functions is used, in fact through Fourier analysis, we can resolve periodic signals into individual frequency components. Since whatever switching function q(t) is either 0 or 1, and is generally periodic, a plot of a given q(t) will be a train of square pulses of arbitrary period T, as depicted in Figure 1.16.

Figure 1.16: A periodic pulse train

As can be seen, the pulse is centered on the time  $t = t_0$ . Each pulses in the train have duration *DT* and indicates a measure of the actual ON time, where D is defined as the *Duty Cycle*, with  $0 \le D \le 1$ . Duty cycle is a fraction of the period in which the system is working, where the period is the time it spends for a pulse to complete an ON and OFF cycle. Generally, it is expressed as a percentage, so the formula is:

$$D = \frac{DT}{T} * 100\% \tag{1.1}$$

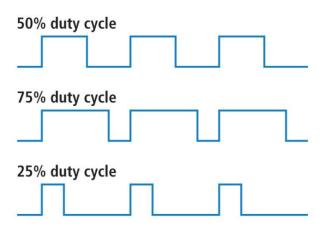

For example, as can be observed from the Figure 1.17, the first pulse has a duty cycle equal to 50%, in fact it remains high for 1/2 of

Figure 1.17: Three pulses with different Duty Cycle

the period or low for 1/2 of the period; the second one has a duty cycle equal to 75%, in fact the signal is on for 3/4 of the total period, while in the third one duty cycle is equal to 25%. It is widely used in electrical and electronics applications to describe the percent time of an active pulse in devices like SMPS, and in biological system as well, to describe the activity of neurons and muscle fibers. Besides duty cycle, a generic pulses is also described by the frequency  $f = \frac{1}{T}$  and the radian frequency  $\omega = \frac{2\pi}{T}$ . In particular, the Fourier components of q(t) are:

- $a_0 = D$ , it means that the DC component is equal to the duty cycle

- $c_n = \frac{2}{\pi} \frac{\sin(n\pi D)}{n}$ ,  $n \neq 0$

- $\theta_n = -n\omega t_o$

So, the Fourier Series for a general q(t) can be written as

$$q(t) = D + \frac{2}{\pi} \sum_{n=1}^{+\infty} \frac{\sin(n\pi D)}{n} \cos(n\omega t - n\phi_0)$$

(1.2)

The Fourier representation in 1.2 shows that the function q(t) is determined entirely by just three parameters: duty cycle D, radian frequency  $\omega = 2\pi f$ , and the reference time  $t_0$  thats fully define the switching function. Hence, switch action can always be interpreted in terms of one or more of the them, in particular:

- *Duty Cycle adjustment*: The duty cycle is related to the pulse width *DT*. Converters that operate by regulating the duty cycle of their switches exhibit PWM action;

- *Frequency adjustment*: It is unusual in power electronics for a very basic reason, that is places tight constraints on the switching frequencies due to the need to provide matching frequency components of voltage and current in a given source or load;

- *Timing adjustment*: It is one of the oldest methods to change the behavior of a power converter;

Today PWM and phase control are the most common adjustment techniques in power electronics. In this thesis a PWM technique and the duty cycle have been used to control our DC brushless motor.

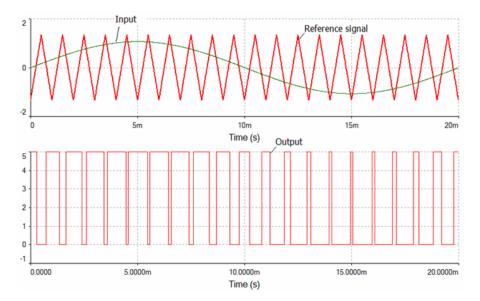

#### 1.5.1 Pulse Width Modulation