# Nonvolatile and SEU-Recoverable Latch Based on FeFET and CMOS for Energy-Harvesting Devices

Aibin Yan, Zhuoyuan Lin, Guangzhu Liu, Qingyang Zhang, Zhengfeng Huang, Jie Cui, Xiaoqing Wen, Patrick Girard

### ▶ To cite this version:

Aibin Yan, Zhuoyuan Lin, Guangzhu Liu, Qingyang Zhang, Zhengfeng Huang, et al.. Nonvolatile and SEU-Recoverable Latch Based on FeFET and CMOS for Energy-Harvesting Devices. ISCAS 2024 - IEEE International Symposium on Circuits and Systems, May 2024, Singapore, Singapore. pp.1-5, 10.1109/ISCAS58744.2024.10558033. lirmm-04738244

## HAL Id: lirmm-04738244 https://hal-lirmm.ccsd.cnrs.fr/lirmm-04738244v1

Submitted on 15 Oct 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Nonvolatile and SEU-Recoverable Latch Based on FeFET and CMOS for Energy-Harvesting Devices

Aibin Yan<sup>1</sup>, Zhuoyuan Lin<sup>1</sup>, Zhengfeng Huang<sup>2</sup>, Jie Cui<sup>1</sup>, Xiaoqing Wen<sup>3</sup>, Patrick Girard<sup>4</sup>

School of Computer Science and Technology, Anhui University, Hefei, China

<sup>3</sup>Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology, Fukuoka, Japan <sup>4</sup>Laboratory of Informatics, Robotics and Microelectronics of Montpellier, University of Montpellier / CNRS, Montpellier 34095, France

Abstract—Nonvolatile memories are widely used in emerging energy-harvesting Internet-of-Things (IoT) applications, and nonvolatile memories constructed from FeFET devices hold great promise. This paper presents a nonvolatile and single-event-upset (SEU)-recoverable latch based on FeFET and CMOS for energy-harvesting devices. The latch uses n-type FeFET devices to provide nonvolatility without any additional control signals. Moreover, since the soft error problem has become increasingly severe, radiation hardening by design gains a great attention as a promising approach to mitigate the reliability issue. The latch uses feedback interlocked loops with n-type FeFETs and C-elements, enabling it to provide nonvolatility and SEU-recovery simultaneously. Simulation results with Candence Virtuoso verifies that the proposed latch design has correct functioning with excellent performance compared to the state-of-the-art designs.

#### I. INTRODUCTION

In recent years, the continuous advancement of 5G technologies has facilitated the development of the Internet-of-Thing (IoT) industry, with various forms of smart devices being used in a large number of different applications in areas as diverse as healthcare and wellness care, machine building, environmental protection and home automation, among others [1]. These smart devices can be categorized as limited battery capacity and battery-less self-powered [2]. Devices with limited battery capacity often require frequent recharging when operating in a variety of complex and diverse real-world environments [2-3]. Devices in this category are costly to maintain and have significant application limitations. For battery-less self-powered devices, the energy harvesting technology can be used to efficiently capture the energy available in the environment, such as wind energy, solar energy, Wi-Fi, and Radio Frequency (RF) energy, and convert it to ensure the continuous operation of the device [4-5]. However, the energy of these external environments is usually unstable and cannot provide the stable power supply as battery-powered devices, and thus frequent power failures and recovery operations can lead to high energy consumption.

On one hand, as the Complementary Metal Oxide Semiconductor (CMOS) technology continues to advance and transistor feature sizes continue to shrink, soft errors have an increasing impact on the operation of electronic devices [6]. Single-event-upset (SEU) is a typical soft error that occurs when a high-energy particle, such as a neutron, a proton, a heavy ion, an alpha particle, or an electron, impacts a transistor

in a storage element [7], and the SEU can be detected at the drain of the affected transistor. Electronic devices without radiation-hardening are prone to soft errors that can lead to data corruption in the storage elements. Therefore, it is also an issue of great concern for safety-critical applications.

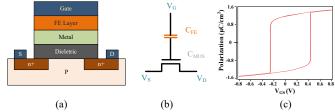

On the other hand, many emerging nonvolatile memory (NVM) technologies, such as spin-transfer torque RAMs (STT-RAMs) [8-9], ferroelectric field-effect transistors (FeFETs), magnetic random-access memories (MRAMs) and resistive random-access memories (ReRAMs) [10], have been proposed in recent years. An FeFET is a NVM device with promising applications, which can be categorized into n-type FeFET and p-type FeFET [10]. Figure 1 shows the features of a n-type FeFET device. As shown in Fig. 1-(a), there is a physical representation of the FeFET. An FeFET is essentially a CMOS transistor with a ferroelectric (FE) layer embedded in the gate. Note that the FE layer is integrated by ferroelectric materials. Figure 1(b) shows the equivalent circuit of the FeFET, where the FE capacitance (CFE) couples with the capacitance of the underlying MOSFET (CMOS). As shown in Fig. 1-(c), there is a polarization-voltage (P-V) hysteresis curve. The P-V curve shows the relationship between the VGS and the polarization of the n-type FeFET. V<sub>GS</sub> is calculated by subtracting the gate voltage from the source voltage. Depending on the V<sub>GS</sub>, the polarizations of the FE layer in the FeFET can be changed, making the FeFET exhibit different resistance states (HRS, P < 0 for a n-type FeFET and P > 0 for a p-type FeFET), or low resistance state (LRS, P > 0 for a n-type FeFET and P < 0 for a p-type FeFET). Note that the difference of resistance between HRS and LRS is almost as high as  $10^6$ .

Fig. 1. The features of a n-type FeFET device. (a) A physical representation. (b) The equivalent circuit. (c) The P-V hysteresis curve.

It is assumed that logic "1" is stored when the n-type FeFET is in the positive polarization state and logic "0" is stored when it is in the negative polarization state. We refer to the positive polarization state as state "1" and the negative polarization state

<sup>&</sup>lt;sup>2</sup> School of Microelectronics, Hefei University of Technology, Hefei, China

as state "0".

In this paper, FeFET-based latch structures are firstly reviewed, some of which modify conventional CMOS designs by adding several FeFETs to build peripheral nonvolatile modules, but providing nonvolatility in this way often requires additional control signals for backing up and restoring data [10-11]. The design proposed in [12] can provide nonvolatility by improving the structure of conventional inverters to perform backup and restore operations for data without additional control signals. All these designs can provide nonvolatile functionality. However, they cannot effectively provide protection against soft errors.

For the purpose of radiation hardening for basic storage elements, researchers have proposed many solutions, such as those in [13-16]. In [13], the circuit can tolerate SEUs, but it cannot ensure necessary recovery from SEUs. The solutions in [14-16] are SEU-recoverable. However, these designs only take into account the soft error resistance and do not enable nonvolatility.

In this paper, we propose a nonvolatile and SEU-recoverable FeFET-based latch. Eliminating the requirement for additional control signals, the proposed latch can autonomously back up data before the power failure and restore data after the power supply is restored. Moreover, compared to the state-of-the-art designs, the proposed latch provides both nonvolatility and soft error recovery, and also performs low cost in terms of power consumption and latency.

The rest of the paper is organized as follows. Section II describes in detail the proposed FeFET-based latch design. Section III evaluates the proposed design by comparing it with existing designs. Section IV concludes the paper.

#### II. PROPOSED FEFET-BASED LATCH DESIGN

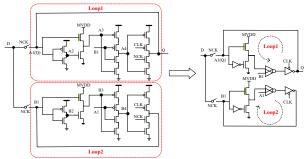

Figure 2 shows the structure of the proposed FeFET-based nonvolatile and SEU recovery latch. We propose a hybrid backup circuitry created using FeFET and CMOS technology in each feedback loops, which consists of a conventional nMOS, an inverter and a nonvolatile n-type FeFET. Note that the hybrid backup circuit uses nMOS and FeFET in series to form a voltage divider structure. Depending on the resistance state (HRS or LRS) exhibited by the FeFET in different polarization states, the corresponding storage values can be obtained by the voltage divider principle. A hybrid backup circuitry, a TG, a Celement (CE), and a Clock-gating (CG)-based inverter are used to create each feedback circuit, and the proposed latch consists of a couple of the feedback circuits which forms a symmetrical structure. As shown in Fig. 2, the hybrid backup circuitry, the CE and the CG-based inverter are connected in series in the feedback loop. We use the input of the hybrid backup circuit in a different feedback loop as one of the inputs connected to the CE in another feedback loop. The proposed latch stores values in the feedback loops by the hybrid backup circuitry. Representing an intermediate voltage between VDD and GND, the MVDD in the figure supplies the hybrid backup circuitry as high voltage, so that the output of the hybrid backup circuitry needs to pass through the CE and CG-based inverter in series to re-amplify the voltage to VDD. Note that the two feedback

loops have the same values at the same time.

Fig. 2. Structure of the proposed FeFET-based nonvolatile and SEU recovery latch

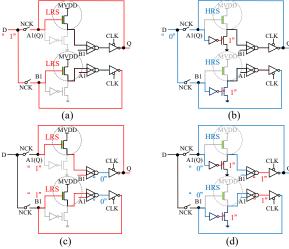

Fig. 3. Schematic of the proposed FeFET-based nonvolatile and SEU recovery latch in normal mode. In transparent mode, (a) FeFET is in LRS and (b) FeFET is in HRS. In hold mode, (c) FeFET is in LRS and (d) FeFET is in HRS. Note that '0' and '1' are used to represent GND and VDD, respectively.

Figure 3 shows the schematic of the proposed FeFET-based nonvolatile and SEU recovery latch in normal mode. In normal mode, the proposed latch works in transparent mode when CLK = 1 and in hold mode when CLK = 0.

In transparent mode (CLK = 1 and NCK = 0), the TGs open, and the values from D directly affects Q. For each feedback loop, the FeFET of the hybrid backup circuitry stores the values and exhibits the corresponding state "0"/"1". Figure 3-(a) and (b) show the states of the proposed latch in transparent mode, including the states of the latch and the states of the FeFET devices. When CLK = 1, the CG-based inverters of the two symmetrical loops are closed so that the values from D determine Q and B1 completely. As shown in Fig. 3-(a), when D = 1 and CLK = 1, Q is 1 and the FeFET devices are both in LRS. The operation process and corresponding states of the FeFET devices are the same as that described in the previous sub-section. The input voltage of the gate of the FeFET devices are VDD, and the voltage of the source of the FeFET devices both are MVDD. The FeFET devices can get a V<sub>GS</sub> that reaches a positive threshold to make the FeFET devices go to state "1" and the devices are both in LRS. As shown in Fig. 3-(b), when D = 0 and CLK = 1, Q is 0 and the FeFET devices are in HRS. For each FeFET device in the proposed latch, the input of the gate is GND with the source of the FeFET device being

connected to MVDD, which means that the FeFET device can get a V<sub>GS</sub> that reaches a negative threshold to make the FeFET go to state "0", and then the FeFET device is able to exhibit HRS.

In hold mode (CLK = 0 and NCK = 1), the TGs connected to D are closed, and the CG-based inverters are opened. The value of the proposed latch is stored in the symmetrical feedback loops. Figure 3-(c) and (d) show the states of the proposed latch in hold mode. As shown in Fig. 3-(c), when the value stored in the proposed latch is 1 and CLK = 0, Q is 1 and the FeFET devices are in LRS. At the gate of the FeFET devices, the inputs are VDD, and the source of the FeFET devices are connected to MVDD, which means that the V<sub>GS</sub> reaches a positive threshold to make the FeFET go to state "1", and thus the FeFET devices both exhibit LRS. As shown in Fig. 3-(d), when the value stored in the proposed latch is 0 and meanwhile CLK = 0, Q is 0 and the FeFET devices are both in HRS. At the gate of the FeFET devices, the inputs are GND and the source of the FeFET devices are connected to MVDD, which means that the V<sub>GS</sub> reaches a negative threshold to make the FeFET go to state "0", and then the FeFET devices exhibit HRS.

The proposed latch uses CEs to interlock values in each of the two symmetric feedback loops to robustly maintain correct data. Note that the latch can recover from any possible SEU in hold mode. Let us discuss the principle of SEU-recovery for the proposed latch. For example, when B1 is affected by SEU, the error passes to the CE of the hybrid backup circuit in series as well as another feedback loop in symmetry. Note that the erroneous values of B1 and MVDD work together to obtain the V<sub>GS</sub>, which here reaches the threshold voltage and changes the state of the FeFET device. The hybrid backup circuit then passes the erroneous values out to the CE in the current feedback loop. Since the CE's output still has the previous value when the two inputs are different, and the value of A1, which is in the different feedback loop, is not affected by the SEU, the CE receives the correct value of A1 as well as the erroneous value of the hybrid backup circuit and thus it outputs the original correct value. The correct output of the CE is returned to B1, restoring the value of the node and re-affects the V<sub>GS</sub> of the FeFET device, restoring it to the correct state.

In nonvolatile mode, the states of the FeFETs can determine the state of the proposed latch when recovering from a power failure. If Q is low before power failure, the FeFET devices store value "0", which means that the devices are both in state "0". For each FeFET device, which is in the HRS, the resistance is much larger than that of the nMOS connected in series with it. We can approximate the FeFET to be disconnected and the resistance of the nMOS to be neglected. Based on the principle of voltage division, Q finally returns to the low voltage. If Q is high before power failure, the FeFET devices store value "1". For each FeFET device, it is in state "1" and exhibits LRS, with the resistance of the device much larger than the nMOS which is connected in series with it. We can approximate the FeFET as having negligible resistance and the nMOS is disconnected. After the output of the backup circuits has been amplified by the CEs and CG-based inverters, Q returns to high voltage. Finally, Q can restore to the previous state correctly.

#### III. LATCH COMPARISON AND EVALUATION

Extensive simulations were performed using Cadence Virtuoso to verify the functioning of the proposed FeFET-based latch under a 65 nm CMOS technology as well as a FeFET model based on the Landau-Khalatnikov equation [17]. The thickness of the ferroelectric layer was set to 6.5 nm and the supply voltage was 0.8 V. Note that the same models and simulation parameters were used in the comparison of the state-of-the-art CMOS-based and/or FeFET-based latch designs for the purpose of a fair comparison.

#### A. Simulations of the Proposed Latch

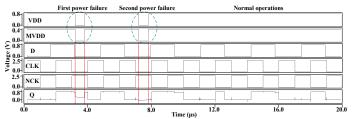

Figure 4 shows the simulations of power failures and normal operations of the proposed latch. We assume that VDD and MVDD are powered off at the power failures.

When suffering from power failures, the description of Section II regarding the nonvolatile mode of the proposed latch is still consistent with the current latch's state. As shown in Fig. 4, when it is in the first power failure (CLK = 0 and Q = 1), the FeFET devices keep state "1". If the power recovers from the power failure, the output can recover to 1 at a short time. When it is in the second power failure (CLK = 0 and Q = 0), the FeFET devices keep state "0". If the power recovers from power failure, the output can recover to 0. Note that the proposed latch can also perform the normal operations correctly, which is similar to a conventional latch.

Fig. 4. Simulations of power failures and normal operations of the proposed latch

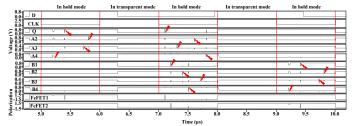

Fig. 5. Simulations of SEU injections of the proposed latch.

Figure 5 shows the simulation results of SEU injections of the proposed latch. We selected all of the possible SEUs (see Cases 1 to 2 below) for simulations.

Case 1: Each node in the top feedback loop, including Q(A1), A2, A3, and A4 suffers from an SEU, respectively. The SEUs were injected at Q at time 5.4  $\mu$ s and 7.1  $\mu$ s. As shown in Fig. 5, Q can recover from the SEUs. Similarly, SEUs were injected at A2, A3 and A4 at time sequences of (5.8  $\mu$ s, 7.6  $\mu$ s), (5.7  $\mu$ s, 7.3  $\mu$ s) and (5.2  $\mu$ s, 7.8  $\mu$ s), respectively. Clearly, all these nodes can completely recover from the injected SEUs.

Case 2: Each node in the bottom feedback loop, including B1, B2, B3, and B4 suffers from an SEU, respectively. The

TABLE I

COMPARISON RESULTS FOR ALTERNATIVE SEU/NONVOLATILE LATCH DESIGNS

| Latch                      | Technology | Number of<br>Transistors/Devices | SEU<br>Tol. | SEU<br>Rec. | NV. | Addi<br>Ctrl | D-Q Delay<br>(ps) | CLK-Q Delay<br>(ps) | Power<br>(nW) |

|----------------------------|------------|----------------------------------|-------------|-------------|-----|--------------|-------------------|---------------------|---------------|

| Latch [13]                 | CMOS       | 20MOS                            | ٧           | ×           | ×   |              | 3.31              | 4.11                | 240.4         |

| DICE [14]                  | CMOS       | 12MOS                            | ٧           | ٧           | ×   |              | 4.86              | 4.89                | 352.9         |

| SHLR [15]                  | CMOS       | 22MOS                            | ٧           | ٧           | ×   |              | 5.12              | 5.19                | 193.0         |

| RFC [16]                   | CMOS       | 24MOS                            | ٧           | ٧           | ×   |              | 5.64              | 5.58                | 193.3         |

| FeFET-in NVFF [10]         | FeFET      | 12MOS+1FeFET                     | ×           | ×           | ٧   | ٧            | 508.79            | 499.44              | 174.1         |

| FeFET-in NVFF [11]         | FeFET      | 11MOS+1FeFET                     | ×           | ×           | ٧   | ٧            | 179.11            | 174.45              | 149.7         |

| NCFET NV-Latch-NC [12]     | FeFET      | 12MOS+2FeFETs                    | ×           | ×           | ٧   | ×            | 277.32            | 270.01              | 190.0         |

| Proposed Latch<br>(SEU+NV) | FeFET      | 26MOS+2FeFETs                    | ٧           | ٧           | ٧   | ×            | 5.65              | 7.38                | 247.0         |

SEUs were injected at B1 at time 7.2  $\mu$ s and 9.4  $\mu$ s. As shown in Fig. 5, B1 can recover from the SEUs. Similarly, SEUs were injected at B2, B3 and B4 at time sequences of (7.4  $\mu$ s, 9.8 $\mu$ s), (7.7  $\mu$ s, 9.7  $\mu$ s) and (7.5  $\mu$ s, 9.2  $\mu$ s). Clearly, all these nodes can completely recover from the injected SEUs. Therefore, the simulations clearly demonstrate that the proposed latch can provide recovery from any possible SEUs.

#### B. Comparison Results with Alternative Designs

Table I illustrates the reliability and overhead comparison results for alternative SEU recovery and/or nonvolatile latches. Note that, in the table, "Tol." means "tolerant", "Rec." means "recoverable", "NV." means "nonvolatile", "Addi Ctrl" means whether a nonvolatile latch needs additional control signals, "D-Q Delay" is the average of the transmission delays (rise and fall) from D to Q, "CLK-Q Delay" means the average of the delays (rise and fall) from CLK to Q, and "Power" means the average of the power dissipation (dynamic and static).

For latch reliability comparisons, it can be seen from Table I that, the latch based on CMOS in [13] is SEU-tolerant but it cannot offer SEU-recovery and nonvolatility. The other CMOS-based latches, such as DICE [14], SHLR [15] and RFC [16], are SEU-recoverable, but they also cannot offer nonvolatility. The FeFET-based latches, including FeFET-in NVFF [10], FeFET-in NVFF [11], NCFET NV-Latch-NC [12], can only offer nonvolatility and cannot be SEU-recoverable (even non-SEU-tolerant). It can be seen that the proposed latch can simultaneously provide SEU-tolerance, SEU-recovery and nonvolatility. Note that, the proposed latch design does not need additional control signals, which is better than the nonvolatile latches that need additional control signals (including FeFET-in NVFF [10], and FeFET-in NVFF [11]).

Since the compared designs include CMOS-based as well as FeFET-based latches, we indicate the area overhead of the designs by comparing the number of transistors/devices. Note that the FeFET device is made by embedding ferroelectric material on the basis of CMOS and has excellent compatibility with CMOS, and thus we can approximate that an FeFET and a CMOS have the same area overhead and define it as a standard area. With regard to the number of transistors/devices, it can be seen from Table I that DICE is the latch having the minimum standard areas among the SEU-recoverable or SEU-tolerant latches (however, it cannot provide nonvolatility). It can also be seen that FeFET-in NVFF in [11] uses the smallest number of transistors and devices but the latch can only offer nonvolatility

without tolerance and recovery from SEUs. Clearly, the existing designs consist of 12 to 24 standard area. To provide more functionalities, such as SEU-tolerance, SEU-recovery, and nonvolatility, more area has to be introduced. That is the reason why 28 standard areas are used for the proposed latch, so as to integrates more functionalities.

With regard to the D-Q delay, for the proposed latch and some existing latches, such as SHLR, RFC, and the latch in [13], their D-Q delay is small because of the high-speed transmission path from D to Q. In contrast, the latches, such as FeFET-in NVFF in [10], FeFET-in NVFF in [11], and NV-Latch-NC, have a large D-Q delay because they use extra devices from D to Q. Note that the FeFET-based circuits tend to require more delay overhead than the CMOS-based circuits [18].

With regard to the CLK-Q delay, it can be seen from Table I that it is close to the D-Q delay because they are both related to the devices on the path from D to Q. The proposed latch has a moderate CLK-Q delay. The latches, such as the proposed latch, DICE, RFC, and the latch in [13], have a small CLK-Q delay, because they have a small D-Q delay. In contrast, FeFET-in NVFF in [10], FeFET-in NVFF in [11], and NV-Latch-NC, have a large D-Q delay, so that they have a large CLK-Q delay.

With regard to the power dissipation, DICE consumes the highest power, because of the high competition for current between nodes inside the latch and the fact that the latch does not use the CG technique. Note that, when a latch has a large area and/or does not use the CG technique, its power dissipation is high. Since the proposed latch uses redundant area to provide more functioning, it consumes extra but moderate power.

#### IV. CONCLUSIONS

In this paper, we have proposed a nonvolatile and SEU-recoverable latch based on FeFET and CMOS for energy-harvesting devices. Simulation results has demonstrated that the proposed design is SEU-recoverable and nonvolatile with moderate overhead compared to the state-of-the-art latch designs. Additionally, the proposed latch does not require additional control signals, making it applicable to energy harvesting and safety-critical applications.

## REFERENCES

T. Wu, "Reliable and Efficient Parallel Checkpointing Framework for Nonvolatile Processor with Concurrent Peripherals," *IEEE Transactions* on Circuits and Systems I: Regular Papers, vol. 70, no. 1, pp. 228-240, 2023.

- [2] Y. Wang, H. Fang, L. Long, et al, 2022. "Performance-oriented cache management scheme based on a retention state for energy-harvesting nonvolatile processors," *Future Generation Computer Systems*, vol. 129, pp. 90-98, 2022.

- [3] M. Wahbah, M. Alhawari, B. Mohammad, et al, "Characterization of Human Body-Based Thermal and Vibration Energy Harvesting for Wearable Devices," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, no. 3, pp. 354-363, 2014.

- [4] M. A. Weimer, T. S. Paing and R. A. Zane, "Remote area wind energy harvesting for low-power autonomous sensors," *IEEE Power Electronics Specialists Conference*, Jeju, Korea (South), pp. 1-5, 2006.

- [5] K. Ma, "Architecture exploration for ambient energy harvesting nonvolatile processors," *International Symposium on High Performance Computer Architecture*, Burlingame, CA, USA, pp. 526-537, 2015.

- [6] J. D. Black, P. E. Dodd and K. M. Warren, "Physics of Multiple-Node Charge Collection and Impacts on Single-Event Characterization and Soft Error Rate Prediction," *IEEE Transactions on Nuclear Science*, vol. 60, no. 3, pp. 1836-1851, 2013.

- [7] M. Ebara, K. Yamada, K. Kojima, et al, "Process Dependence of Soft Errors Induced by Alpha Particles, Heavy Ions, and High Energy Neutrons on Flip Flops in FDSOI," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 817-824, 2019.

- [8] Y. Zhang, L. Zhang, W. Wen, et al, "Multi-level cell STT-RAM: Is it realistic or just a dream?," *IEEE/ACM International Conference on Computer-Aided Design*, San Jose, CA, USA, pp. 526-532, 2012.

- [9] Y. Kumar, S. Sivakumar and J. Jose, "ENDURA: Enhancing Durability of Multi Level Cell STT-RAM based Non Volatile Memory Last Level Caches," 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration, Patras, Greece, pp. 1-6, 2022.

- [10] A. A. Saki, S. H. Lin, M. Alam, et al, "A Family of Compact Non-Volatile Flip-Flops With Ferroelectric FET," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 11, pp. 4219-4229, 2019.

- [11] S. K. Kim, T. W. Oh, S. Lim, et al, "High-Performance and Area-Efficient Ferroelectric FET-Based Nonvolatile Flip-Flops," *IEEE Access*, vol. 9, pp. 35549-35561, 2021.

- [12] X. Li, "Advancing Nonvolatile Computing With Nonvolatile NCFET Latches and Flip-Flops," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 11, pp. 2907-2919, 2017.

- [13] F. S. Alghareb, R. Zand and R. F. Demara, "Non-Volatile Spintronic Flip-Flop Design for Energy-Efficient SEU and DNU Resilience," *IEEE Transactions on Magnetics*, vol. 55, no. 3, pp. 1-11, 2019.

- [14] T. Calin, M. Nicolaidis, and R. Velazco, "Upset Hardened Memory Design for Submicron CMOS Technology," *IEEE Transactions on Nuclear Science*, vol. 43, no. 6, pp. 2874-2878, 1996.

- [15] S. Kumar and A. Mukherjee, "A Self-Healing, High Performance and Low-Cost Radiation Hardened Latch Design," *IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems*, Athens, Greece, pp. 1-6, 2021.

- [16] A. Yan, "A self-recoverable, frequency-aware and cost-effective robust latch design for nanoscale CMOS technology," *IEICE Transactions on Electronics*, vol. 98.C, no. 12, pp. 1171-1178, 2015.

- [17] T. Song, "Landau-Khalatnikov simulations for ferroelectric switching in ferroelectric random access memory application," *Journal of the Korean Physical Society*, vol. 46, no. 1, pp. 1-5, 2005.

- [18] C. Pan, "Beyond-CMOS non-Boolean logic benchmarking: Insights and future directions," *Design, Automation & Test in Europe Conference & Exhibition*, Lausanne, Switzerland, pp. 133-138, 2017.