# Automatic optimisation of system architectures using EAST-ADL

Martin Walker, Mark-Oliver Reiser, Sara Tucci-Piergiovanni, Yiannis Papadopoulos, Henrik Lönn, Chokri Mraidha, David Parker, Dejiu Chen, David Servat

## ▶ To cite this version:

Martin Walker, Mark-Oliver Reiser, Sara Tucci-Piergiovanni, Yiannis Papadopoulos, Henrik Lönn, et al.. Automatic optimisation of system architectures using EAST-ADL. Journal of Systems and Software, 2013, 86, pp.2467 - 2487. 10.1016/j.jss.2013.04.001 . cea-01810011

## HAL Id: cea-01810011 https://cea.hal.science/cea-01810011v1

Submitted on 7 Jun2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. ELSEVIER

Contents lists available at ScienceDirect

The Journal of Systems and Software

## Automatic optimisation of system architectures using EAST-ADL

Martin Walker<sup>a,\*</sup>, Mark-Oliver Reiser<sup>b</sup>, Sara Tucci-Piergiovanni<sup>c</sup>, Yiannis Papadopoulos<sup>a</sup>, Henrik Lönn<sup>d</sup>, Chokri Mraidha<sup>c</sup>, David Parker<sup>a</sup>, DeJiu Chen<sup>e</sup>, David Servat<sup>c</sup>

<sup>a</sup> University of Hull, Cottingham Road, Hull HU6 7RX, UK

<sup>b</sup> Technische Universität Berlin, Ernst-Reuter-Platz 7, D-10587 Berlin, Germany

<sup>c</sup> CEA Saclay Nano-INNOV, Point Courrier No. 174, 91191 Gif sur Yvette cedex, France

<sup>d</sup> Volvo Technology, Dept 6260, M2.7, 405 08 Gothenburg, Sweden

e KTH Royal Institute of Technology, Brinellvägen 83, 100 44 Stockholm, Sweden

### ARTICLE INFO

Article history: Received 31 July 2012 Received in revised form 28 March 2013 Accepted 1 April 2013 Available online 8 April 2013

Keywords: Multi-objective optimisation Architectural description languages Dependability Analysis Timing Analysis

#### ABSTRACT

There are many challenges which face designers of complex system architectures, particularly safety–critical or real-time systems. The introduction of Architecture Description Languages (ADLs) has helped to meet these challenges by consolidating information about a system and providing a platform for modelling and analysis capabilities. However, managing this wealth of information can still be problematic, and evaluation of potential design decisions is still often performed manually. Automatic architectural optimisation can be used to assist this decision process, enabling designers to rapidly explore many different options and evaluate them according to specific criteria. In this paper, we present a multi-objective optimisation approach based on EAST-ADL, an ADL in the automotive domain, with the goal of combining the advantages of ADLs and architectural optimisation. The approach is designed to be extensible and leverages the capabilities of EAST-ADL to provide support for evaluation according to different factors, including dependability, timing/performance, and cost. The technique is applied to an illustrative example system featuring both hardware and software perspectives, demonstrating the potential benefits of this concept to the design of embedded system architectures.

© 2013 Elsevier Inc. All rights reserved.

## 1. Introduction

Achieving quality attributes such as dependability (e.g. measured in terms of reliability, availability, and safety) and performance (e.g. measured in terms of throughput of information and response times) in complex systems is a challenging task. It is beneficial to consider these attributes throughout the whole design process, factoring them into early decisions and thereby ensuring that quality attributes are controlled from the early stages rather than left to emerge (or not) at the end, when any required changes would incur larger costs and delays. However, balancing the many demands on the system design can be difficult, and the task of

<sup>c</sup> Corresponding author. Tel.: +44 (0)1482 465994.

E-mail addresses: martin.walker@hull.ac.uk (M. Walker),

mark-oliver.reiser@tu-berlin.de (M.-O. Reiser), sara.tucci@cea.fr (S. Tucci-Piergiovanni), y.i.papadopoulos@hull.ac.uk (Y. Papadopoulos), henrik.lonn@volvo.com (H. Lönn), chokri.mraidha@cea.fr (C. Mraidha), d.j.parker@hull.ac.uk (D. Parker), chen@md.kth.se (D. Chen), david.servat@cea.fr (D. Servat). exploring potentially huge design spaces for optimal configurations that maximise quality (i.e., dependability and performance) and minimise cost poses even more challenges.

Recent work on model-based development has looked into how progressively refined models of requirements and design can be used to drive the development and verification of complex systems. This work has resulted in methods like UML and SysML which enable system modelling that encompasses description of structure, behaviour and allocation of functions to hardware resources. More recently, ADLs such as AADL and the automotive EAST-ADL have emerged as potential future standards for model-based design of embedded systems in the transport and space industries.

Beyond modelling of nominal behaviour, these languages also incorporate error modelling semantics that enable dependability analysis. Early work has demonstrated that dependability analysis of EAST-ADL models is possible via HiP-HOPS (Chen et al., 2008) while dependability analysis of AADL error models is possible via conversion to fault trees (Joshi et al., 2007) and Generalised Stochastic Petri Nets (GSPN) (Feiler and Rugina, 2007). MARTE (www.omgmarte.org) is another significant development, implemented as a UML profile for the design of real-time embedded systems, enabling prediction of other quality attributes, including performance and schedulability.

Abbreviations: ADL, Architecture Description Language; COE, Central Optimisation Engine; FAA, Functional Analysis Architecture; FDA, Functional Design Architecture; HDA, Hardware Design Architecture; OSDM, Optimisation Space Definition Module; VRM, Variability Resolution Mechanism.

<sup>0164-1212/\$ –</sup> see front matter © 2013 Elsevier Inc. All rights reserved. http://dx.doi.org/10.1016/j.jss.2013.04.001

New ADLs are likely to influence the design of future dependable systems. These languages can achieve transparency and consistency in a model-based process but are not yet sufficiently developed to guarantee effective assessment and satisfaction of quality attributes. We can identify two challenges that need to be tackled from the early stages of design:

- (a) Ensuring effective prediction of quality attributes such as dependability and performance, via use of advanced, scalable, automated model-based analysis techniques.

- (b) Enabling effective exploration of potentially huge design spaces for design solutions that achieve better or optimal trade-offs among dependability, performance and cost. We note that this capability is particularly relevant where little prior design experience exists to guide engineers in the design of a system, e.g. in case of innovative designs or when relatively immature technologies are employed.

#### 1.1. Analysis of architectural models

Over the last fifteen years, in order to tackle the first of these challenges, work on model-based dependability analysis has resulted in new approaches that partly automate and thereby simplify the synthesis of dependability evaluation models. In several techniques, predictive system failure models such as fault trees and FMEAs (Failure Modes and Effects Analysis) are constructed from the topology of the system and component failure models using a process of composition. In this approach, automation and reuse of component failure models across applications become possible to some extent. Compositionality and careful reuse are expected to bring benefits in dependability analysis similar to those introduced by reuse of trusted software components in software engineering. Techniques that follow this approach include HiP-HOPS (Papadopoulos et al., 2001), Component and State-Event Fault Trees (Grunske et al., 2005) and the Failure Propagation and Transformation Calculus (Wallace, 2005). Another body of research with similar objectives has developed in the area of formal verification, focusing on automated dependability analysis of systems represented as state automata (e.g. see work on Altarica (Bieber et al., 2004) and FSAP-NuSMV (Bozzano and Villafiorita, 2007)). In these approaches, model-checking is used to verify the satisfaction of dependability requirements or detect violations of requirements in normal or faulty conditions.

Tools have been developed to support these dependability and performance evaluation techniques and complex case studies have been reported that demonstrate benefits. However, relatively little work has been applied in the context of model-based design (especially in combination with ADLs). In the ATESST2 and MAE-NAD EU projects, it has been demonstrated that scalable automated dependability analysis can be achieved via harmonisation of EAST-ADL with HiP-HOPS. This work has shown benefits from the ability to produce complex fault trees and multiple failure FMEAs from designs expressed in an ADL (Chen et al., 2008). However, there is still scope for improvement in this work that could extend the state-of-the-art in model-based dependability analysis. In principle, AADL models-effectively state automata showing transitions from normal to degraded and failed states-can be converted to GSPNs and then analysed for dependability (Feiler and Rugina, 2007). However, in this approach, it is not possible to perform qualitative analysis, i.e., establishment of direct causal relationships between causes and effects of failure as in FMEA, which is important when probabilistic data are not available, e.g. at early stages of design. An alternative approach has been demonstrated in (Joshi et al., 2007) via conversion of AADL error models to fault trees. The main difficulty we have identified here is that the temporal semantics of the AADL error model (a form of state machine) are lost in the translation to combinatorial fault trees and this potentially causes serious errors. To correct this conceptual flaw and enable true temporal dependability analysis, we propose to enable analysis of AADL error models via HiP-HOPS, where a recently integrated temporal logic called Pandora can be used to achieve automated synthesis and analysis of dynamic fault trees, making it possible to capture the often significant effects of sequencing of faults. The problem has been discussed in (Walker and Papadopoulos, 2009) and a general solution was proposed; however, this solution still needs to be adapted in the context of particular modelling languages.

Another issue, often ignored in modern dependability analysis techniques, is that of separation of concerns in design. Most modelbased dependability analysis techniques assume that the model of the system (whether in the form of a block diagram or a state machine) is a functional model, effectively a joint representation of hardware and software. However, this ignores the separation of concerns that typically takes place in practical modelling, where people tend to develop separate models for hardware and software and link those models with allocation relationships. Such models are not directly analysable by the present state-of-the-art. In HiP-HOPS, a concept has been developed that enables integrated dependability analysis of designs that are represented in more than one perspective (e.g. hardware, software, middleware) via assessment of the fault propagation through allocation relationships.

In the context of timing analysis, many model-based approaches have been recently developed for the automotive domain. Projects such as ATESST and ATESST2 (www.atesst.org), TIMMO (www.timmo.org), and EDONA (www.edona.fr) have been carried out to provide concepts, tools and methodologies for the description of automotive architectures and timing properties.

Among the wide range of timing analyses, schedulability analysis (Selic, 2000) is considered a good candidate for analysing timing properties at the design stage. A model-based framework for schedulability analysis has been developed along these lines in the context of the EDONA project. This framework enables model-based schedulability analysis at the EAST-ADL design level. The EAST-ADL design level includes functional architecture, hardware architecture, and an allocation model stipulating the mapping of functions to hardware nodes. The schedulability framework is based on supplementing EAST-ADL with concepts from the modelling language MARTE following the procedure presented by Anssi et al. (2010). In this framework, schedulability analysis is performed after a manual transformation of EAST-ADL models towards a refined architecture: the MARTE task model. The manual transformation establishes the mapping of functions on tasks (including task priorities and periods). Then the framework provides an automatic transformation of MARTE task models to an academic scheduling analysis tool called MAST (http://mast.unican.es).

It should be noted that in the EDONA approach, schedulability analysis verifies the task model, and does not directly verify the design-level architecture.<sup>1</sup> Schedulability results therefore have to be manually 'fed-back' to the design level by interpreting schedulability properties obtained from the MARTE task model. Furthermore, extrapolating feedback to improve the design-level architecture is cumbersome or even impossible for non-schedulability experts. The reason for this lies in the fact that schedulability results depend not only on design-level architecture properties but also *on the choices made during the refinement towards the task model* (e.g. priority assignment, task periods, scheduling policy, etc.).

<sup>&</sup>lt;sup>1</sup> It is worth noting that EAST-ADL lacks implementation-like concepts, such as the task concept, although other languages (e.g. AUTOSAR) can be used to overcome this later in the system development process.

The ATESST2 and MAENAD projects made improvements to model-based timing analysis for EAST-ADL models in order to produce automatic feedback on the EAST-ADL architecture. Simple feedback can be obtained by analysing architecture properties which do not need refinement towards a task model, such as resource utilisation, which can be computed only knowing the allocation of functions/signals to hardware resources. For more advanced indicators, such as response time analysis of function activation chains that traverse several shared hardware resources, full schedulability analysis is still needed, which necessitates refinement towards a task model to configure schedulability analysis tools. However, by applying *controlled* refinements, it is possible to produce automatic feedback at design level. In this paper we adopt one of these possible controlled refinements, which is detailed in Section 2.4.

#### 1.2. Optimisation of architectural models

Model-based analysis and verification technologies can enrich a model-driven development process by answering important questions regarding the quality of individual design proposals. In complex distributed systems, however, rich functionalities and their distribution across shared hardware and communication channels allow a large number of configuration options at design time and a large number of reconfiguration options at runtime. This creates difficulties in design because, as potential design spaces expand, their exploration for suitable or optimal designs becomes increasingly difficult. When a number of different architectural configurations can potentially deliver the functions of a system, designers are faced with a difficult optimisation problem. Assuming that it is technically and economically possible to fulfil all quality requirements, they must find an architecture that entails minimal development and other lifecycle costs. On the other hand, if fulfilling or optimising all quality requirements is infeasible, then they must find the architecture or architectures that achieve the best possible tradeoffs among quality attributes and cost. The problem is compounded by the fact that quality attributes are often conflicting, e.g. improving safety often means not only increasing costs but also reducing availability. The various formulations of the above represent hard, multi-objective optimisation problems that can only be approached systematically with the aid of optimisation algorithms that can efficiently search large potential design spaces.

Whilst many design problems can only be tackled effectively by the human intellect, it is clear that, as potential design spaces expand, their exploration for suitable or optimal designs (e.g. in terms of quality and cost) becomes increasingly difficult, and some automation is needed. Modelling languages and emerging ADLs could therefore benefit from concepts and technological support that enable this type of optimisation, while still benefiting from the support for multiple analysis and evaluation functions that an ADL offers.

Some work has recently been done in this field from the direction of safety and reliability analysis, though not in the context of ADLs. Classical dependability models like Reliability Block Diagrams (RBDs) (Konak et al., 2006) and, more recently, advanced compositional dependability analysis techniques such as HiP-HOPS have been combined with meta-heuristics (Pareto-based Genetic Algorithms) to assist in the automatic evolution of design models that can meet dependability and cost requirements. HiP-HOPS has contributed to this area by enabling the optimisation of systems that have a networked architecture (i.e. they are not necessarily in parallel/series configurations as in RBDs) and by overcoming the traditional assumption made in RBDs that a component or system either works or fails in a single failure mode (Papadopoulos and Grante, 2005; Papadopoulos et al., 2011; Adachi et al., 2011). Recent work that has focused on enabling multi-objective optimisation of software architectures has led to the development of new tools that also offer a blend of analysis and optimisation capabilities. One such tool is PerOpteryx, which is based on the Palladio modelling environment (Martens et al., 2010; Koziolek and Reussner, 2011). PerOpteryx allows for the automatic optimisation of software architecture models, developed with Palladio using the Palladio Component Model (PCM), on the basis of four main quality dimensions: cost, reliability, maintainability, and performance. One particular advantage of PerOpteryx is its ability to take advantage of domain specific knowledge, such as performance tactics, to enhance the optimisation (Koziolek et al., 2011).

Another tool is AQOSA (Automated Quality-driven Optimisation of Software Architecture), which uses model transformation technology to convert input models (e.g. from AADL or a general UML2 model) into an intermediate format (AQOSA-IR) that can be used as the basis of the optimisation process (Etemaadi and Chaudron, 2012). Different candidates are provided by a repository of possible components, and a set of external objective function plugins provides the evaluation that drives the process. AQOSA is designed to be independent of any given domain specific language (DSL) or ADL, but therefore relies on a correct model transformation to its own intermediate model to perform the optimisation.

Finally, other work by Grunske et al. has shown the potential of using various meta-heuristics for dependability versus cost optimisation of architectural designs. This work has been applied to AADL models and also looks at other optimisation approaches beyond genetic algorithms, e.g. ant trail algorithms (Aleti et al., 2009a,b; Meedeniya et al., 2010, 2011; Meedeniya and Grunske, 2010). An introduction to the model-based optimisation field can also be found in Grunske et al. (2007), and a wider survey of literature on architectural optimisation techniques can be found in Aleti et al. (2012).

All of the approaches mentioned above exploit meta-heuristics to search a design space for optimal solutions. However, they operate on different models (EAST-ADL, PCM, AQOSA-IR etc.) and use different means of defining the design space (e.g. variability mechanisms). They also address different objectives, which they define in different ways, and use different techniques to evaluate those objectives. The aim of this paper is to contribute to the state of the art by developing an approach which brings a unique combination of objective evaluation techniques (e.g. HiP-HOPS, MAST) derived from information obtained from the variability capabilities and quality attributes provided by EAST-ADL. Therefore, while there are both commonalities and differences across the optimisation approaches mentioned above, we believe our approach offers a unique configuration that combines the benefits of external analysis tools and the all-in-one modelling capabilities offered by EAST-ADL.

#### 1.3. Contributions of the paper

In this paper, we show how earlier work on design optimisation, e.g. work developed in the context of HiP-HOPS, can be transferred to model-based design—specifically in the context of the EAST-ADL language. The novel contributions of the paper are:

- The development of a general method for automatic optimisation of EAST-ADL models via genetic algorithms. The method so far enables evaluation of unavailability, simple cost metrics, and schedulability of candidate designs to drive the optimisation, but could be extended in the future to other functional and non-functional attributes as well.

- The use (in the context of optimisation) of advanced mechanisms which allow adequate parameterisation of models and

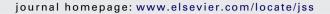

Fig. 1. The EAST-ADL abstraction levels (http://www.east-adl.info/).

expression of design variability in the language where the model is expressed (i.e., EAST-ADL).

- Applicability of the approach on architectural models which are represented in multiple perspectives, i.e., separate hardware and software design diagrams which are linked with allocations of software to hardware. This is a non-trivial matter as most approaches to dependability and optimisation assume a single functional model of the system as basis for any analysis.

- The use of annotations of a core structural model to formalise timing, cost, energy consumption, etc. for the purpose of architecture evaluation as a part of optimisation. The modular approach makes it possible to provide annotations consistent with variants, and corresponding to the input needs for fitness functions of the intended optimisation. Whilst not all of these annotations are currently exploited, the optimisation architecture described in the paper is extensible and could tap further into the wealth of design information captured within an EAST-ADL model.

In the next section, we shall describe EAST-ADL, its major features, and its capabilities for linking with external analysis tools to perform safety and timing analyses (amongst others). In Section 3, we describe the multi-objective optimisation concept and the tool architecture being developed to fulfil this concept, and in Section 4 we apply the approach to a simple example system to illustrate many of the advances mentioned above (multiple perspectives, variability representation, timing and dependability information etc.). Finally we present our conclusions in Section 5.

## 2. Representing system architectures with EAST-ADL

## 2.1. Introduction to EAST-ADL

EAST-ADL is an Architecture Description Language (ADL) initially defined in the European ITEA EAST-EEA project and subsequently refined and aligned with the more recent AUTOSAR automotive standard (www.autosar.org). Currently, it is maintained and evolved by the EAST-ADL Association (www.east-adl.info).

EAST-ADL is an approach for defining automotive electronic systems by way of a comprehensive information model that captures engineering information in a standardised form. Aspects covered include vehicle features, functions, requirements, variability, software components, hardware components and communication.

As a guiding principle, EAST-ADL defines multiple abstraction levels and distributes all development information across these levels (see Fig. 1). Thus, software- and electronics-based functionality of the vehicle is described at different levels of abstraction during the development from early analysis to implementation. The proposed abstraction levels are tailored to provide a separation of concerns and an implicit style for using the modelling elements. The embedded system is complete on each abstraction level, and parts of the model are linked with various traceability relations. This makes it possible to trace an entity from feature level down to components in hardware and software.

The features in the main technical feature model at vehicle level represent the major functionalities and characteristics of the complete system, i.e., the entire vehicle from a top-level perspective, without exposing any realisation details. It is possible to manage the content of each individual vehicle and entire product lines in a systematic manner. In addition to this main feature model with its technical perspective, other feature models may be defined that provide views on the main feature model, e.g. a customer/marketing-oriented view defining models and packages of optional equipment.

A complete representation of the electronic functionality in an abstract form is modelled in the Functional Analysis Architecture (FAA). The purpose is to define and structure the system's functionality from a problem domain perspective, similar to a traditional functional analysis. Entities of the FAA, so-called analysis functions, capture the principal interfaces and behaviour of the vehicle's subsystems.

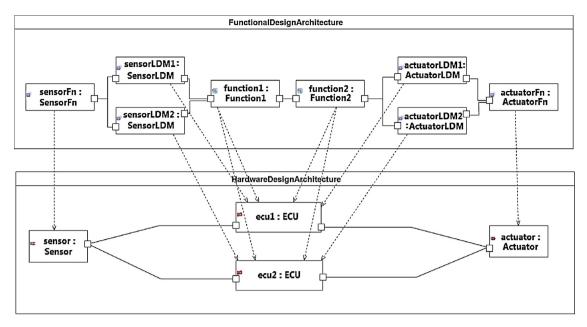

The solution domain aspects are introduced while defining the design level, which comprises the Functional Design Architecture (FDA) and the Hardware Design Architecture (HDA). The FDA defines a function architecture that takes into account hardware allocation, efficiency, legacy and reuse, commercial-off-the-shelf (COTS) availability, and other architectural qualities. The function structure is such that one or more functions can be subsequently realised by one or several AUTOSAR software components (SW-C). The external interfaces of such components correspond to the interfaces of the realised functions. On the other hand, the HDA defines the execution environment in which the software will be deployed. Its main entities are sensors, actuators, units of execution, their interfaces, and communication links between all these. Finally, the allocation joins the FDA and HDA by defining for each software entity in the FDA on which unit of execution, as defined in the HDA. it will reside.

On the lowest, most concrete abstraction level, the implementation level, EAST-ADL does not provide its own modelling entities; instead, this level is entirely defined by models from the AUTOSAR standard. In this respect, EAST-ADL can be thought of as an extension to AUTOSAR providing support for modelling on higher abstraction levels during earlier development phases. However, traceability is supported from implementation level elements (AUTOSAR) to FDA/HDA elements and, from there, further up to vehicle level elements.

Verifying and validating a feature across all abstraction levels, by using simulation or formal techniques, requires an environment model from the early stages of the design process. This "plant model" captures the behaviour of the vehicle dynamics, driver, etc. The core part of the environment model can be the same for all abstraction levels, which means that, for the purpose of simulation, both FAA and FDA/HDA are attached to the same environment model.

#### 2.2. Variability modelling in EAST-ADL

EAST-ADL provides extensive support for managing variability, which is a key element of the EAST-ADL-based optimisation approach presented in this article. First, variability modelling is used to define the optimisation space (also referred to as the "architectural degrees of freedom" in Aleti et al. (2012)) and then configuration and variability resolution are applied to produce the individual optimisation candidates to be evaluated with respect to the optimisation objectives. Before going into more detail on

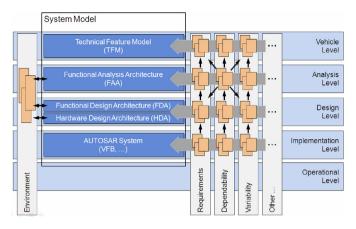

Fig. 2. Feature models on different EAST-ADL levels and the configuration links connecting them.

the optimisation approach in Section 3, we therefore describe the EAST-ADL variability management concepts here.

Modelling of variability in EAST-ADL starts on the vehicle level, where model range features and variability are represented. At this point, the purpose of variability management is to provide a highly abstract overview of the variability in the complete system together with dependencies between these "variabilities". A *variability* in this sense is a certain aspect of the complete system that changes from one variant of the complete system to another. In this abstract overview, the idea is not to specify how the system varies with respect to an individual variability but only that the system shows such variability. For example, the front wiper may or may not have an automatic mode. At vehicle level, the impact of this variability on the design is not defined; only the fact that such variability exists is defined by introducing an optional feature named "RainControlled-Wiping". This is subsequently validated and refined during analysis and design.

One or more feature models may be defined on the vehicle level: the core Technical Feature Model—the main feature model in an EAST-ADL system model—is used to define the complete system's variability on a global level from a technical perspective, and one or more optional Product Feature Models can be used to define views on this technical variability which can be tailored to a particular view-point or purpose, e.g. the marketing-oriented end customer perspective. An example of this is shown at the top of Fig. 2.

While the details of how variability is actually realised in the system are largely suppressed at the vehicle level, they are the focus of attention when managing variability in the FAA, FDA and HDA. In fact, a specific variability may lead to modifications in any development artefact, such as requirements specifications and functional models. Here, describing that a specific variability occurs is not sufficient; it is necessary to describe how each variation affects and modifies the corresponding artefact.

The purpose of feature modelling is to define the commonalities and variabilities of the product variants within the scope of a product line. Feature models are normally used on a high level of abstraction, as described above for vehicle level variability. However, in EAST-ADL, they are also used on analysis and design levels and acquire a much more concrete meaning there: they can be attached to analysis and design functions and are then used to expose the variability within this function only. Fig. 2 illustrates this for the FAA: the top-level analysis function "Car" contains a subfunction "WiperSystem" which in turn consists of the subfunction "RainSensor" and "WiperController"; all the analysis functions "Car", "WiperSystem" and "WiperController" have a feature model attached.

In addition to their feature model, analysis and design functions may contain variation points defining how the function's structure varies from one system configuration to another. In EAST-ADL, such structural variation can be represented by marking structural entities—e.g. subfunctions, ports, connectors—as optional, which is denoted graphically by a dashed line. Fig. 2 presents an example: the "WiperSystem" has an optional subfunction "rs" of type "Rain-Sensor". All actual system variation on analysis and design level is defined using this straightforward concept of optional structural entities.

Configuration decision modelling is another key variability management concept in EAST-ADL: the configuration of a target feature model FM<sub>T</sub>-i.e. the selection and deselection of its features-is defined in terms of the configuration of another feature model FM<sub>S</sub>, called source feature model. A configuration decision model can thus be seen as a directed relation from FM<sub>S</sub> to FM<sub>T</sub> that allows us to derive a configuration of FM<sub>T</sub> from any given configuration of FM<sub>S</sub>. In EAST-ADL, this mechanism is used to define how a certain configuration on a higher level affects the binding of variability on lower abstraction levels and in lower-level components. Again, Fig. 2 provides an example: configuration links are depicted as dashed arrows and are defined between all the feature models; the one from the "Technical Feature Model" to the feature model attached to "Car", for instance, defines how to configure the "Car" analysis function depending on a given configuration of the core technical feature model on vehicle level; note how this configuration link crosses abstraction layers while the links from the "Car" to the "WiperSystem" feature model crosses containment hierarchies within the analysis architecture (the same applies to the FDA and HDA, but this was omitted from the figure). Similarly, configuration links are used to define how the structural variability within analysis and design functions is resolved depending on

a given configuration of the function's feature model. For example, the configuration link in the "WiperSystem" function of Fig. 2 states how the optional subfunction "rs" will be selected or deselected depending on the configuration of the wiper system's feature model.

Variability management on analysis and design level is driven by the variability identified on the vehicle level. This means that the main driver for variability definition and also variability instantiation is the vehicle-level feature model. Variability specification in FAA and FDA/HDA essentially consists of the definition of *variation points* within the analysis and design functions (in the form of optional subfunctions, connectors and ports). As mentioned above, feature models can be attached to functions in order to expose the variability within these functions and hide the actual structuring, representation and binding of this function-internal variability. This way, the benefits of information hiding can be applied to the variability representation and variability binding within the containment hierarchy of functions in the FAA and FDA/HDA of EAST-ADL.

In summary, EAST-ADL provides the means to define variantrich systems and to organise this information such that an entire, fully resolved system configuration can be derived automatically from the configuration of a single feature model on vehicle level. For the purpose of this article, this means that we can define the optimisation space, i.e. the set of systems to be evaluated, by way of EAST-ADL's variability modelling concepts and then produce individual candidates within this optimisation space by applying EAST-ADL's configuration and variability resolution mechanisms.

#### 2.3. Dependability analysis of EAST-ADL models with HiP-HOPS

EAST-ADL offers powerful fault modelling capabilities centred on its ErrorModel concepts. The ErrorModel in EAST-ADL is a separate modelling view, parallel to the nominal system models on each level, and allows system designers to specify how the system elements can generate failures and how those failures can propagate to other parts of the system.

As with other parts of EAST-ADL, the ErrorModel only stores information; analysis capabilities have to be provided by an external tool. As part of the ATESST2 and MAENAD projects, significant effort has gone into enabling the HiP-HOPS (Hierarchically-Performed Hazard Origin and Propagation studies) safety analysis tool to analyse EAST-ADL models by means of model transformation technology. This has entailed some harmonisation of the error modelling concepts in both EAST-ADL and HiP-HOPS and the result is a powerful dependability analysis capability for EAST-ADL models.

A HiP-HOPS analysis has three main stages:

- Fault modelling and failure annotation

- Synthesis of fault trees to model the propagation of failure through the system

- Fault Tree Analysis (FTA) and synthesis of Failure Modes and Effects Analysis (FMEA) tables

The first phase is manually performed and consists of annotating the elements of the system model (or in this case, the EAST-ADL error model) with logical expressions that describe their local failure behaviour, i.e., what output failures they propagate (known as *output deviations*) and how those output failures are caused by a mixture of input faults and internal failure modes. In their basic form, these expressions take the form of a failure class (e.g. commission, omission) and the name of the port and component where the deviation occurs and combines them with logical operators such as AND and OR. For example:

indicates that an omission of the 'out' port of an actuator component is caused by either a similar omission received at the 'in' port of the Actuator or an internal failure mode called "ActuatorStuck", which may also have probabilistic failure data (e.g. failure rate, repair rate, MTTF etc.) defined. Such expressions can take more complex forms to express generalised patterns of component failure behaviour.

The second and third phases are conducted automatically by HiP-HOPS. First, a network of interconnected fault trees is synthesised by combining the logical expressions, thereby showing the relationship between system hazards and combinations of individual component or function failures. In the third phase, the fault trees are analysed using FTA reduction algorithms to obtain the minimal causes of system failures together with estimates for the probabilities of those failures. This information is used to construct FMEA tables which show not only the effects of each individual failure mode, but also the effects of multiple failure modes occurring in conjunction.

#### 2.3.1. Multi-perspective analysis in HiP-HOPS

One of the biggest differences between the HiP-HOPS error model and the EAST-ADL approach is that EAST-ADL does not limit the system modeller to a single architecture, as HiP-HOPS does. Not only are the ErrorModel and nominal model separate, but EAST-ADL provides multiple layers or levels of potential modelling as well as different views or perspectives of a model. HiP-HOPS can be applied to EAST-ADL models at both the analysis and design levels, each of which may contain a number of different perspectives. For example, at the analysis level, the primary modelling perspective is the Functional Analysis Architecture (FAA), which provides an abstract view of the functions of the system and which will have a similarly abstract Error Model attached. Later, at the design level, the model may be separated into the Functional Design Architecture (FDA), which represents the concrete functional perspective, and the Hardware Design Architecture (HDA), representing the hardware perspective, and each of these may have a separate-but interrelated-Error Model.

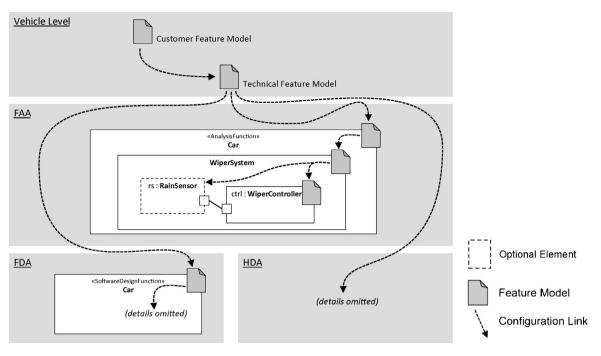

In HiP-HOPS, software and hardware are usually modelled together as part of the same architecture, with software functions being defined as subcomponents of hardware elements. This can be emulated in EAST-ADL by combining everything into a single perspective, but the advantages of having multiple perspectives are then lost. Instead, in order to make it compatible with EAST-ADL and to allow for the propagation of failures from software to hardware or vice versa, HiP-HOPS has been extended with native multi-perspective capabilities, as shown in Fig. 3.

In EAST-ADL, hardware and software entities can be in separate architectures (e.g. HDA and FDA) and the relation from one perspective to the other is accomplished by means of *allocation* relationships, in which software functions are allocated to the hardware components that execute them. Failures of the hardware components will propagate to the software functions allocated to them. HiP-HOPS now provides the same capabilities, and in addition to an output deviation being caused by an input deviation or an internal failure mode, it may now also be caused by a failure propagated from the component the current function is allocated to. For example:

Omission-Function.out = Omission-Function.in OR FromAllocation (PowerFailure)

Fig. 3. Multi-perspective modelling in HiP-HOPS.

This specifies that the omission of output from a software function is caused either by a lack of input or a particular failure (power failure in this case) being propagated from the hardware component that the function is allocated to.

Furthermore, in both EAST-ADL and now in HiP-HOPS, it is possible to define *more* than one possible allocation, e.g. using variability constructs in EAST-ADL. This allows scope for potential optimisation of the model on the basis of changing the allocation of software functions to different hardware components.

The introduction of multiple perspectives to HiP-HOPS has necessitated a change to the semantics of common cause failures, which HiP-HOPS previously treated as global failures. Whereas before common cause failures (CCFs) were globally accessible throughout the model, and could cause a failure of any component, now CCFs are defined per modelling perspective, and thus a CCF defined for the hardware perspective (e.g. flooding, fire) would not be accessible from a function in the software perspective, for instance.

For any rare cases where arbitrary cross-perspective propagation is required, HiP-HOPS provides a 'Goto' declaration. This allows failures to propagate from one component in one perspective to another component in a different perspective (or, for that matter, in the same perspective), even if those components do not share an allocation relationship.

Because these new connections (allocations and gotos) connect to existing HiP-HOPS constructs (namely, output deviations and the normal local failure logic), they fit relatively seamlessly into the HiP-HOPS fault tree synthesis process. Once the fault trees are generated, they can be analysed as normal without any further distinction between one perspective and another.

This harmonisation of EAST-ADL and HiP-HOPS error modelling concepts provides a powerful dependability analysis capability for EAST-ADL models, allowing fault propagation to be traced across several different modelling views. This also enables optimisation of EAST-ADL models using dependability characteristics (e.g. safety, unavailability) as objectives, as shown in Section 4.

## 2.4. Timing analysis of EAST-ADL models

EAST-ADL, and specifically its Timing Extension, provides a rich set of concepts to support timing analysis. The term "timing analysis", however, encompasses a wide range of analyses applicable to different models (and levels of abstraction) produced during the development process. High-level analyses, such

as using model-checking for the verification of the timing properties of the functional model, can usually be employed from the very beginning of the development process, as soon as functional behaviours are defined. Conversely, low-level analyses, such as task level schedulability analysis, compute timing properties of functions when conceptually executed on detailed software/hardware resource models. These resource models include information about processor/bus schedulers and task/message configurations and are in general produced at later stages of the development process.

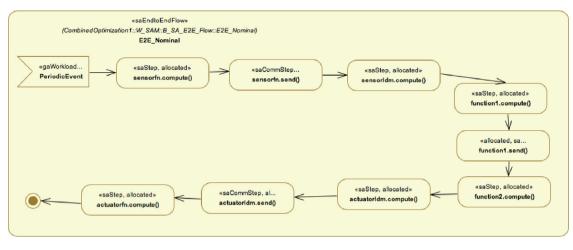

In this paper we are primarily interested in the design level of EAST-ADL, where the allocation of functions on hardware nodes is defined and timing analysis can be applied in conjunction with dependability analysis. Specifically, the design-level concepts used by the analysis are:

- activation chains of functions, the rate of their activation, worst case execution times of functions and end-to-end deadlines;

- (2) the topology of the hardware network in terms of processors and the buses that connect processors;

- (3) the allocation of functions on processors.

These concepts come from EAST-ADL's FunctionModelling, HardwareModelling and Timing aspects, and are specified in the FDA, the HDA, and the associated Timing View respectively.

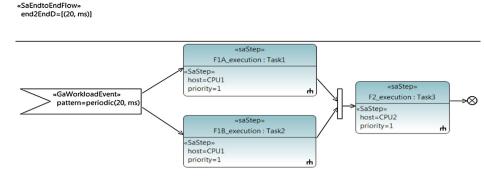

Timing analysis at this stage aims to evaluate the impact that hardware resources may have on the execution of functions, although it makes use of more abstract resources than those used by schedulability analysis (no tasks, schedulers, etc.). To give a simple example on the importance of evaluating the resource impact on function execution, let us consider the architecture in Fig. 3. In this example, Functions F1A and F1B do not have precedence dependencies, so they can be logically executed in parallel. As a comparison, assume that the two functions are allocated on the same CPU, meaning that F1A and F1B are executed sequentially. Now let us consider that Function F2 must produce a value for each cycle of duration T (deadline). In each cycle F2 must consume at least one value produced by F1A and one produced by F1B in the same cycle. It is clear that if the two functions could be executed in parallel and start at the beginning of the cycle, input values for F2 will be available after max(C1, C2), where C1 and C2 are estimated worst case execution times. On the other hand, in case of sequential execution, the input values for F2 will be available only after *sum*(*C*1, *C*2). These situations must be carefully analysed as

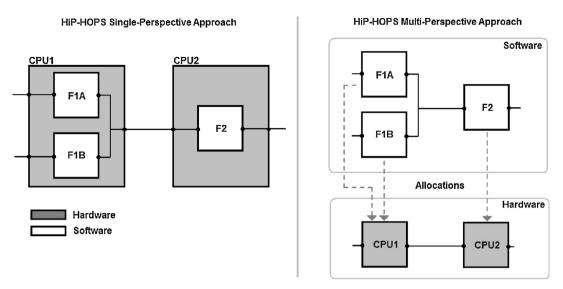

Fig. 4. MARTE task model.

the effect of accessing hardware resources may lead to response times violating deadlines.

To this end we propose an approach that provides a connection to the MAST analysis tool and gives automatic feedback to the EAST-ADL model. As stated in Section 1.1, we need to solve the mismatch between the schedulability analysis level (where the MAST tool works) and the EAST-ADL design level. To this end, we devised a controlled refinement towards a task model that ensures the MAST results provide valuable insight into the EAST-ADL level. It should be noted that this refinement may be embedded in a model transformation that is transparent to the user.

The controlled refinement performs a 1:1 mapping of EAST-ADL functions to MARTE tasks. A task must be configured in terms of periods and priorities; the controlled refinement assigns to a task the period of the function it is mapped to, and all priorities are fixed to the same value. The effect of assigning the same level of priorities for all the tasks (functions) allows for the computing of the upper bound on worst case response times, i.e., any other priority assignment will improve response times. This effect is explained by the way in which response times are computed by MAST when priorities are at the same level.

To clarify this point, consider the example in Fig. 3 again. Applying our controlled refinement to this model means obtaining a MARTE model as shown in Fig. 4. Each function is here represented by a task executing the function itself at the rate of 20 ms, expressed by an external trigger. Priorities and allocations to CPUs are also shown. The deadline of 20 ms for the entire cycle is also specified.

Once the EAST-ADL model is transformed into a MARTE model, MAST can be applied to compute the response time. The response time is obtained by considering worst case execution times and the additional delay caused by sequencing F1A and F1B on CPU1 (for sake of simplicity we do not consider communication delays in the example). In fixed-priority schemes, the additional delay due to sequencing executions is called pre-emption time. Remember that under ordinary circumstances, the highest priority task will access the CPU first and lower priority tasks will access after higher priority tasks terminate their execution. The time spent by a task waiting for higher priority tasks to execute is the pre-emption time. The global pre-emption time is the sum of all pre-emption times for all tasks. Obviously, to improve response time, the global pre-emption time should be minimised.<sup>2</sup> But what happens if priorities are set to the same level, as in our case? MAST in this case considers that each task is pre-empted by all other tasks. In case of Fig. 4 the global pre-emption time on CPU1 will be *sum*(*C*1, *C*2). Any other assignment considering different levels of priority will give a lower value for the global pre-emption time on CPU1 (C1 or C2).

The global pre-emption time could be decreased by reducing the number of tasks. In the example, an alternative mapping with the two functions on a single task would mean reducing the preemption time on CPU1 to 0, as only one task runs in CPU1. Indeed, the 1:1 mapping is another source of pessimism that gives us the worst response time, independent of improvements that can be achieved later by applying smarter refinements towards alternative task models.

Once it has been established that the response time can only be improved by subsequent refinements, it can be correctly interpreted in EAST-ADL as a sufficient condition. A response time that meets deadlines at the task level implies that the EAST-ADL architecture can be considered valid. On the other hand, a negative result does not necessarily imply a design error for schedulability. Experience suggests that this does not present a problem if the designer is aware of this characteristic. Furthermore, a complementary and less conservative analysis could be made where a perfect priority assignment is assumed. This would serve to assess feasibility of the architecture.

The response time computed with MAST under the proposed controlled refinement allows us to compare different architectures from a timing point of view, enabling architecture optimisation as described in Section 4.

### 3. Optimisation of EAST-ADL architectures

Model-based systems analysis techniques allow a great deal of information to be obtained about a system, including its dependability and timing characteristics, amongst others. This is especially true when these analysis techniques are combined with ADLs like EAST-ADL, which serve to centralise all the knowledge about a particular system, since it is no longer necessary to produce a specific error model tailored for a particular dependability analysis tool, or a separate timing model solely for timing analysis etc.

However, as mentioned earlier, this wealth of information can also be difficult to manage. Achieving a balance between the different attribute requirements during the development of complex systems becomes problematic, both because there is a vast number of possible design alterations that could be made and because the interrelationships between the attributes—and therefore the effects of any alterations—are not necessarily clear. This is particularly true when tradeoffs between multiple conflicting attributes (like safety versus cost, or energy consumption versus performance) are involved, as improving one attribute may lead to a worsening of another.

The increasing automation of analysis techniques helps overcome this to an extent, assuming the automated tools are compatible with the model in question. Such tools allow models to be rapidly evaluated according to different criteria, enabling designers to quickly see the effects of any changes to the design architecture and informing design decisions as part of an iterative process.

<sup>&</sup>lt;sup>2</sup> It should be noted that the worst case, in which all the tasks are activated at the same time, is assumed by the analysis, so that the pre-emption time is always included in the response time.

Even with this automation, evolving the design manually is still a complex and time-consuming process, relying on manual experimentation with different design options, and may still be difficult to fulfil the competing requirements on the system—particularly as the time and effort involved means that typically only a small number of potential design options can be investigated in this way.

In such situations, automatic architectural optimisation can potentially be applied. Automatic optimisation allows a much more efficient search of the design space (the total set of possible design variations), covering a much greater number of alternatives than could be considered manually. However, to be effective, the optimisation must be guided in some way, which requires some form of heuristic evaluation. It is here that the use of ADLs such as EAST-ADL for representing the design model pays dividends, because such a model contains all of the information necessary for analysis to take place with respect to each system attribute being considered. For example, if the objectives of the optimisation were to maximise safety and performance while minimising cost and unavailability, it has to be possible to evaluate each of the candidate designs being explored according to those four characteristics by means of some form of analysis. By making changes to the design model automatically as part of the optimisation process and allowing the analysis tools to access the same common model, it then becomes possible to evaluate the new variant directly and seamlessly, facilitating a rapid, efficient search of the design space.

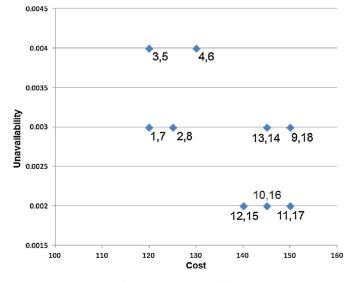

## 3.1. Multi-objective optimisation

Taken together, the problem of optimising a large potential design space to obtain one or more good solutions that feature a desirable balance of attributes is known as a *multi-objective optimisation problem*. There are a variety of different automated algorithms that can be employed to solve such problems, but in general they all aim to quickly find viable solutions (i.e., valid design variants in this case) that offer optimial or near-optimal attributes without needing to investigate all possible designs. It should be noted that in a multi-objective optimisation problem, there is not typically a single optimum solution, because the different objectives may be mutually exclusive; instead, the goal is often to produce a set of 'optimal' solutions that feature a range of attributes that balance the different tradeoff between the objectives whilst still meeting any constraints.

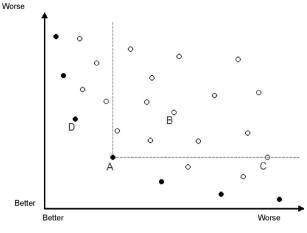

These are known as the *Pareto solutions* and are based on the concept of *dominance*. A dominant solution is one that is better in at least one objective than every other solution yet found, and no worse in the other objectives. The set of dominant solutions is known as the *Pareto set*. When plotted on the graph, they tend to form a curve known as the *Pareto frontier*, which shows the current progress of the optimisation; new solutions beyond the Pareto frontier are new optimal solutions and will dominate older solutions, whereas solutions within the frontier are dominated and non-optimal. This is shown in Fig. 5, where the Pareto frontier consists of the solutions marked as black dots, whilst dominated solutions are white dots.

In Fig. 5, solutions are shown as dots plotted against two axes, each representing different objective attributes (e.g. unavailability and cost). In this case, the goal is to minimise each attribute, so lower values are better. Thus A dominates B because it has lower values for each attribute; it is better in both respects. A also dominates C, because although they have the same value for one objective (e.g. unavailability), A has a lower value for the other (e.g. it is cheaper). Conversely D is a non-dominated solution because it is better than A in one objective but worse in another; for example, D may be cheap but not very reliable, whereas A is more reliable but also more expensive—both are equally valid solutions.

Fig. 5. Pareto frontier.

Although there are many different multi-objective optimisation algorithms, e.g. tabu search (Kulturel-Konak et al., 2003), ant colonies (Liang and Smith, 2004), and simulated annealing (Kim et al., 2004), one of the most prominent approaches is the use of genetic algorithms. The general principles will be briefly discussed next.

## 3.1.1. Genetic algorithms (GAs)

Genetic algorithms are optimisation algorithms inspired by the evolutionary processes found in nature. They have been identified as a particularly effective method for solving combinatorial optimisation problems (such as those discussed here) and they are capable of navigating large, complex search spaces (Coit and Smith, 1996a). The general process is as follows:

- A *population* (set) of individual candidate solutions is randomly generated. Each individual is represented by a different *encoding*, analogous to human genes, which encapsulates the way they can vary from each other. The encoding can be thought of as the 'DNA' of each individual.

- Genetic operators—crossover and mutation—are applied to the population to obtain a new generation of child solutions, which are added to the population (or, in some genetic algorithms, become the sole new population). Crossover involves mixing the genes of two random parent candidates to produce a child; mutation involves randomly changing the genes of a candidate to produce a new solution (or alter an existing candidate).

- This process of reproduction continues until the population grows too large, at which point those with the least successful genomes are discarded. This is established by evaluating the solutions in the population according to the objective criteria (the evaluation functions are known as *fitness functions*) and retaining those with the best results—in other words, survival of the fittest.

- After a set number of generations, the optimisation ceases, and the current population should contain the best (i.e., optimal) solutions discovered so far.

The nature of the problem domain and context has a large influence on the nature of the genetic algorithm, and consequently there are many versions of genetic algorithms, each of which can be customised further by means of different parameters. Generally, however, they all share the same major features: a population of individuals represented by some form of encoding, crossover and mutation operators to produce new individuals, and some kind of fitness function to evaluate the individuals. Encodings, which identify the characteristics of the individual solutions, can take many different forms. One of the simplest is to use a string of integers: each position of the string represents a different characteristic, and the value at that position determines the nature of the characteristic for that individual. For example, a simple system of three components connected in series could be represented by a string of three integers, and the value of each integer indicates the version or manufacturer of each of the three components. While simple, this type of encoding is also quite limited, so other forms of encoding are possible, such as hierarchical (i.e., tree-based) encodings which mimic the hierarchical structure of the system architecture.

GAs also differ in how they handle multiple objectives (assuming they do at all). One common approach is to combine the different evaluations into a single value by applying a weighting to each objective—in effect, converting a multiple-objective problem into a single-objective problem. So for example, if the objectives were safety, performance, and cost, each would be normalised and weighted—e.g.  $0.4 \times$  safety,  $0.3 \times$  performance,  $0.3 \times$  (inverse of cost)—and the result of the formula used as the fitness for that individual. However, this is not always desirable (since it can hide useful tradeoffs) and the fitness weightings can be very difficult to derive.

Another approach is the penalty-based GA approach. In this approach, one objective is treated as the main objective and minimised (or maximised)-e.g. cost-and other objectives are treated as scaled, weighted constraints and applied as a penalty to the main objective. For example, a maximum unavailability limit might be set, and the more the design candidate exceeds the limit, the more harshly the fitness is penalised. Thus even if two solutions both achieve the same cost, the one that does not violate any constraints-or which violates them by the smallest degree-is preferred by the algorithm. However, because successful exploration of the design space often requires infeasible solutions (i.e., those that break the constraints) to be explored too, a dynamic penalty function can be employed that varies the penalty according to the length of the optimisation run so far (e.g. applying light penalties early in the process, to encourage more exploration, and gradually making them heavier as time goes on). This form of dynamic penalty-based GA has been found to have superior performance compared to either static versions or versions that only allow feasible solutions to be part of the population (Coit and Smith, 1996b).

There are also true multi-objective approaches that evaluate against multiple objectives at once and maintain a Pareto front of optimal, non-dominated solutions. This allows a broader set of solutions and generally results in a better coverage of the search space (Salazar et al., 2006), albeit at the cost of higher complexity. These types of algorithms are generally better suited to multi-objective problems because they allow the various tradeoffs between the objectives to be better represented, rather than being biased towards one objective and using the others as constraints or weighted penalties etc. There are many different multi-objective GAs, including:

- PESA-II (Pareto Envelope-based Selection Algorithm 2) (Corne et al., 2001), which seeks to maximise evenly distributed spread in the Pareto set by including crowding in the selection criteria; solutions that are found in less crowded regions of the search space are preferred for selection to encourage the algorithm to look at under-explored areas of the search space.

- SPEA-II (Strength Pareto Evolutionary Algorithm 2) (Zitzler et al., 2001). Unlike PESA-II, which adopts a "pure elitist" strategy that allows no dominated solutions to be retained, SPEA-II does keep some dominated solutions. The selection criteria are altered to include a dominance strength (how many solutions it dominates) and a density value (how close an individual is to other solutions).

Thus although dominated, crowded solutions are possible, non-dominated, non-crowded solutions are preferred.

NSGA-II (Non-Dominated Sorting Genetic Algorithm 2) (Deb et al., 2002). In NSGA-II, both non-dominated and dominated solutions are kept in the same population, ranked according to dominance (based on how many other solutions they dominate). More dominating solutions are preferred during selection, and crowding is used as a tie-breaker if two solutions have equal dominance.

## 3.1.2. Chosen algorithm

After comparing the three algorithms above, the algorithm chosen for use in the ATESST2 and MAENAD projects for the automatic optimisation of EAST-ADL models is a variant of the NSGA-II genetic algorithm, which was deemed to have a good balance of characteristics. NSGA-II is also used as the basis of the PerOpteryx optimisation engine (Koziolek et al., 2011) and is also used in AQOSA (Etemaadi and Chaudron, 2012). NSGA-II offers reasonably good performance, wide coverage of the design space, and (most importantly) excellent support for multiple objectives (Parker, 2010). The algorithm is not guaranteed to find all Pareto optimal solutions (though nor are any of the other algorithms, genetic or otherwise), but it should still produce a set of superior solutions much faster and more efficiently than could be performed manually.

The encoding used is a form of hierarchical, tree-based encoding, where each tree node represents a different variability point for one or more functions or components in the system architecture. If an optional function is present and also has a choice of subfunctions (or subcomponents), then the node will have corresponding child nodes beneath it which can also be varied.

The different values of the encoding represent all possible variations of the system architecture-in effect, the encoding encapsulates the entire design space. It is defined in EAST-ADL by means of the variability management mechanism, allowing more complex configurations of features to be represented, including dependencies between features (possibly hierarchical) and duplication of features. Variability is therefore used to represent the possible options for architectural variation of the design by defining the variation points of the design space; this notion of optimisation space corresponds exactly to what is called a configuration space in feature modelling terminology. Thus for example a critical component can be defined with several implementations or perhaps an alternative replicated subsystem specified (which provides additional redundancy, but increases cost); the optimisation algorithm can then choose one of these options and evaluate the effects of that option on the overall attributes of the system.

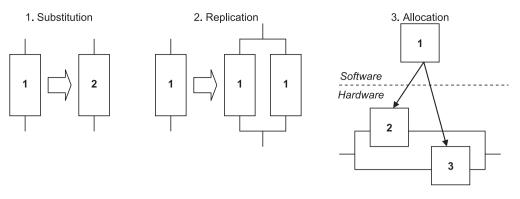

Optimisation variants can be defined in one of three main ways:

- 1. *Substitution*: A component/function (or subsystem) is substituted for another that has different objective attributes (e.g. safety, cost, performance). A substitute must be functionally equivalent, i.e., it must perform the same task and have a compatible interface, but need not achieve the task in the same way or make use of all connections (e.g. an electronic braking subsystem may be replaced by a hydraulic version). Different substitutes are often termed as different *implementations* of a function or component.

- 2. *Replication*: To improve reliability, a critical component or model element may be duplicated to achieve redundancy. Replicants are usually connected in parallel to ensure that a failure of one element does not lead to a failure of the whole subsystem. Note that the replicants have to be defined in advance as optional elements; the optimisation does not generate them itself.

Fig. 6. Different variation strategies.

3. Allocation: In systems with both hardware and software elements, there may be a choice of allocation strategy, e.g. in terms of which software function is allocated to be executed on which hardware platform. This allows timing performance as well as reliability to be balanced over the available processing resources of the system.

These different variations are illustrated in Fig. 6. Furthermore, more complex optimisation is possible via a combination of two or more of the above, e.g. replication that uses more than one implementation.

During the optimisation process, different variants can then be chosen from amongst the predefined choices, and the variability mechanisms ensure that the connections between the chosen components are kept consistent. This enables relatively seamless connections between different choices of functions/components in the model and ensures that e.g. failures are propagated correctly through the system model.

This variability-based approach is very flexible and allows complex compositional variants to be modelled; for example, a single component may be substituted for another component from a different manufacturer, or replaced by a replicated subsystem with heterogeneous subcomponents. This allows more sophisticated design patterns (such as voters and monitors etc.) to be evaluated as part of the optimisation; furthermore, such configurations can often be stored in a library and reused in other models.

## 3.2. EAST-ADL optimisation tool architecture

This section describes the EAST-ADL optimisation tool architecture as currently being developed in the MAENAD project. The tool architecture is designed to meld all of the various analysis and optimisation tools required, using the EAST-ADL system model as the glue. A prototype optimisation environment has been developed based on the EPM tool (based on the Eclipse framework), which currently implements a core subset of EAST-ADL (Abele et al., 2012). There are three main goals to be fulfilled by the tool architecture:

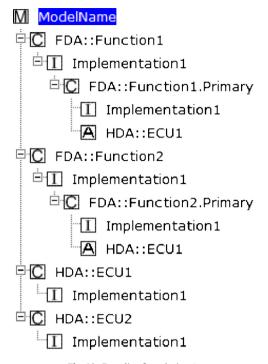

- Design space definition: In order for optimisation to take place, it must be possible to define the design space by means of specifying variability points in the model that the optimisation can later choose and evaluate. This is primarily achieved through the use of EAST-ADL's variability management mechanism, which allows alternative implementations and allocations to be specified. In the tool architecture, this role is fulfilled by the EPM tool.

- Rapid objective evaluation: For optimisation to be guided rather than random, it must be possible to evaluate new solutions to determine whether they are better or worse than previous solutions. In a multi-objective problem, this means analysing the solutions (in the form of design candidates) for each of the

objectives being evaluated. In this case, HiP-HOPS is the primary tool to evaluate safety and reliability characteristics, cost (currently only a simplistic summation) is handled by a dedicated plugin, and timing analysis capabilities are provided by the MAST tool. Other plugins can be added as needed to evaluate other objectives.

• Efficient design space exploration: Finally, optimisation requires that the design space be explored by means of an algorithm. In this case, a variant on the NSGA-II genetic algorithm is used, based on prototype optimisation technology in HiP-HOPS but implemented as an EPM plugin instead. In combination with the design space definition and analysis capabilities, it allows automatic optimisation of an EAST-ADL architecture.

An additional crucial step is variability resolution. In order for a design variant to be analysed and evaluated, the variability first has to be 'resolved', i.e., to produce a model in which all of the variability points have been selected or deselected to produce a particular system configuration with a concrete set of objective attributes.

There are still certain issues and constraints to be dealt with. For example, EAST-ADL does not require a one-to-one mapping between its nominal and error model architectures, i.e., it does not ordinarily require that each function has a corresponding error model type; however, for the error model to be evaluated correctly when the nominal architecture changes, the optimisation requires a one-to-one mapping to be applied. This is resolved by explicitly defining the ErrorModel for each nominal model variant. Furthermore, it is very important that the optimisation variability ensures substitutability, i.e., that if the optimisation algorithm selects a different option, the resulting system design remains valid and sensible. This imposes two requirements on the variants: that they share a compatible interface (i.e., they share at least a common subset of ports and connections) and that they perform equivalent functions. Otherwise, the optimisation algorithm may select a different option that leads to an invalid or nonsensical system design. This is not necessarily a simple problem, especially in an ADL such as EAST-ADL, where the error model, software, and hardware may all be represented in separate model views and a change in one may need to be reflected in the others. At the same time, this is a criterion for validity of the model regardless of context: it is not only optimisation which requires that a valid timing model (or error model or any other model) must emerge together with the core architecture as a result of changes to the variability; this is a general issue in any variability resolution process.

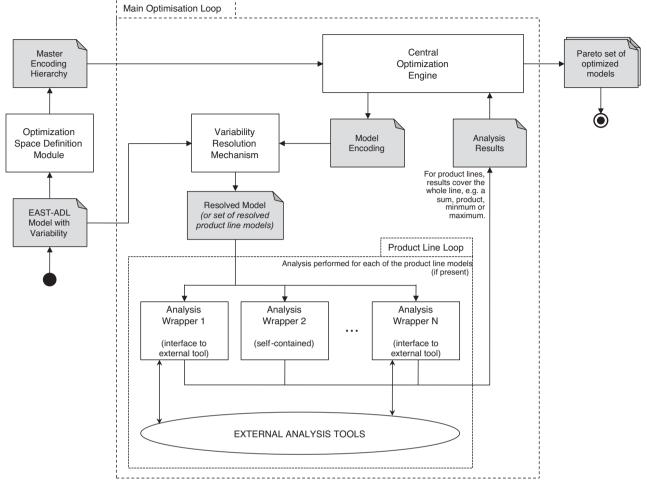

The tool architecture itself is shown in Fig. 7. This diagram shows the flow of operations in the optimisation process. The initial EAST-ADL model (with variability) is passed to the Optimisation Space Definition Module (or OSDM), which generates a Master Encoding Hierarchy. This defines the search space for the Central Optimisation Engine, which generates different model encodings that are

Fig. 7. EAST-ADL optimisation tool architecture.

passed to the Variability Resolution Mechanism to be resolved into analysable models. The analysis wrappers then evaluate these models according to different objectives and return the results. Eventually the optimisation settles on a set of Pareto optimal solutions, which constitute the final results of the process. There is also a further planned process involving product line optimisation (see Section 3.2.5), although this is not included in the current prototype.

The major elements of the architecture will be described next.

## 3.2.1. Optimisation Space Definition Module (OSDM)

The OSDM provides the input for the overall optimisation process by taking the original "variant-rich" EAST-ADL model, which contains variability elements to define the variation points of the design, and derives from this input the set of possible encodings of the optimisation search space-the Master Encoding Hierarchy. This is a structure that can be manipulated to obtain the set of all valid design candidates. The Master Encoding Hierarchy allows the Central Optimisation Engine to explore the design space automatically by using an abstract structure without the need for semantic knowledge of the EAST-ADL design model itself. This is "abstract" in the sense that it does not include any information on the structure, behaviour or other properties of the individual candidates; it just provides a means to unambiguously identify each candidate. It takes the form of a tree-based hierarchical structure (based on a normal variability feature model) in which each node defines an individual variability and the nature of the node describes the type of variability. In EAST-ADL, the core technical feature model

on vehicle level provides such an abstract view of the complete system's variability, as detailed in Section 2.2, and can therefore be used as is for this purpose.

The OSDM is therefore necessary to ensure that the optimisation engine itself does not need to know anything about the semantics of the models it deals with other than what variability is present in the original model and how it can be encoded. It is then the job of the VRM to convert a particular encoding—i.e., a particular configuration of the variability in the model—into a new model in which all the variability is resolved. This can then be analysed by the external tools, and the optimisation engine then determines whether to keep or discard that particular design candidate on the basis of those analysis results.

Unlike the other elements, which are used in each optimisation iteration, the OSDM is only required once, at the beginning of the optimisation, not iteratively in each optimisation cycle as with the other elements.

#### 3.2.2. Central Optimisation Engine (COE)

The Central Optimisation Engine is the driver of the optimisation process, responsible for exploring the design space (by choosing which encodings to evaluate) and for collecting the best solutions so far. The COE will use genetic algorithms based on established HiP-HOPS technology (Papadopoulos et al., 2011), but is implemented as a separate plugin to facilitate easier communication with the other elements of the tool architecture.

When optimisation is initiated, the optimisation engine receives three things: a set of optimisation parameters (such as the number of generations to run for, the size of the solution population to maintain, and a specification of which objectives are to be evaluated), the original variant-rich EAST-ADL model, and the Master Encoding Hierarchy from the OSDM-a tree containing the different variation points in the model. This is essentially the base DNA of the model to be optimised. To perform optimisation, the optimisation engine chooses a particular encoding by selecting which variation points to use and which not to use according to its internal heuristics, e.g. via crossover and mutation operators (called "model encoding" in Fig. 7). This encoding is then passed on to the VRM. The VRM returns a version of the original model with the variability resolved, which is then passed to the plugin interfaces to the various analysis engines (timing, safety, cost etc.), according to the optimisation objectives. Once complete, the analysis results are returned so the optimisation algorithm can evaluate them against its objectives and then repeat the cycle.

Since EAST-ADL's core technical feature model on vehicle level is used as the master encoding hierarchy in the prototype, an ordinary feature configuration of this feature model, i.e., a selection and deselection of its features, can be used to represent a model encoding.

As mentioned above, the optimisation engine also requires the optimisation parameters, which specify the goals of the process and the objectives to evaluate. So for example, an optimisation may be initiated to minimise cost, maximise reliability, maximise processing slack, and minimise response times; alternatively, we may only be interested in minimising cost and maximising safety. Constraints can also be provided (e.g. minimum safety requirements, maximum cost etc.), although the optimisation engine will not necessarily treat these as hard limits during the optimisation process itself.

#### 3.2.3. Variability Resolution Mechanism (VRM)

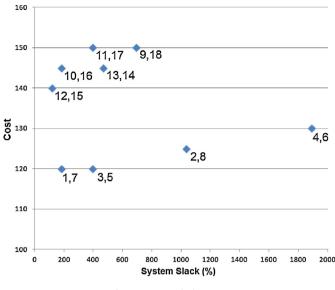

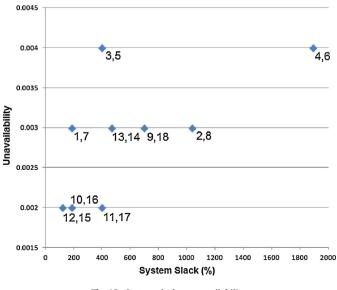

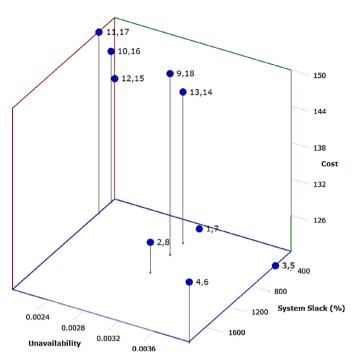

The Variability Resolution Mechanism (VRM) is responsible for taking the original, variant-rich EAST-ADL model and producing a new model, with all variability resolved, according to the encoding received from the optimisation engine. The basis for this step is an EAST-ADL model with variability defined. For this purpose, standard EAST-ADL variability modelling techniques, as described in Section 2.2, can be employed.