# TOWARDS SCALABLE OLTP OVER FAST NETWORKS

Tobias Ziegler

### TOWARDS SCALABLE OLTP OVER FAST NETWORKS

Doctoral thesis by Tobias Ziegler, M.Sc.

submitted in fulfillment of the requirements for the degree of *Doctor rerum naturalium (Dr. rer. nat.)*

Reviewers

Prof. Dr. rer. nat. Carsten Binnig Prof. Spyros Blanas, Ph.D.

Department of Computer Science Technical University of Darmstadt

Darmstadt, 2023

Tobias Ziegler: Towards Scalable OLTP Over Fast Networks

Darmstadt, Technical University of Darmstadt

Year thesis published in TUprints: 2023 URN: urn:nbn:de:tuda-tuprints-247162

URL: https://tuprints.ulb.tu-darmstadt.de/24716

Date of the viva voce: 22.08.2023

Urheberrechtlich geschützt / In copyright

https://rightsstatements.org/page/InC/1.0/

# Erklärung laut Promotionsordnung

### §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

### §8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

### §9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

### §9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

| Darmstadt, June 27, 2023 |  |

|--------------------------|--|

|                          |  |

|                          |  |

| Tobias Ziegler           |  |

### **Abstract**

Online Transaction Processing (OLTP) underpins real-time data processing in many mission-critical applications, from banking to e-commerce. These applications typically issue short-duration, latency-sensitive transactions that demand immediate processing [72]. High-volume applications, such as Alibaba's e-commerce platform [87], achieve peak transaction rates as high as 70 million transactions per second, exceeding the capacity of a single machine. Instead, distributed OLTP database management systems (DBMS) are deployed across multiple powerful machines. Historically, such distributed OLTP DBMSs have been primarily designed to avoid network communication, a paradigm largely unchanged since the 1980s.

However, fast networks challenge the conventional belief that network communication is the main bottleneck. In particular, emerging network technologies, like Remote Direct Memory Access (RDMA), radically alter how data can be accessed over a network. RDMA's primitives allow direct access to the memory of a remote machine within an order of magnitude of local memory access [20]. This development invalidates the notion that network communication is the primary bottleneck. Given that traditional distributed database systems have been designed with the premise that the network is slow, they cannot efficiently exploit these fast network primitives, which requires us to reconsider how we design distributed OLTP systems.

This thesis focuses on the challenges RDMA presents and its implications on the design of distributed OLTP systems. First, we examine distributed architectures to understand data access patterns and scalability in modern OLTP systems. Drawing on these insights, we advocate a distributed storage engine optimized for high-speed networks. The storage engine serves as the foundation of a database, ensuring efficient data access through three central components: indexes, synchronization primitives, and buffer management (caching). With the introduction of RDMA, the landscape of data access has undergone a significant transformation. This requires a comprehensive redesign of the storage engine components to exploit the potential of RDMA and similar high-speed network technologies. Thus, as the second contribution, we design RDMA-optimized tree-based indexes especially applicable for disaggregated databases to access remote data efficiently. We then turn our attention to the unique challenges of RDMA. One-sided RDMA, one of the network primitives introduced by RDMA, presents a performance advantage in enabling remote memory access while bypassing the remote CPU and the operating system. This allows the remote CPU to process transactions uninterrupted, with no requirement to be on hand for network communication. However, that way, specialized one-sided

RDMA synchronization primitives are required since traditional CPU-driven primitives are bypassed. We found that existing RDMA one-sided synchronization schemes are unscalable or, even worse, fail to synchronize correctly, leading to hard-to-detect data corruption. As our third contribution, we address this issue by offering guidelines to build scalable and correct one-sided RDMA synchronization primitives. Finally, recognizing that maintaining all data in memory becomes economically unattractive, we propose a distributed buffer manager design that efficiently utilizes cost-effective NVMe flash storage. By leveraging low-latency RDMA messages, our buffer manager provides a transparent memory abstraction, accessing the aggregated DRAM and NVMe storage across nodes. Central to our approach is a distributed caching protocol that dynamically caches data. With this approach, our system can outperform RDMA-enabled in-memory distributed databases while managing larger-than-memory datasets efficiently.

# Zusammenfassung

Die Bedeutung von Online-Transaktionsverarbeitung (OLTP) im Echtzeitbetrieb, beispielsweise in der Banken- und E-Commerce-Branche, ist immens. Anwendungen mit sehr hohem Datenaufkommen, wie beispielsweise Alibabas Onlinehandel, die bis zu 70 Millionen Transaktionen pro Sekunde aufweisen [87], übersteigen die Kapazitäten eines Einzelrechners. Um diese hohen Datendurchsätze bewältigen zu können, wird ein für das OLTP-Datenbankmanagementsystem (DBMS) verteilter Ansatz, welcher auf einer Vielzahl von Rechnern läuft, unerlässlich. Historisch gesehen wurde die Entwicklung solcher verteilter OLTP-Datenbanken vor allem mit dem Ziel vorangetrieben, die Netzwerkkommunikation zu reduzieren - eine Herangehensweise, die seit den 1980er-Jahren weitgehend konstant geblieben ist. Mit dem Aufkommen schneller Netzwerke wird jedoch eben diese Ansicht, dass die Netzwerkkommunikation der größte Engpass ist in Frage gestellt. Insbesondere neuartige Netzwerktechnologien wie Remote Direct Memory Access (RDMA) revolutionieren die Methode des Datenzugriffs über Netzwerke. Sie bieten Netzwerkprimitive, die einen direkten und schnellen Zugriff auf entfernten Arbeitsspeicher über das Netzwerk ermöglichen. Allerdings sind die für langsame Netzwerke konzipierten verteilten Datenbanksysteme nicht in der Lage, die Vorteile dieser Netzwerkprimitive vollständig zu nutzen. Diese Arbeit fokussiert sich auf die mit RDMA verbundenen Herausforderungen und die dadurch bedingten Auswirkungen auf die Gestaltung von verteilten OLTP-Systemen. Wir untersuchen zunächst verteilte Architekturen, um das Verständnis von Datenzugriffsmustern und Skalierbarkeit in modernen OLTP-Systemen zu vertiefen. Basierend auf diesen Erkenntnissen schlagen wir eine Speicher-Engine vor, die speziell für ein skalierbares, verteiltes OLTP-System optimiert ist.

Die Speicher-Engine, eine Kernkomponente jeder Datenbank, hat drei Hauptfunktionen: Bereitstellung von Indizes, Synchronisationsmechanismen und Puffermanagement (Caching). Angesichts der neuen Netzwerkprimitive, die RDMA zur Manipulation und zum Lesen von Daten über das Netzwerk bereitstellt, wird eine Überarbeitung dieser drei Kernfunktionen notwendig. Daher schlagen wir in unserem zweiten Beitrag die Entwicklung von baumstrukturierten Indizes vor, die speziell für den Einsatz mit RDMA und insbesondere für disaggregierte Datenbanken optimiert sind. Dies ermöglicht das effiziente Speichern, Finden und Zugreifen auf entfernte Daten über das Netzwerk. Ein entscheidender Vorteil von One-Sided RDMA (eine der neuen Netzwerkprimitive von RDMA) besteht darin, dass Daten über das Netzwerk manipuliert werden können, ohne dass die entfernte CPU involviert wird. Dies ermöglicht es der entfernten CPU, weiterhin Transaktionen zu bearbeiten, ohne dass sie für die Netzwerkkommunikation zur Verfügung stehen muss.

Allerdings erfordert dieser Ansatz spezielle Synchronisationsmechanismen, die mit Hilfe von One-Sided RDMA Primitiven implementiert werden. Unsere Untersuchungen haben ergeben, dass bestehende One-Sided RDMA-Synchronisationsprimitiven entweder nicht skaliert werden können oder fehlerhaft synchronisieren, was zu Datenbeschädigungen führen kann. Um dieses Problem zu lösen, schlagen wir Richtlinien vor, die zur korrekten und skalierbaren Gestaltung dieser One-Sided RDMA-Synchronisationsprimitiven beitragen. Da die Speicherung aller Daten im Arbeitsspeicher aus Kostengründen nicht mehr praktikabel ist, schlagen wir als abschließenden Schritt ein Design für einen Puffermanager vor, der den kostengünstigeren NVMe-Flash-Speicher nutzt. Unser Puffermanager nutzt RDMA mit niedriger Latenz und bietet eine transparente Speicherabstraktion, sodass auf den aggregierten DRAM- und NVMe-Speicher über mehrere Server hinweg zugreifen werden kann. Im Gegensatz zu vorherigen verteilten In-Memory RDMA-Designs kann unser Puffermanager Datenmengen bewältigen, die den verfügbaren Arbeitspeicher übersteigen. Im Zentrum unseres Ansatzes befindet sich ein verteiltes Caching-Protokoll, das Daten dynamisch zwischenspeichert. Unser System kann dabei mit RDMA-fähigen verteilten Datenbanken, die ausschließlich im Arbeitsspeicher arbeiten, konkurrieren oder diese sogar übertreffen, während es gleichzeitig größere Datensätze performant und kosteneffizient verwaltet.

### **Publications**

The following peer-reviewed publications are part of this cumulative dissertation. Their content is printed in Part II, Chapters 8 to 13.

- [1] Tobias Ziegler, Sumukha Tumkur Vani, Carsten Binnig, Rodrigo Fonseca, and Tim Kraska. "Designing Distributed Tree-based Index Structures for Fast RDMA-capable Networks." In: 2019 International Conference on Management of Data, SIGMOD Conference 2019, Amsterdam, The Netherlands, June 30 July 5, 2019. Ed. by Peter A. Boncz, Stefan Manegold, Anastasia Ailamaki, Amol Deshpande, and Tim Kraska. ACM, 2019, pp. 741–758. DOI: 10.1145/3299869.3300081. URL: https://doi.org/10.1145/3299869.3300081.

- [2] Tobias Ziegler, Dwarakanandan Bindiganavile Mohan, Viktor Leis, and Carsten Binnig. "EFA: A Viable Alternative to RDMA over InfiniBand for DBMSs?" In: International Conference on Management of Data, DaMoN 2022, Philadelphia, PA, USA, 13 June 2022. Ed. by Spyros Blanas and Norman May. ACM, 2022, 10:1–10:5. DOI: 10.1145/3533737.3538506. URL: https://doi.org/10.1145/3533737.3538506.

- [3] Tobias Ziegler, Carsten Binnig, and Viktor Leis. "ScaleStore: A Fast and Cost-Efficient Storage Engine using DRAM, NVMe, and RDMA." In: SIGMOD '22: International Conference on Management of Data, Philadelphia, PA, USA, June 12 17, 2022. Ed. by Zachary Ives, Angela Bonifati, and Amr El Abbadi. ACM, 2022, pp. 685–699. DOI: 10.1145/3514221.3526187. URL: https://doi.org/10.1145/3514221.3526187.

- [4] Tobias Ziegler, Viktor Leis, and Carsten Binnig. "RDMA Communciation Patterns." In: *Datenbank Spektrum* 20.3 (2020), pp. 199–210. DOI: 10.1007/s13222-020-00355-7. URL: https://doi.org/10.1007/s13222-020-00355-7.

- [5] Tobias Ziegler, Philip A. Bernstein, Viktor Leis, and Carsten Binnig. "Is Scalable OLTP in the Cloud a Solved Problem?" In: 13th Annual Conference on Innovative Data Systems Research, CIDR 2023, Amsterdam, The Netherlands, January 8-11, 2023, Online Proceedings. www.cidrdb.org, 2023. URL: https://www.cidrdb.org/cidr2023/papers/p50-ziegler.pdf.

- [6] Tobias Ziegler, Jacob Nelson-Slivon, Viktor Leis, and Carsten Binnig. "Design Guidelines for Correct, Efficient, and Scalable Synchronization using One-Sided RDMA." In: SIGMOD '23: International Conference on Management of Data, Seattle, WA, USA, June 18 - 23, 2023. ACM, 2023.

Further co-authored peer-reviewed publications are:

- [1] Arnd Christian König, Yi Shan, Tobias Ziegler, Aarati Kakaraparthy, Willis Lang, Justin Moeller, Ajay Kalhan, and Vivek Narasayya. "Tenant Placement in Over-subscribed Database-as-a-Service Clusters." In: *Proc. VLDB Endow.* 15.11 (2022), pp. 2559–2571. URL: https://www.vldb.org/pvldb/vol15/p2559-k%5C%5C%f6nig.pdf.

- [2] Lasse Thostrup, Jan Skrzypczak, Matthias Jasny, Tobias Ziegler, and Carsten Binnig. "DFI: The Data Flow Interface for High-Speed Networks." In: SIGMOD Rec. 51.1 (2022), pp. 15–22. DOI: 10.1145/3542700.3542705. URL: https://doi.org/10.1145/3542700.3542705.

- [3] Muhammad El-Hindi, Tobias Ziegler, Matthias Heinrich, Adrian Lutsch, Zheguang Zhao, and Carsten Binnig. "Benchmarking the Second Generation of Intel SGX Hardware." In: International Conference on Management of Data, DaMoN 2022, Philadelphia, PA, USA, 13 June 2022. Ed. by Spyros Blanas and Norman May. ACM, 2022, 5:1–5:8. DOI: 10.1145/3533737.3535098. URL: https://doi.org/10.1145/3533737.3535098.

- [4] Matthias Jasny, Lasse Thostrup, Tobias Ziegler, and Carsten Binnig. "P4DB The Case for In-Network OLTP." In: SIGMOD '22: International Conference on Management of Data, Philadelphia, PA, USA, June 12 17, 2022. Ed. by Zachary Ives, Angela Bonifati, and Amr El Abbadi. ACM, 2022, pp. 1375–1389. DOI: 10.1145/3514221.3517825. URL: https://doi.org/10.1145/3514221.3517825.

- [5] Matthias Jasny, Lasse Thostrup, Tobias Ziegler, and Carsten Binnig. "P4DB The Case for In-Network OLTP (Extended Technical Report)." In: CoRR (2022). DOI: 10.48550/arXiv.2206.00623. arXiv: 2206.00623. URL: https://doi.org/10.48550/arXiv.2206.00623.

- [6] Lasse Thostrup, Jan Skrzypczak, Matthias Jasny, Tobias Ziegler, and Carsten Binnig. "DFI: The Data Flow Interface for High-Speed Networks." In: SIGMOD '21: International Conference on Management of Data, Virtual Event, China, June 20-25, 2021. Ed. by Guoliang Li, Zhanhuai Li, Stratos Idreos, and Divesh Srivastava. ACM, 2021, pp. 1825–1837. DOI: 10.1145/3448016.3452816. URL: https://doi.org/10.1145/3448016.3452816.

- [7] Benjamin Hilprecht, Carsten Binnig, Tiemo Bang, Muhammad El-Hindi, Benjamin Hättasch, Aditya Khanna, Robin Rehrmann, Uwe Röhm, Andreas Schmidt, Lasse Thostrup, and Tobias Ziegler. "DBMS Fitting: Why should we learn what we already know?" In: 10th Conference on Innovative Data Systems Research, CIDR 2020, Amsterdam, The Netherlands, January 12-15, 2020, Online Proceedings. www.cidrdb.org, 2020. URL: http://cidrdb.org/cidr2020/papers/p34-hilprecht-cidr20.pdf.

- [8] Matthias Jasny, Tobias Ziegler, Tim Kraska, Uwe Röhm, and Carsten Binnig. "DB4ML An In-Memory Database Kernel with Machine Learning Support." In: Proceedings of the 2020 International Conference on Management of Data, SIGMOD Conference 2020, online conference [Portland, OR, USA], June 14-19, 2020. Ed. by David Maier, Rachel Pottinger, AnHai Doan, Wang-Chiew Tan, Abdussalam Alawini, and Hung Q. Ngo. ACM, 2020, pp. 159–173. DOI: 10.1145/3318464.3380575. URL: https://doi.org/10.1145/3318464.3380575.

- [9] Lukas Berg, Tobias Ziegler, Carsten Binnig, and Uwe Röhm. "ProgressiveDB Progressive Data Analytics as a Middleware." In: *Proc. VLDB Endow.* 12.12 (2019), pp. 1814–1817. DOI: 10.14778/3352063.3352073. URL: http://www.vldb.org/pvldb/vol12/p1814-berg.pdf.

- [10] Jaco A. Hofmann, Lasse Thostrup, Tobias Ziegler, Carsten Binnig, and Andreas Koch. "High-Performance In-Network Data Processing." In: 10th International Workshop on Accelerating Analytics and Data Management Systems Using Modern Processor and Storage Architectures, ADMS@VLDB 2019, Los Angeles, California, USA, August 26, 2019. Ed. by Rajesh Bordawekar and Tirthankar Lahiri. 2019, pp. 64–73. URL: http://www.adms-conf.org/2019-camera-ready/hofmann% 50%5C\_adms19.pdf.

- [11] Tobias Ziegler, Carsten Binnig, and Uwe Röhm. "Skew-resilient Query Processing for Fast Networks." In: *NoDMS BTW*. Ed. by Holger Meyer, Norbert Ritter, Andreas Thor, Daniela Nicklas, Andreas Heuer, and Meike Klettke. Vol. P-290. LNI. Gesellschaft für Informatik, Bonn, 2019, pp. 81–85. DOI: 10.18420/btw2019-ws-06. URL: https://doi.org/10.18420/btw2019-ws-06.

- [12] Gustavo Alonso, Carsten Binnig, Ippokratis Pandis, Kenneth Salem, Jan Skrzypczak, Ryan Stutsman, Lasse Thostrup, Tianzheng Wang, Zeke Wang, and Tobias Ziegler. "DPI: The Data Processing Interface for Modern Networks." In: 9th Biennial Conference on Innovative Data Systems Research, CIDR 2019, Asilomar, CA, USA,

- January 13-16, 2019, Online Proceedings. www.cidrdb.org, 2019. URL: http://cidrdb.org/cidr2019/papers/p11-alonso-cidr19.pdf.

- [13] Marcel Blöcher, Tobias Ziegler, Carsten Binnig, and Patrick Eugster. "Boosting scalable data analytics with modern programmable networks." In: *Proceedings of the 14th International Workshop on Data Management on New Hardware, Houston, TX, USA, June 11, 2018.* Ed. by Wolfgang Lehner and Kenneth Salem. ACM, 2018, 1:1–1:3. DOI: 10.1145/3211922.3211923. URL: https://doi.org/10.1145/3211922.3211923.

Due to the nature of the synopsis and for better readability, selected paragraphs from these publications were transferred verbatim throughout the synopsis without explicit labeling as suggested in the department regulations Kumulative Dissertation und Eigenzitate in Dissertationen (21.09.2021) §1.

## Acknowledgments

First and foremost, I would like to express my deepest gratitude to Prof. Dr. Carsten Binnig for his support and guidance throughout my doctoral journey. His incredible mentorship has consistently pushed me to grow both personally and academically. No matter the topic, whether it be academic or personal, his door has always been open for me. He also got me into research in the first place by inspiring me with his wisdom, technical knowledge, and visions. Without him, I would have never pursued my Ph.D. I am truly fortunate to have had him as my advisor all these years.

The same can be said for Prof. Dr. Viktor Leis, whose mentorship was incredibly valuable throughout my journey. He always provided insightful ideas, participated in brainstorming sessions and answered the many questions I had regarding building databases, some of which I sent in the middle of the night. He gave me additional tools to be a better researcher, engineer, and writer. I couldn't have asked for a better team to guide me than Carsten and Viktor.

I also sincerely thank Prof. Spyros Blanas for his valuable time and effort in reviewing this dissertation.

I am deeply grateful to my colleagues at the Systems Group at TU Darmstadt for making the past years enjoyable and productive. The supportive atmosphere, the exchange of ideas, the feedback on my work, and the engaging discussions have always been fun and (often) productive. I thank every one of you. In particular, thanks to the best office buddies I could have wished for: Muhammad, Matthias, Lasse, and Nils. Special thanks go to Mona. Her attention to detail ensured that I always met the administrative deadlines I tended to push away while focusing on research.

I am fortunate to have collaborated with exceptional individuals on various projects. Working with them has been a privilege, and their expertise and guidance have significantly contributed to my academic growth. In particular, I express my gratitude to Philip A. Bernstein, who is one of the greatest database researchers, for his willingness to share his expertise has been invaluable.

I am deeply grateful to my parents for their unwavering support and encouragement during my life. Lastly, I would like to express my appreciation to Maren. She made me laugh during challenging times and celebrated my achievements with me. Her encouragement has made this journey way easier. I am truly thankful to all the individuals who have played a part, directly or indirectly, in my academic and personal development.

# **Contents**

| I | Sy                          |         | 1                                            |    |  |  |

|---|-----------------------------|---------|----------------------------------------------|----|--|--|

| 1 | Intr                        | oductio | vn                                           | 3  |  |  |

|   | 1.1                         | Tradit  | ional Distributed Database Design            | 3  |  |  |

|   | 1.2                         | Fast N  | Networks                                     | 4  |  |  |

|   | 1.3                         | State   | of the Art                                   | 7  |  |  |

|   | 1.4                         | Storag  | ge Engine: The Missing Component             | 8  |  |  |

|   | 1.5                         | Contri  | ibutions                                     | 12 |  |  |

|   | 1.6                         | Outlin  | ne                                           | 14 |  |  |

| 2 | RDI                         | MA Pri  | mer                                          | 15 |  |  |

|   | 2.1                         | Capab   | oilities                                     | 15 |  |  |

|   | 2.2                         | Primit  | tives                                        | 15 |  |  |

|   |                             | 2.2.1   | One-Sided Verbs                              | 16 |  |  |

|   |                             | 2.2.2   | Two-Sided Verbs                              | 17 |  |  |

| 3 | Scalable OLTP Architectures |         |                                              |    |  |  |

|   | 3.1                         | Towar   | ds Scalable Online Transaction Processing    | 19 |  |  |

|   |                             | 3.1.1   | Revisiting the Old Taxonomy                  | 20 |  |  |

|   |                             | 3.1.2   | A New Taxonomy Based on the Data Access Path | 21 |  |  |

|   |                             | 3.1.3   | Data Access Archetypes                       | 23 |  |  |

|   |                             | 3.1.4   | Key Findings: A Road Towards Scalable OLTP   | 28 |  |  |

|   | 3.2                         | Fast N  | Networks in the Cloud                        | 28 |  |  |

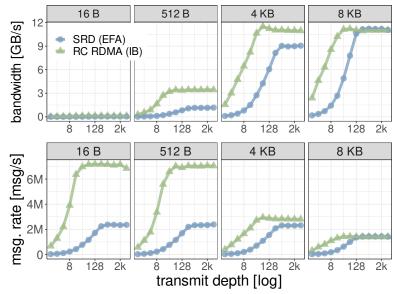

|   |                             | 3.2.1   | A Detailed Comparison of EFA and RDMA        | 29 |  |  |

|   |                             | 3.2.2   | Benchmarking EFA and RDMA                    | 32 |  |  |

|   |                             | 3.2.3   | Key Findings: RDMA Is Faster                 | 34 |  |  |

|   | 3.3                         | Summ    | ary                                          | 35 |  |  |

| 4 | RDI                         | MA-Ena  | abled Tree-Based Index Structures            | 37 |  |  |

|   | 4.1                         | The N   | Teed for Tree-Based Indexes                  | 37 |  |  |

|   | 4.2  | Mapping the Design Space                          | 8 |

|---|------|---------------------------------------------------|---|

|   | 4.3  | Design 1: Coarse-Grained/Two-Sided                | 1 |

|   |      | 4.3.1 Index Structure                             | 1 |

|   |      | 4.3.2 RDMA-Based Accesses                         | 2 |

|   | 4.4  | Design 2: Fine-Grained/One-Sided                  | 3 |

|   |      | 4.4.1 Index Structure                             | 3 |

|   |      | 4.4.2 RDMA-Based Accesses                         | 3 |

|   | 4.5  | Design 3: Hybrid Scheme                           | 6 |

|   |      | 4.5.1 Index Structure                             | 6 |

|   |      | 4.5.2 RDMA-Based Accesses                         | 6 |

|   | 4.6  | Experimental Evaluation                           | 7 |

|   | 4.7  | Key Findings: Non-Trivial Trade-Offs              | 9 |

|   | 4.8  | Summary                                           | 9 |

| 5 | One  | e-Sided RDMA Synchronization 5                    | 1 |

|   | 5.1  | The Need for Guidelines                           | 1 |

|   | 5.2  | Methodology                                       | 4 |

|   | 5.3  | Pessimistic Synchronization                       | 5 |

|   |      | 5.3.1 Basic Pessimistic Latch Implementation      | 5 |

|   |      | 5.3.2 Performance of RDMA Atomics                 | 6 |

|   |      | 5.3.3 Effect on a Disaggregated DBMS 60           | 0 |

|   | 5.4  | Optimistic Synchronization                        | 1 |

|   | 5.5  | Key Findings: One-Sided Synchronization Is Hard 6 | 2 |

|   | 5.6  | Summary                                           | 3 |

| 6 | Buff | fer-Managed Storage Engine 69                     | 5 |

|   | 6.1  | ScaleStore: Design Overview                       | 6 |

|   |      | 6.1.1 Design Considerations From Previous Work    | 6 |

|   |      | 6.1.2 Main Building Blocks for ScaleStore 6       | 7 |

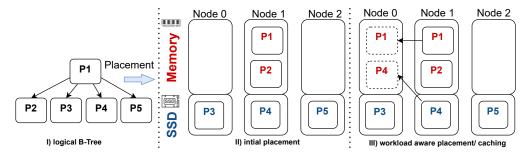

|   |      | 6.1.3 A Motivating Example                        | 9 |

|   |      | 6.1.4 Main Components                             | 0 |

|   | 6.2  | Low-Latency RDMA Messaging                        |   |

|   |      | 6.2.1 Efficient Message Handling in RDMA          |   |

|   |      | 6.2.2 Evaluation                                  |   |

|   | 6.3  | Invalidation-Based Page Coherence Protocol        |   |

|   |      | 6.3.1 Protocol Overview 7                         |   |

|    |      | 6.3.2   | Local Hot Path                        | 75         |

|----|------|---------|---------------------------------------|------------|

|    |      | 6.3.3   | Remote Invocation                     | <b>7</b> 6 |

|    | 6.4  | High l  | Performance Page Eviction             | 78         |

|    |      | 6.4.1   | Epoch-Based LRU Approximation         | 78         |

|    |      | 6.4.2   | Page Provider                         | <b>7</b> 9 |

|    | 6.5  | Synch   | ronization Primitives & Indexes       | 80         |

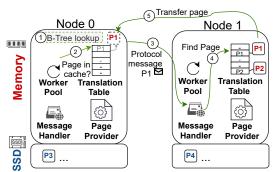

|    |      | 6.5.1   | Example: B-Tree Lookup                | 80         |

|    | 6.6  | Exper   | imental Evaluation                    | 82         |

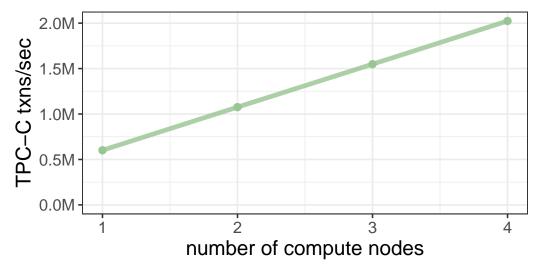

|    |      | 6.6.1   | Scale-Out                             | 82         |

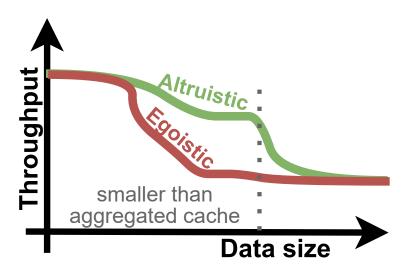

|    |      | 6.6.2   | Data Scalability                      | 83         |

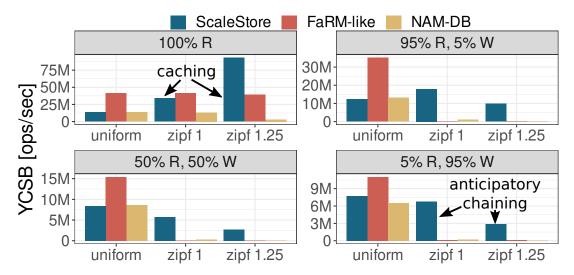

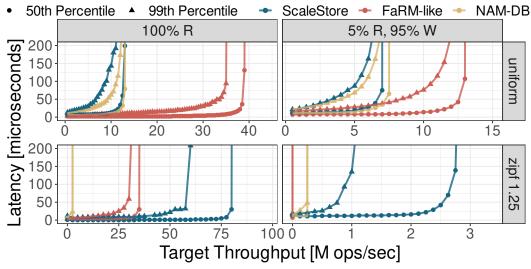

|    |      | 6.6.3   | Distributed In-Memory DBMS Comparison | 84         |

|    | 6.7  | Summ    | nary                                  | 86         |

| 7  | Con  | cluding | Remarks and Future Work               | 89         |

|    | 7.1  | Reflec  | tion                                  | 89         |

|    | 7.2  | Future  | e Research Directions                 | 91         |

|    |      | 7.2.1   | Reconsidering Eviction & Admission    | 91         |

|    |      | 7.2.2   | Concurrency Control                   | 92         |

|    |      | 7.2.3   | Durability & Recovery                 | 93         |

|    |      | 7.2.4   | Evolution of Hardware                 | 93         |

| II | Pe   | er-Rev  | riewed Publications                   | 95         |

| В  | Is S | calable | OLTP in the Cloud a Solved Problem?   | 97         |

|    | 8.1  | Introd  | luction                               | 98         |

|    | 8.2  | OLTP    | Data Access Archetypes                | 100        |

|    |      | 8.2.1   | Archetype: Single-Writer              | 101        |

|    |      | 8.2.2   | Archetype: Partitioned-Writer         | 102        |

|    |      | 8.2.3   | Archetype: Shared-Writer              | 104        |

|    |      | 8.2.4   | Categorizing Systems With Archetypes  | 106        |

|    |      | 8.2.5   | The Importance of Latency             | 108        |

|    | 8.3  | Towar   | ds a Scalable Cloud OLTP DBMS         | 110        |

|    |      | 8.3.1   | A Blueprint for a Shared-Caching DBMS | 110        |

|    |      | 8.3.2   | Caching and Eviction Go Hand in Hand  | 113        |

|    |      | 8.3.3   | Elasticity                            | 113        |

|    |      | 8.3.4   | ACID Guarantees                       | 115        |

|    |      | 8.3.5   | Cloud Infrastructure and Services                             | . 116 |

|----|------|---------|---------------------------------------------------------------|-------|

|    | 8.4  | Summa   | ary                                                           | . 118 |

|    | 8.5  | Acknow  | wledgments                                                    | . 118 |

| 9  | EFA  | : A Via | ble Alternative to RDMA Over InfiniBand for DBMSs?            | 119   |

|    | 9.1  | Introdu | $\operatorname{uction}$                                       | . 120 |

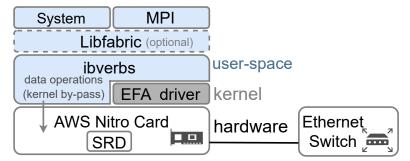

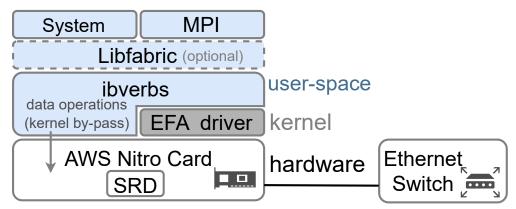

|    | 9.2  | Elastic | Fabric Adapter                                                | . 121 |

|    |      | 9.2.1   | SRD: A Reliable and Unordered Protocol                        | . 121 |

|    |      | 9.2.2   | Ibverbs: Low Level Interface                                  | . 122 |

|    |      | 9.2.3   | Libfabric: EFA's Programming Interface                        | . 123 |

|    | 9.3  | Experi  | mental Evaluation                                             | . 124 |

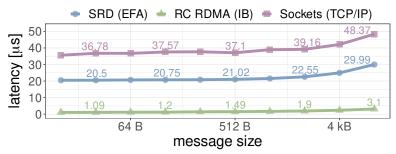

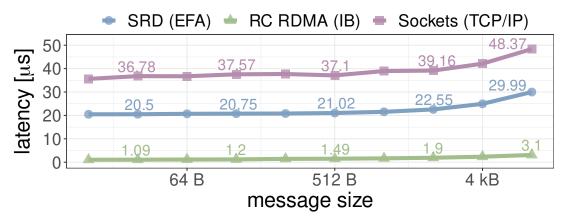

|    |      | 9.3.1   | Latency Comparison                                            | . 124 |

|    |      | 9.3.2   | Synchronous Bandwidth                                         | . 125 |

|    |      | 9.3.3   | Asynchronous Networking                                       | . 126 |

|    |      | 9.3.4   | NIC Parallelism                                               | . 127 |

|    |      | 9.3.5   | EFA Interface Evaluation                                      | . 128 |

|    | 9.4  | Relate  | d Work                                                        | . 129 |

|    | 9.5  | Lesson  | s Learned and Summary                                         | . 129 |

|    | 9.6  | Acknow  | wledgments                                                    | . 130 |

| 10 | Desi | gning C | Distributed Tree-Based Index Structures for Fast RDMA-Capable |       |

|    | Netv | vorks   |                                                               | 131   |

|    | 10.1 | Introdu | $\operatorname{uction}$                                       | . 133 |

|    | 10.2 | Overvi  | ew                                                            | . 135 |

|    |      | 10.2.1  | RDMA Basics                                                   | . 135 |

|    |      | 10.2.2  | Design Space for RDMA-Based Indexes                           | . 136 |

|    |      | 10.2.3  | Scalability Analysis                                          | . 140 |

|    | 10.3 | Design  | 1: Coarse-Grained/Two-Sided                                   | . 143 |

|    |      | 10.3.1  | Index Structure                                               | . 143 |

|    |      | 10.3.2  | RDMA-Based Accesses                                           | . 145 |

|    | 10.4 | Design  | 2: Fine-Grained/One-Sided                                     | . 146 |

|    |      | 10.4.1  | Index Structure                                               | . 146 |

|    |      | 10.4.2  | RDMA-Based Accesses                                           | . 147 |

|    |      | 10.4.3  | Optimization of Index Structure                               | . 149 |

|    | 10.5 | Design  | 3: Hybrid Scheme                                              | . 150 |

|    |      | 10 5 1  | Index Structure                                               | 150   |

|    |       | 10.5.2  | RDMA-Based Accesses                                                                                                                                      |

|----|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 10.6  | Experi  | mental Evaluation                                                                                                                                        |

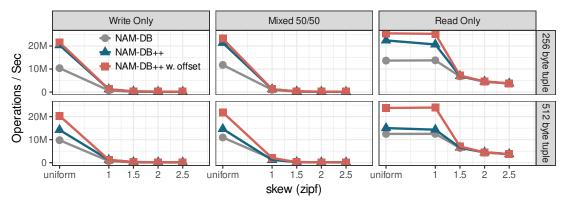

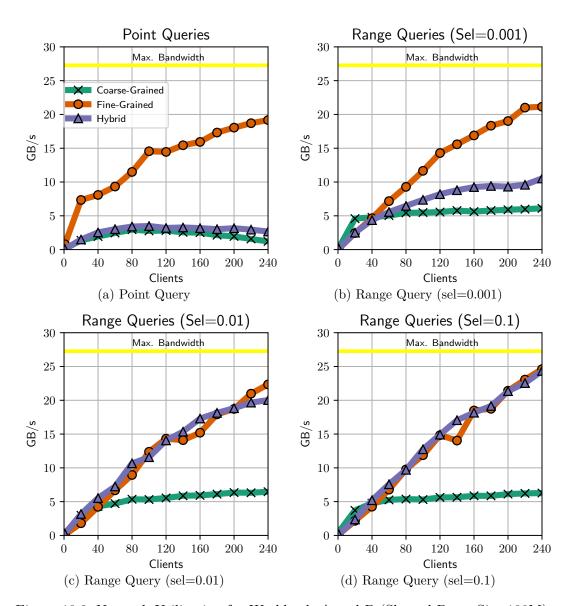

|    |       | 10.6.1  | Exp.1: Throughput                                                                                                                                        |

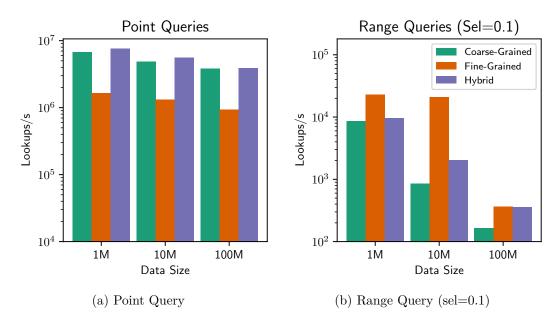

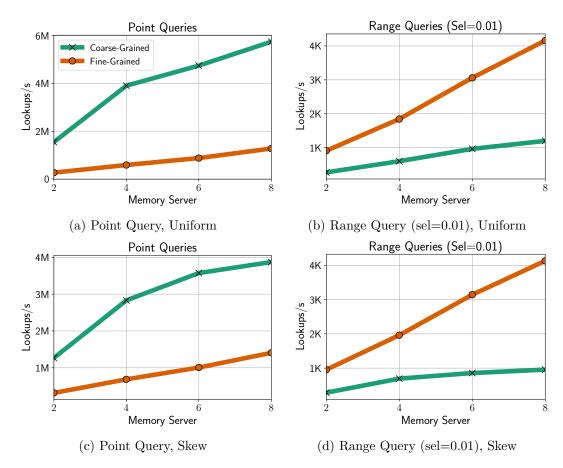

|    |       | 10.6.2  | Exp.2: Scalability                                                                                                                                       |

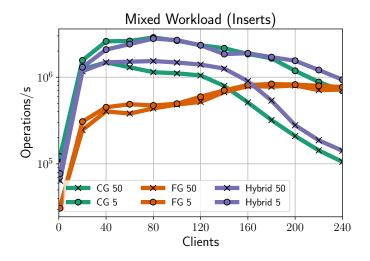

|    |       | 10.6.3  | Exp.3: Workloads With Inserts                                                                                                                            |

|    | 10.7  | Other   | Architectures                                                                                                                                            |

|    | 10.8  | Related | d Work                                                                                                                                                   |

|    | 10.9  | Conclu  | sions                                                                                                                                                    |

|    | 10.10 | )Appen  | dix                                                                                                                                                      |

|    |       | 10.10.1 | Additional Index Operations                                                                                                                              |

|    |       | 10.10.2 | Latency of Index Designs                                                                                                                                 |

|    |       | 10.10.3 | Effect of Co-location                                                                                                                                    |

|    |       | 10.10.4 | Opportunities and Challenges of Caching                                                                                                                  |

|    |       |         |                                                                                                                                                          |

| 11 |       | _       | lelines for Correct, Efficient, and Scalable Synchronization Using                                                                                       |

|    |       | Sided   |                                                                                                                                                          |

|    |       |         | action                                                                                                                                                   |

|    | 11.2  | _       | ound and Methodology                                                                                                                                     |

|    |       |         | Remote Direct Memory Access                                                                                                                              |

|    |       |         | RDMA Hardware Stack                                                                                                                                      |

|    |       |         | Existing Synchronization Techniques                                                                                                                      |

|    |       |         | Evaluation Methodology                                                                                                                                   |

|    | 11.3  |         | istic Synchronization                                                                                                                                    |

|    |       |         | Running Example of a Pessimistic Latch                                                                                                                   |

|    |       |         | Performance of RDMA Atomics                                                                                                                              |

|    |       |         | Optimized Pessimistic Latches                                                                                                                            |

|    |       |         | Ablation Study of Latch Optimizations                                                                                                                    |

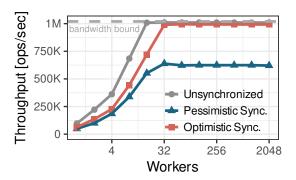

|    |       | 11.3.5  | Effect on a Disaggregated DBMS                                                                                                                           |

|    | 11.4  | Optimi  | stic Synchronization                                                                                                                                     |

|    |       | 11.4.1  | Intuition for Optimistic Synchronization                                                                                                                 |

|    |       | 11.4.2  | PCIe's Ordering Guarantees                                                                                                                               |

|    |       | 11.4.3  | Correct Optimistic Synchronization                                                                                                                       |

|    |       | 11.4.4  | Single-Threaded Performance                                                                                                                              |

|    |       | 11.4.5  | Scalability of Optimistic Techniques $\dots \dots \dots$ |

|    |       | 11.4.6  | Effect on a Disaggregated DBMS                                                                                                                           |

|    | 11.5  | Discuss | sion of Other Approaches                                                                                                                                 |

|    | 11.6  | Lessons Learned and Conclusion                                          | 204 |

|----|-------|-------------------------------------------------------------------------|-----|

| 12 | RDN   | MA Communciation Patterns                                               | 209 |

|    | 12.1  | Introduction                                                            | 210 |

|    | 12.2  | RDMA Background                                                         | 212 |

|    | 12.3  | Related Work                                                            | 213 |

|    | 12.4  | Methodology                                                             | 214 |

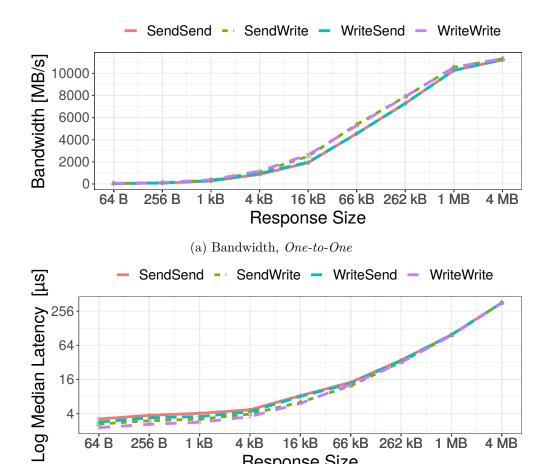

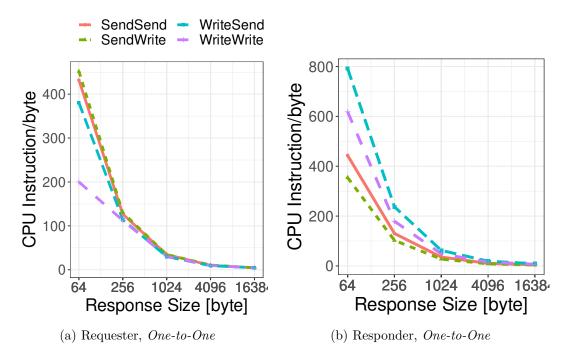

|    | 12.5  | Evaluation: One-to-One                                                  | 218 |

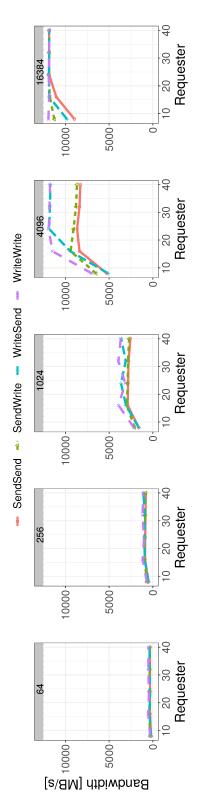

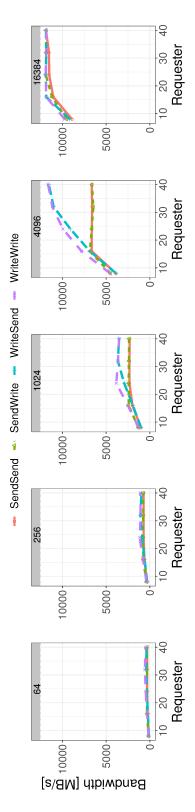

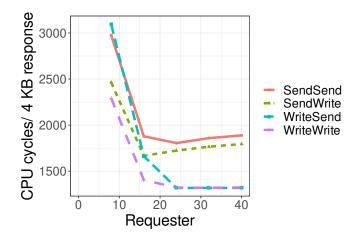

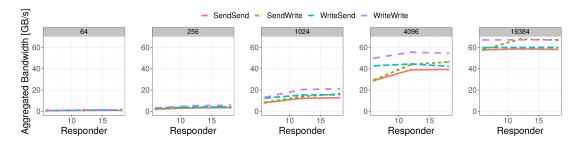

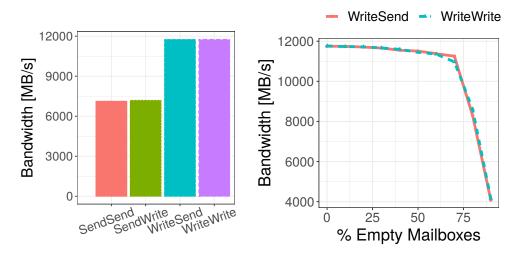

|    | 12.6  | Evaluation: N-to-One                                                    | 220 |

|    | 12.7  | Evaluation: N-to-M                                                      | 225 |

|    | 12.8  | RDMA Optimizations                                                      | 229 |

|    | 12.9  | Discussion and Conclusions                                              | 231 |

|    | 12.10 | 0Acknowledgements                                                       | 231 |

| 10 | ٠.    | C. A.F                                                                  |     |

| 13 |       | eStore: A Fast and Cost-Efficient Storage Engine using DRAM, NVMe, RDMA | 233 |

|    |       | Introduction                                                            |     |

|    |       |                                                                         |     |

|    | 13.2  | System Overview                                                         |     |

|    |       | 13.2.1 A Motivating Example                                             |     |

|    | 199   | 13.2.2 Main Components                                                  |     |

|    | 13.3  | Distributed Page Coherence                                              |     |

|    |       | 13.3.2 Local Hot Path                                                   |     |

|    |       |                                                                         |     |

|    |       | 13.3.3 Remote Invocation                                                |     |

|    |       | 13.3.5 Low-Latency RDMA Messaging                                       |     |

|    | 19 /  | High Performance Page Eviction                                          |     |

|    | 10.4  | 13.4.1 Epoch-Based LRU Approximation                                    |     |

|    |       | 13.4.2 Page Provider                                                    |     |

|    |       | 13.4.3 RDMA and NVMe Optimizations                                      |     |

|    | 13.5  | Programming Abstraction                                                 |     |

|    | 10.0  | 13.5.1 Interface                                                        |     |

|    |       | 13.5.2 Example: B-Tree Lookup                                           |     |

|    | 126   | Evaluation                                                              |     |

|    | 10.0  | 13.6.1 Experimental Setup                                               |     |

|    |       | 13.6.2 Scale-Out                                                        | 257 |

|      | 13.6.3 | Data Scalability     | 259 |

|------|--------|----------------------|-----|

|      | 13.6.4 | ScaleStore vs. GAM   | 259 |

|      | 13.6.5 | Workload Change      | 260 |

|      | 13.6.6 | Elasticity           | 261 |

|      | 13.6.7 | System Comparison    | 261 |

| 13.7 | Relate | d Work               | 266 |

| 13.8 | Conclu | sion and Future Work | 268 |

| 13.9 | Acknow | vledgments           | 269 |

# **Acronyms**

**2PC** Two-Phase Commit

**DBMS** Database Management System

**DMA** Direct Memory Access

**EFA** Elastic Fabric Adapter

**SRD** Scalable Reliable Datagram

**IPoIB** IP over InfiniBand

**NIC** Network Interface Card

**OLTP** Online Transaction Processing

**RDMA** Remote Direct Memory Access

RNIC RDMA-enabled NIC

SQ Send Queue

**CQ** Completion Queue

**RQ** Receive Queue

**RoCE** RDMA over Converged Ethernet

${f MVCC}$  Multiversion Concurrency Control

**TPU** Tensor Processing Units

**GPU** Graphics Processing Units

SSD Solid State Drives

FPGA Field Programmable Gate Array

# Part I

# **Synopsis**

# 1 Introduction

Online Transaction Processing (OLTP) forms the foundation of real-time data processing across various applications, such as banking transactions, credit card payments, or e-commerce. These applications typically issue short-duration, latency-sensitive transactions that demand immediate processing [72]. Alibaba recently reported that their mission-critical workloads reach peak transaction rates of up to 70 million transactions per second [87].

These high transaction volumes surpass the capacity of a single machine and require distributed OLTP Database Management System (DBMS), which are deployed across multiple powerful machines<sup>1</sup>. The basic architecture of these systems, originally designed to minimize network communication, has seen little alteration since the 1980s. At that time, high network latency was the primary concern for efficient OLTP.

However, with the emergence of modern high-speed network protocols, the landscape of distributed DBMSs is undergoing significant transformations. These modern networks challenge the conventional belief that network communication is the bottleneck, questioning if the design decisions based on such a notion are still valid.

The subsequent sections explore this observation in more detail. We first examine how distributed DBMSs were historically designed and why modern high-speed networks challenge the existing design paradigm. This examination sets the stage to explore the unresolved challenges this thesis intends to address.

# 1.1 Traditional Distributed Database Design

The shared-nothing architecture [202] has been the foundation of distributed databases since its proposal in the 1980s, underpinning numerous commercial systems [45, 90, 115].

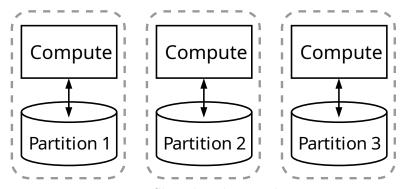

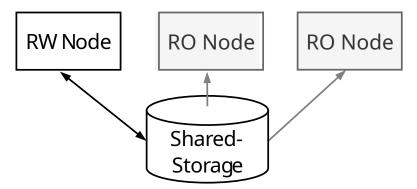

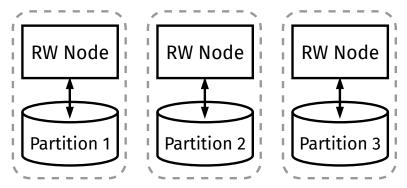

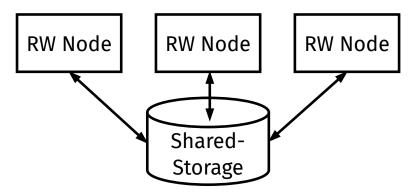

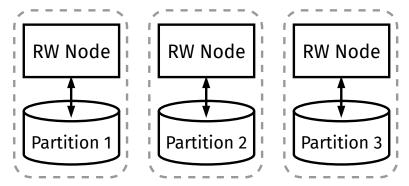

As shown in Figure 1.1, its core idea is to partition (or shard) the database across multiple nodes with node-private storage and compute resources. In this design, every node hosts an autonomous database where only local data can be accessed. When a

<sup>&</sup>lt;sup>1</sup>In this dissertation, we focus on databases that run in a single datacenter, i.e., cluster.

Figure 1.1: Shared-nothing architecture.

transaction is confined to one partition, i.e., only requiring data from a single node, it can be processed locally without network communication. However, OLTP workloads can be complex and hard to partition [156], resulting in transactions that access data on multiple partitions. As resource sharing is avoided and every node operates independently, distributed databases require intricate techniques such as Two-Phase Commit (2PC) [70] to coordinate these cross-partition transactions. This limits their scalability for more complex workloads containing cross-partition transactions [46, 239] (due to the need for inter-node communication and coordination). Furthermore, this design struggles to handle workload shifts, balance load across all machines, and is susceptible to hot spots, e.g., in cases of read skew [170, 178, 202]. Moreover, tightly coupling storage to the compute resources makes it impossible to scale them independently, a need increasingly driven by modern cloud databases [6, 217, 218]. Nonetheless, in 1982, the sharednothing architecture offered a reasonable trade-off since the network latency for sending a 2kB packet was about  $13000 \times$  more expensive than a simple memory reference [169]. Consequently, reducing network access through data partitioning and only accessing local data was a sensible design choice.

### 1.2 Fast Networks

In recent years, advancements in networking technology have invalidated the long-standing assumption that networks are fundamentally slow. Notably, the increase in bandwidth has been so dramatic that it now closely rivals the bandwidth of main memory [20]. Modern servers, such as the NVIDIA DGX A100, come equipped with as many as eight network cards yielding an aggregated bandwidth of up to 200 gigabytes per second. This

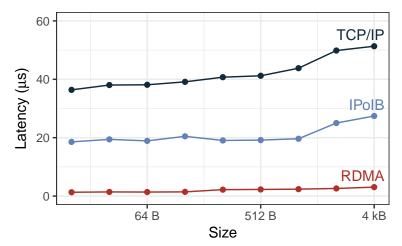

Figure 1.2: Latency comparison TCP/IP over Ethernet, IPoIB, and RDMA. Measured on ConnectX5 with Mellanox benchmark tools sockperf for TCP/IP and IPoIB and ib\_write\_lat for RDMA)

network bandwidth is undeniably impressive. Unfortunately, the bottleneck for most distributed OLTP databases is not the bandwidth but the network latency.

Therefore, many database vendors [29, 89, 128, 175] are increasingly adopting specialized interconnects such as InfiniBand, which offer low latency, often in the single-digit microsecond range [20]. These interconnects employ a communication stack known as *Remote Direct Memory Access (RDMA)*. Utilizing this stack requires software adaptations, especially in the context of existing legacy systems.

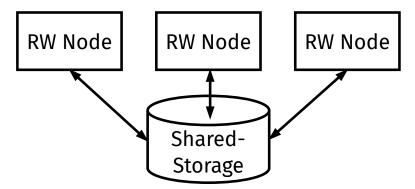

To enable the transition without modifying existing applications, IP over InfiniBand (IPoIB) implements a traditional TCP/IP stack as an overlay on InfiniBand. Although IPoIB allows for straightforward migration, it does not fully leverage the low latency. Figure 1.2 compares the latency of traditional TCP/IP over Ethernet, IPoIB, and RDMA for data transfers from 16 B to 4 kB the typical message sizes in data center applications [10, 174].

By utilizing optimization techniques such as kernel-bypass<sup>2</sup>, which avoids the overhead of context switches and bypasses the operating system's network stack, RDMA primitives can outperform IPoIB by one order of magnitude. Compared to traditional socket-based networking (TCP/IP), this improvement is even greater. Consequently, a redesign of the communication stack is necessary to fully exploit the advantages of specialized interconnects like InfiniBand.

<sup>&</sup>lt;sup>2</sup>See Chapter 2 for a detailed discussion on RDMA and its low-level details.

#### 1 Introduction

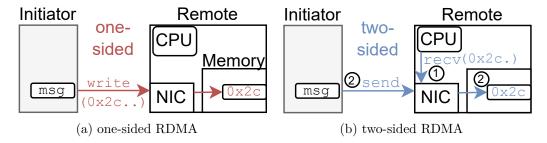

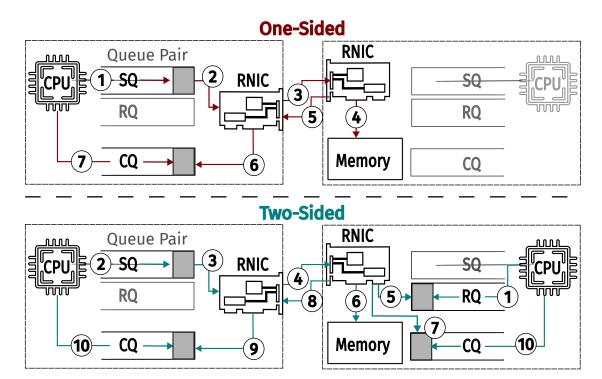

Figure 1.3: RDMA primitives: (a) Depicts a one-sided write that directly writes into the remote memory. (b) Shows a two-sided send and receive operation where the receive operation steers the incoming send to the memory location.

This redesign should incorporate RDMA primitives, which can be categorized into one-sided and two-sided verbs:

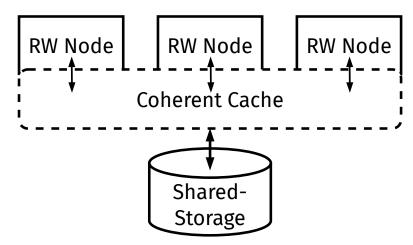

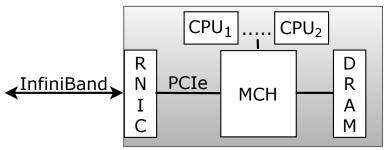

One-sided verbs. One-sided verbs (read, write, and atomic) provide remote memory access semantics. That means the sender (initiator) can directly read or manipulate remote memory as depicted in Figure 1.3a. When using one-sided verbs, the CPU of the remote node is not actively involved in the data transfer. Instead, the remote Network Interface Card (NIC) performs the entire memory access. For this to work, the initiator must provide the remote memory address to the remote NIC, as depicted in Figure 1.3a. This example shows a message transfer via one-sided write to the remote memory.

Two-sided verbs. Two-sided verbs, specifically send and receive, operate on channel semantics and involve the receiver's CPU in the communication process (see Figure 1.3b). The receive operation, which must be posted before the send operation, specifies the memory location for incoming data. This control mechanism allows the remote CPU to direct the incoming send to the appropriate memory location, thereby exercising granular control over data storage. Notably, the remote CPU's involvement is asynchronous and limited to providing the receive request, with no direct role in the NIC's memory access operation once the message arrives.

To summarize, RDMA verbs are fundamentally different compared to the traditional blocking socket-based POSIX API and allow for novel database designs. On the other hand, they provide unique challenges and adopting new primitives like RDMA into existing systems often fails to fully leverage specialized interconnects, given the different communication paradigms. In addition, it is not clear which RDMA primitive is best suited for databases. Hence, academia and industry have explored the numerous opportunities these novel communication primitives present as shown in the next section.

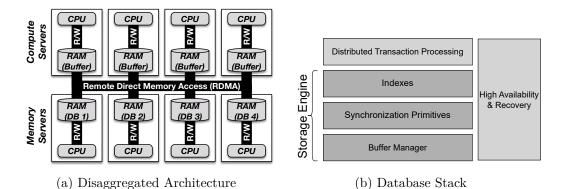

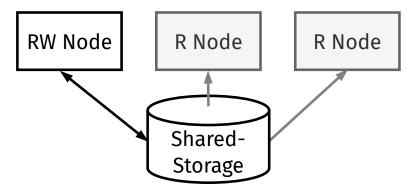

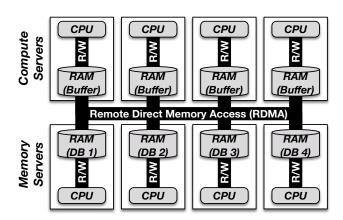

Figure 1.4: (a) Shows a disaggregated architecture as used by NAM-DB where the compute layer can access the storage via one-sided RDMA. (b) Depicts a typical database stack.

### 1.3 State of the Art

Database systems are highly sophisticated pieces of software composed of multiple components, as illustrated in Figure 1.4b. The conventional shared-nothing architecture typically isolates network communication within distributed transaction processing. Thus, the techniques in the lower layers, free from network communication, could be universally applied in both single-node and distributed databases.

The RDMA primitives, however, enable new designs where the network communication can be pushed down the stack to access remote data directly. For instance, some work proposes efficient techniques to ensure high availability, replication, and recovery [165, 166, 207, 222, 242]. In this line of work, Zamanian et al. argue that the bottleneck shifted from the network to the CPU. Thus, conventional replication schemes that re-execute the transaction logic on the replicas are becoming suboptimal. To address this challenge, the authors propose a high-availability solution that effectively utilizes one-sided RDMA to directly update the replicas' data, avoiding redundant computation.

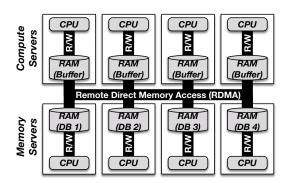

Most existing research revolves around distributed transaction processing, a complex domain. For example, several papers optimize distributed lock management, an integral part of concurrency control, by using RDMA [33, 51, 158, 236]. In addition, other papers take a more comprehensive approach and propose radically new architectures. Unlike the shared-nothing architecture, which restricts access to local data, NAM-DB [20, 239] uses one-sided RDMA to enable network-wide data access. NAM-DB adopts a disaggregated architecture as shown in Figure 1.4a where compute and storage are decoupled. The benefit is that compute and storage can be added and removed independently. In NAM-

DB, all data is stored in the memory servers and can be accessed and manipulated by the compute nodes via one-sided RDMA.

Besides decoupled designs, more tightly coupled alternatives are still being explored. For example, FaRM [55, 56, 196] couples compute and storage tightly like the shared-nothing architecture so that local data can be accessed without network communication. However, for distributed transaction processing FaRM exposes a shared address space across all machines. Meaning every node can read remote data using one-sided RDMA. Another example of a tightly coupled design is FaSST [103] which presupposes static partitioning and optimizes the performance of the traditional shared-nothing design with RDMA. In contrast to NAM-DB and FaRM, the authors argue that one-sided RDMA is less scalable, and thus they exploit two-sided RDMA in FaSST.

The reviewed literature indicates a prevailing trend of using RDMA for efficient data access. In particular, FaRM and NAM-DB pushed the idea that data can be accessed from every node via one-sided RDMA. However, despite these advancements, some areas remain largely unexplored. Firstly, the emphasis has been predominantly on distributed transaction processing, leaving room for more research focusing on the lower components in the database stack, such as indexing, latching, and caching (cf. Figure 1.4b). Secondly, the balance between tightly coupled and decoupled computational and storage designs warrants further exploration. While NAM-DB is based on the disaggregated architecture, FaSST's arguments favoring static partitioning and two-sided RDMA indicate potential areas for further investigation. Below we explore these areas in more detail and highlight challenges that need to be addressed.

# 1.4 Storage Engine: The Missing Component

As we discussed earlier, the lower layers of the database stack, indexes, synchronization, and caching remained largely unexplored; those three layers combined are called the *storage-engine* (cf. Figure 1.4b) and ensure efficient data access:

Indexes are essential for any OLTP database, enabling efficient lookups by eliminating the need for full table scans and substantially reducing query execution time. Accompanying this, synchronization primitives<sup>3</sup> become indispensable for parallel index lookups to fully utilize modern multi-core CPUs, which have been the primary driver of performance improvement since the end of Moore's law. Lastly, the buffer manager is

<sup>&</sup>lt;sup>3</sup>In this context, synchronization primitives refer to the low-level synchronization mechanisms, such as latching, rather than the higher-level concurrency control required in transaction execution. For most people outside the database community, latches are synonymous with locks, e.g., mutexes or spinlocks.

critical in optimizing data access efficiency. Its primary responsibility lies in maintaining a low-latency DRAM cache (the buffer pool), which effectively stores frequently accessed, or hot data, thereby avoiding access latency of slower storage devices. Less frequently accessed or cold data is evicted to the slower storage devices once the buffer pool capacity is reached.

Historically, hardware advancements have driven the continuous optimizations of these layers to improve data access. For example, the buffer manager in disk-based systems keeps frequently accessed data in memory to avoid very high disk latency. Fast-forward a few decades, in-memory systems have abandoned the buffer manager under the assumption that the data set fits into the DRAM, and memory prices continue to decline. With the increased speed of in-memory databases and the primary performance gains stemming from multi-core CPUs, the bottleneck shifted to synchronization and indexes, which were then heavily optimized.

In light of the recent advancements in RDMA-enabled databases, the landscape of data access has undergone a significant transformation. This requires a comprehensive redesign of the storage engine components to exploit the potential of RDMA. This need is underscored by the fact that efficient data access forms the cornerstone of the performance of all higher layers and the entire OLTP system. While state-of-the-art systems have improved the efficiency of distributed transactions, we have identified a shift in the performance bottleneck towards data access, as facilitated by the storage engine. As we will demonstrate in this dissertation, our prototype storage engine can outperform NAM-DB by up to  $100\times$ .

However, building such a network-optimized storage engine introduces several unresolved challenges. To address these challenges, we first revisit distributed database architectures before examining each storage engine layer in detail.

### **Challenge 1: Evaluating Distributed Architectures**

The fundamental objective of a storage engine is to ensure efficient data access. However, there is an inherent dependency on the underlying distributed system architecture, i.e., data access depends on where the data is stored across multiple nodes and how it can be accessed.

A notable observation is that RDMA-enabled systems such as FaRM, NAM-DB, and FaSST implement divergent data access paths and design choices. For instance, FaSST [103] adopts a shared-nothing architecture with local access only, while NAM-DB [239] uses one-sided read and writes, allowing every node to access and manipulate

#### 1 Introduction

all data. FaRM positions itself in the middle, utilizing one-sided read operations to access all data directly. Nevertheless, it deviates from the NAM-DB model regarding write operations. Instead of implementing one-sided write operations, FaRM resorts to message-passing techniques, transmitting write requests to a partition's owner that applies the changes locally.

This multifaceted nature of available design decisions raises the question of which architecture to adopt and whether these architectures exhibit fundamental differences, e.g., in system scalability. Consequently, the initial challenge lies in comprehensively analyzing these architectures. In the second step, we can devise optimized storage engine components integrated optimally into the architecture, as discussed in the following.

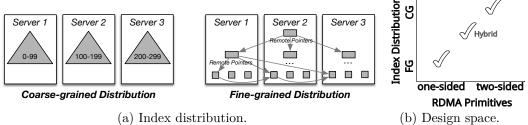

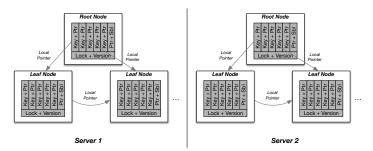

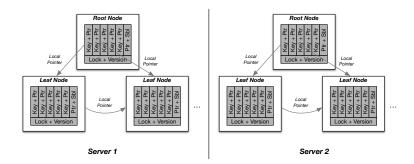

#### Challenge 2: Designing RDMA-Optimized Indexes

Disaggregated RDMA-enabled DBMSs like NAM-DB demonstrate considerable flexibility, permitting independent scaling of compute and storage resources. Nevertheless, this decoupling introduces a unique challenge: the need for efficient data retrieval via the network from remote storage. While RDMA primitives provide part of the solution to retrieve data once the location is known, this is often not the case requiring indexes. B-Tree indexes are particularly prevalent in OLTP databases as they facilitate efficient point lookups, inserts, deletes, and range scans - crucial operations for any general-purpose OLTP database.

Yet, much of the current research focuses on alternative index structures, such as hashtables [55, 104, 204, 227, 233, 239], which, unfortunately, do not offer efficient range scans. Some research does look at tree-like indexes, but it is mostly within tightly-coupled architectures [103, 233], avoiding the need for RDMA-enabled index access. Cell [150] has been the only index that considers one-sided RDMA, but does focus on how to balance the CPU ressources in a client server setting instead of an evaluation of how to leverage RDMA for building efficient indexes.

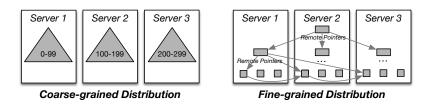

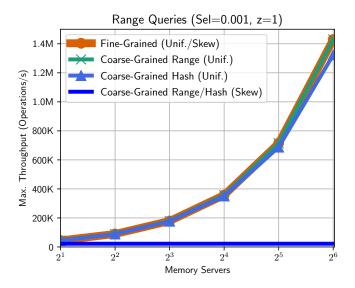

As such, a principled study on building efficient RDMA-enabled tree-like indexes for disaggregated architectures has yet to be conducted. In particular, two critical design questions must be addressed: (1) Which RDMA verb to use for efficiently traversing the index, and (2) how should data be distributed across storage servers to optimize RDMA-based access and avoid hot spots? Addressing these unresolved questions forms the second challenge of this dissertation.

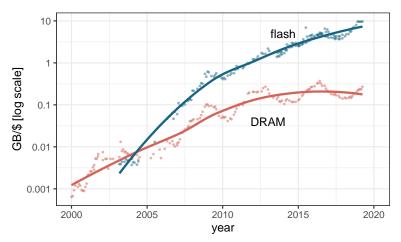

Figure 1.5: Price development for DRAM and flash (higher is cheaper). Source: https://jcmit.net/memoryprice.htm.

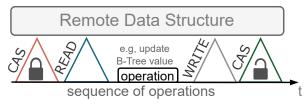

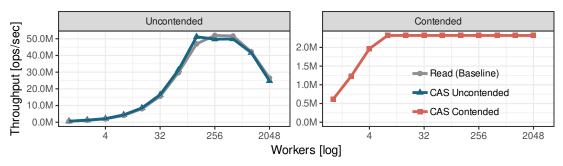

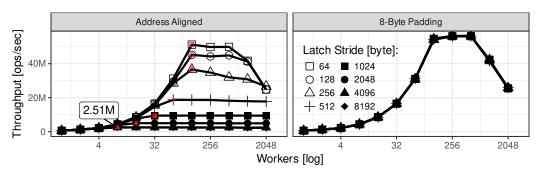

#### Challenge 3: Ensuring Correctness in One-Sided RDMA Synchronization

RDMA-enabled disaggregated DBMSs offer good scalability w.r.t. the number of compute nodes. However, this scalability inherently introduces increased concurrency, requiring careful and efficient synchronization. Given the ability of all compute nodes to access any data item via one-sided RDMA operations, traditional server-side synchronization techniques become obsolete. This is because server-side synchronization involves the remote CPU, which one-sided RDMA operations bypass. Thus, new synchronization techniques built with one-sided RDMA primitives are required.

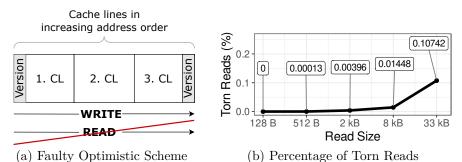

While various one-sided synchronization techniques have been proposed in related work [55, 150, 223, 233, 256] it is hard to navigate the design space. In particular, since many designs rely on hardware behaviour that worked at that time, but our analysis reveals that some of these methods do not work anymore. Some suffer from scalability limitations and other published schemes fail to synchronize correctly on modern NICs, leading to potential data corruption. Our investigation suggests that these problems primarily stem from incorrect assumptions about the memory model of RDMA and the behaviour of modern NICs. This revelation emphasizes the need for comprehensive guidelines to assist engineers in creating scalable and reliable one-sided synchronization schemes.

#### Challenge 4: Designing a High-Performance Buffer Manager

The previously discussed systems were strictly in-memory; hence, they did not require a buffer manager. The design choice to abandon the buffer manager has been backed by two key factors in the past: (1) The high overhead associated with traditional buffer managers [80] and (2) the steady decline in memory costs. A decade ago, the prices of DRAM were consistently decreasing every year, making in-memory data processing seem economically viable. However, this trend has halted in the past decade and DRAM prices have plateaued, as demonstrated in Figure 1.5.

At the same time, there is a growing need to handle larger data sets, as witnessed by cloud vendors now regularly supporting databases up to 100 TB in size. This shift makes it economically impractical to maintain the entirety of the data (both relations and indexes) in-memory across a cluster of machines. Instead, a more cost-effective approach is required, where the storage engine, specifically the buffer manager component, can offload infrequently accessed data to economical storage options like NVMe flash storage while maintaining high performance.

However, integrating a buffer manager in a distributed system where all compute nodes can access all data presents its own challenges. In particular, how to integrate RDMA with secondary storage since fully one-sided RDMA designs intrinsically operate under the assumption that the necessary objects are in memory. However, this premise becomes invalid when data is evicted from the buffer pool. Moreover, data organization within these systems requires a different approach. Rather than managing in-memory objects of varied sizes, buffer-managed systems often adopt a fixed-size, page-based design where data is systematically organized in blocks to utilize SSDs as best as possible. Until now, no buffer manager has effectively combined RDMA with efficient NVMe storage, and designing such a system remains an open question. This constitutes the fourth challenge that this thesis aims to address.

### 1.5 Contributions

This thesis addresses the challenges enumerated above with the following contributions that can be summarized as follows:

#### **Contribution 1: Analysis of Distributed Architectures**

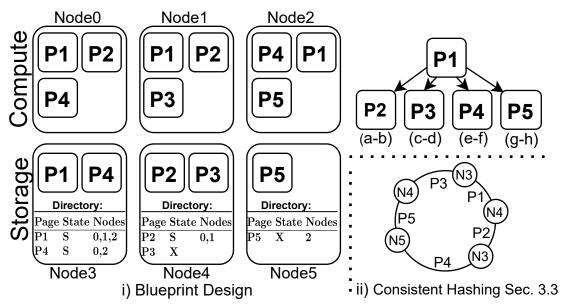

We conduct a comprehensive analysis of various distributed DBMS architectures and propose a novel taxonomy as a tool to categorize their scalability attributes. We posit that the disaggregated multi-writer architecture, exemplified by NAM-DB, exhibits considerable benefits regarding scalability and elasticity. However, to maximize this architecture's potential, it is essential to incorporate caching as a fundamental component. This thesis will explore this approach in further detail.

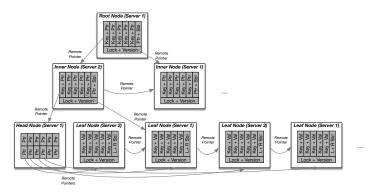

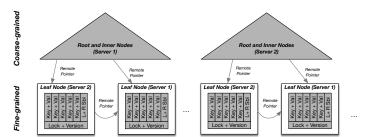

#### Contribution 2: RDMA-Optimized Indexes

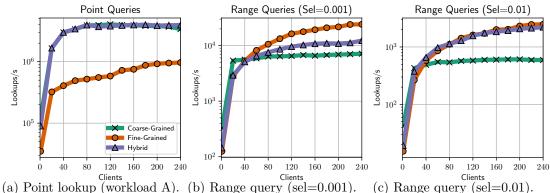

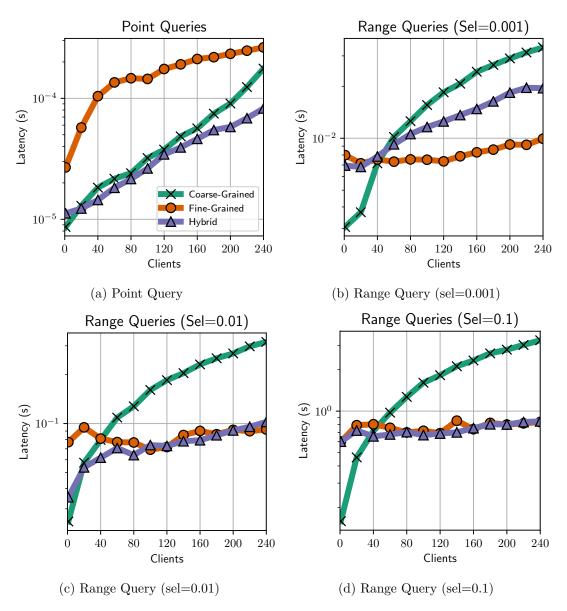

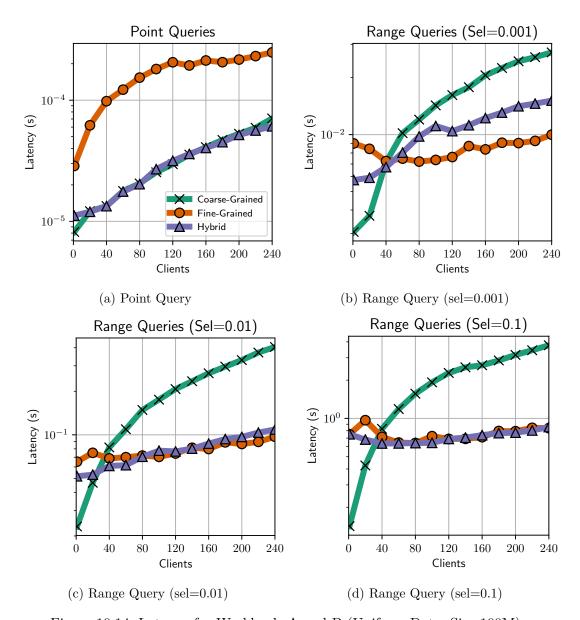

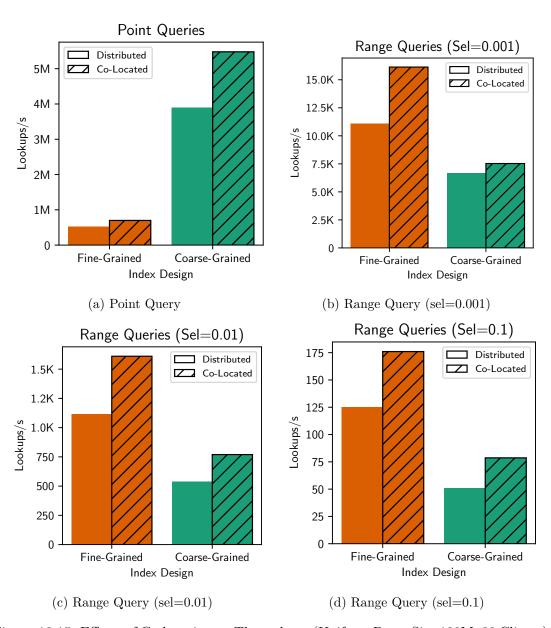

We explore RDMA-optimized tree-like index designs tailored explicitly for disaggregated architectures. The two main aspects that we focus on are: (1) How the index itself should be distributed across several memory servers and (2) which RDMA primitives should be used by compute servers to access the distributed index structure in the most efficient manner. Our experimental evaluation shows the trade-offs for different distributed index design alternatives using a variety of workloads.

#### Contribution 3: One-Sided RDMA Synchronization Guidelines

Driven by the observation that achieving fast and scalable one-sided synchronization presents significant challenges, we conduct a comprehensive analysis of one-sided synchronization techniques We identify and address scalability and correctness issues in one-sided RDMA synchronization primitives. To resolve these issues, we develop a set of comprehensive guidelines for creating scalable and reliable one-sided RDMA synchronization primitives. Our research demonstrates that adherence to our guidelines not only guarantee correctness but also results in substantial performance enhancements.

#### Contribution 4: High-Performance Cache-Coherent Storage Engine

In the final contribution, we primarily focus on the last component — the buffer manager. Concurrently, we incorporate lessons learned from our preceding body of work to build a full-fledged storage engine (support for indexes, synchronization primitives, and buffer cache) in a holistic way. We present an innovative design for a distributed buffer manager that balances performance and cost-efficiency through NVMe flash storage. Our buffer manager employs a distinct cache-coherence protocol to address the perennial issue of buffer-cache consistency. Additionally, our buffer manager offers user-friendly abstractions with synchronization primitives for efficiently building distributed indexes. We show that

#### 1 Introduction

our storage engine is on par with the performance of distributed in-memory-only engines while effectively handling workloads that exceed available memory capacity.

### 1.6 Outline

The remainder of this dissertation is organized as follows: Chapter 2 introduces RDMA in detail. Chapter 3 revisits the question of how a scalable OLTP design should look like. We examine various designs based on their data access behavior and present a scalability comparison. Further, this chapter benchmarks the low-latency networks that are available in the cloud: RDMA and Elastic Fabric Adapter (EFA). Chapter 4 explores the design space of RDMA-enabled distributed indexes, and Chapter 5 develops guidelines for implementing efficient and correct one-sided RDMA synchronization primitives. Chapter 6 presents our buffer manager design that emerged based on the previous work. This chapter details how we combine cost-efficient NVMe storage with RDMA and evaluates the system against optimized distributed in-memory DBMSs. Finally, Chapter 7 concludes this thesis and outlines future work.

## 2 RDMA Primer

RDMA's low-level primitives are efficient yet notoriously tricky to use and pose unique design challenges to developers. Thus, this chapter describes RDMA in sufficient depth to understand the subsequent contributions that shed light on those challenges.

## 2.1 Capabilities

RDMA allows one machine to directly access remote memory over the network without interrupting the CPU on the remote system. Instead, specialized RDMA-enabled NIC (RNIC) perform the memory accesses on the remote side. Conversely, the same technique is used on the sender to avoid unnecessary copys from the user-space into the kernel-space. The sender essentially instructs the RNIC what memory needs to be sent, and the NIC's Direct Memory Access (DMA) engine copies the data and places it on the wire. This offloading is also called zero-copy transfer and decreases CPU usage and, thus, latency. Several network architectures offer RDMA – most notably InfiniBand and RDMA over Converged Ethernet (RoCE) [219]. This thesis focuses on the reliable RDMA connection type<sup>1</sup>, reliably connected queue pair (RC QP), as specified per the InfiniBand standard [91].

## 2.2 Primitives

Previously, we casually mentioned that the sender instructs the NIC. This is done with low-level primitives. In particular, the reliable connected RDMA implementations typically provide different primitives (called verbs) that can be categorized into the following two classes: (1) one-sided and (2) two-sided verbs.

<sup>&</sup>lt;sup>1</sup>Besides reliable connection (RC), there is an unreliable connection (UC) and an unreliable datagram (UD)

Figure 2.1: A detailed depiction of one-sided (upper) and two-sided RDMA (lower) operations. Depicting the components involved in the transfer from the sender (left) to the remote (right) and highlighting the differences in CPU involvement.

#### 2.2.1 One-Sided Verbs

As mentioned before, one-sided verbs provide remote memory access semantics, where the initiator specifies the remote memory address that should be accessed. The one-sided operations are so named since they can be initiated by one party (the sender or initiator) without CPU involvement from the other party (the receiver or target). There are three operations supported:

- read operations allow the sender to read data directly from a remote memory.

- write operations allow the sender to write data directly into a remote memory.

- atomics include Compare-and-Swap (CAS) and Fetch-and-Add (FAA). These operations atomically modify remote memory and operate on 8 B target memory.

Figure 2.1 (upper) visually outlines the process of a one-sided operation. The sender is depicted on the left side of the figure, with the receiver on the right. Components not

engaged in the process are greyed out to emphasize the difference between one-sided and two-sided operations. In the *reliable connected queue pair* connection type, the *queue pair* is the mechanism to execute the primitives reliably. As shown in the figure, a queue pair consists of a *send queue* and a *receive queue*; in the following, we will see what each queue does.

The one-sided operation begins ① when the sender's CPU submits a work request to its local Send Queue (SQ), which is mapped to the memory. This work request specifies the remote target address, the target length in bytes, and the chosen operation (read, write, or atomic). The sender's RNIC then retrieves the work request from the SQ ② and forwards it to the receiver ③. The receiver's RNIC processes this incoming one-sided request by executing the specified operation directly on the target memory ④. It is noteworthy that throughout this entire process, the receiver's CPU is not involved. Upon the operation's completion, an acknowledgment is transferred from the receiver's RNIC to the sender ⑤. The sender's RNIC generates a completion event that is enqueued into the Completion Queue (CQ) ⑥. The completion event informs the sender's CPU that the operation has been completed. Note that the sender's CPU can asynchronously inspect the CQ for the completion event. In practical terms, this means that there can be numerous outstanding work requests in the SQ before the completion is checked and that the sender CPU accomplishes other work during this whole process.

#### 2.2.2 Two-Sided Verbs

Two-sided verbs provide channel semantics. In contrast to one-sided verbs, there are only two operations that are executed pair-wise:

- receive operations are executed on the receiver and specify the remote memory region where the incoming message should be placed.

- send operations are executed on the sender and specify the payload, i.e., the message that should be transferred.

Contrasting with one-sided operations, both the sender's and receiver's CPUs participate in the two-sided operations, as depicted in Figure 2.1 (lower). The receiver's CPU ① initiates the two-sided process, where a receive request is posted to the Receive Queue (RQ). This step can be executed asynchronously, allowing for posting multiple receive requests in advance (as we will see, those are consumed by incoming requests and thus must be available). Note that after posting the receive request, the receiver CPU is not actively involved in the data transfer. Following this, the sender posts a send request

#### 2 RDMA Primer

②, which is then processed ③ and relayed to the receiver's RNIC ④. Once an incoming send operation arrives, a receive request is fetched from the RQ ⑤. The receive request specifies the memory address that the RNIC utilizes for copying the message ⑥ – as such, the receiver has granular control over memory, unlike with one-sided where the sender has the control. The receiver's RNIC writes the incoming message to memory and generates a completion event ⑦. This event informs the receiver's CPU of the memory address to which the incoming message will be copied. The final steps are the same as for one-sided operations: an acknowledgment is dispatched to the sender ⑧, after which a completion event is produced ⑨. This event indicates the successful end of the two-sided operation.

This chapter has laid the foundation for understanding RDMA, setting the stage for subsequent discussions. As we delve deeper into the subject in later chapters, we will address more nuanced aspects of RDMA, such as maintaining consistency between local CPU processes and remote operations.

## 3 Scalable OLTP Architectures

The primary role of a storage engine revolves around ensuring efficient data access. As previously discussed, integrated components of the storage engine optimize data access, such as indexing, caching, and synchronization. Yet, data access is also inherently tied to the underpinnings of the distributed system architecture it resides on. In essence, efficient data access is based on how well a design accommodates read and write operations and the technique employed for accessing the data. Therefore, before diving into the storage engine, we first investigate those two areas (1) distributed architectures in Section 3.1 and (2) modern network technologies in Section 3.2.

## 3.1 Towards Scalable Online Transaction Processing

**Publication.** The work on scalable OLTP in the cloud is published in the peer-reviewed publication "Is Scalable OLTP in the Cloud a Solved Problem?" in the 13th Annual Conference on Innovative Data Systems Research, CIDR 2023, Amsterdam, The Netherlands, January 8-11, 2023, Online Proceedings [251], cf. Chapter 8.

Contributions of the author. Tobias Ziegler is the leading author of the publication [251] mentioned above. He is responsible for mapping and analyzing the design space and deriving the taxonomy from the results. The co-authors Philip A. Bernstein, Viktor Leis, and Carsten Binnig have contributed invaluable feedback. All authors agree with the use of the publication for this dissertation.

The DBMS market has shifted significantly from on-premise to the cloud in the last few years. According to a recent market report<sup>1</sup>, in 2021 DBMS revenue in the cloud was on par with the on-premise market. Consequently, classical DBMS vendors such as IBM and Oracle have been or are about to be overtaken by hyperscalers such as AWS, Microsoft, and Google, which have heavily invested in their cloud-native DBMSs.

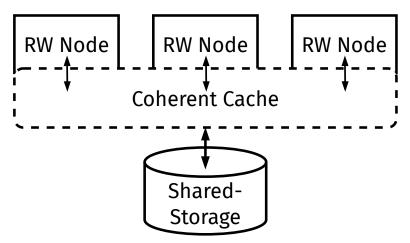

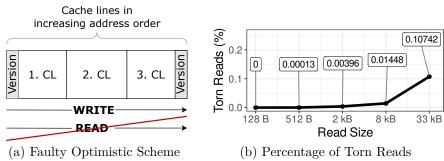

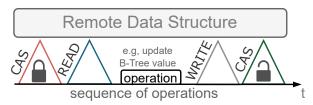

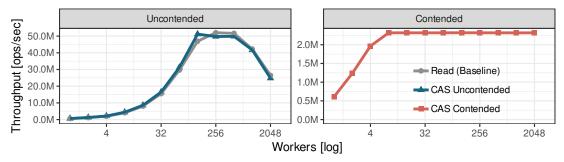

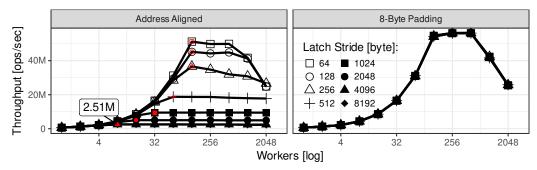

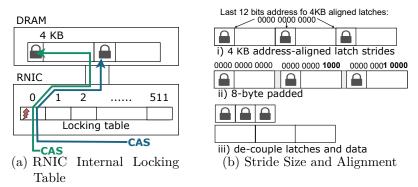

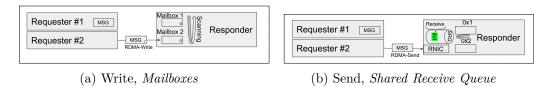

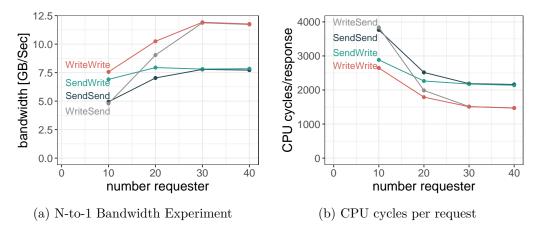

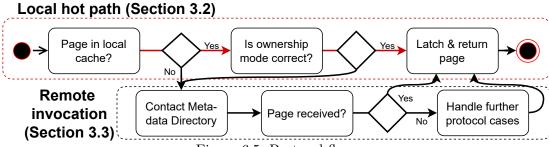

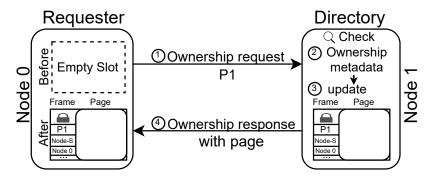

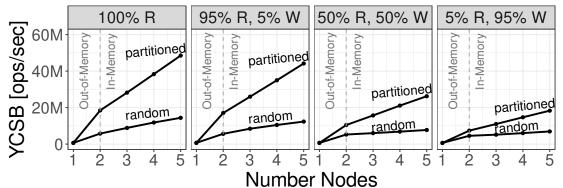

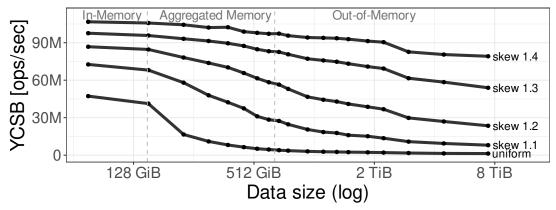

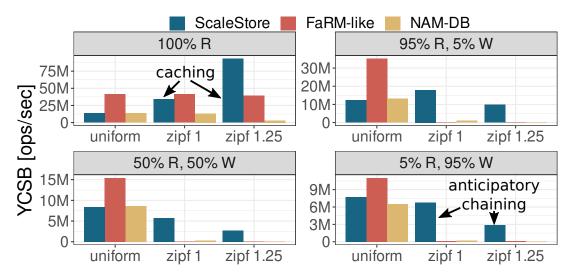

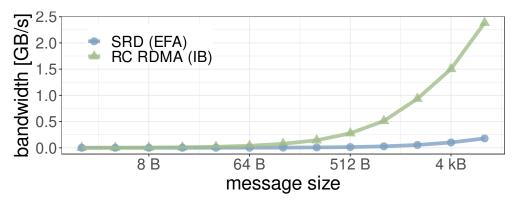

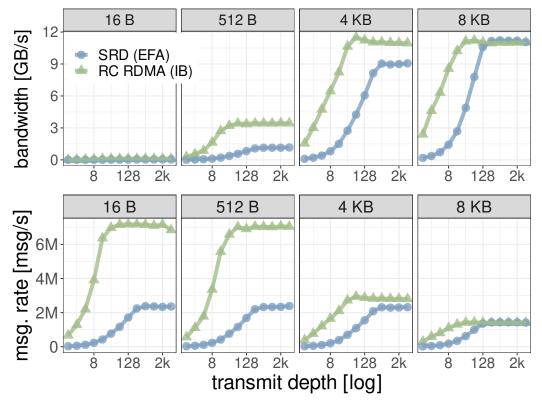

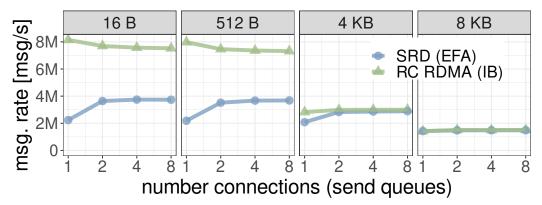

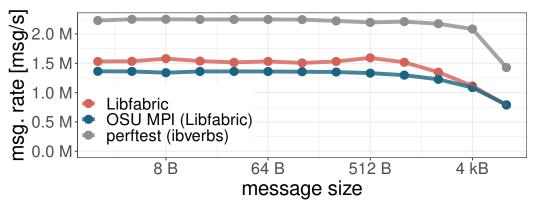

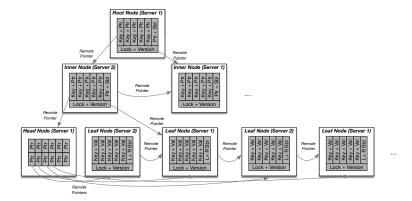

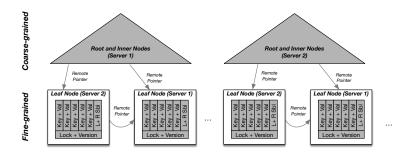

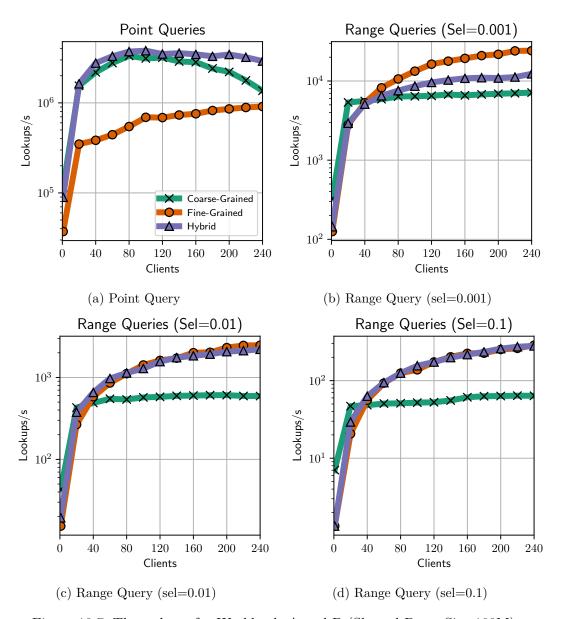

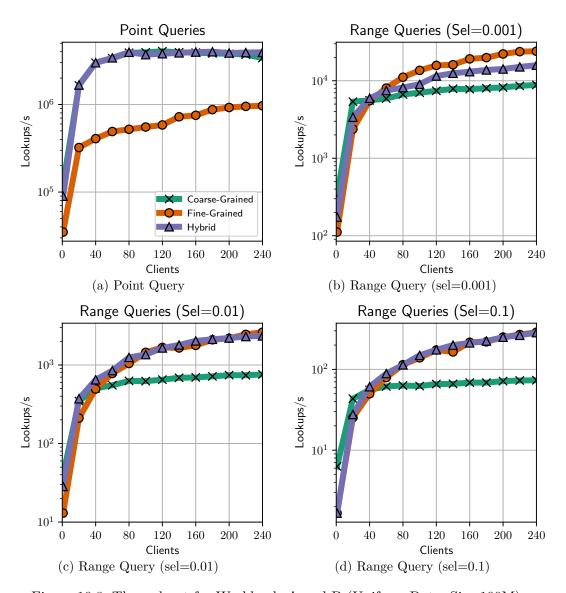

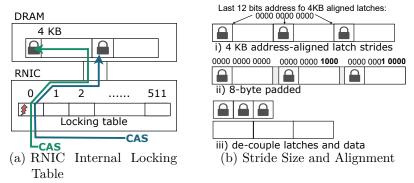

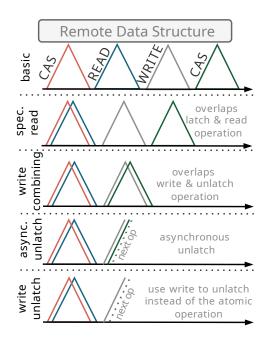

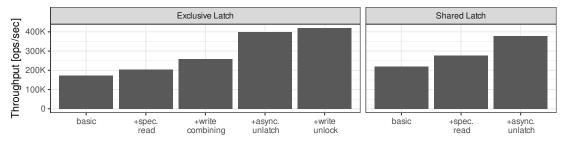

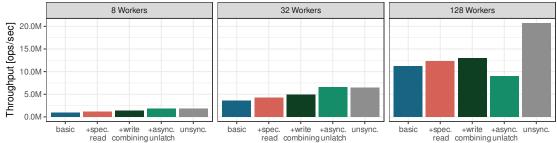

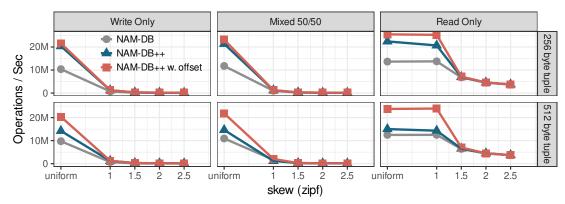

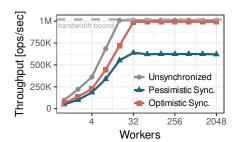

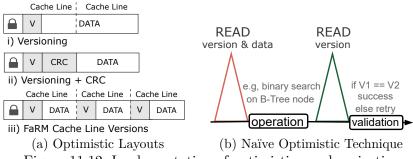

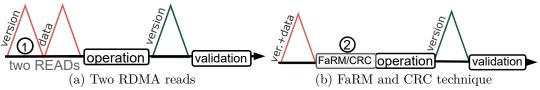

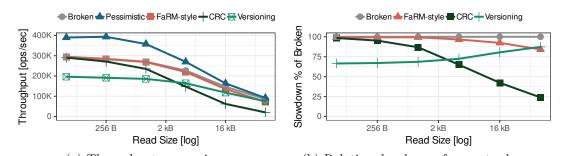

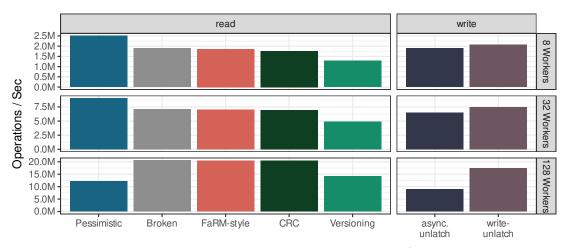

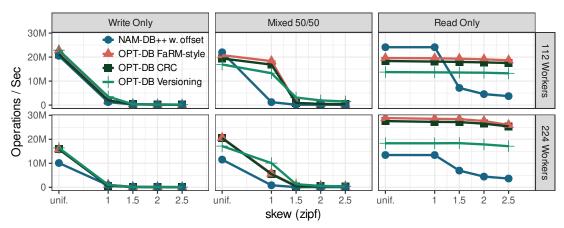

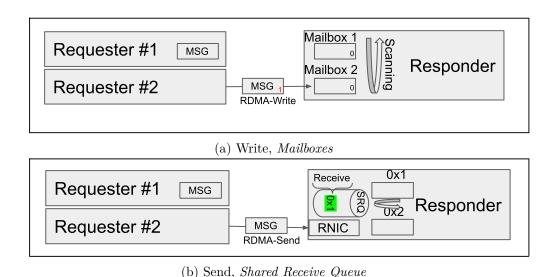

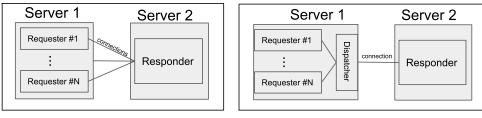

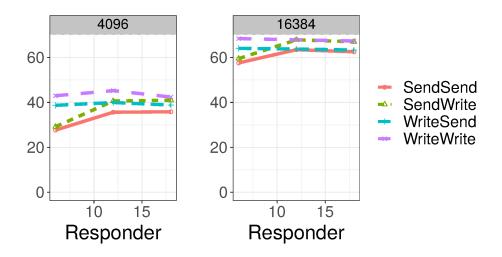

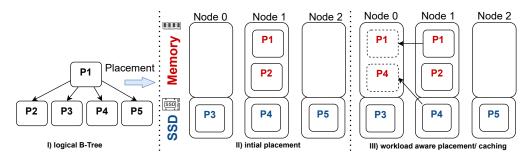

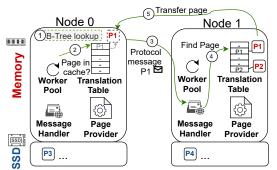

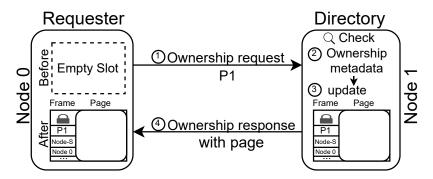

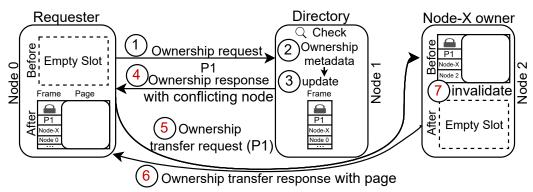

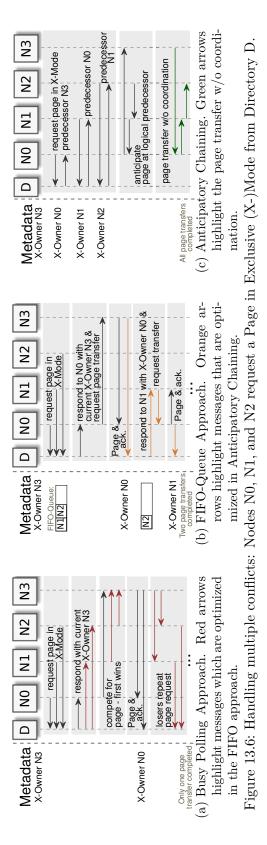

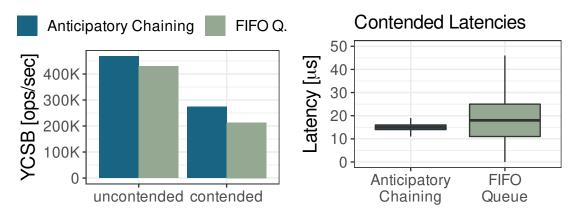

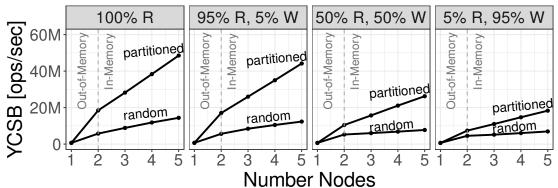

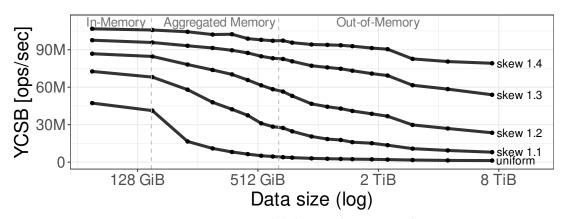

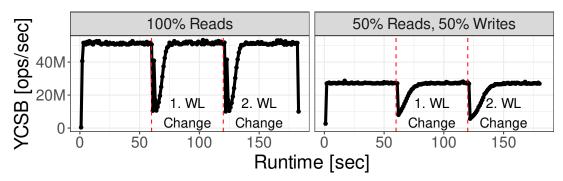

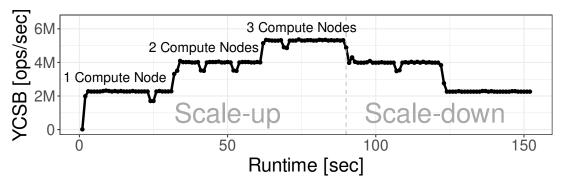

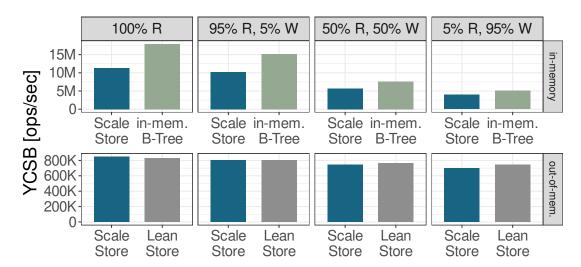

$<sup>{1\</sup>atop {\tt https://blogs.gartner.com/merv-adrian/2022/04/16/dbms-market-transformation-2021-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the-big-picture/2022-the$