# Effect of relative humidity and temperature on the stability of DNTT transistors

Za'aba, Nor; Morrison, John J.; Taylor, David

## **Organic Electronics**

DOI: 10.1016/j.orgel.2017.03.002

Published: 01/06/2017

Peer reviewed version

Cyswllt i'r cyhoeddiad / Link to publication

Dyfyniad o'r fersiwn a gyhoeddwyd / Citation for published version (APA): Za'aba, N., Morrison, J. J., & Taylor, D. (2017). Effect of relative humidity and temperature on the stability of DNTT transistors: A density of states investigation. Organic Electronics, 45, 174-181. https://doi.org/10.1016/j.orgel.2017.03.002

Hawliau Cyffredinol / General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

· Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Effect of Relative Humidity and Temperature on the Stability of DNTT Transistors: A Density of States Investigation

Nor K. Za'aba<sup>1</sup>, John J. Morrison<sup>2</sup> and D. Martin Taylor<sup>1,\*</sup>

<sup>1</sup>School of Electronic Engineering, Bangor University, Dean Street, Bangor, Gwynedd LL57 1UT, UK

<sup>2</sup>Department of Chemistry, University of Manchester, Oxford Road, Manchester M13 9PL, UK \*Email: d.m.taylor@bangor.ac.uk

### Abstract

Exposure to moisture and elevated temperatures usually results in significant degradation of organic thin film transistor (OTFT) performance. Typical observations include reduced mobility, unstable threshold voltage and the appearance of hysteresis in electrical characteristics. In this contribution we investigate the effects of environmental conditions on OTFTs based on DNTT, a high-mobility, small-molecule, organic semiconductor, with polystyrene (PS) as the gate insulator. Device characteristics were measured after consecutive 30-minute exposures to a relative humidity (RH) that was gradually increased from 20% to 80% with temperature fixed at 20°C and for temperatures increasing from 20°C to 90°C with RH held at 10%. Despite significant negative shifts in turn-on and threshold voltages, only slight changes in the hole mobility were observed at the highest RH and temperature. The DNTT density of states (DoS) extracted from transfer characteristics in the linear regime using the Grünewald approach showed little change with environmental conditions. In all cases, the DoS decreased from ~1 x  $10^{20}$  down to ~1 x  $10^{17}$ cm<sup>-3</sup> eV<sup>-1</sup> in the 0.45 eV energy range above the hole mobility edge. Some evidence was obtained for a weak trap feature between  $\sim 0.25$  and 0.35 eV above the mobility edge. These results confirm the high stability of DNTT as a semiconducting material and that OTFT instability observed here is associated almost entirely with a flatband voltage shift caused by hole trapping in the polystyrene gate dielectric or at the polystyrene/DNTT interface.

Key Words: OTFT, DNTT, Density of States, Environmental Effects

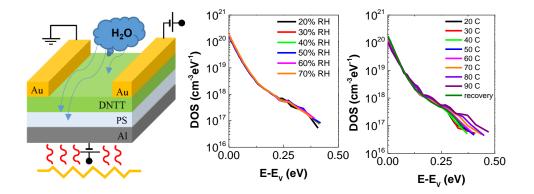

# **Graphical Abstract:**

# **Highlights:**

- Effect of relative humidity and temperature on DNTT transistors.

- Grünewald approach used to determine DNTT Density of States (DoS).

- DoS insensitive to relative humidity.

- Slight increase in DoS ~0.3 eV above mobility edge with increasing temperature.

- Instability in  $V_{ON}$  and  $V_T$  associated with hole trapping in the gate insulator.

#### **1. Introduction**

Recent reports have demonstrated that organic thin film transistors (TFTs) based on the fused heteroarene small molecule dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) meet performance criteria required for application in electronic circuits [1-7]. Carrier mobility is comparable to amorphous silicon, typically  $\mu \sim 1 \text{ cm}^2/\text{Vs}$ , and higher than that of pentacene films, turn-on voltage is close to zero and on-off ratio exceeds 10<sup>6</sup>. Importantly, DNTT is more resistant to oxidation by atmospheric oxygen than pentacene due to its higher ionization potential [1,2]. Taking these factors together, DNTT-based TFTs have the potential to make significant impact on the future development of large-area organic electronic circuits and considerable research effort has already been devoted to the development of functioning circuits [3,8,9] and improving OTFT performance by device engineering [9].

For practical applications, both material and operational stability are required. Not surprisingly, therefore, the effects of environmental factors on the electrical stability of organic TFTs have been extensively studied. Oxygen was recognized to be a reversible dopant of polythiophenes as long ago as 1991 [10]. Later, it was suggested that ozone played a role in shifting the onset voltage in polythiophene [11]. Previous reports [12,13] had highlighted the degrading effects of atmospheric moisture on a number of different organic semiconductors with high moisture levels resulting in significant deterioration in transistor performance [14]. Most recently, Risteska et al [15] studied the effects of oxygen and moisture on the bias stress effect in pentacene TFTs. They found that exposure to oxygen during bias stress gave rise to acceptor-like states while exposure to moisture gave rise to both acceptor- and donor-like states.

Absorbed moisture can induce charge traps either in the semiconductor or at the semiconductor/dielectric interface, causing deleterious changes in charge transport and/or threshold voltage. The field-effect mobility of several molecular organic semiconductors has been shown to decrease with increasing humidity [13]. However, this is not the case for DNTT-based TFTs. A recent study showed that moisture led to negative shifts of threshold and turn-on voltages, and an increase in off-current [16]. The measured mobility appeared to be unaffected. The observed changes were ascribed to charged states either at the insulator-semiconductor interface or in the semiconductor itself. In either case, measurement of the semiconductor density of states (DoS) should provide evidence for the presence of any new, moisture-related states.

Measuring the DoS in organic semiconductors has been important for understanding the nature of carrier transport phenomena in these materials and several methods have been suggested

for extracting the DoS from TFT transfer characteristics. In a comparative study [17], Kalb and Batlogg analysed and discussed the advantages and drawbacks of the various methods. Some require measurements to be made over a range of temperatures but also require knowledge of the temperature dependence of the band mobility for accurate results. Other approaches assume a fixed width for the accumulation channel, which can lead to significant errors. A simple approach is one introduced by Grünewald et al [18] in which the form of the DoS relative to the Fermi level is extracted from a single transfer characteristic measured in the linear regime of operation. No assumption is made about the form of the DoS, although Boltzmann rather than Fermi-Dirac statistics are used to describe the dependence of transistor current on the gate induced potential within the semiconductor. Errors associated with this assumption will be negligible until the Fermi level approaches the mobility/band edge. The method, therefore, provides a useful tool for investigating trends caused by external agencies including process variables. It has been adopted for both inorganic [19,20] and organic [21-24] semiconductors. It is based on relating the gateinduced incremental increases in device current to the band-bending resulting from the accumulation of charge carriers at the semiconductor/insulator interface. Importantly, it does not rely on iterative fits of the transfer curve with a gradually optimized, pre-determined form for the DoS. Such an approach can be time-consuming and can lead to ambiguous results owing to the insensitivity of the transfer plot to any fine detail in the DoS [18].

While many studies involving the DoS in pentacene [22,23,25-27] and other small molecules have been reported [24], to date little attention has been given to the DoS in DNTT. In one report [25], the computer model developed by Oberhoff et al [26] was applied to transfer characteristics obtained from DNTT single crystal devices. More recently, Yogev et al [28] derived the DoS from changes in contact potential difference between the tip of a scanning Kelvin probe microscope (SKPM) and the semiconductor surface on changing the gate voltage in a thin film DNTT transistor. In the present contribution, we extend measurements to evaporated DNTT thin film transistors exposed to a range of relative humidities ( $20\% \le RH \le 80\%$ ) and temperatures ( $10^{\circ}C \le T \le 90^{\circ}C$ ) and use the Grünewald et al [18] approach to extract the DoS under the various conditions.

#### 2. Experimental

As previously reported [7] DNTT was synthesised following a published route [29] from 2-naphthaldehyde with an overall yield of 35%. The iodine-catalysed ring closure was followed by two recrystallisations from o-dichlorobenzene, yielding yellow microcrystals of high purity DNTT.

Full details of the purification steps are given in section S.1 of the Supplementary Information. Polystyrene (PS),  $M_W = 350,000$ , for the gate insulator was purchased from Sigma Aldrich and used without further purification.

Bottom-gate top-contact TFTs were fabricated using our previously reported 90-device arrays [6] following procedures reported in [7]. Briefly, a ~1.0  $\mu$ m thick film of polystyrene was spin-coated from 8 wt% toluene solution onto aluminium gate electrodes previously evaporated through a shadow mask onto a polyethylene naphthalate (PEN) substrate. After heating for 10 mins at 100°C to remove residual solvent, the substrate was moved into an evaporator for deposition of a DNTT film ~70 nm thick with the substrate held at room temperature. Topographical AFM images of our DNTT films on polystyrene were indistinguishable from those presented in an earlier report [7] and show grain sizes in the range 50 – 500 nm. Without breaking the vacuum, gold source/drain electrodes were evaporated through a shadow mask to define the channel dimensions. In the measurements reported here, transistors had a channel width W = 2 mm with channel length, *L*, either 150 µm or 200 µm.

Test devices were placed in an artificial climate chamber (CLIMACELL) set to a RH in the range 10% to 80% and temperatures between 20°C and 90°C. Prior to each measurement, the test device was held at the set conditions for 30 minutes to come into equilibrium with the test environment. Transistor characteristics were obtained using a Keithley source/measure unit (model 2636B).

#### 3. Results and Discussion

#### 3.1 Effect of Relative Humidity

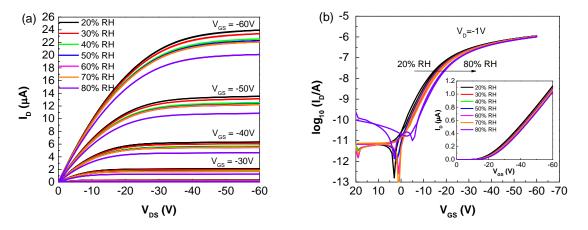

To investigate the effect of RH the test device was held at 20°C while RH was incremented in 10% steps from 20% to 80%. Figure 1(a) shows the output characteristics obtained for both the forward (0 to -60 V) and reverse sweeps of drain voltage,  $V_{DS}$ . The linear increase in device current,  $I_D$ , at low  $V_{DS}$  follows the predicted behaviour for the linear regime,  $V_{DS} < (V_{GS} - V_T)$ , that is

$$I_D = \frac{W}{L} \mu C_i (V_{GS} - V_T) V_{DS}$$

<sup>(1)</sup>

where,  $\mu$  is the carrier mobility,  $C_i$  the capacitance per unit area of the gate dielectric and  $V_{GS}$  the gate voltage. At higher  $V_{DS}$  clear saturation occurs and on reducing  $V_{DS}$  no hysteresis was observed between forward and reverse sweeps at any RH. The corresponding transfer characteristics are given in Figure 1(b). Again little hysteresis was observed between forward and reverse sweeps of the gate voltage. The only other notable feature in the transfer plots is the rapid increase in off-

current as RH increases above 70% due to parasitic currents through water films on the device surface and/or increased gate leakage current. At lower RH the off-currents were determined by the displacement current of a few pA charging the gate capacitance.

The transfer data obtained during the forward sweep (+20 V to -60 V) are replotted using linear scales in the inset of Figure 1(b). Based on equation (1) and a measured  $C_i = 2.37$  nF/cm<sup>2</sup>, the slope of the linear section of such plots yields the carrier mobility while extrapolation to the  $V_{GS}$  axis yields  $V_T$ . These are given in Table 1 for the different values of RH, together with  $V_{ON}$ , subthreshold slope, SS, and on-off ratio extracted from the main plot in Figure 1(b). The reduction of ~16% in  $I_D$  seen in Figure 1(a) as RH increased is now seen to have arisen almost entirely from the shifts in  $V_{ON}$  and  $V_T$  as reported in [16]. The contribution from the reduction in mobility is only ~1%. The on-off ratio, defined here as the ratio of the current flowing at  $V_{GS} = -60$  V to that at  $V_{ON}$ , is significantly affected by the rapidly increasing off-current at the highest humidity. This same high off-current also results in an overestimate of the negative shift in  $V_{ON}$ . The relatively high values of SS (3.7 to 4.1 V/decade) are mainly the consequence of the relatively thick and hence low  $C_i$  gate dielectric used in our OTFTs. Simple scaling to the much thinner C<sub>14</sub>-phosphonic acid treated AlO<sub>x</sub> ( $C_i = 800$  nF/cm<sup>2</sup>) used by Zschieschang et al [30] in their DNTT transistors would result in an SS ~12 mV/decade compared with 90 mV/decade reported by these authors.

**Figure 1.** Effect of increasing relative humidity at 20°C on (a) output and (b) transfer characteristics of a DNTT TFT (W = 2 mm,  $L = 150 \text{ }\mu\text{m}$ ) with polystyrene gate insulator. The transfer plots were obtained in the linear regime with drain voltage,  $V_{DS} = -1\text{V}$ . The inset in (b) shows the data for the forward sweep (+20V to -60V) plotted on linear axes.

| RH                              | 20%                 | 30%                 | 40%                 | 50%                 | 60%                 | 70%                 | 80%                  |

|---------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|

| $\mu$ (cm <sup>2</sup> /V.s)    | 0.95                | 0.95                | 0.95                | 0.95                | 0.94                | 0.94                | 0. 94                |

|                                 | (0.94)              | (0.93)              | (0.93)              | (0.93)              | (0.93)              | (0.93)              | (0.94)               |

| $V_{ON}\left(\mathbf{V}\right)$ | 3                   | 2                   | 2                   | 2                   | 1                   | 1                   | -6                   |

|                                 | (0)                 | (0)                 | (-1)                | (-1)                | (-2)                | (-5)                | (-6)                 |

| $V_T(\mathbf{V})$               | -22                 | -23                 | -23                 | -24                 | -24                 | -24                 | -26                  |

|                                 | (-24)               | (-24)               | (-25)               | (-25)               | (-25)               | (-25)               | (-25)                |

| Ion/Ioff                        | $1.8 \times 10^5$   | $1.7 \times 10^5$   | $1.7 \times 10^5$   | $1.7 \times 10^5$   | $1.7 \times 10^{5}$ | $1.6 \times 10^5$   | $1.5 \text{ x} 10^4$ |

|                                 | $(1.6 \times 10^5)$ | $(1.6 \times 10^5)$ | $(1.6 \times 10^5)$ | $(1.6 \times 10^5)$ | $(1.7 \times 10^5)$ | $(5.8 \times 10^4)$ | $(1.6 \times 10^4)$  |

| SS (V/decade)                   | 3.67                | 3.71                | 3.75                | 3.83                | 3.85                | 3.92                | 4.09                 |

|                                 | (3.56)              | (3.65)              | (3.71)              | (3.72)              | (3.84)              | (3.91)              | (3.90)               |

**Table 1** Device parameters extracted from the transfer characteristics measured with  $V_D = -1$ V, T = 20°C and RH increasing from 20% to 80%. The values in brackets are for decreasing RH.

When RH was reduced back to 20% in stages over a period of 3 hours, device characteristics remained well-behaved but only partial recovery occurred. For decreasing RH, the output and transfer characteristics corresponding to Figure 1 are given in Figure S1 in the Supplementary Information with extracted parameter values appearing in brackets in Table 1. While mobility remained virtually unchanged throughout the RH cycle, long-term shifts occurred in  $V_{ON}$  and  $V_T$ . Transfer plots measured after returning to the initial conditions show a translation of around -2.5 V along the V<sub>GS</sub> axis while maintaining the same profile. This is readily explained by a shift,  $\Delta V_{FB}$ , in the flatband voltage arising from hole trapping in the PS film or at the PS/DNTT interface. For an <u>effective</u> interface trapped charge density  $Q_{it}$ , which includes also the influence of charges in the insulator,  $\Delta V_{FB} = -Q_{it}/C_i$ . Thus a -2.5 V shift in the post-RH exposure transfer plots corresponds to an effective hole density of ~3.7 x 10<sup>10</sup> cm<sup>-2</sup> trapped on water-related states.

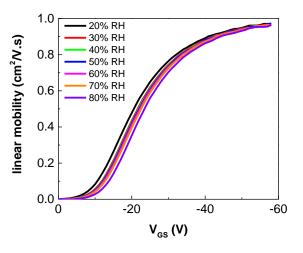

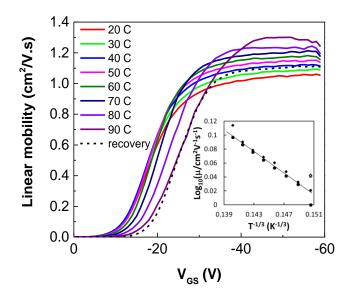

The relative constancy of mobility and subthreshold slope are mirrored in Figure 2, where the gate-voltage dependent mobility, extracted from the local slope of the transfer characteristics using the relation

$$\mu = \frac{L}{WC_i V_{DS}} \frac{\partial I_D}{\partial V_{GS}},\tag{2}$$

is plotted as a function of gate voltage for increasing values of RH. The rate of mobility increase and the final values reached, which correspond to those extracted using equation (1) and given in Table 1, show only slight reductions over the RH range. The main effect of increasing RH, therefore, is a systematic shift of the transfer plot to negative voltages which, as indicated above, is caused by additional hole trapping at water-related defects at the PS/DNTT interface or in the bulk PS. Such defects will not contribute to the semiconductor DoS.

**Figure 2.** Gate-voltage-dependent mobility extracted by applying equation (2) to transfer characteristics obtained in the linear regime.

#### 3.2 Effect of Temperature

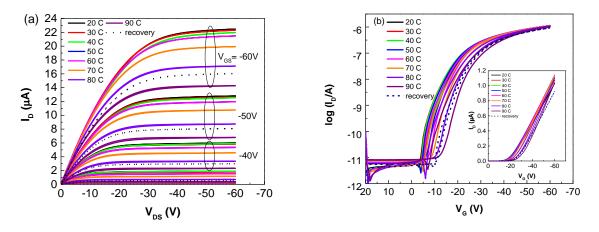

To investigate the effect of temperature, RH was held constant at 10% while temperature was increased from 20°C to 90°C. As before, measurements were made 30 minutes after attaining the new conditions. On the timescale of the measurements, the output characteristics given in Figure 3(a) were stable, showing no hysteresis between forward and reverse voltage sweeps. The transfer characteristics in Figure 3(b) again show that the decreasing currents at higher temperatures were caused by shifts in  $V_{ON}$  and  $V_T$  to more negative values. As seen from the dash plots in Figure 3, even after holding the device open-circuited overnight at 20°C and 10% RH very little recovery occurred.

Device parameters extracted from the transfer plots in Figure 3 are given in Table 2. As before, mobility and threshold voltages were extracted using equation (1), but now with a measured  $C_i = 2.54 \text{ nF/cm}^2$ , to the linear sections of the transfer characteristics shown in the inset of Figure 3(b). As temperature increased up to 90°C, mobility increased slightly from 1.00 to 1.25 cm<sup>2</sup>/Vs. The shifts in  $V_{ON}$ ,  $V_T$  and SS are similar to the changes caused by increasing RH. On-off current ratios remain ~10<sup>5</sup> at all temperatures. The only significant change observed after conditioning of the device overnight at 20°C and RH=10% was a reduction of the mobility almost to its previous room temperature value and a reduction in the subthreshold slope below its initial value, both of which would be consistent with slight improvements in the morphology of the DNTT layer.

**Figure 3.** Effect of increasing temperature at RH = 10% on (a) output and (b) transfer ( $V_{DS}$  = -1 V) characteristics of a DNTT TFT (W = 2mm, L = 200 µm) with polystyrene gate insulator. The inset in (b) shows the data from the main figure obtained during the forward voltage sweep (+20 V to - 60 V) replotted on a linear scale. The dashed plots were obtained after holding the device at 20°C and 10% RH overnight.

**Table 2** Device parameters extracted from the transfer characteristics in Figure 3(b) obtained during the forward voltage sweep with temperature increasing from 20°C to 90°C, RH = 10% and  $V_{DS} = -1V$ . Values in the final column were obtained subsequently at 20°C after holding the device overnight at 20°C and 10% RH.

| Temperature                       | 20 °C                | 30 °C                | 40 °C                | 50 °C              | 60 °C                | 70 °C                | 80 °C              | 90 °C              | 20 °C              |

|-----------------------------------|----------------------|----------------------|----------------------|--------------------|----------------------|----------------------|--------------------|--------------------|--------------------|

| $\mu (\text{cm}^2/\text{V.s})$    | 1.00                 | 1.07                 | 1.10                 | 1.13               | 1.16                 | 1.19                 | 1.22               | 1.25               | 1.10               |

| $V_{ON}(\mathbf{V})$              | -3                   | -3                   | -4                   | -4                 | -5                   | -5                   | -6                 | -7                 | -10                |

| $V_{T}(\mathbf{V})$               | -18                  | -20                  | -21                  | -21                | -21                  | -23                  | -24                | -27                | -27                |

| I <sub>on</sub> /I <sub>off</sub> | 2.18x10 <sup>5</sup> | 2.33x10 <sup>5</sup> | 2.38x10 <sup>5</sup> | $2.47 \times 10^5$ | 2.50x10 <sup>5</sup> | 2.33x10 <sup>5</sup> | $2.03 \times 10^5$ | $1.65 \times 10^5$ | $2.00 \times 10^5$ |

| SS                                | 4.19                 | 4.10                 | 4.15                 | 4.22               | 4.41                 | 4.37                 | 4.40               | 4.62               | 3.53               |

| (V/decade)                        |                      |                      |                      |                    |                      |                      |                    |                    |                    |

The post-heating transfer characteristic at 20°C shows a displacement of about -8 V from the original plots, corresponding to an effective interface trapped hole density of ~9 x  $10^{10}$  cm<sup>-2</sup> arising from heating the device to 90°C.

Figure 4 shows the gate-voltage dependence of the mobility, extracted by applying equation (2) to the forward sweep of each gate-voltage cycle in Figure 3(b). The initial rate of rise is similar at all temperatures albeit that the plots are shifted to more negative values consistent with a shift in flat-band voltage. As seen in the inset to Figure 4, the mobility saturates at values consistent with

those given in Table 2. Interestingly, and not unexpectedly for transport through an accumulation layer, the temperature dependence fits the model for hopping conduction in a 2-dimensional sheet [31] i.e.  $\mu = \mu_0 \exp((T_0/T)^{1/3})$  with  $T_0 = 288$  K. Since the mobility measured subsequently at 20°C is slightly higher than measured initially, we assume that this is linked to the higher than expected increase in mobility that occurred at ~90°C, which may be the result of morphological changes induced in the DNTT by increased molecular motion in the polystyrene which has a glass transition temperature at ~100°C.

**Figure 4** Gate-voltage-dependent mobility extracted by applying equation (2) to the transfer characteristics obtained for increasing temperatures during the forward voltage sweep (+20 V to - 60 V) together with the post-heating plot at 20°C (dotted curve). The inset shows the temperature dependence of the mobility from Table 2 (dots) and values corresponding to  $V_{GS} = -50V$  in the main figure (diamonds). The open data points were obtained at 20°C post-heating.

#### 3.3 Density of States

The Grünewald et al model [18] for extracting the DoS from the transfer characteristic of a thin film transistor assumes that  $V_{ON}$  corresponds to the flatband condition at the semiconductor/insulator interface. In the absence of parasitic effects the corresponding current,  $I_O$ , then measured is the true off-current flowing between source and drain through the bulk semiconductor. The model further assumes that the transfer characteristic reflects the accumulation of charge carriers at the semiconductor/insulator interface. Trapped insulator and interface charges are accounted for by a flatband voltage shift. Implicit in the approach is that the semiconductor is

not doped, thereby avoiding complicating features that would arise from the need to consider the effect of a conventional depletion region on the subthreshold slope. In the latter case, for example, the measured  $V_{ON}$  and  $I_O$  may not correspond to the flatband condition.

Distortion of the transfer characteristic caused by a gated Schottky contact [32] at low  $V_{GS}$  and series resistances at the source and drain at higher  $V_{GS}$  [33] will also lead to erroneous values for the DoS. No evidence for the last two effects is present in the transfer or mobility data presented here. This is confirmed also by the well-behaved increases in the slopes of the linear sections of the output characteristics at low  $V_{DS}$  when  $V_{GS}$  increases. Furthermore, in a previous report [7], we have shown that the mobility extracted from PS/DNTT transistors such as those investigated here is independent of channel length in the range 50 – 200 µm. Both the linear and saturation regimes yielded values ~ 1 cm<sup>2</sup>/Vs as seen here. Therefore, we may safely ignore contact effects in our DoS calculations.

Within the above framework, and assuming Boltzmann statistics apply, the dependence of device current on gate voltage is written as

$$I_D(V_F) = I_{OFF} \frac{1}{l} \int_0^l e^{\beta V(x)} dx$$

(3)

where  $V_F = (V_{GS}-V_{ON})$ , *l* the thickness of the semiconductor, V(x) the potential profile through the accumulation channel measured relative to that deep into the semiconductor and  $\beta = q/kT$  with *q* the electronic charge, *k* Boltzmann's constant and *T* the absolute temperature. The Poisson equation

$$\frac{d^2 V(x)}{dx^2} = -\frac{q p(V(x)))}{\varepsilon_s \varepsilon_0}$$

(4)

where p(V(x)) is the concentration of accumulated holes at distance *x* from the interface,  $\varepsilon_S$  the relative permittivity of the semiconductor and  $\varepsilon_0$  the permittivity of free space, is then solved subject to appropriate boundary conditions. This leads to an expression relating the interface potential,  $V_0$ , to  $V_F$ , namely

$$\exp(\beta V_0) + \beta V_0 - 1 = \beta \frac{C_i l}{\varepsilon_s \varepsilon_0 I_0} \left[ V_F I(V_F) - \int_0^{V_F} I(\tilde{V_F}) d\tilde{V_F} \right].$$

(5)

The right hand side of equation (5) may be calculated numerically from the experimental transfer characteristic. With suitable choice of units for  $\beta$ , the dependence of  $V_0$  (in eV) on  $V_F$  is then determined. Following further manipulation, the total hole density  $p(V_0)$  may be obtained from

$$p(V_0) = \frac{C_i^2}{\varepsilon_s \varepsilon_0 q^2} V_F \left(\frac{dV_0}{dV_F}\right)^{-1} .$$

(6)

Assuming the zero Kelvin approximation for the Fermi function, Kalb [34] shows that the density of states N(E) may be extracted from

$$N(E) \approx \frac{dp(V_0)}{dV_0}.$$

(7)

It will be immediately obvious from the need to undertake two numerical differentiating steps in equations (6) and (7) that any extraneous noise in the transfer characteristic will be amplified significantly. Accordingly, limited smoothing was undertaken by utilizing values at  $V_{GS}+\delta V$  and  $V_{GS}-\delta V$  for effecting the differentiation at  $V_{GS}$ , where  $\delta V$  represents the sweep voltage step size (= 1 V).

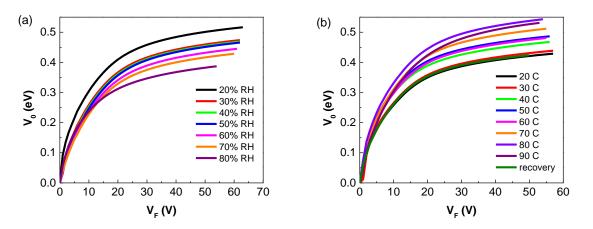

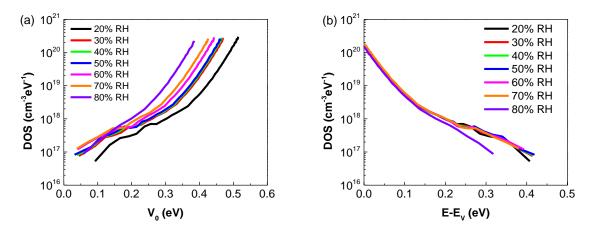

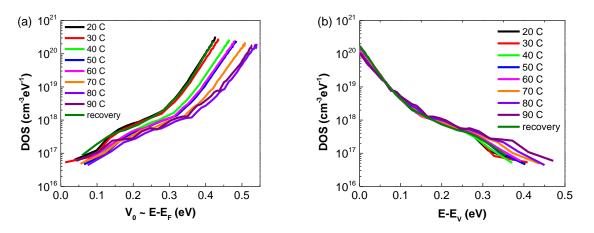

Plots of  $V_0$  versus  $V_F$  obtained using the procedure outlined above are given in Figure 5 showing the effect of (a) RH and (b) temperature. As RH increases, the plots of  $V_0$  rise more slowly with  $V_F$ . Increasing temperature has the opposite effect with  $V_0$  rising more rapidly. Using these plots together with equations (6) and (7), allows the DoS to be calculated as a function of  $V_0$  (=  $E - E_F$ ). The profiles for different RH appear in Figure 6(a) and for different temperatures in Figure 7(a).

Figure 5 Plots of  $V_0$  versus  $V_F$  showing the effect of (a) relative humidity and (b) temperature.

**Figure 6** Density of states for different values of RH plotted relative to (a)  $V_0$  (=*E*-*E*<sub>*F*</sub>) and (b) the mobility edge assumed to coincide with ~*E*<sub>*V*</sub>.

**Figure 7** Density of states for different values of temperature plotted relative to (a)  $V_0 (=E-E_F)$  and (b) the mobility edge assumed to coincide with  $E_V$ .

Ideally, we wish to plot the DoS relative to the valence band edge,  $E_V$ . For CuSCN [20] and a small molecule/polymer blend [24], a sharp rise was observed in the DoS at high  $V_0$  attributed to a band edge. Except in a very small number of plots, we do not see such a rise.  $V_0$  vs  $V_F$  plots continue to rise steadily. However, a sharp rise in DoS at high  $V_0$  in [20] and [24] implies saturation of the  $V_0$  vs  $V_F$  plot. It is readily shown from equation (5) that if the carrier mobility becomes constant and equation (1) applies, then such a plot never saturates (see section S.3 in Supplementary Information). Rather, it continues to rise following the relation

$$\beta V_0 = \ln \alpha_1 \left( V_F^2 + \alpha_2 \right) \tag{8}$$

where  $\alpha_1$  and  $\alpha_2$  are constants determined by device and materials parameters and in the case of  $\alpha_2$  also dependent on the form of the transfer curve in the subthreshold region. To obviate the need to identify the location of  $E_F$  in the bandgap, some authors simply assume a value for ( $E_F$ - $E_V$ ) e.g. ~0.5 eV in pentacene [17].

In the present case, values of  $V_{GS}$ , and hence  $V_F$  and  $V_O$ , can be identified at which the effective mobility becomes constant at ~1 cm<sup>2</sup>/Vs. We now assume that this occurs at a mobility shoulder coinciding with a transport band edge [23,35] ( $E_V$  in the case of a p-type semiconductor). Our method for determining the mobility edge is shown in section S.4 in the Supplementary Information. Upon evaluating the relevant energy, the DoS may be replotted as a function of (E- $E_V$ ).

In Figure 6(b) we see that the effect of RH on the DoS is minimal with the plots obtained for all relative humidities coalescing to a single curve over most of the range. (The departure from the general trend seen at 80% RH arises from the effect of the parasitic leakage current on the transfer characteristic at low device currents). Over the initial 0.1 eV above  $E_V$ , the DoS decreases exponentially from ~10<sup>20</sup> cm<sup>-3</sup>eV<sup>-1</sup> with a characteristic energy ~0.027 eV. Thereafter the DoS shows a broad, weak feature before decreasing to ~10<sup>17</sup> cm<sup>-3</sup>eV<sup>-1</sup> at ~0.4 eV above  $E_V$ . The plots for different temperatures (Figure7(b)) also coalesce to a common curve over most of the range, decreasing from ~10<sup>20</sup> cm<sup>-3</sup>eV<sup>-1</sup> with similar initial characteristic energy. These plots, however, show a slight increase in deeper states at higher temperatures, which eventually mask the weak feature lying between ~0.25 and ~0.35 eV above  $E_V$ .

A feature with similar energy (0.28 eV above the mobility edge) was observed in pentacene [36] and attributed to oxygen related defects. A sharp peak, even higher than in thin film pentacene, was observed in the DoS of rubrene single crystals when exposed to oxygen and light [37]. This could be expected based on the lower ionization potential of rubrene, ~4.75 eV [38] compared with that of pentacene, ~5.0 eV [2]. The ionization potential of DNTT (~5.4 eV [28]) is significantly higher than that of pentacene, so the concentration of any oxidation-related species in DNTT is expected to be lower. This is consistent with a peak amplitude here of ~2 x  $10^{17}$  cm<sup>-3</sup>eV<sup>-1</sup> above the background, which is significantly lower than observed in pentacene [23, 36]. While oxidation of the sulphur atoms to disulphones is possible in DNTT, this requires exposure to strong oxidizing agents. In the unlikely event that oxidized forms of DNTT were produced as by-products of synthesis, these would be more soluble than the parent molecule in dichlorobenzene and would be removed during recrystallization. Without further detailed studies, we do not believe that the weak feature in DNTT can be attributed to an oxidation product of DNTT.

Another possible reason given for a peak in the DoS of organic semiconductors is a packing mismatch due to the presence of isomers. For example, in 2,8-difluoro-5,11bis(triethylsilylethynyl) anthradithiophene (diF-TES ADT), a mixture of sys- and anti-isomers gave rise to strong peaks in the DoS at ~0.4 eV above the valence band [39]. The molecular structure of DNTT does not allow for this possibility.

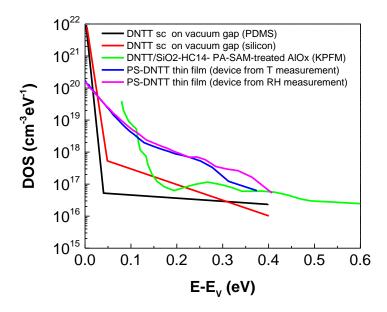

In Figure 8 we compare the DoS obtained here with those obtained (a) by applying the Oberhoff computer model to transistor characteristics of single-crystals of DNTT placed over vacuum gaps defined by PDMS or silicon spacers [25] and (b) by SKPM on thin film transistors formed from evaporated films of DNTT on SAM-treated AlOx [28].

Xie et al [25] modelled the transfer data from single-crystal DNTT transistors, assuming *a priori* that it followed a double exponential profile. The best fit DoS showed a rapid decrease from ~ $10^{22}$  cm<sup>-3</sup>eV<sup>-1</sup> to  $10^{18}$  cm<sup>-3</sup>eV<sup>-1</sup> followed by a slower decrease to below  $10^{17}$  cm<sup>-3</sup>eV<sup>-1</sup>. In their analysis of SKPM data from pentacene thin film transistors formed on HMDS-treated SiO<sub>2</sub>, Yogev et al [27] assume that the steep fall is the Gaussian tail of the occupied molecular orbitals. SKPM measurements by the same group on DNTT films evaporated onto SAM-modified AlO<sub>x</sub> [28] gave a similar profile to those reported by Xie et al [25] for single crystal DNTT but displaced by ~0.1 eV to deeper states (Figure 8). This probably reflects measurements made over a polycrystalline grain, thus excluding states related to traps at intergrain boundaries. We conclude therefore that, while the method seems appropriate, an unaccounted for systematic error is present in their estimate of the energy range of the DoS spectrum and possibly *E<sub>F</sub>*.

In our case, the DoS shows a more gradual decrease from ~ $10^{20}$  cm<sup>-3</sup>eV<sup>-1</sup> but asymptoting to the same concentration (~ $10^{17}$  cm<sup>-3</sup>eV<sup>-1</sup>) of deeper states seen in [28]. Since  $V_{ON}$ , in our case coincides with flatband conditions, we locate  $E_F$  for DNTT ~0.4 eV above  $E_V$  at room temperature but rising to ~ 0.5 eV at 90°C. Close to the mobility edge, the DoS rises above that determined in [28] by SKPM but remains lower than determined for single crystal DNTT by Xie et al [25]. This may be an intrinsic property arising from the very different quality of the DNTT in the two cases - single crystal versus polycrystalline. That the SKPM spectrum also reveals a weak feature similar to that seen in our DoS suggests that it may be due to an intrinsic property of the polycrystalline grains in DNTT rather than associated with the substrate dielectric – polystyrene in our case.

15

As indicated earlier, because the Grünewald approach uses the Boltzmann approximation when describing the current flow, this will introduce errors in our DoS when the Fermi level approaches within a few kT (~50 meV) of the mobility/valence band edge. It should be noted, however, when finally deconvoluting the DoS from the extracted carrier concentration the step-function approximation of the Fermi-Dirac distribution is used [34] thus minimizing this source of error. A small systematic error in state energy could also arise from our method for estimating the mobility edge. Additional sources of error could include incorrect estimation of the voltage, *V*<sub>ON</sub>, and/or current, *I*<sub>OFF</sub>, corresponding to the flatband condition. We have undertaken a sensitivity analysis to test this possibility (section S.4 in Supplementary Information). Within reasonable limits, we find that such errors would be small.

**Figure 8** Comparison of DoS spectra obtained in the present work using the Grünewald et al model with those obtained by applying the Oberhoff et al model to single-crystal DNTT [25] and from evaporated films using Scanning Kelvin Probe Microscopy [28].

### 4. Conclusions

In conclusion, we have undertaken a detailed study of the effect of relative humidity and temperature on the density of states in thin film transistors based on DNTT as the active layer and polystyrene as the gate insulator. Using the approach reported by Grünewald et al [18], we extract density of states spectra from transfer characteristics obtained in the linear regime. By assuming

that the onset of constant mobility coincides with the valence band edge, we show that the DoS in DNTT is insensitive to relative humidity in the range 10 - 70%, and in the absence of parasitic currents perhaps to even higher RH. We further show that, as temperature increases, the only change observed in the DoS is a slight increase in the deeper states lying more than ~0.3 eV above the mobility edge. The device instability that is observed, i.e. shifts in  $V_{ON}$  and  $V_T$ , may be ascribed almost entirely to flatband voltage shifts arising from hole trapping in the polystyrene dielectric or its interface with DNTT. Such traps do not form part of the manifold of energy states contributing to the DoS in DNTT. Finally we have identified a weak trap feature located ~0.25 to 0.35 eV above the mobility edge, the origin of which requires further investigation.

### Acknowledgements

NKZ wishes to thank MARA, Malaysia for the financial support under the Overseas Postgraduate Program.

#### References

1. U. Zschieschang, F. Ante, T. Yamamoto, K. Takimiya, H. Kuwabara, M. Ikeda, T. Sekitani, T. Someya, K. Kern, H. Klauk, Adv. Mater. 22 (2010) 982.

2. U. Zschieschang, F. Ante, D. Kälblein, T. Yamamoto, T. Kazuo, H. Kuwabara, M. Ikeda, T. Sekitani, T. Someya, J. Blochwitz- Nimoth, H. Klauk, Org. Electron. 12 (2011) 1370.

3. F. Ante, , D. Kälblein, T. Zaki, U. Zschieschang, K. Takimiya, M. Ikeda, T. Sekitani, T. Someya, J. N. Burghartz, K. Kern and H. Klauk, Small 8 (2012) 73.

4. G.A. Abbas, Z. Ding, H.E. Assender, J.J. Morrison, S.G. Yeates, E.R. Patchett, D.M. Taylor, Org. Electron 15 (2014) 1998.

5. D.M. Taylor, Semicond. Sci. Techn. 30 (2015) 054002.

6. E.R. Patchett, A. Williams, Z. Ding, G.A. Abbas, H.E. Assender, J.J. Morrison, S.G. Yeates, D.M. Taylor, Org. Electron. 15 (2014) 1493.

7. D.M. Taylor, E.R. Patchett, A. Williams, Z. Ding, H.E. Assender, J.J. Morrison, S.G. Yeates, Chem. Phys. 456 (2015) 85.

8. J.A. Avila-Niño, E.R. Patchett, D.M. Taylor, H.E. Assender, S.G. Yeates, Z. Ding, J.J. Morrison, Org. Electron. 31 (2016) 77.

9. A. Reuveny, S. Lee, T. Yokota, H. Fuketa, C.M. Siket, S. Lee, T. Sekitani, T. Sakurai, S. Bauer, T. Someya, Adv. Mater. 28 (2016) 3298.

10. D.M. Taylor, H. Gomes, A.E. Underhill, S. Edge, P.I. Clemenson, J. Phys D: Appl. Phys. 24 (1991) 2032.

11. M.L. Chabinyc, R.A. Street, J.E. Northrup, Appl. Phys. Lett. 90 (2007) 123508.

12. S. Hoshino, M. Yoshida, S. Uemura, T. Kodzasa, N. Takada, T. Kamata, K. Yase, J. Appl. Phys. 95 (2004) 5088.

13. M.L. Chabinyc, F. Endicott, B.D. Vogt, D.M. DeLongchamp, E.K. Lin, Y. Wu, P. Liu, B.S. Ong, Appl. Phys. Lett. 88 (2006) 113514.

14. D. Li, E.-J. Borkent, R. Nortrup, H. Moon, H. Katz and Z. Bao, Appl. Phys. Lett. 86 (2005) 042105.

15. A. Risteska, J. Bedolla, J.E. Northrup, W. Bergholz, V. Wagner, D. Knipp, Adv. Electron. Mater. 2 (2016) 1500179.

16. Z. Ding, G. Abbas, H.E. Assender, J.J. Morrison, S.G. Yeates, E.R. Patchett, D.M. Taylor, ACS Appl. Mater. Interf., 6 (2014) 15224.

17. W.L. Kalb, B. Batlogg, Phys. Rev. B 81 (2010) 035327.

- 18. M. Grünewald, P. Thomas, D. Würtz, Phys, Stat. Sol. 100 (1980) K139.

- 19. K. Weber, M. Grünewald, W. Fuhs, P. Thomas, Phys. Stat. Sol. B Basic Res. 110 (1982) 133.

- 20. P. Pattanasattayavong, A.D. Mottram, F. Yan, T.D. Anthopoulos, Adv. Funct. Mater. 25 (2015) 6802.

- 21. P.J. Diemer, Z.A. Lamport, Y. Mei, J.W. Ward, K.P. Goetz, W. Li, M.M. Payne, M. Guthold,

- J.E. Anthony, O.D. Jurchescu, Appl. Phys. Lett. 107 (2015) 103303.

- 22. W.L. Kalb, F. Meier, K. Mattenberger, B. Batlogg, Phys. Rev. B 76 (2007) 184112.

- 23. W.L. Kalb, S. Haas, C. Krellner, T. Mathis, B. Batlogg, Phys. Rev. B 81 (2010) 155315.

- 24. S. Hunter, A.D. Mottram, T.D. Anthopoulos, J. Appl. Phys. 120 (2016) 025502.

- 25. W. Xie, K. Willa, Y. Wu, R. Häusermann, K. Takimiya, B. Batlogg, C.D. Frisbie, Adv. Mater. 25 (2013) 3478.

- 26. D. Oberhoff, K.P. Pernstich, D.J. Gundlach, B. Batlogg, IEEE Trans. Electron Dev. 54 (2007)17.

- 27. S. Yogev, E. Halpern, R. Matsubara, M. Nakamura, Y. Rosenwaks, Phys. Rev. B 84 (2011) 165124.

- 28. S. Yogev, R. Matsubara, M. Nakamura, U. Zschieschang, H. Klauk, Y. Rosenwaks, Phys. Rev. Lett. 110 (2013) 036803.

- 29. T. Yamamoto, K. Takimiya, JACS 129 (2007) 2244.

- 30. U. Zschieschang and H. Klauk, Org. Electron. 25 (2015) 340.

- 31. N. Lustig and W.E. Howard, Sol. St. Comms. 72 (1989) 59.

- 32. E.G. Bittle, J.I. Basham, T.N. Jackson, O.D. Jurchescu, D. Gundlach, Nature Comms. 7 (2016) 10908.

- 33. M.M. Ibrahim, A.C. Maciel, C.P. Watson, M.-B. Madec, S.G. Yeates, D.M. Taylor, Org. Electron. 11 (2010) 1234.

- 34. W.L. Kalb, Trap States in Organic Field-effect Transistors: Quantification, Identification and Elimination, Doctoral Thesis, Swiss Federal Institute of Technology, Zurich, 2009, p115.

- 35. N.F. Mott, E.A. Davis, Electronic Processes in Non-crystalline Materials, Clarendon Press, Oxford, 1971, p45.

- 36. W.L. Kalb, K. Mattenberger, B. Batlogg, Phys. Rev. B 78 (2008) 035334.

- 37. C. Krellner, S. Haas, C. Goldmann, K. P. Pernstich, D. J. Gundlach, B. Batlogg, Phys. Rev. B 75 (2007) 245115.

- 38. X.-K. Chen, Y.-T. Fu, H. Li, J.-L. Bredas, Adv. Mater. Interfaces 1 (2014) 1400362.

39. P.J. Diemer, J. Hayes, E. Welchman, R. Hallani, S.J. Pookpanratana, C.A. Hacker, C.A. Richter, J.E. Anthony, T. Thonhauser, O.D. Jurchescu, Adv. Electron. Mater. 3 (2017) 1600294.