### Symbolic Simulation of Mixed-Signal Systems with Extended Affine Arithmetic

Thesis approved by the Department of Computer Science of the University of Kaiserslautern for the award of the Doctoral Degree Doctor of Engineering (Dr.-Ing.)

to

Čarna Radojičić, M.Sc.

#### Reviewers:

Univ. Prof. Dr. Christoph Grimm Design of Cyber Physical Systems University of Kaiserslautern

Univ. Prof. Dr. Lars Hedrich Institute of Computer Science Johann Wolfgang Goethe-Universität, Frankfurt

Prof. Dr. Zainalabedin Navabi ECE Department Worcester Polytechnic Institute, Massachusetts

### Dean:

Univ. Prof. Dr. Klaus Schneider Embedded Systems Group University of Kaiserslautern

Date of Defense: 8th September, 2016

## Declaration

I hereby declare and confirm that this thesis is entirely the result of my own original work. Where other sources of information have been used, they have been indicated as such and properly acknowledged. I further declare that this or similar work has not been submitted for credit elsewhere.

## Acknowledgment

I would like to express my sincere gratitude to my supervisor Prof. Christoph Grimm for his guidance, remarks and engagement throughout my work. Thank You dear professor for supporting and encouraging me in every step of my difficulties during this thesis. I am also grateful to my second and third supervisor Prof. Lars Hedrich and Prof. Zainalabedin Navabi for the careful reading of my work and giving useful comments and suggestions.

I give special thanks to my colleagues from the Institute of Computer Technology TU Vienna, Florian Schupfer and Michael Rathmair. Thank you Florian for the opportunity to be the part of your project and research team. Many thanks to all my colleagues at the Department for Design of Cyber-Physical Systems TU Kaiserslautern Xiao Pan, Frank Wawrzik, Ralf Gruenwald, Javier Moreno, Christopher Heinz and Thiyagarajan Purusothaman for cooperation and a pleasant working ambiance.

I am very grateful to my sister and brother for their unconditional support and motivation throughout my life. They are the most important people in my life and I dedicate this thesis to them. Special thanks I want to give to my parents on their boundless love they gave to me. My dear father and mother, I know you are now on more beautiful place, happy and proud. I will love you forever.

Last but not least, many thanks I give to all my friends, especially Branka and Zorica for all their love, support and patience. Thank you.

## Kurzfassung

Analog-Digitale Systeme verbinden analoge Schaltungen mit digitalen Hardware und Software Systemen. Eine konkrete Herausforderung ist die empfindliche Reaktion von analogen Teilen auf bereits kleine Änderungen der Parameter bzw. Eingangssignale. Die genauen Werte von Schaltungs- und und Systemparametern wie z.B. Prozess, Spannung und Temperatur sind oft unbekannt; wir modellieren sie daher wie unbekannte Werte ('Unsicherheiten'). Unbekannte Werte von Parametern und Eingangssignalen können das Systemverhalten beeinflussen und dazu führen, dass Eigenschaften des Systems nicht mehr in dem vorgegebenen Rahmen liegen. Zur Verifikation Analog-Digitaler Systeme ist der Einfluss von Unsicherheiten auf das Systemverhalten von zentraler Bedeutung.

Verifikation von Analog-Digitalen Systemen wird normalerweise durch numerische Simulation durchgeführt. Ein einziger Simulationslauf ermöglicht es Entwicklern einzelne Parameterwerten aus oftmals Bereichen von unsicheren Werten zu verifizieren. Numerische Simulationsmethoden wie die Monte Carlo Simulation, die Corner Case Simulation und erweiterte Methode wie Importance Sampling oder Design-of-Experiments ermöglichen die Verifikation von Bereichen – auf Kosten einer höheren Anzahl an Simulationsläufen und dem Risiko, dass mögliche Fehler nicht entdeckt werden. Formale und symbolische Methoden sind interessante Alternativen. Diese Methoden bieten eine umfassende Verifikation. Aber formale Methoden skalieren nicht gut bezogen auf Heterogenität und Komplexität. Diese Ansätze sind auch nicht kompatibel zu bestehenden und etablierten Modellierungssprachen. Das erschwert ihre Integration in den industriellen Entwurfsfluss. In frühere Arbeiten zur Verifikation von Analog-Digitalen Systemen wurde Affine Arithmetik für die symbolische Simulation benutzt. Dies ermöglicht die hohe Abdeckung durch formale Methoden mit der einfachen Anwendbarkeit der Simulation zu kombinieren. Affine Arithmetik berechnet die Ausbreitung von Unsicherheiten durch meist lineare, analoge Schaltungen und DSP Applikationen mit exakten Werten. Aber, sie ist aktuell nur in der Lage mit angrenzenden Bereichen zu rechnen, ermöglicht jedoch nicht die Darstellung von und das Rechnen mit diskreten Werten, wie sie beispielsweise durch Software entstehen. Dies ist eine gravierende Einschränkung: Unsicherheiten in Analog-Digitalen Systemen werden oft durch eingebettete Software kompensiert; Verifikation von Systemeigenschaften muss daher beide Teile, analoge Schaltungen und eingebettete Software erfassen.

Das Ziel dieser Arbeit ist die Erweiterung von Affiner Arithmetik, die auch symbolische Simulation von digitaler Hardware und Software ermöglicht, und schließlich die Demonstration ihrer Anwendbarkeit und Skalierbarkeit. Verglichen mit anverwandten Arbeiten und State-of-the-art, bietet Dissertation die folgende Leistungen:

- 1. Die Arbeit stellt Erweiterte Affine Arithmetik Formen (XAAF) zur Repräsentation von Branch- und Mergeoperationen vor.

- 2. Die Arbeit beschreibt arithmetische und Vergleichsoperationen mit XAAF, und verringert die Überapproximation mit Hilfe von LP Solvern.

- 3. Die Dissertation zeigt und diskutiert Möglichkeiten die XAAF in bestehende Modellierungssprachen, insbesondere SystemC, zu integrieren. Auf diese Weise können Brüche im Entwurfsfluss vermieden werden.

Die Anwendung und Skalierbarkeit dieser Methodik wird mit der symbolischen Simulation eines  $\Delta$ - $\Sigma$  Wandlers dritter Ordnung und einer PLL-Schaltung eines IEEE 802.15.4 Transceivers demonstriert.

### Abstract

Mixed-signal systems combine analog circuits with digital hardware and software systems. A particular challenge is the sensitivity of analog parts to even small deviations in parameters, or inputs. Parameters of circuits and systems such as process, voltage, and temperature are never accurate; we hence model them as uncertain values ('uncertainties'). Uncertain parameters and inputs can modify the dynamic behavior and lead to properties of the system that are not in specified ranges. For verification of mixed-signal systems, the analysis of the impact of uncertainties on the dynamical behavior plays a central role.

Verification of mixed-signal systems is usually done by numerical simulation. A single numerical simulation run allows designers to verify single parameter values out of often ranges of uncertain values. Multi-run simulation techniques such as Monte Carlo Simulation, Corner Case simulation, and enhanced techniques such as Importance Sampling or Design-of-Experiments allow to verify ranges – at the cost of a high number of simulation runs, and with the risk of not finding potential errors. Formal and symbolic approaches are an interesting alternative. Such methods allow a comprehensive verification. However, formal methods do not scale well with heterogeneity and complexity. Also, formal methods do not support existing and established modeling languages. This fact complicates its integration in industrial design flows.

In previous work on verification of Mixed-Signal systems, Affine Arithmetic is used for symbolic simulation. This allows combining the high coverage of formal methods with the ease-of use and applicability of simulation. Affine Arithmetic computes the propagation of uncertainties through mostly linear analog circuits and DSP methods in an accurate way. However, Affine Arithmetic is currently only able to compute with contiguous regions, but does not permit the representation of and computation with discrete behavior, e.g. introduced by software. This is a serious limitation: in mixed-signal systems, uncertainties in the analog part are often compensated by embedded software; hence, verification of system properties must consider both analog circuits and embedded software.

The objective of this work is to provide an extension to Affine Arithmetic that allows symbolic computation also for digital hardware and software systems, and to demonstrate its applicability and scalability. Compared with related work and state of the art, this thesis provides the following achievements:

- 1. The thesis introduces extended Affine Arithmetic Forms (XAAF) for the representation of branch and merge operations.

- 2. The thesis describes arithmetic and relational operations on XAAF, and reduces over-approximation by using an LP solver.

- 3. The thesis shows and discusses ways to integrate this XAAF into existing modeling languages, in particular SystemC. This way, breaks in the design flow can be avoided.

The applicability and scalability of the approach is demonstrated by symbolic simulation of a  $\Delta$ - $\Sigma$  Modulator and a PLL circuit of an IEEE 802.15.4 transceiver system.

# Contents

| 1 | Inti | roduction                                                 | 1          |

|---|------|-----------------------------------------------------------|------------|

|   | 1.1  | Motivation                                                | 1          |

|   | 1.2  | Goals and scope of the work                               | 3          |

|   | 1.3  | Hypotheses                                                | 4          |

|   | 1.4  | Contributions                                             | 4          |

|   | 1.5  | Outline                                                   | 5          |

| 2 | Sta  | te of the art                                             | 7          |

|   | 2.1  | Simulation-based approaches                               | 7          |

|   | 2.2  | Formal methods                                            | 9          |

|   |      | 2.2.1 Equivalence checking                                | 9          |

|   |      | 2.2.2 Model checking                                      | 10         |

|   |      | 2.2.3 Reachability analysis                               | 11         |

|   |      | 2.2.4 Run-time verification                               | 13         |

|   |      |                                                           | 14         |

| 3 | Syn  | abolic Simulation based on Affine Arithmetic (AA)         | <b>.</b> 7 |

|   | 3.1  | Symbolic simulation                                       | 17         |

|   |      | 3.1.1 System-level simulation using SystemC (AMS)         | 17         |

|   |      | 3.1.2 Circuit-level simulation                            | 19         |

|   | 3.2  |                                                           | 21         |

|   |      | 3.2.1 Computation with AA forms                           | 22         |

|   |      |                                                           | 24         |

|   | 3.3  |                                                           | 27         |

|   | 3.4  |                                                           | 28         |

|   | 3.5  | Modeling parameter uncertainties with Affine Arithmetic 2 | 29         |

|   |      |                                                           | 30         |

|   |      |                                                           | 34         |

| 4 | Ext  | ended Affine Arithmetic-XAA                               | 88         |

|   | 4.1  | Definition and computation                                | 39         |

|   | 4.2  |                                                           | 12         |

|   | 4.3  |                                                           | 42         |

|   | 4 4  |                                                           | <br>15     |

Contents 8

|              |       | 4.4.1 Conditional statements                                                                                                             | 16         |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              |       | 4.4.2 Iteration statements                                                                                                               | 18         |

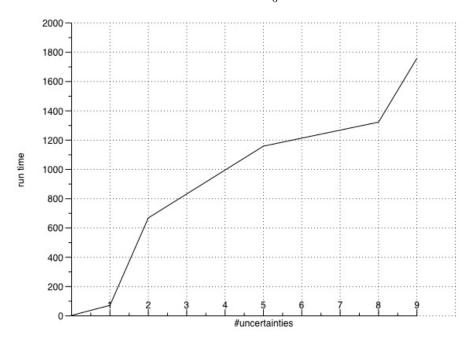

|              | 4.5   | Scalability of symbolic simulation with XAAF                                                                                             | 18         |

|              | 4.6   | Illustration examples                                                                                                                    | 19         |

|              |       | 4.6.1 Example 1 - Control flow example                                                                                                   | 19         |

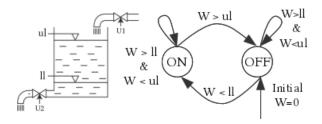

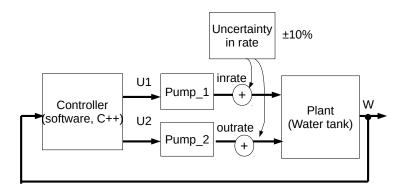

|              |       | 4.6.2 Example 2 - Water level control system                                                                                             | 52         |

| 5            | Ext   | nded Affine Arithmetic Assertions $(XAA + A)$                                                                                            | 8          |

|              | 5.1   | Description                                                                                                                              | 8          |

|              | 5.2   | Specification of properties with XAA+As                                                                                                  | 31         |

|              | 5.3   | Illustration example $\dots \dots \dots$ | 34         |

|              | 5.4   | Implementation                                                                                                                           | 66         |

| 6            | Eva   | uation                                                                                                                                   | 9          |

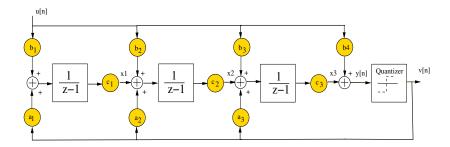

|              | 6.1   | 3rd order Delta-Sigma Modulator                                                                                                          | 69         |

|              |       | 6.1.1 Modulator description                                                                                                              | 70         |

|              |       | 6.1.2 Results of Symbolic Simulation                                                                                                     | 70         |

|              |       | 6.1.3 Comparison with Monte-Carlo simulation                                                                                             | 72         |

|              |       | 1 0 1                                                                                                                                    | 77         |

|              | 6.2   |                                                                                                                                          | 79         |

|              |       | 1                                                                                                                                        | 79         |

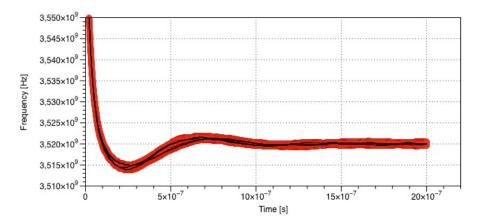

|              |       | v                                                                                                                                        | 36         |

|              |       |                                                                                                                                          | 38         |

|              |       | 6.2.4 Comparison with numeric simulation 8                                                                                               | 39         |

|              | 6.3   | Discussion                                                                                                                               | 92         |

| 7            | Con   |                                                                                                                                          | 4          |

|              | 7.1   |                                                                                                                                          | <b>9</b> 4 |

|              | 7.2   | <i>3</i> 1                                                                                                                               | 95         |

|              | 7.3   | Future work                                                                                                                              | 95         |

| $\mathbf{A}$ | The   |                                                                                                                                          | 7          |

|              | A.1   |                                                                                                                                          | 97         |

|              | A.2   |                                                                                                                                          | 97         |

|              | A.3   |                                                                                                                                          | 99         |

| Li           | st of | Figures 10                                                                                                                               | 1          |

| Li           | st of | Tables 10                                                                                                                                | 3          |

| Al           | obrev | iations 10                                                                                                                               | 4          |

| Li           | terat | ire 10                                                                                                                                   | 5          |

### Chapter 1

### Introduction

### 1.1 Motivation

Mixed-signal systems are systems composed of analog and digital circuits usually controlled by additional software. Analog circuits are by nature highly sensitive to deviations in their operating conditions/environments. These deviations cause variations in the circuit parameters, which modify the original circuit behavior. The modified behavior can change the properties of the original behavior and lead to their violation. Hence it is of crucial importance to take them into account during system analysis and verification.

Usually, the exact values of these variations are **unknown** and in this work they are defined and modeled as *uncertain* values. In the rest of the thesis the term *uncertainties* will be used to describe them. There are various sources of these *uncertainties*, such as:

- Variations in the manufacturing process

- Variations during life time operation temperature drift, components aging, etc.

- Uncertainties introduced by abstraction of reality. Real systems are

often abstracted with behavioral models, which are easier to simulate

and verify

- Uncertainties introduced by analog to digital conversion and the computation in the digital domain with finite-precision arithmetic

- Noise in single blocks, power supply, system environment, etc.

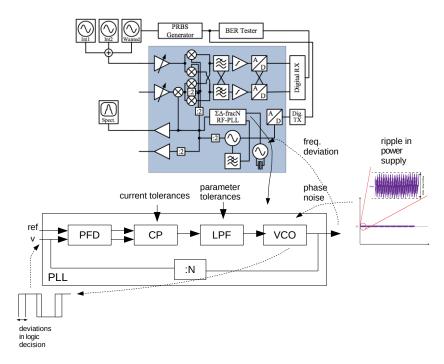

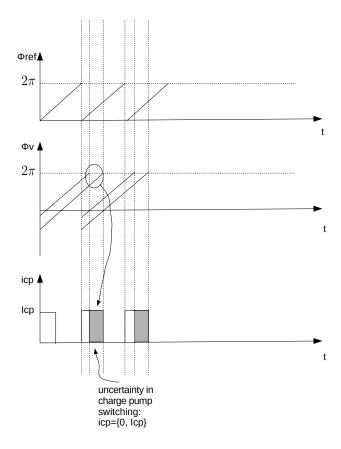

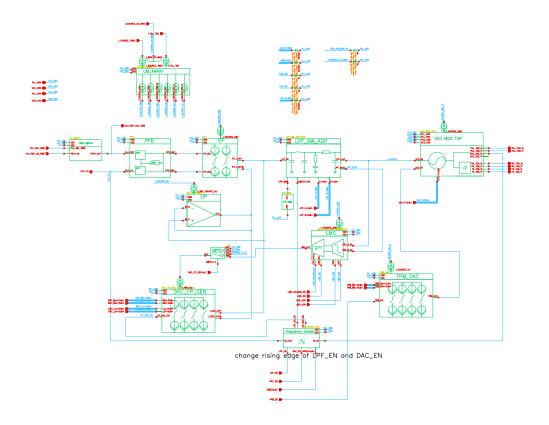

Figure 1.1 shows an example of an IEEE 802.15.4 RF (Radio Frequency) transceiver with some possible uncertainties. Noise in power supplies can have a high impact on the system behavior. It can cause variations in decision thresholds of a phase/frequency detector of the transceiver PLL (Phased-Locked Loop) circuit. This can further lead to inability of the PLL to lock and generate the required carrier frequency brought to the input of a mixer

circuit. The frequency mismatch in the mixer causes introduction of new frequencies in the band of interest. This undesired effect might lead to wrong interpreted data on the receiver side.

Figure 1.1: Block diagram of RF transceiver with possible uncertainties

A general approach to analyze a system behavior under uncertainties is a numeric simulation. In the numeric simulation one simulation run is able to cover only one particular operating condition. To include the wide range of uncertain values, a high number of runs is required. If one run finds a trajectory that violates the properties, one can guarantee the presence of errors. However, if this trajectory is not found, one cannot guarantee the absence of these errors.

In contrast to simulation, formal methods are able to verify a system over a wide range of operating conditions within one execution. However, these methods are not able to cope with a complexity and heterogeneity of AMS (Analog/Mixed-Signal) systems, such as one shown in Fig. 1.1.

In addition, neither simulation nor formal methods are able to trace the specification violations to their sources. Formal methods are able to generate counter examples which lead to specification violation. However, formal verification is not able to give the answer to this question: "Which part of a system causes a specification to fail?"

### 1.2 Goals and scope of the work

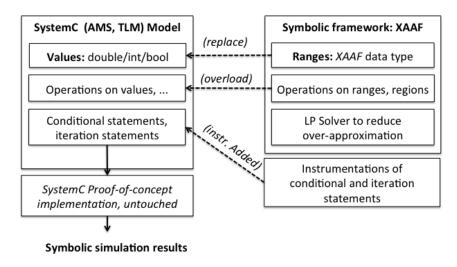

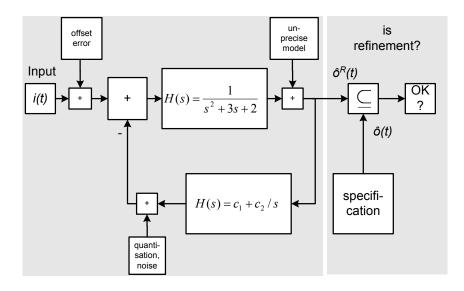

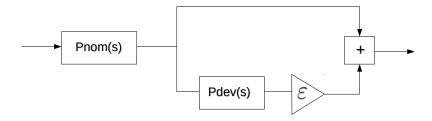

The goal of this work is to combine the high coverage of formal methods with the general applicability of simulation. The first step towards this goal is to capture the sets of uncertain values in a formal way using, for example ranges. Section 3.5 provides possible classes of uncertainties and the way to formally model them. The next step defines operations on ranges required to capture dynamics in a system behavior. The overall idea of the proposed approach is shown in Fig. 1.2.

Figure 1.2: The idea of the methodology

The proposed methodology is applied on AMS systems modeled by a block diagram. This way of modeling is a common industrial practice used in traditional hardware description languages (HDLs) such as SystemC-AMS, Matlab-Simulink, VHDL-AMS, Verilog, etc. Uncertainties are captured as symbolic ranges. Operations applied on ranges compute a symbolic output in one simulation run. The symbolic response covers the whole set of trajectories over the considered range of uncertain values.

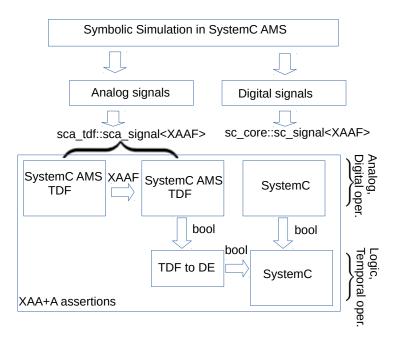

The scope of the work is currently reduced to SystemC AMS simulator. However, the same concept can be implemented within any simulator, which supports the use of abstract data types. As simulator, this work uses the proof-of-concept implementations available from Accellera and Fraunhofer (AMS extensions). This simulator has been developed for verification and validation by numerical, non-symbolic simulation.

In order to permit symbolic simulation of existing models, we give the double/int/bool values of a numeric simulator the semantics of symbolic simulation. Objective is to allow us the use of the existing, numeric sim-

ulator for symbolic simulation. This permits us to keep the changes and modifications of the models small while ensuring compatibility with existing tools and flows. For integration of symbolic simulation into the existing simulator, we use the following approaches (see Fig. 1.2):

- Operator overloading, which allows us to define operations on ranges. In this way, arithmetic and relational operators get symbolic semantics. In the model, the signal and variables values that shall be simulated symbolically must be the abstract data type XAAF.

- Instrumentation of control flow statements that is necessary for symbolic simulation of multiple control flow paths on the software side.

### 1.3 Hypotheses

Combining symbolic approach with simulation, the new methodology should successfully deal and solve the problems of state of the art methods. To show this, I define the requirements that the method should meet. In the rest of the thesis I will call them hypothesis whose validation will be presented at the end of this work.

## Hypothesis 1 - Applicability on Complex Mixed-Signal Systems.

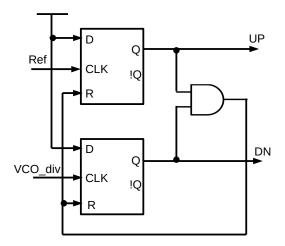

The proposed methodology is based on simulation that allows the application of the method on general systems. This hypothesis is validated applying the new verification methodology on a complex industrial case study: a dual-path charge-pump PLL circuit of one IEEE 802.15.4 transceiver. The hypothesis is accepted if the method is able to show that the system meets/does not meet the desired property in the presence of different sources of uncertainties.

#### Hypothesis 2 - Comprehensive Verification Coverage.

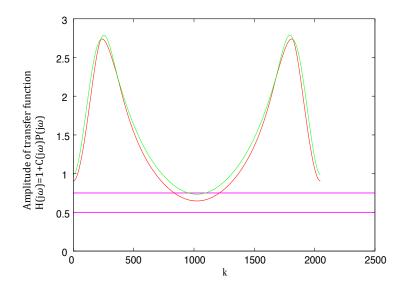

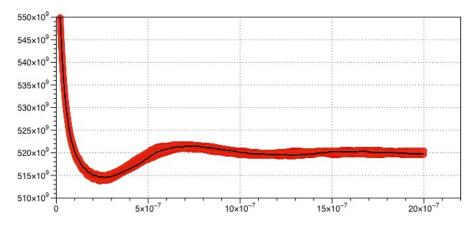

The new methodology captures uncertain values as ranges giving them symbolic values. Computation with symbolic values results in a symbolic system response. The hypothesis is accepted if the symbolic output encloses the whole set of outputs computed for the particular parameter values inside the ranges. This is shown finding the worst-case bounds and comparing their values with the ones obtained by numeric techniques such as Monte Carlo and Design of Experiments.

### 1.4 Contributions

The starting point of this work is Affine Arithmetic proposed by [1]. Affine Arithmetic (AA) is a powerful technique to compute with intervals in a symbolic way. It was introduced as an improved alternative of Interval Arithmetic (IA) [2]. Symbolic representation of ranges with AA overcomes a well-known dependency problem of IA. AA proved its efficiency in a vast number

of applications.

The first application of AA was in computer graphics [3]: computing octrees, quad-trees and ray tracing. This work reports more accurate results compared with Interval Arithmetic applied on the same examples.

[4, 5] use AA In Digital Signal Processing (DSP) to analyze finite-precision effects caused by rounding errors in floating-point arithmetic. An upper bound for the error is estimated using a general applicable static error analysis based on AA. The results of the proposed error estimation are compared with techniques based on detailed simulation strategy [6]. It is shown that using AA a comparable estimation can be obtained with a significantly lower computational effort.

AA also found its applicability in the verification and analysis of analog circuits. [7] proposes semi-symbolic analysis of analog circuits based on AA. Using this approach AA is used in sizing of analog circuits taking the changes of operating conditions and manufacturing tolerances into account. Affine Arithmetic computes the bounds of the worst-case circuit behavior and the global minimum of sizing problem is determined due to inclusion isotonicity.

[8] and [9] use AA for symbolic (forward) simulation of mixed-signal systems and analog circuits, respectively. The goal of these works was to increase coverage of simulation-based techniques towards formal methods.

However, Affine Arithmetic currently supports only computations in the continuous domain. This is not enough for symbolic simulation of mixed-signal systems. Beside continuous parts, they also contain digital or software parts, which require computations in the discontinuous domain. The discrete operations cannot be handled with the standard form of Affine Arithmetic.

This thesis extends Affine Arithmetic towards crossing continuous/discontinuous borders with symbolic values. The extended Affine Arithmetic will be able to handle:

- Discrete parts of Mixed-Signal systems such as comparators, switches, etc.

- Control flow statements in the software code with conditional variables as ranges

More details about the extension of Affine Arithmetic and computation with extended affine forms will be given in Chapter 4.

### 1.5 Outline

The rest of the thesis is organized as following. Chapter 2 briefly discusses state of the art methods used in verification of analog/mixed signal systems. The methods are compared with respect to run-time complexity, scalability and coverage obtained during verification process.

Chapter 3 is reserved for a brief overview of symbolic simulation based on Affine Arithmetic (AA), which is the basis for this thesis. The mathe-

matical form of AA and the basic mathematical operations with affine forms can be found in this chapter. Nonlinear operations with AA terms require the use of approximation schemes that are in this chapter briefly described. To keep the form of AA, these operations add a new symbol per each execution. To avoid symbol explosion, the method acting as a garbage collection or Hansen's forms are used. The short description of approaches and the improved scalability of AA is given.

Finally, this chapter shows the practical use of Affine Arithmetic, listing sources of system uncertainties and describing the way to model them using AA. Symbolic simulation based on AA results in symbolic outputs, which encloses the set of simulation traces, obtained in one (symbolic) simulation run. The way to perform the symbolic simulation on system, as well on circuit level is briefly explained.

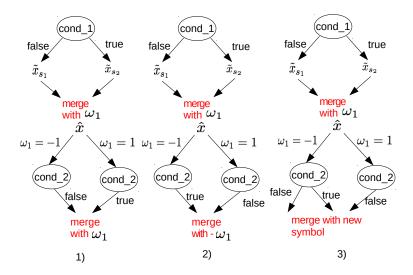

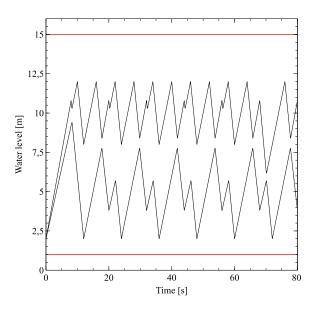

Chapter 4 briefly introduces the extension of Affine Arithmetic proposed in this work. It allows computation with uncertain values on the digital and software side of a system. Beside standard mathematical operations this chapter introduces new operations to pass uncertainties through the discontinuous domain. The idea is illustrated through two small examples: a simple control flow in the software code and a water level control system modeled as automata with two discrete states. The chapter ends with a brief explanation of the method implementation.

Chapter 5 introduces the assertion-based approach proposed to automatically compare symbolic outputs with the properties a system should fulfill. The following points are covered:

- the assertion language with the appropriate set of operators

- the list of typical system properties and the way to describe them using these operators

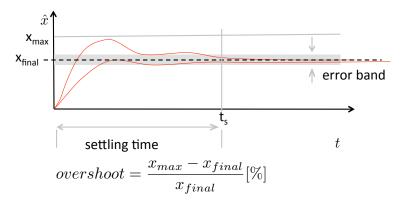

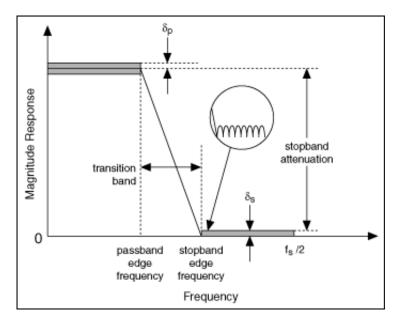

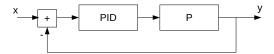

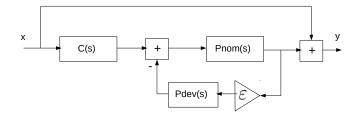

- illustration using two small examples: a 2nd order IIR (Infinite Impulse Response) filter and a closed loop control system. The properties, that were verified, are: the overflow of filter output due to finite precision in DSP and the stability property of a control system.

- the implementation of approach as a separate library in SystemC AMS simulation environment

Chapter 6 proves the efficiency and the applicability of Extended Affine Arithmetic on two more complex non-trivial case studies: a 3rd Order Delta-Sigma Modulator and a Charge-Pump PLL circuit. The considered PLL circuit is used for generation of high frequency carriers in a multiband IEEE 802.15.4 RF transceiver shown in Fig. 1.1. The proposed assertion approach is used to describe typical properties of the case studies and checked them automatically. The chapter ends with the discussion that highlights the advantages of the proposed method over state of the art methods. Chapter 7 concludes the thesis and points to future directions.

## Chapter 2

## State of the art

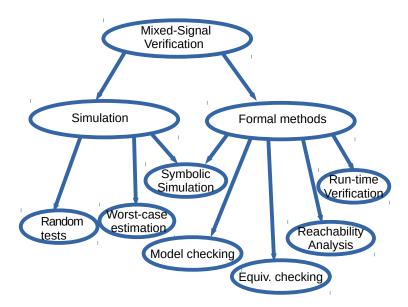

Figure 2.1 gives an overview of state of the art methods for mixed-signal verification. These can be classified into two major classes: simulation and formal methods (see Fig. 2.1).

Figure 2.1: Methods for verification of Mixed-Signal Systems

### 2.1 Simulation-based approaches

Simulation is a common method used to analyze analog/mixed-signal behavior over a wide set of operating conditions. This approach can be categorized into two groups:

1. Statistical methods based on generation of random test cases

#### 2. Methods based on estimation of worst-case behavior

Statistical methods use probability density functions to generate random values for system parameters. These are known as Monte-Carlo simulation. For a thorough system analysis this approach is a very expensive where too many tests are repeated to obtain sufficient problem coverage. To reduce this number, the technique called Importance sampling [10, 11] is proposed. In contrast to Monte-Carlo this approach does not use the original probability density function, but the samples are chosen from the other function called importance density function. Using this function the values are sampled from regions, which have the highest impact on the system performance. Although the number of runs is reduced, random tests cannot guarantee that worst-case scenarios are covered.

The focus of the second class of simulations is to investigate the effects of parameters and find the values, which can lead to worst-case scenarios. [12] considers corner values of parameters to estimate the worst-case behavior. However, this can lead to false estimation, since corners are not by default worst-case parameter values. The methods in [13] and [14] deliver more accurate results but a specification of a minimum yield requirement is required. [15] proposes Design of Experiments (DOE) which uses different classes of metamodels to find parameters with the highest impact. It estimates "worst-case" system behavior using significantly lower number of simulation runs. However, in general all methods based on numeric simulations require multi runs which still cannot guarantee dependability. Table 2.1 compares multi-run methods looking at run-time complexity.

Table 2.1: Comparison of run-time complexity.

| method                | complexity | comment                                       |

|-----------------------|------------|-----------------------------------------------|

| Monte-Carlo           | O(1)       | probabilistic approach; many runs needed      |

| Importance sampling   | O(1)       | monte-carlo runs reduced, but still many runs |

| Corner-Case           | $O(2^k)$   | runs increase exponentially with k uncert.    |

| Design of Experiments |            | number of runs                                |

|                       |            | dependable on various factors:                |

|                       |            | number of uncertainties,                      |

|                       |            | Euclidean distance between pairs of           |

|                       |            | samples in the parameter space,               |

|                       |            | used meta-model                               |

Numeric simulations are able to prove the existence of errors but cannot prove the absence of them. Counter-examples provide 100% guarantee that system properties are violated. If the counter-examples are not found, the correctness of system behavior cannot be proved due to finite numbers of simulated scenarios. To increase the coverage of numeric simulations, formal verification methods were proposed.

### 2.2 Formal methods

The high applicability and efficiency of formal methods were proved in the verification of digital systems [16]. Clarke in [16] proposes model checking methods. These are based on state-graph models of system behavior and allow exhaustive exploration of all possible states and transitions in the graph model. However, due to infinite continuous state space, formal verification of analog/mixed-signal systems is still a challenge. Literature survey provides the following techniques for formal verification of analog/mixed-signal designs.

### 2.2.1 Equivalence checking

One approach to verify analog/mixed-signal designs in more formal way is equivalence checking. It is based on proving the equivalence of two models. In [17] verification of analog circuits is done by checking equivalence between two transfer functions. One transfer function models the circuit implementation and the other the specification. The transfer functions are transformed to the discrete Z-domain, which allows the canonical encoding into Ordered Binary Decision Diagrams (OBDDs). However, this method considers circuit parameters only in nominal conditions; no variations are taken into account. Later, [18] proposes the method, which explores the effect of parameter tolerances to the circuit behavior. The circuit transfer function is extracted from the circuit netlist. Both methods are restricted to linear analog circuits.

[19, 20] proposes an equivalence checking approach for nonlinear analog circuits. The idea of the method is to compare functional behaviors of two circuits represented in the form of differential algebraic equations (DAE). Since levels of abstractions for modeling two circuits might be different, the internal state space variables might also be different. Thus, the direct comparison of the state space would lead to wrong verification results. Transforming the state space of both circuits to canonical representations, which are then directly compared, solves this. However, this is not a trivial task and for complex systems the transformation could not be automatically performed.

Beside circuit-level, equivalence checking can also be performed at system-level as proposed in [21]. There, equivalence is checked between two VHDL-AMS system models. Each VHDL-AMS model contains digital part, analog part and convertor components for converting analog to digital and via versa. Digital part of two designs is verified using classical equivalence checking methods like SAT/BDD method. Analog parts were simplified using rewriting engine and compared using AMS simulator. However, it is not easy to find appropriate rewriting rules to arbitrary classes of analog circuits and this method is often restricted to simple and specific designs. In general, all

methods based on equivalence checking suffer from the complexity problem as it is surveyed in [22].

|                         | [17]               | [19]                 | [18]                 | [21]                      |

|-------------------------|--------------------|----------------------|----------------------|---------------------------|

| Type of systems         | Linear             | Nonlinear            | Linear               | Nonlinear AMS             |

| Models                  | Transfer function  | ODE-DAE              | Transfer function    | ODE-DAE                   |

| Analysis Regions        | Transient response | Near operating point | Near operating point |                           |

|                         | _                  | transient response   |                      | analysis                  |

| Analysis domain         | Frequency          | Time                 | Frequency            | Time                      |

| Techniques and analysis | OBDDs comparisons  | Qualitative analysis | Interval analysis    | Rewriting, SAT simulation |

| Tools                   | N/A                | MAPLE                | MAPLE                | M-CHECK                   |

| Case studies            | Low pass filter    | CMOS inverter,       | Band pass filter     | D/A converter             |

|                         | •                  | Onamp                | -                    | ,                         |

**Table 2.2:** Methods for equivalence checking [22]

### 2.2.2 Model checking

The other approach to formal verification is based on algorithmic system verification like model checking. Depending on the system complexity the researchers propose two classes of methods: direct and indirect methods.

The first class of methods is applied on the original systems where a generated state model is the exact representation of the system behavior [23, 24]. These methods are restricted to linear systems with a simple continuous dynamics. For nonlinear systems with more complex dynamic behavior the computation time to generate a discrete model significantly increases. Therefore, the indirect methods must be applied. They convert original systems to abstract models easier to analyze and verify.

The work in [25, 26] proposes timed automata to approximate continuous system parts. In [27] the time automata is refined by adding clocks allowing us to reduce over-approximation of abstract models; the number of spurious behaviors that do not correspond to concrete ones. The applicability of this method is restricted to systems with a monotonic behavior.

[28] proposes Linear Hybrid Automata (LHA) to abstract continuous system dynamics. To deal with system nonlinearities, [29, 30] extend LHA with a piecewise linear model. The approach is based on linear phase-portrait approximation where the state space of the nonlinear system is divided into linear regions. Since there is no standard method for partition of state space, strongly nonlinear models can hardly be handled.

[31, 32] proposes the discretization of the infinite continuous state space of nonlinear analog systems. The continuous space is discretized into regions called hypercube, which represent the discrete states of the finite state model. Once a model is created, model-checking algorithms are applied to verify typical system properties. The system properties are described with Computation Tree Logic (CTL) formulas. [33, 34] extend CTL formu-

las [35, 36] to cover analog behavior. The main weakness of these approaches is the state explosion problem and the total runtime, which grows exponentially with the number of state variables. Only systems with few state variables (maximum five) can be handled.

In [37] the authors propose a new model for the state representation of AMS designs, Timed Hybrid Petri Nets (THPN). The reachable states of THPN are computed by Difference Bound Matrix (DBM)-based algorithm, which uses convex polygons (zones) to represent them. The desired system properties are described with ACTL (Analog Computation Tree Logic) and automatically verified. This approach requires specification of AMS designs in the form of differential equations (DEs) which are then transformed into THPN.

One more approach towards formal verification of AMS designs is a a Bounded Model Checking (BMC) implemented in the Property-Checker tool [38]. This tool is intended to verify the AMS behaviors, which should reach steady states. As all previous methods, this tool also requires the specification of AMS design in the intermediate language. The design must be described using the semantics of XML language.

The first step towards the integration of formal methods in a standard design flow is proposed by [39]. The authors improve the previous work [37] to allow specification of AMS circuits using a familiar language (in this case VHDL-AMS). A new model called Labeled Hybrid Petri Net (LHPN) is introduced, which is automatically generated from VHDL-AMS designs. To enable the application of the methodology in general (not only on VHDL-AMS designs), [40, 41] propose the generation of LHPNs from simulation traces got from an arbitrary simulator. System properties are then verified using one of the following model checkers: binary decision diagrams (BDD)-based model checker [42, 43], (difference bound matrices) DBMbased model checker [44] and (satisfiability modulo theories) SMT-based model checker [42, 43]. Since LHPN is generated from simulation traces, the quality of the model depends on the quality of delivered simulation results. To increase the quality of verification results the authors propose the use of coverage metrics. They should give information about the regions, which are not explored by simulation traces but where the undesired behavior can appear. The lower quality of simulation results, the more information coverage metrics should deliver.

### 2.2.3 Reachability analysis

To deal with the state explosion problem, one line of research performs state exploration directly on system dynamics. This approach is in literature known as reachability analysis. In general, this approach cannot find the exact representation of all reachable states. This is due to complex system dynamics and unknown exact values of initial conditions. Therefore, reach-

Type of systems AMS Nonlinea Nonlinear Models ODE, DAE THPN/ODE piecewise linear automation Analysis Regions No restriction No restriction Steady State Bounded MC Techniques and analysis umerical anal Numerical approx State space partitions perCubes Convex polygons ACTL FOI Temporal Logic CTL-AT ATACS Property Checker Tools Amcheck Case studies Smitt trigger, Opamp, VCC Tunnel diode. Sequential circuit

Opamp,

**Table 2.3:** Methods for model checking [22]

able sets are often approximated using different geometrical representations.

[45] proposes the partition of the continuous state space using hypercubes of fixed size. However, the computation time of this approach is too high. To reduce this time the authors in [46] propose the reduction of the state space dimension by projections of the state space with polygons.

In d/dt [47, 48] and Checkmate [49, 50, 51, 52] tools, the set of reachable states is approximated using polyhedra. d/dt uses orthogonal polyhedra, while **Checkmate** is based on abstractions using the sequence of convex polyhedra, so called *flow pipe* approximations. In [53] the authors extend d/dt to support verification of nonlinear analog circuits whose behavior is described with differential algebraic equations (DAEs). The extended approach is illustrated on a second order biquad low pass filter. However, d/dt misses an automatic translation from a circuit description to a hybrid automata (HA) and a formal language to specify analog properties. In [54] the Checkmate tool is used to verify properties of two analog circuits, a tunnel diode oscillator circuit and a delta-sigma modulator. Systems are converted to Approximate QTSs (Quotient Transition Systems), which represent conservative approximation of the infinite-state representation of the original system. Since AQTSs represent approximations of the considered hybrid system, the tool verifies only universal properties (properties which must hold for all paths of QTS). These properties are described by ACTL class of formulas [55].

One more approach on reachability analysis not considered by [22] is the work presented recently in [56]. This work proposes the use zonotopes for the approximation of the reachable set. It provides efficient results on verification of a locking property of dual-path charge-pump PLL circuit. However, there are some open questions: "Can this approach handle circuit nonlinearities (e.g. in Voltage-Controlled Oscillator)?" or more important "Can this approach be applied in general?"

|                         | [45]                  | [46]                         | [54]                    | [53]                    |

|-------------------------|-----------------------|------------------------------|-------------------------|-------------------------|

| Types of Systems        | Nonlinear             | Nonlinear                    | Nonlinear               | Nonlinear               |

| Models                  | ODE                   | ODE                          | HA/ODE-DAE              | HA/ODE-DAE              |

| Analysis Regions        | No restriction        | No restriction               | No restriction          | No restriction          |

| Techniques and analysis | Simulation            | Projection numerical approx. | Numerical approx.       | Numerical approx., MILP |

| State space partitions  | Fixed size hyperCubes | Polygons                     | Convex                  | Orthogonal              |

|                         |                       |                              | polyhedra               | polyhedra               |

| Tools                   | COSPAN                | Matlab/Coho                  | Checkmate               | d/dt                    |

| Case studies            | Interlock Circuits    | Van der Pool                 | Tunnel Diode            | Low Pass Filter         |

|                         |                       | Oscillator                   | $\Lambda = \Sigma \mod$ | $\Lambda = \Sigma \mod$ |

**Table 2.4:** Methods for reachability analysis [22]

#### 2.2.4 Run-time verification

Run-time verification is the other set of methods dealing with the complexity problem of formal methods. The basic idea is to use monitors, that monitor signal traces generated from numeric simulations. Monitors check properties automatically and can work in *offline* and *online* mode. The properties to be verified are described with assertions whose semantic follow the syntax of the appropriate specification language. This idea was firstly adopted for verification of digital designs [57]. In [58, 59] the authors propose formal specification languages like Property Specification Language (PSL) and System Verilog Assertion (SVA). For specification of analog behavior these languages require extensions and the certain number of modifications.

[60] presents Signal Temporal Logic (STL), as extension of PSL. The language is used to specify analog properties, which are verified *offline*. [61] also proposes the *offline* tool, but for verification of mixed-signal properties. This tool requires modeling AMS system with System of Recurrence Equations (SRE) and it does not support mixed behaviors for continuous time (only discrete).

In general, the weakness of offline methods is that properties can be checked only after simulation. For complex systems memory usage to save the signal traces can increase significantly.

To face with this problem the authors in [62] extend the work [60] towards *online* monitoring. The approach proposes an incremental monitoring method, which combines the simplicity of the offline method with the early failure detection of online monitoring. Concretely, the offline method is not applied on the entire set of simulation traces but incrementally on each simulation trace.

Online monitoring can be also found in [63] where SVAs are extended to cover continuous time. In [64] an assertion library is integrated in the environment of MLDesigner which uses multi domain approach to model systems: CTDE (Continuous Time Discrete Event) MOCs (Model of Computations) for analog modeling and Discrete Event MOCs for modeling digital system parts.

Monitoring timed automata (MTA) [65], based on the approach [66], also

allows the verification of system properties during simulation. In [67] the authors integrate the MTA in the automatic stimulus generation framework which is interfaced with the VHDL-AMS simulator.

Above described assertion-based methods are limited to verification of time behavior; frequency behavior is not covered. To allow description of properties in the frequency domain, [68, 69] introduce the language of Mixed Signal Assertions (MSA). They combine continuous time, discrete time and frequencies with temporal logic.

In general run-time verification is a very fast and hence an attractive approach. However, there is no guarantee that a system meets specifications due to the finite number of tested simulation traces.

### 2.2.5 Symbolic simulation

The goal of symbolic simulation is to combine the high coverage of formal methods and interactive way of analysis as simulation. Symbolic simulation is also a part of formal verification, e.g. to compute reachability. The idea is based on symbolic approach, which replaces concrete numeric values with symbols. Symbolic simulation can be seen as a methodology, which removes tradeoff in conventional simulations between required simulation runs and a coverage. With symbolic representation, a comprehensive coverage of formal methods is obtained in one or very few simulation runs.

In early 70's [70] symbolic simulation was applied for software testing and debugging. Since program variables are symbols, control flows in software code are executed for all possible branches/path conditions. For large programs, a comprehensive simulation is problematic, because the number of paths increases exponentially (path explosion problem). To cope with the path explosion problem, Satisfiability Modulo Theories (SMT) solvers[71] are used to more accurately determine the reachable paths. The control flow is pruned by heuristics to focus on "relevant" paths [72, 73]. Recent tools allow symbolic execution at the level of C code [74], Low Level Virtual Machine (LLVM) [75] or Dalvik [76] intermediate code and are able to handle larger software systems. While for C code a specific symbolic executor is used, abstract virtual machines like LLVM or Dalvik do not need any specific high-level language at all.

Design languages such as VHDL, Verilog and SystemC have, together with their simulation methods, reached a complexity where it would be desirable to use an existing compiler and simulator for symbolic simulation or model checking. The question "Can a Simulator Verify a Circuit?" was first asked by Bryant [77] who proposed the use of the ternary logic (0,1,X) of logic simulators for this purpose. Unfortunately, this will quickly lead to simulations with "X" states only.

In [78] Bryant and Seger propose Symbolic Trajectory Evaluation where symbolic simulator is seen as model checker. The properties are described

with limited class of formulas written in Linear Temporal Logic (LTL) logic. This work was later extended to support verification of safety properties [79, 80, 81]. [82] proposes Generalized Symbolic Trajectory Evaluation (GSTE) which enables adding fairness to system properties. To avoid simulations with "X" states only, GSTE does not encode the entire system state space symbolically. It looks at the complexity of specification and replaces only required inputs and initial states with symbols. This methodology found place in industry applications; Motorola used STE for verification of memory subsystems while Intel performed block-level verification based on this methodology. However, only limited class of properties can be described and verified; existential properties cannot be expressed. CTL model checking is still more expressive.

In [83] Chris Wilson overcomes the problem of "too many X" combining the ternary logic with more powerful BDD structure. In Wilson's simulator the symbolic values are represented in two ways: as BDD variable or symbol "X" tagged with the corresponding index. When the output values depend on inputs with multiple tags, its result is "X". The idea is to start symbolic simulation using only tagged values for input variables. If outputs result in "X", then input symbols are replaced with BDD variables and symbolic test is performed again. This process is repeated until the output value is either 0 or 1. This simulator is restricted to simple data paths, since every time tagged "X" is replaced with BDD variable the entire simulation must be repeated. Recent tools rely on more powerful BDD techniques or even SAT/SMT solvers. For this purpose, HDLs are translated into automata or other intermediate representations. For formal verification in complex modeling and design languages, languages such as SystemC are translated to intermediate languages, SISSI [84].

Recent works [85, 86] brought the idea of symbolic approach to analog and mixed-signal circuits. Both methods combine symbolic representation of system behavior with Interval Arithmetic (IA)[2] to compute over the ranges of system parameters. In [85] mixed-signal designs are modeled symbolically in the form of recurrence equations and computed over the intervals of system parameters. However, due to divergence problem associated with IA, symbolic simplifications need to be applied at each time step This leads to high computational costs.

[86] proposes symbolic representation of mixed-signal behavior in the form of SAT constraints by using NL-SMT solver. The constraints over variables are represented as intervals using Interval Arithmetic. Similar, the over approximation problem of IA is solved by symbolic simplifications with ICP(Interval Constraint Propagation) which is applied at each computation step. Since this leads to significant increase of computational costs, the combination with numeric simulations was required.

[8, 87, 9] overcomes the problems of IA using the improved alternative called Affine Arithmetic [1, 88]. One more advantage of these works over

[85, 86] is that the symbolic methodology is used directly in an existing simulator without translation a system model to a formal one. However, these approaches were restricted to continuous state space due to inability of Affine Arithmetic to compute in the discrete domain. This work extends Affine Arithmetic towards discrete computations with symbolically represented ranges.

### Chapter 3

# Symbolic Simulation based on Affine Arithmetic (AA)

### 3.1 Symbolic simulation

Recent works [8, 89] use Affine Arithmetic [1, 88, 90] for symbolic simulation of analog/mixed-signal systems. A system is simulated over a set of variable inputs, initial conditions and parameter values. All system variations are symbolically modeled as ranges using affine forms. Using symbolic representation Affine Arithmetic brings the simulation the following advantages:

- 1. High dependability of verification results using one (symbolic) simulation run

- 2. Measuring the impact of each variation to the total system performance and the trace ability of variations back to their sources

In [8] simulation is performed at system level using an existing System C AMS simulator [91], intended for numeric simulation. Beside system-level simulation, symbolic simulation is also performed at circuit level [89]. In [89] Affine Arithmetic is integrated in an equation solver to compute a circuit response over a set of circuit parameter values.

### 3.1.1 System-level simulation using SystemC (AMS)

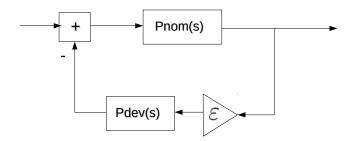

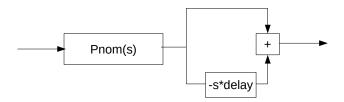

In [8] AMS system is modeled in a usual way by a block diagram as shown by Figure 3.1. The functions of blocks are described by mathematical functions in time-domain (multiplication, integration, differential equations, etc.), by transfer functions H(s), or by linear circuits with switches, or by C++ code.

The functional blocks communicate via directed signals ((timed) data-flow, signal-flow). For simulation, the outputs of the blocks are computed in discrete time steps, following the data flow's direction by computation of the block's functions, or by solving the equation systems of the blocks. This way of modeling is the common industrial practice and is the underlying

Figure 3.1: Modeling AMS system by a block diagram [8]

model of computation of modeling languages such as Matlab/Simulink and SystemC AMS. [8] uses SystemC AMS.

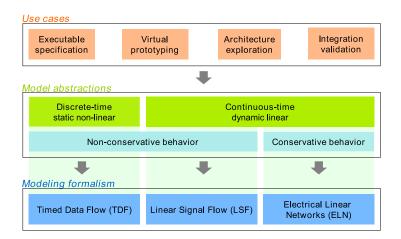

SystemC AMS [91] is introduced as an extension to SystemC modeling language [92], which enables modeling, simulation and verification of analog and mixed signal systems in the same simulation environment. SystemC is a C++ class library intended for simulation of cycle-accurate system behavior using discrete-event simulation kernel in the background. As an extension, SystemC AMS keeps all properties of SystemC while adding new features to handle mixed-signal behavior. New execution semantics include modeling AMS systems on different levels of abstractions: discrete-time, continuous-time, non-conservative and conservative modeling. They are supported by three models of computation shown in Figure 3.2:

- Timed Data Flow (TDF) TDF supports the abstraction of signals and system quantities as discrete-time values available at discrete time points. The distance between the points is defined by the sampling period  $T_s$ . All standard types supported by C++ can be used to specify the type of discrete-time values. TDF also supports the use of templates to specify value types. Therefore, one can implement its own data type and use it to represent quantities and signal values.

- Linear Signal Flow (LSF) LSF and ELN support continuous-time modeling which is more natural way of modeling the physical world. The system behavior is specified as a set of differential algebraic equations (DAEs) solved by a suitable equation solver. LSF supports sys-

Figure 3.2: Modeling formalisms in SystemC AMS [93]

tem modeling only with the set of available modules called primitive modules. The response of such a system is computed using a linear DAE solver.

Electrical Linear Network (ELN) - Unlike LSF, ELN supports modeling a conservative continuous-time behavior. These models are more complex, hence they require that interactions between system quantities satisfy Kirchhoff's laws.

In [8] the authors use TDF as model of computation. In order to turn the existing SystemC AMS numeric simulator to a symbolic one, C++ values double/int/bool are given the symbolic semantics using Affine Arithmetic (AA). Replacement of standard C++ data types with AAF is possible through operator overloading.

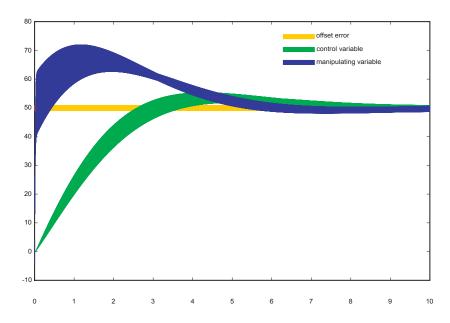

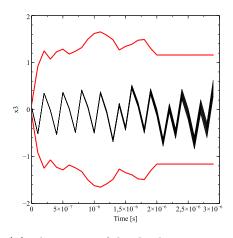

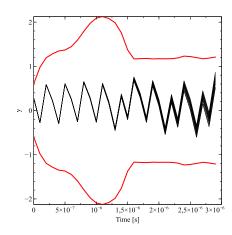

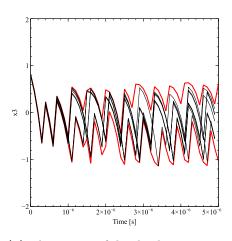

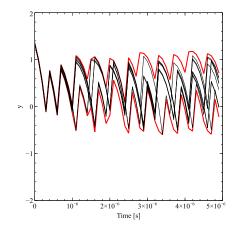

One symbolic simulation run results in the safe set of all possible system behaviors over the considered range of operating conditions. The system response for the system shown in Figure 3.1 is shown in Figure 3.3. The errors introduced in the control loop fall towards 0 and the output signal converges to the steady state value. This behavior is exactly what a designer expects from a designed PI controller (Figure 3.1 bottom). In contrast to Interval Arithmetic, Affine Arithmetic is able to track correlations between same quantities in a system loop. This further avoids overapproximation of output signal values that could lead to false negatives.

#### 3.1.2 Circuit-level simulation

Beside at system level, symbolic simulation can also be applied at circuit level [89, 94, 95].

[89] implements a symbolic SPICE-like circuit simulator. It was used

Figure 3.3: Visualization of simulation results [8]

for symbolic (forward) simulation of analog circuits which are modeled by nonlinear differential equations in the implicit form:

$$\mathbf{F}(\mathbf{x}, \mathbf{p}) = \mathbf{0}.$$

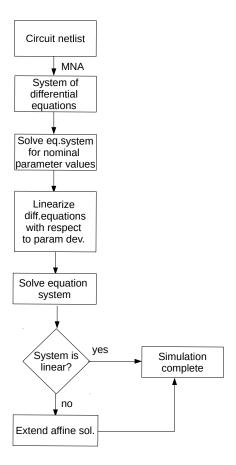

So far this seems to be the only approach that is able to handle nonlinear differential equations in the implicit form of high complexity as needed for symbolic (forward) simulation. Circuit simulation is performed in two steps. In the first step, a net list of the circuit is transformed into the corresponding system of differential equations using the Modified-Node-Analysis (MNA). Then in the second step the equation system is solved in the numerical solver, which uses one of the methods of numerical integration like forward Euler, backward Euler or trapezoidal method to solve the given equations. The solver provides DC, AC and transient circuit analysis. To deal with affine terms, the circuit simulator performs the algorithm divided into three steps:

- 1. The nominal solution of the system is computed using a well-known Newton-Raphson method.

- 2. The equation is linearized at the nominal point with respect to parameter variations and variable inputs. For linear systems the simulator solves linearized equations providing an exact affine solution.

- 3. To deal with nonlinear systems, the algorithm requires the third step in which the affine solution is overapproximated to deliver the conser-

vative solution. For this purpose, the new deviation symbol (modeling overapproximation) is added.

Figure 3.4 shows the flow of affine circuit simulation.

Figure 3.4: The flow of affine circuit simulation

### 3.2 Affine Arithmetic

Affine Arithmetic (AA) is a powerful technique to compute with ranges. It is proposed as an improved alternative for classical Interval Arithmetic (IA) [2] to handle its dependency problem. The form, which AA uses to represent an arbitrary quantity  $\tilde{x}$ , is as follows:

$$\tilde{x} = x_0 + \sum_{i=1}^{m} x_i \varepsilon_i \qquad \varepsilon_i \in [-1, 1].$$

(3.1)

Each deviation symbol  $\varepsilon_i$  is a symbolic variable whose exact value is *unknown*, but lies in interval [-1,1]. The deviation symbols are scaled by par-

tial deviations  $x_i$ , whose number is equal to m.

The affine form given by Eq. 3.1 is an informal representation of a range  $[x_{lo}, x_{up}]$  with lower and upper bounds calculated as:

$$x_{lo} = x_0 - \sum_{i=1}^{m} |x_i|$$

$x_{up} = x_0 + \sum_{i=1}^{m} |x_i|$ .

The range is converted back to affine form according to the following:

$$[x_{lo}, x_{up}] = \frac{x_{lo} + x_{up}}{2} + \frac{x_{up} - x_{lo}}{2} \varepsilon; \varepsilon \in [-1, 1].$$

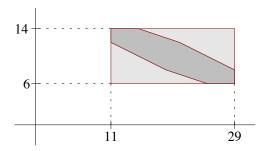

With symbolic representation Affine Arithmetic identifies the correlation between affine forms and hence delivers more tight and realistic bounds than Interval Arithmetic. Figure 3.5 shows the geometrical representation of joint range of two correlated quantities represented in Affine and Interval Arithmetic. In Interval Arithmetic joint range of x and y is a box, while in Affine Arithmetic the joint range represent a zonotope, a center-symmetric convex polytope. AA delivers much more accurate bounds than IA, as shown by Figure 3.5.

**Figure 3.5:** Joint range of dependent quantities  $\tilde{x} = 20 - 4\varepsilon_1 + 2\varepsilon_3 + 3\varepsilon_4$  and  $\tilde{y} = 10 - 2\varepsilon_1 + \varepsilon_2 - \varepsilon_4$  in Affine Arithmetic (zonotope) and Interval Arithmetic (box)[88]

### 3.2.1 Computation with AA forms

Arithmetic operations on affine forms can be divided into two groups: linear and nonlinear. These operations are defined through the following definitions. The acronym AAF in the following definitions refers to the set of affine forms defined by Eq. 3.1.

**Definition 3.1.** If  $\tilde{x}, \tilde{y} \in AAF$  and  $c \in \mathbb{R}$  is a real constant then

$$\tilde{x} + \tilde{y} = x_0 + y_0 + \sum_{i=1}^{m} (x_i + y_i)\varepsilon_i$$

$$\tilde{x} - \tilde{y} = x_0 - y_0 + \sum_{i=1}^{m} (x_i - y_i)\varepsilon_i$$

$$c\tilde{x} = cx_0 + \sum_{i=1}^{m} cx_i\varepsilon_i.$$

The above operations satisfy the closure property; they result in affine forms with exact lower and upper bounds. For nonlinear operations the final result must be approximated to be represented as an affine form. However, the safe inclusion is guaranteed; the final result is always over-approximation and never underestimation of the exact result.

**Definition 3.2.** If  $\tilde{x}, \tilde{y} \in AAF$ , nonlinear function  $f(\tilde{x}, \tilde{y})$  is then computed as:

$$f(\tilde{x}, \tilde{y}) \subseteq f^a(\tilde{x}, \tilde{y}) + \delta \varepsilon_{m+1}$$

where  $\varepsilon_{m+1} \in [-1,1]$  is a new deviation symbol.  $\delta$  is the upper bound of the approximation error between the nonlinear function f and the linear approximated function  $f^a$ :

$$|f(\tilde{x}, \tilde{y}) - f^a(\tilde{x}, \tilde{y})| \leq \delta \ \forall \varepsilon_i \in [-1, 1].$$

The linear approximated function  $f^a$  is computed using one of the approximation schemes described in the next section (Section 3.2.2). Nonlinear operations such as multiplication and division of two affine terms  $\tilde{x}$  and  $\tilde{y}$  are computed as follows:

$$\tilde{x} * \tilde{y} := x_0 * y_0 + \sum_{i=1}^{m} (x_0 y_i + x_i y_0) \varepsilon_i$$

$$+ (\sum_{i=1}^{m} |x_i| \sum_{i=1}^{m} |y_i|) \varepsilon_{m+1}$$

(3.2)

The multiplication result can be seen as the Taylor approximation of  $\tilde{x} * \tilde{y}$  with the first order polynomial around the nominal values  $x_0$  and  $y_0$ :

$$f^{a}(\tilde{x}, \tilde{y}) = f(x_{0}, y_{0}) + \frac{\partial f}{\partial x}(x_{0}, y_{0}) * (\tilde{x} - x_{0}) + \frac{\partial f}{\partial y}(x_{0}, y_{0}) * (\tilde{y} - y_{0})$$

$$= x_{0} * y_{0} + \sum_{i=1}^{m} (x_{0}y_{i} + x_{i}y_{0})\varepsilon_{i}$$

with the maximum approximation error:

$$\delta = \sum_{i=1}^{m} |x_i| \sum_{i=1}^{m} |y_i|.$$

The symbol  $\varepsilon_{n+1}$  is a new deviation symbol which together with  $z_m$  encloses the exact result. Division of two affine terms is computed as:

$$\frac{\tilde{x}}{\tilde{y}} = \tilde{x} * (\frac{1}{\tilde{y}})$$

with condition that the range modeled with  $\tilde{y}$  does not contain zero.  $\frac{1}{\tilde{y}}$  can be computed using one of approximation schemes described in the next section.

### 3.2.2 Approximation schemes of nonlinear operations

In contrast to linear, nonlinear operations do not satisfy the closure property. To keep affine form of a final result, the nonlinear part is replaced with the linear one using one of the approximation schemes. Without loss of generality, it is assumed that the computation is performed in one dimension. Let  $\tilde{x}$  be the affine variable  $\tilde{x} = x_0 + \sum_{i=1}^m x_i \varepsilon_i$  and f the nonlinear function applied on  $\tilde{x}$ . To get the affine form of z the nonlinear function is approximated with the linear one:

$$z = f(x_0 + \sum_{i=1}^{m} x_i \varepsilon_i) \subseteq f^a(x_0 + \sum_{i=1}^{m} x_i \varepsilon_i) + \delta \varepsilon_{m+1}.$$

(3.3)

The approximated function  $f^a$  is a linear function:

$$f^{a}(x_{0} + \sum_{i=1}^{m} x_{i}\varepsilon_{i}) = k * (x_{0} + \sum_{i=1}^{m} x_{i}\varepsilon_{i}) + n$$

where  $k, n \in \mathbb{R}$ . The values of k, n and the approximation error  $\delta$  depends on the applied approximation scheme. Depending on the application the following approximation schemes are used:

- 1. Minimum range approximation. This approximation delivers the minimized range of the final result. This scheme is very useful for formal verification methods where a system response in the worst case is of high interest. The computed bounds which enclose all possible system behaviors should be as tight as possible since too high over approximation could lead to false negatives.

- 2. Chebyshev approximation. This approximation is very useful in the applications for which sensitivity analysis is of crucial importance. Although minimum range approximation provides the minimum over approximation on the computed bounds, the approximation error over the whole range is quite high which could lead to wrong interpreted effects of single sources of uncertainties to the total performance.

The Chebyshev approximation is computed according to the Lemma 1 that can be found in [96]. According to this lemma the coefficients of n-degree polynomial approximation of nonlinear function f over a range [a,b] can be computed using n+2 points:

$$a \le x_1 < x_2 < \dots < x_{n+2} \le b$$

.

for which it holds that

$$\delta = r(x_i) = -r(x_{i+1}) \tag{3.4}$$

where  $\delta$  represents the maximum approximation error found as:

$$\delta = \max_{x \in [a,b]} |f(x) - f^a(x)|$$

In Affine Arithmetic nonlinear functions are approximated with the first order polynomials:

$$f^a(\tilde{x}) = k * \tilde{x} + n$$

where  $\tilde{x}$  is an affine term. Thus, the number of points used to compute the polynomial coefficients are three. The coefficient k is computed assuming function f is convex or concave over the interval [a, b]  $(a \neq b)$ :

$$k = \frac{(f(b) - f(a))}{b - a}.$$

In that case two points  $x_1$  and  $x_3$  are the lower and upper bound of the interval [a, b]. The third point  $x_2$  lies in the range [a, b] and at this point the approximation error reaches the maximum value. So, the first derivative of the approximation error function  $r'(x_2)$  is equal to zero:

$$r'(x_2) = f'(x_2) - k = 0$$

$f'(x_2) = k$

and the value  $x_2$  is computed as:

$$x_2 = (f')^{-1}(k).$$

When this value is found, Eq. 3.4 is used to find the value n of approximated function and the approximation error  $\delta$ :

$$\delta = r(x_i) = f(x_1) - k * x_1 - n$$

$$\delta = -r(x_{i+1}) = k * x_2 + n - f(x_2).$$

Now, n and  $\delta$  are calculated as:

$$\delta = \frac{f(x_1) - k * x_1 + k * x_2 - f(x_2)}{2}$$

$$n = \frac{f(x_1) - k * x_1 + f(x_2) - k * x_2}{2}.$$

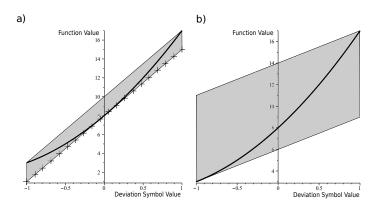

**Figure 3.6:** Linearization of nonlinear function using: a) Chebyshev b) Minrange approximation [97]

In contrast to Chebyshev approximation, the min-range approximation results in the function with the exact values on the bounds of the range  $\tilde{x}$ . However, inside the range the approximation error is higher than using Chebyshev approximation. The approximation function is computed as the tangent of function f at one end point. Hence, the approximation error at that point is equal to zero. If  $f'(x), f''(x) \geq 0$ , the tangent is computed at the lower bound k = f'(a), otherwise at the upper bound k = f'(b). The coefficient f and the approximation error f are computed as:

$$\delta = \frac{f(a) - k * a + k * b - f(b)}{2}$$

$$n = \frac{f(a) - k * a + f(b) - k * b}{2}.$$

Figure 3.6 illustrates Chebyshev and min-range approximation of a nonlinear function (plotted by bold curve) over interval [-1, 1].

As given by 3.3 the approximation of nonlinear functions with linear ones introduces a new deviation symbol to ensure the safe inclusion. The new deviation symbol introduces overapproximation which contains exact computations. However, the performance of nonlinear operations in a loop or over a long simulation time horizon can lead to symbol explosion and loss of effectiveness of the approach. To attack this problem, literature survey proposes the following techniques:

- 1. Cleanup method proposed by [98] which servers as a garbage-like collection with the difference that new added deviation symbols are not removed from memory but replaced with only tow terms. More details are given in the following part of the section.

- 2. The other approach [99] combines Affine Arithmetic with Interval Arithmetic [2] where an approximation error is enclosed simply with

an interval. This form of Affine Arithmetic is known as Hansen's form Affine Arithmetic Form. The work in the thesis uses this approach. The advantage of Hansen's form over (1) is described in Section 3.4.

### 3.3 Implementation of *cleanup* method

As mentioned above, nonlinear functions must be approximated to satisfy the closure property of Affine Arithmetic. In order to ensure the safe inclusion, approximations add additional deviation terms. One deviation term is added every time step the nonlinear operation is performed. Thus, the maximum required memory for each affine variable depends linearly on the number of time steps:

$$u_d * n + u_s \subseteq O(n)$$

where  $u_d$  is the number of uncertainties added by nonlinear operations, n is the number of time steps and  $u_s$  is the number of static uncertainties.

Even worse, the run time complexity grows quadratic with the number of time steps n:

$$\sum_{i=1}^{n} (u_d i + u_s) = u_d \frac{n(n+1)}{2} + u_s n$$

$$u_d \frac{n^2}{2} + (\frac{u_d}{2} + u_s) n \subseteq O(n^2).$$

To deal with this problem, Heupke [98] proposes the *cleanup* method to dynamically manage a high number of terms. The idea is similar to one of the garbage collection with the difference that added deviation terms are not deleted form memory but replaced with only two terms. All deviation terms whose values lie below a user-defined level are summed up. One deviation term sums up all terms with positive scaling factors and the other with negative factor signs. In this way a safe inclusion is kept and the number of terms is significantly reduced. The *cleanup* method is called every m time steps. Since m is constant during simulation, the memory complexity becomes the same as the computation with pure numeric terms [98]:

$$u_d * m + u_s \subseteq O(1)$$

.

The run time complexity is also improved growing linear with the number of time steps [98]:

$$(u_d * m + u_s)n + 2n/m(u_d * m + u_s) = (u_d * m + u_s + 2(u_d * m + u_s)/m)n \subseteq O(n).$$

However, this method faces the following weak points:

- 1. It can be only applied on robust systems in a closed loop in which the impact of variations converges to values close to zero. If this is not the case, a threshold value for which the method should be called can hardly be specified.

- 2. The second weak point is that the moment in which a method is called is determined by a user. Hence, too often calls could lead to additional overapproximation and lead to incorrect behavior of a feedback loop. On the other hand, rare calls would lead to a high number of symbols that need to be handled by the method and the simulation process, itself. The computational cost would increase and the efficiency of the cleanup method would be lost.

#### 3.4 Hansen's form of Affine Arithmetic

In contrast to the *cleanup* method, Hansen's form [99] applied on AA terms enables a constant time and space complexity of nonlinear operations in general. Each affine form given by Eq. 3.1 can be re-written using Hansens form as follows:

$$\tilde{x} = x_0 + \sum_{i=1}^{m} x_i \varepsilon_i + [0, 0]$$

$\varepsilon_i \in [-1, 1]$

where Interval [0,0] is used to represent a nonlinear part and its default value is *zero* interval in the case there are no nonafffine terms. Linear operations given by Definition 3.2.1 applied on Hansen forms of Affine Arithmetic result again in the Hansens forms. Also, in contrast to usual Affine Arithmetic, nonlinear operations of Hansen's affine forms result again in Hansen's form. The operations only update the bounds of interval enclosing the exact results. Thus, multiplication operation can be re-written:

$$\tilde{x} * \tilde{y} = (x_0 + \sum_{i=1}^m x_i \varepsilon_i + [0, 0]) * (y_0 + \sum_{i=1}^m y_i \varepsilon_i + [0, 0])$$

$$= x_0 * y_0 + \sum_{i=1}^m (x_0 * y_i + x_i * y_0) \varepsilon_i + \sum_{i=1}^m []_i$$

where  $[]_i$   $i \in \{1, ..., m\}$  are computed as follows:

$$[]_{i} = \begin{cases} [-|x_{i}||y_{i}|,|x_{i}||y_{i}|] & i \neq j \\ [0, x_{i}y_{i}] & i = j, x_{i} * y_{i} > 0 \\ [x_{i}y_{i},0] & i = j, x_{i} * y_{i} < 0 \end{cases}$$

*Example.* Let  $\tilde{x}$  has value  $1 + \varepsilon_1 + [0, 0]$  and  $\tilde{y} = 1 - \varepsilon_1 + \varepsilon_2 + [0, 0]$ . Multiplication of  $\tilde{x}$  and  $\tilde{y}$  results in the following:

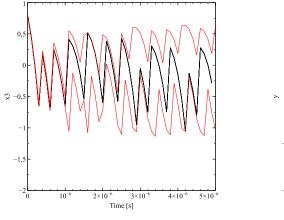

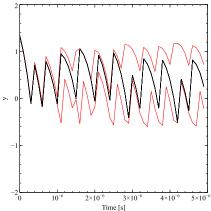

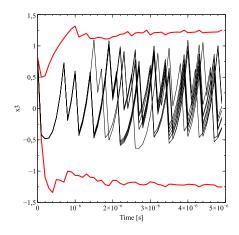

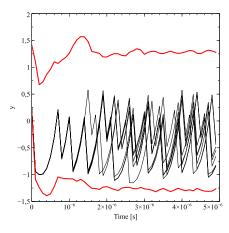

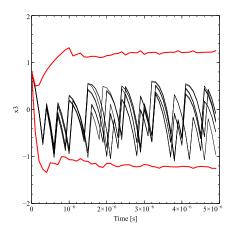

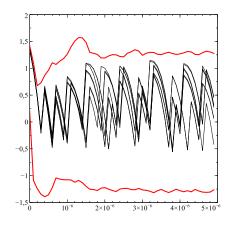

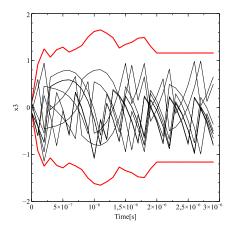

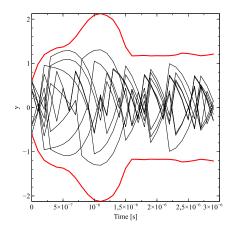

$$\tilde{x} * \tilde{y} = 1 + \varepsilon_1 * 0 + \varepsilon_2 + [-2, 1]$$