## Advanced Methods for Hardware Reverse Engineering

### DISSERTATION

zur Erlangung des Grades eines Doktor-Ingenieurs der Fakultät für Elektrotechnik und Informationstechnik an der Ruhr-Universität Bochum

> by Christian Kison Bochum, Mai 2018

Copyright  $\bigodot$  2018 by Christian Kison. All rights reserved. Printed in Germany.

To my beloved family.

Christian Kison Place of birth: Soltau, Germany Author's contact information: Christian.Kison@rub.de www.rub.de

| Thesis Advisor:    | Prof. DrIng. Christof Paar             |

|--------------------|----------------------------------------|

|                    | Ruhr-Universität Bochum, Germany       |

| Secondary Referee: | Prof. Dr. Jean-Pierre Seifert          |

|                    | Technische Universität Berlin, Germany |

| Thesis submitted:  | 30.05.2018,2018                        |

| Thesis defense:    | 10.07.2018,2018                        |

| Last revision:     | July 5, 2019                           |

Everything not saved will be lost. –Nintendo "Quit Screen" message

## Abstract

In daily life, it has become impossible to avoid electronic systems in our surroundings. We encounter them daily either in direct form, such as a Personal Computer (PC) and a laptop, or indirectly as part of an embedded system, such as mobile phones and key locking systems. In our modern world, we can use the electronics in our everyday activities to communicate our thoughts, ideas, and feelings over digital channels and subconsciously in routine work. They all have the common goal of creating a more comfortable life for us. Accordingly, these technological advancements and innovations leave a substantial user-specific digital footprint that holds daily routine and personal information that requires protection.

Consequently, innovations come with a risk if immature designed cryptographic systems are applied. We could leak confidential data, industrial expertise, or military insights. These risks become threats in the presence of malicious adversaries that try to exploit or even create system weaknesses for personal gains. Attackers can bypass embedded system security or create security vulnerabilities at the very root by altering any core Integrated Circuit (IC) component. For example, they could modify the circuitry during the design or fabrication. Malicious circuity, known as hardware Trojans, or vulnerability discovery can invalidate sophisticated security measure or deny the IC's service. They pose a major threat to today's military systems, financial infrastructures, transportation security, and safety of household appliances. Even though advanced countermeasures against hardware Trojan insertion by an untrusted offshore fab exist (e.g., split manufacturing, Trojan-aware hardware design techniques), they are not a panacea since they might be circumvented. Thus, detection of inserted hardware Trojans is the only reliable mechanism to witness malicious circuitry. Since many resources are required to analyze and detect hardware Trojans in manufactured ICs (by using visual inspection), it is believed that only few institutions can actually address such concerns. This limits sophisticated institutions to perform further threat assessments of advanced hardware trojans e.g physical parasitic Trojans.

The focus of this thesis is to enhance the Hardware Reverse Engineering process for the scientific community and tackle the existing prejudice that invasive hardware reverse engineering is expansive and is only possible within wealthy institutions. We ease the deprocessing that is necessary for hardware reverse engineering that enables us to carry out more hardware security audits. Furthermore, we want to show additional steps for to detect advanced parasitic hardware Trojans that are hard to detect with known academic techniques.

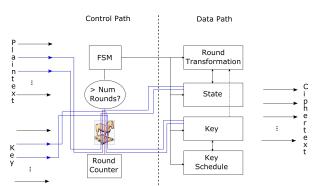

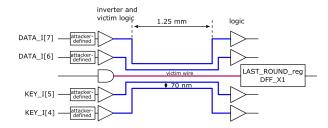

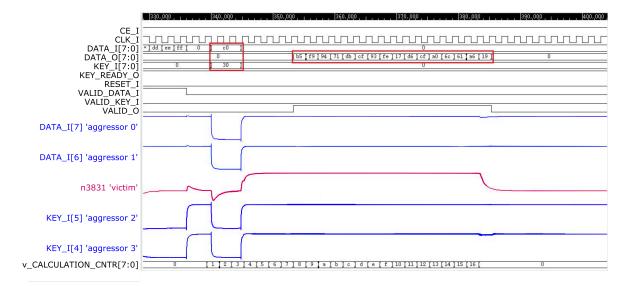

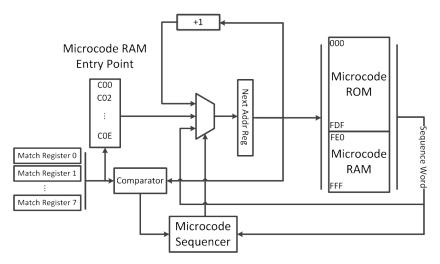

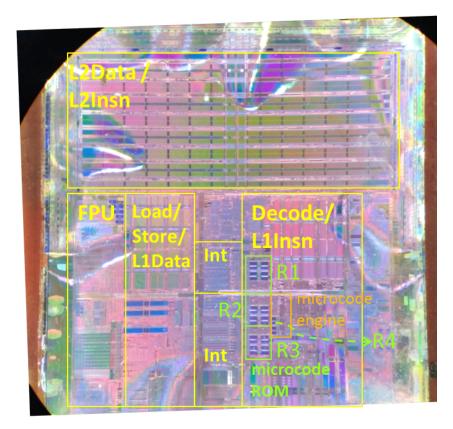

The first project, Security Implications of Voltage Contrast, introduces a new Region of Interest (ROI) detection method with the Scanning Electron Microscope (SEM) in a Voltage Contrast (VC) analysis. This technique allows us to gain valuable knowledge about the underlying hardware in a frontside and backside attack, which is beneficial for the hardware reverse engineering. Furthermore, we use the VC analysis in a new side channel attack for key leakage that designers and manufacturers must consider for future hardware protection. We use an XMEGA32A4U as our Device Under Test (DUT). The second project covers Security Implications of Intentional Crosstalk and evaluates the security of a new parametric Trojan, the crosstalk Trojan. In a proof of concept, we design an intentional crosstalk on a publicly available AES core that triggers secret key leakage and in the fully-fledged OR1200 processor to leverage user privileges. We discover that current hardware reverse engineering cannot cover this kind of malicious circuitry and extend the known process to mitigate the former. In the third project, Hardware Reverse Engineering of complex CPU-Microcode we target a modern fully fledged AMD K8 CPU to reverse engineer the microcode and extract the microcode ROM. In this thesis the focus is set on the microcode extraction that allows to gain knowledge of the microcode engine. We reveal the complex, highly optimized ROM architecture of a sophisticated, optimized CPU and use the knowledge gained to construct our own microcode updates.

The results of this project shows that we are able to gain valuable knowledge of even complex CPU internals and proprietary designs with common reverse engineering equipment. Furthermore, hardware reverse engineering can be extended to ease the planar deprocessing to a significantly smaller ROI while gaining valuable knowledge for any reverse engineering. Thus, much effort can be eliminated when using further techniques e.g., from the Failure Analysis (FA) community as support. Furthermore, we address the problem of parametric hardware Trojan detection and demonstrate a mitigation of the crosstalk Trojan that was introduced.

Abstract

#### Keywords

$\label{eq:Hardware Reverse-Engineering, Side-Channel, Physical Attack, Invasive Attacks, Hardware Trojans.$

## Kurzfassung

#### Fortgeschrittene Methoden für Hardware Reverse Engineering

In unserem täglichen Leben ist es unmöglich, den Umgang mit elektronische Systeme in unserer Umgebung zu vermeiden. Wir begegnen ihnen täglich entweder in direkter Form als PC und Laptop oder indirekt als Teil eines eingebetteten Systeme, wie zum Beispiel Mobiltelefonen und digitale Schlösser. Wir nutzen sie in unserem Alltag um unsere Gedanken, Ideen und Gefühlen über digitale Kanäle auszutauschen. Sie alle haben das gemeinsame Ziel, uns ein komfortableres Leben zu ermöglichen. Dementsprechend hinterlassen all diese Technologien und Innovationen einen digitalen Fingerabdruck unseres Alltages und unserer Person, der abgesichert sein muss.

Folglich bringen diese technologischen Fortschritte und Innovationen leider oft auch Sicherheitsrisiken mit sich, wenn unausgereifte kryptografische System zum Einsatz kommen. Wir könnten geheime Informationen, industrielle Geheimnisse oder militärsiche Vorgänge unabsichtlich verraten. Diese Risikien werden zu Bedrohungen, wenn Angreifer mit böswilligen Absichten anwesend sind, die Sicherheitsmechanismen eingebetteter Systeme direkt an der Wurzel aushebeln, indem sie auf unterster Ebene Chip-Komponenten ändern und zum Beispiel Integrierte Schaltungen während des Entwurfs und der Fertigung modifizieren. Böswillige Schaltungen, die auch als "Hardware-Trojaner" bezeichnet werden, können hochentwickelte Sicherheitsmaßnahmen ungültig machen oder notwendige Dienste behindern. Sie stellen eine große Bedrohung für heutige militärische Systeme, die finanzielle Infrastruktur, die Transportsicherheit, sowie Haushaltsgeräte dar. Obwohl fortgeschrittene Gegenmaßnahmen gegen hardware Trojaner (Split-Manufacturing, Trojaner-bewusste Design Techniken) existieren, sind diese kein Allheimittel da diese umgangen werden könnten. Damit bleibt nur die Detektion von ggf. eingesetzten Hardware Trojanern, durch visuelle Inspektion als verlässlicher Erkennungsmechanismus. Da für die Analyse und Erkennung von Hardware-Trojanern in Endprodukten (durch visuelle Inspektion) viele Investitionen und Ressourcen benötigt werden, glaubt man, dass nur wenige Institutionen solche Probleme lösen können.Folglich können nur wenige Institutuionen eine Gefahrenabschätung von Hardware Trojanern durchführen, besonders für weiterführende hardware Trojaner, beispielsweise parasitäre hardware Trojaner.

Der Fokus dieser Arbeit liegt auf der Verbesserung des Hardware Reverse Engineering Prozesses bei der Analyse von Systemen mit komplexen kleinen Hardwarestrukturen für die wissenschalftliche Gemeinschaft. Wir erleichtern die Deprozessierung der Hardware, welche für Hardware Reverse Engineering generell benötigt wird. Außerdem zeigen wir zusätzliche erforderliche Schritte um fortgeschrittene parasitäre Trojaner erkennen zu können.

Das erste Projekt, Sicherheitsimplikationen von Spannungskontrast, zeigt eine neue Erkennungsmethode, mit der ein kleiner interessanter Bereich mithilfe des Rasterelektronenmikroskop in einer Spannungskontrast-Analyse identifiziert werden kann. Wir verwenden eine Spannungskontrast-Analyse in einem neuen Seitenkanalangriff, die den geheimen Schlüssel ermittelt. Gleichzeitig ermöglicht sie durch Vorder- und Rückseiten-Angriffen wertvolle Erkenntnisse über die zugrunde liegende Hardware zu gewinnen. Der XMEGA32A4U ist der hierbei eingesetzte Versuchschip. Das zweite Projekt behandelt *Sicherheitsimplikationen beabsichtigter kapazitiver Übersprecher* und untersucht einen neuen parametrischen Trojaner, den Crosstalk-Trojaner. In einem Proof of Concept konzipieren wir ein beabsichtigtes Übersprechen auf einer internen Leiterbahn in einem öffentlich verfügbaren AES-Modul, in welchem der Trojaner einen geheimen Schlüssel offenbart. In einem weiteren Versuch mit einem modernen vollwertigen OR1200-Prozessor erhöht er bei gezielter Auslösung die Rechte eines Nutzers auf Adminrechte. Wir zeigen, dass der derzeitige Hardware-Reverse-Engineering Vorgang diese Art bösartiger Schaltungen nicht abdeckt, und erläutern die nötigen Erweiterungen für den bisher bekannten Prozess. Im dritten Projekt, *Hardware Reverse Engineering eines komplexen CPU-Microcodes*, haben wir eine moderne, vollwertige AMD K8-CPU untersucht, um den darauf verwendeten Mikrocode zu ermitteln und den Mikrocode-Speicher zu extrahieren. Wir zeigen die komplexe, hochoptimierte ROM-Architektur einer vollwertigen kommerziellen CPU und nutzen das gewonnene Wissen, um eigene Microcode-Updates zu erzeugen.

Die Ergebnisse der Projekte zeigen, dass auch moderne, komplexe CPU-Interna und proprietäre Designs erfolgreich analysiert werden können. Der Hardware Reverse Engineering Prozess kann erweitert werden, um die planare Verarbeitung auf eine signifikant kleinere Regionen zu begrenzen, was den Vorgang erleichtert und gleichzeitig ermöglicht, wertvolles nützliches Wissen für den Reverse-Engineer zu gewinnen. Wir zeigen, dass viel Aufwand erspart werden kann, wenn weitere unterstützende Techniken aus der Failure Analysis verwendet werden. Darüber hinaus befassen wir uns mit dem Problem der Erkennung von parametrischen Hardware-Trojanern und demonstrieren eine Abschwächung des eingeführten Crosstalk-Trojaners indem wir den Stand der Technik des Hardware Reverse Engineerings erweitern.

#### Schlagworte

Hardware Reverse-Engineering, Seitenkanalangriffe, Physikalische Angriffe, Invasive Angriffe, Hardware Trojaner

## Acknowledgements

This thesis is the result of the last four years, which I spent at the Chair for Embedded Security at the Ruhr-University Bochum and the Bundeskriminalamt in Wiesbaden. I've visited conferences, workshops and had hackathon-like meetings all over the world, meeting people with the same interests which were often also their hobbies. In the last four years, I traveled in moreor-less regular intervals between Wiesbaden and Bochum, balancing my work life, and social life with sports and family visits "in the North", as often as possible. Wherever I was headed I felt like having a second, third or even temporary fourth home. It was a fun time of meeting and working with people, having a slightly different mindset compared to students in the north, where i am from. Here, I would like to express my gratitude and thank those, who made all of this possible and enjoyable.

First and foremost, I would like to thank my family for all of the support throughout the years. I know that I can always count on them and ask for their support and help, being a safe-net and backbone. Thank you for all your support, faith, love and the courage to challenge myself in such a remote place. In Wiesbaden, I would like to thank my friend and colleague Jürgen Frinken, who fought the BKAs bureaucratic hurdles with me. Thank you for introducing me to this topic, the inspiring work and the experience throughout the years. Back in Bochum, I would like to thank my flatmates Benjamin, Phillip and Marc for the great time we had. Knowing Marc back from the days in Brunswick, we first joked on taking this path and now finished it. I have to admit that it felt great beating him constantly (even drunken) in Mario Kart.

Coming back to academia, I am very grateful to my supervisor, Christof Paar. Aside from the scientific guidance and the helpful advises, you always managed to motivate me. I am very grateful for the wonderful working atmosphere at our chair and want to thank my colleagues and friends. Special thanks go out to my escape room mates Basti and Max for challenging every room record with me and Christian Zenger for the "freibeuter" evenings.

Furthermore, I would like to thank Johann Machnik, Gerhard Wagner and my colleagues at KT52 for being helpful with their vast experience and knowledge whenever I needed an advice. Also thanks to the BKA badminton team, the MTV1817 volleyball team and the RUB Europahaus for a good counterbalance to my work life.

I would also like to thank further co-authors (in alphabetic order) for the joint research work: Gunnar Alendal, Omar A. Awad, Georg G. Becker, Malte Elson, Robert Gawlik, Thorsten Holz, Nikol Rummel and Sebastian Wallat. A very big "thank you" goes to those (un)lucky enough to proof-read my thesis in the various stages of writing: Jürgen Frinken, Erik Krupicka, Daniel Kison, Marius Eggert and Dennis Grubert. Last but not least, I want to thank our team assistant, Irmgard Kühn, who manages so many of the administrative tasks, keeps it off our backs, and is in general great, friendly person to talk to.

## Table of Contents

| Imprint                                       | v    |

|-----------------------------------------------|------|

| Preface                                       | vii  |

| Abstract                                      | ix   |

| Kurzfassung                                   | xiii |

| Acknowledgements                              | cvii |

|                                               |      |

| Preliminaries                                 | 1    |

| Introduction                                  | 3    |

|                                               | 5    |

| State-of-the-Art Hardware Reverse Engineering | 11   |

| 2.1 PCB Reverse Engineering                   | 11   |

| 2.1 PCB Reverse Engineering                   | 11   |

| 2.1       PCB Reverse Engineering             |      |

|                                               | 12   |

|

1

2

## 2.3 Gate-level Netlist Reverse Engineering 18

#### II Security Implications of Voltage Contrast and Intentional Interconnect Crosstalk

| 3 | Volt | age Contrast Side Channel Analysis              | 21 |

|---|------|-------------------------------------------------|----|

|   | 3.1  | Introduction                                    | 21 |

|   | 3.2  | Related Work                                    | 22 |

|   | 3.3  | Background                                      | 24 |

|   |      | 3.3.1 Voltage Contrast                          | 24 |

|   |      | 3.3.2 Static Voltage Contrast                   | 24 |

|   |      | 3.3.3 Dynamic Voltage Contrast                  | 25 |

|   | 3.4  | Voltage Contrast Analysis                       | 27 |

|   | 3.5  | Voltage Contrast Side Channel Analysis (VCSCA)  | 29 |

|   |      | 3.5.1 Obtaining Voltage Contrast Traces         | 29 |

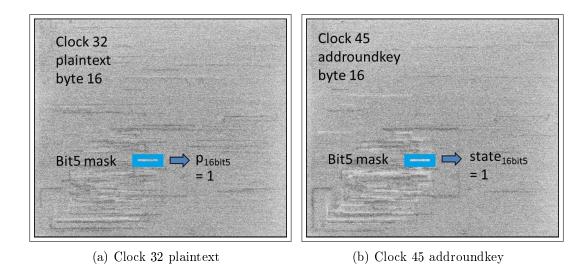

|   |      | 3.5.2 Locating AES Bit wires in a VCSCA         | 30 |

|   |      | 3.5.3 Extracting additional netlist information | 34 |

|   |      | 3.5.4 Template Attack with VCSCA                | 35 |

|   |      | 3.5.5 Simple VCSCA                              | 36 |

|   |      |                                                 |    |

19

|   | 3.6<br>3.7<br>3.8 | Backside Voltage Contrast Analysis373.6.1 ROI identification383.6.2 Preparation383.6.3 Backside Traces39Discussion39Conclusion41 |

|---|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 4 | Secu              | rity Implications of Intentional Capacitive Crosstalk 43                                                                         |

|   | 4.1               | Introduction                                                                                                                     |

|   | 4.2               | Background and Related Work                                                                                                      |

|   |                   | 4.2.1 Hardware Trojans                                                                                                           |

|   |                   | 4.2.2 Chip-level Hardware Reverse Engineering                                                                                    |

|   |                   | 4.2.3 Threat Model                                                                                                               |

|   | 4.3               | Crosstalk Trojan Design Methodology                                                                                              |

|   |                   | 4.3.1 Capacitive Crosstalk                                                                                                       |

|   |                   | 4.3.2 Design Methodology                                                                                                         |

|   | 4.4               | Case Study I: Cryptographic Designs                                                                                              |

|   |                   | 4.4.1 Crosstalk Trojan Design                                                                                                    |

|   |                   | 4.4.2 Crosstalk Trojan Implementation                                                                                            |

|   | 4.5               | Case Study II: OpenRISC 1200                                                                                                     |

|   |                   | 4.5.1 Crosstalk Trojan Design                                                                                                    |

|   |                   | 4.5.2 Crosstalk Trojan Implementation                                                                                            |

|   | 4.6               | Mitigating the Risk of Parasitic Trojans                                                                                         |

|   |                   | 4.6.1 Parametric Crosstalk Trojan Detection                                                                                      |

|   |                   | 4.6.2 On Sophisticated Parasitic Trojans                                                                                         |

|   | 4.7               | Discussion                                                                                                                       |

|   | 4.8               | Conclusion                                                                                                                       |

### III Real-World SoC Embedded Security Analysis

| 5 | Mic | ocode Mask ROM Extraction from a modern CPU                                                                                                                   | 65 |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 5.1 | Introduction                                                                                                                                                  | 66 |

|   | 5.2 | Background and Related Work                                                                                                                                   | 68 |

|   |     | 5.2.1 Microcode Background                                                                                                                                    | 68 |

|   |     | 5.2.2 Related Work                                                                                                                                            | 68 |

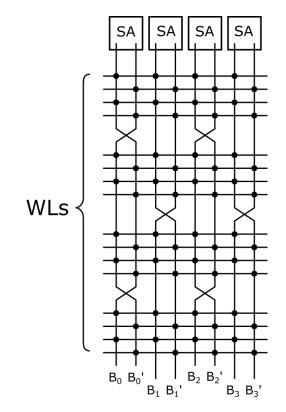

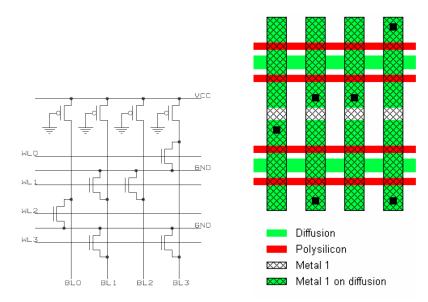

|   |     | 5.2.3 Mask Read-Only Memory (ROM) Readout                                                                                                                     | 69 |

|   | 5.3 | Reverse Engineering Microcode                                                                                                                                 | 70 |

|   |     | 5.3.1 AMD K8 and K10                                                                                                                                          | 70 |

|   |     | 5.3.2 Update Mechanism $\ldots \ldots \ldots$ | 71 |

|   |     | 5.3.3 Framework/Low-Noise Environment                                                                                                                         | 72 |

|   | 5.4 | Hardware Reverse Engineering of Microcode ROM                                                                                                                 | 73 |

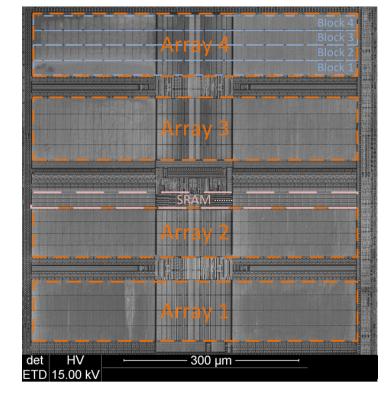

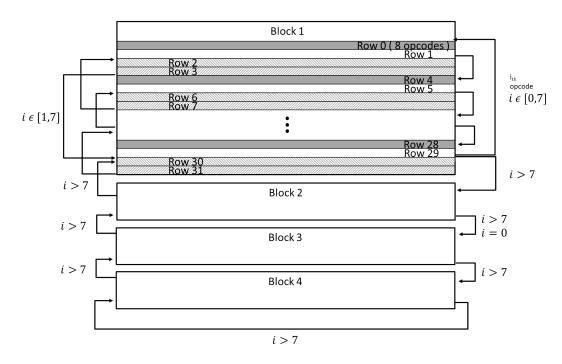

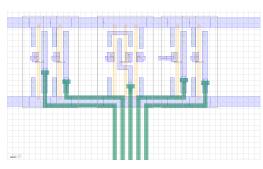

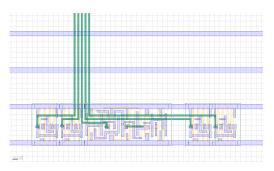

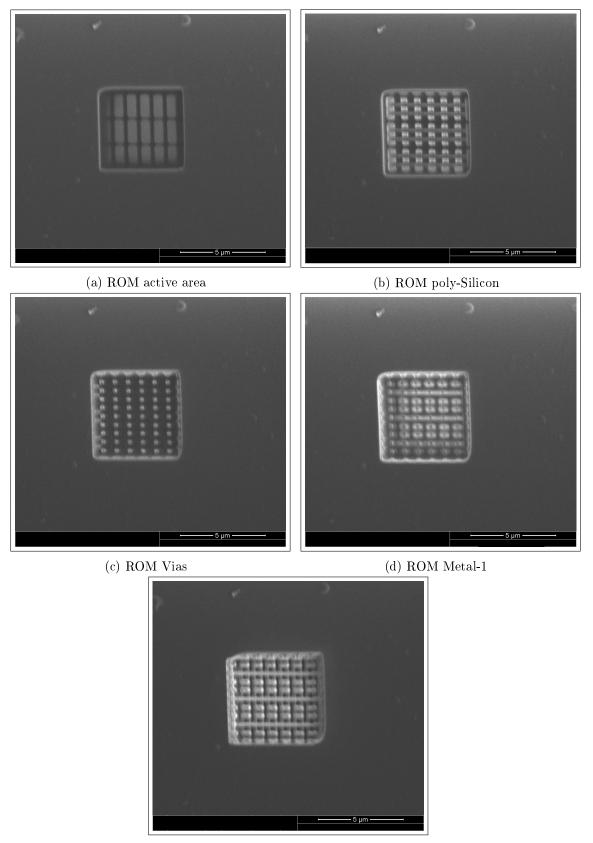

|   |     | 5.4.1 Microcode masked ROM Overview                                                                                                                           | 73 |

|   |     | 5.4.2 ROM structure and Memory Identification                                                                                                                 | 74 |

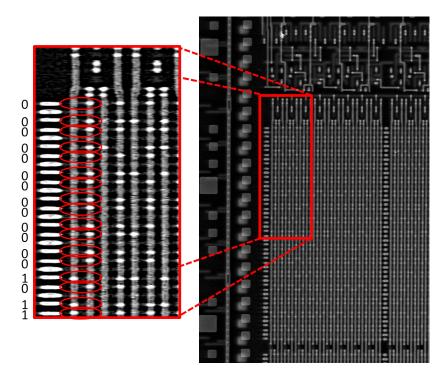

|   |     | 5.4.3 ROM Acquisition                                                                                                                                         | 75 |

63

|     | 5.5<br>5.6                | 5.4.4 Microcode ExtractionPhysical Mapping5.5.1 Microcode Emulation5.5.2 Physical OrderingConclusion | 78<br>79<br>80<br>80<br>82 |

|-----|---------------------------|------------------------------------------------------------------------------------------------------|----------------------------|

| 6   | Con                       | clusion and Future Work                                                                              | 83                         |

| IV  | Ар                        | pendix                                                                                               | 85                         |

| Α   |                           | age Contrast Side Channel Analysis Appendix<br>Additional Figures                                    | <b>87</b><br>87            |

| В   | <b>Secu</b><br>B.1<br>B.2 | urity Implications of Intentional Capacitive Crosstalk Appendix<br>Case Study: Cryptographic Designs | <b>89</b><br>89<br>89      |

| C   | C.1                       | rocode ROM<br>NOR ROM contact-layer                                                                  | <b>91</b><br>91<br>91      |

| Bi  | bliogi                    | raphy                                                                                                | 91                         |

| Lis | st of                     | Abbreviations                                                                                        | 105                        |

| Lis | st of                     | Figures                                                                                              | 107                        |

| Lis | st of                     | Tables                                                                                               | 112                        |

| Lis | st of .                   | Algorithms                                                                                           | 113                        |

| Ab  | out 1                     | the Author                                                                                           | 117                        |

| Pu  | ıblica                    | tions                                                                                                | 119                        |

| Co  | Conferences and Workshops |                                                                                                      |                            |

# Part I Preliminaries

## Chapter 1

## Introduction

In our daily life, it has become impossible to avoid electronic systems in our surroundings. We encounter them in the direct form, such as a PC and laptop or indirectly, as part of an embedded system, such as mobile phones and key locking systems with the common goal to create a more comfortable life. We use them in our everyday activities to communicate our thoughts, ideas, and feelings over digital channels or subconsciously in routine work.

With *Home automation*, we allow digital systems to control one of our most important and intimate zones. They can observe the house's inside temperature, open windows, and stove. They can even automate daily tasks, such as starting the heater, opening rolls or the door without being physically near the house.

Sensors and actors in the *car environment* are responsible for our entertainment and safety while some applications allow piloting on the driveway. They have become inevitable in today's fuel usage optimization and especially in critical safety applications, ranging from airbag control to smart break assistance in pedestrian protection. They can even make ethical decisions when choosing crash prevention courses.

Safety critical applications also appear in other fields, such as *health care*, *aerospace*, and *industry applications*, surveying potential dangers e.g., in hazardous environments. Even noneconomic areas, like the military, space exploration, and political parties depend on electrical systems, such as digitally controlled military equipment and poll systems. They are increasingly accepted in a number of countries. These systems often enjoy such high levels of trust that they have become a pillar of our society.

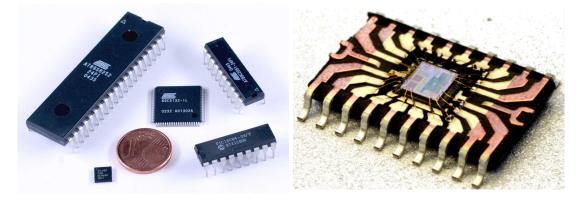

Figure 1.1: Multiple packaged microantroller ICs(left) and a depackaged IC(right).

The core of almost any embedded and digital system is an IC or a more advanced Central Processing Unit (CPU). Some exemplary microcontrollers ICs are shown in Figure 1.1. Depending on their applications, we have systems with varying complexity. While small power-saving Microcontroller (uC) can be used in small home automation projects, other more complex systems, such as modern cars, have more than 100 controllers. Computationally expensive ICs like CPUs and Graphics Processing Units (GPUs) are used in servers and desktop machines. Between them reside the embedded systems with a fluid transition on both sides. With today's' smartphone calculating powers, it has become hard to count them as a part of an embedded system or a fully hand-held desktop machine. Cars have also become increasingly powerful with complex automatic pilot/driving applications. Even Application Specific Integrated Circuits (ASICs) as dedicated hardware chips for one specific task, containing a static circuit, are included.

The increase in computational power has allowed artificial intelligence with neuronal networks to reemerge, benefiting from dedicated ASICs and complete human tasks in fascinating ways. Various scientific fields, such as biology, medicine, and computer science apply specialized neuronal networks in their research. Another miscellaneous application, *GO*, known as the last board game with a human in the lead, has been conquered with neuronal networks running on Tensor Processing Unit (TPU) ASICs. An ever-increasing demand for new IC designs and solutions exists.

IC Design High-volume IC production is based on a vast, globally distributed network of designers, vendors, and fabrications. Designers and vendors are economically driven to optimize their design and use the latest fab while the fab pushes to ever smaller technology sizes. Starting with *Moore's law* from the 1970s, it was estimated that Complementary Metal Oxide Semiconductor (CMOS) technology size shrinks by half every 18 months. Hereby, the width of the transistor gate is the naming factor of the technology node, even though in modern technologies, this is not always true. In fact, in the 14 nm technology size introduced by Intel in 2017, not a single element is close to the size of 14 nm. This might be an indicator that Moore's law might no longer hold true. Nevertheless, the industry continues the naming convention of the technology (half-)nodes.

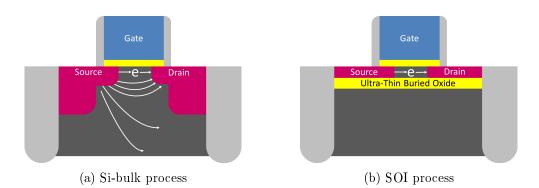

The IC industry earned 412.2 billion USD in the year 2017. International Roadmap For Devices And Systems (IRDS)'s estimations for the first ICs with 7 nm technology are expected in 2019, while 5 nm is expected to be produced in the year 2021. Each shrinkage introduces new problems and further requirements on the purity of the materials. New equipment requires constant parameter fine-tuning while maintenance is enough to reset all efforts. The requirements for further technology nodes can be illustrated with the actual size under 10nm: this gate width is equivalent to less than 100 atom layers. Small impurities can easily result in one defective transistor out of the billions rendering the sample useless. Any defect, such as a transistor that does not meet speed or power constraints, results in a worse yield. Hence, new technology is only enrolled when it results in an economic advantage. To this extent, the vendors introduce ever more sophisticated techniques, like 3-dimensional gates (FinFET), Silicon-on-Insulator (SOI) processes, hyperscaling, and UV light lithography, driving the price for a new fab to a new height of 8.5 billion USD.

The yield of the fab is a direct factor for the IC industry's margin, causing it to become the most important factor for the economic rentability. This sets the resources for yield improve-

ments as basically unlimited. To underline its importance, the IRDS even has its own *yield* enhancement group, optimizing solely this field. The specialized process for finding, identifying, and preventing IC faults during the fabrication is the **Failure Analysis (FA)**. By creating a process of analyzing faults and fine-tuning the fabrication, the yield has steadily improved. FA research is presented yearly at the ISTFA<sup>1</sup> conference.

**Failure Analysis (FA)** techniques are dedicated to locating and isolating the faults produced during the fabrication or further preparations. They include all production steps from a large area fault during packaging to small cracks in the gate isolation or impurities in the wafer. Please note that FA techniques are applied from the vendor with all the necessary information of the layout, a debugged interface and simulations. They do not include basic design choices prior to simulations. If the fault cannot be explained by the extended debugging interface in a chip, first non-invasive techniques for a coarse ROI localization can be used, such as measuring sidechannels, like heat, photonics, electro-magnetic (EM) emanation, and power consumption. For fine localization advancement, more invasive techniques e. g., Laser Voltage Probing (LVP), VC, and Atomic Force Microscopy (AFM), which exploit the physical characteristics of the CMOS technology, are considered. Once their results are compared to simulated data from Electronic Design Automation (EDA) tools, the ROI location can be determined with high accuracy. Sometimes, multiple techniques can be cascaded to further pinpoint the ROI.

Once the fault has been isolated, the last steps of the precise sample preparation are completed with a Focused Ion Beam (FIB) system to determine the exact fault. The FA has the major drawback that only a small number of samples—or even just one unique sample—exist. Deprocessing in a small technology size remains a challenge. Sample preparation requires expertise and necessary equipment to reliably reveal the faults. Please note that it might be necessary to prepare the sample for the FA technique(s) as well, without damaging the sample or excluding other techniques with this step.

FA processes have been well studied due to ample funding, and they are powerful tools in used to analyze the inner workings and state of the IC. They are useful to gain additional knowledge of any IC-internals. Since this highly specialized equipment is bought by the industry, it comes with a heavy price tag that academia is unable to spend. Furthermore, to fully utilize the FA techniques, in-depth knowledge from the devices is mandatory. If this knowledge is not present, the IC has to be reverse engineered.

Hardware Reverse Engineering: In general, the process of acquiring in-depth layout and schematic information of an unknown IC and its environment is called Hardware Reverse Engineering. It is the main focus of this thesis. In the context of an IC design supported FA, the engineer acquires necessary details from the designer. Nevertheless, in most cases, customers and third-parties do not have such a source of information, even though design internals of discontinued ICs are required.

Rapid advances and innovations result in short technology life cycles for hardware and software components. Once the hardware has a new revision, old ICs become obsolete and are discontinued. This becomes a problem when outdated hardware components wear out and further equipment depends on highly specialized, proprietary interfaces. They become unavailable

<sup>&</sup>lt;sup>1</sup>International Symposium for Testing and Failure Analysis

for repairs or replacements since nanoscale chip repairs are generally very difficult. In the worst case, expensive industrial equipment, tools, and machines are on standstill due to a single defect IC component with unknown circuitry or some valuable data persists in inaccessible memory. Hence, the chip must be reverse engineered for reproduction or forensic analysis. Forensic applications can access lost (key-)data and determine evidence in law enforcement cases through hardware reverse engineering.

Special ASICs Intellectual Property (IP) cores are increasingly included during the IC design phase. They are inserted either as hard-wired or soft cores, depending on the buyers' license and preference. Hard-wired cores are delivered as already-routed layouts, while soft cores are placed and routed during the IC design and are usually more expensive due to their flexible options. Depending on the license, a certain number of copies or design changes are allowed. The hard-wired cores are usually performance-critically routed, or given unannotated to counter overproduction and intellectual theft. The already optimized design has been researched, developed, and tested. If enough knowledge has been generated, it is patented. In the presence of malicious competitors that try to cut their investments and illegally copy or overproduce an already finished design, the legitimate IP holder requires a means of control. Hence, hardware reverse engineering can be used to analyze the suspected designs and detect IP fraud. Interestingly, this shows hardware reverse engineering has two faces as it is first used to reverse engineer protected IP cores, but also for detection of the former.

In the cryptographic community, the risk of proprietary 'security-by-obscurity' systems is well known. Multiple examples from the recent past show that vendors sometimes design immature and dangerous cryptographic systems. They risk leaking personal data, industrial expertise, and military insights once the obscurity vanishes. Once the chip is deployed and a vulnerability is discovered, (hardware) patches are possible (in very few cases) and might force massive hardware rollbacks and damage the reputation. In order to protect against these risks, it is recommended to use well-known cryptographic primitives, and vendors need to certify security-related designs. Hardware security audits guarantee security by testing against non-invasive and semi-invasive attacks in certified laboratories. Reverse engineering can lead to the discovery of further weaknesses (e.g. Side-Channel Analysis (SCA) or invasive probing attacks) and improve security certificates.

Security risks become threats in the presence of malicious adversaries that try to exploit or create system weaknesses for personal gains. They can bypass embedded system security or create vulnerabilities at the very root by altering any core IC component, e.g. modify the circuitry during design or fabrication. In the worst case, an adversary starts tampering during the IC design phase and denies further security patches after roll-out. Malicious circuity *a.k.a.* known as 'hardware Trojans' can invalidate sophisticated security measures or deny the IC's service. Therefore, they pose a major threat to today's military systems, financial infrastructures, transportation security, and household appliances [143]. Since ample resources are required to analyze and detect hardware Trojans in manufactured ICs (by using visual inspection), only a handful of institutions can actually address such concerns [143].

With further advances in Trojan design, only invasive hardware reverse engineering strategies can counter such circuits, particularly when no golden model is present, or the golden model has to be verified [145, 143]. Nevertheless, the search for countermeasures has become of increasing interest in academia. Embedded system security has become an important academic sub-discipline with high industrial participation. In particular, they attempt to (i) find respective malicious circuits [26], (ii) secure the IC design [153, 52], or (iii) secure the production chain [74, 15].

Ideally, the results of hardware reverse engineering provide a complete understanding of the underlying IC. With modern multi-billion transistor ICs, this is an infeasible task without automatic solutions. Even considering that tedious tasks can be automated, human interactions are required for understanding the resulting sea-of-gate. Thus, the task of hardware reverse engineering is a dedicated, specialized task, often taking several months of work. Reverse engineering only selected parts of the IC eases the process and saves resources. Once the exact implementation of the interesting parts, such as hardware Advanced Encryption Standard (AES) accelerator or memory encryption unit, is known, there are further non-invasive or semi-invasive attacks possible against which the designs are not protected.

Side Channel Analysis (SCA) Non-invasive attacks are attacks that do not change or alter the chip internally and externally. They observe the DUT during operation to attack the *implementation* of an algorithm through their observed side channels. These include heat, photonics, EM emanation, sound, and power consumption. These observations allow derivation of internal signals and secret key material with different leakage models and data hypotheses. This highlights that any algorithm running in the IC can be attacked with side channel attacks if the implementation is known and no generated on-chip randomness is used. Hence a-priory hardware reverse engineering is mandatory for unknown proprietary algorithms before they can be attacked with SCA. Semi-invasive die preparation improves existing side channels, such as the EM emanation. Otherwise, it creates access to side channels, such as the photon emission from the backside of the chip. Please note that side channels have also been used for hardware reverse engineering in Side Channel Analysis for Reverse Engineering (SCARE) attacks [106, 47, 60, 151, 10, 142, 68, 53, 40].

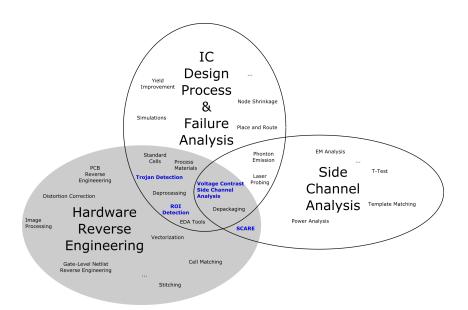

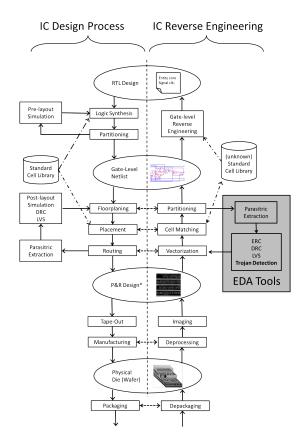

In the context of the three topics of the IC design, the failure analysis and side channel analysis interdisciplinary topics can support the academic topic of hardware reverse engineering. Figure 1.2 shows possible intersections with highlighted topics that are related to this thesis.

Aim and contributions of the thesis: The aim of this thesis is to improve hardware reverse engineering. The contributions of this thesis show that the current state of hardware reverse engineering (1) can be linked with other side-channel and failure analysis techniques. This can be done to help the hardware reverse engineer prior to the tedious gate-level netlist reverse engineering. It is (2) not sufficient to include advanced emerging parametric Trojans and (3) can be extended with a proposed process-flow to detect parametric Trojans. An overview with contributions (1) to (3) can be seen in Figure 2.2. Finally, this work (4) shows the reverse engineering process of an optimized mask NOR ROM in a modern, fully-fledged CPU to help reverse engineer its microcode engine and content. To show statement (1), we introduce the Voltage Contrast Side Channel Attack (VCSCA) that uses the VC to gain additional knowledge of the function of wires and gates within the sea-of-gates. In order to show the statement of (2)

Figure 1.2: An incomplete intersection Diagram of Hardware Reverse Engineering, the Failure Analysis coupled with the IC Design and Side Channel Attacks point out some possible interdisciplinary topics.

and (3), this thesis presents a new parametric Trojan that is impossible to detect using stateof-the-art hardware reverse engineering and gate-level netlist reverse engineering. In fact, it is difficult to see the Trojan if the reverse engineer does not know of its existence.

Please note that this thesis focuses on the hardware aspect of deprocessing and die reverse engineering prior to the gate-level netlist. Some publications rename "hardware reverse engineering" as IC reverse engineering or *silicon reverse engineering* to highlight the sub-Printed Circuit Board (PCB) reverse engineering. Algorithms and techniques for post gate-level netlist reverse engineering have a sizeable academic community to automatically detect high-level abstractions, but are not the main part of this thesis. Another adjoining academic field camouflages gates to increase the reversing effort. Some publications have been done in academia, but during the time of this work, no real-world camouflaged gates emerged that would have an impact on the practical current, state-of-the-art hardware reverse engineering. Hence, both academic topics are mentioned and discussed in the respective chapters.

**Structure:** This thesis is divided into three parts, followed by an appendix. Part I consists of the preliminaries, including this introduction and the current state of hardware reverse engineering (Chapter 2). Part II presents the academic analysis of voltage contrast and capacitive crosstalk projects in detail. We start with a side channel attack against a real-world XMega32A4U in Chapter 3 to obtain a full key recovery of a dedicated AES core and review different methods of how the VC can support a hardware reverse engineer in his tasks (contribution(1)). Chapter 4 includes the implementation of a new kind of parametric hardware Trojan that exploits the capacitive crosstalk effect for malicious purposes (contribution (2), (3)). Chapter 5 in Part III covers the hardware reverse engineering of microcode mask ROM from a real-

world, fully-fledged and modern CPU (contribution (4)). The thesis concludes with suggestions for future work and closing remarks in Chapter 6.

## Chapter 2

## State-of-the-Art Hardware Reverse Engineering

In this chapter, we systematically survey hardware reverse engineering. To this end, we examine diverse methods and techniques to analyze Integrated Circuits (ICs) and Application Specific Integrated Circuits (ASICs) in order to retrieve the crucial (annotated) gate-level netlists of a hardware design in Section 2.1 and Section 2.2. The goal of the reverse engineer is to understand (parts of) the design's inner workings in order to perform another high-level task, i.e. to detect counterfeit products or to inject hardware Trojans. Therefore, we briefly discuss the state of the gate-level netlist reverse engineering (Section 2.3), which focuses on the retrieval of high-level Register Transfer Level (RTL) information (e.g. control unit or datapath components). Please note that the gate-level netlist can be obtained through several means in multiple real-world scenarios, i.e.

- (1) chip-level reverse engineering (see Section 2.2),

- (2) bitstream reverse engineering in case of Field Programmable Gate Arrays (FPGAs),

- (3) directly from the layout in case of an untrusted (off-shore) foundry or from an Intellectual Property (IP) provider.

Note that this model is consistent with prior research on hardware security [9, 35, 116, 26].

A survey of anti-reverse engineering techniques is out of the scope of this work, but the interested reader is referred to [59].

#### 2.1 PCB Reverse Engineering

The deprocessing of hardware reverse engineering starts at the Printed Circuit Board (PCB) and package level of the piece of hardware. Firstly, the IC is removed from the PCB e.g., through desoldering or drilling. The challenge to protect the die is becoming ever more difficult with reduced die size, Ball Grid Array (BGA) grid pitch, die thickness, and even underfilled flip-chip packages. Secondly, the mold package must be removed with wet-chemical or mechanical means. Hereby, the die is to be protected, which often results in choosing wet-chemical depackaging, as the die is protected by the seal-layer<sup>1</sup> from the front side. The backside offers enough silicon in bulk to withstand carefully applied depackaging processes as well. The bonding wires are of special concern, as newer copper bondings are, compared to gold bonding wires, difficult

<sup>&</sup>lt;sup>1</sup> passivation, often  $SiO_2$

to preserve. For invasive hardware reverse engineering, the wires can be neglected once their connectivity is known or the connectivity can be derived. Advanced techniques for finding bonding wire connectivity can be completed with (3D) micro-X-ray-tomography or selective packaging delayering with a mill.

#### 2.2 Chip-level Reverse Engineering

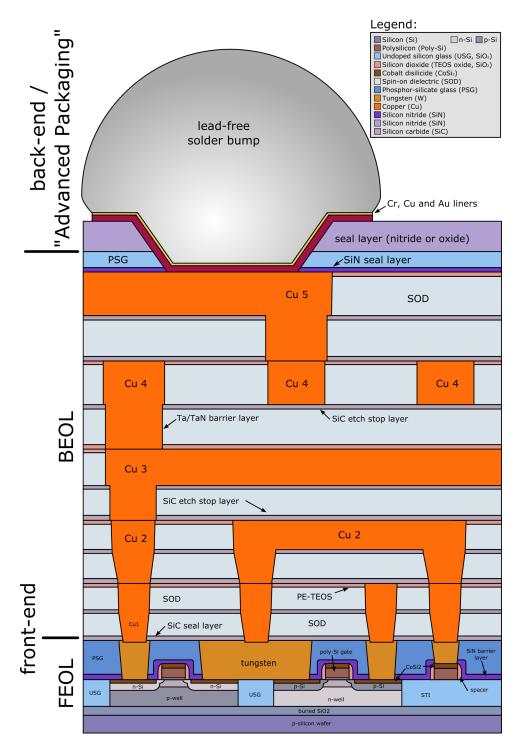

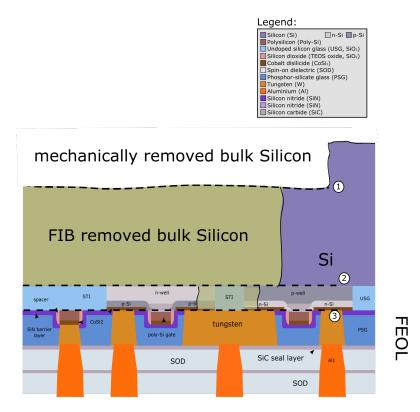

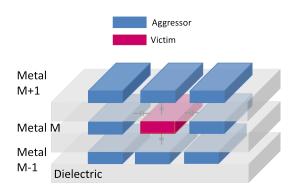

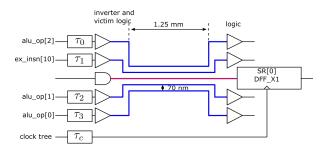

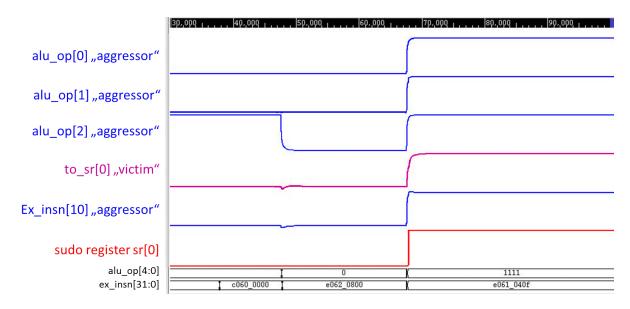

To learn the gate-level netlist of an ASIC post-manufacturing, chip-level reverse engineering has to be performed when the gate-level netlist cannot be obtained through other sources. Here, the goal is to deprocess and image the IC layers until the IC is fully digitized and interpreted as an error-free gate-level netlist. To this end, various steps are involved: (1) depackaging and mechanical preprocessing, (2) delayering and imaging, and (3) software-based post-processing [108]. An overview can be seen in Figure 2.2. The hardware reverse engineering is coupled with the IC design process it is supposed to reverse. Common practices (e.g. routing styles, standard cell rows, ....) and optimizations(e.g. flipped standard cell rows, ....) have great potential to ease, correct, and optimize steps in the hardware reverse engineering process. They are indicated with dashed double arrows in Figure 2.2. Each step for hardware reverse engineering will be explained in more detail in the following. The interested reader is referred to [155] for details in the IC design process. A schematic of a stacked IC can be seen in Figure 2.1.

#### 2.2.1 Depackaging and Physical Preprocessing

The first hurdle of chip-level reverse engineering is to depackage or decapsulate the molded chip to gain access to the physical design. This process depends on the package and is done through wet-chemical or mechanical means. In particular, the die must be protected from any harm. Typically, wet-chemical depackaging is chosen since the die is protected by a seal-layer from the front side (often a  $SiO_2$  passivation layer). Note that the backside usually has a silicon bulk stabilizing the die to withstand careful depackaging processes. Additionally, bonding wires are of special concern during any (semi-)invasive attacks while the chip remains operational.

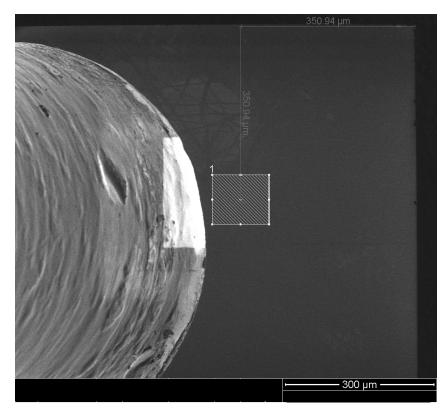

Special packages, e.g. fully embedded ceramic packages or metal cases, might be hard to etch. They have to be mechanically drilled with a powerful Computerized Numerical Control (CNC) drill or by hand. Please note that Cu bondings are of special concern for future work with the IC industry mitigating to Cu processes, for production cost reasons. After fully depackaging the die, preparation to retrieve the physical design from Figure 2.2 is started. Prior knowledge through Failure Analysis (FA) andVoltage Contrast Side Channel Attack (VCSCA) as introduced in Chapter 3 are very valuable at this point.

**Deprocessing.** Hardware reverse engineering through visual inspection is an invasive, destructive process used to extract functionality information from the ICs. Therefore, IC dice are thinned in an alternating delayering and scanning process to obtain an image of every stacked metal and polysilicon layer.

The delayering process is a combination of wet chemical, mechanical, and plasma processes (often summarized as Chemical Mechanical Polishing (CMP)) to optimize the planarity of the die and the contrast for the imaging step via Scanning Electron Microscopes (SEMs)[108, 145]. In particular, planarization of the current layer with a large *surface-to-thickness* ratio is challenging.

Figure 2.1: An overview of a stacked IC in a copper process. The front-end is built first with all the technology cells while the back-end interconnects respective cells. The schematic shown is a copper process with 5 metal layers and a SOI technology(see the buried SIO<sub>2</sub>). Source in the list of Figures.

Figure 2.2: IC Reverse Engineering compared to the IC design process. LVS: Layout versus Schematic; DRC: Design Rule Check. \*The Placed and Routed Design (P&R Design) includes cell instances for proprietary standard cells (for the fab) during the IC Design process, in contrast to unannotated designs during Hardware Reverse Engineering. Contributions of this thesis are shown in green. Furthermore, it is very beneficial if the locations of the Region of Interest (ROI) are known, as the necessary planar surface is reduced significantly. The reverse engineer can then focus on his ROI while neglecting the rest of the chip [85]. These steps usually require expensive equipment and experienced users, as the shrinking technology node makes the process of planar delayering exponentially difficult. The risk to destroy the ICs under investigation always remains and requires multiple samples. The equipment resources increase with shrinking technology size, along with the necessary imaging time, precision, alignment, and calibration needs.

The complexity of deprocessing is further increased with current material changes to decrease costs and improve physical properties e.g., low K-materials and copper wire/via technologies. Each IC requires slight adjustments in equipment parameters and processing duration. In the following, we briefly introduce possible equipment.

Mechanical Polishing/Lapping tools are mandatory to polish in a "planar" way. It is mandatory to fix the sample on a flat surface prior to the polishing process. Two kinds of automated polishing methods are known: (1) is the lapping with a flat lapping stone while (2) is a very precise CNC drilling machine. Both types have adjustable spring forces used to press the sample with defined forces onto the lapping substrate. Surface alignment is done with a collimator or an accurate height measurement with a CNC-like setup. Please note that the IC surface can initially be curved due to packaging materials creating mechanical stress. Furthermore, as the lapping in the corners and edges is more intense (as a constant force is applied to a smaller area), a "bullseye" effect easily happens. This forces a reverse engineer to reduce the lapping time as much as possible and remove more material with other techniques.

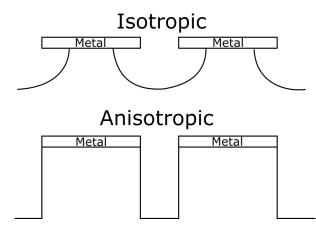

Wet chemical processes have the major drawback of being isotropic, which can become harmful as deprocessing requires a planar surface in contrast to isotropic etching behavior. An example with two interconnects can be seen in Figure 2.3. Furthermore, the chemicals for etching (mostly fluoric-acid) SiO<sub>2</sub> are hazardous and toxic. It is not recommended to use them at all without the necessary safety gear. There are wet chemical processes used to selectively etch materials, such as Al and Cu. These can be used in one of the last steps, e.g., to etch Al to highlight the underlying Ti/TiN compared to the W vias shown in the imaging.

Figure 2.3: Isotropic compared to anisotropic etching. The isotropic etch might underetch structures, decreasing the stability. Anisotropic etching can done during plasma (dry) etching.

**Dry/Plasma Etching** is the process of etching with a plasma source, known as etch species. It can be either charged (ions) or neutral (atoms and radicals). A significant advantage to wet etching is the "directional", anisotropic etching which is more beneficial for planar processes. Plasma etchers are usually cut-off chambered machines where the Fluorine<sup>+</sup> radicals are fewer in numbers and exist only in a small chamber without human access during the processing. It is well researched in the context of the IC design process. Gases can be used to etch different materials selectively[21].

**Broadband Ion Beams** use the same physical principles as a Focused Ion Beam (FIB). Ions are accelerated to hit the surface of the IC at a very small angle but are not focused on a single spot or rastered. This physically knocks out ions from the surface of the sample in a slow process. As in the plasma process, different gas combinations can be used to specify a selectivity in the materials to be removed or speed up the process, imitating the plasma process.

Every IC has a different chip manufacturing process due to cost optimizations or technology node requirements. Therefore, different conductors, semiconductors, and dielectrics must be investigated and selectively removed without destroying the functional information of the IC [108]. Recipes from the IC fabrication or the FA are used or at least used as a starting point. For modern, nanoscale technologies, it is essential to use the necessary equipment to approximate or measure remaining layer thickness. Deprocessing quality can be assessed with invasive cross-sectioning or non-invasive optical-based thickness measurements.

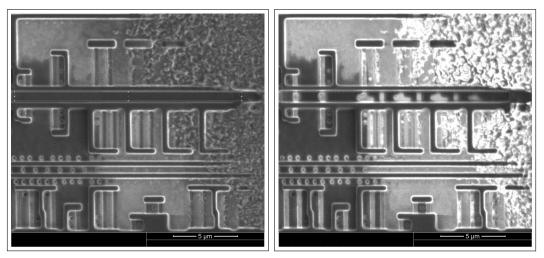

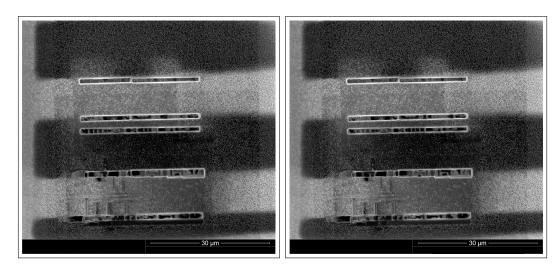

**Imaging** In state-of-the-art reverse engineering, digitalizing and imaging is performed using a SEM or even a more eroding FIB. Since modern technology sizes hit the diffraction limit of optical microscopes, more advanced visualizing tools are mandatory. Such modern equipment is costly, but it results in higher magnification of images. A clear brightness yielded from the SEM images is beneficial for post-processing as it allows us to distinguish between vias, wires, and spin-on dielectric (SOD), see Figure 2.4. Usually, the sample has to be prepared to prevent the accumulation of electrical charges during the imaging process. The deposition of a very thin C surface layer through evaporation or low vacuum chambers are reasonable solutions. Further parameters, like acceleration voltage and precise stage movement, are beneficial for the following stitching and imaging processes.

Figure 2.4: Example of metal 1 layer is shown. Brightness allows to distinguish between wires(light grey), vias, and the SOD(dark areas). The brighter dots are vias between Metal 1 and Metal 2.

An in-depth understanding of the physics of the processes and the necessary equipment are mandatory for achieving an adequate delayering quality. Basic recipes and processes are taken from the FA community as they have similar goals when isolating faults.

#### 2.2.2 Software-based Post-processing.

In order to generate a functional chip representation from the digitized tile images (mosaic of a big image) of the previous step, the tile images have to be stitched and vectorized. This step can be separated into a Back End of Line (BEOL) and a Front End of Line (FEOL) process.

**Vectorization/BEOL.** To vectorize the BEOL, different image processing techniques have to be used to differentiate lines that are wires, circles and, dots(vias), as shown in Figure 2.4. In older process technologies, they appear due to the material mass differences of the aluminum wires and the tungsten vias. This difference can be used to separate the vias from the wires in a first step. Further geometrical constraints from the routing and placement geometries can be applied to improve the results.

Known wire extraction is based on edge detection[90] or grid based[78]. To improve the detection, image filters can use common geometrical design rules for vectorization. As the routing is commonly done in full  $\lambda$  steps, a constant minimal separation distance can be used to create a Design Rule Check (DRC) grid. Matching these with the underlying image allows for the detection and extraction of line segments. During the common routing process, two following layers have primary routing directions with a 90-degree shift. If the Metal-2 layer is routed horizontally, the next Metal-3 layer is routed vertically to create an orthogonal mesh, which is helpful for automatic line detection.

**Cell Matching/FEOL.** As most IC are built from a standard-cell library, containing around 50-300 cells, we first identify standard cells, including their rotated and mirrored versions to find their instances positions. Each standard cell is first recognized manually, and its function is reverse engineered once. Layers containing the active area, poly-silicon, and Metal-1 are necessary for manual cell reverse engineering. When the cell is identified, it can be automatically detected by using the images from the FEOL(e.g. poly-Silicon and M1) through image processing. As the (stitched) images are never free of faults, the image processing has to be robust and tolerant in order to recognize cell instances. Hence, pattern recognition, like template matching, is preferable. With robust cell image filters, the image can still be recognized with small defects(scratches, dust) and small routing differences (cell I/O, Metal-1 routing) in the image IC structures. Figure 2.5 shows the three standard cells that were detected.

Additionally, it is possible to automate the manual part in the FEOL recognition with Layout Versus Schematic (LVS)-like algorithms[51]. The images are first vectorized as in the BEOL process and in the following cell-parted in order to isolate single cell candidates. Then, a LVS algorithm is compared with each possible standard cell to find the function of the respective cell candidate. The authors of [51] automatically isolated and identified standard cell functionality with a database of known cell libraries. This LVS-like algorithm compares the transistors and its connections with annotated known transistor connection networks in a database. This allows us to identify cells, even if the cell library is from a different technology size or has different buffer strengths. Finally, with the standard cell instances in the FEOL and their connections through the metal lines in the BEOL, the ROI is extracted as a gate-level netlist.

Figure 2.5: Cell Recognition of three standard cells on Metal-1. Small scratches in the bottom part and routing optimization on Metal-1 might disturb the recognition.Not that recognized cells are also mirrored and rotated.

## 2.3 Gate-level Netlist Reverse Engineering

After having specified how a reverse engineer can access the gate-level netlist for ASICs designs, we now provide an overview of publicly documented reverse engineering techniques to retrieve high-level information (e.g. control units or hierarchy information of submodules). Please note that gate-level netlist reversing techniques for FPGAs designs can be applied at this point as well.

Chisholm *et al.* [38] presented a workflow on how to reverse engineer module-level descriptions from gate-level netlists, addressing the synergy of the human analyst's creativity and the computer's ability to solve repetitive tasks. In a case study, Hansen *et al.* [71] described several best practices for a human analyst to reverse engineer gate-level netlist. Shi *et al.* [127] evaluated a technique to automatically reverse engineer a Finite State Machine (FSM) from gate-level netlists. Meade *et al.* [100] extended this technique in order to retrieve the state transition function for the reverse engineered FSMs. In further work, Meade *et al.* [99] developed a technique to separate control unit registers from datapath registers. In order to automatically reverse engineer functional submodules in a larger hardware design, diverse techniques have been developed based on Boolean function analysis [126], pattern mining of simulation traces and model checking [92], module boundary identification [135, 134], and word-level structure identification [93].

Since the functional identification of subcircuits requires us to find the correct matching between known subcircuits and the subcircuit under inspection, a reverse engineer has to find the correct input permutation. To avoid this computationally demanding task, Gascón *et al.* [64] addressed this problem with a template-based solution.

## Part II

# Security Implications of Voltage Contrast and Intentional Interconnect Crosstalk

## Chapter 3

## Voltage Contrast Side Channel Analysis

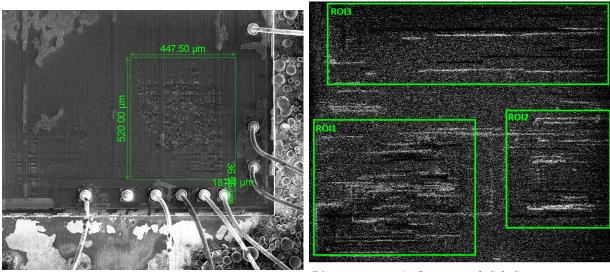

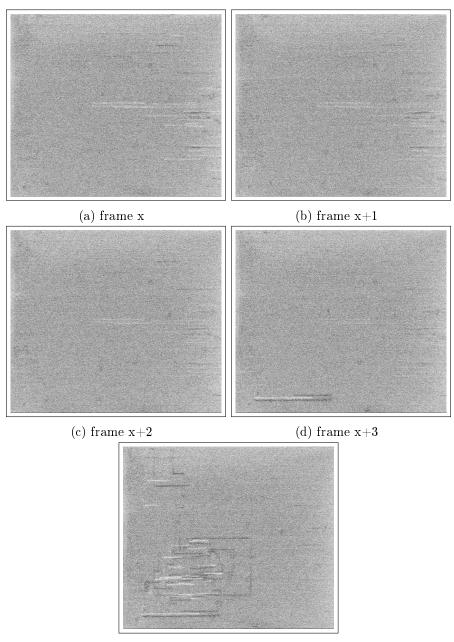

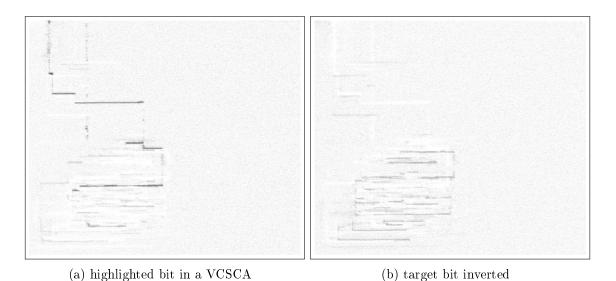

This chapter demonstrates how the Scanning Electron Microscope (SEM) becomes a powerful tool for Side Channel Analysis (SCA) and Hardware Reverse Engineering through Voltage Contrast analysis. This enables an attacker to locate AES bit-wires in the top metal layer and thus, to recover valuable netlist information. An attacker gets a valuable entry-point to look for weaknesses or Intellectual Property (IP) in the AES circuit. The results were published in [85] and extended by a backside approach in Section 3.6. The publication is a joint work with Jürgen Frinken.

#### **Contents of this Chapter**

| 3.1        | Introduction                                   | 1        |

|------------|------------------------------------------------|----------|

| <b>3.2</b> | Related Work                                   | <b>2</b> |

| 3.3        | Background                                     | 4        |

| <b>3.4</b> | Voltage Contrast Analysis                      | 7        |

| 3.5        | Voltage Contrast Side Channel Analysis (VCSCA) | 9        |

| 3.6        | Backside Voltage Contrast Analysis             | 7        |

|            | Discussion                                     | o        |

| 3.7        | Discussion                                     | 9        |

**Contribution:** In the context of this project, my contribution is the initial idea, implementation and evaluation of the given approach.

## 3.1 Introduction

A crucial part in hardware reverse engineering is to know the location of their ROI prior to their delayering process. Without this knowledge, the literal search for the needle in the haystack can become a major obstacle for the reverse engineer. ROI s are usually security-sensitive elements, e.g., fuse bytes, cryptographic algorithms or proprietary parts of an IC [81, 130]. We may have luck if vendors "mark" sensitive areas with a shield or we already know the basic structure from a similar IC within the same vendor family. However, this is an exception especially in today's multi-million gate IC s. Identifying crucial elements is often extremely difficult.

The classical approach is a stepwise delayering down to the silicon substrate while taking images from each layer. After assembling and overlaying the different layers, a hardware reverse engineer can begin to interpret the logical cells to find his ROI. Even with semi-automated tools that help to recognize standard cells of a library and wirings, we need to attend and review the process of millions of gates to get a flawless netlist from the chip structure: There is no feedback mechanism that alerts of the reverse engineer about mistakes and even the slightest mistake in the image acquisition might lead to faulty connections and a completely different circuit behavior. To make things worse, it is difficult to completely planarize the die with low to medium prized equipment, resulting in bad layer images and therefore worse recognition rates with the current chip-area-to-layer-thickness ratio.

Pinpointing the delayering process to a ROI reduces the costs and processing time when the user can focus on keeping the structure of the ROI still recognizable, neglecting the rest of the chip. Another reason is to achieve better signal-to-noise-ratio with located EM-traces or make other (fault-)attacks possible [120, 121]. Sometimes this might even enable more advanced analysis like inter-gate side channel leakages as discussed in [137].

## 3.2 Related Work

In order to find the hot spot or ROI, multiple more practical approaches emerged, often in combination with use of a Side Channel (SC). The EM near-field cartography, thermal analysis and optical photon emission are the three most noteworthy examples [120, 121, 113, 19, 32, 58, 129]. All techniques are semi-invasive attacks[131]. They depackage the IC to strengthen existing side channels like EM emanation (to make pinpointed small loop measurements possible) and to gain access to additional SC s like photon emission and heat distribution. The mentioned semi-invasive techniques are possible from the top- and backside of the chip, whereby the backside approach usually needs additional equipment for milling and thinning the silicon bulk [58].

To be precise enough for locating the smallest activity areas, spatial located EM emanation cartography takes several hours. It finds multiple high Signal-to-Noise Ratio (SNR) spots along the power distribution, as the radiation is directly related to the power consumption. Furthermore EM emanation often results in better SNR from the frontside, as the probe can be moved closer to the emanation source [120, 121, 113]. Nevertheless this approach allows to find a ROI within  $\mu m$  range. Thus, we can can skip most parts of the chip and concentrate on the ROI. The drawback for EM near-field cartography is the long measurement time to scan the whole die surface and may show multiple hot spots.

In the case of the photon emission, the price of the equipment maps directly onto the measuring time and quality: An IR-range sensitive camera with good Quantum Efficiency (QE) and low dark-current costs several 10k USD. Transistors have a probability to emit a photon during a state transition which passes through the thinned silicon backside. A first mandatory preparation is the thinning of the silicon bulk on the backside. The basic idea is to capture the emitted photons and visualize them in a highly spatial resolute setup. This becomes a major obstacle for modern CMOS processes, due to the diffraction limit of IR light. Additional preparation steps after the thinning, like a Numerical Aperture Increasing Lens (NAIL), might become necessary [144]. This extends the preparation time and bears the risk of breaking the chip. After a camera-dependent image integration time, we can find the activity of individual transistors during the loop execution of one code fragment [129]. By increasing the supply voltage during the interesting clock cycles, the authors enhance the IR photon emission probability to highlight corresponding areas. Using this technique the authors of [124] successfully extracted an AES key by observing the memory access pattern of the **subbytes** routine. Meanwhile [58] pinpoints a Picosecond Imaging Circuit Analysis (PICA) attack on single transistors to find **xor** values. Finding the respective hot spots and transistors is done with an optical long time image integration like in [124, 129]. Once a ROI has been determined, PICA can be used to see transistor switches in high-frequency ICs.

Surface Liquid Crystal (LC) is a wide spread analysis method based on the thermal radiation for failure analysis in the industry. It is well established and can be exploited for ROI localisation from the attacker's point of view. LC s allow spatial resolutions of 4  $\mu m$  and better[19]. For modern CMOS processes this approach has equal spatial limitations, due to the IR light diffraction limit. Therefore new approaches like the Fluorescent Microthermal Imaging (FMI) emerged which try to fluoresce light with shorter wavelength [19]. Furthermore did the authors of [46] try to extend the thermal hot spot detection to the IC backside. Depending on the camera, are thermal and photon emission failure analysis methods qualified to find the ROIs. Both approaches are usually done over multiple program executions to heat-up or gather enough emitted photons in a normal working chip. These failure analysis methods face big challenges and difficulties with the upcoming CMOS sizes and decreasing power supply voltages. The modern CMOS size is below the diffraction limit of IR light and the decreasing power supply voltage drops the probability of photons being emitted and reduce the produced heat due to smaller currents.

This chapter uses the SEM as advanced inspection tool. Access to a suitable SEM should not be problematic as bigger institutes and universities with mid-class laboratories usually own one, due to their distribution in many academic fields. Companies and private persons can find second hand SEM s for under 10k EUR or rent it on a hourly basis. A well-funded hardware reverse engineer usually has access to a SEM for taking layer images. Once the setup is built and the Device Under Test (DUT) is vulnerable to our approach, we are able identify the ROI faster as the EM cartography and have less sample preparation compared to the photon emission analysis. Furthermore we don't require to run the chip multiple times and have better spatial resolution than thermal analysis methods.

Our contribution in this chapter is the following:

- (1) We demonstrate an approach to pinpoint the AES location within the XMEGA microprocessor with Voltage Contrast (VC) analysis.

- (2) We exploit the VC as a SC and perform a full key-recovery in a template-attack and a Simple Side Channel Analysis (SSCA).

- (3) Using the VC images reveals additional information of the AES circuit useful for a reverse engineer. Furthermore are we showing the potential of VC SC in a Side Channel Analysis for Reverse Engineering (SCARE) approach to find additional circuit netlist information.

- (4) The results show a possibility to counter hardware-obfuscation and hardware protection and to verify parts of an extracted netlist.

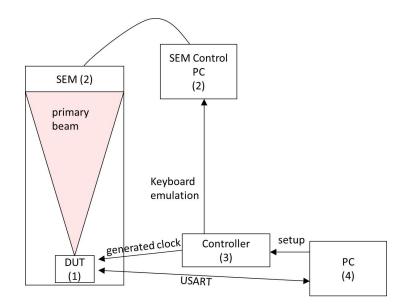

The rest of this section is structured as follows: Section 3.3.1 describes the different VC analysis methods and their physical understanding. Section 3.4 locates the AES circuit with the common Dynamic Voltage Contrast (DVC) analysis. Section 3.5 is the main contribution that gives a Proof of Concept (POC) for the VCSCA. The DUT is a widespread Atmel XMEGA microcontroller. We show a template-attack and a SSCA approach to recover the full AES key. Section 3.8 concludes this work.

## 3.3 Background

In this section, we will introduce the required background information and reference to more detailed descriptions. We start with the voltage contrast in general and continue with the dynamic voltage contrast and Capacitive Coupled Voltage Contrast (CCVC), respectively.

### 3.3.1 Voltage Contrast

The SEM has become a powerful diagnostic tool during the last 60 years, used in many applications for IC inspection and failure analysis. When an electron beam-gun fires (primary) electrons on a scanning surface, secondary electrons are hit out of a solid specimen. These emitted secondary electrons have usually low energy (0 - 50 eV), which makes them easily detectable by using a positive electrical-field metal-plate as a detector. Out of the SEM images are the secondary electron images the most widely used, due to their ease of production and similarity to light microscope with improved depth of field [24].

During VC failure analysis, the natural negative charge of the electrons is used to view different voltage potentials, with the help of their electrical field and their direct influence on secondary electrons. Note that VC also works with positive ions in a FIB since only the difference in charge is important. Using VC with positive ions from a FIB achieves better results<sup>1</sup> and the voltage interpretation of brightness and darkness is reversed compared to the SEM VC [23, 24, 28]. VC analysis needs the chip to be depackaged to gain access to the die surface.

VC analysis can be classified into two categories, which are on the one hand the static VC methods, including Passive Voltage Contrast (PVC) and Active Voltage Contrast (AVC) and on the other hand the Dynamic Voltage Contrast (DVC).

## 3.3.2 Static Voltage Contrast

The static VC is performed on chips with a removed passivation layer or even partly delayered chips. Static VC is split in the two sub-techniques PVC and AVC. The PVC does not connect the DUT to any signals or voltages and thereby shows the charging up of floating gates and capacitances. It is often used to find shorts and imperfectly connected wires and structures during chip manufacturing. The DUT does not have to be functional anymore, allowing to take VC images of intermediate layers. Note that is possible to create floating structures by removing metal layers or by wire cutting with a FIB [115]. To pinpoint shorts and badly connected wires, the structures are split and analyzed separately by applying a voltage in the AVC.

<sup>&</sup>lt;sup>1</sup>With individually optimized parameters

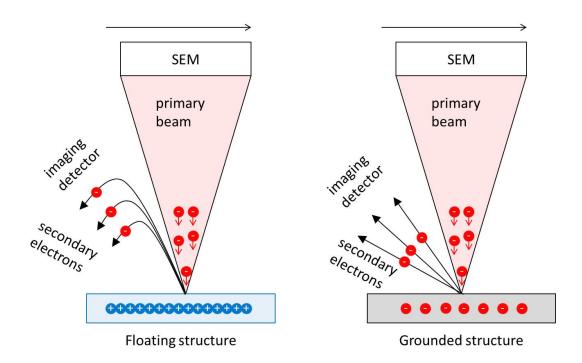

Figure 3.1: Passive Voltage Contrast. Floatin structures charge up while grounded structures are supplied with electrons from the GND signal.

Figure 3.1 shows the PVC. Isolated structures are charging up, due to secondary electrons being hit out of the structure. In the immediate consequence, the majority of produced secondary electrons are prevented to reach the detector by the inverted electrical field. These structures appear dark in the image. Grounded structures do not appear bright, because of the high yield[115].

AVC differs from PVC as it applies voltages in some structures to force them to look dark or bright in flawless structures. Is the outcome not as expected, a short or open connection can be assumed. Knowing the detailed place-and-route of the netlist and structures is very helpful, but not mandatory. The authors of [136] use the PVC to detect stealthy dopant-level circuits (trojans).

## 3.3.3 Dynamic Voltage Contrast

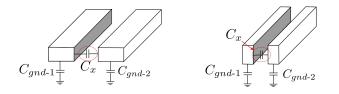

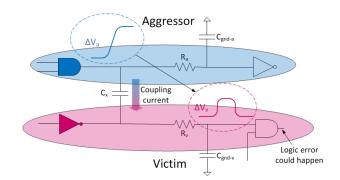

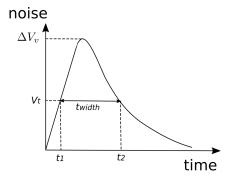

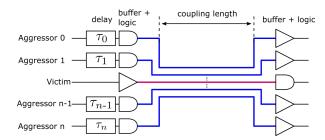

DVC is performed during dynamic rather than the static operation of the DUT. In the scope of an IC or Microcontroller (uC), the device is running normally while performing the voltage contrast. If the device is still under the passivation layer, CCVC can be applied. CCVC exploits the property that the voltage potentials of the top metal-wires are electrically coupled with the covering dielectric passivation of the die, forming a capacitor. Therefore, CCVC is performed while the passivation layer is still covering the die and the chip is still operational, or at least voltages can be applied to top wires and structures.

When a line or wire buried under the passivation is assumed to have the voltage  $U_p$ , an voltage  $U_S$  is generated through capacitive effects. This effect can be described as a transfer function  $U_S/U_p$ , which depends on the electrical  $(U_E)$  and geometrical  $(d_e, d_p, W)$  parameters.  $U_E$  and

$d_E$  are the extraction grid potential and distance, while  $d_p$  and W represent the buried line depth and width, respectively[18]:

$$\frac{U_S}{U_p} = f(U_E, d_E, d_p, W) \tag{3.1}$$

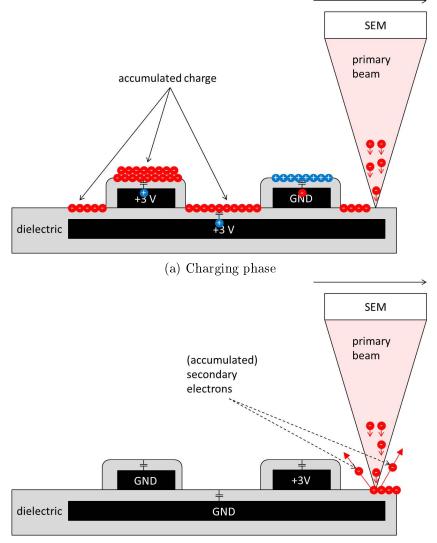

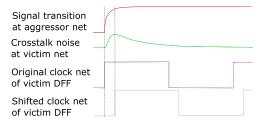

The CCVC phenomena is made visible with a SEM through dynamic changes. Therefore the CCVC is separated into two phases shown in Figure 3.2.

(b) Read-out phase

Figure 3.2: Capacitive Coupled Voltage Contrast with its two phases. First charging phase accumaltes charges. After a clock cycle the metal changed and the accumulated charge is release when hit by an electron.

The first phase charges up the ICs surface with the electron-beam with location-depending accumulated charges (due to  $U_S$ ), coupled to the underlying electrical potentials ( $U_p$ ). In the

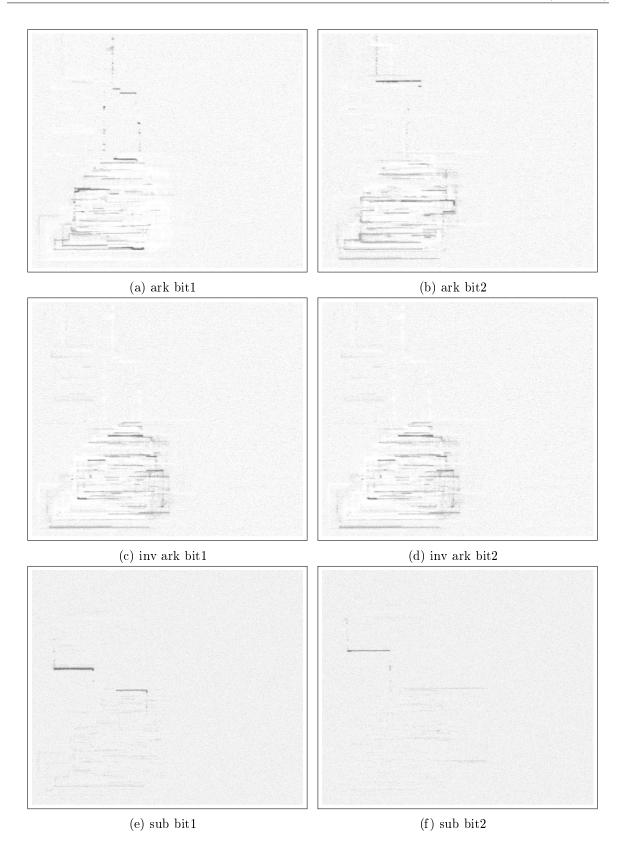

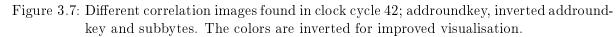

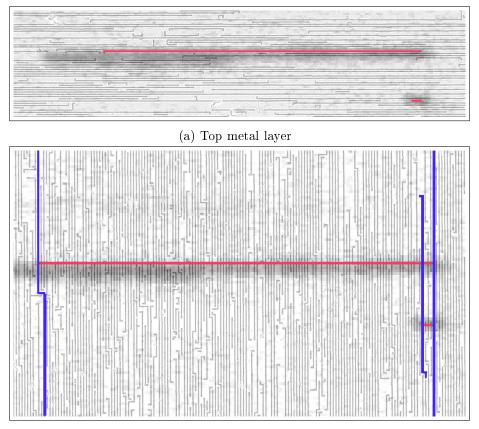

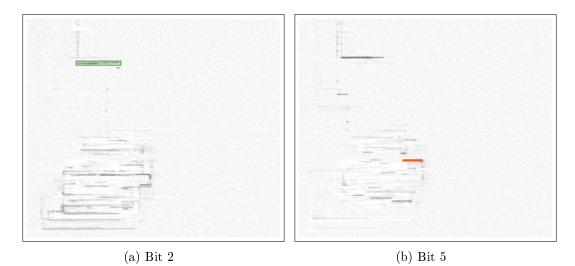

second phase, the accumulated electrons are hit out as secondary electrons. Compared to the normal structures, are more electrons detected, 'brightening' the structure. We can utilize this phenomenon when the electrical potential of the top layers is data-dependent. Please note that this is not always the case as modern CMOS processes route the VCC or GND signal through the top metal layer. The data dependency leaks further information in a SC that are meant to be kept secret. This has already been seen as a theoretical threat in [30]. We show a practical attack and utilize the CCVC as a SC, not considered in the SC community so far<sup>2</sup>.