# The ATLAS Level-1 Central Trigger Processor (CTP)

- Introduction

- Functionality and Implementation

- Tests and Results

R. Spiwoks<sup>1</sup>, S. Ask<sup>1</sup>, N. Ellis<sup>1</sup>, P. Farthouat<sup>1</sup>, P. Gallno<sup>1</sup>, J. Haller<sup>1</sup>, A. Krasznahorhay<sup>1,2</sup>, T. Maeno<sup>1</sup>, T. Pauly<sup>1</sup>, H. Pessoa Lima Jr.<sup>3,4</sup>, I. Resurreccion Arcas<sup>1</sup>, G. Schuler<sup>1</sup>, J. M. de Seixas<sup>4</sup>, R. Torga Teixeira<sup>1</sup>, T. Wengler<sup>1</sup>

<sup>1</sup>CERN, <sup>2</sup>University of Debrecen, <sup>3</sup>Brazilian Center for Physics Research, <sup>4</sup>Federal University of Rio de Janeiro

→ See also presentation "The ATLAS Level-1 Trigger Timing-in" by T. Pauly

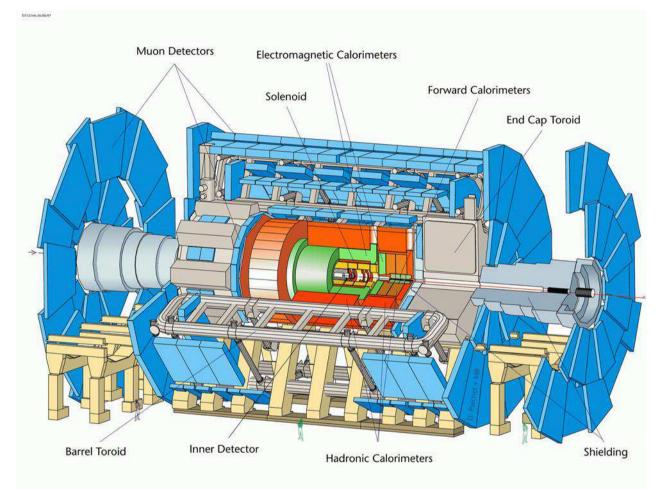

# The ATLAS Experiment (1)

General-purpose Experiment at CERN's Large Hadron Collider (LHC): Proton-proton collisions at 14 TeV centre-of-mass energy About 25 collisions per bunch crossing (BC) every 25 ns (40 MHz)

#### $\Rightarrow$ Interaction rate of 1 GHz

R.Spiwoks

### The ATLAS Experiment (2)

#### Installation of the 8th and final coil of the ATLAS barrel toroid

R.Spiwoks

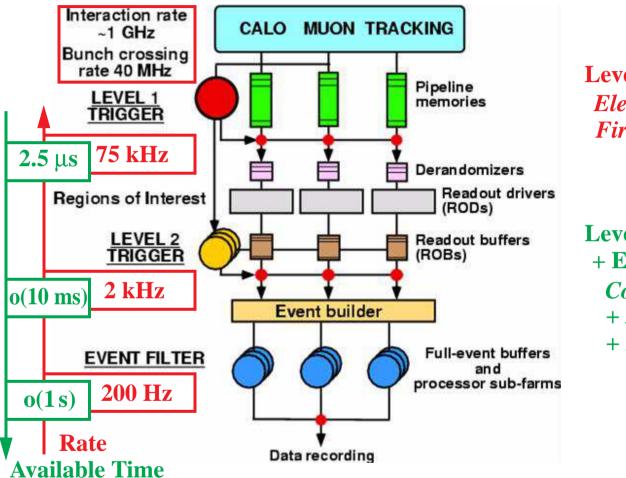

### The Trigger/DAQ System

Level-1 Trigger: Electronics + Firmware

Level-2 Trigger + Event Filter: Computers + Networks + Software

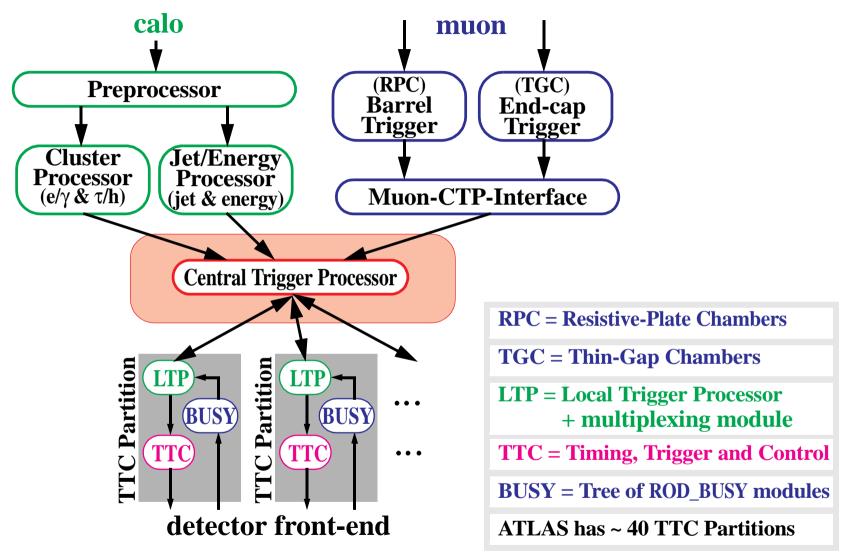

### The Level-1 Trigger System

$\rightarrow$  A new LTP multiplexing module has been specified in order to allow concurrent combinations of TTC Partitions for stand-alone tests

# The Central Trigger Processor (1)

#### • Trigger Input:

- **Multiplicities** from Calorimeter and Muon Triggers: electrons/photons, taus/hadrons, jets, and muons;

- **Energy flags** from Calorimeter Trigger:  $\Sigma E_T$ ,  $E_T^{miss}$ ,  $\Sigma E_T^{jet}$

- Calibration requests from sub-detectors

- Other specialized triggers: scintillators, beam pick-ups, etc.

- $\Rightarrow$  Up to a total of **160 trigger inputs** at any one time

Plus **internal triggers** (generated in CTP): random triggers, prescaled clock, bunch crossing groups

# The Central Trigger Processor (2)

#### • Level-1 Accept (L1A):

- Derived from trigger inputs according to a **trigger menu:**

$\begin{array}{l} - \mbox{ Up to } 256 \ trigger \ items \ are \ made \ from \ combinations \ of \ conditions \ on \ the \ trigger \ inputs, \ e.g. \ \\ 1EM10 \equiv at \ least \ one \ electron/photon \ with \ E_T \geq 10 \ GeV \ \\ 1MU6 \ \equiv at \ least \ one \ muon \ with \ p_T \geq 6 \ GeV/c \end{array}$

**XE20**  $\equiv$  missing energy of at least 20 GeV

- Each trigger item has a mask, a priority<sup>1</sup> and a prescaling factor <sup>1</sup> for preventive dead-time:

high priority: as little deadtime as possible low priority: comparatively high deadtime

- L1A is the OR of all trigger items

- An example of a trigger menu might contain

| 1MU6                  | mask = ON, priority = LOW, prescaling = 1000 |

|-----------------------|----------------------------------------------|

| <b>2MU6</b>           | mask = ON, priority = HIGH, prescaling = 1   |

| <b>1EM20 AND XE20</b> | mask = ON, priority = LOW, prescaling = 1    |

...

# The Central Trigger Processor (3)

#### Additional Functionality:

- **Trigger-type** word (8 bits) accompanying every L1A Sent promptly via the TTC system to the front-end electronics

- Dead-time in order to prevent front-end buffers becoming full

- Region-of-Interest (RoI) for the Level-2 Trigger and event data for the Read-out System (ROS) and for monitoring *Provides much more information than the trigger-type word, allowing a detailed understanding of why the event was selected*

- Time-stamp (GPS-based UTC time) accompanying every L1A

- Timing signals, e.g. Event Counter Reset (ECR), ...

- Scalers in order to provide monitoring of rates and of deadtime

#### • Constraints:

- Trigger latency target, i.e. from trigger input to L1A:  $100 \text{ ns} \equiv 4 \text{ BC}$

- Trigger menu changes with physics/beam/detector conditions

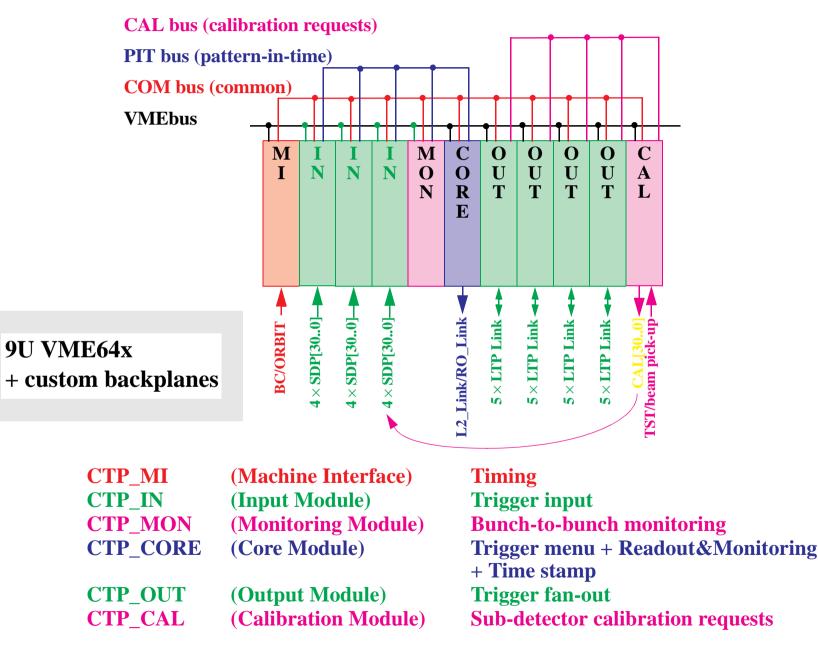

## The Design of the CTP

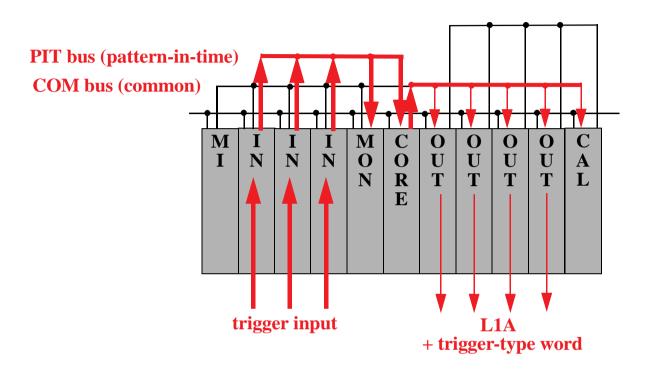

### The Trigger Path of the CTP

CTP\_IN modules receive, synchronize (phase) and align (BC) the trigger inputs, and route them to the **PIT bus (Pattern-In-Time)**

CTP\_CORE module receives and synchronizes the PITs, compares with trigger menu and generates Level-1 Accept (L1A), sends L1A to the COM bus

CTP\_OUT receives L1A from the COM bus and fans it out to sub-detector LTPs

R.Spiwoks

LECC 2005, Heidelberg, 13-SEP-2005

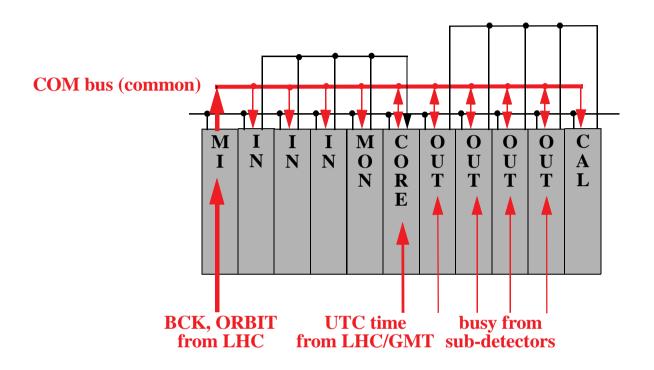

# The Timing Path of the CTP

- CTP\_MI module receives timing signals from LHC, generates additional timing signals and sends all to the COM bus

- CTP\_OUT modules receive busy signals from sub-detector LTPs and send them to the COM bus

- CTP\_CORE module receives GPS-based UTC time from LHC GMT (General Machine Timing) timing system

All CTP modules receive timing signals from the COM bus

R.Spiwoks

LECC 2005, Heidelberg, 13-SEP-2005

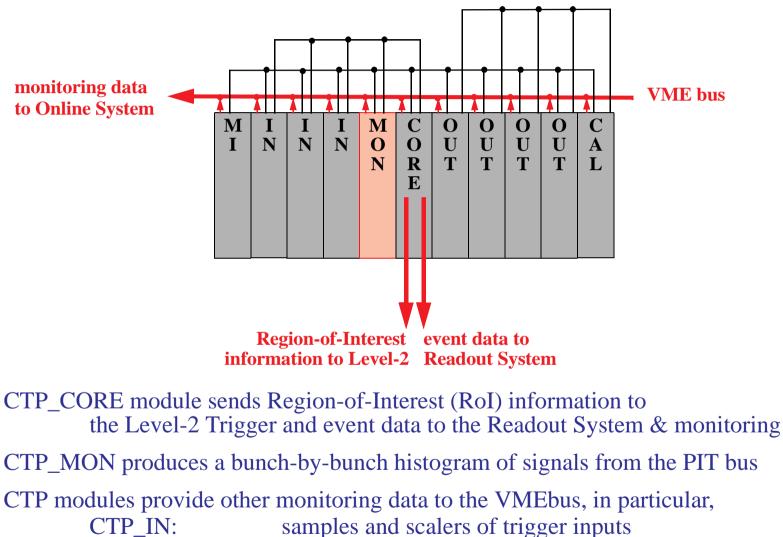

# The Readout & Monitoring of the CTP

samples and scalers of trigger inputs scalers of trigger items and of deadtime CTP\_CORE: scalers of deadtime of sub-detectors

R.Spiwoks

CTP OUT:

LECC 2005, Heidelberg, 13-SEP-2005

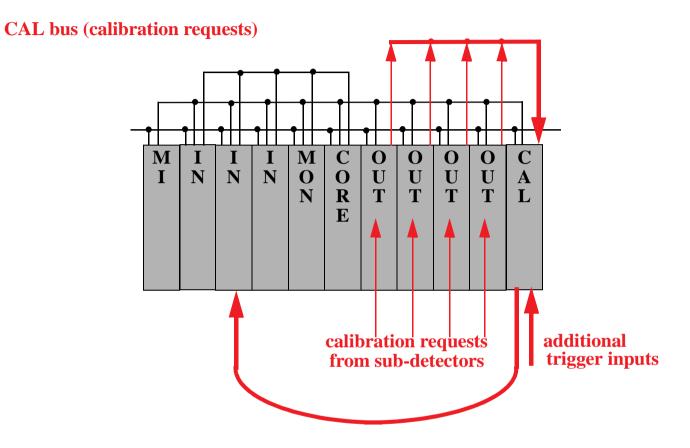

### The Calibration Requests in the CTP

CTP\_OUT modules receive calibration requests from sub-detector LTPs and send them to the CAL bus

CTP\_CAL time-multiplexes calibration requests, receives additional trigger inputs and sends all to a CTP\_IN module

R.Spiwoks

LECC 2005, Heidelberg, 13-SEP-2005

# The CTP Input Module (CTP\_IN)

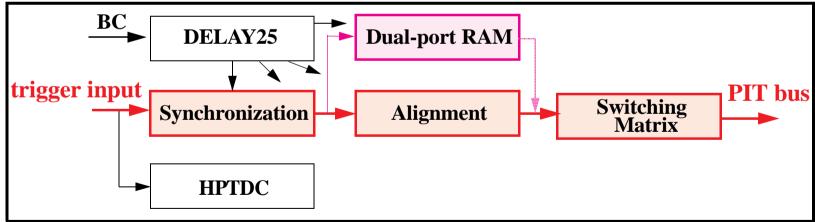

### $\rightarrow$ Trigger Path:

- Measure phase of trigger inputs using CERN High-Performance TDC (**HPTDC**)

- Adjust clock of CTP\_IN module using CERN **DELAY25** (**PHOS4** on older version)

- Store synchronized data in **diagnostic memory** (dual-port RAM)

- Adjust BC alignment of trigger inputs using **pipeline** in FPGA

- Select and route trigger inputs to be sent to PIT bus using a CPLD

Trigger Path of CTP\_IN Module

# The CTP Core Module (CTP\_CORE) (1)

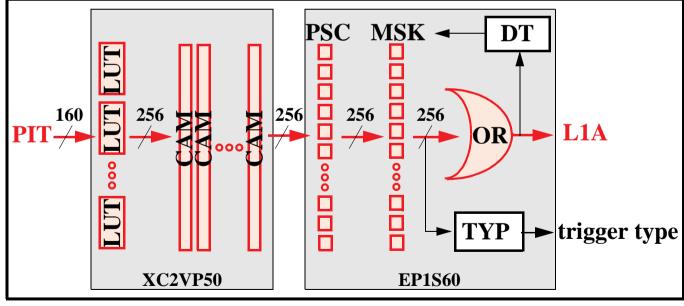

#### $\rightarrow$ Trigger Path:

- Combine Pattern-In-Time (PIT) using Look-up Tables (LUT), and Content-Addressable Memories (CAM) to form 256 trigger items

- Each CAM contains a 256-bit word and is ternary,

- i.e. allows bit-wise matching of "0", "1" or "don't care"

- Prescale (**PSC**, 24 bit), mask (**MSK**, mask + dead-time + busy), and OR the trigger items to generate **Level-1 Accept** (**L1A**)

- Generate preventive dead-time (DT) and trigger-type word (TYP)

Trigger Path of the CTP\_CORE Module

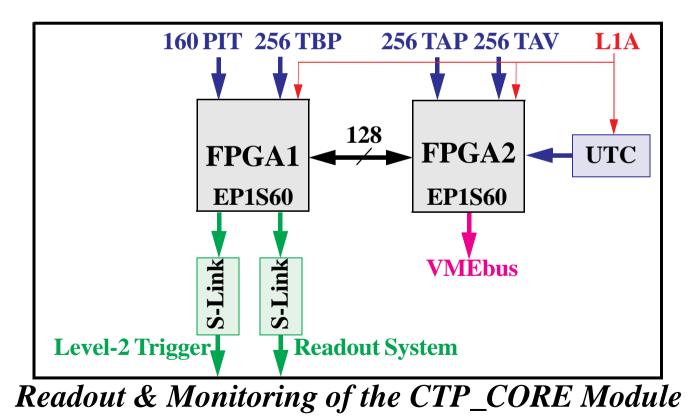

# The CTP Core Module (CTP\_CORE) (2)

#### $\rightarrow$ Readout & Monitoring:

Copied into FIFOs for every L1A ( + programmable window around L1A):

- 160 signals from the **PIT** bus + 12 internal triggers

- 256 trigger items before prescaling (after LUT and CAM) (TBP)

- 256 trigger items after prescaling (TAP)

- 256 trigger items after veto (TAV)

- 64-bit UTC time-stamp (based on GPS) with 5-ns jitter

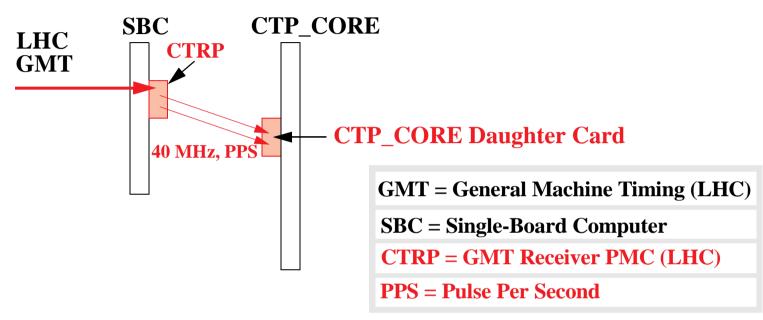

## The CTP Core Module (CTP\_CORE) (3)

### $\rightarrow$ Time Stamping:

$\rightarrow$  Use LHC General Machine Timing (GMT) (CERN/AB/CO) system, which contains GPS-based precise UTC time

**CTRP card** (CERN/AB/CO) on single-board computer receives GMT signal **CTP\_CORE daughter card** receives 40.00 MHz and pulse-per-second from CTRP card and contains 200.00 MHz counter At every L1A it produces a time-stamp with relative precision of 5 ns

$\rightarrow$  Measure absolute time precision, expect much better than 1 µs

$\rightarrow$  Use other information from GMT, e.g. cycle type, beam energy

R.Spiwoks

# The Testing of the CTP

#### • Test beam programme during Autumn 2004:

Combined beam tests for prototypes and final modules of all ATLAS sub-detectors and trigger and data acquisition

#### **Trigger Input:**

| Calorimeter Trigger: | 1 CABLE: $4\times3$ bit $e/\gamma + 4\times3$ bit jet multiplicities   |

|----------------------|------------------------------------------------------------------------|

|                      | 1 CABLE: 1 bit total E <sub>T</sub>                                    |

| Muon Trigger:        | 1 CABLE: 6×3 bit muon multiplicities,                                  |

|                      | from MUCTPI, 1 Sector Logic RPC or TGC                                 |

| Scintillators:       | 1 CABLE: $3 \times 1$ bit scintillators (via LTP $\rightarrow$ CTP_IN) |

|                      | $\Rightarrow$ total of 46 bits                                         |

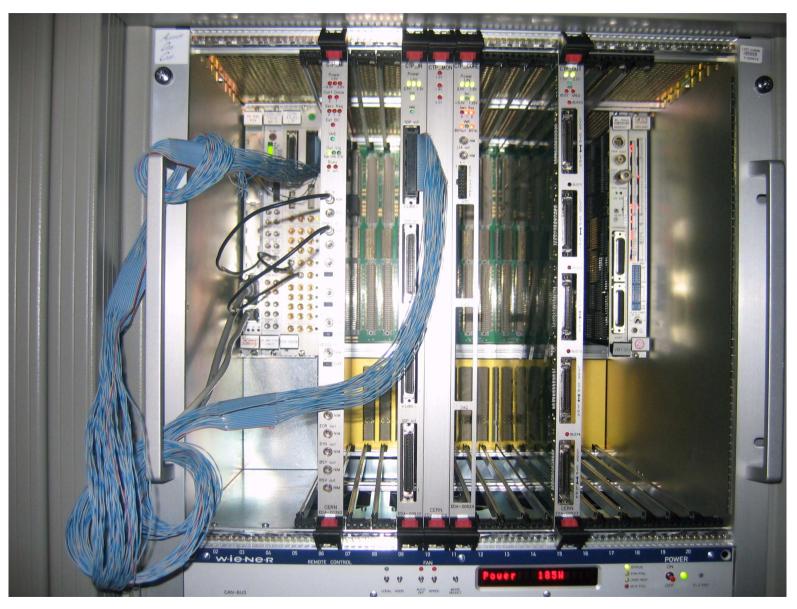

#### • Full-system stand-alone tests in Laboratory:

- Use LTP to emulate trigger input:

pattern generator and dedicated cable with **16 (out of 31) signals** + parity

- Full chain: LTP  $\rightarrow$  CTP ( $\rightarrow$  LTP)

- Alternatively use MUCTPI for trigger input

### The CTP Full-System Tests (1)

## The CTP Full-System Tests (2)

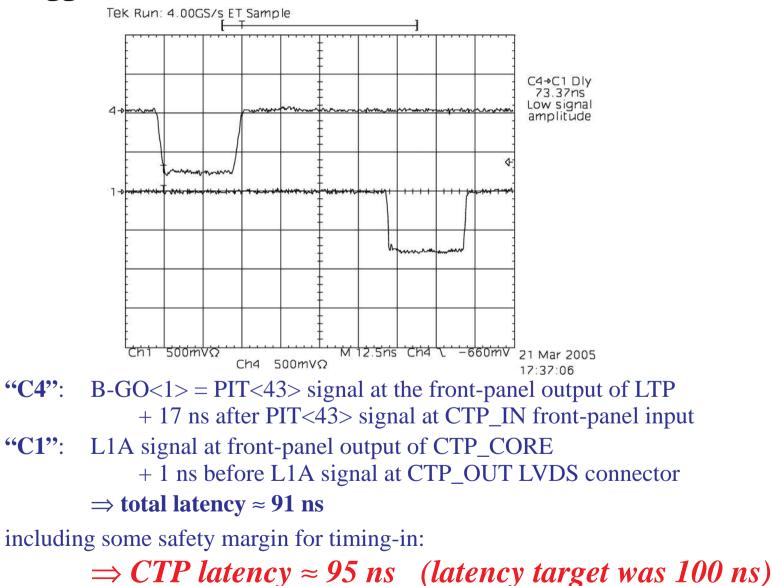

• Timing-In:

### $\rightarrow$ Arrival of trigger inputs at CTP\_IN:

- **synchronization** (phase) w.r.t. to local clock, local clock can be shifted by DELAY25 (PHOS4)

- alignment (BC) w.r.t. to latest trigger input, uses pipeline

#### Method A (Phase):

- measure phase of trigger inputs with HPTDC

#### Method B (Data):

- capture trigger inputs in diagnostic memory and compare with expected data

- reduce clock delay until data errors appear

#### Method C (Parity):

- same as method B (or in addition to method B) but using parity error

#### $\Rightarrow$ Automatic procedure:

Sample all trigger inputs, adjust phase synchronization, and BC alignment if expected data are known

$\rightarrow$  CTP\_CORE timing is fixed w.r.t. to CTP\_IN(s)

## The CTP Full-System Tests (3)

#### • Trigger Formation:

R.Spiwoks

LECC 2005, Heidelberg, 13-SEP-2005

### The CTP Full-system Tests (4)

#### • Control and Monitoring:

Use common ATLAS ROD Crate DAQ, i.e. configuration and run controllers (see also presentation "VMEbus Processor Hardware and Software Infrastructure in ATLAS" by M. Joos)

Use trigger database and trigger menu compiler for configuration of event-selection criteria, etc.

(see also presentation "Configuration of ATLAS Trigger" by R. Spiwoks)

Use run controllers with low-level hardware-access software

Monitoring software is currently under development:

- event sampling

- integrating scalers, bunch-to-bunch scalers, deadtime scalers

- global values, including temperature and voltage

### **Conclusion**

CTP has been used during Autumn 2004 test beam and full-system tests to generate triggers with real and emulated trigger inputs

Measured CTP latency is ~ 95 ns (< 100 ns)!

Work on the CTP to be finished:

- test of CTP Core module firmware for readout&monitoring

- design and manufacturing of CTP Calibration module

- monitoring software

CTP will be installed in underground counting room and available for ATLAS commissioning from Autumn 2005