# Test Beam results and integration of the ATLAS Level-1 Muon Barrel Trigger

M. Bianco, E. Brambilla, G. Cataldi, G. Chiodini, G. Fiore, E. Gorini, F. Grancagnolo, A. Miccoli, R. Perrino,

M. Primavera, S. Spagnolo, G. Tassielli, A. Ventura

University of Lecce and I.N.F.N. Lecce

A. Aloisio, M. G. Alviggi, V. Canale, M. Caprio, G. Carlino, F. Conventi, R. De Asmundis, M. Della Pietra,

D. Della Volpe, P. Iengo, V. Izzo, A. Migliaccio, S. Patricelli, G. Sekhniaidze

University of Napoli Federico II and I.N.F.N. Napoli

V. Bocci, G. Chiodi, E. Gennari, A. Nisati, E. Pasqualucci, Fr. Pastore, E. Petrolo, R. Vari, S. Veneziano

I.N.F.N. Rome, Italy

G. Aielli, P. Camarri, R. Cardarelli, C. Delle Fratte, A. Di Ciaccio, A. Di Simone, L. Di Stante, B. Liberti,

A. Salamon, R. Santonico, E. Solfaroli

University of Rome "Tor Vergata" and I.N.F.N. Rome2, Italy

V. Aprodu, M. Petcu

Institute of Atomic Physics, Bucharest

Abstract-The ATLAS Level-1 Muon Trigger will be crucial for the online selection of events with high transverse momentum muons and for its correct association to the bunch-crossing corresponding to the detected events. This system uses dedicated coarse granularity and fast detectors capable of providing measurements in two orthogonal projections. The Resistive Plate Chambers (RPCs) are used in the barrel region ( $|\eta| < 1$ ). The associated trigger electronics is based on a custom chip, the Coincidence Matrix, that performs space coincidences within programmable roads and time gates. The system is highly redundant and communicates with the ATLAS Level-1 trigger Processor with the MUCTPI Interface. The trigger electronics provides also the Readout of the RPCs. Preliminary results achieved with a full trigger tower with production detectors in the H8 test beam at CERN will be shown. In particular preliminary results on the integration of the barrel muon trigger electronics with the MUCTPI interface and with the ATLAS DAQ system will be discussed.

Index Terms-trigger, muon, level-1, barrel, ATLAS, RPC

# I. INTRODUCTION

AIN goal of the ATLAS First-Level Trigger [1] is to reduce the trigger rate by a factor of  $O(10^4)$  from the initial bunch-crossing rate of 40 MHz, while eliminating accidental triggers due to low energy background particles. It is based on multiplicity information from clusters found in the calorimeters and from tracks found in dedicated muon trigger detectors. Each single bunch-crossing must be processed, so data are held in pipelines. Also electronics must be structured in pipelines, each component repeating its specific actions every 25 ns. Pipelines allow a fixed latency of up to 2.5  $\mu$ s for a

Manuscript received November 1st, 2004. This work was supported by the IEEE.

Corresponding author: Fr. Pastore is with the INFN Sezione Roma, P.le Aldo Moro 2, 00185 Rome, Italy. E-mail: francesca.pastore@roma1.infn.it

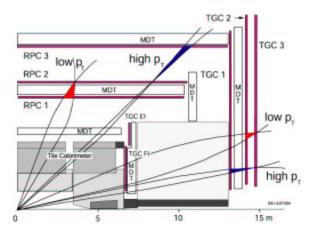

Fig. 1. The ATLAS Level-1 Muon Barrel Trigger schema

trigger decision, before sending events to the Read Out Drivers (ROD). A correct identification of the bunch-crossing (BC) is crucial for event selection and for reducing the required readout bandwidth.

The Muon Trigger in the Barrel region is performed using Resistive Plate Chambers (RPCs) as dedicated detectors, while Thin-Gap Chambers (TGCs) are used in the end-cap and forward regions. The system identifies muon candidates looking for coincidence of hits in different layers and discriminates their transverse momentum  $(p_t)$  depending on the width of the roads used for the coincidence (Fig. 1). The overcome muon candidate  $p_t$  thresholds and the  $\eta$  and  $\phi$  position, called Region of Interest (RoI), are sent to the higher trigger levels. The trigger detectors segmentation unit is the sector, which can identify up to two muon candidates classified using six programmable  $p_t$  thresholds. The two highest  $p_t$  candidates are

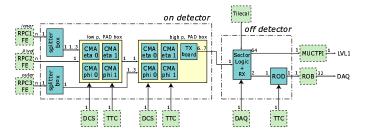

Fig. 2. Trigger slice layout, showing different on- and off-detector devices

selected by detector-specific Sector Logic modules, which can also handle overlaps of chamber regions and sends detailed information to the Muon Central Trigger Processor Interface (MUCTPI) [6]. MUCTPI calculates detector-wide multiplicities and communicates with the Central Trigger Processor (CTP) responsible for taking the final decision, based on multiplicities of identified trigger objects, using  $p_t$  thresholds and global energy variables from calorimeters.

## II. MUON BARREL TRIGGER OVERVIEW

The Muon Trigger system in the Barrel region is based on three stations of double gaps RPCs. Each gap is read out by two orthogonal series of pick-up strips, 3 cm pitch, providing hits coordinates in both the bending and non-bending directions ( $\eta$  and  $\phi$  respectively). Strips in  $\phi$  directions are orthogonal to the wires of the precision tracking chambers (MDT), thus RPCs supply additional second coordinate tracking information. Each trigger sector corresponds to one half ATLAS sector, each formed by six or seven RPC chambers, and is divided into PAD regions, which comprises four RoIs. Then a total of 64 trigger sectors are foreseen in the ATLAS Barrel, with 832 PAD regions and 1664 RoIs.

Two complementary trigger decisions are used: a low- $p_t$  trigger, which discriminates  $p_t > 6$  GeV/c muons using the two middle RPC stations located near the center of the the magnetic field region, and a high- $p_t$  trigger, which detects muons with  $p_t >$ 20 GeV/c using the third outer station. Trigger coincidence algorithm is performed separately for the two views. It requires the time coincidence and the hit patterns of muons coming from the interaction point: 3 out of 4 hit layers in the low  $p_t$  stations, and in addition 1 of the 2 outer layers in the high  $p_t$ . When trigger conditions are satisfied for both views, a valid trigger information is generated with a granularity of  $\Delta \phi \times \Delta \eta = 0.1 \times 0.1$ . The values of the thresholds and the imposed logic majorities are programmable and can be changed in order to ensure trigger robustness against detector or background specific conditions [2].

#### **III. TRIGGER SLICE DESCRIPTION**

### A. On-detector electronics

The main part of the trigger logic is performed by the ondetector electronics. The signals from the RPCs detectors are amplified, discriminated and digitally shaped by the Front-End electronics [3], before being processed by the Coincidence

Matrix ASIC (CMA) chips [4], the real core of the trigger algorithm. Coincidence and majority operations, as well as  $p_t$  thresholds cuts, pipelined delays, clusterizing of hits, derandomizing buffering and also format of the strips readout are altogether performed inside this chip. All the parameters defining the trigger configuration and up to three  $p_t$  threshold values are some of the programmable parameters of the CMA. Each CMA produces as outputs a trigger pattern and the hit list relative to RPC doublets in one projection. Information from two adjacent CMAs in the  $\phi$  projection and two in the  $\eta$  projection are combined by the PAD logic, which is performed by programmable FPGAs to generate trigger results and containing up to four RoI per PAD. A low- $p_t$  PAD processor, containing a low- $p_t$  PAD motherboard and four low- $p_t$  CMAs, is mounted on top of the central (pivot) RPC station and transmits its outputs to the corresponding high- $p_t$  PAD, mounted on top of the outer station, which collects both low and high  $p_t$  trigger results and sends them to the off-detector system. The high $p_t$  trigger applies coincidence criteria using the low- $p_t$  trigger results and the hit patterns coming from the outer RPC doublet. Besides four CM mezzanines, two for  $\eta$ -CMs and two for  $\phi$ -CMs, and the pad logic chip, each PAD motherboard also contains a number of devices to offer different services. Many voltage and temperature sensors are present to monitor key areas and voltage domains. Prode Delay chips are used to time in the ASICs with 1 ns delay steps. The TTCRx mezzanine receives and controls LHC timing signals and distributes the 40 MHz machine clock. The ELMB mezzanine contains a microcontroller for the communication, external via CAN bus and local via I2C, JTAG and SPI buses. In particular ELMB controls all the types of initializations, for FPGA and ELMB firmwares and for the parameters of the trigger configuration. Initialization can be executed via CAN bus either through a remote control, sending individual commands, or through a local control, in which parameters can be stored locally on a flash memory and then loaded on the devices when one init message arrives from the DAQ system.

Since coincidence windows can encompass several chambers on the same coincidence layer, signals coming from these chambers are fan out by Splitter boards and then sent to the CMAs on adjacent PADs. Splitter motherboards contain power distributions, devices for temperature and voltage monitoring and a remote control link to neighboring PAD. They also convert front-end signals into LVDS standard. In ATLAS 832 PAD boxes and an equal number of Splitter boxes will be installed.

### B. Off-detector electronics

Off-detector electronics receive readout and trigger information via optical links, synchronously at 40 MHz, through a Receiver and Sector Logic board (RX-SL) [5]. Trigger and readout data share the same optical fiber and readout data are sent with low priority when trigger data are not available. Each SL board combines trigger information from up to eight PAD regions, exactly one ATLAS sector, and sends data to the MUCTPI. When a Level-1 Accept (L1A) signal is received by the PAD board, readout data containing hit and coincidence patterns plus Level-1 counters are sent asynchronously to the ROD and later on to the Read Out Buffers. An external Trigger and Timing Control system (TTC) forms the L1A signal based on the global ATLAS trigger result produced by the CTP. A total of 16 VME crates will be used in ATLAS to manage the Muon Barrel trigger electronics, while 416 optical links will be necessary to connect electronics from detectors layers to the USA15 counting room.

# IV. TEST BEAM SETUP

In May 2004 a combined testbeam was available at the CERN H8 test area with two one-week periods of 25 ns bunch structured beam useful for trigger validation. Two RPC BML chambers, containing inner and middle low- $p_t$  stations, and two BOL chambers, containing the outer high- $p_t$  station, were installed and integrated with precision tracking MDT chambers, positioned as the real ATLAS distances, thus reproducing an entire trigger tower (Fig. 3). Also Muon Endcap chambers TGCs system and calorimeters were installed along the beam line, so that all the trigger system could be tested. Prototype modules

Fig. 3. Particular of the set-up of the Muon Barrel trigger at the H8 test beam. In the foreground the BOL chamber with high- $p_t$  trigger electronics mounted on, the BML station is visible in the background.

for almost all parts of the system have been installed at the test beam, while many final design and series production modules have been validated by the test beam results. In particular four preproduction Splitter box and four final prototypes of PAD boards, mother-boards and daughter-boards, have been used, after successfully slice tests in laboratory. Preliminary prototypes for the Sector Logic board and the MUCTPI have been tested, using a custom ROD-backplane and a MUCTPI interface. Also the CTP was fully integrated with all the systems, producing triggers for combined runs. A ROD emulator was used since the final ROD board is currently under design. The entire cabling system, both front-end cabling and trigger cabling, and the optical fibers were from the production stack. The final power supply system of the ATLAS experiment for high and low voltage of chambers and trigger electronics was installed.

Trigger initialization procedure was executed by a Linux station using CAN-Open communication protocol and exploiting the local control procedure of ELMB micro-controllers. This procedure was tested for the first time and greatly reduced time of initialization. The upper stream of the readout system was connected with the ATLAS Trigger/DAQ online system. The ATLAS standard detector control system (DCS) was used for the chamber environmental setup and monitor.

The global data taking was alternatively detector-specific standalone and combined, and different kinds on trigger inputs have been used: the trigger coming from large hodoscopes in front of the muon chambers and the trigger signal coming from the CTP, as a result of the combinations of different trigger detectors signals.

# V. READOUT SLICE PERFORMANCES

One of the main purpose of the test beam data taking was to test robustness of the readout path, through the low- $p_t$  PAD motherboard traces via differential cables to the high- $p_t$  PAD and going to the ROD system via optical links. Online check of integrity of data fragments were made continuously, as well as controls of their synchronization and alignment for BC and L1A identification counters. Different configurations of the CM ASICs were tested in order to ensure the correct functionality: timing adjustments in the pipeline delays were used to align the readout windows and synchronize the system with the other trigger detectors. CMA devices tag RPC hits with a time interpolator with 3.125 ns steps (1/8 of a bunch-crossing), to have a good readout resolution of the system.

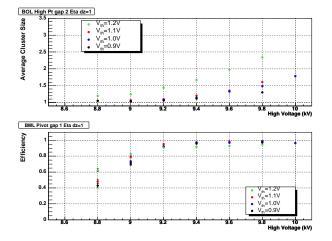

Performances of the RPC chambers have been monitored during the whole data taking period. A new cabling schema was adopted in order to limit any background interference. Different high voltage scanning and low voltage thresholds on frontend electronics allowed to set the operational working point at 9800 V with 1.0 V threshold (Fig. 4). With several sets of combined data taking, chambers efficiencies could be evaluated, comparing MDT track segments extrapolation with the position of the RPC clusters. At the operational working point, chambers showed an average 98-99 % efficiency and a cluster size less than 1.5 strip units.

#### VI. TRIGGER SLICE PERFORMANCES

Using the 25 ns bunch beam, trigger performances and synchronizations could be studied. This was the first test of the whole off-detector trigger slice and showed the expected

Fig. 4. High Voltage scan results for RPC chambers: cluster size (top) and efficiency plateau (bottom) for different FE thresholds.

behavior of the system. The Region of Interest information was correctly transmitted along the slice, and checked at the CTP output. Correlations between data coming from different trigger detectors, like for example RPCs hits, TGC hits and MDTs track extrapolations, confirmed the validity of the data and the perfect trigger and readout synchronization during data taking. Also the full integration of the Muon and the Calorimeters Triggers was successful with data taking controlled by the CTP trigger output signal.

During normal data taking self-trigger rate was around 200 Hz, while using cosmic rays during no-beam periods the rate was always less than 5 Hz, using the system configured for triggering on horizontal tracks.

At the test beam the Sector Logic and the MUCTPI were configured in order to generate debugging readout data, along with the proper trigger data. The Muon Barrel system showed a 99.5% efficiency in identifying the correct BC compared with value found by the MUCTPI while using the RPC trigger as the only input signal. This ensured that the BC identification capability is not significantly degradated along the trigger data path.

The RPCs trigger efficiency has been measured at the output of the PAD system, using the RPC readout information which also contain coincidence patterns, using a hodoscope trigger which covers a large part of one RPC chamber. With the default configuration 3-over-4, the trigger efficiency of the low $p_t$  system in the  $\phi$  projection was 99.4%. The  $\eta$  coordinate system could not be tested since the length of cabling could not compensate unexpected delay between low and high- $p_t$ trigger procedures. For this reason, ASICs redesign is currently going on for small functional changes, above all larger pipeline buffers and more robustness against radiation damages.

## VII. TRIGGER LATENCY EXTRAPOLATION

Key parameter of the level-1 trigger system is the trigger latency, the time delay imposed to the front end electronics before sending the readout data. It's fixed by the required

TABLE I

CONTRIBUTIONS (IN NS) TO RPC TRIGGER LATENCY

| $\Delta T$                      | H8 test beam | ATLAS expected |

|---------------------------------|--------------|----------------|

| TOF to middle station           | 31 (9.5 m)   | 50 (15 m)      |

| optical fibers transmission     | 625 (125 m)  | 325 (65 m)     |

| LV1 Muon Barrel processing time | 599          | 599            |

| SL-MUCTPI LVDS connections      | 5 (1 m)      | 50 (10 m)      |

| MUCTPI-CTP output               | 290          | 290            |

| L1A latency                     | 650          | 350            |

| MUCTPI input                    | 1260         | 1024           |

| CTP output                      | 1550         | 1314           |

processing time plus time propagation along the cabling system. The maximum acceptable value in ATLAS is 2.5  $\mu$ s, equal to 100 bunch-crossings. This test beam was useful to spot out possible problems in timing whenever real chambers and electronics from different sub-detectors are assembled together. Cross check studies from different sub-detectors have been useful to get a consistent picture of the system.

All trigger signals (10x10 hodoscope, large hodoscope and CTP) have been aligned in time in order to switch to one trigger to another while keeping the timing the same. All subdetectors trigger signals had to be synchronous to the machine clock, so a great work has been done by the central trigger group to set up delays for phase synchronization. Concerning the RPC system, we measured the time window required by the interaction signal at the hodoscope to reach the output of the Sector Logic. For this measurement many contributions must be evaluated; the time propagation along cables and optical fibers is taken as 5 ns/m and 3.3 ns/m is for particles speed in air. Time needed for the signal to arrive from the hodoscope to the CTP output was measured with a scope, adding contributions from discriminators and coincidence modules, and resulted in 1.55  $\mu$ s. The contributions of MUCTPI latency (125 ns), MUCTPI-CTP connections and pipelines (40 ns) and CTP latency (125 ns) must be subtracted. No input pipeline for the RPC data on the MUCTPI was added, since it was coming later than the TGC data. RPCs latency can be obtained subtracting time-offlight from the hodoscope to the RPC chambers, which was evaluated as 31 ns from the layout geometry. The total latency of the slice also includes in addition the L1A latency, which was estimated equal to 650 ns (25 ns for TTCvi processing time plus 125 m of optical fibers).

In Table I contributions to the low- $p_t$  trigger latency measurements are shown compared with those extrapolated for the real ATLAS cable length setup. The extrapolated ATLAS trigger latency for the Barrel Muon system at the input of the MUCTPI results in  $\Delta T_L = 1024$  ns, equal to ~ 41 BCs. Uncertainty on this measurement can be set at 15 ns.

The partial contributions to the system processing time have been measured in laboratory using the same configuration and pipeline adjustments as in the test beam: this gives a total processing time of 638 ns, 423 ns for on-detector and 215 ns for off-detector electronics. The trigger latency expected from these calculation is then 1063 ns, while the value declared on the TDR is 950 ns. With an uncertainty of 3 BC units, the present measurement is in agreement with both the expected values.

# VIII. CONCLUSIONS

Functionality of the full chain of the RPC electronics system has been tested with muons at H8 beam line of CERN SPS. Besides the check of the validity of the trigger logic, the main purpose of the test was to validate the entire slice and can be seen as an important precommissioning tool for:

- fibers, power controls, cabling

- on/off detector boards and their integration

- multi-detector integration

- trigger and readout patterns

- ATLAS DAQ and Event Filter architecture

First-level Muon Trigger system in Barrel performed successfully and more detailed data analysis will allow to check the system behavior in all its configurations. The trigger output signals have been successfully accepted by the MUCTPI, imposing a latency which corresponds to what was expected. The readout data have been merged in the ATLAS common readout chain and synchronized with ones from the other subdetectors.

## ACKNOWLEDGMENT

We would like to acknowledge the CERN SPS and H8 beam line crew for giving us 25ns structured beam during the test. We are grateful to T. Wengler and T. Pauly for their help in the MUCTPI system integration and for their contributions to our latency measurements.

#### REFERENCES

- ATLAS First-Level Trigger Technical Design Report, CERN/LHCC/98-24 (1998).

- [2] A. Di Mattia *et al.*, "ATLAS Level-1 Muon Barrel Trigger robustness study at X5 test facility", Nucl. Instrum. Meth., A 518 (2004) 529-531

- [3] G. Aielli *et al.*, "Rpc Front-End Electronics For The Atlas Lvl1 Trigger Detector", Nucl. Instrum. Meth. A 409 (1998) 291.

- [4] V.Bocci et al. "The Coincidence Matrix ASIC of the Level-1 Muon Barrel Trigger of the ATLAS Experiment", August 2003 Issue (vol. 50, no. 4) of IEEE Trans. on Nucl. Sc.

- [5] A.Salamon et al., "The Sector Logic demonstrator of the Level-1 Muon Barrel Trigger of the ATLAS Experiment", Proc. of the 7th Workshop on Electronics for LHC Experiments, Stockholm, Sweden, 10-14 Sep 2001

- [6] N.Ellis et al. "The ATLAS Level-1 Muon to Central Trigger Processor Interface (MUCTPI)", 8th Workshop on Electronics for LHC Experiments Colmar, France, Sep. 9 R 13, 2002