# A Model for Sequential Processing in the ATLAS LVL2/LVL3 Trigger

# Version 1.0

J. Bystricky, D. Calvet, J. Ernwein, O. Gachelin, T. Hansl-Kozanecka, J.R. Hubbard, M. Huet, P. Le Dû, I. Mandjavidze, M. Mur, M. Smizanska, and B. Thooris

> CEA - DAPNIA, Saclay 91191 Gif-sur-Yvette, France

#### Abstract

A model of the ATLAS trigger is proposed, including preprocessing, data transfers, algorithm sequences and execution times. Latencies and processor and switch occupations are calculated, based on trigger menus for low luminosity  $(10^{33} \text{ cm}^{-2} \text{ s}^{-1})$  described in a previous ATLAS note [1]. A sequential processing option is proposed in which all trigger selection algorithms are executed at LVL2. We show that this option requires fewer resources (network bandwidth and processors) than standard options in which trigger selection is split between LVL2 and LVL3 processing farms.

# Table of Content

| 1.   | Introduction 2                                             |

|------|------------------------------------------------------------|

| 2.   | Single-Farm Architecture 2                                 |

| 3.   | Assumptions 3                                              |

| 3.1  | Data Volumes 3                                             |

| 3.2  | Data Transfer.5                                            |

| 3.3  | Preprocessing 5                                            |

| 3.4  | Algorithm Execution Times 6                                |

| 4.   | Processing Sequence                                        |

| 4.1  | Processing Sequence Step-by-Step 8                         |

| 4.2  | Latency and Occupation Step-by-Step11                      |

| 4.3  | Detector Parameters for Processes at L=10 <sup>33</sup> 15 |

| 4.4  | Global Resources17                                         |

| 5.   | Sequential Processing at L=10 <sup>33</sup>                |

| 5.1  | Notation                                                   |

| 5.2  | Model for Sequential Processing22                          |

| 5.3  | Summary of Rates25                                         |

| 5.4  | Latency and Occupation at LVL2                             |

| 5.5  | Latency and Occupation at LVL3                             |

| 5.6  | Sequential Processing Options                              |

| 5.7  | Sequential vs. Parallel Processing                         |

| 6.   | Conclusions                                                |

| Refe | erences                                                    |

## 1. Introduction

The execution time and the latency of the LVL2 and LVL3 event selection depends on the initial (LVL1) and final (LVL3) trigger menus and on the trigger architecture and implementation. Many of the parameters - algorithm execution times, network transmission time, and overheads - can be measured on today's machines and extrapolated to future machines. In this note, we propose a model for sequential processing of the ATLAS trigger algorithms, and we estimate the parameters required by this model, based on the information we have today.

Two options for LVL2 and LVL3 processing are considered. Both options assume sequential processing of the trigger algorithms. In the first option, the trigger selection is separated into LVL2 algorithms and LVL3 algorithms as described in the ATLAS Technical Proposal [2]; LVL2 reduces the trigger rate to a few kHz, and LVL3 reduces the rate to about 100 Hz (or a bandwidth of about 100 MB/s). In the second option all selection algorithms are executed in the LVL2 processors, and LVL3 is reserved for physics analysis and data acquisition, with an event rate of about 100 Hz.

For each of these two options, we evaluate the event selection latencies and the required processing power and network bandwidth. A trigger menu for low luminosity  $(10^{33} \text{ cm}^{-2} \text{ s}^{-1})$  described in an earlier ATLAS DAQ note [1] has been used for these studies.

The calculations contained in the present note have been labelled "paper modelling". This model is idealized with respect to the situation we will encounter in a real experiment. In real life, execution times will be distributed about some mean, with tails reaching out to execution times which are much longer than the average times estimated here. Furthermore, even though we have considered processor and network overheads in this note, we have not taken into account queuing delays. The results obtained here are necessarily optimistic with respect to the average parameters assumed, even though the parameters have been estimated conservatively.

## 2. Single Farm Architecture

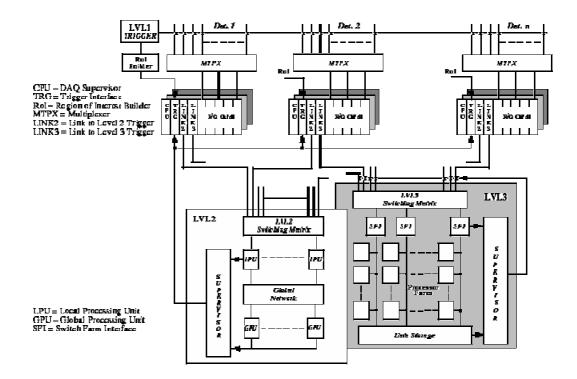

The LVL2 system described in the Technical Proposal is based on a "local-global" scheme, as shown in Fig. 1. In this scheme, "feature extraction" algorithms are executed in parallel in "local" processor farms on "local" data from each subdetector and each RoI. The results of the local feature extraction are transferred to a "global" processor farm, which makes the overall LVL2 decision.

We propose a different LVL2 architecture with a single processor farm and a single network linking that farm to the Read-Out Buffers (ROBs). This "single-farm" scheme is motivated by the ATLAS physics requirements. Efficient use of resources (networks and processors) requires a sequential processing scheme, in which events can be rejected after any of the processing steps. In our scheme, this is accomplished by assigning a single processor to each event; this processor executes the trigger algorithms step-by-step, requesting data for the next processing step only if the analysis is still consistent with at least one set of trigger conditions.

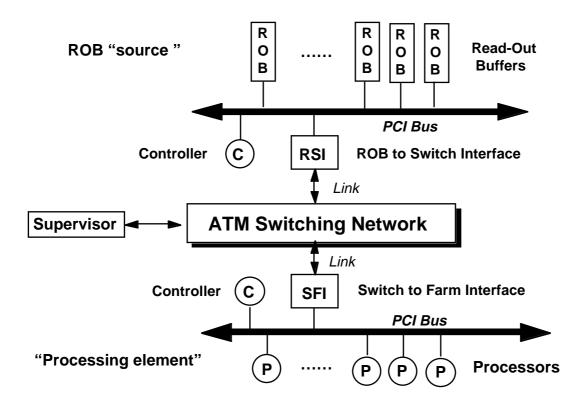

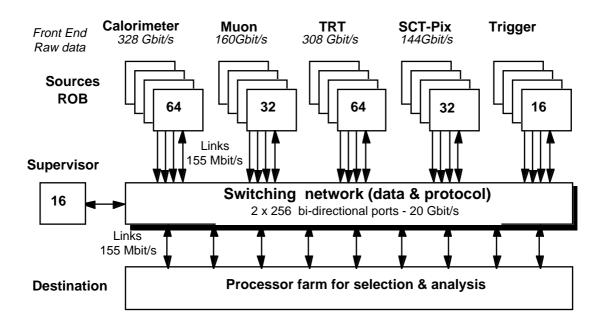

The specific implementation described here is based on the functional model shown in Figs. 2 and 3. A group of ROBs is connected to a switching network via a ROB-to-Switch Interface (RSI). Similarly, a group of processors (typically 4-8) in the processor farm are connected to the same switching network via a Switch-to-Farm Interface (SFI). The LVL2 Supervisor assigns

an event to a given LVL2 processor, which requests data from the ROBs as needed for processing the sequential trigger algorithms. All of the control messages and all of the data transit through the same bi-directional switching network. The final LVL2 decision is sent to the LVL2 Supervisor by the LVL2 processor in charge of the event. The Supervisor broadcasts the decisions to all of the ROB's via the network.

If the event is accepted at LVL2, the ROBs send all their data to the LVL3 processor specified by the LVL2 (or LVL3) Supervisor; this process is called "Event Building". For certain types of events, partial data instead of full data may be sent to the LVL3 Event Builder, but this case will not be considered in this note.

## 3. Assumptions

In this paper we attempt to model the "final" ATLAS T/DAQ system, rather than today's demonstrators or prototypes. The set of working assumptions listed in this section are our "best-guess" values, based in part on measurements made with today's hardware and in part on estimates of future hardware and software performance. Data transfer times are taken to be those which can be obtained with today's ATM switching hardware and software performance. Algorithm execution times are taken to be five times faster than those obtained today.

Many people have contributed to our current understanding of the parameters, partly through discussions and partly by measuring certain parameters on today's hardware. Developping a better set of working assumptions requires more discussion, more measurements, and more complete modellization. We would appreciate constructive criticism of the assumptions used here.

#### 3.1 Data Volumes

Our assumptions concerning the data volumes in the ROBs and the RSIs are based on the work by R. Bock and P. Le Dû on the interfaces with the front-end systems [3]. The data volumes (per event) are given in the following table for each subdetector, along with the number of ROBs, the number of RSIs, and  $\Delta \eta \propto \Delta \phi$  for the ROBs and the RSIs. There are two entries for the TRT data, one for low luminosity and one for high luminosity.

#### DATA VOLUMES PER EVENT IN ROBS AND RSIS

| Subdetector                                                        | data                                          | ROBs                                                | $\Delta\eta \ge \Delta\phi$                                   | RSI's                                          | Δη x Δφ                                                       |

|--------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|

| muon<br>calorimeter<br>TRT L= $10^{33}$<br>TRT L= $10^{34}$<br>SCT | 185 kB<br>450 kB<br>80 kB<br>320 kB<br>320 kB | 128 ROB<br>256 ROB<br>256 ROB<br>256 ROB<br>128 ROB | 0.8 x 0.2<br>0.4 x 0.4<br>0.8 x 0.1<br>0.8 x 0.1<br>1.2 x 0.2 | 32 RSI<br>64 RSI<br>64 RSI<br>64 RSI<br>32 RSI | 0.8 x 0.8<br>1.6 x 0.4<br>0.8 x 0.4<br>0.8 x 0.4<br>1.2 x 0.8 |

| Total L= $10^{33}$<br>Total L= $10^{34}$                           | 1035 kB<br>1275 kB                            | 768 ROB<br>768 ROB                                  |                                                               | 192 RSI<br>192 RSI                             |                                                               |

We assume that there has been zero suppression for the TRT data in the front-end Read-Out Drivers (ROD's). Without zero suppression, the TRT data would be 790 kB. The TRT data includes data from three beam crossings, but we assume that data from a single beam-crossing are used for feature extraction. The SCT data includes 55 kB of pixel data.

The number of ROBs in the table is only half of the standard number of ROBs. This is based on the assumption that we can input data to each ROB from two ROD's (i.e., two 1 Gbit/s links). This assumption needs verification. We will produce tables with the standard hypothesis (1 536 ROBs) in the next version of this note.

The data volume in each Region of Interest (RoI), as well as the size of the RoI for each trigger and/or for each subsystem, is given in the next table.

| DATA VOLUMES IN RoIs AFTER PREPROCESSING |              |                  |                    |                  |                         |

|------------------------------------------|--------------|------------------|--------------------|------------------|-------------------------|

| RoI type                                 | system       | RoI data         | ROBs/RoI           | RSIs/RoI         | Δη x Δφ                 |

| muon trigger<br>muon trigger             | MUON<br>CALO | 1 kB<br>3 kB     | 1 ROB<br>3 ROB     | 1 RSI<br>2 RSI   | 0.1 x 0.1<br>0.4 x 0.4  |

| e / γ/ τ trigger<br>jet trigger          | CALO<br>CALO | 3 kB<br>3 kB     | 3 ROB<br>9 ROB     | 2 RSI<br>5 RSI   | 0.4 x 0.4<br>1.2 x 1.2  |

| track $L=10^{33}$                        | TRT          | 0.1 kB           | 3 ROB              | 2 RSI            | 0. 8 x 0.2              |

| track L=10 <sup>34</sup><br>track        | TRT<br>SCT   | 0.3 kB<br>0.2 kB | 3 ROB<br>2 ROB     | 2 RSI<br>1 RSI   | 0.8 x 0.2<br>0.2 x 0.2  |

| TRT scan $L=10^{33}$                     | TRT          | 16 kB            | 256 ROB            | 64 RSI           | 5.0 x 6.4               |

| TRT scan L= $10^{34}$ missing- $E_T$     | TRT<br>CALO  | 64 kB<br>16 kB   | 256 ROB<br>256 ROB | 64 RSI<br>64 RSI | 5.0 x 6.4<br>10.0 x 6.4 |

| b-jet tag                                | SCT          | 3 kB             | 8 ROB              | 3 RSI            | 0.8 x 0.8               |

Note that we assume that only data inside the RoI is transferred to the LVL2 processors (after preprocessing in each ROB). The e /  $\gamma$  and  $\tau$  algorithms are based on the same RoIs; they have been grouped together in the table. The single hadron trigger is a special case of the  $\tau$  trigger.

## 3.2 Data Transfer

Data transfer rates and overheads have been measured at Saclay, both on ATM switching fabrics and on PCI busses. The nominal transfer rates are 19 MB/s (155 Mbits/s) for each link of the ATM switch, and 132 MB/s for the PCI bus; the maximum rates of useful data were measured to be about 15 MB/s for a ATM link, and 70 MB/s for the PCI bus. The data transfer latency was 50 µs through the ATM switch.

The ATM switches have dual links at each port, for data transfers in the two directions. The occupancy should be calculated for transfers in each direction. In our case, data transfers from the ROBs to the (LVL2 and LVL3) processors (designated ATM1) have much higher bandwidth than the control messages transferred from the processors to the ROBs (ATM2).

The processors suffer overheads for data transfers. The device-driver software overhead for sending a message has been measured to be about 30  $\mu$ s; we assume that this overhead can be reduced to 10  $\mu$ s in the future. The overhead for receiving a message has been measured to be about 50  $\mu$ s; we assume that it will continue to be about 50  $\mu$ s in the future. (The ATM measurements were made using a 50 MHz PowerPC with a LynxOS operating system and a 50 MHz Sparc20 workstation )

We assume that the data from the ROBs will be reordered in the RSIs before being transferred to the switching network, and that data arriving from different RSIs will again be reordered in the SFI's before transfer to the LVL2 processors. We assume that the data can be reordered at the rate of 50 MB/s.

#### 3.3 Preprocessing

We assume that the raw data in the ROBs is preprocessed before sending it to the LVL2 processors. We assume that this preprocessing is performed separately for each ROB. The preprocessing algorithms have not yet been written (although the calorimeter preprocessing is rather trivial), so their execution times could not be measured. Our assumptions about the preprocessing algorithms and their execution times are given in the following table. Our model assumes intelligence equivalent to a 100 MIPS DSP in each of the ROBs.

| Trigger                       | system | preprocessing | algorithm                             |

|-------------------------------|--------|---------------|---------------------------------------|

| muon trigger                  | MUON   | 100 µs        | Space points                          |

| e / $\gamma$ / $\tau$ trigger | EMC    | 50 µs         | Calibration only                      |

| e / $\gamma$ / $\tau$ trigger | HAC    | 20 µs         | Calibration only                      |

| jet trigger                   | EMC    | 50 µs         | Calib.+Energy sums                    |

| jet trigger                   | HAC    | 20 µs         | Calibration only                      |

| missing- $E_T$                | EMC    | 70 µs         | Calib. + Calculate E <sub>X</sub> , E |

| missing- $E_T$                | HAC    | 40 µs         | Calib. + Calculate $E_X$ , E          |

| track L=1033                  | TRT    | 200 µs        | Data compression                      |

| track L=1034                  | TRT    | 800 µs        | Data compression                      |

| track                         | SCT    | 200 µs        | Space points                          |

| b-jet tag                     | SCT    | 800 µs        | Space points                          |

#### PREPROCESSING EXECUTION TIMES PER ROB

#### 3.4 Algorithm Execution Times

Stand-alone versions of the subdetector feature extraction algorithms have been written and benchmarked at several institutions. The pioneer work on algorithms and their execution times was performed at CERN [4]. More recently stand-alone muon feature extraction code has been written and benchmarked in Rome, using a 40 MIPS DSP with optimized Fortran code [5]. The calorimeter feature extraction code has been benchmarked at Saclay on several machines, with different levels of optimization. Detailed studies of the precision-tracker code have been carried out by S.Sivoklokov, R.Dankers, and J.Baines [6]. For the TRT, we use the benchmarks established by Hauser and Legrand [4], even though their algorithm has not yet been compared with the algorithm used in the ATRIG code. For the full TRT scan required for the B-physics algorithms, M.Smizanska has measured execution times on standard CERN processor farms [7]; execution times for optimized code have not yet been measured.

The assumptions about feature extraction execution times shown in the table below are based on extrapolations of the measured execution times to what we would expect using optimized code on a future 500 MHz processor. In general, we have divided the measured execution times by a factor five to account for the expected improvement in the speed of the processors, but we have multiplied the values obtained using stand-alone code by a factor two because we expect that additional data manipulation will be required in the final code. We have also reduced the execution time for the full TRT scan by a factor three because we believe that such an improvement can be obtained when we optimize the code for low- $p_T$  tracks.

The algorithm for the b-jet tag has not been studied in the trigger group. Typically execution times for off-line code are "a few seconds", with long tails at larger execution times.

The estimate in the table below is 250 ms average execution time, using optimized code in the LVL2 processors. This assumes a factor five improvement in the processor speed, and another factor two due to optimization of the LVL2 code.

| Trigger                     | system | processing | measured execution tin |     |

|-----------------------------|--------|------------|------------------------|-----|

|                             |        | (µs)       | (µs)                   |     |

| muon trigger                | MUON   | 100        | 220                    | [5] |

| $e / \gamma / \tau$ trigger | CALO   | 100        | 125                    |     |

| jet trigger                 | CALO   | 100        |                        |     |

| track                       | TRT    | 600        | 700                    | [4] |

| track                       | SCT    | 800        | 1 840                  | [6] |

| TRT scan L= $10^{33}$       | TRT    | 50 000     | 680 000                | [7] |

| TRT scan L=10 <sup>34</sup> | TRT    | 200 000    |                        |     |

| missing- $E_T$              | CALO   | 100        |                        |     |

| b-jet tag                   | SCT    | 250 000    |                        |     |

An important feature of the sequential processing model is that the LVL2 processors must be able to perform in a multi-task mode, with several events being processed at the same time. When a processor requests new data for the event being processed, these data will be available only after a delay of several 100  $\mu$ s. In order to avoid losing this time, the processor must be able to switch to another event. The overhead due to this context switching has been measured at Saclay to be about 60  $\mu$ s; we assume that the context switching will require 50  $\mu$ s in the future.

In the more standard option for the ATLAS trigger, some of the event selection is performed at LVL3. Here we assume that any recalculation of the missing- $E_T$  and any calculation of b-jet tags would be performed at LVL3 in this option. We expect that the LVL3 code would be similar to the off-line analysis code, and less optimized than the LVL2 code.

We assume that the processing time would be larger by a factor two at LVL3, compared to the processing time for the same algorithm at LVL2. Furthermore, we assume that the LVL3 analysis is not limited to Regions of Interest, and that the minimum time for the treatment of any event at LVL3 would be about 100 ms. We also assume that a full physics analysis can be performed in a few seconds, on average. These LVL3 execution times are summarized in the following table:

| Algorithm                        | processing time (ms) |

|----------------------------------|----------------------|

| masses, multiplicities           | 100                  |

| B physics algorithms $L=10^{33}$ | 100                  |

| B physics algorithms $L=10^{34}$ | 400                  |

| b-jet tag                        | 500                  |

| physics analysis                 | 1 - 10 s             |

#### LVL3 ALGORITHM PROCESSING TIMES

# 4. Processing Sequence

This chapter gives a quantitative model for sequential processing in a single-farm architecture. The timing is given for each step in the processing sequence. These estimated times are then used to calculate the event selection latencies and the resources required (network links and processors) for different LVL2 and LVL3 strategies. The average latency and the resources required are then calculated for a specific trigger menu and for a specific model for the sequential algorithms and for the step-by-step rejection factors.

Two important processing steps have been left out of the present study. For events accepted by the LVL2 trigger, LVL2 data produced by the LVL2 processors (features, masses,etc.) must be transfered through the switching network to the LVL2 trigger ROBs; this process has not been modelled here. Furthermore, the LVL2 and LVL3 processing must be monitored for efficiency and errors; unfortunately, we do not yet have a model for these control functions.

#### 4.1 Processing Sequence Step-by-Step

The LVL2 and LVL3 processing sequence (for any given algorithm) is broken down into 13 processing steps, starting with the transfer of data from the front-end RODs to the ROBs, and ending with the transfer of the LVL3 decision to the supervisor. Any comparison of different event selection strategies must include all of the data transfers and all of the trigger selection algorithms (whether executed at LVL2 or at LVL3).

The execution times in this section are based on the assumptions listed in Chapter 3 of this note. When data transfers are required, an estimate of the data volume to be transferred is given in the last column, after the execution time. Execution times listed as "x/RSI" or "y/ROB" indicate that the execution times (x or y) should be multiplied by the number of RSIs or ROBs implicated in that particular data transfer. Execution times listed as "RoI data / z MB/s" indicate execution times of  $1/z \mu s$  per byte of data in the RoI. The expressions "ROB", "RSI", and "RoI" refer to the number of ROB's, RSI's, or RoI's involved in that particular transfer of data. Preprocessing, feature extraction, and LVL3 algorithm execution times are denoted by "T<sub>pre</sub>",

"T<sub>fex</sub>", and "T<sub>alg</sub>", respectively.

The sequential nature of the processing model described here is illustrated by the repetition indicated for processing steps 3 to 7. The sequential data requests and data transfers are described in these five processing steps. Each data request is preceded by a test of the compatibility of the event with the LVL2 trigger conditions.

The processing steps and their execution times are given below:

| 1) | SEND LVL1 DATA 7 | TO LVL2          |                        |            |

|----|------------------|------------------|------------------------|------------|

| ,  | ROD latency      |                  | 100 µs                 |            |

|    | ROBIN            | ROD -> ROB       | 10 µs / link           |            |

|    | ROI Builder      | RoIs -> SUPER    | 100 µs                 |            |

| 2) | ASSIGN LVL2 PRO  | CESSOR           |                        |            |

|    | SUPER            | code message     | 50 µs                  |            |

|    |                  | send -> SFI      | 10 µs                  |            |

|    | ATM1             | latency          | 50 µs                  |            |

|    |                  | transfer         | 6 µs                   | 0.1 kB     |

|    | SFI              | receive          | 50 µs                  |            |

|    |                  | send -> LVL2     | 10 µs                  |            |

|    | PCI              | transfer         | 2 µs                   | 0.1 kB     |

|    | LVL2             | switch context   | 50 µs                  |            |

| 3) | REQUEST DATA FR  | COM ROBs         |                        |            |

|    | LVL2             | process RoI info | 50 µs                  |            |

|    |                  | send -> SFI      | 10 µs                  |            |

|    | PCI              | transfer         | 2 µs                   | 0.1 kB     |

|    | SFI              | receive          | 50 µs                  |            |

|    |                  | send -> RSI      | 10 µs                  |            |

|    | ATM2             | latency          | 50 µs                  |            |

|    |                  | transfer         | 6 µs / RSI             | 0.1 kB/RSI |

|    | RSI              | receive          | 50 µs / RSI            |            |

|    |                  | send -> ROB      | 10 µs / ROB            |            |

|    | PCI              | transfer         | $2 \mu s / ROB$        | 0.1 kB/ROB |

|    | ROB              | receive          | $50 \ \mu s \ / \ ROB$ |            |

| 4) | PREPROCESS DATA  | A IN EACH ROB    |                        |            |

# ROB preprocess T<sub>pre</sub> / ROB

# 5) SEND PREPROCESSED DATA TO LVL2

| ROB<br>PCI  | send -> RSI<br>transfer                    | 10 µs / ROB<br>RoI data / 70 MB/s    | RoI data |

|-------------|--------------------------------------------|--------------------------------------|----------|

| RSI         | receive<br>reorder data                    | 50 µs / ROB<br>RoI data / 50 MB/s    |          |

|             | send -> SFI                                | 10 µs / RSI                          |          |

| ATM1        | latency<br>transfer                        | 50 μs<br>RoI data / 15 MB/s          | RoI data |

| SFI         | receive<br>reorder data                    | 50 μs / RSI<br>RoI data / 50 MB/s    |          |

| PCI<br>LVL2 | send -> LVL2<br>transfer<br>switch context | 10 μs<br>RoI data / 70 MB/s<br>50 μs | RoI data |

#### 6) EXECUTE FEATURE EXTRACTION ALGORITHMS

| LVL2 | feature extraction | T <sub>fex</sub> / RoI |

|------|--------------------|------------------------|

|------|--------------------|------------------------|

| 7) TEST COMPATIBILITY | WITH LVL2 TRIGGER |       |

|-----------------------|-------------------|-------|

| LVL2                  | reject / continue | 50 µs |

# REPEAT STEPS 3 TO 7 AS REQUIRED FOR OTHER DETECTOR SYSTEMS AND/OR ROIs

| 8) '                                | 8) TEST GLOBAL LVL2 TRIGGER CONDITIONS |                  |                 |            |  |  |  |

|-------------------------------------|----------------------------------------|------------------|-----------------|------------|--|--|--|

|                                     | LVL2                                   | accept / reject  | 150 µs          |            |  |  |  |

| 9) SEND LVL2 DECISION TO SUPERVISOR |                                        |                  |                 |            |  |  |  |

|                                     | LVL2                                   | send -> SFI      | 10 µs           |            |  |  |  |

|                                     | PCI                                    | transfer         | 2 µs            | 0.1 kB     |  |  |  |

|                                     | SFI                                    | receive          | 50 µs           |            |  |  |  |

|                                     |                                        | send -> SUPER    | 10 µs           |            |  |  |  |

|                                     | ATM2                                   | latency          | 50 µs           |            |  |  |  |

|                                     |                                        | transfer         | 6 µs            | 0.1 kB     |  |  |  |

|                                     | SUPER                                  | receive          | 50 µs           |            |  |  |  |

| 10) BR(                             | DADCAST LVL2 D                         | ECISION          |                 |            |  |  |  |

|                                     | SUPER                                  | broadcast -> RSI | 10 µs           |            |  |  |  |

|                                     | ATM2                                   | latency          | 50 µs           |            |  |  |  |

|                                     |                                        | transfer         | 6 µs / RSI      | 0.1 kB/RSI |  |  |  |

| ]                                   | RSI                                    | receive          | 50 µs / RSI     |            |  |  |  |

|                                     |                                        | send -> ROB      | 10 µs / ROB     |            |  |  |  |

| ]                                   | PCI                                    | transfer         | $2 \mu s / ROB$ | 0.1 kB/ROB |  |  |  |

| ]                                   | ROB                                    | receive          | 50 μs / ROB     |            |  |  |  |

|                                     |                                        | clear buffer     | 10 μs / ROB     |            |  |  |  |

|                                     |                                        | 10               |                 |            |  |  |  |

#### 11) SEND DATA TO LVL3 PROCESSORS

| ROB<br>PCI  |             | send -> RSI<br>transfer                | 10 µs / ROB<br>RoI data / 70 MB/s                | RoI data |

|-------------|-------------|----------------------------------------|--------------------------------------------------|----------|

| RSI         |             | receive<br>reorder data<br>send -> SFI | 50 μs / ROB<br>RoI data / 50 MB/s<br>10 μs / RSI |          |

| ATM1        |             | latency<br>transfer                    | 50 μs<br>RoI data / 15 MB/s                      | RoI data |

| SFI         |             | receive<br>reorder data                | 50 µs / RSI<br>RoI data / 50 MB/s                |          |

| PCI         |             | send -> LVL3<br>transfer               | 10 μs<br>RoI data / 70 MB/s                      | RoI data |

| LVL3        |             | switch context                         | 50 µs                                            |          |

| 12) EXECUT  | E LVL3 ALGC | RITHMS                                 |                                                  |          |

| LVL3        |             | execute algorithms                     | T <sub>alg</sub>                                 |          |

| 13) SEND LV | L3 DECISION | TO SUPERVISOR                          |                                                  |          |

|             | LVL2        | send -> SFI                            | 10 µs                                            |          |

|             | PCI         | transfer                               | 2 µs                                             | 0.1 kB   |

|             | SFI         | receive                                | 50 µs                                            |          |

|             |             | send -> SUPER                          | 10 µs                                            |          |

|             | ATM2        | latency                                | 50 µs                                            |          |

|             |             | transfer                               | 6 μs                                             | 0.1 kB   |

|             | SUPER       | receive                                | 50 µs                                            |          |

#### 4.2 Latency and Occupation Step-by-Step

The execution times can be regrouped to indicate the overall latency at each step of the processing, as well as the total execution time for each of the hardware elements. The notation is the same as in the preceding section, except that the expression "max(ROB/RSI)' is used in the calculation of latencies to take account of the parallel operation of the groups of ROBs assigned to each RSI.

For certain operations involving the LVL2 Supervisor and the broadcast of information by the LVL2 Supervisor, percentage occupations are listed in parentheses after the operation. These percentages are above 100%, so these operations will not be possible without special treatment. In step 1), the 200% WRITE occupation of the ROBs corresponds to the non-standard use of two 1 Gbit/s links for each ROB. The 600% Supervisor occupation in step 2) and the 500% Supervisor occupation in step 9) can be resolved by implementing the LVL2 Supervisor as a farm, with at least six bi-directional links connecting to the switching network. The 600% ROB and the 900% RSI occupations due to the broadcast by the LVL2 Supervisor to all of the ROBs of the final LVL2 decisions can be resolved by grouping the decisions in the Supervisor, and broadcasting them together at fixed intervals (once every 1 ms); the occupation levels of the Supervisor, the RSI PCI busses, and the ATM2 links (Supervisor  $\rightarrow$  ROBs) are also reduced to acceptable levels by this grouping of the final decision broadcasts.

The step-by-step latencies and the occupation of each of the hardware elements is given below:

| 1) | SEND LVL1 DATA TO LVL2                          |                                     |                        |

|----|-------------------------------------------------|-------------------------------------|------------------------|

|    | Latency                                         | 100 µs                              |                        |

|    | SUPER occupation                                | 10 µs                               |                        |

|    | ROB occupation<br>RSI PCI occupation            | 20 µs / ROB                         | (200% WRITE occupancy) |

|    | RSI occupation<br>ATM occupation                | 0<br>0                              |                        |

|    | SFI occupation                                  | 0                                   |                        |

|    | SFI PCI occupation<br>LVL2 processor occupation | $\begin{array}{c} 0\\ 0\end{array}$ |                        |

| 2) | ASSIGN LVL2 PROCESSOR                           |                                     |                        |

|    | Latency                                         | 228 µs                              |                        |

|    | SUPER occupation                                | 60 µs                               | (600% occupation)      |

|    | ROB occupation                                  | 0                                   |                        |

|    | RSI PCI occupation<br>RSI occupation            | $\begin{array}{c} 0\\ 0\end{array}$ |                        |

|    | ATM1 occupation                                 | 6 µs                                |                        |

|    | SFI occupation                                  | 60 µs                               |                        |

|    | SFI PCI occupation                              | 2 µs                                |                        |

|    | LVL2 processor occupation                       | 50 µs                               |                        |

| 3) | <b>REQUEST DATA FROM ROBs</b>                   |                                     |                        |

|    | Latency                                         | $272 \mu s + 6 \mu s * I$           | RSI/RoI *RoI           |

|    |                                                 | $+ 12 \mu s * max(R)$               | OB/RSI)                |

|    | SUPER occupation                                | 0                                   |                        |

|    | ROB occupation                                  | $50 \mu s * ROB/Rol$                | I * RoI                |

|    | <b>RSI PCI occupation</b>                       | $2 \mu s * ROB/Rol$                 | I * RoI                |

|    | RSI occupation                                  | $10 \ \mu s * ROB/Rol$              | I * RoI                |

|    |                                                 | + 50 $\mu$ s * RSI/Re               | oI * RoI               |

|    | ATM2 occupation                                 | 6 μs * RSI/RoI                      | * RoI                  |

|    | SFI occupation                                  | 60 µs                               |                        |

|    | SFI PCI occupation                              | 2 µs                                |                        |

|    | LVL2 processor occupation                       | 60 µs                               |                        |

# 4) PREPROCESS DATA IN EACH ROB

| Latency                   | max(T <sub>pre</sub> )           |

|---------------------------|----------------------------------|

| SUPER occupation          | 0                                |

| ROB occupation            | T <sub>pre</sub> * ROB/RoI * RoI |

| RSI PCI occupation        | 0                                |

| RSI occupation            | 0                                |

| ATM occupation            | 0                                |

| SFI occupation            | 0                                |

| SFI PCI occupation        | 0                                |

| LVL2 processor occupation | 0                                |

# 5) SEND PREPROCESSED DATA TO LVL2

| Latency                              | 130 μs<br>+ RSI data / 70 MB/s<br>+ RSI data / 50 MB/s                                                            |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                      | + 50 µs * max (ROB/RSI)                                                                                           |

|                                      | + 50 μs * RSI/RoI * RoI<br>+ RoI * RoI data / 15 MB/s<br>+ RoI * RoI data / 50 MB/s<br>+ RoI * RoI data / 70 MB/s |

| SUPER occupation                     | 0                                                                                                                 |

| ROB occupation<br>RSI PCI occupation | 10 µs * ROB/RoI * RoI<br>RoI * RoI data / 70 MB/s                                                                 |

| RSI occupation                       | 50 µs * ROB/RoI * RoI<br>+ RoI * RoI data / 50 MB/s                                                               |

| ATM1 occupation                      | + 10 µs * RSI/RoI * RoI<br>RoI * RoI data / 15 MB/s                                                               |

| SFI occupation                       | 50 µs * RSI/RoI * RoI<br>+ RoI * RoI data / 50 MB/s                                                               |

|                                      | + 10 μs                                                                                                           |

|                                      |                                                                                                                   |

# SFI PCI occupationRoI \* RoI data / 70 MB/sLVL2 processor occupation50 μs

# 6) EXECUTE FEATURE EXTRACTION ALGORITHMS

| Latency                   | T <sub>fex</sub> * RoI |

|---------------------------|------------------------|

| SUPER occupation          | 0                      |

| ROB occupation            | 0                      |

| RSI PCI occupation        | 0                      |

| RSI occupation            | 0                      |

| ATM occupation            | 0                      |

| SFI occupation            | 0                      |

| SFI PCI occupation        | 0                      |

| LVL2 processor occupation | T <sub>fex</sub> * RoI |

# 7) TEST COMPATIBILITY WITH LVL2 TRIGGER

| Latency                   | 50 µs |

|---------------------------|-------|

| SUPER occupation          | 0     |

| ROB occupation            | 0     |

| RSI PCI occupation        | 0     |

| RSI occupation            | 0     |

| ATM occupation            | 0     |

| SFI occupation            | 0     |

| SFI PCI occupation        | 0     |

| LVL2 processor occupation | 50 µs |

# REPEAT STEPS 3 TO 7 AS REQUIRED FOR OTHER DETECTOR SYSTEMS AND/OR ROI'S

| 8)  | TEST GLOBAL LVL2 TRIGGER C       | ONDITIONS                           |                   |

|-----|----------------------------------|-------------------------------------|-------------------|

|     | Latency                          | 150 µs                              |                   |

|     | SUPER occupation                 | 0                                   |                   |

|     | ROB occupation                   | 0                                   |                   |

|     | RSI PCI occupation               | 0                                   |                   |

|     | RSI occupation<br>ATM occupation | $\begin{array}{c} 0\\ 0\end{array}$ |                   |

|     | SFI occupation                   | 0                                   |                   |

|     | SFI PCI occupation               | Ō                                   |                   |

|     | LVL2 processor occupation        | 150 µs                              |                   |

| 9)  | SEND LVL2 DECISION TO SUPER      | RVISOR                              |                   |

|     | Latency                          | 178 µs                              |                   |

|     | SUPER occupation                 | 50 µs                               | (500% occupation) |

|     | ROB occupation                   | 0                                   | · - ·             |

|     | RSI PCI occupation               | 0                                   |                   |

|     | RSI occupation                   | 0                                   |                   |

|     | ATM2 occupation                  | 6 µs                                |                   |

|     | SFI occupation                   | 60 µs                               |                   |

|     | SFI PCI occupation               | 2 µs                                |                   |

|     | LVL2 processor occupation        | 10 µs                               |                   |

| 10) | BROADCAST LVL2 DECISION          |                                     |                   |

|     | Latency                          | 218 µs                              |                   |

|     | SUPER occupation                 | 10 µs                               | (100% occupation) |

|     | ROB occupation                   | 60 µs / ROB                         | (600% occupation) |

|     | <b>RSI PCI occupation</b>        | 8 µs / RSI                          | (80% occupation)  |

|     | RSI occupation                   | 90 µs / RSI                         | (900% occupation) |

|     | ATM2 occupation                  | 6 µs / RSI                          | ( 60% occupation) |

|     | SFI occupation                   | 0                                   |                   |

|     | SFI PCI occupation               | 0                                   |                   |

|     | LVL2 processor occupation        | 0                                   |                   |

|     |                                  |                                     |                   |

## 11) SEND DATA TO LVL3 PROCESSORS

| 11) | SEND DATA TO LVLS PROCESSORS         |                                                                                       |  |  |  |  |

|-----|--------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

|     | Latency                              | 330 μs<br>+ RSI data / 70 MB/s<br>+ RSI data / 50 MB/s                                |  |  |  |  |

|     |                                      | + 50 μs * RSI<br>+ EVT data / 15 MB/s<br>+ EVT data / 50 MB/s<br>+ EVT data / 70 MB/s |  |  |  |  |

|     | SUPER occupation                     | 0                                                                                     |  |  |  |  |

|     | ROB occupation<br>RSI PCI occupation | 10 μs * ROB<br>EVT data / 70 MB/s                                                     |  |  |  |  |

|     | RSI occupation                       | 50 μs * ROB<br>+ EVT data / 50 MB/s                                                   |  |  |  |  |

|     | ATM1 occupation                      | + 10 μs * RSI<br>EVT data / 15 MB/s                                                   |  |  |  |  |

|     | SFI occupation                       | 50 μs * RSI<br>+ EVT data / 50 MB/s                                                   |  |  |  |  |

|     | SFI PCI occupation                   | + 10 μs<br>EVT data / 70 MB/s                                                         |  |  |  |  |

|     | LVL3 processor occupation            | 50 µs                                                                                 |  |  |  |  |

| 12) | EXECUTE LVL3 ALGORITHMS<br>LVL3      | T <sub>alg</sub>                                                                      |  |  |  |  |

| 13) | SEND LVL3 DECISION TO SUPER          | RVISOR                                                                                |  |  |  |  |

|     | latency                              | 178 μs                                                                                |  |  |  |  |

|     | SUPER occupation                     | 50 µs                                                                                 |  |  |  |  |

|     | ROB occupation<br>RSI PCI occupation | 0<br>0                                                                                |  |  |  |  |

|     | RSI occupation                       | 0                                                                                     |  |  |  |  |

|     | ATM2 occupation                      | 6 µs                                                                                  |  |  |  |  |

|     | SFI occupation                       | 60 µs                                                                                 |  |  |  |  |

|     | SFI PCI occupation                   | 2 µs                                                                                  |  |  |  |  |

|     | LVL2 processor occupation            | 10 µs                                                                                 |  |  |  |  |

|     |                                      |                                                                                       |  |  |  |  |

# 4.3 Detector Parameters for Processes at L=10<sup>33</sup>

The latencies and occupations can be expressed more concisely if the variables are replaced by the detector parameters listed in Section 3. Here we treat the case of low luminosity,  $L=10^{33}$  cm<sup>-2</sup> s<sup>-1</sup>. In the table below, we list the LVL2 parameters for the following processes (or algorithms):

| MUON             | = | stand-alone LVL2 muon trigger                      |

|------------------|---|----------------------------------------------------|

| $e/\gamma/\tau$  | = | electron / gamma / tau trigger in CALO system      |

| JETs             | = | jet trigger in CALO system                         |

| SCT              | = | track trigger in SCT                               |

| TRT              | = | track trigger in TRT                               |

| TRK              | = | combined track trigger in SCT + TRT                |

| MsE <sub>T</sub> | = | missing- $E_T$ recalculation at LVL2 (CALO system) |

| Scan             | = | full TRT scan for B physics                        |

| b-tag            | = | b-jet tag in SCT system                            |

|                  |   |                                                    |

# DETECTOR PARAMETERS FOR LVL2 PROCESSING AT L= $10^{33}$ cm<sup>-2</sup> s<sup>-1</sup>

| Detector param         | neters  | MUON | $e/\gamma/\tau$ | JETs   | SCT    | TRT   | TRK    | MsE <sub>T</sub> | Scan      | b-tag  |

|------------------------|---------|------|-----------------|--------|--------|-------|--------|------------------|-----------|--------|

| ROB/RoI<br>RSI/RoI     |         | 1    | 32              | 9<br>5 | 2<br>1 | 32    | 5<br>3 | 256<br>64        | 256<br>64 | 8<br>3 |

| max(ROB/RSI            | )       | 1    | 2<br>3          | 4      | 2      | 3     | 3      | 4                | 4         | 4      |

| ROB data               | (kB)    | 1.0  | 1.0             | 0.3    | 0.1    | 0.03  |        | 0.1              | 0.1       | 0.4    |

| RSI data               | (kB)    | 1.0  | 1.5             | 0.6    | 0.2    | 0.05  |        | 0.3              |           | 1.0    |

| RoI data               | (kB)    | 1.0  | 3.0             | 3.0    | 0.2    | 0.10  | 0.30   | 16.0             | 16.0      | 3.0    |

| PCI transfer at        | 70 MI   | B/s  |                 |        |        |       |        |                  |           |        |

| ROB data/70            | (µs)    | 14   | 14              | 4      | 1      | 1     | 1      | 1                | 1         | 6      |

| RSI data/70            | (µs)    | 14   | 21              | 8      | 2      | 1     | 1      | 4                | 4         | 14     |

| RoI data/70            | (µs)    | 14   | 42              | 42     | 2      | 1     | 4      | 229              | 229       | 42     |

| Reorder data           |         |      |                 |        |        |       |        |                  |           |        |

| ROB data/50            | (µs)    | 20   | 20              | 6      | 2      | 1     | 1      | 2                | 2         | 8      |

| RSI data/50            | (µs)    | 20   | 30              | 12     | 4      | 1     | 2      | 6                | 6         | 20     |

| RoI data/50            | (µs)    | 20   | 60              | 60     | 4      | 2     | 6      | 320              | 320       | 60     |

| ATM transfer a         | at 15 M | IB/s |                 |        |        |       |        |                  |           |        |

| ROB data/15            | (µs)    | 67   | 67              | 20     | 7      | 2     | 4      | 7                | 7         | 27     |

| RSI data/15            | (µs)    | 67   | 100             | 40     | 13     | 3     | 7      | 20               | 20        | 67     |

| RoI data/15            | (µs)    | 67   | 200             | 200    | 13     | 7     | 20 1   | 067              | 1 067     | 200    |

| max(T <sub>pre</sub> ) | (µs)    | 100  | 70              | 70     | 200    | 200   | 200    | 110              | 200       | 800    |

| T <sub>fex</sub>       | (µs)    | 100  | 100             | 100    | 800    | 600 1 | 400    | 100              | 50000;2   | 50000  |

For the LVL3 algorithms, the RoI is the full detector. The relevant detector parameters for low and high luminosity are given in the table below:

|                                   |              | L=10 <sup>33</sup>     | L=10 <sup>34</sup>     |

|-----------------------------------|--------------|------------------------|------------------------|

| ROB<br>RSI<br>ROB/RSI<br>ROB data | (kB)         | 768<br>192<br>4<br>1.3 | 768<br>192<br>4<br>1.7 |

| ROD data<br>RSI data<br>EVT data  | (kB)<br>(kB) | 1.3<br>5.4<br>1 035    | 6.6<br>1 275           |

| ROB data/70                       | (µs)         | 19                     | 24                     |

| RSI data/70                       | (µs)         | 77                     | 94                     |

| EVT data/70                       | (µs)         | 14 786                 | 18 214                 |

| ROB data/50                       | (µs)         | 26                     | 34                     |

| RSI data/50                       | (µs)         | 108                    | 132                    |

| EVT data/50                       | (µs)         | 20 700                 | 25 500                 |

| ROB data/15                       | (µs)         | 87                     | 113                    |

| RSI data/15                       | (µs)         | 360                    | 440                    |

| EVT data/15                       | (µs)         | 69 000                 | 85 000                 |

| T <sub>pre</sub>                  | (µs)         | 0                      | 0                      |

| T <sub>alg</sub> (min)            | (µs)         | 10 <sup>5</sup>        | 10 <sup>5</sup>        |

| T <sub>alg</sub> (physics)        | (µs)         | 107                    | 107                    |

#### DETECTOR PARAMETERS FOR LVL3 PROCESSING

# 4.4 Global Resources at L=10<sup>33</sup>

=

Using the detector parameters listed above, we can calculate the resources required for any given trigger menu. The trigger menu must be decomposed into the trigger rate, the number of data requests for each subsystem and the number of RoIs of each type. Then the occupations can be derived from the equations shown below, where "RATE" is the relevant trigger rate, "REQ" is the number of data requests of a given type and "RoI" is the number of RoIs of that type. The total occupations are obtained by adding the total LVL2 occupations for the given trigger menu to the total LVL3 occupations. The split between LVL2 and LVL3 processing depends on the trigger strategy (option).

The total LVL2 occupations are obtained by adding the "minimal" LVL2 occupations to the contributions from each type of processing performed at LVL2 (RoIs and full TRT scan for both options, and missing- $E_T$  and b-jet tags if all of the selection algorithms are executed at LVL2). The minimal LVL2 processing time includes the initialization steps 1) and 2) (sending the

LVL1 data to LVL2, and assigning a LVL2 processor), and the global decision steps 8) and 9). We assume that the final decisions are grouped together in the LVL2 Supervisor and broadcast to the ROBs once per millisec; this adds an average of 500  $\mu$ s to the overall latency, but adds less than 10% to the ROB, RSI, and ATM occupancies. Only the 500  $\mu$ s latency due to the broadcast of the final decisions has been added into the minimal LVL2 processing numbers listed below.

| Buffer occupation          | O ROI DATA)<br>RATE * [ 1 156 μs ]                  |          |

|----------------------------|-----------------------------------------------------|----------|

| ROB occupation             | $\begin{bmatrix} 1 & 150 & \mu s \end{bmatrix} = 0$ |          |

| RSI PCI occupation         | 0                                                   |          |

| RSI occupation             | 0                                                   |          |

| ATM1 occupation            | RATE * $[6 \mu s]$                                  |          |

| ATM2 occupation            | RATE * $[6 \mu s]$                                  |          |

| SFI occupation             | RATE * [ 120 µs ]                                   |          |

| SFI PCI occupation         | RATE * $[4 \mu s]$                                  |          |

| LVL2 processor occupation  | RATE * [ 210 µs ]                                   |          |

| MUON algorithms            |                                                     |          |

| Buffer occupation          | REQ * $[648 \mu s] + RoI * [2]$                     | 257 µs ] |

| ROB occupation             | RoI * [                                             | 160 µs ] |

| <b>RSI PCI occupation</b>  | RoI * [                                             | 16 µs ]  |

| RSI occupation             | RoI * [                                             | 140 µs ] |

| ATM1 occupation            | RoI * [                                             | 67 µs ]  |

| ATM2 occupation            | RoI * [                                             | 6 µs ]   |

| SFI occupation             | REQ * $[70 \mu s] + RoI * [$                        | 70 µs ]  |

| SFI PCI occupation         | REQ * $[2 \mu s] + RoI * [$                         | 14 µs ]  |

| LVL2 processor occupation  | REQ * $[160 \mu s] + RoI * [$                       | 100 µs ] |

| $e/\gamma/\tau$ algorithms |                                                     |          |

| Buffer occupation          | REQ * $[759 \mu s] + RoI * [$                       | 514 µs ] |

| ROB occupation             | RoI * [ _ ]                                         | 390 µs ] |

| <b>RSI PCI occupation</b>  | RoI * [                                             | 48 µs ]  |

| RSI occupation             | RoI * [                                             | 360 µs ] |

| ATM1 occupation            | RoI * [                                             | 200 µs ] |

| ATM2 occupation            | RoI * [                                             | 12 µs ]  |

| SFI occupation             | REQ * [ 70 µs ] + RoI * [                           | 160 µs ] |

| SFI PCI occupation         | REQ * [ $2 \mu s$ ] + RoI * [                       | •        |

| LVL2 processor occupation  |                                                     | •        |

# GLOBAL RESOURCES FOR LVL2 PROCESSING AT L= $10^{33}$

JET algorithms

| Buffer occupation          | REQ * [ | $790 \mu s$ ] + R | RoI * [ 682 μs ]      |

|----------------------------|---------|-------------------|-----------------------|

| ROB occupation             |         | •                 | CoI * [ 1 170 μs ]    |

| RSI PCI occupation         |         | R                 | RoI*[ 60 μs]          |

| RSI occupation             |         |                   | RoI*[ 900 μs]         |

| ATM1 occupation            |         |                   | $RoI * [ 200 \mu s ]$ |

| ATM2 occupation            |         |                   | $xoI * [ 30 \mu s ]$  |

| SFI occupation             | REQ * [ |                   | $xoI * [ 310 \mu s ]$ |

| SFI PCI occupation         | REQ * [ | •                 | $koI * [ 42 \mu s ]$  |

| LVL2 processor occupation  |         | $160 \mu s$ ] + R | •                     |

| SCT algorithms             |         |                   |                       |

| Buffer occupation          | REO * [ | $782 \mu s$ ] + R | CoI * [ 875 μs ]      |

| ROB occupation             |         | •                 | koI*[ 520 μs]         |

| RSI PCI occupation         |         |                   | RoI*[ 6μs]            |

| RSI occupation             |         |                   | RoI*[ 184 μs]         |

| ATM1 occupation            |         |                   | $RoI*[13 \mu s]$      |

| ATM2 occupation            |         |                   | CoI*[ 6μs]            |

| SFI occupation             | REQ * [ |                   | CoI*[ 54 μs]          |

| SFI PCI occupation         | -       | $2 \mu s$ ] + R   | •                     |

| LVL2 processor occupation  | -       | $160 \mu s$ ] + R | •                     |

| TRT algorithms             |         |                   |                       |

| Buffer occupation          | REQ * [ | $840 \mu s$ ] + R | CoI * [ 722 μs ]      |

| ROB occupation             |         | R                 | coI * [ 780 μs ]      |

| RSI PCI occupation         |         | R                 | RoI*[ 7 μs]           |

| RSI occupation             |         | R                 | RoI * [ 302 µs ]      |

| ATM1 occupation            |         | R                 | CoI*[ 7 μs]           |

| ATM2 occupation            |         | R                 | loI * [ 12 μs ]       |

| SFI occupation             | REQ * [ | 70 µs ] + R       | loI * [ 102 μs ]      |

| SFI PCI occupation         | REQ * [ | 2 µs ] + R        | loI * [ 1 μs ]        |

| LVL2 processor occupation  | REQ * [ | 160 µs ] + R      | toI * [ 600 μs ]      |

| TRK (TRT + SCT) algorithms |         |                   |                       |

| Buffer occupation          | REQ * [ | $841 \mu s$ ] + R | loI * [ 1 598 μs ]    |

| ROB occupation             |         | R                 | loI * [ 1 300 μs ]    |

| <b>RSI PCI occupation</b>  |         | R                 | RoI * [ 14 µs ]       |

| RSI occupation             |         | R                 | RoI * [ 486 µs ]      |

| ATM1 occupation            |         |                   | $toI * [ 20 \mu s ]$  |

| ATM2 occupation            |         |                   | $toI * [ 18 \mu s ]$  |

| SFI occupation             | REQ * [ |                   | loI * [ 156 μs ]      |

| SFI PCI occupation         | REQ * [ | $2 \mu s$ ] + R   | toI * [ 4 μs ]        |

| •                          |         | 19                |                       |

LVL2 processor occupation REQ \* [  $160 \,\mu s$  ] + RoI \* [  $1400 \,\mu s$  ]

Missing- $E_T$  recalculation at LVL2

| 8 -1                  |                  |           |             |            |             |

|-----------------------|------------------|-----------|-------------|------------|-------------|

| Buffer occu           | pation           | REQ * [   | 6 120 µs ]  |            |             |

| ROB occup             | ation            | REQ * [ 4 | 3 520 µs ]  |            |             |

| RSI PCI oc            | cupation         | REQ * [   | 741 µs ]    |            |             |

| RSI occupa            | tion             | REQ * [ 1 | 9 520 µs ]  |            |             |

| ATM1 occu             | pation           | REQ * [   | 1 067 µs ]  |            |             |

| ATM2 occu             | pation           | REQ * [   | 384 µs ]    |            |             |

| SFI occupat           | tion             | REQ * [   | 3 590 µs ]  |            |             |

| SFI PCI occ           | cupation         | REQ * [   | 231 µs ]    |            |             |

| LVL2 proce            | essor occupation | REQ * [   | 260 µs ]    |            |             |

| Full TRT scan         |                  |           |             |            |             |

| Buffer occu           | pation           | REQ * [ 5 | 56 110 μs ] |            |             |

| ROB occup             | ation            | REQ * [ 6 | 66 560 μs ] |            |             |

| RSI PCI oc            | cupation         | REQ * [   | 741 µs ]    |            |             |

| RSI occupa            | tion             | REQ * [ 1 | 9 520 µs ]  |            |             |

| ATM1 occu             | pation           | REQ * [   | 1 067 µs ]  |            |             |

| ATM2 occu             | pation           | REQ * [   | 384 µs ]    |            |             |

| SFI occupat           | ion              | REQ * [   | 3 590 µs ]  |            |             |

| SFI PCI occ           | cupation         | REQ * [   | 231 µs ]    |            |             |

| LVL2 proce            | ssor occupation  | REQ * [ 5 | 50 160 µs ] |            |             |

| b-jet tag calculation | at LVL2          |           |             |            |             |

| Buffer occu           | pation           | REQ * [ 1 | 534 µs ] +  | RoI * [ 2: | 50 470 µs ] |

| ROB occup             | ation            |           |             | RoI * [    | 6880 µs ]   |

| RSI PCI oc            | cupation         |           |             | RoI * [    | 58 µs ]     |

| RSI occupa            | tion             |           |             | RoI * [    | 720 µs ]    |

| ATM1 occu             | pation           |           |             | RoI * [    | 200 µs ]    |

| ATM2 occu             | pation           |           |             | RoI * [    | 18 µs ]     |

| SFI occupat           | ion              | REQ * [   | 70 µs ] +   | RoI * [    | 210 µs ]    |

| SFI PCI occ           | cupation         | REQ * [   | 2 µs ] +    | RoI * [    | 42 µs ]     |

| LVL2 proce            | ssor occupation  | REQ * [   | 160 µs ] +  | RoI * [ 2: | 50 000 µs ] |

|                       |                  |           |             |            |             |

The total LVL3 occupations are obtained in a similar way, by adding the "minimal" LVL3 occupations to the contributions from any special processing assigned to LVL3. In the standard option, the missing- $E_T$  and the b-jet tag calculations are performed at LVL3. The missing  $E_T$  calculation can be absorbed in the "minimal" LVL3 occupations, since the missing- $E_T$  algorithm is much faster than the minimal LVL3 processing assumed here. The b-jet tag, on the other hand, is slow, and must be taken into account explicitly.

The minimal LVL3 occupations are much higher than the minimal LVL2 occupations because we assume that all of the data are transfered to the LVL3 processors. We assume there is no preprocessing in the ROBs, and that the minimum processing time in the LVL3 ROBs is 100 ms. Finally, we assume that the LVL3 code is less optimal than the LVL2 code, so that algorithm execution times are longer by a factor two. The latencies and occupations (per event) for the minimal LVL3 processing and for the b-jet tag calculation are given below:

| Minimal LVL3 processing per event |            |                      |

|-----------------------------------|------------|----------------------|

| Latency                           | 214 779 μs |                      |

| ROB occupation                    | 7 680 µs   |                      |

| <b>RSI PCI occupation</b>         | 14 786 µs  |                      |

| RSI occupation                    | 61 020 µs  |                      |

| ATM1 occupation                   | 69 000 µs  |                      |

| ATM2 occupation                   | 6 µs       |                      |

| SFI occupation                    | 30 370 µs  |                      |

| SFI PCI occupation                | 14 788 µs  |                      |

| LVL3 processor occupation         | 100 060 µs |                      |

| b-jet tag calculation at LVL3     |            |                      |

| Latency                           |            | RoI * [ 500 000 µs ] |

| LVL3 processor occupation         |            | RoI * [ 500 000 µs ] |

# GLOBAL LATENCY AND GLOBAL RESOURCES FOR LVL3 PROCESSING AT $L=10^{33}$

# 5. Sequential Processing

The model for sequential processing is a single LVL2 processing farm performing the full event selection, reducing the event rate from the initial 100 kHz LVL1 rate to the final 100 Hz LVL3 output rate. The supervisor assigns each event to a single LVL2 processor, which requests data from the ROBs as required for the event processing. Events can be rejected by the LVL2 processor at any time, if it is decided that the event does not satisfy the trigger selection criteria.

The processing sequence consists in the following steps:

- 1) confirm the LVL1 trigger using calorimeter and muon data from the trigger RoIs

- 2) verify muon, electron, and hadron triggers by matching the features in the calorimeter and muon systems to track parameters measured in the inner detector

- 3) perform the full TRT scan for events with a confirmed muon trigger

- 4) verify trigger muon isolation criteria in the calorimeter data

- 5) analyze non-trigger RoIs flagged by the LVL1.5 trigger menu [2]

- 6) recalculate the missing- $E_T$  if required by the trigger menu

- 7) look for b-jet tags if required by the trigger menu

- 8) verify the global selection criteria by combining features from all RoIs satisfying the above selection criteria.

Events can be rejected at each step in the processing sequence.

#### 5.1 Notation

The notation used for the trigger conditions is shown in the following table:

| Symbol      | Subsystem         | Description                                         |  |  |

|-------------|-------------------|-----------------------------------------------------|--|--|

| mu          | MUON              | stand-alone muon algorithm                          |  |  |

| trk<br>calo | TRT + SCT<br>CALO | track algorithm for RoI<br>muon isolation algorithm |  |  |

| scan        | TRT               | full TRT scan                                       |  |  |

| em          | CALO              | $e / \gamma / \tau$ algorithms                      |  |  |

| tau         | CALO              | $\tau$ / hadron algorithms                          |  |  |

| jet         | CALO              | jet algorithm                                       |  |  |

| b-jet       | CALO + SCT        | jet + b-jet tag algorithm                           |  |  |

| me          | CALO              | missing- $E_T$ calculation                          |  |  |

#### TRIGGER ALGORITHMS

#### 5.2 Model for Sequential Processing

Trigger menus for low luminosity have been published in a preceding ATLAS note [1]. This trigger menu has been used to construct a model for the sequential processing described above. Rejection rates for each trigger algorithm have been estimated as best we can; a few details are given in ref.[1]. Each line in the table below corresponds to a different sequence of trigger algorithms (involving various threshold and isolation criteria), some of which may be performed in the LVL3 processor farm.

The notation has been described in the previous section. Two columns of event rates are given: the first column is the rate for all events passing that set of algorithms, and the last column is the exclusive rate for that algorithm. The sum of the event rates in the last column should add up to the full LVL1 trigger rate.

| Trigger algorithm sets                                                                                                      | Inclusive rate | Exclusive rate |

|-----------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| 1 mu                                                                                                                        | 8 000 Hz       | 601 Hz         |

| 1  mu + 1  trk                                                                                                              | 6 000 Hz       | 1 873 Hz       |

| 1  mu + 1  trk + 1  calo + scan                                                                                             | 4 000 Hz       | 3 419 Hz       |

| 1  mu + 1  trk + scan + me                                                                                                  | 25 Hz          | 25 Hz          |

| 1  mu + 1  trk + 6  jet + scan                                                                                              | 38 Hz          | 32 Hz          |

| 1  mu + 1  trk + 5  jet + scan                                                                                              | 50 Hz          | 5 Hz           |

| 1  mu + 1  trk + 4  jet + scan                                                                                              | 75 Hz          | 13 Hz          |

| 1  mu + 1  trk + 3  jet + scan                                                                                              | 100 Hz         | 0 Hz           |

| 1  mu + 1  trk + 6  b-jet + scan                                                                                            | 6 Hz           | 6 Hz           |

| 1  mu + 1  trk + 5  b-jet + scan                                                                                            | 13 Hz          | 7 Hz           |

| 1  mu + 1  trk + 4  b-jet + scan                                                                                            | 25 Hz          | 12 Hz          |

| 1  mu + 1  trk + 3  b-jet + scan                                                                                            | 50 Hz          | 25 Hz          |

| 1  mu + 1  trk + 3  colo + 6  jet + scan                                                                                    | 75 Hz          | 62 Hz          |

| 1  mu + 1  trk + 1  calo + 5  jet + scan<br>1  mu + 1  trk + 1  calo + 5  jet + scan                                        | 100 Hz         | 13 Hz          |

|                                                                                                                             | 150 Hz         | 25 Hz          |

| 1  mu + 1  trk + 1  calo + 4  jet + scan                                                                                    |                | 0 Hz           |

| 1  mu + 1  trk + 1  calo + 3  jet +  scan                                                                                   | 200 Hz         |                |

| 1  mu + 1  trk + 1  calo + 2  jet + scan                                                                                    | 302 Hz         | 2 Hz           |

| 1  mu + 1  trk + 1  calo + 1  jet + scan                                                                                    | 20 Hz          | 5 Hz           |

| 1  mu + 1  trk + 1  calo + 6  b-jet + scan                                                                                  | 13 Hz          | 13 Hz          |

| 1  mu + 1  trk + 1  calo + 5  b-jet + scan                                                                                  | 25 Hz          | 12 Hz          |

| 1  mu + 1  trk + 1  calo + 4  b-jet + scan                                                                                  | 50 Hz          | 25 Hz          |

| 1  mu + 1  trk + 1  calo + 3  b-jet + scan                                                                                  | 100 Hz         | 50 Hz          |

| 1  mu + 1  trk + 1  calo + 2  b-jet + scan                                                                                  | 200 Hz         | 100 Hz         |

| 1  mu + 1  trk + 1  calo + 1  b-jet + scan                                                                                  | 15 Hz          | 15 Hz          |

| 1  mu + 1  trk + 1  calo + scan + me                                                                                        | 20 Hz          | 20 Hz          |

| 2 mu                                                                                                                        | 400 Hz         | 155 Hz         |

| 2  mu + 2  trk                                                                                                              | 200 Hz         | 90 Hz          |

| 2  mu + 2  trk + 2  calo + scan                                                                                             | 100 Hz         | 95 Hz          |

| 3 mu                                                                                                                        | 20 Hz          | 13 Hz          |

| 3  mu + 3  trk                                                                                                              | 7 Hz           | 4.5 Hz         |

| 3  mu + 3  trk + 3  calo + scan                                                                                             | 2.5 Hz         | 2.5 Hz         |

| 1 mu + 1 em                                                                                                                 | 800 Hz         | 770 Hz         |

| 1  mu + 1  em<br>1  mu + 1  em + 2  trk                                                                                     | 30 Hz          | 20 Hz          |

| 1  mu + 1  em + 2  trk<br>1  mu + 1  em + 2  trk + 1  calo + scan                                                           | 10 Hz          | 10 Hz          |

| $1 \operatorname{Ind} + 1 \operatorname{em} + 2 \operatorname{tr} \mathbf{k} + 1 \operatorname{calo} + \operatorname{scal}$ | 10 HZ          | 10 HZ          |

| 2  mu + 1  em                                                                                                               | 40 Hz          | 32 Hz          |

| 2  mu + 1  em + 3  trk                                                                                                      | 8 Hz           | 6 Hz           |