PREPARED FOR SUBMISSION TO JINST

TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS 30 September - 4 October 2024 Glasgow, Scotland

# Development of the ATLAS Liquid Argon Calorimeter Off-detector Readout Electronics for the HL-LHC

#### Markus Helbig on behalf of the ATLAS Liquid Argon Calorimeter Group

Technische Universität Dresden, Dresden, Germany

*E-mail:* markus.helbig@tu-dresden.de

ABSTRACT: The High-Luminosity LHC will start operations for physics in 2030. The expansion of the dataset will be achieved by increasing the instantaneous luminosity of the LHC to 5-7.5 times its design value. For the ATLAS Liquid Argon calorimeter system, this poses new technical and operational challenges due to the higher radiation doses for the front-end electronics and increased pile-up caused by coincident and consecutive collisions. Additionally, the trigger rate of the first-level hardware trigger is projected to be increased to close to ten times its current value. At the same time, two new trigger subsystems must be provided with reconstructed energy data up to cell-level granularity in real time.

To keep up with these conditions and requirements while not sacrificing data quality, the Liquid Argon calorimeter readout needs to undergo a fundamental upgrade. The new off-detector electronics will be realized on custom ATCA-compliant boards based on FPGAs. A total of 278 new signal processing boards will receive the digitized data from 182 468 calorimeter cells at 40 MHz. They provide enough resources to facilitate the use of new online energy reconstruction algorithms and transmit the results to trigger and DAQ systems. A new timing system consisting of 30 additional ATCA blades will complement the new on-detector electronics by providing timing, monitoring and control functionality.

This article gives a summary on the planned off-detector electronics upgrades and the recent progress in firmware and hardware development.

KEYWORDS: Calorimeters, Electronic detector readout concepts (gas, liquid)

© Copyright 2024 CERN for the benefit of the ATLAS Collaboration. Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license.

## 1 Introduction

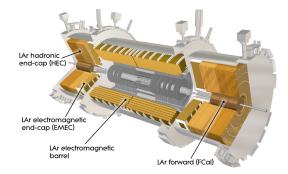

As part of the ATLAS experiment [1], the Liquid Argon Calorimeters [2] are a system of sampling calorimeters encompassing a total of 182 468 cells in multiple layers. The calorimeters — divided into the electromagnetic barrel (EMB), electromagnetic endcaps (EMEC), the forward calorimeters (FCal) and hadronic endcaps (HEC) as shown in Figure 1 — use Liquid Argon (LAr) as active medium and lead, copper or tungsten as absorber material. Within the calorimeters, the incoming particles give rise to electromagnetic showers which deposit their energy inside the cells and leave an ionization trace in the liquid argon. This allows for the measurement of the position, energy and timing of the incoming photons, electrons,  $\tau$  leptons and hadronic jets.

In the setup of the current run, the readout of the LAr calorimeters consists of two distinct readout paths. On the digital trigger path, energy values are sent to the trigger systems every bunch crossing (25 ns) at a reduced granularity of 34k supercells. This part of the detector readout electronics has been upgraded recently and was commissioned during the most recent long shutdown [3]. The data readout path is activated upon a trigger accept signal. Typically four digitized samples of the signal pulse are transmitted from the on-detector to the off-detector electronics at full granularity for energy and timing reconstruction on DSPs using an Optimal Filter approach [4], allowing for a sustained trigger rate of 110 kHz.

Figure 1. Overall structure of the ATLAS Liquid Argon Calorimeter system [5]

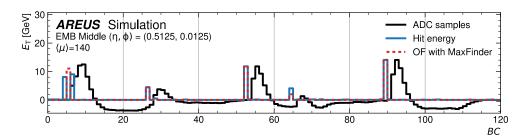

With the High-Luminosity LHC (HL-LHC), which is expected to start operation in 2030, the luminosity of the LHC will increase to up to 5-7.5 times its nominal value of  $1 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. The mean number of proton-proton interactions per bunch crossing will thus reach values of  $\langle \mu \rangle \sim 140 - 200$ . At the same time, the LAr calorimeters will likewise undergo an upgrade of the on-detector and off-detector electronics [6]. Beside the inherent need to replace the on-detector components due to the increased radiation levels in the detector area, a complementing upgrade of the off-detector components will allow for a better handling of the increased pile-up. The use of more sophisticated algorithms for energy reconstruction aims to maintain or improve the current energy reconstruction performance (Figure 2). The upgraded hardware should support a first-level trigger rate of 1 MHz and enables trigger decisions based on data at cell-level granularity.

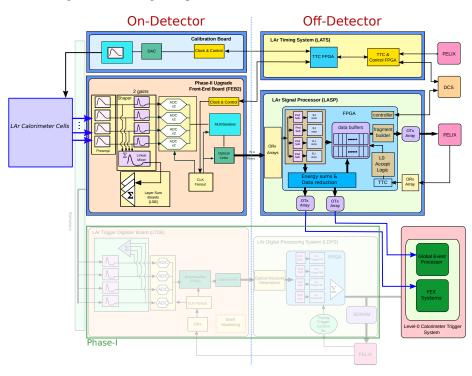

In the following section, the current status, recent achievements and future plans for the new components of the LAr Phase-II upgrade (Figure 3) — in particular the new Liquid Argon Signal Processor (LASP) and its complementing Smart Rear Transition Module (SRTM), as well as the new Liquid Argon Timing System (LATS) — are presented in more detail.

**Figure 2**. Performance of the currently used Optimal Filtering approach for energy reconstruction under HL-LHC conditions. For energy depositions in short succession, hit energies can be underestimated or attributed to the wrong bunch crossing. Adapted from [7]

**Figure 3**. Plan of the LAr calorimeter on-detector and off-detector electronics for the HL-LHC. The systems shown on the upper half of the figure are going to be installed during the next long shutdown, while the shaded once are already operational. Adapted from [6]

# 2 Liquid Argon Signal Processor

The purpose of the Liquid Argon Signal Processor (LASP) is the calculation of energy and timing values as well as quality indicators for each energy deposition. The energy values are transmitted to two new parts of the ATLAS trigger system: the forward Feature EXtractor (fFEX) and the Global Event Processor (GEP). While waiting for a trigger decision, the data are buffered within the LASP and further transmitted to the data acquisition (DAQ) systems upon a trigger accept.

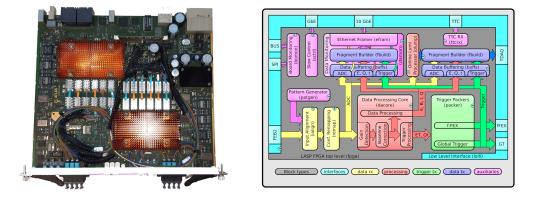

**Hardware.** The LASP system comprises a total of 278 Advanced Telecommunications Computing Architecture (ATCA) blades equipped with two Intel<sup>®</sup> Agilex<sup>TM</sup> 7 FPGAs each. One LASP blade receives data from up to 6 front-end boards, corresponding to up to 768 calorimeter cells, via Samtec

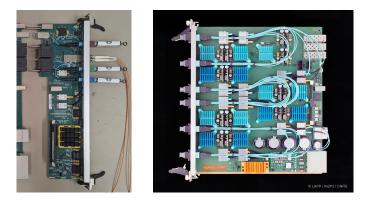

Firefly<sup>™</sup> modules. The 66 unidirectional optical links have a data rate of 10 Gbps each. For the links to the fFEX and GEP trigger systems, with a data rate of 25 Gbps per link, Firefly<sup>™</sup> modules are used as well. For the data path to the DAQ systems, three pairs of copper traces per FPGA towards an ATCA rear transition module with link speeds of 10 Gbps are provided. Additional Ethernet connections allow for configuration, control and monitoring. Multiple testboards (Figure 4) with Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGAs have been manufactured and tested. Currently, the design of the next version of boards is being finalized and production is expected for the beginning of 2025. Besides moving from the Stratix<sup>®</sup> 10 to an Agilex<sup>™</sup> 7 FPGA with more resources and higher achievable operating frequency for data processing, an improved clock distribution and JTAG scheme has been introduced. The preparation of a hardware testbench for verifying the power supply and for low-level tests of the high-speed interfaces of the blades is ongoing.

**Figure 4.** Left: LASP testboard. The ATCA blade prominently hosts two Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGAs and several Samtec FireFly<sup>TM</sup> modules for data reception from the new frond-end boards and for transmission to the hardware trigger systems. On the final boards, Intel<sup>®</sup> Agilex<sup>TM</sup> 7 FPGAs will be installed. Right: Schematic overview of the LASP firmware. The LASP provides output to the DAQ system as well as the trigger systems fFEX and GEP.

**Firmware.** On the FPGAs, multiple tasks are accomplished (Figure 4). First, the incoming data from the new front-end boards are received and decoded. They consist of 16-bit ADC values at two gains for each calorimeter cell, which are sent at every bunch crossing. The payload also includes an embedded bunch crossing identifier and comes encoded with the lpGBT protocol developed at CERN [8]. The data are then aligned in time to account for different delays on the individual fibers. Subsequently, the energy and timing values are calculated in the main processing stage which also includes the correction of a bunch crossing-dependent baseline and the selection of the optimal gain. Currently, different novel energy reconstruction reconstruction techniques based on Machine Learning are under investigation to replace the Optimal Filter [4] approach of the current readout. Under tight latency constraints of 150 ns, these methods show promising results in mitigating the increased pile-up noise under HL-LHC conditions [9, 10]. For transmission to the GEP a selection of the most energetic cells is performed while the cell-level granularity is kept. Furthermore, the energies of cells in the forward regions are prepared for transmission to the fFEX by a summation step. Eventually, the trigger data are formatted, encoded with the core1990/Interlaken protocol [11] and sent to the respective trigger systems. In order to compensate for the trigger latency of 10 µs,

the raw ADC values, the computed energy and timing values and the trigger data are buffered. Upon a trigger accept, they are finally sent to the DAQ systems. Control and monitoring of the boards is implemented via a memory-mapped interface based on the IPbus protocol [12].

# 3 Smart Rear Transition Module for LASP

For the main purpose of extending the IO capabilities of the LASP, the presented ATCA blades come with 278 complementing ATCA rear transition modules (SRTM) based on Xilinx<sup>®</sup> Zynq<sup>TM</sup> UltraScale+<sup>TM</sup> MPSoCs. The SRTM is responsible for receiving the TTC (timing, trigger and control) signal from the FELIX system and forward it to both LASP FPGAs. Similarly, the three data streams on the DAQ path coming from each LASP FPGA are merged into a single Interlaken/core1990 stream. For the reception and transmission of the aforementioned data, FireFly<sup>TM</sup> modules are used. The processor within the Zynq<sup>TM</sup> will run an OPC Unified Architecture (OPC UA) server to provide detailed board monitoring to the detector control system.

At the beginning of this year, the most recent version of the SRTM board (Figure 5) was successfully tested. On the firmware side, efforts currently concentrate on the integration and testing of the Local Trigger Interface (LTI) protocol and the DAQ stream merging.

# 4 Liquid Argon Timing System

The Liquid Argon Timing System (LATS) is responsible for the distribution of the TTC clock to the new front-end electronics boards. Additionally, it provides the 1524 new front-end boards with a bunch-counter reset (BCR) signal and delivers the calibration pulses to the 122 calibration boards. The LATS also acts as a bridge for the configuration and monitoring of the aforementioned boards.

The hardware of the LATS consists of 30 boards in ATCA format, called LATOURNETT, to be installed in shared racks with the LASP boards. Each board features 13 Intel<sup>®</sup> Cyclone<sup>®</sup> 10 GX FPGAs among which one *central* FPGA is connected to the upstream systems, and 12 *matrix* FPGAs provide connections to the on-detector boards. On the LATS-side, these links are based on Samtec FireFly<sup>™</sup> modules. Two testboards have been produced and tested successfully (Figure 5). In the next iteration, the board will be supplemented with an additional passive ATCA RTM and an improved clock distribution and JTAG scheme. Having passed the preliminary design review, a production of four updated boards is planned for 2025.

A functional firmware is available for the LATOURNETT testboards, as well as for the Cyclone<sup>®</sup> 10 GX devkit for small-scale integration testing in the lab. For configuring and monitoring the on-detector boards, the capabilities of the lpGBT's internal/external control channels are harvested. The integration of the LTI protocol into the firmware is ongoing.

## **5** Integration

Recently, the first successful readout of a fully populated new front-end board via the LASP has been demonstrated. Besides, for the core1990/Interlaken link from the LASP towards the fFEX a test setup based on an Intel<sup>®</sup> Agilex<sup>™</sup> 7 devkit and a Xilinx<sup>®</sup> Virtex<sup>™</sup> UltraScale+<sup>™</sup> devkit has been set up. Furthermore, on the software side, an OPC UA server is being developed to facilitate

**Figure 5**. Left: SRTM v2.0 prototype. It connects to the LASP via the ATCA Zone 3 connectors. Right: Testboard for the LATS, called LATOURNETTv1. As the design is mainly limited by the number of high-speed transceivers, but not by FPGA resources, a solution with multiple low-range FPGAs was adopted. The next version of this board will be complemented by a passive ATCA RTM to ease routing and maintainability of the rear SFP+ and GbE connections.

controlling and monitoring of the LATS and through this the new front-end electronics. Similarly, the development of configuration, monitoring and debugging tools for the LASP is progressing.

The next integration milestone will be a test setup based on half of a Liquid Argon *front-end crate* — comprising a total of 14 new front-end boards, or 3584 ADC channels — attached to a Liquid Argon calorimeter mockup. The raw data will be aligned and buffered on the LASP board. Upon an accept signal, several hundred consecutive samples should be sent to an attached FELIX [13] machine. This test will be crucial to demonstrate that the entirety of analog and digital front-end board electronics, the clock distribution, configuration processes, the LASP boards and essential LASP firmware components work successfully. Equally, it helps to measure important properties of the analog side such as coherent noise, crosstalk, gain, and linearity.

# 6 Conclusion

The on-detector and off-detector electronics of the ATLAS Liquid Argon calorimeter system need to be upgraded before the start of the HL-LHC in 2030 to cope with the higher radiation doses, increased pile-up and to support a higher first-level trigger rate. In particular, the second phase of the off-detector electronics upgrade will provide the capacity for better real-time reconstruction algorithms and a more fine-granular readout on the trigger path. It also adds timing, monitoring and control for the new on-detector electronics boards. Testboards for all systems have been produced and evaluated, with new prototype boards being in the making. Recently, a first successful readout of a fully populated new front-end board prototype was demonstrated. Currently, the hardware and firmware is scaled up aiming at a readout of half of a front-end crate with 14 new front-end boards using the new off-detector electronics. Overall, the project is on track for the HL-LHC.

## Acknowledgments

This work was in part supported by the German Federal Ministry of Education and Research within the projects 05H19ODCA9 and 05H24OD9.

#### References

- The ATLAS Collaboration, *The ATLAS Experiment at the CERN Large Hadron Collider*, JINST 3 (2008) S08003 [doi: 10.1088/1748-0221/3/08/S08003]

- The ATLAS Collaboration, ATLAS liquid-argon calorimeter: Technical Design Report, ATLAS-TDR-2 [http://cds.cern.ch/record/331061]

- [3] G. Aad et al., The Phase-I trigger readout electronics upgrade of the ATLAS Liquid Argon calorimeters, JINST 17 (2022) P05024 [doi: 10.1088/1748-0221/17/05/P05024]

- [4] W.E. Cleland and E.G. Stern, Signal processing considerations for liquid ionization calorimeters in a high rate environment, Nucl. Instrum. Methods Phys. Res. A 338 (1994) 467

[doi: 10.1016/0168-9002(94)91332-3]

- [5] Joao Pequenao, Computer generated image of the ATLAS Liquid Argon, [https://cds.cern.ch/record/1095928]

- [6] The ATLAS Collaboration, ATLAS Liquid Argon Calorimeter Phase-II Upgrade: Technical Design Report, ATLAS-TDR-027 [cds.cern.ch/record/2285582]

- [7] ATLAS LAr Calorimeter Group, *Public Liquid-Argon Calorimeter Plots on Upgrade*, https://twiki.cern.ch/twiki/bin/view/AtlasPublic/LArCaloPublicResultsUpgrade

- [8] J.M. Mendez et al., New LpGBT-FPGA IP: Simulation model and first implementation, in Proceedings of TWEPP2018, 2019 [doi: 10.22323/1.343.0059]

- [9] G. Aad et al., Artificial Neural Networks on FPGAs for Real-Time Energy Reconstruction of the ATLAS LAR Calorimeters, Comput Softw Big Sci 5 19 (2021) [doi: 10.1007/s41781-021-00066-y]

- [10] G. Aad et al., Firmware implementation of a recurrent neural network for the computation of the energy deposited in the liquid argon calorimeter of the ATLAS experiment, JINST 18 (2023) P05017 [doi: 10.1088/1748-0221/18/05/P05017]

- [11] ATLAS TDAQ Collaboration, *Core1990: Interlaken protocol* (*Git repository*), https://gitlab.cern.ch/atlas-tdaq-felix/core1990\_interlaken

- [12] C. Ghabrous Larrea et al., *IPbus: a flexible Ethernet-based control system for xTCA hardware*, *JINST* 10 (2015) C02019 [doi: 10.1088/1748-0221/10/02/C02019]

- [13] W. Wu et al., FELIX: the New Detector Interface for the ATLAS Experiment, IEEE Trans. Nucl. Sci. 66 7 (2019) 986 [doi: 10.1109/TNS.2019.2913617]