Master's Thesis

## Optimierung der Frontend-Ausleseelektronik für den Belle II DEPFET Sensor

# Optimization of the front-end read-out electronics for the Belle II DEPFET Sensor

prepared by

### Philipp Wieduwilt

from Stade

at the II. Physikalisches Institut

Thesis number:

II.Physik-UniGö-MSc-2016/04

Thesis period: 1st February 2016 until 1st August 2016

First referee: Prof. Dr. Ariane Frey

Second referee:

CERN-THESIS-2016-437

PD Dr. Jörn Große-Knetter

### Zusammenfassung

Das Belle Experiment am KEKB $e^+e^-$ -Beschleuniger in Tsukuba, Japan lieferte insgesamt eine integrierte Luminosität von  $1 \text{ ab}^{-1}$ . Die gewonnenen Daten wurden für *B*-Physik Studien und für Suchen nach Physik jenseits des Standardmodels genutzt. Für noch detailliertere Studien und um noch höhere Sensitivität auf neue Physik zu erreichen, wird der KEKB Beschleuniger zu SuperKEKB ausgebaut. SuperKEKB wird dabei eine 40 mal höhere instantane Luminosität erreichen als sein Vorgänger. Ebenfalls wird der am KEK benutzte Belle Detektor verbessert zu Belle II. Neben der Optimierung der bei Belle benutzten Subdetektoren, wird Belle II zusätzlich mit zwei Lagen eines Silizium-Pixeldetektors nahe des Wechselwirkungspunktes ausgestattet sein. Dieser auf der DEPFET Technologie basierende Pixeldetektor kann sehr dünn gebaut werden und verringert dadurch unerwünschten Energieverlust und Vielfachstreuung der gemessenen Teilchen. Zur Auslese der DEPFET Pixelmatrizen werden zur Zeit drei dedizierte Frontend-Chips entwickelt. Die Funktionalität dieser Chips muss zurzeit untersucht und bestätigt werden, um einen erfolgreichen Einsatz des Belle II Pixeldetektors zu gewährleisten. In dieser Arbeit werden Testalgorithmen vorgestellt und diskutiert, die entwickelt wurden, um die Leistungsfähigkeit der Frontend-Ausleseelektronik zu untersuchen und zu optimieren. Die entwickelte Software wird benutzt, um Scans der Operationsparameter der Chips auszuwerten und Schwächen der aktuellen Chip-Designs zu untersuchen, um so eine Rückmeldung an die Chip-Designer für zukünftige Designiterationen zu geben.

### Abstract

The Belle experiment at the KEKB  $e^+e^-$ -collider in Tsukuba, Japan yielded an integrated luminosity of  $1 \text{ ab}^{-1}$ . The collected data was used for in depth *B*-physics studies, as well as beyond standard model searches. For even more detailed physics studies and higher sensitivity to new physics contributions, the KEKB collider is being upgraded to SuperKEKB, which is expected to deliver a 40 times higher instantaneous luminosity. Also the Belle detector will be upgraded to Belle II. Besides the upgrade of the Belle-proven sub-detector components, Belle II will be equipped with additional two layers of a silicon pixel detector closest to the interaction point, which will improve vertex resolution. This pixel detector will be based on the DEPFET technology, which allows for very thin sensors to reduce energy loss and multiple scattering effects. For the read-out of the DEPFET pixel matrices, three dedicated front-end chips are being developed. Confirming and studying the functionality of the chip designs is crucial. In this thesis, testing algorithms will be presented and discussed, that were developed for investigating and optimizing the performance of the current designs of the front-end read-out electronics. The software is used to evaluate parameter scans, tune the chip parameters and investigate weaknesses of the existing chip designs, in order to provide feed-back to the chip designers for future design iterations.

**Keywords:** Belle II, silicon pixel detectors, DEPFET sensors, read-out electronics, analog-digital conversion, optimization of operation parameters

# Contents

| 1        | Introduction: The Belle II Detector at the SuperKEKB Collider |                                  |                                                                         |    |  |  |

|----------|---------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------|----|--|--|

| <b>2</b> | The DEPFET Pixel Detector for Belle II                        |                                  |                                                                         |    |  |  |

|          | 2.1                                                           | 2.1 Principles of DEPFET Sensors |                                                                         |    |  |  |

|          | 2.2 The Front-end Electronics for the Pixel Detector          |                                  |                                                                         |    |  |  |

|          |                                                               | 2.2.1                            | The SWITCHER                                                            | 7  |  |  |

|          |                                                               | 2.2.2                            | The Drain Current Digitizer (DCD)                                       | 8  |  |  |

|          |                                                               | 2.2.3                            | The Data Handling Processor (DHP)                                       | 11 |  |  |

| 3        | Analog-Digital Conversion                                     |                                  |                                                                         |    |  |  |

|          | 3.1                                                           | Chara                            | cteristics of Transfer Curves: Dynamic Range, Noise and Linearity $\ .$ | 13 |  |  |

|          | 3.2                                                           | Cyclic                           | Redundant Signed-Digit Analog-Digital Conversion Algorithm              | 16 |  |  |

| 4        | The Front-end Electronics in Detail                           |                                  |                                                                         |    |  |  |

|          | 4.1                                                           | Analo                            | g-Digital Conversion Implementation in the Drain Current Digitizer .    | 17 |  |  |

|          |                                                               | 4.1.1                            | Current Memory Cells and Comparators                                    | 19 |  |  |

|          |                                                               | 4.1.2                            | Parameters for Adjusting the Analog Performance                         | 20 |  |  |

|          | 4.2                                                           | Inter-                           | ASIC Communication                                                      | 22 |  |  |

|          |                                                               | 4.2.1                            | Data Links Communication: Signal Delay Compensation                     | 23 |  |  |

| <b>5</b> | Exp                                                           | oerime                           | ntal Setups for ASIC Testing                                            | 27 |  |  |

|          | 5.1                                                           | The H                            | lybrid5: A PCB-based ASIC Testing Interface                             | 27 |  |  |

|          | 5.2                                                           | Electr                           | ical Multi-Chip Modules                                                 | 28 |  |  |

|          | 5.3                                                           | Back-                            | end Read-out and Laboratory Setup                                       | 29 |  |  |

| 6        | Rea                                                           | d-out                            | ASICs Failure Identification                                            | 33 |  |  |

|          | 6.1                                                           | Drain                            | Current Digitizer: Analog Performance and Failure Identification        | 33 |  |  |

|          |                                                               | 6.1.1                            | Dynamic Range                                                           | 34 |  |  |

|          |                                                               | 6.1.2                            | Noise and Linearity                                                     | 34 |  |  |

|          |                                                               | 6.1.3                            | Comparator Offsets and Long Codes                                       | 36 |  |  |

| 9 | Sun                  | nmary                                                          | & Conclusion                                                           | 75 |  |  |

|---|----------------------|----------------------------------------------------------------|------------------------------------------------------------------------|----|--|--|

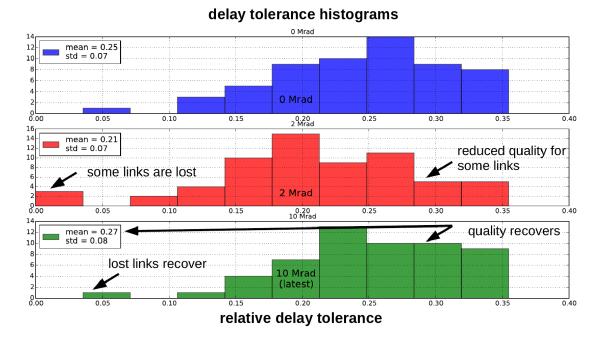

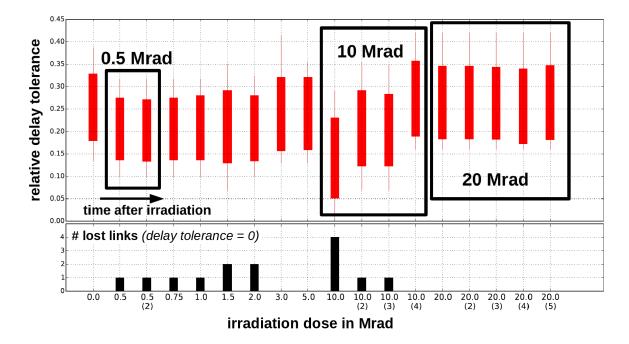

|   |                      | 8.3.2                                                          | Stability of the Inter-ASIC Communication                              | 70 |  |  |

|   |                      | 8.3.1                                                          | Stability of the Working Point                                         | 69 |  |  |

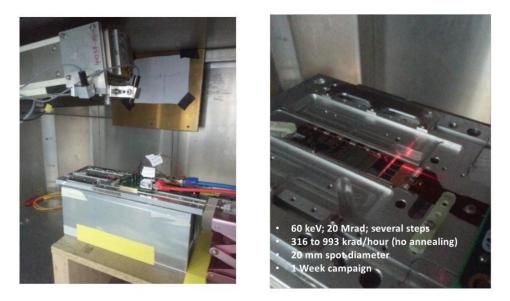

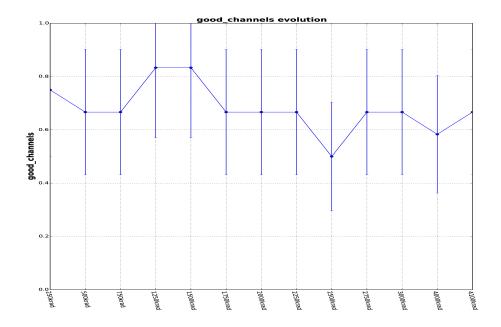

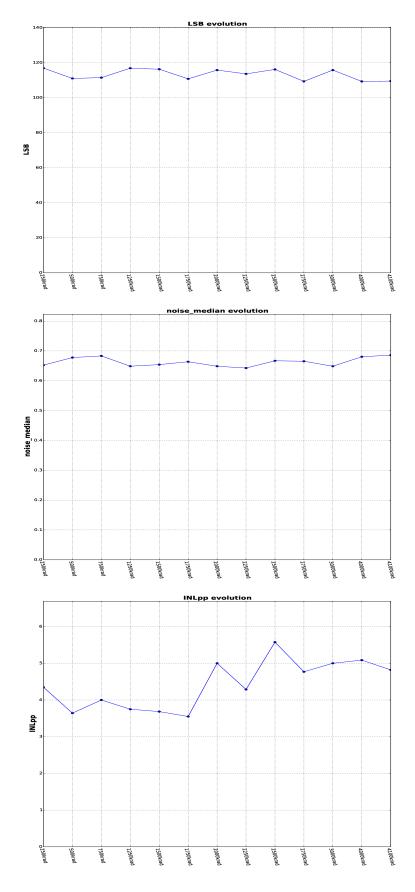

|   | 8.3                  | ASICs                                                          | Operation Stability and Irradiation Damage                             | 68 |  |  |

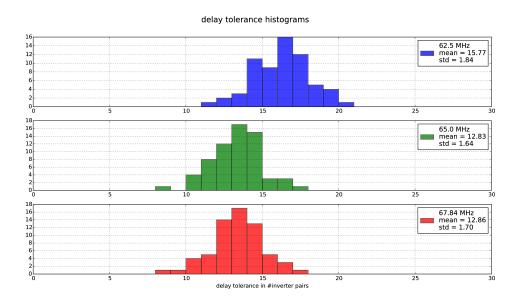

|   | 8.2                  | Inter-A                                                        | ASIC Communication Stability at High Clock Frequencies $\ldots \ldots$ | 67 |  |  |

|   | 8.1                  | Worki                                                          | ng Point Variations among Modules                                      | 63 |  |  |

| 8 | $\operatorname{Res}$ | ults fr                                                        | om Test System Measurements and Irradiation Campaigns                  | 63 |  |  |

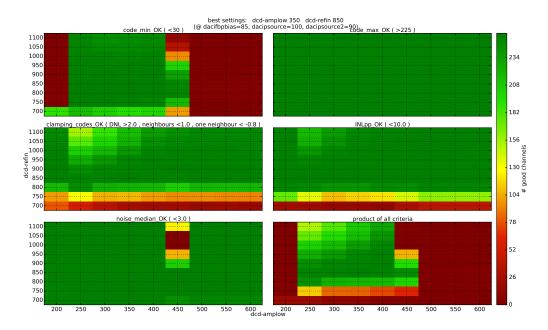

|   |                      | 7.2.2                                                          | Optimization of the Supply Voltages                                    | 60 |  |  |

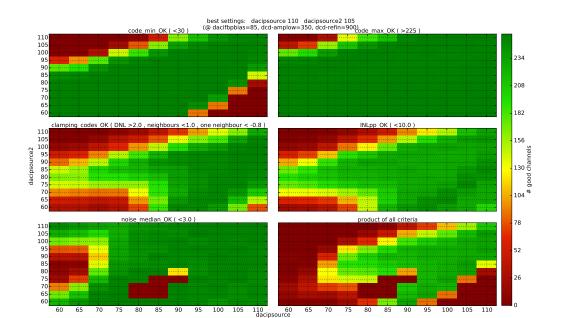

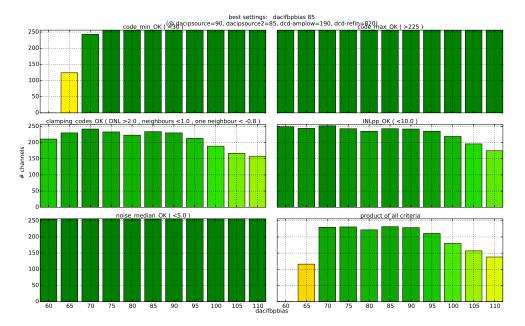

|   |                      | 7.2.1                                                          | Optimization of the DAC Currents                                       | 59 |  |  |

|   | 7.2                  | Optimization of the Drain Current Digitizer Analog Performance |                                                                        |    |  |  |

|   |                      | 7.1.2                                                          | Using Transfer Curves                                                  | 55 |  |  |

|   |                      | 7.1.1                                                          | Using the Digital Test Pattern                                         | 52 |  |  |

|   | 7.1                  | Optim                                                          | nization of the Inter-ASIC Communication                               | 51 |  |  |

| 7 | Rea                  | d-out                                                          | ASICs Optimization: Parameter Scans and Tuning                         | 51 |  |  |

|   |                      | 6.2.3                                                          | Indications of Cross-Talk among Communication Links                    | 48 |  |  |

|   |                      | 6.2.2                                                          | Digital Test Pattern                                                   |    |  |  |

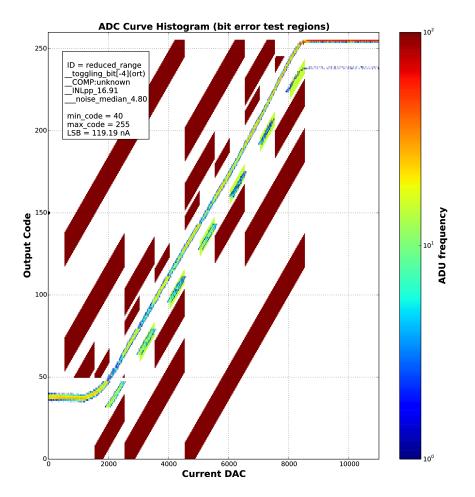

|   |                      | 6.2.1                                                          | Bit Error Recognition in Transfer Curves                               |    |  |  |

|   | 6.2                  | Inter-A                                                        | ASIC Communication Failures                                            | 41 |  |  |

# Nomenclature

## Abbreviations

| Abbreviation         | Meaning                                                           |

|----------------------|-------------------------------------------------------------------|

| A                    |                                                                   |

| ADC                  | analog-to-digital conversion or converter                         |

| ADU                  | arbitrary digital unit                                            |

| ASIC                 | application specific integrated circuit                           |

| $\mathbf{C}$         |                                                                   |

| CMC                  | current memory cell                                               |

| $\operatorname{CMP}$ | comparator                                                        |

| CRSD                 | cyclic redundant signed-digit analog-digital conversion algorithm |

| D                    |                                                                   |

| DAC                  | digital-to-analog converter (used as parameter/settings)          |

| DAQ                  | data acquisition                                                  |

| DCD                  | the Drain Current Digitizer                                       |

| DEPFET               | depleted $(p$ -channel) field effect transistor                   |

| DHH                  | the Data Handling Hybrid                                          |

| DHP                  | the Data Handling Processor                                       |

| DNL                  | differential non-linearity (of an ADC curve)                      |

| DUT                  | device under test                                                 |

| G                    |                                                                   |

| GCK                  | global reference clock                                            |

| Ι                    |                                                                   |

| INL                  | integrated non-linearity (of an ADC curve)                        |

| J                    |                                                                   |

| JTAG                 | joint test action group, IEEE standard 1149.1 for testing, debug- |

|                      | ging and controlling of integrated circuits                       |

| $\mathbf{L}$         |                                                                   |

| LSB                  | least significant bit $\equiv$ ADU                                |

|                      |                                                                   |

### Nomenclature

| Abbreviation | Meaning                                                          |

|--------------|------------------------------------------------------------------|

| М            |                                                                  |

| MSB          | most significant bit                                             |

| 0            |                                                                  |

| OWP          | optimal working point                                            |

| Р            |                                                                  |

| PCB          | printed circuit board                                            |

| PXD          | the Belle II DEPFET pixel detector                               |

| S            |                                                                  |

| SVD          | the Belle II silicon strip sensor as part of the vertex detector |

| SWITCHER     | front-end matrix steering chip for PXD                           |

| $\mathbf{T}$ |                                                                  |

| TC           | transconductor                                                   |

| TIA          | transimpedance amplifier                                         |

| $\mathbf{V}$ |                                                                  |

| VXD          | the Belle II vertex detector                                     |

# 1 Introduction: The Belle II Detector at the SuperKEKB Collider

The SuperKEKB collider at the KEK research complex in Tsukuba, Japan is an asymmetric  $e^+e^-$ -collider, it is the upgrade of the former KEKB collider. SuperKEKB is expected to deliver a 40 times higher instantaneous luminosity compared to its predecessor [1]. KEKB and SuperKEKB are so called *B*-Factories, the center-of-mass energy of the  $e^+e^-$ system is at 10.58 GeV, which is right at the  $\Upsilon(4s)$  resonance. Thus, mainly  $\Upsilon(4s)$  mesons are produced, which in turn, predominantly decay into pairs of B mesons (branching fraction of BB > 96 % [2]). Due to its short lifetime, the  $\Upsilon(4s)$  decays practically immediately at the interaction point. By employing an asymmetric collider, the B mesons are boosted along the beam-axis and, due to their larger lifetime of  $\sim 1 \text{ ps}$ , travel a measurable path in the detector, resulting in displaced vertices for the individual *B*-decays. Reconstruction of the decay vertices allows for measurements of the time-dependence of B-decays, with which CP-violation in the B-meson system can be studied. The Belle experiment at KEKB accumulated  $1 \text{ ab}^{-1}$  of data over 10 years. With the significantly increased luminosity, SuperKEKB is expected to deliver an integrated luminosity of  $50 \text{ ab}^{-1}$  over 5 years of running, which will allow for *B*-physics studies with much higher statistics [3]. With the analysis of this data, uncertainties on CP-violation parameters can be decreased and sensitivity to beyond standard model contributions will be increased [4, 5].

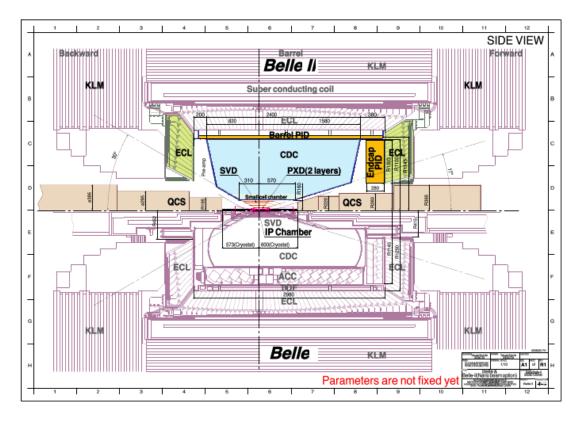

To be able to measure at such high collision rates and to improve the resolution of vertex reconstruction, also the former Belle detector is now being upgraded to Belle II [6]. Figure 1.1 shows a comparison of the layout of the Belle detector (bottom half) to the designed layout of Belle II (top half). Specifically to improve vertex resolution, Belle II will be equipped with additional two layers of high resolution silicon pixel sensors, which are located very close to the interaction region (labelled "PXD (2 layers)" in 1.1). The sensors in this inner pixel detector (PXD) will be based on the DEPFET technology. Using DEPFET pixels as an active silicon pixel detector, very thin sensors with low material

#### 1 Introduction: The Belle II Detector at the SuperKEKB Collider

budget can be built, which reduces the effects of energy loss and multiple scattering on the measured particles. Increased luminosity also means an increase in background and an overall higher particle flux through the tracking detectors, especially for the innermost layers. It is therefore crucial to design the PXD DEPFET sensors and the front-end electronics for radiation hardness. Current estimations state a 1 - 2 Mrad/y irradiation level for the PXD system, the design target is that all PXD components should survive at least a 10 Mrad irradiation dose [6]. The front-end electronics of the Belle II pixel detector will consist of three dedicated chip types. Each of these read-out and steering chips are supposed to fulfil specific tasks, therefore a verification of their functionalities is crucial. In this thesis, I will present and discuss methods and algorithms that were developed in order to investigate certain chip functionalities and to define a strategy to optimize the chip performances. These optimization strategies were applied to several testing systems, and the effects of chip production variations and irradiation on the chip performances were investigated.

Figure 1.1: Comparison of the layout of the former Belle detector (bottom half) and the design layout of the future Belle II detector (top half) as presented in [6]. The Belle II detector design is very similar to the proven Belle design, one major improvement is the additional DEPFET pixel sensor (PXD) close to the interaction point (IP). All other sub-detector systems also undergo a design upgrade.

# 2 The DEPFET Pixel Detector for Belle II

Tracking and vertex reconstruction in the Belle II experiment will be based on two sensor types, together forming the six layers of the Belle II vertex detector (VXD). From the interaction point outwards there are

- two layers of DEPFET pixel sensors (PXD) closest to the beam-pipe and

- four layers of silicon strip sensors (SVD) [7].

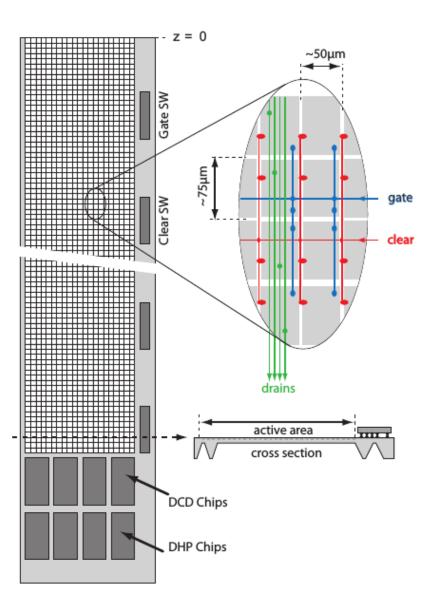

The combined impact parameter and vertex resolution design value is  $\approx 20 \,\mu m$ , dependent on the incident angle and momentum of the measured particle, which maintains and even improves the Belle performance, while operating at much higher background [6]. Figure 2.1 shows a 3D model of the two PXD layers, as well as a cross-section through the PXD system indicating its dimensions. The inner layer is located at a radius of 14 mm, the outer layer at a radius of 22 mm around the beam pipe. These small radii are possible due to the small beam pipe radius of only 10 mm, which is large enough for the nano beam technology developed for SuperKEKB in order to increase the luminosity [3]. Each layer consists of multiple ladders, aligned parallel to the beam pipe, the inner layer has eight and the outer layer has twelve ladders. Each ladder consists of two half-ladder modules, one forward and one backward module, which are glued together. Each half-ladder module has a sensitive DEPFET pixel matrix (light-grey coloured), read-out and steering electronics (not indicated here) and a Kapton cable connection (light-brown) for powering and data connection to the outside. The front-end ASICs are bump-bonded directly onto the halfladder modules support frame (dark blue coloured), which also implements the routing of powering and data lines. A half-ladder module can be considered the building block of the PXD detector

Figure 2.1: 3D model of the two layers of the Belle II DEPFET pixel detector and its individual sensor modules (left, [6]) and a cross-section indicating the dimensions of the PXD system and the radii at which the PXD layers are located (right, [8]).

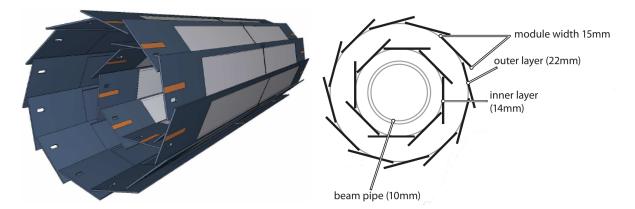

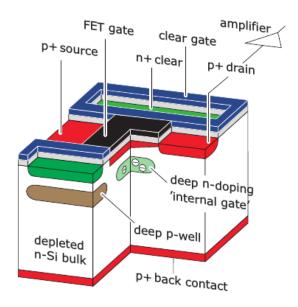

### 2.1 Principles of DEPFET Sensors

To understand the requirements on the front-end electronics for the PXD system, one needs to understand the principles of DEPFET pixel signals. DEPFET stands for *depleted p*-channel field effect transistor, the schematic of a DEPFET pixel is illustrated in figure 2.2. In short, a DEPFET pixel is a MOSFET<sup>1</sup>, with source, gate and drain electrodes, located on top of a depleted silicon bulk with an additional deep n-well implant below the gate electrode (*internal gate*) [9, 10]. A negative high voltage between the source electrode and the p+ back-side contact depletes the bulk via side-ward depletion. Due to the *n*-implant, the potential minimum will form just below the gate electrode in the internal gate. A charged particle traversing the bulk material will generate electron-hole pairs. The holes drift to the back-side contact, whereas the electrons drift to the potential minimum in the internal gate. When the transistor is switched on, i.e. a negative gate voltage is applied, a current is flowing from the source to the drain electrode. Any accumulated charge in the internal gate will modulate the potential landscape and will increase the transistor current. This internal amplification, denoted  $g_q$ , is defined as

$$g_q = \frac{\Delta I_d}{e^-} \quad , \tag{2.1}$$

i.e. the the current modulation  $\Delta I_d$ , per accumulated electron  $e^-$ . The  $g_q$  value characterizes the DEPFET pixel, typical values are  $400 - 700 \text{ pA}/e^-$  for PXD DEPFET pixels [6]. The DEPFET operation principle has some useful properties:

$<sup>^{1}</sup>MOSFET = metal-oxide field effect transistor$

- The signal (accumulated electrons) is already amplified during read-out.

- The accumulated charge can be read out multiple times (non-destructive read-out).

- No lateral charge transfer over large distances is necessary, this reduces charge loss.

- The internal gate has very small capacitance, thus very low noise performance also at room temperature is possible.

- The DEPFET pixel only dissipates power in the small time window when being read out. Thus no cryogenic cooling of a DEPFET pixel matrix is necessary.

After the accumulated charge was read out, one needs to remove the signal charge. This is achieved by applying a positive voltage to a neighbouring  $n^+$  contact. Via a punch through to the internal gate, all charges are collected and removed. After this *clear* procedure, the pixel is sensitive to new signals. The total DEPFET pixel current signal must be corrected for the pedestal current to measure only  $\Delta I_d$ . It holds

$$I_{\text{pixel}} = I_{\text{ped}} + \Delta I_d \tag{2.2}$$

where  $I_{\text{pixel}}$  is the measured pixel current,  $I_{\text{ped}}$  is the pedestal current and  $\Delta I_d$  is the additional current flowing due to accumulated charge in the internal gate, i.e. the actual signal current. Pedestal correction can be done using a *double sampling* read-out procedure, where performing a consecutive read-clear-read allows for the subtraction of a highly correlated pedestal value. However, read-out speed and small dead-times are favoured, so a *single sampling* read-clear sequence is done, where the pedestal values are recorded once and are stored in registers and are assumed to be constant for a specific period of time.

The Belle II PXD DEPFET matrices will have pixel sizes of  $50 \times 55 \,\mu\text{m}^2$  (central part) and  $50 \times 70 \,\mu\text{m}^2$  (forward and backward part) for the inner layer and  $50 \times 60 \,\mu\text{m}^2$  (central part) and  $50 \times 85 \,\mu\text{m}^2$  (forward and backward part) for the outer layer [9]. Each half-ladder sensor matrix consists of  $768 \times 250$  DEPFET pixels. Special efforts have been taken to adjust the DEPFET technology to meet the Belle II requirements. This includes a thinning-technology, which allows for production of  $75 \,\mu\text{m}$  thick substrates. Another concern is the radiation hardness of the sensors. Thin oxides in conjunction with reduced gate lengths yield radiation hard sensors with reasonably high expected signal-to-noise ratios of 20-30 [6].

**Figure 2.2:** Schematic of the principle components of a DEPFET pixel [6]: Signal charges (electrons) are generated in the depleted bulk and are collected in the internal gate and modify the source-drain current of the DEPFET transistor. After read-out, the accumulated charge is removed via a clear potential.

### 2.2 The Front-end Electronics for the Pixel Detector

For steering and reading out a full DEPFET pixel matrix, the following tasks must be performed for each DEPFET pixel:

- Activating the pixel by applying an appropriate gate voltage.

- Sampling the pixel current (pedestal + signal current),

- subtracting the pedestal current and

- digitizing the signal current.

- Clearing the accumulated pixel charge by applying a clear voltage pulse.

- Processing of the digital signal.

The Belle II DEPFET sensors use three dedicated application specific integrated circuit (ASIC) chips for these tasks. The read-out needs to be fast with about  $20 \,\mu s$  for a  $768 \times 250$  pixel matrix and the front-end read-out chips need to be placed on the sensor module with a limitation in available space, their power consumption and dissipation

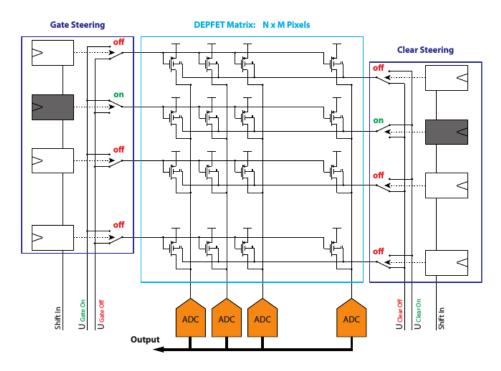

should not exceed a few Watts. Using ASICs as the front-end chips is the preferred way to meet these constraints, as they allow for fast processing at low power consumption and small physical dimensions. In contrast to programmable microprocessors, an ASIC implements a fix electric circuit consisting of analog blocks and digital logic blocks. The circuitry of an ASIC cannot be changed after production, if implemented, its functionality can be influenced by adjustable current sources (analog blocks) or by setting configuration bits (digital blocks). The SWITCHER ASIC for the Belle II PXD system activates and clears the DEPFET pixels in a rolling-shutter read-out mode, as indicated in figure 2.3, by applying the appropriate gate and clear voltages. Segments consisting of four geometrical pixel rows are selected consecutively and the drain currents flow into the Drain Current Digitizer (DCD) chips via the drain lines. Each DCD receives 250 input currents, performs an analog pedestal correction for each input and digitizes all currents in parallel using analog-digital converters (ADCs) with 8-bit resolution. The 250 8-bit digital output codes per DCD are sent to the Data Handling Processor (DHP) chips. The DHP buffers the digital data, performs a digital pedestal correction and zero-suppression and implements a hit finder. Hit data is send out to the back-end electronics upon trigger request. To reduce the material budget as much as possible, the PXD half-ladder modules are realized as allsilicon modules, as shown in figure 2.4. The read-out ASCIs are directly bump-bonded on the silicon support frame, which also implements the routing of power and data lines within three different metal layers (Al and Cu). The DEPFET pixel matrix dissipates only very little power and low-noise operation is possible even at temperatures in the order of 20°C, indirect cooling of the matrix is sufficient and is provided by a cold air flow, with a temperature of -5 °C, through the whole vertex detector system and by heat conduction through the half-ladder silicon support frame [6]. The front-end ASICs, on the other hand, dissipate power in the order of 0.5 - 2 W, active cooling is necessary and provided by cooling pipes filled with a liquid coolant [6, 11, 12].

### 2.2.1 The SWITCHER

The SWITCHER selects segments of four geometrical rows of the DEPFET pixel matrix by applying a negative high voltage, around -5 V, to the gate electrodes. Selection of row segments is controlled by shift registers and strobe signals and is configurable by uploading a specific *SWITCHER sequence*. One SWITCHER chip can address 32 row segments of a DEPFET pixel matrix, multiple SWITCHER chips can be cascaded for steering the read-out of a large matrix [14]. For the 768 × 250 pixels of the PXD half-ladder matrices, six SWITCHERs are needed and are located on the module rim, alongside the DEPFET matrix. The SWITCHER ASIC dissipates power in the order of 0.4 W.

**Figure 2.3:** Sketch of the rolling-shutter read-out mode controlled by the SWITCHER chip [13]. Segments of four geometrical matrix rows are activated consecutively, the pixels of one segment are connected to the drain lines (common for one pixel column) and are read out.

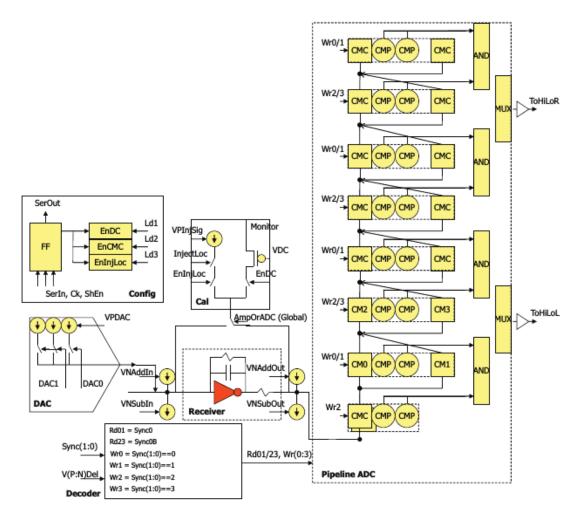

### 2.2.2 The Drain Current Digitizer (DCD)

The Drain Current Digitizer (DCD) chip has 256 analog inputs to receive the drain currents from DEPFET pixels. In fact, one DEPFET matrix segment consists of four geometrical rows and 250 columns, in total 1000 pixels, which are read out by four DCD chips. Thus, each DCD receives only 250 drain currents, six DCD inputs are not connected to the matrix and are not used. Each input current is fed into a separate analog channel of the DCD. The basic structure of the analog circuit present in each DCD channel is shown in figure 2.5, the description is based on [15]. The analog input stage (*Receiver*) is based on a transimpedance amplifier (TIA), which keeps the drain line potential at a constant level. This way, no line capacitance is charged, which increases the read-out speed and reduces noise. Analog pedestal subtraction is realized via a 2-bit DAC (VP-DAC), variable for each channel, and an adjustable current (VNSubIn), which is the same for all channels. The TIA can be programmed to perform an amplification (gain) of the (pedestal corrected) input signal. The TIA also acts as a low-pass filter, which, together with the signal sampling and shaping, reduces the signal noise. The current is then fed into a current-mode *pipeline analog-digital converter (ADC)*, which digitizes the analog input with 8-bit resolution. The pipeline ADC will be discussed in more detail in sec-

**Figure 2.4:** Schematic of a PXD half-ladder module [6]: The read-out chips are bumpbonded on the silicon frame, routing of power and data lines is implemented in the silicon. The result is a thin all-silicon module, reduction of the overall material budget is a major design target of the Belle II PXD system to reduce energy loss and multiple scattering effects.

tion 4.1. The digital data of all DCD channels is processed in a digital block. It decodes and derandomizes the data and sends it partly multiplexed, partly parallel to the next ASIC. The timing requirement for Belle II is a read-out frequency of at least 10 MHz, i.e. a read-out time of  $\leq 100$  ns, per row segment. One DCD dissipates power in the order of 1-2 W.

Different versions of the DCD chip have been developed. The current version for Belle II PXD is labelled DCD-Bv4-Pipeline. My discussions and all presented measurements are

based on this DCD version. Previous versions implemented cyclic ADCs instead of the current pipeline version and are extensively discussed in [13] and [8].

**Figure 2.5:** Basic circuit of one analog channel of the DCD-Bv4-Pipeline chip [15]. The channel receives the DEPFET drain current, subtracts a pedestal current, amplifies the signal and then digitizes it with 8-bit resolution in a pipeline analog-digital converter (ADC).

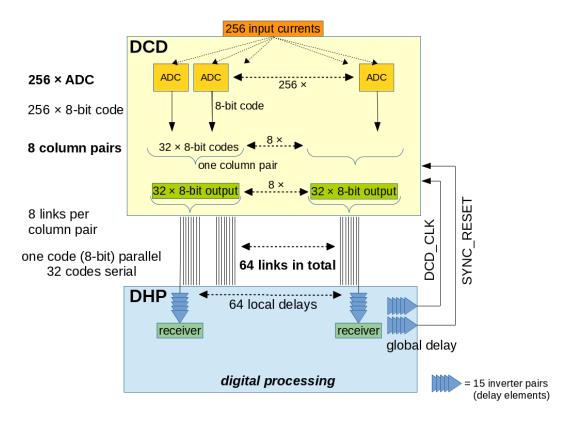

### 2.2.3 The Data Handling Processor (DHP)

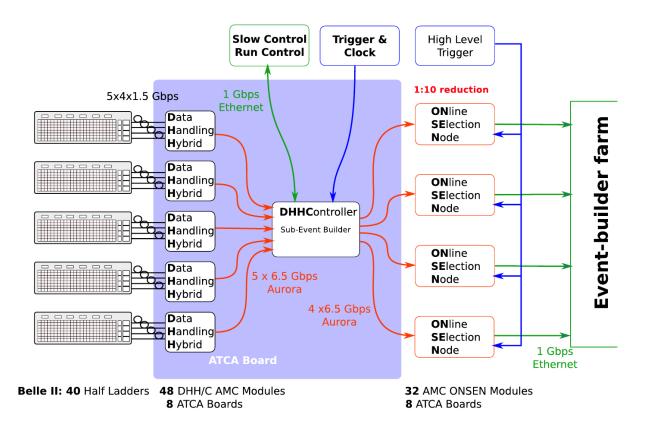

A  $768 \times 250$  pixel matrix produces a data rate of about 80 Gbit/s, which is impossible to send off-module to back-end electronics. The purpose of the Data Handling Processor (DHP) is further processing of the digital data received from the DCD chip to reduce the overall data rates. The data communication between DCD and DHP uses 64 physical links to send the digital data. The incoming raw data from the DCD is buffered in the DHP. A pedestal subtraction is realized by subtracting cached, digital pedestal values, additionally, a common mode correction is applied. The common mode is a signal offset shared by all pixels in one row segment. After pedestal and common mode correction, the data is zero-suppressed, that means only signals above a set threshold are kept. A hit finder searches for hits inside a full matrix frame and stores the information, hit position and signal strength, in a hit buffer. Upon receipt of a trigger signal, the data is send out to the back-end electronics via high speed links. The data handling hybrid (DHH) system provides the primary back-end read-out. Figure 2.6 sketches the back-end electronics read-out chain. The DHP reduces the overall data rate to about 1.6 Gbit/s per DCD-DHP pair or 6.4 Gbit/s per half-ladder module. It is possible to send out the DCD digital raw data directly for testing measurements. The DHP also generates and distributes all timing signals (clocks) to the other ASICs and provides the joint test action group (JTAG) control interface for configuring all ASICs. The DCD and DHP chips are located at the end-of-stave region of a PXD half-ladder module. The current design version of the DHP is labelled DHPT-1.0 as described in [16]. The suffix "T" denotes the  $TSMC^2$ 65 nm technology, the process the DHPT is implemented in.

$<sup>^2{\</sup>rm The}$  Taiwan Semiconductor Manufacturing Company Limited (TSMC) is a manufacturer of semiconductor technology.

Figure 2.6: Sketch of the back-end read-out electronics chain [17]. Each Belle II half-ladder (four DCD-DHP pairs) is read out by one DHH system. Data from five DHH boards is collected in one DHH-Controller (DHHC) that processes and distributes slow control commands and low-level trigger information. The ONSEN system implements online event selection and receives high-level trigger signals.

# **3** Analog-Digital Conversion

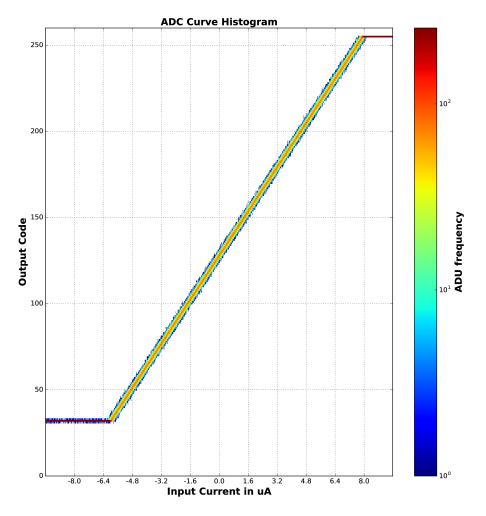

An analog-digital conversion is necessary where digital processing of analog signals is desired. A continuous signal within a specific dynamic range is discretized with a finite digital resolution. The read-out of the DEPFET pixels for the Belle II pixel detector requires the digitization of signal currents up to  $20 \,\mu$ A. The Drain Current Digitizer (DCD) ASIC essentially implements multiple analog-digital converters (ADCs) working in parallel. The performance of a single analog-digital converter can be visualized and measured via an ADC transfer curve. To record the transfer curve, one varies the continuous analog input signal and measures the corresponding discrete digital output code. This chapter will discuss the basics of characterizing ADC transfer curves.

## 3.1 Characteristics of Transfer Curves: Dynamic Range, Noise and Linearity

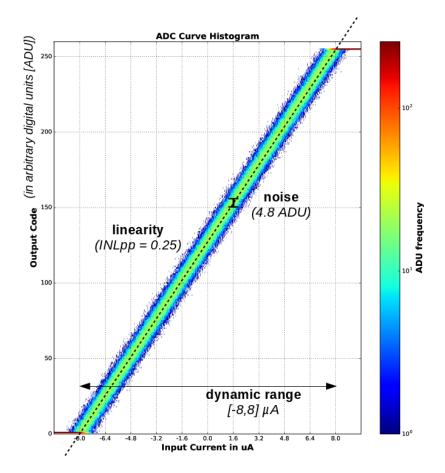

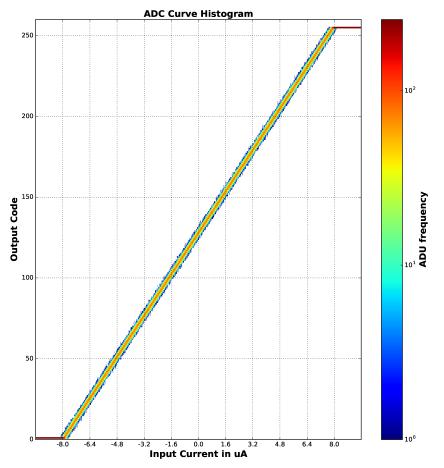

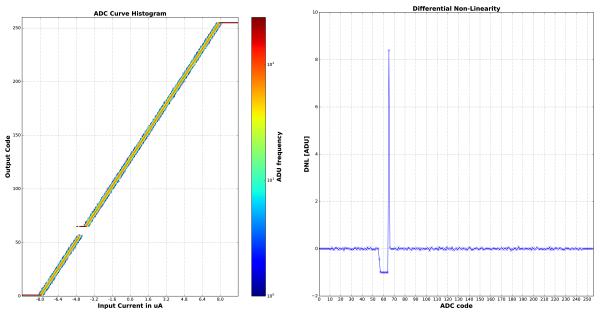

Figure 3.1 shows a prototype example of an ADC transfer curve. Several characteristics of the curve can be measured and are used to evaluate the ADCs performance. A 2-dimensional histogram representation is used, where the x-axis bins measure the analog input value and the y-axis bins measure the digital output code. The ADC transfer curve is recorded multiple times, the color code indicates the frequency at which each input-output bin was recorded.

The analog-digital converter translates the analog inputs to a specific range of digital output codes. In the given example (figure 3.1), the output code range is the interval [0, 255], which means an 8-bit digitization. Smaller input values have lower codes, higher input values have higher codes. Output code 0 corresponds to the minimal input value, while the maximal output code 255 corresponds to the maximal input value. Any input values below or above will be digitized to code 0 or code 255, respectively. The minimal and maximal input values determine the dynamic input range of the ADC, here  $[-8, 8] \mu A$  (see figure 3.1). One must ensure that the dynamic input range of the employed ADC covers the expected signal range. The analog-digital conversion can be subject to electrical noise. To determine the electrical noise, one records the ADC curve multiple times, i.e.

for each input value *i*, the output code *o* is recorded multiple times. Let  $f_{io}$  denote the occurrence of the input *i* and output *o* bin. The ADC curve noise  $\sigma_i$  as a function of the input value can then be defined as the standard deviation of the output codes per input value bin. A measure for the overall ADC noise  $\sigma$  can be defined as the median over all  $\sigma_i$ . The measured ADC noise is a convolution of the noise of the input signal (independent from the ADC performance) and the noise introduced by the analog-digital converter itself.

Another concern is the linearity of the ADC curve. Ideally, the ADC operation should be perfectly linear, i.e. a doubled input value should result in a doubled output code (within the given ranges). The linear behaviour ensures, that the digital resolution is constant over the full dynamic range of the ADC. The digital resolution can be defined as the width of the input value interval for which the output code is constant, this is exactly the slope of the ADC curve. A constant, homogeneous resolution thus means a constant slope, i.e. a linear behaviour. Any deviation from a linear behaviour, that is a non-linearity, can be measured as a local deviation or differential non-linearity (DNL) or as an integrated non-linearity (INL). Using the 2-dimensional histogram representation, the total occurrence of one output code o is denoted as  $f_o$  (i.e. projecting out the input value bins i). Let m denote the mean over all  $f_o$ , that is the mean occurrence of all output codes. The differential non-linearity (DNL) can then be defined as

$$DNL_o = \frac{f_o}{m} - 1 \tag{3.1}$$

which is the non-linearity per output code o. The integrated non-linearity is then simply defined as the cumulative sum of all DNL values up to output code o

$$INL_o = \sum_{k}^{o} DNL_k . aga{3.2}$$

Ideally, for a perfectly linear ADC curve, the DNL of each output code is 0 and thus also the INL is 0 for all output codes. An output code with no readings, i.e. a gap in the ADC curve, has a DNL of -1. A code that appears more often than all others is assigned a positive DNL. One may define a single measure for the ADC curve linearity as a peak-to-peak INL value, which is

$$INLpp = |\max(INL_o) - \min(INL_o)|.$$

(3.3)

Another possibility to determine the ADC curves linearity would be to perform a leastsquares fit of a linear function to the two-dimensional ADC histogram and using the  $\chi^2$  value as a measure for linearity. However, the fit  $\chi^2$  value is influenced by various effects. Higher ADC curve noise, for example, would increase the  $\chi^2$  value, although the linearity is unchanged. Also, if for some reason the ADC curve is fragmented into multiple linear parts, the linear fit is no longer accurate and no reasonable information can be drawn from it (see discussion on bit errors in chapter 6). DNL and INL are much more robust measures to use for characterizing an ADC curve.

Figure 3.1: Prototype example of an ADC transfer curve used to investigate the performance of a current-mode analog-digital converter. On the x-axis the analog input values (current  $I_{in}$ ) are binned, the y-axis measures the corresponding digital output code bin in arbitrary digital units (ADU). The transfer curve was recorded multiple times, a 2-dimensional histogram representation is chosen, where the color code indicates the frequency at which each inputoutput bin was recorded. The characteristic properties of the ADC transfer curve are the dynamic input range, the electrical noise and the linearity.

## 3.2 Cyclic Redundant Signed-Digit Analog-Digital Conversion Algorithm

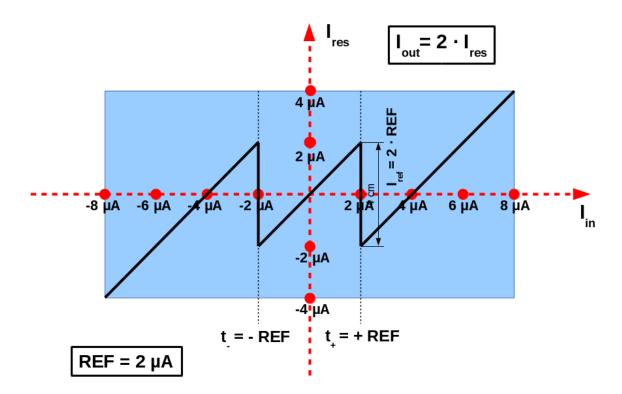

The ADCs in the Drain Current Digitizer (DCD) ASIC convert the DEPFET pixel currents (in the order of some  $\mu$ A) to digital 8-bit signals. The conversion algorithm used in the DCD design is a cyclic redundant signed-digit (CRSD) conversion as described in [18]. The algorithm is an iteration over several n identical stages. In each stage i, the input current  $I_{\rm in}$  is compared to two thresholds, one negative  $t_{-}$  and one positive  $t_{+}$  threshold. Per stage two bits are set, a TOOHIGH and a TOOLOW bit. If  $I_{\rm in} > t_{+}$  then TOOHIGH = 1 and TOOLOW = 0, or simply said the redundant bit code is 10. In this case a reference current  $I_{\rm ref}$  is subtracted from the input current. If  $I_{\rm in} < t_{-}$  the redundant bit code is 01 and the reference current  $I_{\rm ref}$  is added to the input currents. In case  $t_{-} \leq I_{\rm in} \leq t_{+}$  the redundant bit code is 00 and no current is added or subtracted to  $I_{\rm in}$ . The residual current  $I_{\rm res}$  has by construction half the range of the input currents.  $I_{\rm res}$  is thus multiplied by a factor of two to match the next stages input range. The output current  $2 \times I_{\rm res}$  then undergoes the same operation in the next stage i + 1. The final conversion result for the ADCs output code D after n stages is computed from the TOOHIGH-TOOLOW bit pair streams of all stages as

$$D \equiv 2^{0} (\text{TooHigh}_{n} - \text{TooLow}_{n}) + \dots + 2^{n} (\text{TooHigh}_{0} - \text{TooLow}_{0}) \quad . \tag{3.4}$$

The first stage (stage 0) determines the most significant bit (MSB) of the output code D. Each additional conversion stage yields an additional TOOHIGH and TOOLOW bit pair and improves the digital resolution. For an *n*-cyclic conversion process, D is the (n + 1)-bit binary representation, a signed integer, of the input current  $I_{in}$ .

# 4 The Front-end Electronics in Detail

This chapter will present in more detail some aspects of the read-out ASICs, namely the implementation of the analog-digital conversion in the Drain Current Digitizer (DCD) and the digital communication among the DCD and the DHP ASICs. Both aspects are critical for the front-end read-out to work properly. The design of the ASICs implement several parameters that allow for adjusting the AD conversion in the DCD and the inter-ASIC communication.

## 4.1 Analog-Digital Conversion Implementation in the Drain Current Digitizer

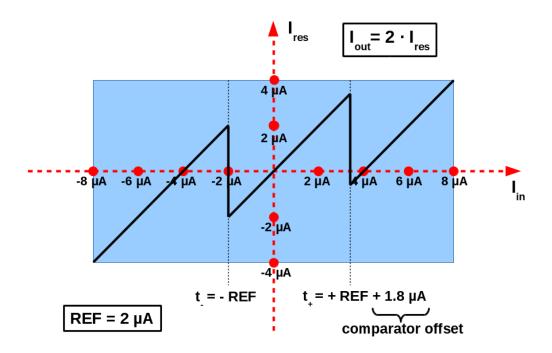

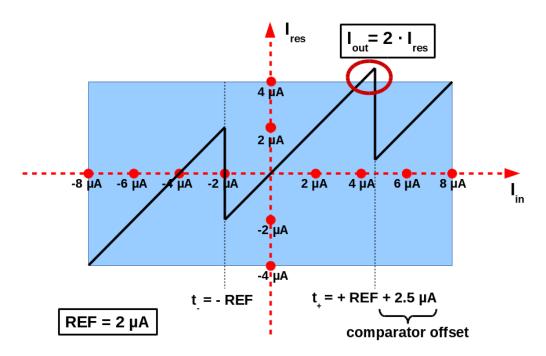

As described in section 2.2.2, the DCD chip provides 256 analog channels, each with a pipeline analog-digital converter implementing the redundant signed-digit (CRSD) conversion algorithm as it was described in section 3.2. The schematic implementation is sketched in figure 2.5, right-hand side. The CRSD-algorithm requires arithmetic operations, i.e. addition and subtraction of currents<sup>1</sup>. In the pipeline ADC implementation of the DCD, current-memory cells (CMC) are used for storing currents and allow for arithmetic operations with currents. The second requirement is the implementation of current comparisons, analog comparators (CMP) are used for this purpose. Each conversion stage of the pipeline ADC, corresponding to one stage of the CRSD conversion algorithm, contains two double cell blocks (each consisting of two CMCs) and two comparators. In this implementation, the ADC uses a reference current REF, which defines the thresholds  $t_{+} = \text{REF}$  and  $t_{-} = -\text{REF}$  of the CRSD-algorithm. The reference current  $I_{\text{ref}}$ , that is added or subtracted after comparison, is set to be  $I_{\text{ref}} = 2 \cdot \text{REF}$ . The design value is REF = 2.0  $\mu$ A. The ideal input/output relation of one conversion stage is graphically represented in figure 4.1. It is vital to adjust the reference current  $I_{\text{ref}}$  and

<sup>&</sup>lt;sup>1</sup>The algorithm requires a multiplication by two of the residual current per conversion stage. This can be realized as a simple addition of two equal currents.

the thresholds  $t_+$  and  $t_-$  properly to achieve an ideal analog-digital conversion. The DCD pipeline ADCs implement an 8-cycle CRSD-conversion, which yields a 9-bit digital result D. To simplify digital data processing, the least significant bit (LSB) of D is omitted. The reduced digital code  $D^*$  is an 8-bit code in standard binary two's complement representation, where  $D^* \in [-127, 127]$ . Note that the DHP reinterprets these codes in an 8-bit unsigned representation  $\in [0, 255]$ . The pipeline ADCs sample the input currents at a rate of 100 ns. The dynamic range for each ADC is in the order of  $32 \,\mu$ A but can be adjusted (see next section) and depends on the dynamic ranges of the current memory cells. Nominally, the current memory cells have a dynamic range of  $[-8, 8] \,\mu$ A, i.e. a  $16 \,\mu$ A range. The first stage of the pipeline ADCs is implemented slightly differently than the following stages, both double cell blocks are written simultaneously, which extends the overall nominal ADC dynamic range to  $32 \,\mu$ A. Table 4.1 states the design specifications of the DCD-Bv4-Pipeline version.

Via the calibration circuit it is possible to inject a know current, either into the TIA or directly into the ADC of one channel at a time. The *fast or internal injection* uses a DCD internal current source, controlled by the 9-bit DAC VPInjSig, for injecting currents into a selected channel. This procedure is fast, but allows only coarse current steps. The *external injection* uses an external current source, which is connected through a monitor pin. The DHH back-end electronics provide a highly linear, finely tunable current source that can be connected via the monitor pin. Currently under study is the idea of using the DEPFET transistors as an adjustable current source for injecting currents into all DCD channels in parallel.

| property                         | value                                 |

|----------------------------------|---------------------------------------|

| number of ADCs                   | 256                                   |

| ADC resolution                   | 8-bit                                 |

| ADC sampling rate                | $100\mathrm{ns}$                      |

| ADC noise                        | 80 nA - 120 nA                        |

| signal-to-noise ratio            | > 17                                  |

| (for a MIP)                      |                                       |

| input amplification factor (TIA) | 1 / 2                                 |

| ADC LSB value                    | 160 nA / 80 nA                        |

| max. dynamic input range         | $40\mu\mathrm{A}$ / $20\mu\mathrm{A}$ |

**Table 4.1:** Overview of the design specifications of the DCD-Bv4-Pipeline ASIC as given in the design manual [15].

Figure 4.1: Input/output current relation of one pipeline ADC stage in the ideal case. The positive and negative thresholds are at  $t_{\pm} = \pm 2 \,\mu$ A, the reference current added or subtracted is  $4 \,\mu$ A. The blue box indicates the dynamic range of the current memory cell (here  $[-8, 8] \,\mu$ A) storing the input current on the x-axis. The effective dynamic range of the CMC of the next stage (y-axis) is halfed, as the residual current  $I_{\rm res}$  is multiplied by a factor of two when fed into the next ADC stage. The figure was adapted from [19].

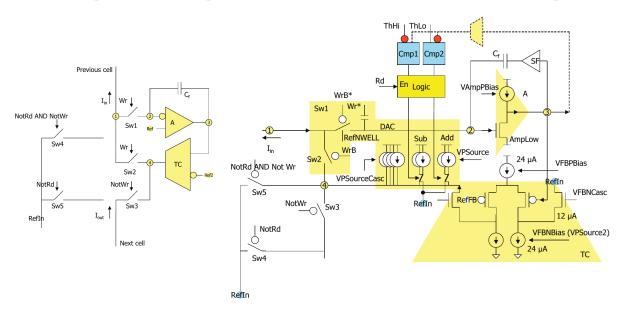

#### 4.1.1 Current Memory Cells and Comparators

The pipeline ADC operation relies on the functioning of the current memory cells (CMC). Figure 4.2, left hand side, shows the basic layout of a single current memory cell as it is used in the DCD design. It makes use of an amplifier (A) and a transconductor (TC), the capacity  $C_f$  acts as the memory element. The current memory cell is designed to store currents in the range of  $[-8, 8] \mu A$  while keeping the input potential at a value of 1 V. For writing a current to the cell at node 1, switches 1 and 2 are closed and the capacity  $C_f$ is charged. The amplifier, which is assumed to have infinite gain and no offset, generates a potential proportional to the input current at node 3. The transconductor generates a feed-back current at node 4, that increases until it compensates the input current completely. When switch 1 is opened again, the potential across  $C_f$  is frozen. For reading, only switch 3 is closed and the stored current, generated as the TC feed-back current via the frozen potential at node 3, is flowing out of the cell. The operation of the current

#### 4 The Front-end Electronics in Detail

memory cell can be adjusted by changing several DAC settings and supply voltages (see figure 4.2, right hand side). The amplifiers use the ground potential labelled as AmpLow. The transconductors have adjustable sourcing (*FBPBias*) and sinking (*PSource2*) current sources. To be able to add and subtract currents, as required by the CRSD-algorithm, the current source *PSource* is present at node 4. The nominal value of *PSource* is 8  $\mu$ A, but it is configurable via a DAC called *IPSource*. According to the output of the comparators, *PSource* is changed by  $\pm 4 \,\mu$ A, thus acting as the reference current  $I_{ref}$  which is added or subtracted in the CRSD conversion algorithm.

The implementation of the comparators is very similar to that of the current memory cells. The transconductor with the current source *PSource* acts as the input stage and is almost identical to the one used in the current memory cells and uses the same biasing current sources *FBPBias* and *PSource2*. The difference is the value of *PSource*, which is changed by  $+2\mu$ A for a high comparator or  $-2\mu$ A for a low comparator, thus acting as the thresholds  $t_{\pm}$  used in the CRSD-algorithm. The comparators also implement amplifiers which share the ground potential *AmpLow*. The supply *RefIn* is used at several nodes as a current dump and as a fixed potential reference, both in the CMCs and the comparators.

*Figure 4.2:* Basic (left) and more detailed (right) layout of the current memory cells used in the pipeline ADCs implementation as part of the analog channels of the DCD [15].

#### 4.1.2 Parameters for Adjusting the Analog Performance

As already seen, there are several parameters, DACs and supply voltages, that influence the operation of the pipeline ADCs in the analog channels of the DCD. For optimizing the DCD operation, one needs to find the optimal working point, i.e. the set of settings for which all ADC channels show best performance. There are three important DAC settings that influence the functionality of the current memory cells and the comparators [13, 15]:

- **IPSource** [**DAC**] shifts the comparator reference current REF and determines the total dynamic range of the ADC. A value of 64 corresponds to a total dynamic range of 16  $\mu$ A, while a value of 120 corresponds to a 32  $\mu$ A range.

- **IPSource2** [**DAC**] controls the working point of the transconductors used in the current memory cells and the comparators. From design its value should be equal to IPSource.

- **IFBPBias [DAC]** is the biasing current of the transconductors in the CMCs and the comparators. From design its value should be equal to IPSource. IFBPBias and IPSource determine specifically the dynamic range of the current memory cells.

There are three analog supply voltages for the DCD [13]. The powering of the analog part is supplied by DCD\_AVDD, which is set to 1.8 V. The two other voltages are:

- **RefIn** [voltage] is used as a reference at several nodes in the CMCs and the comparators. The design value is 1 V at 50 mA.

- AmpLow [voltage] is the ground potential for the amplifiers in the CMCs and the comparators. A change in AmpLow can shift the input characteristic of the CMCs and can also affect their dynamic input range. The design value is 300 mV at -247 mA.

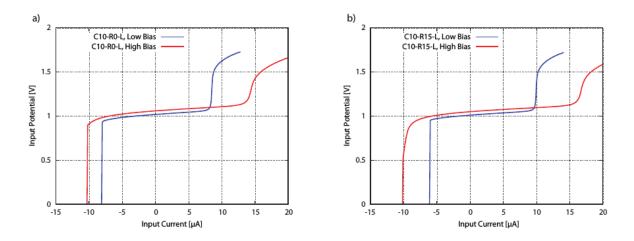

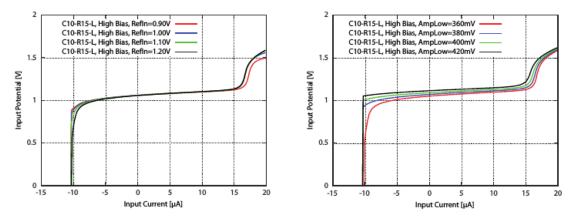

The DCDs on one half-ladder module share the same RefIn and AmpLow voltages while the DACs can be configured individually. Figure 4.3 indicates the dependence of the current-memory cells dynamic range on the DAC settings and on the position on the DCD chip. A higher bias (higher DAC values) increases the CMCs dynamic range. However, the dynamic ranges are not necessarily symmetric and the asymmetry may grow with higher DAC settings. Also, there seems to be a shift of the dynamic range for CMCs far away from the supply pins, which hints to voltage drops across the DCD chip. The dependence of the CMC dynamic range on the voltages RefIn and AmpLow is indicated in figure 4.4. RefIn does not change the characteristic of the CMC. Lower AmpLow values reduce the CMC dynamic range and shift the input characteristic towards the positive range.

Figure 4.3: Dependence of the current memory cells input characteristics on the DACs IPSource, IPSource2 and IFBPBias. High bias means all three DACs at 120, low bias means all three DACs at 60. On the left, a CMC close to the power supply pins of the DCD is shown, on the right a CMC on the other end of the DCD chip [13].

Figure 4.4: Dependence of the current memory cells input characteristics on the voltages RefIn (left) and AmpLow (right) [13].

### 4.2 Inter-ASIC Communication

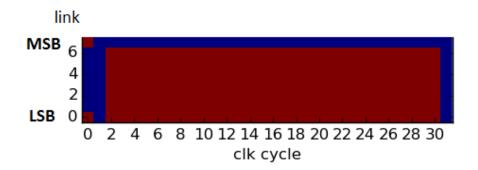

The digital 8-bit codes computed by the ADCs in the DCD channels are sent to the DHP ASIC via several links. The 256 analog channels of the DCD are arranged in eight so called *column pairs*, thus each column pair contains 32 ADCs. Each column pair has eight communication links on which the eight bits of one ADC code are sent in parallel. The total 32 ADC codes per column pair are sent one after another, serially, over the eight links. In total, this requires 8 links  $\times$  8 column pairs, 64 links from DCD to DHP for the ADC data transmission. The serialization is necessary as the number of links is

limited due to the available space for routing on the module. The timing requirement, as mentioned in section 2.2.2, is a read-out time of 100 ns per row segment of the DEPFET matrix. That means, the serial data of 32 ADC codes per column pair has to be sent in 100 ns, which translates into a required clocking frequency of 320 MHz. This 320 MHz high clock DCD\_CLK is provided by the DHP to the DCD. A second clocking signal SYNC\_RESET is used to synchronize all digital logic in the DCD and is also provided by the DHP. All clocking signals are derived from a global reference clock GCK, which is provided by the back-end electronics in the DHH. The value of GCK can be adjusted to operate the front-end electronics at different frequencies. The high frequency DCD\_CLK clock is generated via division by four of GCK, thus the nominal GCK value is 80 MHz. The timing of all eight column pairs of the DCD is identical.

The analog channels of the DCD provide the possibility of an analog pedestal correction via a 2-bit DAC (see section 4.1). This DAC value can be set for each geometrical pixel of the DEPFET matrix individually and is stored in a pedestal memory in the DHP. During the rolling-shutter read-out, it is necessary to consecutively upload these pedestal values to the corresponding DCD channels to perform a proper pedestal correction. This is done in a similar way as for the ADC data transmission. Each DCD column pair has two additional links, over which the 2-bit pedestal DACs are uploaded to the DCD. This requires additional 2 links  $\times$  8 column pairs, 16 pedestal upload links from DHP to DCD. The clocking behaviour is similar to that of the data links and identical for all pedestal upload links. Issues concerning the pedestal upload link communication will not be discussed here, details can be found for example in [20]. In this thesis, the discussion will concentrate on the communication over the 64 data links. Figure 4.5 sketches the signal and data flow between the front-end read-out ASICs.

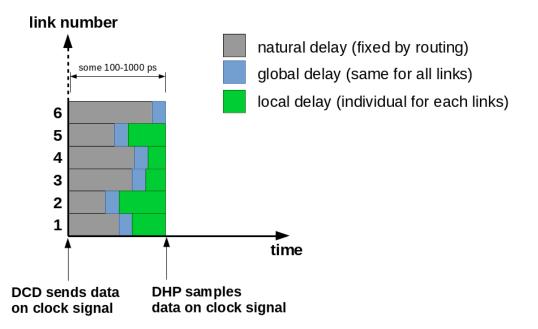

#### 4.2.1 Data Links Communication: Signal Delay Compensation

The 64 data links from DCD to DHP, as well as the 16 pedestal upload links from DHP to DCD, share the clock timing at which data is send and received. The routing of the links and the strength of the output drivers, however, may differ slightly between links. As a result, the data is send out synchronously on DCD side, but it not necessarily arrives synchronously on DHP side. The receivers on DHP side will sample all data links synchronously at the same time, which introduces the question of how to cope with the asynchronism induced by the varying routing and output driver strengths. Several delay elements have been added to the DHP design to allow for delaying of individual signals. As described above, data from the DCD is send out according to DCD\_CLK, which is generated in the DHP. Delaying the DCD\_CLK signal thus introduces a phase shift

Figure 4.5: Sketch of the data flow in the front-end read-out system and the communication among the ASICs.

between the DCD data sending and the DHP data sampling. The delay is achieved via a cascade of inverter pairs (delay elements). In total, 15 inverter pairs are cascaded, each adding a delay in the order of some 100 - 1000 ps. The number of inverter pairs, by which the clock signal is delayed, can be set with a 4-bit JTAG register entry. The same delay architecture is also available for the SYNC RESET signal. It is reasonable to always delay DCD CLK and SYNC RESET by the same amount to ensure synchronicity of the clock signals, so both JTAG register entries will always be set to the same 4-bit value and we call this the *global delay*, as it affects all DCD-DHP communication links in the same way (see figure 4.5). The global delay can take values between 0 (no delay) and 15 (maximal delay, all inverter pairs active). Individual delay of the data links is also possible via the same mechanism. Each link can be delayed through 15 inverter pairs and has its own 4-bit JTAG register for configuring the amount of delay. The 64 4-bit data link delays are denoted *local delays* (see figure 4.5). These delay elements delay the actual signal on the link line. For one specific link, local and global delay accumulate, thus a total delay of 30 inverter pairs is possible. The exact value each inverter pair adds to the delay of the signal depends and the clock frequency and the digital supply voltage of the DHP. Additionally, it cannot be assumed that a global delay element and a local delay element add the same amount of delay. Optimal values for the 64 local delays and the single global delay have to be found to assure proper DCD-to-DHP data transmission. The optimization of the delay settings will be discussed in chapter 7.

The data transmission uses low voltage single-ended signalling (LVSE) for sending the ADC output codes from DCD to DHP. The voltage swing and the reference potential are generated in the DCD and are fixed by design, it is not possible to tweak these parameters to improve the data transfer. Measurements of the current DCD and DHP ASICs showed asymmetric rise and fall times of the data signals, a new iteration of the DHP chip, the DHPT1.1, was submitted with improved data signal receivers [21].

# 5 Experimental Setups for ASIC Testing

Several testing systems and setups have been developed and are used to investigate the performance of the read-out ASICs and the full front-end read-out system. Extensive work on the testing and the debugging of previous iterations of the DCD chip have been carried out by [8] and [13]. A versatile interface system is needed to test the ASIC functionalities. Several such systems are available, two of these, the Hybrid5 boards and the electrical multi-chip modules (EMCMs) have been used for measurements in the scope of this thesis and will be discussed in the following.

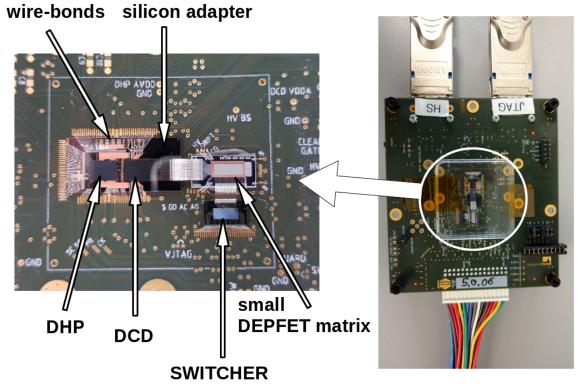

## 5.1 The Hybrid5: A PCB-based ASIC Testing Interface

In the final PXD system, the read-out ASICs will be bump-bonded onto the all-silicon modules. It is, however, useful to decouple the module design (metallization and routing) from the pure ASIC testing. For this purpose the Hybrid5 boards were developed, which implement all routing on a genuine PCB<sup>1</sup> and provide several probing and testing pads on PCB-level [8]. The ASICs are bump-bonded to a silicon wire-bond adapter, which is glued to the PCB. The adapter routes the ASIC pads to be accessible by wire-bonds, the inter-ASIC communication links are routed purely on the adapter. The wire-bond interconnection from the adapter to the PCB connects all power supply, JTAG control and high-speed data lines. Figure 5.1 shows a picture of a Hybrid5 board. Each Hybrid5 is equipped with one DCD and one DHP ASIC. Optionally, a SWITCHER ASIC and a DEPFET matrix can be added, thus providing a small scale testing emulation of the full front-end read-out chain. All power supply and voltage sensing lines are connected to the PCB via a 30-pin Samtec<sup>2</sup> connector. The DHP sends out data to the back-end electronics via high speed links and it provides the JTAG interface for configuration of all ASICs.

$<sup>^{1}</sup>PCB = printed circuit board$

$<sup>^2\</sup>mathrm{Samtec}$  is a company focussed on electronic interconnections (www.samtec.com).

#### 5 Experimental Setups for ASIC Testing

Both links, the high speed data link and the JTAG link, are realized as two separate InfiniBand<sup>3</sup> connections. With the Hybrid5 PCB, it is possible to probe all power supply potentials and also several clocking signals, thus providing an in depth ASIC testing tool.

**Figure 5.1:** Picture of a Hybrid5 board equipped with a DCD and DHP ASIC and a small DEPFET matrix steered by one SWITCHER ASIC. The DCD and DHP are bump-bonded to a wire-bond adapter, which is glued on the Hybird5 PCB board. Interconnection between ASICs and the PCB is done via wire-bonding. The right-hand side shows the full Hybrid5 board with the InfiniBand (top) connections for the JTAG and high speed link interface to the DHH and the Samtec connector (bottom) for the powering.

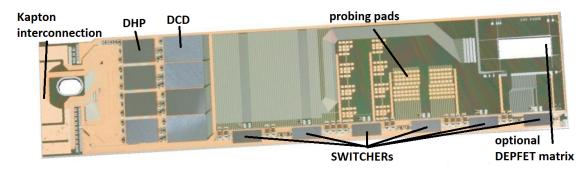

### 5.2 Electrical Multi-Chip Modules

The electrical multi-chip modules (EMCMs) follow a more integrated approach. While a Hybrid5 board can be used to measure and debug a single ASIC pair (DCD+DHP) in great detail, an EMCM is much closer to the final sensor module situation. In fact, an EMCM is designed as a fully functional PXD half-ladder module, but without a DEPFET matrix.

$<sup>^{3}\</sup>mbox{InfiniBand}$  is a computer-networking communication standard providing very high bandwidth at low latency

Figure 5.2 shows a picture of an EMCM module. In total 4 ASIC pairs are present and bump-bonded onto a silicon support frame. The routing of power and data lines is done on the support frame and is close to the final sensor module design. Also, six SWITCHER chips are cascaded alongside the balcony of the EMCM module, with which the interplay of multiple SWITCHERs can be tested. The area normally occupied by the DEPFET matrix provides some testing and monitoring pads. With an EMCM, it is possible to study the full front-end read-out system in a final-like configuration and in addition, the routing on the silicon support frame is being tested. Still, the ASIC properties are measured completely decoupled from any DEPFET matrix properties. It is, however, possible to add a small matrix to an EMCM by gluing it onto the module and connecting it via wirebonds to the provided pads. The connection of powering and data lines to and from the module is realised via a Kapton<sup>4</sup> cable connection. A three-layer Kapton cable is glued to the support frame and wire-bonds connect several Kapton cable pads to three banks of corresponding pads on the module. The same interconnection principle will be used for the final PXD half-ladder modules. The Kapton cable is attached to a PCB, serving as a patch panel, from which powering and data connections to the back-end electronics are maintained.

**Figure 5.2:** Picture of an electrical multi-chip module (EMCM) used to study the frontend read-out ASICs in a final module like configuration, including the routing on the silicon support frame. EMCMs can be equipped with a small DEPFET matrix, connection to the module is realized via a Kapton cable (not shown here).

# 5.3 Back-end Read-out and Laboratory Setup

The Hybrid5 and EMCM modules provide the interface to the ASICs and are now denoted as devices under test (DUTs). For testing of the read-out ASICs, a back-end read-out

<sup>&</sup>lt;sup>4</sup>Kapton is a trade name for poly-amid films used in flexible electronics.

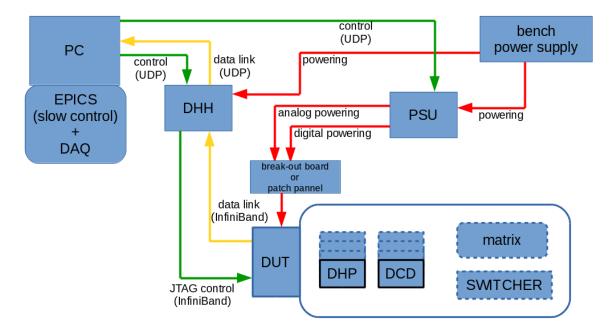

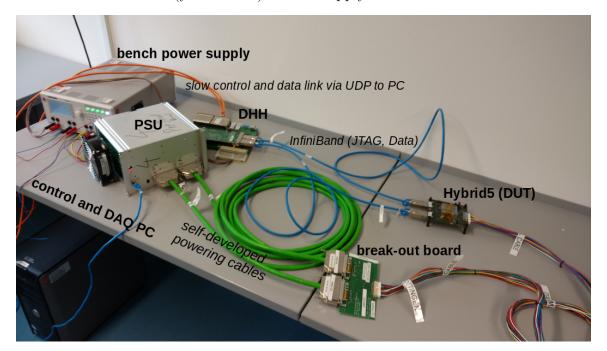

system is necessary. In the laboratory setups, the back-end electronics is represented by a single Data Handling Hybrid (DHH) system, which provides direct interface to a control PC. The DHH system is based on a field programmable gate array (FPGA), for fast data processing and the possibility of updating the firmware. The DHH communicates with the DHP ASICs on the DUT, this includes slow control via the JTAG interface and data reception, and provides a  $UDP^5$  interface to a control PC. The DHH also implements a pedestal memory and a finely tunable current source, it is powered from a standard laboratory bench power supply. The powering of the DUT, and thereby the powering of the ASICs and an optional DEPFET matrix, is supplied by a self-developed power supply unit (PSU), which will also be used in the final Belle II experiment. The PSU needs a general, static powering provided from a standard bench power supply and an active emergency-stop voltage. Analog and digital supply voltages are routed separately via self-developed and self-fabricated cables to a break-out board (Hybrid5) or a patch panel (EMCM and final modules) and from there to the DUT via a Kapton cable (EMCM and final modules) or a 30-pin Samtec connector (Hybrid5). Figure 5.3 sketches the components and connections used in the laboratory setups. Figure 5.4 shows a picture of a Hybrid5 laboratory setup.

Slow control on the control PC is implemented using the EPICS<sup>6</sup> environment, from which the ASICs can be configured and the PSU voltages can be set. The same PC is also used for data acquisition (DAQ), a DAQ software reads the UDP data stream form the DHH and saves it to disk. In the final experiment the back-end read-out is more complex as multiple modules have to be read-out and data streams have to be merged. There, several DHH boards will be connected to one DHH-Controller (DHHC) device, handling low-level trigger signals and distribution slow control commands.

<sup>&</sup>lt;sup>5</sup>The User Datagram Protocol (UDP) is a minimalistic, connectionless networking protocol. <sup>6</sup>Experimental Physics and Industrial Control System (http://www.aps.anl.gov/epics/)

**Figure 5.3:** Sketch of the general laboratory setup for operating and investigating a device under test (DUT), an EMCM or Hybrid5 boards, providing the interface to the read-out ASICs. Slow control is provided from a normal PC via network packages (UDP) and JTAG (via InfiniBand cables) and indicated by green lines. Data is likewise send via InfiniBand and network connection (yellow lines). Power supply lines are marked in red.

**Figure 5.4:** Picture of a laboratory setup with a Hybrid5 board as device under test (DUT).

# 6 Read-out ASICs Failure Identification

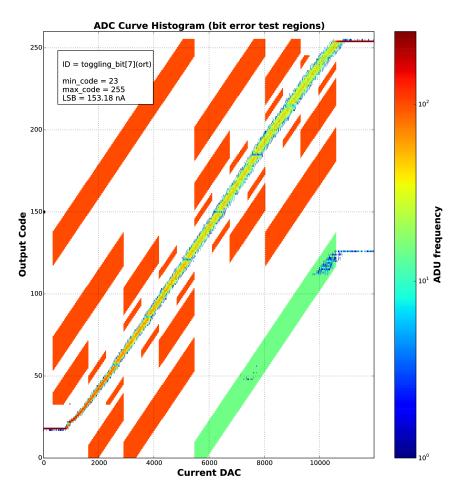

In the previous chapters, the read-out ASICs for the Belle II DEPFET sensor have been presented and the most important aspects of their current design implementations and functionalities have been discussed. Additionally, the testing setups used for measuring ASIC properties have been introduced. Section 4.1 discussed the ideal analog-digital conversion in the analog channels of the DCD ASIC. In order to study and optimize the functionality of the Drain Current Digitizer (DCD) ASIC and the inter-ASIC communication, several testing algorithms have been developed in the scope of this thesis. Simulation studies of the DCD analog-digital conversion and the DCD-to-DHP data transmission have been conducted, respecting the respective implementation details. Based on these results, testing algorithms were defined, that are able to identify specific failure scenarios in the ASIC operation. The figure of merit for evaluating the ADC performance and identifying failures therein is the ADC transfer curve as it was discussed in section 3.1. All testing algorithms run on these transfer curves and will be discussed in this chapter.

# 6.1 Drain Current Digitizer: Analog Performance and Failure Identification

The DCD chip implements 256 analog channel, each with a current-mode pipeline ADC. The functionality of all ADCs can be modified mainly by the three DACs IPSource, IPSource2 and IFBPBias, and the two supply voltages RefIn and AmpLow (see section 4.1.2). For each ADC, a separate ADC curve can be measured and analysed. The quality of the ADC curve, and thereby the functionality of the ADC, is evaluated regarding the dynamic range, noise and linearity.

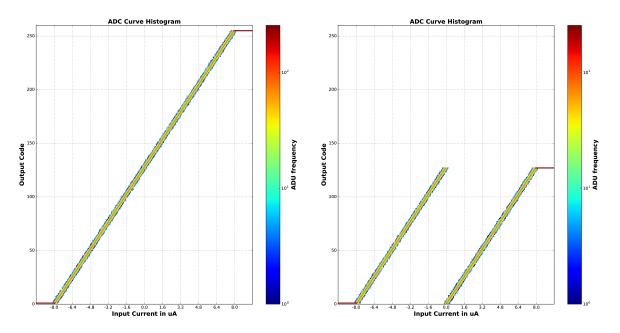

## 6.1.1 Dynamic Range

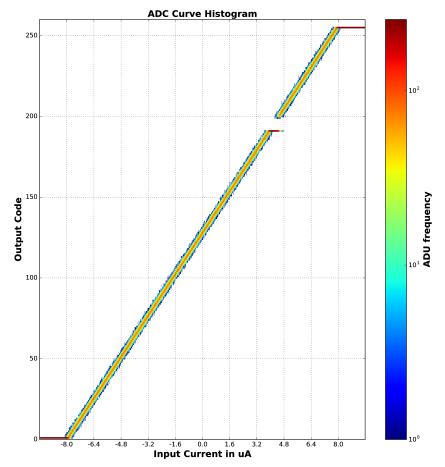

The nominal dynamic range of the current memory cells is  $[-8, 8] \mu A$ . The TIA, acting as the current receiver in the analog channels, can be programmed to perform an additional amplification of the input current by a factor of two (gain = 2) or no amplification (gain = 1). Thus the effective input range for the analog channel is either  $32 \,\mu \text{A}$  (gain = 1) or  $16 \,\mu\text{A}$  (gain = 2), a higher gain means a finer AD conversion. However, the possibility for using gain = 2 is dependent on the overall pedestal spread of all DEPFET pixels and how much the spread can be compensated for by analog pedestal correction. The DCD ADCs digitize with 8-bit resolution, i.e. the nominal code range is 256. The fraction of dynamic input range over code range can be understood as the slope of the ADC curve and is 62.5 nA/ADU for gain = 2 and 125 nA/ADU for gain = 1, ADU stands for arbitrary digital unit and is used as the unit for the digital codes. This can also be understood as the smallest current that can be resolved by the ADC, i.e. the current corresponding to the least significant bit (LSB) which is exactly one ADU. This value can be measured by fitting a linear function to the ADC curve and extracting the slope of the fit. The value of the ADC curve slope depends on the relation and interplay of the CMCs dynamic ranges and the values of the positive and negative thresholds used in the comparators. Both depend on the previously explained DACs IPSource, IPSource2 and IFBPBias and the supply voltages RefIn and AmpLow. For a fixed slope a reduction in the dynamic range translates directly into a reduction of the code range. Thus, for analysing the ADC curve we determine the minimal and maximal ADC code, that were recorded for this curve, as code min and code max. A reduced code range means a smaller than nominal dynamic input range of the ADC. A slight reduction of the code range is accepted. Thresholds for the minimal and maximal codes are defined, if the maximal code is below or the minimal code is above the corresponding threshold, a code min or code max error is identified for the ADC curve. Figure 6.1 shows a simulated ADC curve with a reduced dynamic range. The simulation was implemented according to the CRSD-algorithm of the DCD with the nominal CMCs dynamic ranges, except for stage 0 where the CMC ranges were reduced to  $[-6, 8] \mu A$ .

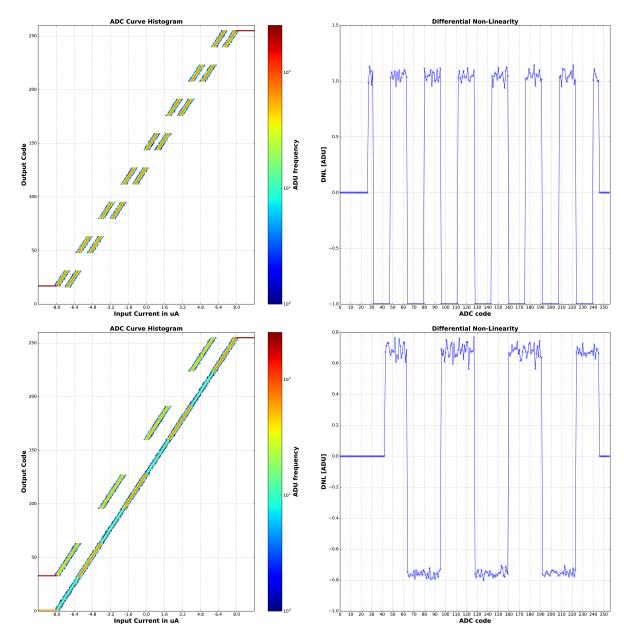

## 6.1.2 Noise and Linearity

The noise  $\sigma_i$  of the ADC curve at input current DAC *i* is defined as the standard deviation of the output codes at that DAC, it has units of ADU. As a measure for the noise of the ADC channel the median of all  $\sigma_i$  of the ADC curve is used. Of course, low noise performance is favoured. The noise measured via the ADC curve is the combined noise

Figure 6.1: Simulated ADC curve with a reduced dynamic range resulting when the CMCs dynamic ranges of stage 0 are reduced to  $[-6, 8] \mu A$ .

of several sources:

- the current source noise  $\sigma_{\text{source}}$ ,

- noise introduced by routing of the current  $\sigma_{\text{route}}$ ,

- noise introduced by the current receiver  $\sigma_{\text{TIA}}$ ,

- and the noise of the pipeline ADC  $\sigma_{ADC}$ , which in turn is a convolution of the noise of the current memory cells and the comparators.

Only when using an external current source, its noise can be measured separately. The individual noise sources of the analog channel cannot be disentangled easily with the Hybrid5 and EMCM setups. Previous measurements done by [13] show a significant noise contribution from the current memory cells and some contribution from the TIA.

The DCD-Bv4 reference manual states an expected average noise per ADC of around 80 nA and a maximal system noise of around 120 nA, this translates to a noise value of 1 - 2 ADU [15]. For evaluation of the quality of the ADC operation regarding noise, the ADC curve noise value is compared to a testing threshold, which is usually in the expected order of 1 - 2 ADU. If the noise exceeds the given threshold, a noise failure of the ADC is identified.

A high linearity of the ADC curve assures a constant digital resolution over the full dynamic input range of the ADC. As a single measure for the non-linearity of the ADC curve, the INL peak-to-peak (INLpp) value as defined in equation 3.3 is used. According to the DCD-Bv4 reference manual, an INLpp value of < 6 ADU is allowed for the ADC non-linearity [15]. By setting an appropriate testing threshold for the INLpp value, the ADC curves are tested for high non-linearities. If the INLpp value exceeds the threshold, an INLpp failure for the ADC curve is identified. The code range, noise and INLpp values can be considered the fundamental measures for evaluating the quality of an ADC curve. However, they do not provide detailed information on the malfunction of the ADC. By conducting simulation of the functionality of the pipeline ADCs used in the DCD, and the DCD-DHP communication, we are able to link specific ASIC failure scenarios to clearly identifiable topologies and patterns in the ADC curves. These will be discussed in the next sections.

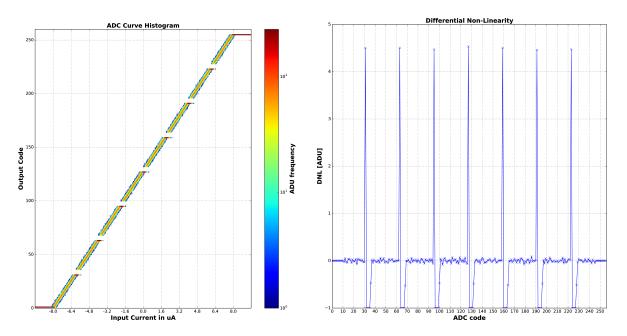

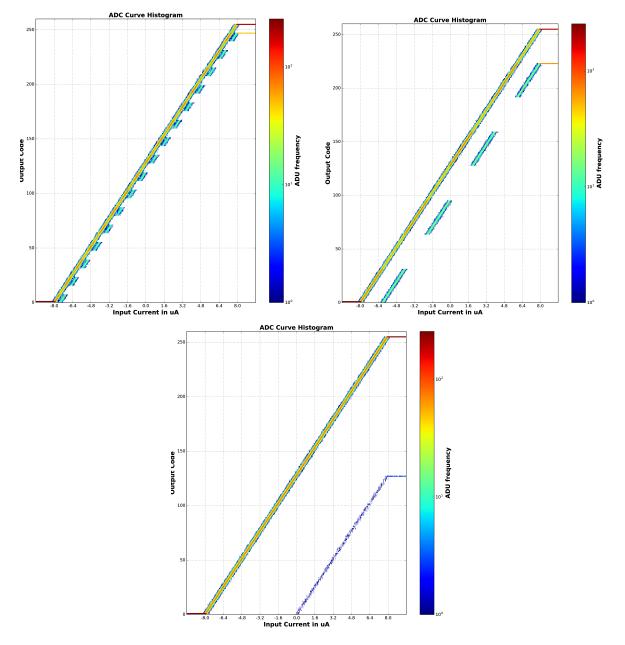

## 6.1.3 Comparator Offsets and Long Codes

Section 4.1 discussed the ideal analog-digital conversion of the pipeline ADCs. The conversion algorithm relies on the proper relation between the CMCs dynamic range, the values of the positive and negative comparator thresholds and the value of the added or subtracted reference current. The influence of non-optimal CMC dynamic ranges have already been discussed. The CMCs use the current defined by the DAC IPSource as the added/subtracted reference current. The comparators also make use of IPSource and derive the thresholds from it (see section 4.1.1). Thus, the reference current is properly defined by the DAC, while the thresholds can be subject to variations that arise due to mismatches of transistors that derive the thresholds from IPSource. Starting from the ideal input-output relation of one ADC stage (figure 4.1), let us consider the case of a small positive offset of the threshold of the high comparator of  $+1.8 \,\mu$ A. Figure 6.2 shows the input-output relation for this case, the positive threshold is at  $3.8 \,\mu$ A as opposed to the nominal  $2 \,\mu$ A. Figure 6.3 shows a simulated ADC curve where the high comparator in conversion stage 0 has an offset of  $+1.8 \,\mu$ A. Small positive offset ( $< 2 \,\mu$ A) does not seem to have any influence on the AD conversion, the ADC curve does not show any arte-

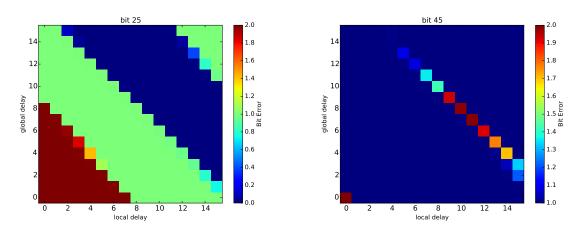

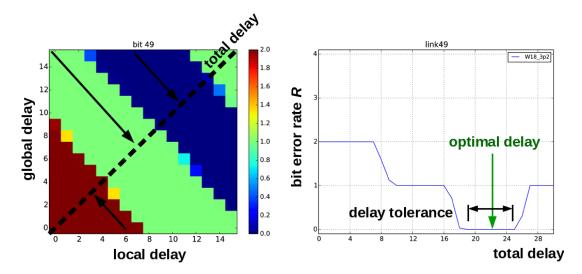

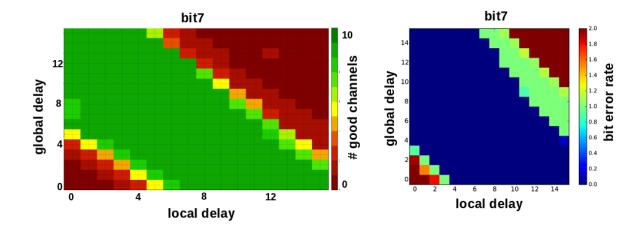

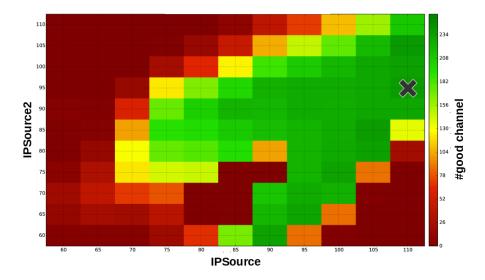

facts. This is true for any offset, positive or negative, of the high or the low comparator threshold, as long as the absolute value is  $< 2 \,\mu$ A. Thus, to some extend, the implemented AD conversion is robust with respect to small threshold shifts.