# OPTIMIZATION AND PERFORMANCE ANALYSIS OF THE COMMON READOUT UNIT FOR THE ALICE EXPERIMENT AT CERN

By SHUAIB AHMAD KHAN ENGG04201404004

Variable Energy Cyclotron Centre, Kolkata

A thesis Submitted to the Board of Studies in Engineering Sciences

In partial fulfillment of requirements for the Degree of DOCTOR OF PHILOSOPHY

of

HOMI BHABHA NATIONAL INSTITUTE

January, 2019

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at Homi Bhabha National Institute (HBNI) and is deposited in the Library to be made available to borrowers under rules of the HBNI.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgement of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the Competent Authority of HBNI when in his or her judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

Shuaib Ahmad Khan

(Shuaib Ahmad Khan)

## DECLARATION

I, hereby declare that the investigation presented in the thesis has been carried out by me. The work is original and has not been submitted earlier as a whole or in part for a degree / diploma at this or any other Institution / University.

Shuaib Ahmad than

(Shuaib Ahmad Khan)

## List of Publications

#### **Refereed Journal Publications**

1. "A potent approach for the development of FPGA based DAQ system for HEP experiments."

Shuaib Ahmad Khan, Jubin Mitra, Erno David, Tivadar Kiss and Tapan Kumar Nayak.

Journal of Instrumentation (2017) (an IOP and SISSA Journal) doi.org/10.1088/1748-0221/12/10/T10010 Vol. 12, 27 Oct. (2017).

"Optimization of multi-gigabit transceivers for high speed data communication links in HEP Experiments."

Shuaib Ahmad Khan, Jubin Mitra, Tushar kanti Das, Tapan K. Nayak.

Nuclear Instruments and Methods in Physics Research A: Accelerators,

Spectrometers, Detectors and Associated Equipment.(2019)

https://doi.org/10.1016/j.nima.2019.02.030

Volume 927, May 2019, Pages 14-23

3. "Trigger and timing distributions using the TTC-PON and GBT bridge connection in ALICE for the LHC Run 3 Upgrade."

Jubin Mitra, Erno David, Eduardo Mendez, **Shuaib Ahmad Khan**, Tivadar Kiss, Sophie Baron, Alex Kluge, Tapan Nayak.

Nuclear Instruments and Methods in Physics Research A: Accelerators, Spectrometers, Detectors and Associated Equipment.(2018)

https://doi.org/10.1016/j.nima.2018.12.076 Volume 922, April 2019, Pages 119-133

### Proceedings Published in Refereed Journal:

1. "Development of a high speed data acquisition system for the detectors at high luminosity LHC."

Shuaib Ahmad Khan, Jubin Mitra and Tapan K Nayak.

Published in Springer Proceedings in Physics, vol 203. Springer, Cham; 2018 page (223-226).

$https://doi.org/10.1007/978-3-319-73171-1\_50$

2. "GBT Link testing and performance measurement on PCIe40 and AMC40 custom design FPGA boards."

Jubin Mitra, **Shuaib Ahmad Khan**, Manoel Barros Marin, Jean-Pierre Cachemiche, Erno David, Frederic Hachon, Frederic Rethore, Tivadar Kiss, Sophie Baron, Alex Kluge and Tapan K. Nayak.

Published in Journal of Instrumentation, Volume 11, March 2016; IOP Publishing Ltd and Sissa Medialab srl.

doi.org/10.1088/1748-0221/11/03/C03039

3. "Common Readout Unit (CRU) - A new readout architecture for the ALICE experiment."

J. Mitra, S.A. Khan, S. Mukherjee and R. Paul.

Published in Journal of Instrumentation, Volume 11, March 2016; IOP Publishing Ltd and Sissa Medialab srl.

doi.org/10.1088/1748-0221/11/03/C03021

#### **Conference Proceedings**

- "Development status of Common Readout Unit at India for the ALICE detector at CERN.", Shuaib Ahmad Khan and Subhasis Chattopadhyay, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 63 (2018) page (1166-1167).

- "Implementation of I2C bus master controller for CRU Slow Control in ALICE at LHC.", Shuaib Ahmad Khan, Filippo Costa, Erno David, Jubin Mitra, Tivadar Kiss, S. Mukherjee, Rourab Paul, Tushar K. Das, A. Chakrabarti, Tapan K. Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 61 (2016) page (1070-1071).

- "GBT link testing and performance measurement on Altera Stratix-V FPGA.", Shuaib Ahmad Khan, Jubin Mitra, and Tapan Kumar Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 60 (2015) page 1052-1053

- "Common Readout Unit (CRU) A New Readout Architecture for the ALICE experiment at the CERN-LHC.", Shuaib Ahmad Khan, Jubin Mitra, Tapan Kumar Nayak, Tivadar Kiss, Erno David, and Alexander Kluge, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 59 (DEC 08-12, 2014) page 972-973

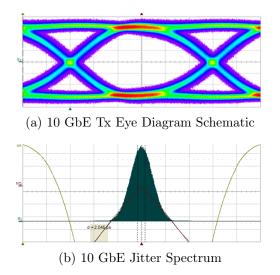

- 5. "Design and Simulation of 10 Gigabit Ethernet on Altera FPGA.", Shuaib Ahmad Khan, Jubin Mitra, Erno David, Tivadar Kiss, and Tapan Kumar Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 59 (DEC 08-12, 2014) page 974-975

- "Testing and Performance Analysis of 10 Gigabit Ethernet.", Shuaib Ahmad Khan, Jubin Mitra, Erno David, Tivadar Kiss, and Tapan Kumar Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 59 (DEC 08-12, 2014) page 884-885

- 7. "Common Readout System in ALICE.", J. Mitra, S.A. Khan, 7th International

Conference on Physics and Astrophysics of Quark Gluon Plasma 1-5 February, 2015, Published in PoS ICPAQGP2015 (2017) pp.098.

- 8. "Error Resilient Secure Multi-gigabit Optical Link Design for High Energy Physics Experiment.", Jubin Mitra, Shuaib Ahmad Khan, Rourab Paul, Sanjoy Mukherjee, Amlan Chakrabarti, Tapan Kumar Nayak, 29th International Conference on VLSI Design and 15th International Conference on Embedded Systems (VLSID) 2016; Published in IEEE xplore 2016, page (472-473). DOI: 10.1109/VLSID.2016.108

- 9. "An efficient approach to manage DMA descriptors and evaluate PCIe based DMA performance for ALICE Common Readout Unit(CRU).", S. Mukherjee, F. Costa, R. Paul, A. Chakrabarti, S. A. Khan, J. Mitra, T. Nayak, Advanced Detectors for Nuclear, High Energy and Astroparticle Physics 2017, Published in Springer Proceedings in Physics, vol 201. Springer, Singapore; 2018 page (107-118). doi.org/10.1007/978-981-10-7665-7\_10

- "Implementation and evaluation of custom logic for various configuration schemes based on I2C and HDLC protocol for ALICE Common Readout Unit(CRU).", S. Mukherjee, F. Costa, R. Paul, A. Chakrabarti, S. A. Khan, J. Mitra, T. Nayak, Advanced Detectors for Nuclear, High Energy and Astroparticle Physics 2017, Published in Springer Proceedings in Physics, vol 201. Springer, Singapore; 2018 page (217-222). doi.org/10.1007/978-981-10-7665-7\_23

- "Channel Processor in 2D Cluster Finding Algorithm for High Energy Physics Application.", Rourab Paul, Amlan Chakrabarti, Jubin Mitra, Shuaib A. Khan, Sanjoy Mukherjee, and Tapan Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 61 (2016) page (1046-1047)

- 12. "An efficient approach to evaluate PCIe DMA design and DMA performance for Com-

mon Readout Unit(CRU).", S. Mukherjee, Filippo Costa, Rourab Paul, A. Chakrabarti,

S. A. Khan, J. Mitra, T. Nayak, Proceedings of the DAE-BRNS Symp. on

Nucl. Phys. 61 (2016) page (1078-1079)

- "Electronic Data Aggregation Architecture for High Energy Physics Big data taking Experiments.", Jubin Mitra, Swagata Mandal, Shuaib Ahmad Khan, Jogender Saini, Subhashis Chattopadhyay, Tapan Kumar Nayak, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 61 (2016) page (1086-1087)

- 14. "Optimization methodology of high speed transceivers for interfaces in HEP Experiments.", Shuaib Ahmad Khan and Subhasis Chattopadhyay, Proceedings of the DAE-BRNS Symp. on Nucl. Phys. 64 (2019) (In Press).

- 15. "Unfolding design strategies and the critical aspects for development of DAQ at the HEP experiments.", Fahad khan, Eram Taslima, Atiya Fatima Usmani, Jubin Mitra, Shuaib Ahmad Khan, International Conference On Cutting-edge Technologies in Engineering 2019, IEEE Conference Record No. 47290, IEEE Digital Explore. (In Press)

- 16. "Design of FPGA based phase reconfiguration technique.", Atiya Fatima Usmani, Eram Taslima, Shuaib Ahmad Khan, 3rd International Conference on Electronics, Materials Engineering & Nano-Technology 2019, IEEE Digital Explore. (In Press)

#### **Internal Notes**

- GBT BER measurement and Transceiver Optimization. (Internal Note) Jubin Mitra, Shuaib Ahmad Khan twiki.cern.ch/twiki/pub/ALICE/CruFwGbt/GBT\_BER\_REPORT.pdf

- 2. GBT-FPGA Firmware Debug Report for Altera Stratix V. (Internal Note) Jubin Mitra, Shuaib Ahmad Khan

$twiki.cern.ch/twiki/pub/ALICE/CruFwGbt/GBT\_Report\_with\_appendix\_NEW.pdf$

- 3. GBT Implementation in Stratix-V FPGA on AMC40 board. (Internal Note) Jubin Mitra, Shuaib Ahmad Khan twiki.cern.ch/twiki/pub/ALICE/CruFwGbt/gbt\_work\_summary\_Nov2014.pdf

- Receiving and HW Testing of the PCIe40\_v1 CRU Cards. (ALICE Internal Note)

T. Kiss, E. David, F. Costa, V. Baid, S.A. Khan (ALICE), and K. Arnaud, J.-P. Cachemiche, P.-Y. Duval, F. Hachon, M. Jevaud, R. Le Gac and F. Rethore (LHCb)

Shuaib Ahmad Khan

( Shuaib Ahmad Khan )

In the name of Allah The Most Gracious and the Most Merciful

All Glory belongs to Him, He is The Most Exalted and The Most High

### ACKNOWLEDGEMENTS

My deep gratitude goes to (**Prof.**) **Dr. Tapan Kumar Nayak**, for his valuable guidance, supervision and constant encouragement through my doctoral research. His broad vision of knowledge, unwavering enthusiasm for physics and rising basic questions in the subject helped me to think progressively in this field. Working with him is a pleasant experience and nutured me to become a better human being.

I would like to thank the deepest appreciation to my PhD committee members for their valuable suggestions and critical comments provided during the annual progress review meetings. I am particularly grateful to **Dr. Subhasis Chattopadhyay** for his continuous support to continue my research work.

My sincere appreciation extends to my technical advisor **Dr. Alexander Kluge** and CRU technical co-ordinator **Tivadar Kiss** for their mentoring, encouragement and early insights into the research work. I tender my grateful thanks to the VECC colleagues Dr. Jubin Mitra, Dr. Swagata Mandal, Vinod Singh Negi, Vikas Singhal, Jogender Saini, Rama Narayana Singaraju, Partha Bhaskar, Dr. Zubayer Ahammed, Dr. Anand Dubey and Tushar K. Das, for nurturing my research acumen. I am thankful to Dr. Anuraag Misra and Dr. Saurabh Srivastava from VECC, Sanjoy Mukherjee, Dr. Supriya Das and Dr. Sidharth K. Prasad from Bose Institute, Dr. Rourab Paul and Dr. Amlan Chakraborty from University of Kolkata for numerous engineering and technical suggestions. I thank to all the staff members from VECC for their time, effort and encouragement from them. I am extremely grateful to my entire CRU team members due to whom this journey is made possible. As part of my research, I have worked in multiple laboratories, without whom my research work would not have matured. From CERN electronics team I would like to thank **Dr. Sophie Baron**; from CPPM lab **Jean** Pierre Cachemiche and his team members; from Wigner Research Institute Erno David, Josef Imrek and Dr. Filippo Costa from CERN DAQ team.

A special thanks to my parents for all their sacrifices and prayers that made me sustained thus far. I would also like to thank all of my friends who supported me in writing, and giving impetus to strive towards my goal.

# CONTENTS

| Conter | nts Page                                                                 | No.  |

|--------|--------------------------------------------------------------------------|------|

| CONT   | ENTS                                                                     | xiii |

| SUMN   | IARY                                                                     | xvii |

| LIST ( | OF FIGURES                                                               | xix  |

| LIST ( | OF TABLES                                                                | xxiv |

| Chapte | er 1: Introduction                                                       | 1    |

| 1.1    | Journey to high speed DAQ systems                                        | 3    |

| 1.2    | The Large Hadron Collider (LHC) at CERN                                  | 5    |

| 1.3    | The ALICE experiment at LHC                                              | 9    |

| 1.4    | Research Motivation                                                      | 10   |

| 1.5    | Scope of the thesis                                                      | 14   |

| 1.6    | Structure of the thesis                                                  | 14   |

| Chapte | er 2: The ALICE experiment and its upgrade                               | 17   |

| 2.1    | Introduction                                                             | 17   |

| 2.2    | The ALICE detector                                                       | 18   |

|        | 2.2.1 The present ALICE detector: before Long Shutdown-2                 | 18   |

|        | 2.2.2 ALICE Data Acquisition and computing for Run1 and Run2             | 29   |

| 2.3    | ALICE upgrade overview: Upgrade of sub-detectors and their readout elec- |      |

|        | tronics                                                                  | 31   |

| 2.4    | Upgrade of Data Acquisition methodology                                  | 34   |

|        | 2.4.1 Trigger system                                                     | 35   |

|        | 2.4.2   | Detector Data links                                              | 37 |

|--------|---------|------------------------------------------------------------------|----|

|        | 2.4.3   | Detector Data Readout Cards in ALICE                             | 37 |

| 2.5    | Comm    | non Readout Unit (CRU)                                           | 38 |

|        | 2.5.1   | ALICE Readout scheme using CRU                                   | 40 |

| 2.6    | Summ    | nary                                                             | 44 |

| Chapte | er 3:   | ALICE readout system and Common Readout Unit (CRU)               | 45 |

| 3.1    | Introd  | luction                                                          | 45 |

| 3.2    | CRU     | design strategy                                                  | 47 |

|        | 3.2.1   | Version A: CRU in the Cavern                                     | 48 |

|        | 3.2.2   | Version B: CRU in the Counting Room                              | 49 |

| 3.3    | Featur  | res and functionalities of CRU                                   | 50 |

| 3.4    | Interfa | aces of CRU: Different Interfaces used, its selection and survey | 53 |

|        | 3.4.1   | Detector side interface                                          | 53 |

|        | 3.4.2   | Server side Interface (aka DDL3)                                 | 55 |

|        | 3.4.3   | Trigger interface                                                | 57 |

| 3.5    | Select  | ion of FPGA and the CRU hardware                                 | 58 |

| 3.6    | CRU     | peculiarities, complexities and the resolution                   | 64 |

|        | 3.6.1   | Design requirements                                              | 64 |

|        | 3.6.2   | Hardware Complexity                                              | 65 |

| 3.7    | Summ    | nary                                                             | 68 |

| Chapte | er 4:   | Link characterization and the signal integrity analysis          | 71 |

| 4.1    | Introd  | luction                                                          | 71 |

| 4.2    | Reade   | out architecture and the interfaces                              | 72 |

| 4.3    | Front   | End Interface: GBT                                               | 74 |

|        | 4.3.1   | Design implementation on FPGA                                    | 76 |

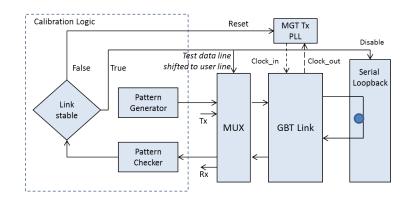

|        | 4.3.2   | Calibration logic                                                | 79 |

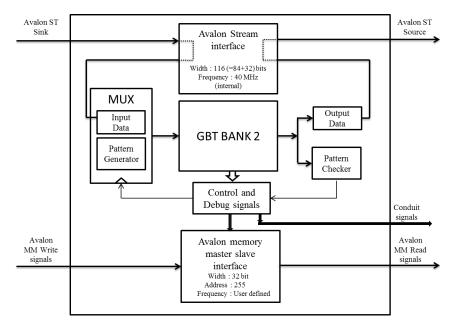

|        | 4.3.3   | GBT Qsys Model                                                   | 88 |

Page xiv

|                                                                             | 4.3.4                                                                                               | FPGA Resource utilization                                      | 88                                                                                                                                                                                  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                             | 4.3.5                                                                                               | Power Consumption                                              | 89                                                                                                                                                                                  |

|                                                                             | 4.3.6                                                                                               | Latency Measurement                                            | 90                                                                                                                                                                                  |

|                                                                             | 4.3.7                                                                                               | Eye diagram measurement                                        | 92                                                                                                                                                                                  |

|                                                                             | 4.3.8                                                                                               | BER analysis                                                   | 93                                                                                                                                                                                  |

| 4.4                                                                         | Back I                                                                                              | End Interface                                                  | 95                                                                                                                                                                                  |

|                                                                             | 4.4.1                                                                                               | Communication over the PCI Express interface                   | 95                                                                                                                                                                                  |

|                                                                             | 4.4.2                                                                                               | 10-Gigabit Ethernet                                            | 97                                                                                                                                                                                  |

|                                                                             | 4.4.3                                                                                               | Performance Evaluation                                         | 104                                                                                                                                                                                 |

| 4.5                                                                         | Avago                                                                                               | MiniPOD performance tests                                      | 108                                                                                                                                                                                 |

| 4.6                                                                         | Resour                                                                                              | rce Estimation                                                 | 109                                                                                                                                                                                 |

| 4.7                                                                         | Summ                                                                                                | ary                                                            | 109                                                                                                                                                                                 |

| Chapte                                                                      | er 5:                                                                                               | Optimization of multi-gigabit transceivers for high speed data |                                                                                                                                                                                     |

|                                                                             |                                                                                                     |                                                                |                                                                                                                                                                                     |

| commu                                                                       | inicatio                                                                                            | on links                                                       | 113                                                                                                                                                                                 |

| <b>commu</b><br>5.1                                                         |                                                                                                     | on links<br>uction                                             | _                                                                                                                                                                                   |

|                                                                             | Introd                                                                                              |                                                                | 113                                                                                                                                                                                 |

| 5.1                                                                         | Introd                                                                                              | uction                                                         | 113<br>114                                                                                                                                                                          |

| 5.1                                                                         | Introd<br>Transo<br>5.2.1                                                                           | uction                                                         | <ul><li>113</li><li>114</li><li>115</li></ul>                                                                                                                                       |

| 5.1<br>5.2                                                                  | Introd<br>Transc<br>5.2.1<br>Test se                                                                | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> </ol>                                                                                                                      |

| 5.1<br>5.2<br>5.3                                                           | Introd<br>Transc<br>5.2.1<br>Test se<br>Metho                                                       | uction                                                         | <ul><li>113</li><li>114</li><li>115</li><li>119</li><li>122</li></ul>                                                                                                               |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introd<br>Transc<br>5.2.1<br>Test se<br>Metho                                                       | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> </ol>                                                                                            |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introd<br>Transc<br>5.2.1<br>Test se<br>Metho<br>Result                                             | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> <li>125</li> </ol>                                                                               |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introd<br>Transo<br>5.2.1<br>Test so<br>Metho<br>Result<br>5.5.1                                    | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> <li>125</li> <li>125</li> </ol>                                                                  |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introd<br>Transc<br>5.2.1<br>Test so<br>Metho<br>Result<br>5.5.1<br>5.5.2<br>5.5.3                  | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> <li>125</li> <li>125</li> <li>125</li> <li>129</li> </ol>                                        |

| <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Introd<br>Transo<br>5.2.1<br>Test so<br>Metho<br>Result<br>5.5.1<br>5.5.2<br>5.5.3<br>Summ          | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> <li>125</li> <li>125</li> <li>125</li> <li>129</li> </ol>                                        |

| <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Introd<br>Transo<br>5.2.1<br>Test so<br>Metho<br>Result<br>5.5.1<br>5.5.2<br>5.5.3<br>Summ<br>er 6: | uction                                                         | <ol> <li>113</li> <li>114</li> <li>115</li> <li>119</li> <li>122</li> <li>125</li> <li>125</li> <li>125</li> <li>125</li> <li>125</li> <li>129</li> <li>133</li> <li>135</li> </ol> |

Page xv

| 6.3    | Functi | onal tests                                  | 140 |

|--------|--------|---------------------------------------------|-----|

|        | 6.3.1  | Basic Electrical Tests                      | 140 |

|        | 6.3.2  | Assembly of the power mezzanine cards       | 145 |

|        | 6.3.3  | Preparation for the Interface tests         | 146 |

|        | 6.3.4  | Configuration of the Card for the first use | 151 |

|        | 6.3.5  | Programming of the Arria 10 FPGA            | 153 |

|        | 6.3.6  | Hardware Tests                              | 154 |

| 6.4    | Summ   | ary                                         | 170 |

| Chapte | er 7:  | Summary and Future Scope                    | 171 |

| 7.1    | Summ   | ary                                         | 171 |

| 7.2    | Future | e scope                                     | 176 |

| REFEI  | RENC   | ES                                          | 179 |

# Summary

The ALICE experiment at the CERN Large Hadron Collider is devoted to the research in heavy-ion physics, where the goals are to study the formation of Quark-Gluon Plasma (QGP), a de-confined matter consisting of quarks and gluons. To extend the physics reach and to understand the QGP matter in greater detail, ALICE is upgrading the detectors for data taking in the year of 2021, where the beam luminosity for Pb-Pb will increase six times to  $6 \times 10^{27} cm^{-2} sec^{-1}$  at center-of-mass energy of 5.5 TeV. The increased interaction rates and the requirement of acquiring all the events information will result in an unprecedented dataflow of ~3 TB/sec from the detectors to the readout system. One of the major goals of the thesis is to design an efficient readout system to cope with the upsurge in data volume by acquiring data at a high rate and recovery from data error against the multi-bit upsets in radiation environments. A new FPGA based common readout unit (CRU) has been designed which acts as a coalesce between different interfaces and requires detector specific processing logic and firmware. The CRU receives data from the detector front-end electronics (FEE) boards located in the harsh radiation zone, performs online data processing and transfers to the back-end servers and storage located in the non-radiation areas.

As a part of the thesis work, optimization and performance analysis of the CRU in the context of the ALICE have been performed. The design aspects, principal tasks and complexities of the CRU have been discussed in detail. The prototype development of the CRU hardware has been illustrated and the detailed qualification tests are executed. The thesis presents performance analysis, evaluation of signal integrity and characterisation tests

#### Summary

on the high-speed interfaces. The measurements of resource utilisation, power consumption, critical path latencies, eye diagrams and bit error rate (BER) constitute the figures of merit for efficient system performance. Emphasis is given on the implementation and testing of the error-resilient 4.8 Gbps GBT links and its Qsys model for system integration is also proposed. Signal quality of the GBT core is characterised at the targeted BER of the order of 1 bit in  $10^{12}$  bits. Total jitter is in the range of picoseconds only. The margin of receiver sensitivity is found to be 2.1 dBm for the two encoding schemes of GBT. An approach to handle the requisites for the testing, performance monitoring and parameter tuning of optical interconnects in FPGA-based systems is presented. A strategy is designed and developed for the latency-optimized implementation of the link to align the phase of the clocks. CRUs are associated with high rates of data transmission. Hence, optimization methodology for multi-gigabit transceivers is designed and tested to address the challenges of the high-frequency losses during the data transfer. It is implemented on the state-ofthe-art 20nm Arria-10 FPGA manufactured by Intel Inc. The setup has been validated for three available high-speed data transmission protocols, namely, GBT, Timing-Trigger and Control over passive optical networks (TTC-PON) and 10-Gbps link. The improvement in the signal integrity is gauged by two metrics, the BER and the eye diagram. It is observed that the technique improves the signal integrity and reduces the BER.

The research and development summarized in the thesis is of high relevance for the firmware calibration and the hardware alignment purposes. The work could be further extended to design a load prediction model for efficient data distribution scheme and to architect a dynamic switching topology for the sudden rise of data volume.

# LIST OF FIGURES

| No.        | Title Page                                                              |    |

|------------|-------------------------------------------------------------------------|----|

| Figure 1.1 | Scheme for the succession of particle accelerators at the CERN acceler- |    |

| ator c     | omplex. The LHC ring is indicated along with four major experiments     |    |

|            | S, ALICE, CMS and LHC-b.                                                | 6  |

|            | Lattice layout of the LHC machine.                                      | 7  |

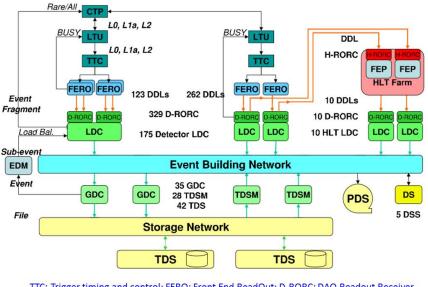

| Figure 2.1 | ALICE DAQ architecture for Run2 and the interface to the HLT system.    | 31 |

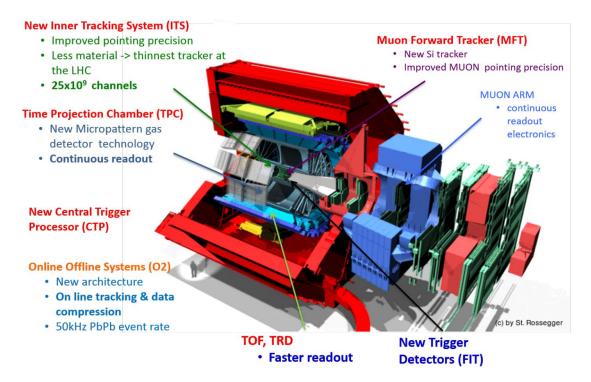

| Figure 2.2 | Scheme of the Major Sub-detectors of ALICE approved for upgrada-        |    |

| tion d     | uring the long shutdown2                                                | 32 |

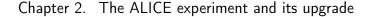

| Figure 2.3 | Data processing capability in the online systems                        | 39 |

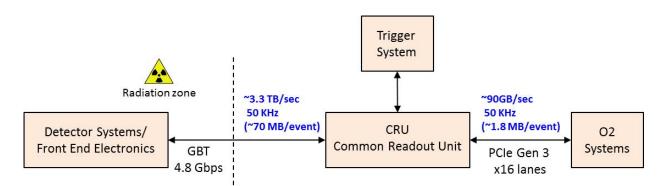

| Figure 2.4 | A system block diagram of ALICE readout scheme. Config I : CRU          |    |

| is use     | d as trigger distribution system and read-out processor. Config II :    |    |

| CRU        | is used as read-out processor. The trigger distribution is done from    |    |

| the C      | TP/LTU directly to the on-detector electronics. Config III : CRU is     |    |

| not us     | ed for the detectors do not upgrade their front-end electronics and use |    |

| detect     | or-specific read-out cards.                                             | 41 |

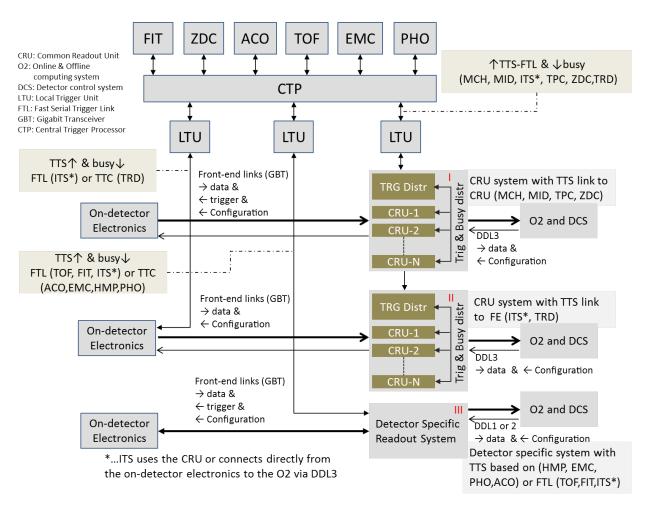

| Figure 2.5 | Flow of data in the ALICE from the detector front-end electronics up    |    |

| to the     | O2 system. (FLP: First Level Processor, EPN: Event Processing Node)     | 42 |

| Figure 3.1 | Implementation version A: CRU as FPGA boards in the cavern              | 48 |

| Figure 3.2 | Implementation version B: CRU as FPGA cards in the counting room.       | 49 |

| Figure 3.3 | PCIe40 - candidate board for CRU development                            | 63 |

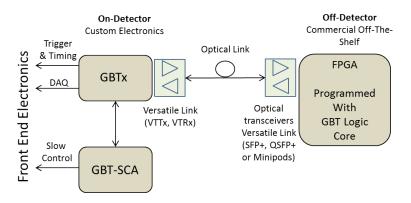

| Figure 4.1    | Figure 4.1 Different communication forms between the CRU, Trigger & FEE Link |    |  |  |  |

|---------------|------------------------------------------------------------------------------|----|--|--|--|

| archite       | ecture with the GBT ecosystem. (Courtesy: Erno David)                        | 73 |  |  |  |

| Figure 4.2    | Link architecture with the GBT ecosystem                                     | 74 |  |  |  |

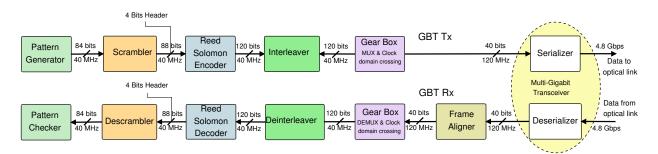

| Figure 4.3    | Block diagram of a GBT link in FPGA                                          | 75 |  |  |  |

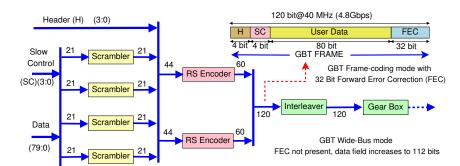

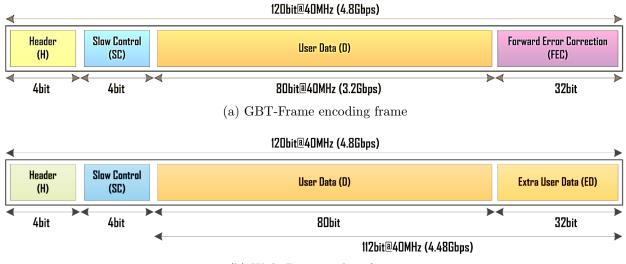

| Figure 4.4    | GBT link encoding scheme                                                     | 76 |  |  |  |

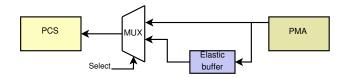

| Figure 4.5    | Clock phase compensation between PCS and PMA $\ \ldots \ \ldots \ \ldots$    | 78 |  |  |  |

| Figure 4.6    | Data format for GBT protocol.                                                | 78 |  |  |  |

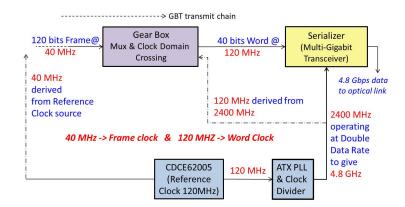

| Figure 4.7    | Clock Distribution Scheme for the Stratix-V FPGA                             | 79 |  |  |  |

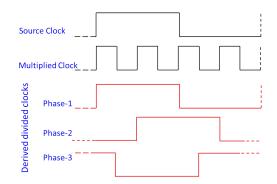

| Figure 4.8    | Multiplication or Division of Clock frequency                                | 80 |  |  |  |

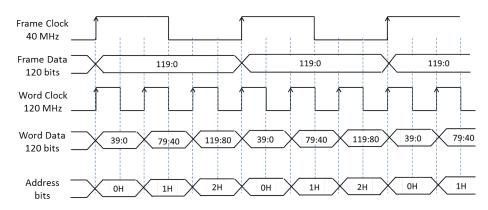

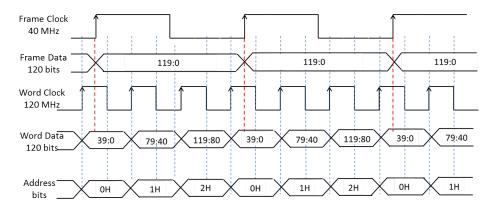

| Figure 4.9    | Word clock and Frame clock phase mismatch                                    | 81 |  |  |  |

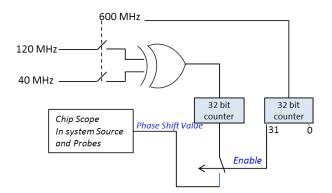

| Figure 4.10   | Logic for Phase Calculation.                                                 | 83 |  |  |  |

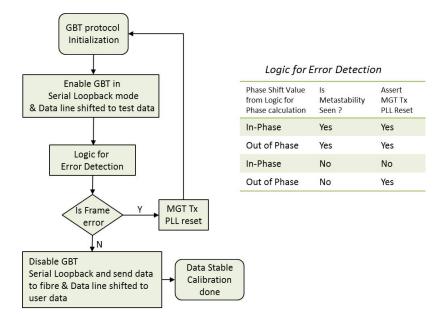

| Figure 4.11   | Phase Calibration logic.                                                     | 84 |  |  |  |

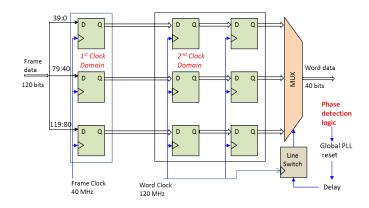

| Figure 4.12   | Synchronization Register Chain for Gearbox                                   | 85 |  |  |  |

| Figure 4.13   | State Machine for Phase Calibration                                          | 85 |  |  |  |

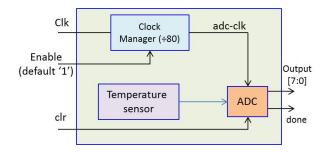

| Figure 4.14   | Temperature sensor IP core for Stratix-V                                     | 86 |  |  |  |

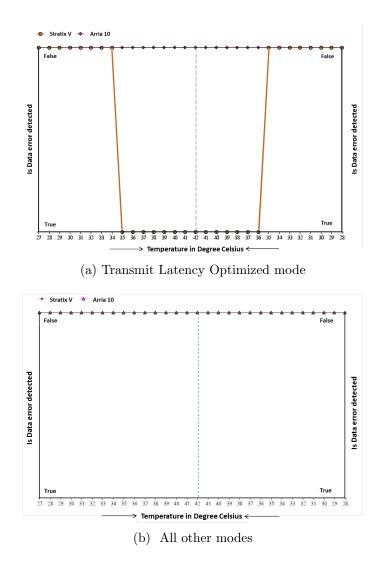

| Figure 4.15   | Showing the data stability vs temperature variation of two FPGAs             |    |  |  |  |

| when <b>(</b> | GBT operating in (a)Transmit Latency Optimized mode (b) All other            |    |  |  |  |

| modes         |                                                                              | 87 |  |  |  |

| Figure 4.16   | GBT Qsys Model                                                               | 88 |  |  |  |

| Figure 4.17   | Screen shot of the GUI for the Qsys model during run                         | 89 |  |  |  |

| Figure 4.18   | Test Setup for the GBT latency measurement                                   | 90 |  |  |  |

| Figure 4.19   | Test setup for BER measurement                                               | 93 |  |  |  |

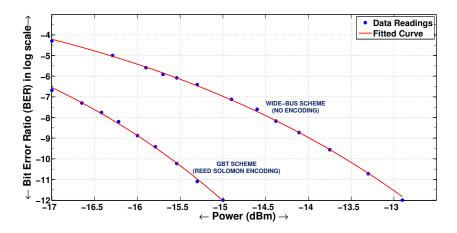

| Figure 4.20   | BER measurement for GBT Frame coding and GBT wide-Bus mode.                  | 94 |  |  |  |

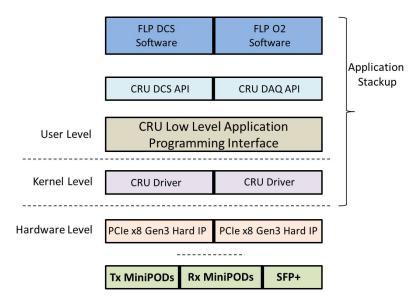

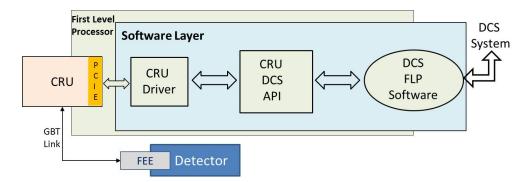

| Figure 4.21   | Figure 4.21 Overview of Software Stackup for CRU                             |    |  |  |  |

| Figure 4.22   | Figure 4.22 Overview of Software Stackup for CRU                             |    |  |  |  |

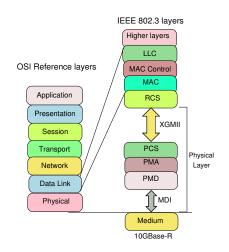

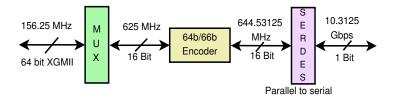

| Figure 4.23   | Position of 10GbE in OSI model.                                              | 98 |  |  |  |

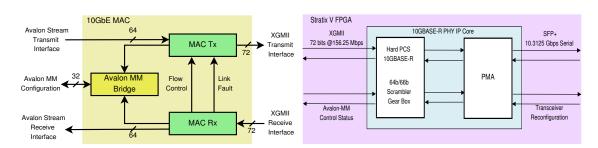

| Figure 4.24 (a)10GbE Intel MAC IP core block diagram (b) 10GBASE-R PHY                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| with Hard PCS and PMA in Intel devices                                                                                                                                            |

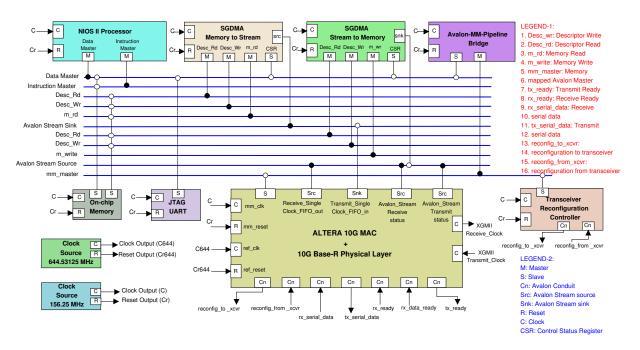

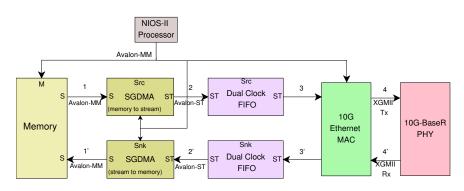

| Figure 4.25 Test system implementation using Qsys system integration tool 100                                                                                                     |

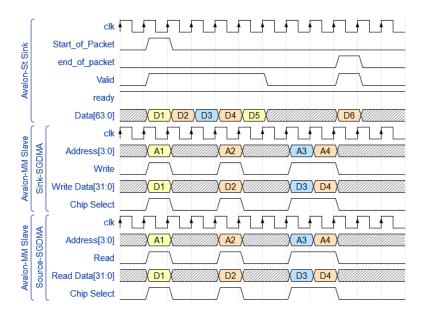

| Figure 4.26 Interface of Avalon-MM and Avalon-ST with source and sink SGDMA                                                                                                       |

| data transfer.                                                                                                                                                                    |

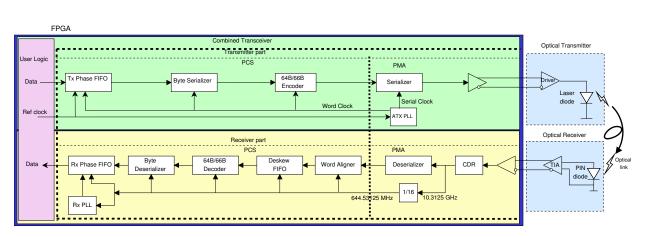

| Figure 4.27 User Logic                                                                                                                                                            |

| Figure 4.28 Simplified digital communication optical link                                                                                                                         |

| Figure 4.29 Three level of frequency translation in 10GbE communication 105                                                                                                       |

| Figure 4.30 MAC to XGMII data payload conversion scheme                                                                                                                           |

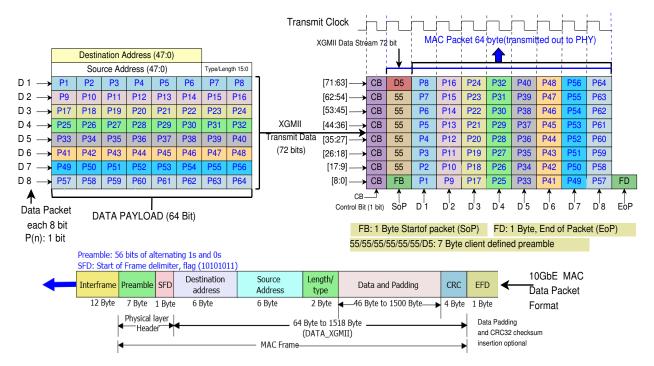

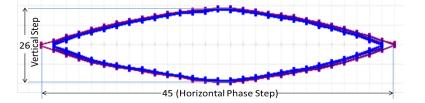

| Figure 4.31 Variation of Eye width and Eye Height with PRBS type 106                                                                                                              |

| Figure 4.32 Plot for tuning of transceiver parameter optimized settings at PRBS31.107                                                                                             |

| Figure 4.33 Eye Diagram for the 10Gb Ethernet on FPGA                                                                                                                             |

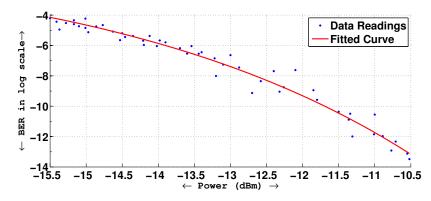

| Figure 4.34 Bit error rate as a function of received optical power at 10Gbps 108                                                                                                  |

| Figure 4.35 MiniPOD <sup>TM</sup> performance with 10 GbE protocol (10.312 Gbps) 108                                                                                              |

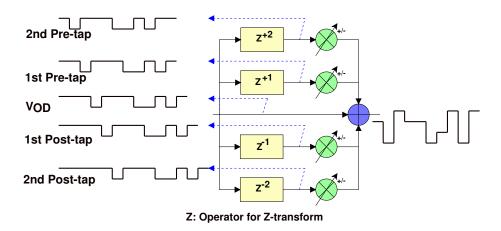

| Figure 5.1 Voltage output differential (VOD) and tunable pre-emphasis taps with                                                                                                   |

| flexible polarity in the embedded transceiver of FPGA                                                                                                                             |

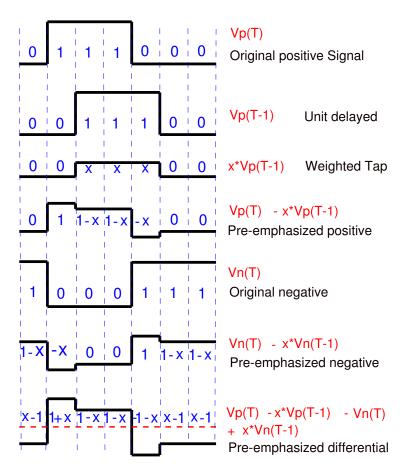

| Figure 5.2 The pre-emphasis signal generation technique at the 1st post-tap in                                                                                                    |

| embedded FPGA transceivers, $0 < x < 1$ is the tap weight                                                                                                                         |

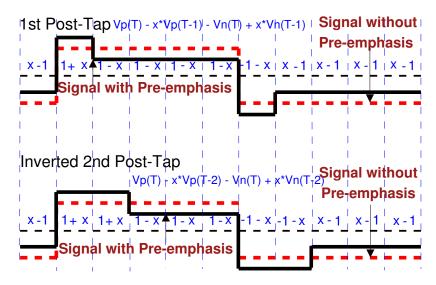

| Figure 5.3 Pre-emphasis 2nd post-tap (Inverted) compared with pre-emphasis 1st                                                                                                    |

| post-tap and their effect on the signal without pre-emphasis. $\dots \dots \dots$ |

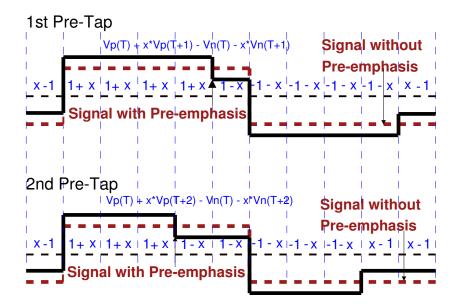

| Figure 5.4 Pre-emphasis 1st pre-tap and the 2nd pre-tap (Inverted) and their                                                                                                      |

| effect on the signal without pre-emphasis                                                                                                                                         |

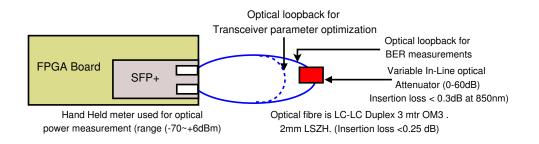

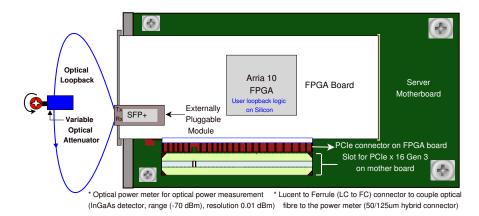

| Figure 5.5 Arria-10 FPGA card inserted in PCIe x16 slot of server. The opti-                                                                                                      |

| cal signal from the externally pluggable SFP+ is looped back via the fibre                                                                                                        |

| equipped with the variable optical attenuator (VOA).                                                                                                                              |

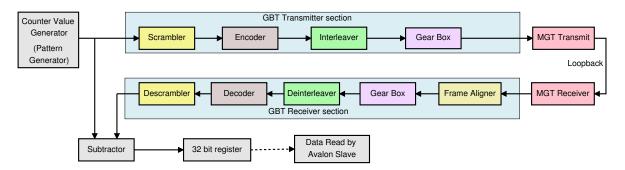

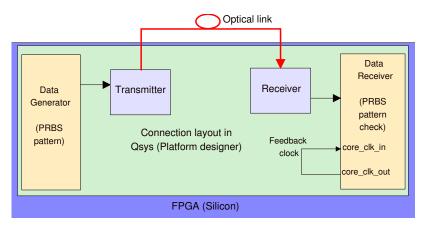

| Figure 5.6                                                                  | Typical BER test loopback logic on FPGA using Qsys tool. PRBS             |  |  |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| patterns are generated. The serialised data is transmitted, looped back and |                                                                           |  |  |  |

| checked for the flipped bits at the receiver                                |                                                                           |  |  |  |

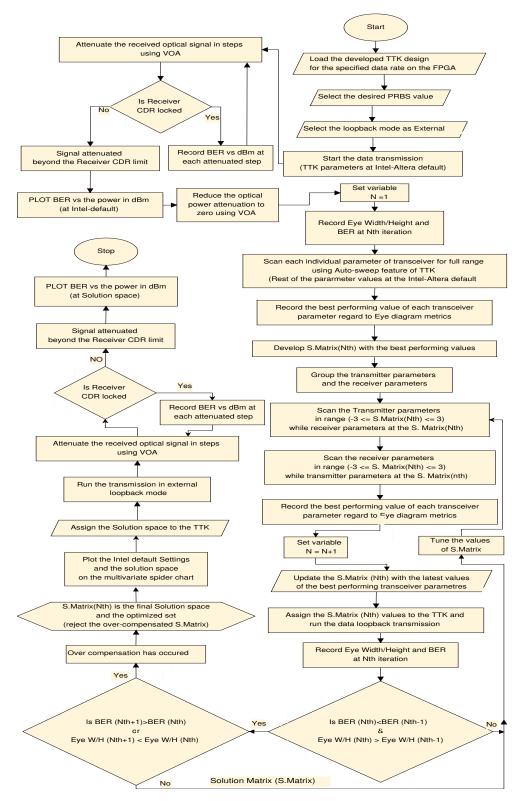

| Figure 5.7                                                                  | Stepwise flow diagram for the Transceiver Optimization. Data trans-       |  |  |  |

| mission                                                                     | n is started with the Intel default parameters and a Solution matrix is   |  |  |  |

| derived                                                                     | d to achieve the optimized signal integrity                               |  |  |  |

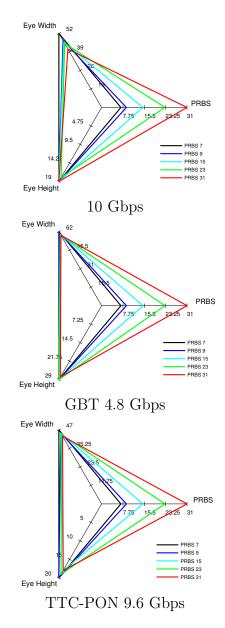

| Figure 5.8                                                                  | Changes in the Eye height and Eye width with PRBS variation for           |  |  |  |

| optical                                                                     | l links at three line rates                                               |  |  |  |

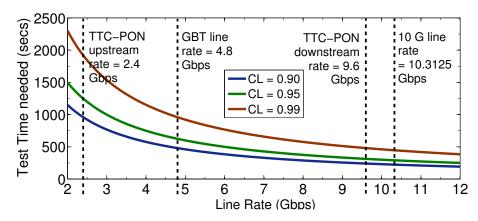

| Figure 5.9                                                                  | Time to achieve BER of $10^{-12}$ for the Line rate of GBT, TTC-PON       |  |  |  |

| and 10                                                                      | Gbps optical links having different CL                                    |  |  |  |

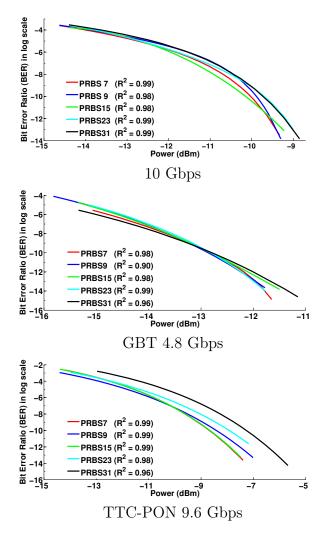

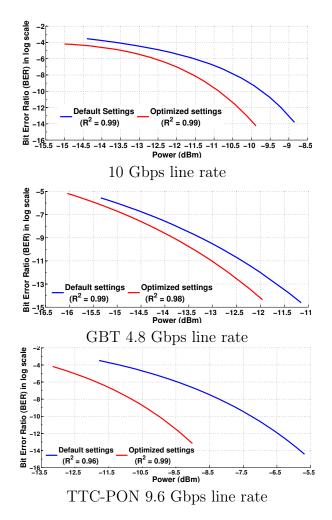

| Figure 5.10                                                                 | BER versus received optical power(dBm) for transceiver at Intel FPGA      |  |  |  |

| default                                                                     | t settings for different PRBS operating in three line rates               |  |  |  |

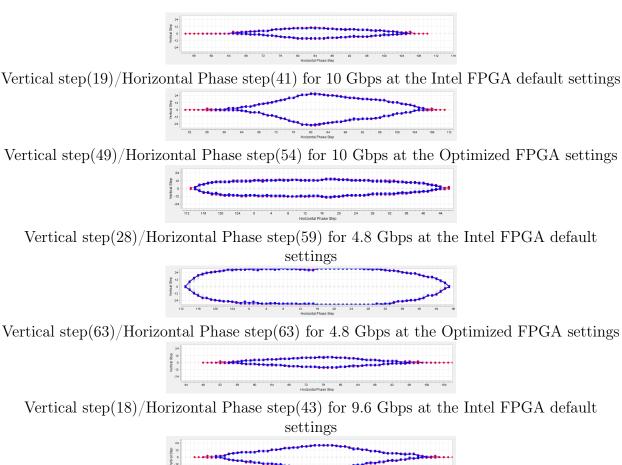

| Figure 5.11                                                                 | Eye diagram at the Intel FPGA default and at the Optimized settings       |  |  |  |

| of tran                                                                     | sceiver                                                                   |  |  |  |

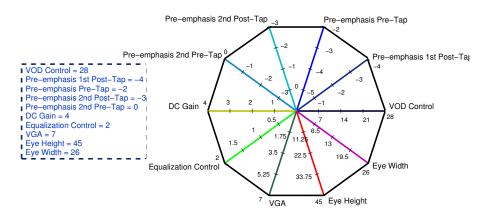

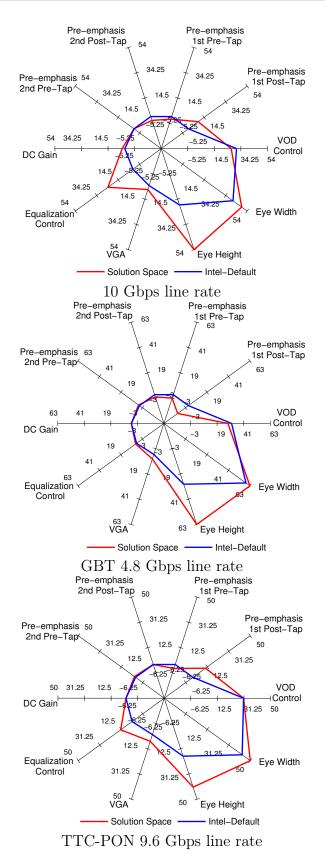

| Figure 5.12                                                                 | Multivariate kiviat diagram showing the solution space and the Intel      |  |  |  |

| FPGA                                                                        | default values for three different link rates                             |  |  |  |

| Figure 5.13                                                                 | Comparison of BER versus the received optical power for default and       |  |  |  |

| optimi                                                                      | zed transceiver settings separately for three line rates                  |  |  |  |

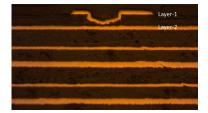

| Figure 6.1                                                                  | Showing an open circuit between layer 1 and layer 2                       |  |  |  |

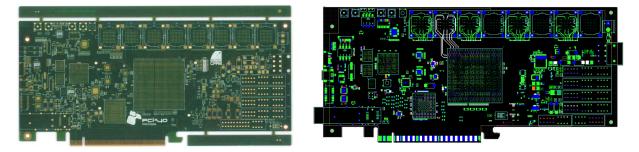

| Figure 6.2                                                                  | Bare board (Left) and its X Ray image (Right)                             |  |  |  |

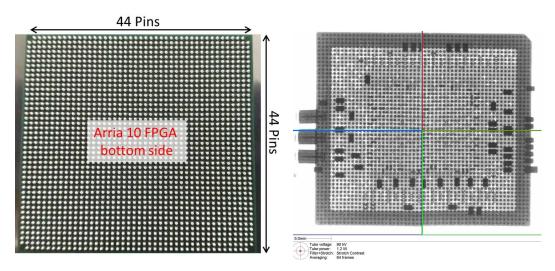

| Figure 6.3                                                                  | (Left) FPGA after solder balling (1932 pins) and (Right) 2D X-Ray         |  |  |  |

| image                                                                       | of the BGA package after mounting on PCB                                  |  |  |  |

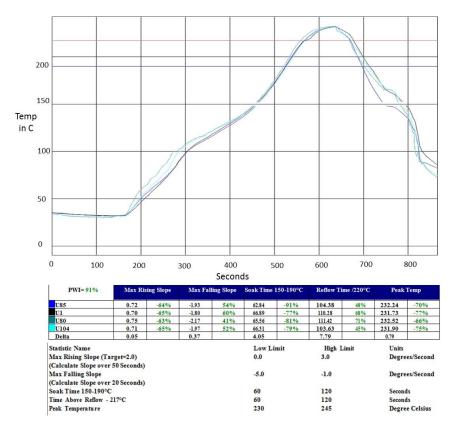

| Figure 6.4                                                                  | Thermal profile characteristics using the Oven VP800-64                   |  |  |  |

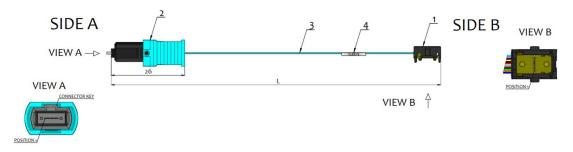

| Figure 6.5                                                                  | Shows the bare ribbon cable assembly drawing                              |  |  |  |

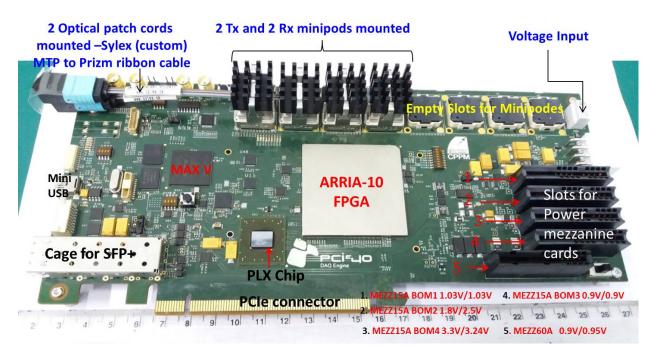

| Figure 6.6                                                                  | Shows the myopic view of the First prototype of the CRU card. $\dots$ 140 |  |  |  |

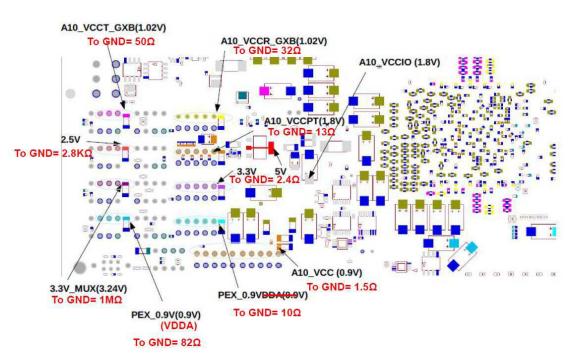

| Figure 6.7                                                                  | Map of test points for measurements of power rail shorts                  |  |  |  |

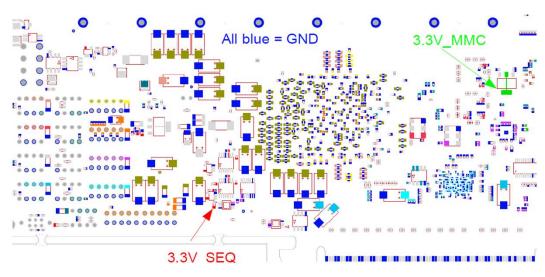

| Figure 6.8                                                                  | Measurement points for 3.3V_SEQ and 3.3V_MMC                              |  |  |  |

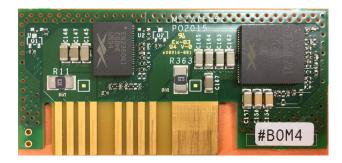

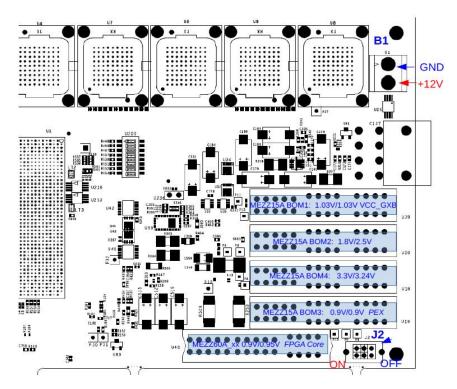

| Figure 6.9 MEZZ15A_6A power mezzanine module. Identical schematic for                 |

|---------------------------------------------------------------------------------------|

| Module-1, 2, 3 and 4                                                                  |

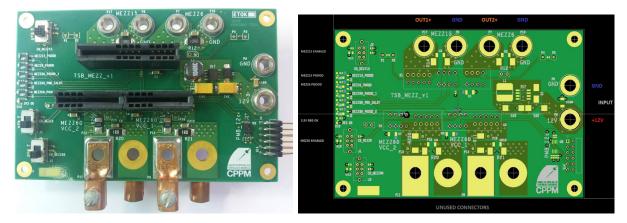

| Figure 6.10 MEZZ60A power mezzanine module-5, top side (left) and bottom side         |

| (right)                                                                               |

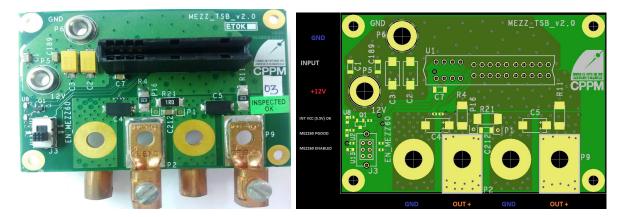

| Figure 6.11 $(Left)$ Test adapter for Module-1 to Module-4, $(Right)$ Schematic guide |

| for the test adapter                                                                  |

| Figure 6.12 (Left) Test adapter for Module-5, (Right) Schematic guide for the test    |

| adapter                                                                               |

| Figure 6.13 Mounting of the Power Mezzanine Cards (top side of PCIe40) 146            |

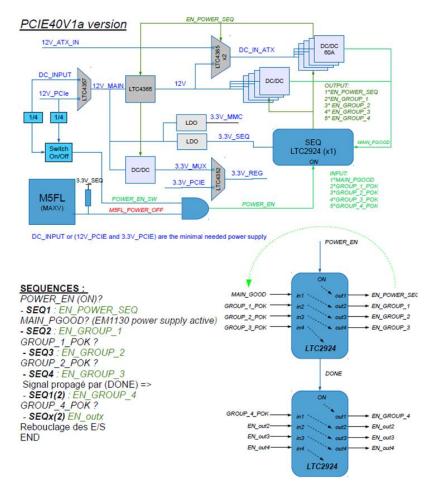

| Figure 6.14 Overview of the Power Sequencer                                           |

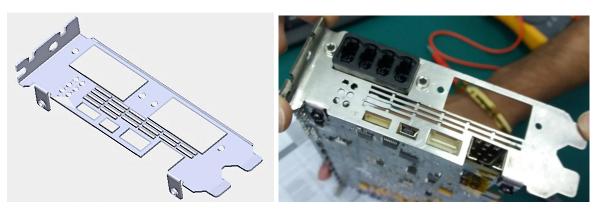

| Figure 6.15 (Left) CAD drawing of the Face-Plate developed using Wire Grid            |

| machine, (Right) Faceplate installed on PCIe40                                        |

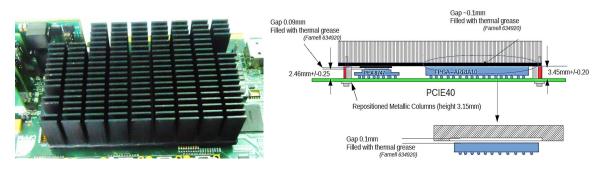

| Figure 6.16 $(Left)$ Heat Sink for Arria-10 installed on the board, (Right) Side View |

| showing the arrangement                                                               |

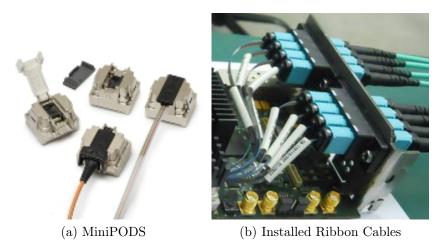

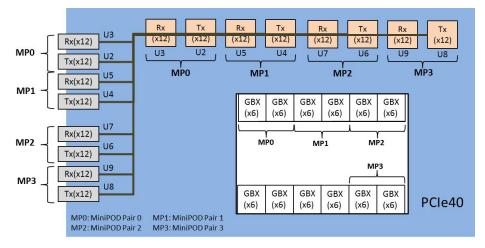

| Figure 6.17 MiniPODs and the on-board flexible ribbon cables                          |

| Figure 6.18 MiniPOD mapping                                                           |

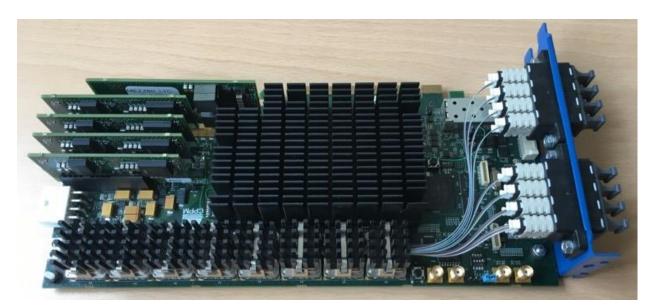

| Figure 6.19 Ready card with all accessories                                           |

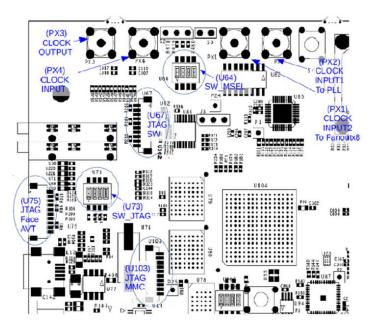

| Figure 6.20 Jumpers, Switches and Connectors Locations                                |

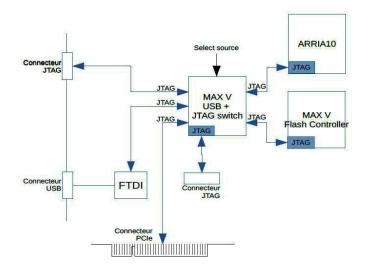

| Figure 6.21 PCIe40 JTAG Programming Scheme                                            |

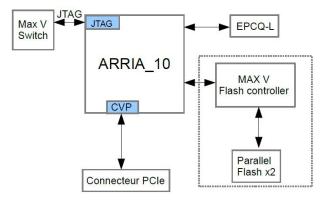

| Figure 6.22 Options for Programming of the Arria-10 FPGA                              |

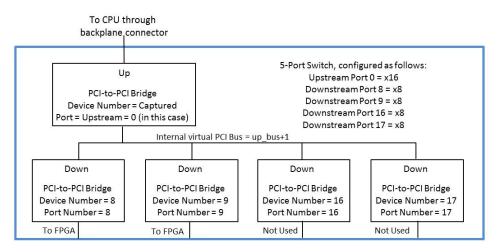

| Figure 6.23 Configuration of PLX-8747                                                 |

# LIST OF TABLES

| No.       | Title Page I                                                           | No. |

|-----------|------------------------------------------------------------------------|-----|

|           |                                                                        |     |

| Table 1.1 | Journey to high speed DAQ system                                       | 4   |

| Table 1.2 | Timelines for LHC operation                                            | 9   |

| Table 1.3 | An Overview of ALICE statistics before and after the scheduled upgrade | 12  |

| Table 2.1 | Trigger level in ALICE detectors                                       | 30  |

| Table 3.1 | Advantages of the Proposed approach over the Conventional approach     | 50  |

| Table 3.2 | CRU requirements in the system                                         | 52  |

| Table 3.3 | Comparison table between PCIe interface and 10 Gigabit Ethernet        |     |

| inter     | face                                                                   | 56  |

| Table 3.4 | Detailed comparison of the specifications of the high speed interface  |     |

| links     | used in high-energy physics experiments                                | 58  |

| Table 3.5 | FPGA selection parameters                                              | 59  |

| Table 3.6 | FPGA device and its family with maximum SerDes speed                   | 61  |

| Table 3.7 | Important Specifications of Arria-10 FPGA                              | 62  |

| Table 3.8 | CRU Hardware Complexities                                              | 66  |

| Table 4.1 | CRU requirements in the system                                         | 75  |

| Table 4.2 | FPGA resource utilization for the GBT-FPGA reference design            | 89  |

| Table 4.3 | Power consumption with the GBT Encoding Scheme                         | 90  |

| Table 4.4 | GBT link latency measurement.                                          | 91  |

| Table 4.5  | The comparison of the total path delay for AMC40 and PCIe40. $\ . \ . \ . \ 92$        |  |  |

|------------|----------------------------------------------------------------------------------------|--|--|

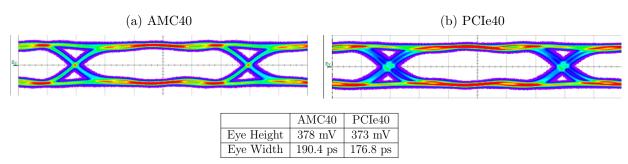

| Table 4.6  | Showing the Eye Diagram for GBT encoded data                                           |  |  |

| Table 4.7  | GBT Jitter Measurement for the two FPGAs                                               |  |  |

| Table 4.8  | FPGA resource utilization for the 10GbE design                                         |  |  |

| Table 4.9  | Latency estimation for data transfer<br>(1 clock cycle = 156.25MHz) 105                |  |  |

| Table 4.10 | Shows the comparison of $\mathrm{MiniPOD}^{TM}$ performance for GBT protocol           |  |  |

| and 1      | 0GbE Protocol                                                                          |  |  |

| Table 4.11 | An integrated design for elementary firmware including low level inter-                |  |  |

| faces.     |                                                                                        |  |  |

| Table 5.1  | Components used in the test setup, their role and specifications 120                   |  |  |

| Table 5.2  | Transceiver parameters, range of operations for the manual optimization.123            |  |  |

| Table 5.3  | Comparison of Optical power(dBm) to attain BER of $10^{-12}$ for the                   |  |  |

| three      | high speed interface links                                                             |  |  |

| Table 5.4  | Comparison of optical power for CDR for the three high speed interface                 |  |  |

| links.     |                                                                                        |  |  |

| Table 6.1  | Voltage levels from the power mezzanine modules                                        |  |  |

| Table 6.2  | Voltage values measured                                                                |  |  |

| Table 6.3  | JTAG switch settings (S = source, T = target) $\ldots \ldots \ldots \ldots \ldots 153$ |  |  |

| Table 6.4  | PCIe end point detection                                                               |  |  |

| Table 6.5  | PCIe end point detection                                                               |  |  |

# Chapter 1

# Introduction

Nuclear and particle physics experiments at high energies, often referred to as High Energy Physics (HEP) experiments, study the constituents of matter and their fundamental interactions. By colliding proton on proton or heavy-ions, such as, Au on Au or Pb on Pb at relativistic energies; one reproduces conditions that are prevalent within a microsecond after the birth of our universe. The evolution of our knowledge of the fundamental particles, their interactions as well as connections to the early Universe, has been proportional to the evolution of the available beam energies in the particle accelerators. The collisions produce zillion of highly energetic particles which are to be recorded by the experiments. The increase of collision energy and beam interaction rates demand for sophisticated and hightech detectors, electronics and data acquisition (DAQ) systems. In addition, the radiation levels in the proximity of the detectors have also been growing, which calls for radiation tolerant systems. The readout electronics in the harshly radiated area are highly prone to damage due to the total dose, single event upsets and non-ionizing energy loss [1] depending on the type of radiation. This poses various challenges for particle detectors, readout electronics, and DAQ systems. To cope with it, DAQ systems should have the ability to support high data rate, error resiliency against the multi-bit upsets in radiation environments, efficient data aggregation and processing schemes, easy reconfigurable with quick upgradation and compactness of hardware due to space constraints. The research and development presented in the thesis is based on the optimization and performance analysis of a completely new readout system, which will be capable of high data rate communication in context of the ALICE experiment at the Large Hadron Collider (LHC) at CERN.

CERN, the European Organization for Nuclear Research is the world's largest particle physics laboratory, founded in 1954 with twelve founder member states from Europe. Scientists from all over the globe contribute here to advance our knowledge about the past, present and future of the universe. CERN was one of the first European joint ventures. It has become a shining example of "*Physics for the benefit of mankind*"; collaborating with the nations that had once been against one another during the second world war. India has a special status of observer since 1991 and has been invited by CERN management to become an associate member of the organization in the year of 2016. Today, there are twenty-two member states (including India) and four associate members. India has played a significant role at CERN in terms of contribution for the building of Large Hadron Collider (LHC) as well as participation in the sophisticated experiments.

The LHC project is the latest and the largest particle accelerator in the world, commissioned in the year of 2008 [2]. It allows the scientists to comprehend the new chapters of the universe; explores the principle ingredients of matter that the universe was composed of at the time. At LHC, the two counter-rotating particle beams at ultrarelativistic energies, collide at four places known as interaction points. Complex detector systems are installed at each interaction point. A Large Ion Collider Experiment (ALICE) is one of the four major detectors at the LHC. It has been recording unprecedented amount of data for proton on proton and heavy ions since the beginning of the LHC program. ALICE is specifically designed for the study of heavy-ion collisions and the goal is to analyze the formation of Quark-Gluon Plasma (QGP). During the last ten years of its operation comprising of Run 1 and Run 2, ALICE has confirmed the formation of QGP and has given us a wealth of information regarding the system formed in the collisions. In order to extend the physics reach and to understand the QGP matter in greater detail, ALICE is upgrading the detectors for data taking in Run 3 foreseen in 2021. During Run 3, the beam luminosity for Pb-Pb will increase by six times viz.  $6 \times 10^{27} cm^{-2} sec^{-1}$  at center-ofmass energy of 5.5 TeV. The corresponding rate of interactions will also be increased from 8 KHz at present to 50 KHz. The high interaction rate and the requirement of acquiring all the events information will result in an unprecedented dataflow of ~3 TB/sec from the detectors to the readout system. This huge data will be experienced for the first time in the ALICE experiment. To handle the high volume of generated data an upgrade is required for the experiment. For this purpose; the upgrade of particle detectors, their readout electronics, and DAQ systems including data storage is planned. The upgrade approach for the data acquisition is based on a new Common Readout Unit (CRU) being developed. CRU for ALICE is the major thrust of the thesis. The thesis aims on the research and development for the challenging new readout system to handle high data rate. It also highlights the design of engineering solutions and methodologies developed during the R&D phase of CRU.

### 1.1 Journey to high speed DAQ systems

Traditional DAQ systems [3, 4] of the last century, could handle low data rate and less data errors against multi-bit upset in radiation zone. The modern DAQ systems for HEP and nuclear physics experiments is a result of continuous evolution [5]. The overview of the journey and the different methodologies adopted in the field of high speed DAQ are summarized in the Table 1.1.

In the early two decades of 1960-1980 the DAQ issues had been acknowledged by custom designed readouts that were framed after the characteristics of the individual experiments. Detectors have several tens to few hundred of readout channels with a readout rate of the order of megabyte per second only. They use non-standard interconnects. The introduction of Nuclear Instrumentation Module (NIM) standard and a modular computer-controlled

| Parameter      | 1960-1980                          | 1980-2000                  | 2000 onwards                          |

|----------------|------------------------------------|----------------------------|---------------------------------------|

| No. of Readout | ~100s                              | $\sim 10^3 - 10^6$         | $\sim 10^6 - 10^9$                    |

| Channels       |                                    |                            |                                       |

| Data Rate      | $\sim 1 \text{ MB/sec}$            | $\sim 1 \text{ GB/sec}$    | ${\sim}10~{\rm GB/sec}$ to few TB/sec |

| Readout        | Front End Electronics              | Parallelism feature of     | Heterogeneous                         |

| Standard       | Non standardized                   | distributed computing      | Computing                             |

| Technology     | 1964: NIM standard                 | 1986: FastBus              | Point to point High                   |

| Evolution      | (backplane bus not                 | BW: $40-60 \text{ MB/sec}$ | speed links                           |

| (Year Wise)    | defined)                           | Support parallelism        | <b>2003:</b> PC based                 |

|                | 1969: CAMAC based                  | 1982-1987: VME             | computing farms with                  |

|                | centralized backplane,             | development with           | Ethernet and PCIe bus                 |

|                | but lacked parallelism,            | microprocessors.           | <b>Present:</b> upto 400Gbps          |

|                | BW limited to $1 \text{ MB/sec}$ , | BW: $40 \text{ MB/sec}$    | Ethernet, PCIe 5.0                    |

|                | <b>1970-1980:</b> NIM based        | <b>1990:</b> NIM, CAMAC,   | specifications released               |

|                | Front End read by                  | Fastbus and VME            | in June 2017. Boosting                |

|                | minicomputer and                   | coexisted                  | on-board and local                    |

|                | CAMAC readout bus                  | <b>1997</b> : VME320 with  | processing with FPGAs                 |

|                |                                    | BW: $320 \text{ MB/sec}$   |                                       |

| Example        | Experiments at                     | Experiments at             | Experiments at                        |

| System         | TRIUMF, BNL                        | SPS, LEP at CERN           | CERN LHC                              |

Table 1.1: Journey to high speed DAQ system

bus named Computer Automated Measurement and Control (CAMAC) focused on the standardisation of front end and back end respectively. However this lacked parallelism with limited data rate and channel count. In the decades of 1980-2000, Fast-Bus standard supported parallelism but the advent of microprocessors leads to the Versa Module European (VME) standard and VME Inter-Crate bus specifications (VIC). The NIM, CAMAC, Fast-Bus and VME coexisted to address the challenges of HEP experiments. In the current century point to point high speed links are evolved, specifications for Ethernet and Peripheral Component Interconnect Express (PCIe) protocol are continuously expanded. With the advent of highly dense latest Field Programmable Gate Arrays (FPGAs), we are heading towards the data rates of Terabytes/sec with high channel count and on-board and local processing.

One of the examples of the demand for modern DAQ systems is at CERN's LHC, operate detectors up to billions of electronics channels. An efficient system is required at the present time to handle the key issues in the design of DAQ for HEP experiments like collecting the data at high rate and channel count with error resilience against the multi-bit upsets in the harsh radiation environment. Before proceeding to the details of the new readout system, it is worthwhile to outline the LHC at CERN, the requirements at the LHC and the design criteria.

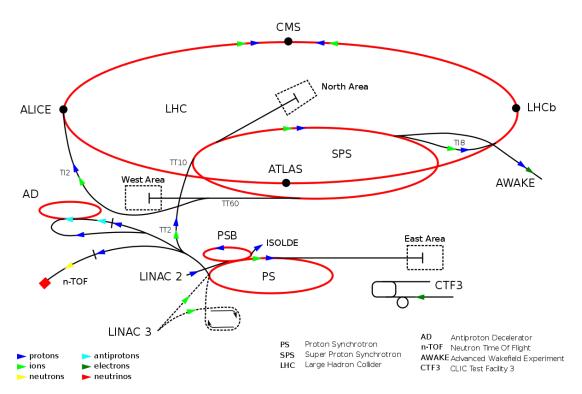

## 1.2 The Large Hadron Collider (LHC) at CERN

CERN has always remained at the cutting edge in the accelerator, detector, electronics and computing technology along with an objective to pursue the nuclear research of scientific and fundamental character. At present, the CERN accelerator complex is a systematic progression of particle accelerators to attain an ultra-relativistic velocity with very high energy [6]. Each accelerator boosts the speed of particles in the beam, before injecting into the next one in the process. The final destination is the LHC as shown in Figure 1.1. It accelerates the particles at a record energy of 7 TeV. To consolidate the journey of CERN's accelerators; a 600 MeV synchrocyclotron was commissioned in the year of 1957. In 1971, the Intersecting Storage Ring (ISR) was commenced which is the world's first proton-proton collider. In the year of 1974, the Super Proton Synchrotron (SPS) was developed, caged in a tunnel of 7 km of circumference. SPS has been the dynamo of CERN's particle physics program and continued to deliver beams for the LHC. The notable highlights of the LHC machine, experiments and the subsystems are briefly summarized in the context of the present dissertation.

LHC is one of the most ambitious mega-science projects ever undertaken; established on the Franco-Swiss border at the Geneva country side. It is installed in a tunnel of 26.7 km of circumference situated up to a depth of 170 m below the Alps and Jura mountain ranges. LHC is a superconducting hadron accelerator and collider with two parallel aligned circular beamlines (or beam pipes). The beamlines contain particle beams counter-rotating in circular trajectories around the ring. The particle beams consist of lead nuclei, proton,

Figure 1.1: Scheme for the succession of particle accelerators at the CERN accelerator complex. The LHC ring is indicated along with four major experiments ATLAS, ALICE, CMS and LHC-b.

or proton and lead nuclei. Protons are obtained for the LHC by removing electrons from hydrogen atoms and Lead ions (Pb) from a source of vaporized lead.

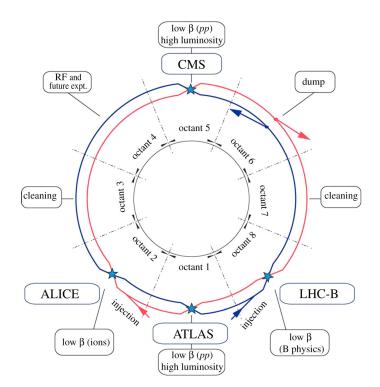

A beam is formed of hundreds of particle bunches. A bunch is composed of about 10<sup>11</sup> protons. The bunches in a beam cross every 25ns, this leads to around 600 million collisions each second. Most of the protons do not collide due to low cross section and continue to move. The beam size is squeezed down to 64 microns at the interaction points to enhance the probability of collision. The beams continue to circulate for hours; and the filling of beams in the LHC require several cycling time before it attains the full targeted energy. LHC uses magnetic fields to contain the particles in well-defined beams and electric fields to accelerate the charged particles up to almost the speed of light. The accelerated beams collide at four places known as interaction points where complex detector systems namely, A Toroidal LHC ApparatuS (ATLAS) [7], Compact Muon Solenoid (CMS) [8], A Large Ion Collider Experiment (ALICE) [9] and Large Hadron Collider Beauty (LHC-b) [10] are installed as

shown in Figure 1.2. Interactions at the crossing points are referred as events. Discovering

Figure 1.2: Lattice layout of the LHC machine.

the Higgs bosons has been the main goal behind building the LHC. In addition, search for the super-symmetric partners of known particles, verifying string theory predictions of extradimension, search and study of the primordial state of matter in the form of QGP, matter and anti-matter asymmetry in the universe and understanding dark matter and dark energy have been on the top of the LHC's agenda of physics topics. The ATLAS and CMS are two large experiments diametrically opposite in pits 1 and 5, respectively. These two protonproton experiments are dedicated for new physics searches and the precision measurements. The ALICE in pit 2 is a dedicated heavy ion physics experiment to search and study the formation of QGP matter, a de-confined matter consisting of quarks and gluons. Whereas the LHC-b in pit 8 is dedicated for the search behind matter and anti-matter asymmetry and other rare phenomenon in the decay of *Beauty particles*.

In the high-energy accelerators like the LHC, particles reach very close to the speed of light. At the LHC; particles revolve at 0.999999991 times the speed of light at top energy of

7 TeV [11]. In these situations; the increase in the speed of the particle is minimal with the increase of energy, instead there is a gain of the relativistic mass. Therefore, particle physics is dealt in terms of the particle's energy, rather than its speed. In a collider experiment, the energy of the collision, known as centre-of-mass energy is the sum of the energies of two colliding particle beams. Interactions at the crossing points are referred as events. The number of events generated per second viz. interaction rate (R) in a LHC collision is proportional to the cross section  $\sigma_{event}$  for the event as shown in equation (1.1). The constant of proportionality is known as Luminosity(L).

$$\mathcal{R} = L\sigma_{event} \tag{1.1}$$

The beam profile has a Gaussian distribution and the luminosity decays with the degradation in the circulating beams. Hence, the parameter, Integrated Luminosity is used to accumulate up the luminosity over a run. LHC is designed to collide proton beams with a centre of mass energy ( $\sqrt{s}$ ) of 14 TeV (7 TeV each beam) and at an unprecedented luminosity of  $10^{34} cm^{-2} s^{-1}$ . It can also accelerate and collide heavy lead ions (Pb-ions) with an energy of 2.75 TeV per nucleon centre-of-mass energy ( $\sqrt{s_{NN}}$ ) of 5.5 TeV at a peak luminosity of  $10^{27} cm^{-2} s^{-1}$  [2].

The HEP experiments at CERN's LHC system are operative since the year 2009 to deduce the missing fragments in the current description of the fundamental structure of matter [12, 13]. The first phase (Run1) of data collection is concluded, and the next phase (Run2) will be completed by 2018. To sustain and coup the full discovery potential of the experiment [14]; a major progressive upgrade is planned for the third phase (Run3) of LHC running. Run3 will start from the year of 2021 followed by a High-Luminosity Large Hadron Collider (HL-LHC) in the year 2025. The LHC timelines are summarized in the Table 1.2. Under this road-map for the upgrade strategy; the LHC will progressively increase its luminosity and hence the collision rate. The integrated luminosity is aimed to

| LHC Timelines |             |     |             |

|---------------|-------------|-----|-------------|

| Run1          | 2009 - 2012 | LS1 | 2013 - 2014 |

| Run2          | 2015 - 2018 | LS2 | 2019 - 2020 |

| Run3          | 2021 - 2023 | LS3 | 2024 - 2025 |

| Run4          | 2025 - 2029 | LS4 | 2030        |

| (HL-LHC)      | 2023 - 2029 | L04 | 2030        |

| and further   |             |     |             |

Table 1.2: Timelines for LHC operation

increase by a factor of ten times more than the initial design value by the year 2030. These large event statistics will help for the analysis of the rare events.

The increase in the interaction rates due to the increase in the luminosity will result in a high volume of data flow. It is of the order of few TB per second from the detector systems to the Data Acquisition system. To handle the high data rate, there is a need for the upgrade of different detector subsystems, electronics and readout, and the data acquisition systems. There are different detectors at LHC viz. ATLAS, CMS, ALICE and LHC-b; each experiment has its own physics motivation and the behaviour of data flow [2]. Consequently, to tackle the upgrades, the experiments at LHC need efficient parallelized readout schemes with high-tech electronics and DAQ techniques to apprehend the unparalleled amount of produced data. The thesis is oriented towards the upgrade of ALICE experiment, focussing on the CRU. CRU helps to handle the high data rate and an integral part of the ALICE DAQ upgrade.

### 1.3 The ALICE experiment at LHC

A Large Ion Collider Experiment (ALICE) is one of the four major detectors at the LHC and devoted to the study of heavy-ion collisions. The goal is to address the physics of strongly interacting matter, in particular, the formation of QGP at extreme values of energy density and temperature in nucleus-nucleus collisions. ALICE will also address several topics of quantum chromodynamics (QCD); the theory of the strong interaction between quarks and gluons, for which ALICE is complementary to other LHC detectors using the study of proton-proton collisions. In addition, the proton data will be used as a reference data for the heavy-ion-program. A detailed study of the hadrons, electrons, muons and photons produced in the collision of heavy nuclei are the main observables. The ALICE detector has been completed by a collaboration including over thousand physicists and engineers from several institutes. The experiment consists of various sub-detector systems arranged in cylindrical shells around the interaction point as well as in the forward directions. It is a challenge for the experiment to detect majority of the several thousands of particles produced in nuclear collisions with high precision. Different detector subsystems are installed in the experiment to identify different types of particles. The sub-detectors at ALICE are grouped into three sections viz. the central Barrel detectors, the muon spectrometer and the forward detectors. Each detector has its own design constraints and specific choice of technology motivated both by the physics aspects and the experimental conditions expected at LHC. Overall dimensions of ALICE are  $16x16x26m^3$  with a total weight of approximately ten thousand tonnes.

During last ten years of operation of ALICE, two phase of data collection, Run-1 and Run-2 are completed by 2018. By analysing data from a large number of collisions or events, ALICE has confirmed the formation of QGP and has given us a wealth of information regarding the system formed in the collisions. The third phase (Run3) of LHC running is foreseen to start from the year of 2021 with increased beam energy and luminosity after the shut down of two years scheduled from the year of 2019 [15].

### 1.4 Research Motivation

Before proceeding to the details of the new readout system, it is worthwhile to outline the requirements at the ALICE and the design criteria which motivated for the upgrade. During the LHC operations in Run-1 and Run-2 till the year 2018, it had provided proton-

Page 10

proton collisions at maximum centre of mass energy of 13 TeV, Pb-Pb collisions at 5 TeV. In addition, LHC had proton on lead and Xenon on Xenon collisions. The Run 3 of LHC after Long Shutdown2 (LS2) will start in the year 2021 with increased beam energy (proton-proton at 14 TeV and Pb-Pb at 5.5 TeV) as well as increased beam luminosity. The luminosities for Pb-Pb collisions will be increased progressively from  $1x10^{27}cm^{-2}s^{-1}$  to  $6x10^{27}cm^{-2}s^{-1}$ at center-of-mass energy of 5.5 TeV. The corresponding rate of interactions will also be increased from 8 KHz at present to 50 KHz. To cope-up with the high data rates, ALICE experiment plans for a major upgrade during LS2. During this upgrade of the detectors, their readout electronics need to be upgraded, and a new data acquisition approach based on Common Readout Unit (CRU) is being developed [16]. Research and development of the challenging new readout system to handle high data rate is the major thrust of the thesis.

ALICE had collected  $1nb^{-1}$  Pb-Pb collisions before LS2 at peak instantaneous luminosities of  $1x10^{27}cm^{-2}s^{-1}$  analogous to the collision rate of 8 KHz. The maximum readout rate of the present ALICE detector is 500 Hz of Pb-Pb events. ALICE upgrade strategy is based on collecting full detector information i.e data from each collision. Data will be transferred to the DAQ system in a self-triggered mode or upon a minimum bias trigger. The specifications for the ALICE detector upgrade is set by the collision rate of 50 kHz for Pb-Pb and 200 kHz for pp and p-Pb collisions. ALICE will collect greater than  $10nb^{-1}$  of Pb-Pb ion collisions at L upto  $6x10^{27}cm^{-2}s^{-1}$  corresponding to the collision rates of 50 KHz. It will also collect  $6pb^{-1}$  of p-p ion collisions at the equivalent Pb-Pb nucleon energy and  $50nb^{-1}$ of p-Pb collisions, both at a levelled collision rate of 200 KHz. The running scenario of the ALICE detector before and after the LS2 are summarized in Table 1.3

Motivated by the past operation experiences and successful physics results, R&Ds for the ALICE upgrade have started. The physics of the upgrade is intended at precision measurement of the QGP, which will be accessible through measurements of heavy-flavour transport parameters, quarkonia down to zero transverse momentum and low mass di-leptons. These processes do not exhibit signatures that can be chosen by hardware triggers, they can only

Chapter 1

| Parameter             |         | ALICE (Run-2)             | ALICE(Run-3)                                                  |  |  |

|-----------------------|---------|---------------------------|---------------------------------------------------------------|--|--|

| Luminosity (L)        | (Pb-Pb) | $1x10^{27}cm^{-2}s^{-1}$  | $6x10^{27}cm^{-2}s^{-1}$                                      |  |  |

|                       | (p-p)   | $10x10^{34}cm^{-2}s^{-1}$ | $5x10^{34}cm^{-2}s^{-1}$                                      |  |  |

| Collison Rate (       | R )     | 8 KHz (Pb-Pb)             | 50 KHz (Pb-Pb)                                                |  |  |

| Integrated Luminosity |         | $1nb^{-1}$ (Pb-Pb)        | $>10nb^{-1}$ (Pb-Pb)<br>$>6pb^{-1}$ (p-p), $50pb^{-1}$ (p-pb) |  |  |

| Max Readout r         | rate    | 50  kHz (Pb-Pb)           | 200 kHz (p-p and p-pb)                                        |  |  |

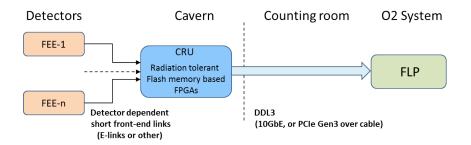

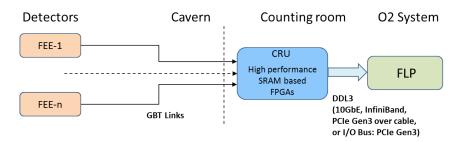

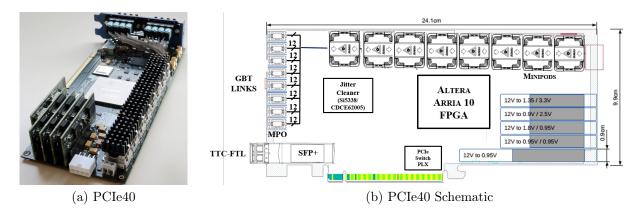

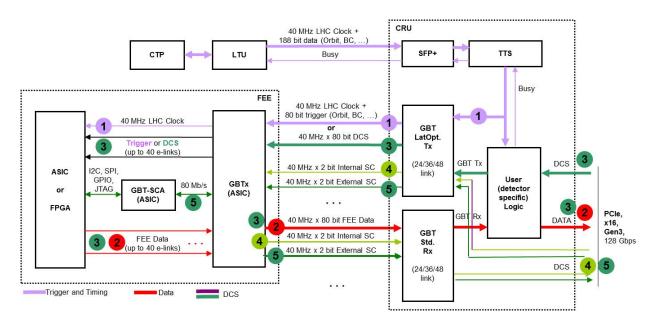

Table 1.3: An Overview of ALICE statistics before and after the scheduled upgrade