CERN-LHCC-2019-003 CMS-TDR-020 29 March 2019 Revised 26 September 2019

# A MIP Timing Detector for the CMS Phase-2 Upgrade

**Technical Design Report**

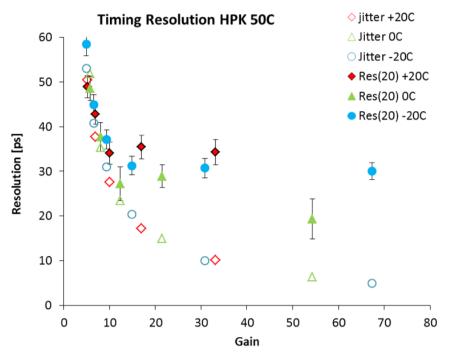

**CMS** Collaboration

# **Editors**

J. Butler, T. Tabarelli de Fatis

# **Chapter Editors**

A. Apresyan, J. Bendavid, A. Bornheim, J. Butler, N. Cartiglia, F. Golf, L. Gray, W. Li, T. Liu, M.T. Lucchini, S. Lusin, W. Lustermann, P. Martinez Ruiz del Arbol, P. Meridiani, I. Ojalvo, O. Sahin, D. Stuart, T. Tabarelli de Fatis, S. Tkaczyk, J. Varela

# **Cover Design**

S. Cittolin

# Acknowledgements

This document would not exist without the devoted efforts of many colleagues, too many to be named explicitly, who contributed text and figures to this TDR. We would like to thank the technical staffs from the various MTD institutions for their excellent work during the design and R&D phase of this upgrade, without which this TDR and the MTD itself would not be possible.

The very useful input from the MTD collaboration, the CMS internal reviewers (Wolfgang Adam, Johan Borg, Tulika Bose, Didier Contardo, Karl Gill, Frank Hartmann, Jan Kieseler, Katja Klein, Frans Meijers, Michael Moll, Paolo Rumerio, Alexander Savin, Jeff Spalding, Roberto Tenchini, Wolfram Zeuner), and the chair of the Phase-2 TDRs editorial board (C. Lourenço) helped to improve the quality of this document and is greatly appreciated. We also thank the individual and institutional reviewers who participated in the Collaboration-Wide Review of the TDR.

We would like to acknowledge the support of the CMS Management, the Upgrade Project Coordination team as well as the many contributions from CMS Technical Coordination. We thank the Offline, Computing, Physics Performance and Datasets, Upgrade Physics Strategy Group, and all the Physics groups for their help in developing and executing the physics and performance studies. The CMS Tracker and Endcap Calorimeter Upgrade projects provided crucial support and advice on various inter-detector coordination issues.

# Contents

| 1 | Ove | rview o | of the MIP Timing Detector Project                          | 1  |

|---|-----|---------|-------------------------------------------------------------|----|

|   | 1.1 | Introd  | luction                                                     | 1  |

|   | 1.2 | Impac   | t of the MTD on the CMS physics program at the HL-LHC       | 6  |

|   | 1.3 | Consid  | derations and requirements for the design of the MTD        | 9  |

|   |     | 1.3.1   | Time resolution                                             | 10 |

|   |     | 1.3.2   | Space constraints for detectors and services                | 10 |

|   |     | 1.3.3   | Impact on Tracker and CE integration and installation       | 10 |

|   |     | 1.3.4   | Impact on the performance of other detectors                | 11 |

|   |     | 1.3.5   | Segmentation/occupancy                                      | 11 |

|   |     | 1.3.6   | Compatibility with CMS Trigger and Data Acquisition systems | 12 |

|   |     | 1.3.7   | Operating temperature                                       | 12 |

|   |     | 1.3.8   | Radiation tolerance                                         | 13 |

|   | 1.4 | Overv   | riew of the MIP Timing Detector design                      | 14 |

|   |     | 1.4.1   | Overview of the Barrel Timing Layer                         | 15 |

|   |     | 1.4.2   | Overview of the Endcap Timing Layer                         | 18 |

|   |     | 1.4.3   | The clock distribution system                               | 19 |

|   |     | 1.4.4   | Supporting Systems                                          | 21 |

|   |     | 1.4.5   | Possible use of the MTD in the Level 1 Trigger              | 21 |

|   | 1.5 | Guide   | e to the remainder of the TDR                               | 22 |

|   |     |         |                                                             |    |

| 2 |     |         | Timing Layer                                                | 23 |

|   | 2.1 |         | riew and principle of operation                             | 23 |

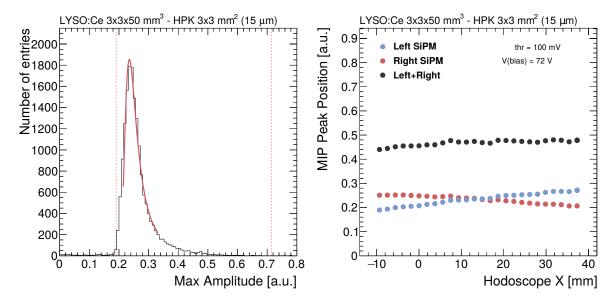

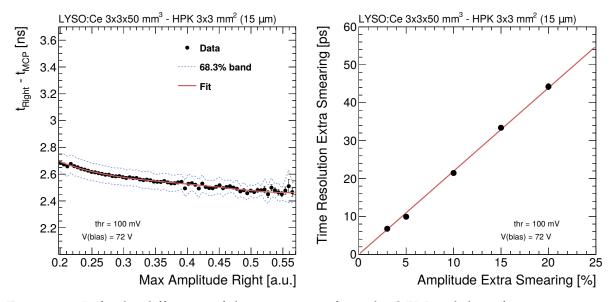

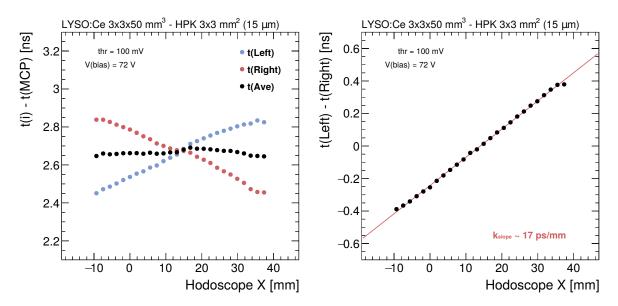

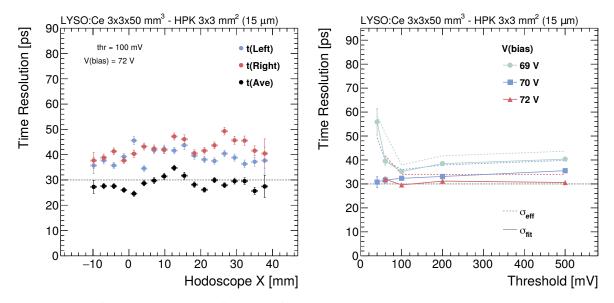

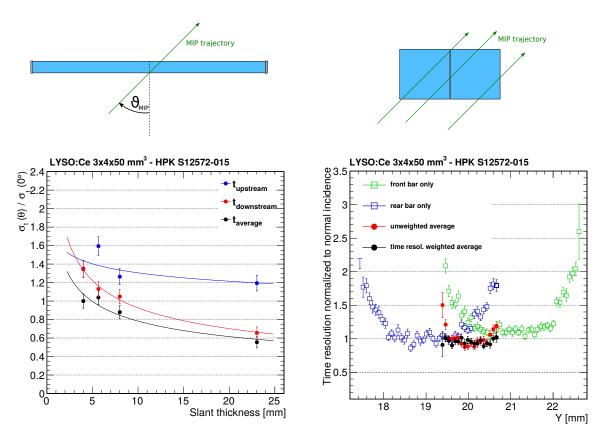

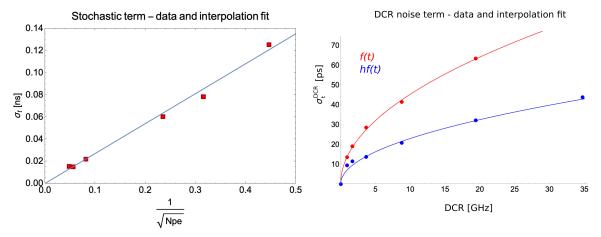

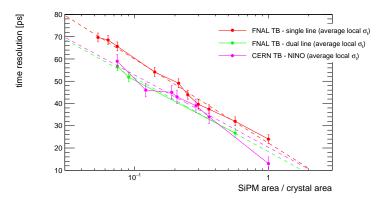

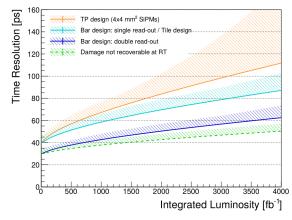

|   |     | 2.1.1   | BTL sensors performance in test beam                        | 27 |

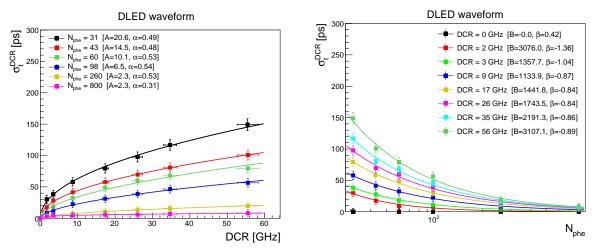

|   |     | 2.1.2   | Mitigation of DCR impact on time resolution                 | 30 |

|   | 2.2 |         | e elements                                                  | 32 |

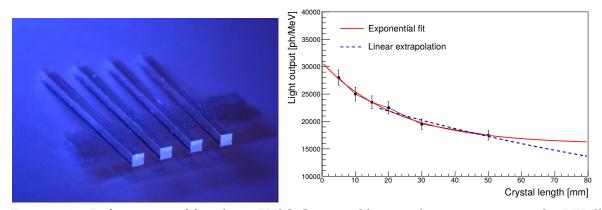

|   |     | 2.2.1   | Scintillating crystals                                      | 32 |

|   |     | 2.2.2   | Silicon photomultipliers                                    | 37 |

|   |     | 2.2.3   | Packaging of active elements                                | 42 |

|   | 2.3 |         | eadout electronics                                          | 45 |

|   |     | 2.3.1   | Requirements and system description                         | 47 |

|   |     | 2.3.2   | Performance                                                 | 67 |

|   |     | 2.3.3   | Production and testing                                      | 76 |

|   | 2.4 | Engin   | eering and integration                                      | 78 |

|   |     | 2.4.1   | Structural design of the TST                                | 79 |

|   |     | 2.4.2   | Tracker-BTL TST mechanics                                   | 80 |

|   |     | 2.4.3   | BTL tray design                                             | 80 |

|   |     | 2.4.4   | Cooling and environmental control                           | 83 |

|   |     | 2.4.5   | BTL Services                                                | 88 |

|   |     | 2.4.6   | BTL detector assembly                                       | 89 |

|   | 2.5 | Power   | r requirements                                              | 92 |

|   |     | 2.5.1   | Readout Unit and power scheme                               | 92 |

|   |     | 2.5.2  | BTL low voltage system                                           | 95  |

|---|-----|--------|------------------------------------------------------------------|-----|

|   |     | 2.5.3  | The BTL bias voltage system                                      | 98  |

|   |     |        |                                                                  |     |

| 3 |     | -      | 8 5                                                              | 103 |

|   | 3.1 |        | iew and principle of operation                                   |     |

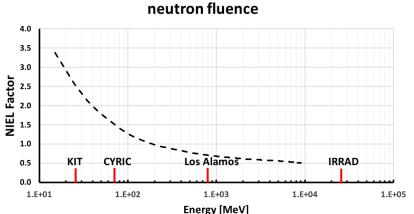

|   |     | 3.1.1  | Radiation levels                                                 |     |

|   |     | 3.1.2  | Relevant parameters in the determination of the time resolution  |     |

|   | 3.2 |        | n sensors                                                        |     |

|   |     | 3.2.1  | Design and specifications                                        |     |

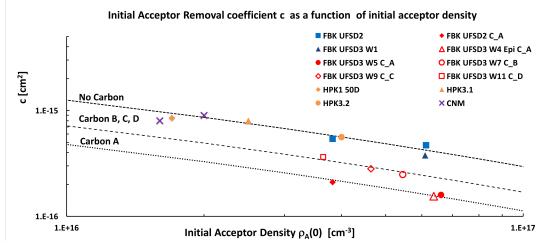

|   |     | 3.2.2  | Radiation hardness studies                                       |     |

|   |     | 3.2.3  | Biasing scheme and power dissipation                             |     |

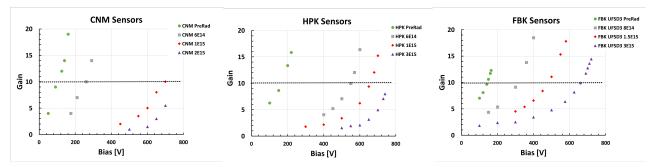

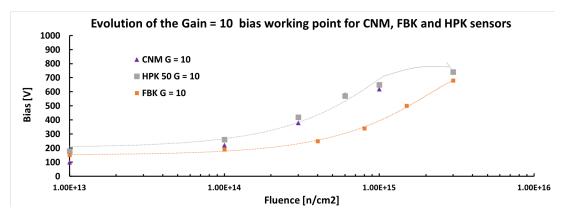

|   |     | 3.2.4  | Performance                                                      |     |

|   |     | 3.2.5  | Development plan and schedule                                    | 121 |

|   | 3.3 | On-de  | tector electronics                                               | 122 |

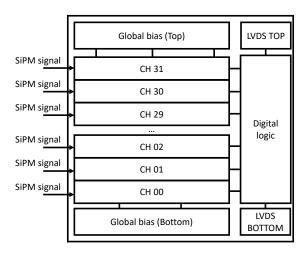

|   |     | 3.3.1  | ETL readout ASIC overview                                        | 122 |

|   |     | 3.3.2  | Design study with waveform analysis using test beam data         | 124 |

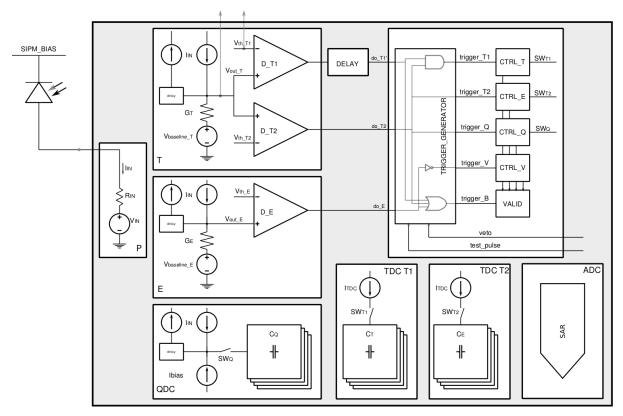

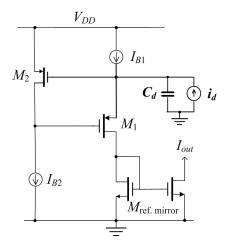

|   |     | 3.3.3  | Preamplifer design                                               | 128 |

|   |     | 3.3.4  | Discriminator design                                             | 129 |

|   |     | 3.3.5  | Results of preamplifier and discriminator performance simulation | 131 |

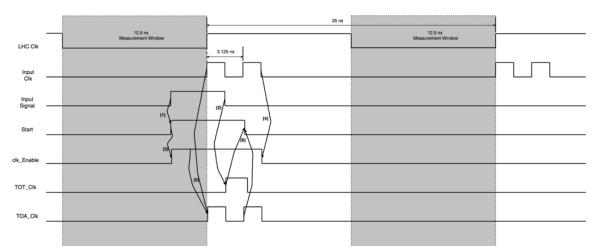

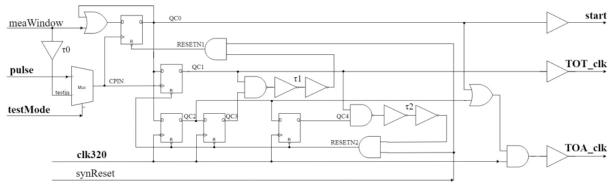

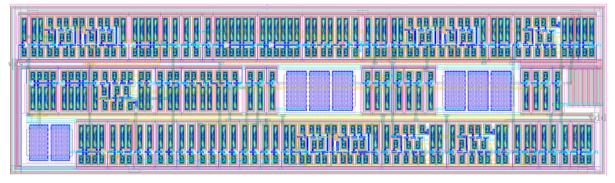

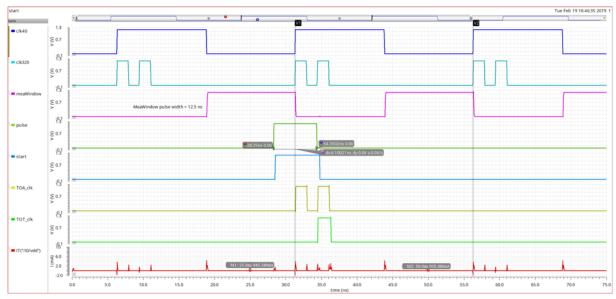

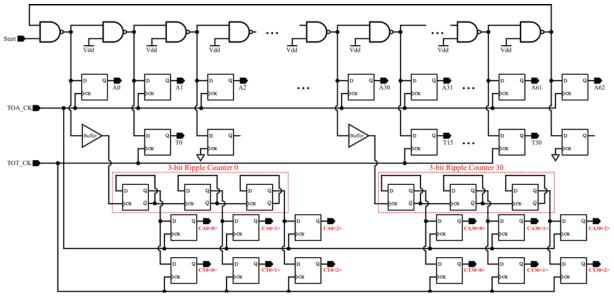

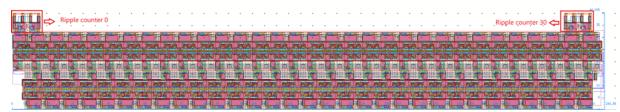

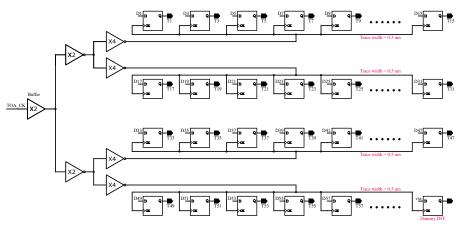

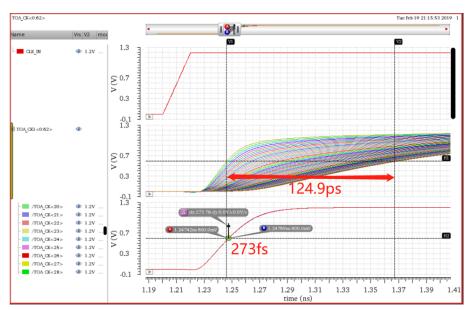

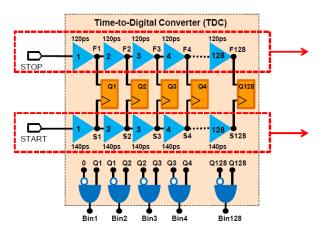

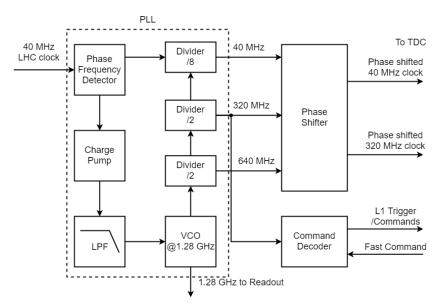

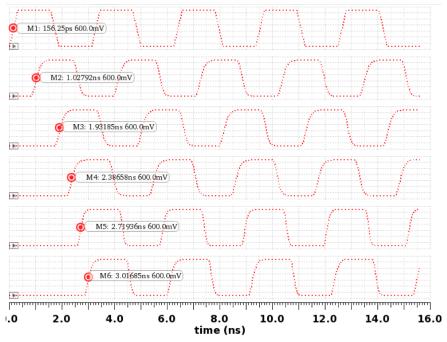

|   |     | 3.3.6  | TDC design                                                       | 132 |

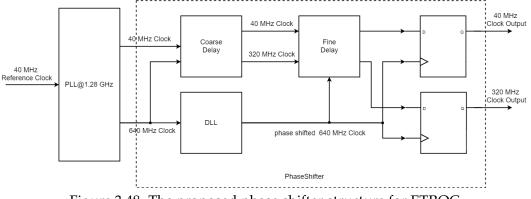

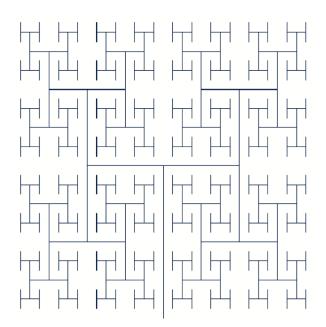

|   |     | 3.3.7  | Clock distribution                                               | 139 |

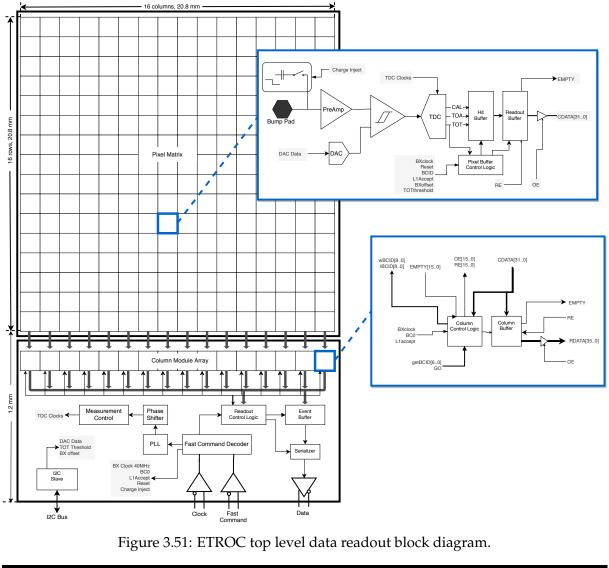

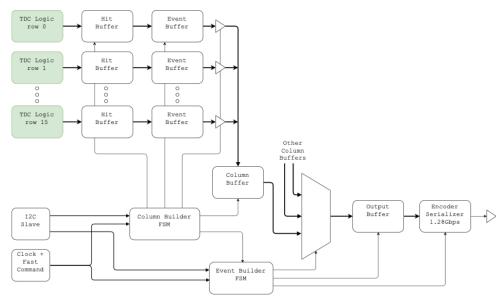

|   |     | 3.3.8  | Level-1 Buffer and data readout                                  | 141 |

|   |     | 3.3.9  | System interfaces                                                | 145 |

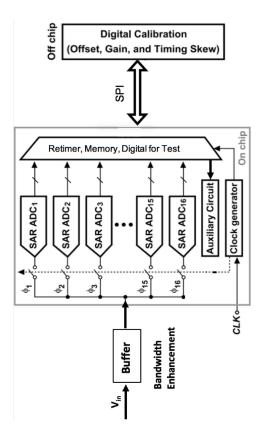

|   |     | 3.3.10 | Waveform sampling design                                         | 145 |

|   |     | 3.3.11 | Radiation effects and mitigation techniques                      | 147 |

|   |     | 3.3.12 | Optimization of power consumption vs performance                 | 148 |

|   |     | 3.3.13 | Development plan and schedule                                    | 149 |

|   | 3.4 | ETL m  | nodules                                                          | 151 |

|   |     | 3.4.1  | Module design                                                    | 151 |

|   |     | 3.4.2  | Module assembly                                                  | 152 |

|   |     | 3.4.3  | Module prototyping                                               | 153 |

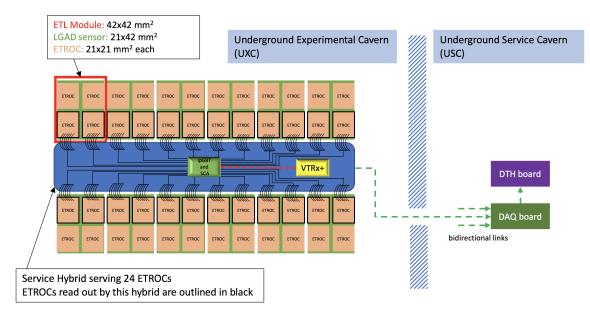

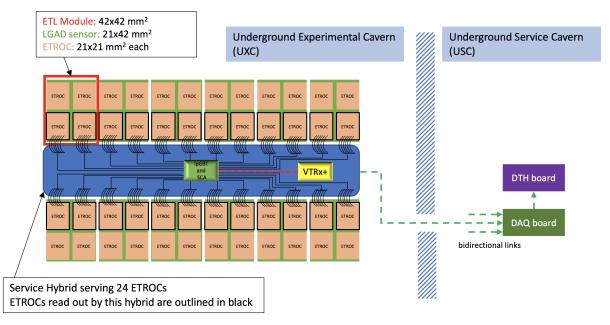

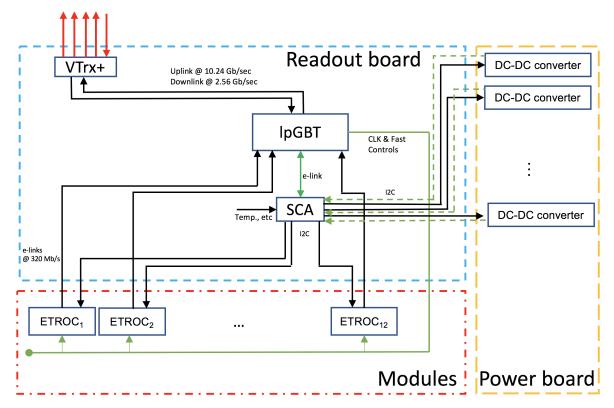

|   |     | 3.4.4  | Service hybrids                                                  | 156 |

|   | 3.5 | Data p | bath and rates                                                   |     |

|   | 3.6 | -      | control and monitoring                                           |     |

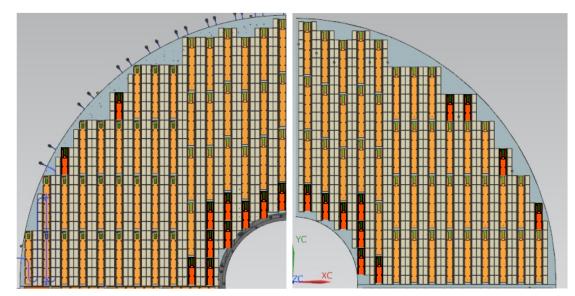

|   | 3.7 | Mecha  | anical engineering, integration, and installation                | 163 |

|   |     | 3.7.1  | Structural design                                                |     |

|   |     | 3.7.2  | Integration of modules and service hybrids                       |     |

|   |     | 3.7.3  | Installation and commissioning                                   |     |

|   | 3.8 | Servic | -                                                                |     |

|   |     | 3.8.1  | DC low voltage power distribution                                |     |

|   |     | 3.8.2  | Bias voltage system                                              |     |

|   |     | 3.8.3  | Grounding                                                        |     |

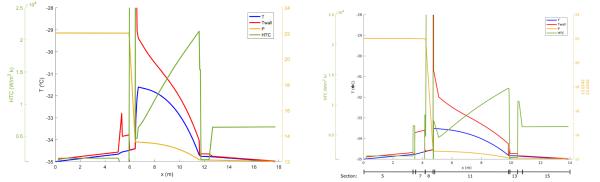

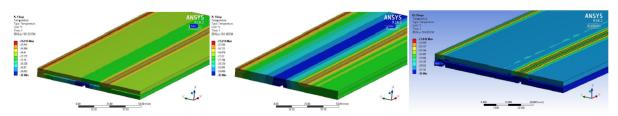

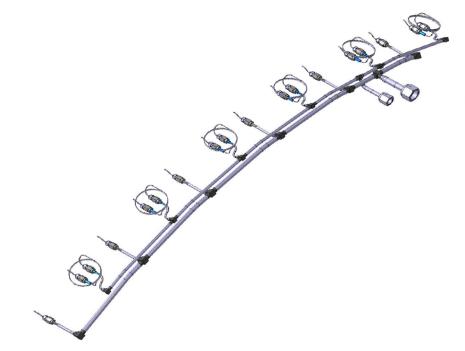

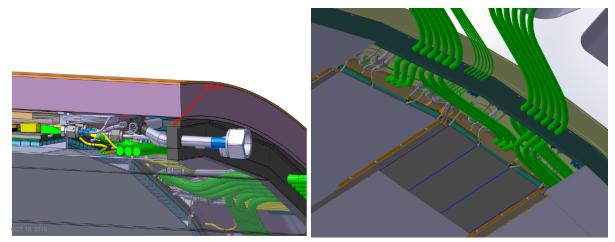

|   |     | 3.8.4  | Cooling                                                          |     |

|   |     |        |                                                                  |     |

#### Contents

| 4 | Con  | nmon sy           | ystems                                                           | 177   |

|---|------|-------------------|------------------------------------------------------------------|-------|

|   | 4.1  | The da            | ata acquisition system                                           | . 177 |

|   |      | 4.1.1             | Overview                                                         | . 177 |

|   |      | 4.1.2             | DAQ system requirements                                          | . 177 |

|   |      | 4.1.3             | Hardware description                                             | . 178 |

|   | 4.2  | The cl            | ock distribution                                                 | . 181 |

|   |      | 4.2.1             | Components of the clock distribution chain                       | . 182 |

|   |      | 4.2.2             | Characterization of current CMS clock distribution system        | . 182 |

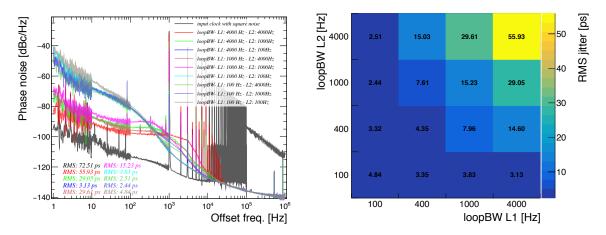

|   |      | 4.2.3             | MTD clock distribution system R&D                                | . 183 |

|   |      | 4.2.4             | Developement plan and decision points                            | . 185 |

|   |      | 4.2.5             | Clock distribution monitoring and calibration                    | . 187 |

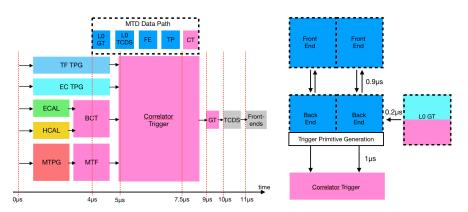

|   | 4.3  | L1 Tri            | gger options                                                     |       |

|   |      | 4.3.1             | Level-1 MTD requirements and architecture                        | . 188 |

|   |      | 4.3.2             | Decision points for the Level-1 MTD                              | . 190 |

|   | 4.4  | Detect            | tor control and safety system                                    | . 191 |

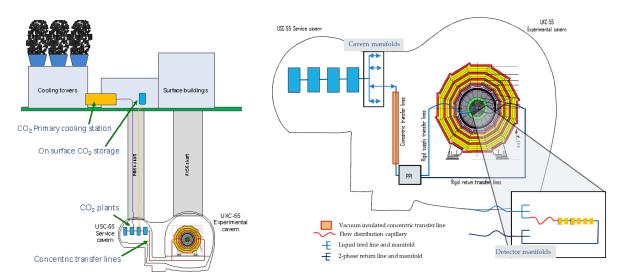

|   | 4.5  | CO <sub>2</sub> c | ooling system                                                    | . 192 |

| 5 | Reco | onstruc           | tion, performance and physics impact                             | 197   |

|   | 5.1  | Introd            | luction                                                          | . 197 |

|   | 5.2  | Detect            | tor simulation and reconstruction                                | . 198 |

|   |      | 5.2.1             | Detector Simulation                                              | . 198 |

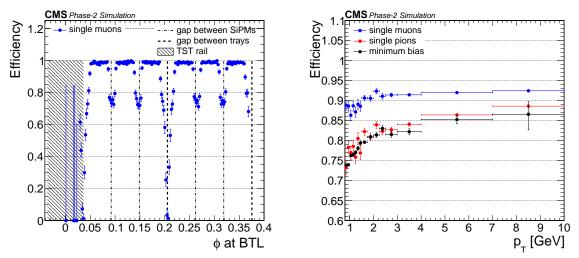

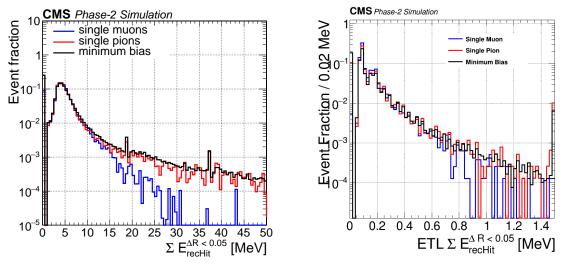

|   |      | 5.2.2             | BTL simulation                                                   | . 200 |

|   |      | 5.2.3             | ETL simulation                                                   | . 202 |

|   |      | 5.2.4             | Reconstruction of deposited energy and time in the MTD           | . 203 |

|   |      | 5.2.5             | Tracking implementation                                          | . 204 |

|   |      | 5.2.6             | Vertexing implementation                                         | . 205 |

|   |      | 5.2.7             | Neutral particles time reconstruction in BTL                     | . 208 |

|   | 5.3  | Perfor            | rmance in the reconstruction of final state observables          | . 210 |

|   |      | 5.3.1             | Rejection of tracks from pileup interactions                     | . 211 |

|   |      | 5.3.2             | Jet and missing transverse momentum                              | . 212 |

|   |      | 5.3.3             | Heavy-flavor tagging                                             | . 215 |

|   |      | 5.3.4             | Lepton isolation from charged tracks                             | . 217 |

|   |      | 5.3.5             | Electron identification from energy deposits in the MTD          | . 220 |

|   |      | 5.3.6             | Time-of-Flight Particle identification                           | . 221 |

|   | 5.4  | Physic            | cs impact examples                                               | . 222 |

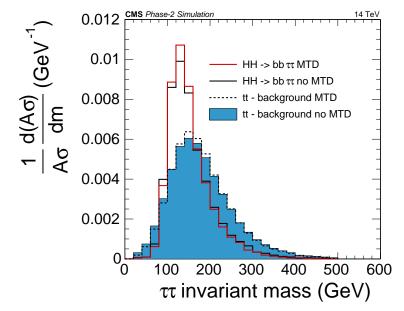

|   |      | 5.4.1             | Higgs boson pair production                                      | . 223 |

|   |      | 5.4.2             | Long-lived particles                                             | . 226 |

|   |      | 5.4.3             | Particle velocity reconstruction in the context of HSCP searches | . 231 |

|   |      | 5.4.4             | Heavy Ion Analysis with TOFPID                                   | . 232 |

| 6 | Org  | anizatio          | on, schedule, and costs                                          | 239   |

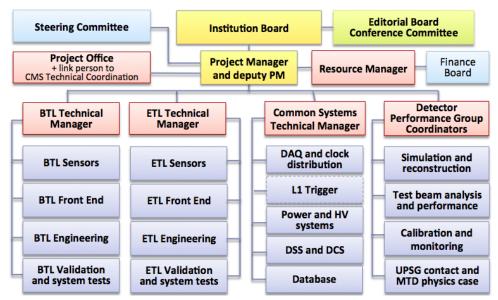

|   | 6.1  | Projec            | t organization                                                   | . 239 |

|   |      | 6.1.1             | Introduction                                                     | . 239 |

|   |      | 6.1.2             | Organization of the MTD project                                  | . 239 |

|    | 6.2<br>6.3<br>6.4 | 6.1.3       Interface with CMS and CERN       2         Project timeline and milestones       2         6.2.1       Project timeline       2         6.2.2       List of milestones       2         Institution interests and construction responsibilities       2         Cost estimate       2 | 243<br>243<br>245<br>248 |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Aŗ | opend             | lices                                                                                                                                                                                                                                                                                             | 253                      |

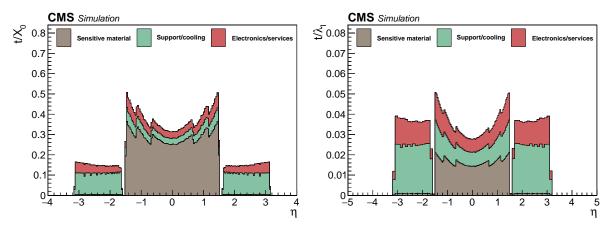

| Α  | Radi              | ation environment                                                                                                                                                                                                                                                                                 | 253                      |

|    | A.I               | Geometry model and simulation parameters                                                                                                                                                                                                                                                          |                          |

|    |                   | Fluence and dose predictions                                                                                                                                                                                                                                                                      |                          |

|    |                   | Uncertainties and safety margin                                                                                                                                                                                                                                                                   |                          |

|    |                   | Considerations on radiation protection for ETL maintenance                                                                                                                                                                                                                                        |                          |

| В  | The               | Barrel Timing Layer: additional technical information                                                                                                                                                                                                                                             | 261                      |

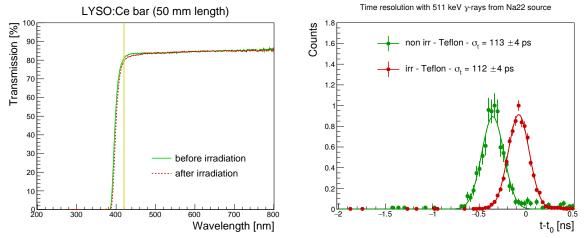

| 2  | B.I               | Studies on BTL radiation tolerance                                                                                                                                                                                                                                                                |                          |

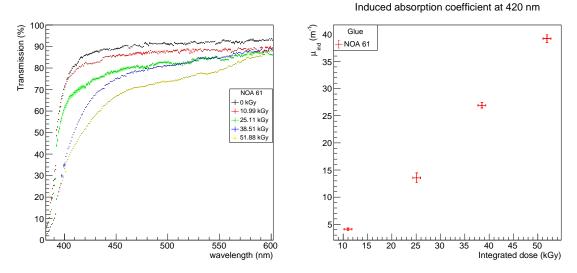

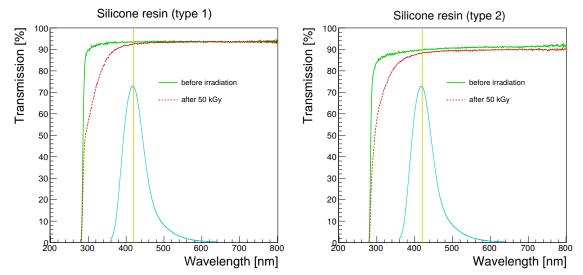

|    | 2.12              | B.I.1 Radiation tolerance of BTL sensor parts                                                                                                                                                                                                                                                     |                          |

|    |                   | B.I.2 Time resolution of irradiated SiPMs                                                                                                                                                                                                                                                         |                          |

|    |                   | B.I.3 Uncertainties on the BTL performance extrapolation                                                                                                                                                                                                                                          |                          |

|    |                   | B.I.4 Plans for full module radiation tolerance tests                                                                                                                                                                                                                                             |                          |

|    | B.II              | BTL test beam campaign for sensor optimization                                                                                                                                                                                                                                                    |                          |

|    |                   | B.II.1 Alternative BTL sensor layouts tested                                                                                                                                                                                                                                                      |                          |

|    |                   | B.II.2 Comparison of BTL sensor layouts                                                                                                                                                                                                                                                           |                          |

| С  | The               | Endcap Timing Layer: additional technical information                                                                                                                                                                                                                                             | 273                      |

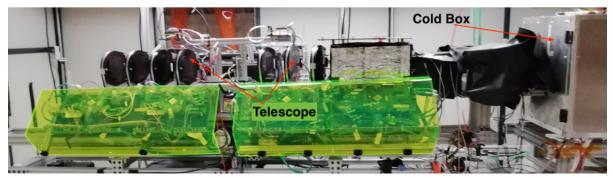

|    | C.I               | Beam tests                                                                                                                                                                                                                                                                                        | 273                      |

|    |                   | C.I.1 Experimental Setup                                                                                                                                                                                                                                                                          | 273                      |

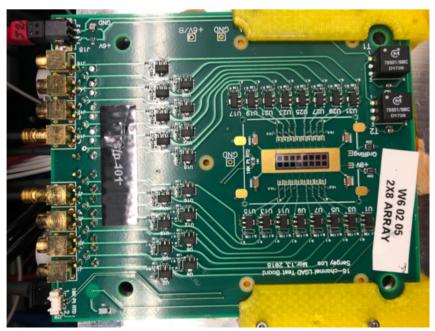

|    |                   | C.I.2 Readout Electronics                                                                                                                                                                                                                                                                         |                          |

|    | C.II              | Waveform Sampling Implementation Details                                                                                                                                                                                                                                                          | 275                      |

| D  | Add               | itional performance studies                                                                                                                                                                                                                                                                       | 279                      |

|    | D.I               | -                                                                                                                                                                                                                                                                                                 | 279                      |

|    | D.II              | Alignment, time synchronization, and monitoring                                                                                                                                                                                                                                                   | 280                      |

|    | D.III             | Spatial alignment                                                                                                                                                                                                                                                                                 | 281                      |

|    | D.IV              | Time synchronisation                                                                                                                                                                                                                                                                              | 281                      |

| Ε  | Leve              | el-1 MTD performance study                                                                                                                                                                                                                                                                        | 283                      |

|    | E.I               | Research on use of MTD in Level-1 trigger                                                                                                                                                                                                                                                         | 283                      |

| Gl | ossar             | y of Special Terms and Acronyms                                                                                                                                                                                                                                                                   | 285                      |

| Re | feren             | ces                                                                                                                                                                                                                                                                                               | 293                      |

| CN | AS Co             | ollaboration                                                                                                                                                                                                                                                                                      | 303                      |

# Chapter 1

# **Overview of the MIP Timing Detector Project**

# 1.1 Introduction

This document is the Technical Design Report (TDR) of the MIP Timing Detector (MTD), a new detector planned for CMS during the High Luminosity LHC (HL-LHC) era. This device will bring a completely new capability to CMS — the ability to measure precisely the production time of minimum ionizing particles (MIP) for use in disentangling the approximately 200 nearly-simultaneous "pileup" interactions that will occur in each bunch crossing of the LHC. It also provides new capabilities for charged hadron identification and the search for long-lived particles.

In this introduction, we summarize the motivation and physics case for the MTD, present the high-level considerations and requirements for the design, and give an overview of the proposed detector.

In 2015, the LHC achieved a center-of-mass energy for proton-proton collisions of 13 TeV. While a small increase in collision energy is planned, the main improvement in the sensitivity of the search for physics "beyond the standard model (BSM)" will come from increased luminosity. In 2019, the LHC began a two-year shutdown, known as Long Shutdown 2 (LS2), to upgrade the injector complex to produce brighter (smaller emittance) beams. After a three-year running period at 13–14 TeV (Run-3), there will be another long shutdown of approximately 2.5 years, Long Shutdown 3 (LS3), starting in 2024, to upgrade the optics in the interaction region to produce more tightly focused and overlapping beams at collision. The LHC will resume operations in 2026. The decade following these upgrades is called the High Luminosity (HL-LHC) era or sometimes Phase-2 of LHC operations. There will be much higher collision rates that will far exceed the capabilities of the existing CMS detector, which will consequently require significant upgrades to continue to function efficiently. The MTD will be added to CMS to help meet the challenge of high luminosity.

For the HL-LHC, the brightness of the beams and the new focusing scheme at the interaction point will enable the accelerator to deliver an instantaneous luminosity of  $2 \times 10^{35}$  cm<sup>-2</sup>s<sup>-1</sup> at the beginning of each fill [1]. However, the nominal scenario is to operate at a stable "leveled" luminosity of  $5.0 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, to limit the number of interactions during each bunch crossing to 140 on average, by continuously tuning the beam focus and the beam crossing profile during the fills. An ultimate scenario, with a leveled luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, will provide 30% more integrated luminosity, at the cost of producing 200 collisions per beam crossing. Hard interactions of interest to CMS, those that probe energy scales ranging from a few GeV to several TeV, occur in far fewer than 1% of the total beam crossings but will always be accompanied by an average of 140–200 additional interactions. The spatial overlap of tracks and energy deposits from the additional collisions can degrade the identification and the reconstruction of

the hard interaction and can increase the rate of false triggers. In addition, the higher collision rate integrated over time results in more radiation damage than can be tolerated by some of the existing subdetectors. The upgraded detector must survive and function efficiently in this much harsher radiation and high pileup environment and must transport a much higher rate of data off the detector to be recorded for analysis.

The primary goal of the CMS Phase-2 upgrade for the HL-LHC is to maintain the current excellent performance of the CMS detector in efficiency, resolution, and background rejection for all final state particles and physics observables used in data analyses. The CMS Upgrade Technical Proposal [2] presents, and the Scope Document [3] further specifies, a detailed plan to deploy an upgraded CMS detector by 2026 to be ready for the start of HL-LHC operations. It identifies the upgrades of CMS components necessary to withstand radiation damage effects and overcome the challenge posed by the high rate of pileup, as detailed in Refs. [4–7].

The CMS collaboration has recently approved a Technical Proposal [8] to include the MIP Timing Detector in the upgrade plan for the HL-LHC era. The MTD will give timing information for MIPs with 30–40 ps resolution at the beginning of HL-LHC operation in 2026, degrading slowly as a result of radiation damage to 50-60 ps by the end of HL-LHC operations. This will help to assign charged tracks to the correct interaction vertices in bunch crossings with an average of 200 collisions or more. It exploits the fact that the individual interactions within the bunch crossing do not all occur at precisely the same time but, because of the longitudinal extent of the beams, are distributed over time with an rms of 180–200 ps. By associating tracks from a vertex to hits and their corresponding times in the MTD, the time at which the collision vertex occurred can be reconstructed. Other tracks pointing roughly towards the vertex but coming at the wrong time, can be eliminated from consideration as contributing to that particular collision. The use of timing and tracking together will, therefore, give CMS excellent association of tracks to vertices even when the vertices are very close together in space. The MTD will provide timing in the barrel and endcap regions, with a hermetic angular coverage up to a pseudorapidity,  $\eta$ , of  $\pm 3$ , with  $\eta$  defined as  $-\ln \tan(\theta/2)$ , where  $\theta$  is the polar angle of a particle measured from the z axis, taken as the beam line. A full definition of the coordinate system used in the CMS experiment and the relevant kinematic variables can be found in Ref. [9].

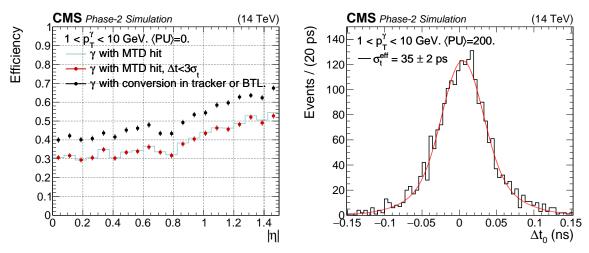

The time of electromagnetic showers will also be determined to a precision of 30–50 ps above a transverse momentum,  $p_{\rm T}$ , of a few GeV in the upgraded calorimeters [6, 7]. We can use these times to associate photons to the correct charged particle vertex, based on compatibility with the time obtained from the MTD.

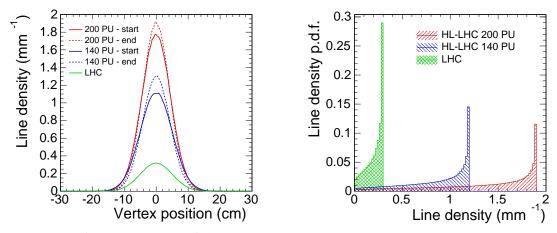

Pileup mitigation in CMS builds upon particle-flow event reconstruction [10], a technique that combines information from different detectors to establish a list of particle candidates: charged leptons, charged hadrons, photons, and neutral hadrons. It improves the quality of the objects included in the vertex of interest by removing charged tracks that are inconsistent with originating from that vertex, as well as neutral deposits in the calorimeters that might belong to a different interaction based on statistical inference techniques, as described in Ref. [11]. The high spatial granularity of the tracking subdetectors will enable the upgraded CMS detector to separate vertices, to identify the hard collision, and to measure signal particles with good efficiency in the offline analyses [2, 3]. In the transition from 140 to 200 pileup interactions, however, the peak "line density",  $dN_V/dz$ , of the number of collision vertices,  $N_V$ , grows from 1.2 to 1.9 mm<sup>-1</sup>, assuming a line spread along the beam axis of about 4.5 cm rms (averaged over the length of the fill), as seen in Fig. 1.1. The probability of spatial overlaps grows in all subdetectors, and these algorithms begin to fail at a substantial rate. For example, the association of

2

Figure 1.1: Left: Distribution of the vertices along the beam direction at the LHC (Run-1 and early Run-2) with  $\approx$ 30 pileup interactions and HL-LHC with 140 and 200 pileup interactions. The solid (dashed) line refers to the start (end) of the fill. Adjustments in the focusing of the beam cause the *z* distributions to become narrower at the end of the fill. Right: Probability density functions of the line density along the beam axis for the pileup of about 30 and for pileup 140 and 200. The modes of the three distributions are 0.3, 1.2, and 1.9 mm<sup>-1</sup> and their means are 0.2, 0.9, and 1.4 mm<sup>-1</sup>, respectively.

a track with the primary vertex relies on a requirement on the distance of closest approach to the vertex along the beam axis. Because tracks from displaced sources — such as secondary interactions, decays of particles in flight, and resolution tails — cannot always be fully identified, the optimal selection window has to be set wider than what would be expected by the intrinsic tracking resolution alone. According to simulation, the optimal window is of the order of 1 mm, causing a non-negligible contamination of tracks from pileup into the primary vertex for vertex densities approaching 1 mm<sup>-1</sup>. The resulting degradation in resolutions, efficiencies, and misidentification rates at 200 pileup interactions impacts several measurements [3, 12]. While measurements relying on isolated objects will suffer mainly from an efficiency reduction when tracks from pileup are incorrectly included in their isolation cones, measurements depending on the resolution of global objects such as missing transverse energy ( $p_{\rm T}^{\rm miss}$ ) or on extended objects such as jets may be distorted and this could result in poorer resolution or higher backgrounds.

The timing upgrade of the CMS detector will improve the particle-flow performance at high pileup to a level comparable to the current Phase-1 CMS detector, which is designed to handle a pileup of approximately 50, exploiting the additional timing information from the MTD and the calorimeters. In the time domain, the RMS spread of 180–200 ps within the 25 ns bunch crossing structure of the colliding beams, is approximately constant during the fill and largely uncorrelated with the spatial distribution. If one considers the beam spot sliced into consecutive time exposures of 30–40 ps, the number of vertices per exposure drops to current Run-2 LHC pileup levels of 40–60. A time resolution of this size would therefore reduce the 'effective multiplicity' of concurrent collisions, thereby recovering the Phase-1 quality of event reconstruction.

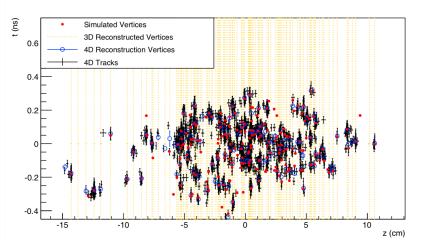

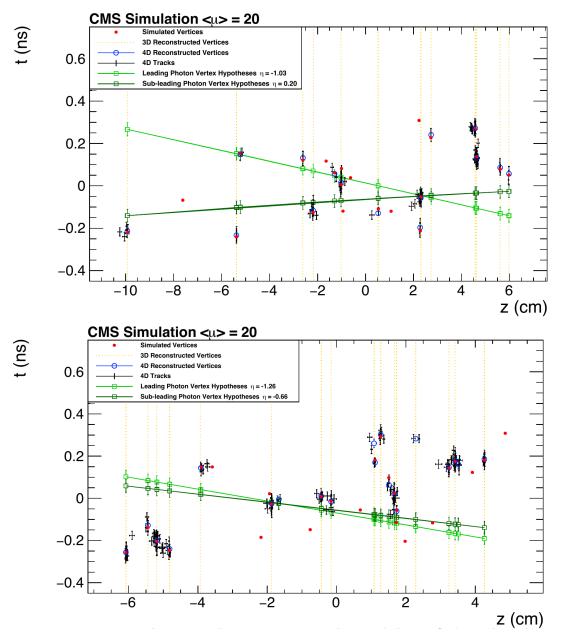

The event display in Fig. 1.2 visually demonstrates the power of space-time reconstruction in 200 pileup collisions, using a time-aware 4-dimensional extension of the deterministic annealing technique adopted in vertex reconstruction by CMS [13]. According to simulation, instances of vertex merging are reduced from 15% in space to 1% in space-time. The use of timing information for each track, together with its *z* position extrapolated to the beam line,

Figure 1.2: Simulated and reconstructed vertices in a bunch crossing with 200 pileup interactions assuming a MIP timing detector with  $\sim$ 30 ps time resolution covering the barrel and endcaps. The horizontal axis is the *z* position along the beam line, where the "0" is the center of the IR. The vertical axis is the time with "0" being the point in time when the beams completely overlap in *z*. The simulated vertices are the red dots. The vertical yellow lines indicate 3D-reconstructed (i.e. no use of timing information) vertices, with instances of vertex merging visible throughout the display. The black crosses and the blue open circles represent tracks and vertices reconstructed using a method that includes the time information and is therefore referred to as "4D". Many of the vertices that appear to be merged in the spatial dimension are clearly separated when time information is available.

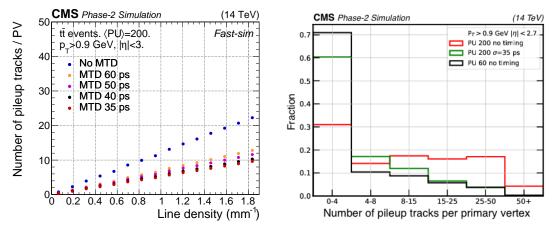

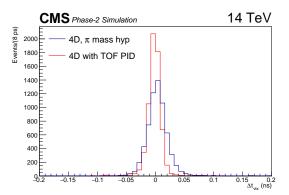

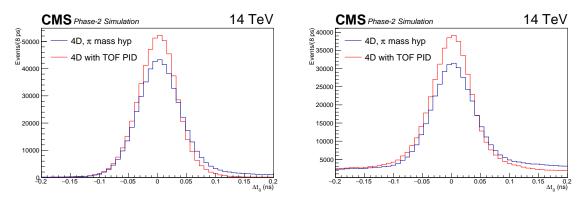

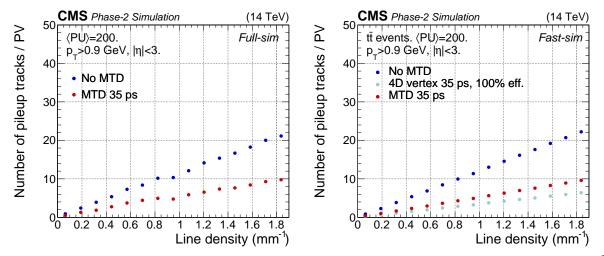

reduces the number of tracks from pileup vertices that are incorrectly associated with the hardinteraction vertex. This reduction is quantified in Fig. 1.3. The left plot shows the mean number of tracks incorrectly associated to the primary vertex as a function of the line density of the collision vertices. For a line density of 1.9 collisions per mm, which is the peak density for the case of 200 pileup collisions, the mean number of incorrectly associated tracks reaches over 20

Figure 1.3: Left: Number of pileup tracks incorrectly associated with the hard interaction vertex as a function of the collision line density for different time resolutions. Right: Distribution of the number of incorrectly associated tracks with the use of a 3  $\sigma$  (where  $\sigma = 35$  ps) selection on timing information and without use of timing information. The vertical axis is the fraction of primary vertices which have the number of pileup tracks shown on the horizontal axis associated to them.

without the use of timing information.

The addition of track-time information from the MTD with 30–40 ps precision and a tracktime reconstruction efficiency of 85% reduces the wrong associations by more than a factor of two. The peak line density of  $1.9 \text{ mm}^{-1}$  is effectively reduced to about  $0.8 \text{ mm}^{-1}$ , which corresponds to less than 80 pileup collisions. The addition of MTD time information, therefore, has the potential to offset fully the CMS performance degradation in the transition from 140 to 200 pileup collisions and to recover the effective background conditions close to Phase-1 operations.

In addition to reducing the mean number of incorrectly associated tracks, the use of timing information significantly reduces the number of primary vertices with a large number of incorrectly associated tracks, as shown in the right plot in Fig. 1.3. The red curve shows the result in the presence of 200 interactions per bunch crossing, when the vertices are reconstructed without the use of timing information: a very large number of tracks from other vertices are wrongly associated to the primary vertex. The green curve shows the number of tracks wrongly assigned to the primary vertex when a 3  $\sigma$  selection on timing is used, showing that timing information dramatically reduces the number of false associations. For comparison, the black curve shows the performance in a scenario where the pileup is 60 and there is no timing information. This pileup level was experienced during Run-2 and may be typical of operations during Run-3.

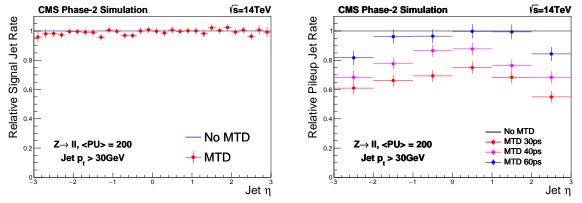

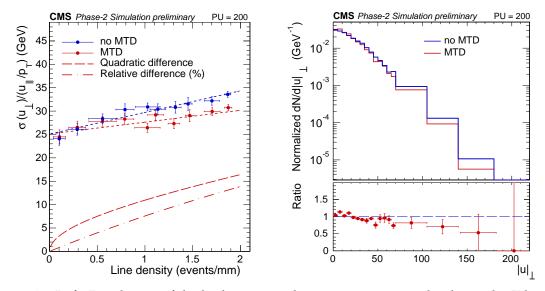

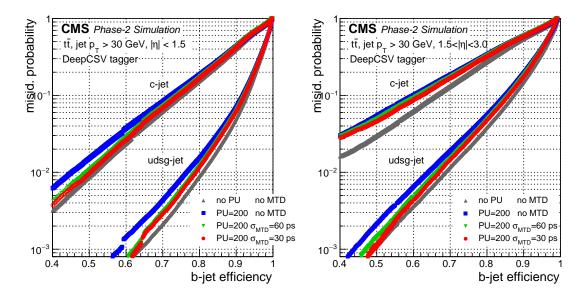

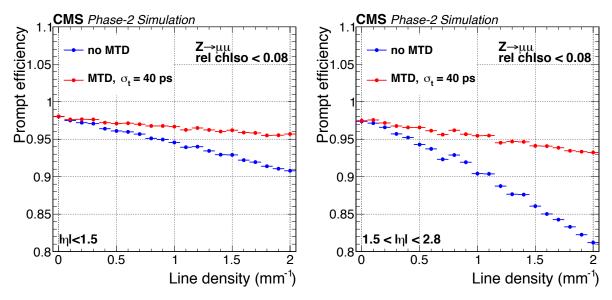

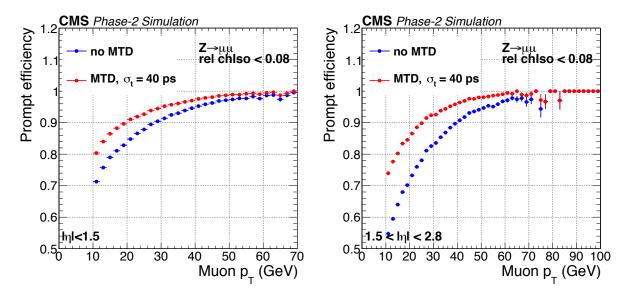

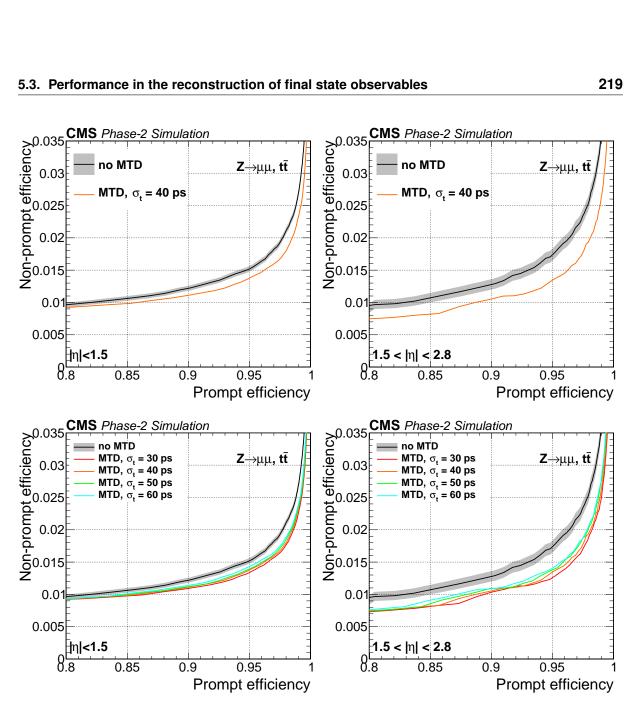

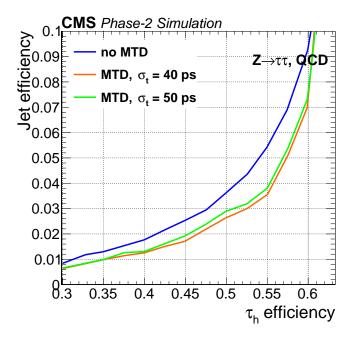

The removal of pileup tracks inconsistent with the hard-interaction improves the reconstruction of many final state observables. For example, removing pileup tracks from the isolation cones improves the identification efficiency for isolated leptons, especially  $\tau$  leptons, and photons, which are key signatures of many processes of interest for the HL-LHC program. The performance of b-jet identification, which relies on vertex reconstruction, is enhanced. The reconstruction of spatially extended objects and global event quantities that are vulnerable to the "pileup pollution", such as jets and  $p_T^{miss}$ , are also improved significantly. At pileup of 200, by using track-time information in jet reconstruction, the rate of pileup jets that are actually spuriously clustered particles from pileup interactions, is reduced by 20–40%, depending on  $\eta$ , for a jet  $p_T$  threshold of 30 GeV. The  $p_T^{miss}$  resolution is improved by about 10%.

In addition to preserving the quality of the data at the highest luminosities, the MTD also brings new capabilities to CMS. The identification of charged hadrons as pions, kaons, or protons based on time-of-flight becomes possible up to a few GeV in  $p_T$ , which is of significant benefit to Heavy Ion physics and for specialized QCD studies in pp collisions, as discussed in Chapter 5.

As the detailed design of the MTD advanced, it became clear that the goal of a time resolution of 30–40 ps is achievable. However, based on radiation exposures of the candidate detector technologies, it also became evident that the time resolution will degrade approximately linearly with integrated radiation dose, so that at the end of the HL-LHC operation the resolution will be 50–60 ps, with the luminosity-weighted average reaching 40–50 ps. The physics discussion in this introductory section is based on the resolutions that are achieved at the beginning of HL-LHC operation. The sources of radiation degradation in the barrel and endcap regions are given in Chapters 2 and 3, respectively. An evaluation of the impact of the degradation on the overall physics is presented in Chapter 5, which concludes that the MTD provides significant value to the CMS physics program even at the end of HL-LHC operation.

Simulation studies, first presented in the MTD Technical Proposal [8], and further developed in Chapter 5 show that the MTD detector will improve electron, muon,  $\tau$ , photon, jet, and  $p_{\rm T}^{\rm miss}$  reconstruction up to  $|\eta| = 3.0$ , by introducing improvements to the particle-flow reconstruction

| 1                                         | 1 0                                                  |                                     |

|-------------------------------------------|------------------------------------------------------|-------------------------------------|

| Signal                                    | Physics measurement                                  | MTD impact                          |

| $H \rightarrow \gamma \gamma$ and         | +15-25% (statistical) precision on the cross section | Isolation and                       |

| $H \rightarrow 4$ leptons                 | $\rightarrow$ Improve coupling measurements          | Vertex identification               |

| $VBF \rightarrow H \rightarrow \tau \tau$ | +30% (statistical) precision on cross section        | Isolation                           |

|                                           | $\rightarrow$ Improve coupling measurements          | VBF tagging, $p_{\rm T}^{\rm miss}$ |

| HH                                        | +20% gain in signal yield                            | Isolation                           |

|                                           | $\rightarrow$ Consolidate searches                   | b-tagging                           |

| EWK SUSY                                  | +40% background reduction                            | MET                                 |

|                                           | $\rightarrow$ 150 GeV increase in mass reach         | b-tagging                           |

| Long-lived                                | Peaking mass reconstruction                          | $\beta_{\rm LLP}$ from timing of    |

| particles (LLP)                           | $\rightarrow$ Unique discovery potential             | displaced vertices                  |

Table 1.1: Expected scientific impact of the MIP Timing Detector, taken from Ref. [8].

so as to achieve a level of performance comparable to the Phase-1 CMS detector at pileup of about 200. The integrated luminosity  $\times$  efficiency is increased and this gain is equivalent to collecting data for three additional years beyond the ten year run planned for the HL-LHC.

The remainder of Chapter 1 provides a brief summary of the physics gains made possible by the MTD, a presentation of key design considerations and requirements, and an overview of the MTD detectors.

# 1.2 Impact of the MTD on the CMS physics program at the HL-LHC

The CMS experimental program at the HL-LHC [2, 3], which includes the precision measurement of standard model (SM) processes, especially the characterization of the Higgs boson, as well as searches for BSM particles and processes, will benefit greatly from the increased luminosity provided by the upgrade of the LHC accelerator complex. The MTD is instrumental in maintaining good resolution and reconstruction efficiency for the physics objects, which are crucial for the HL-LHC scientific program. Efficiency gains from the MTD at the single-object level and the improved  $p_T^{miss}$  reconstruction performance are compounded in multi-object final states — such as di-Higgs boson events or events where the Higgs boson is produced in association with other particles — providing additional overall efficiency gains, at constant rate of reducible backgrounds, of about 20–30% across many measurements.

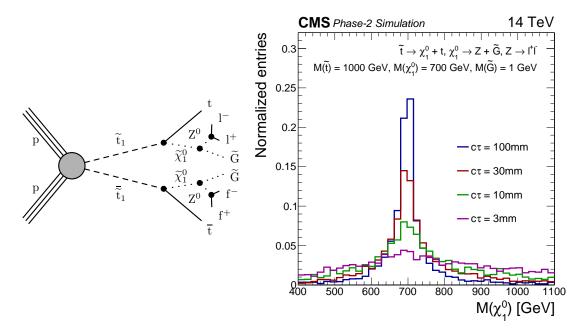

In addition, the ability to reconstruct the time of displaced vertices will provide enhanced capability in searching for long-lived particles (LLPs) by measuring  $\beta_{LLP}$ , where  $\beta$  is the relativistic velocity parameter, and, in certain cases, permitting the reconstruction of the LLP's mass. The projected performance gains from precision timing with hermetic coverage for  $|\eta| < 3$  are summarized in Table 1.1.

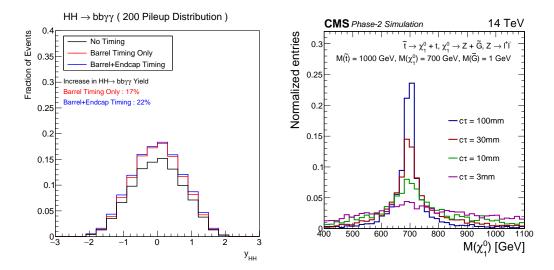

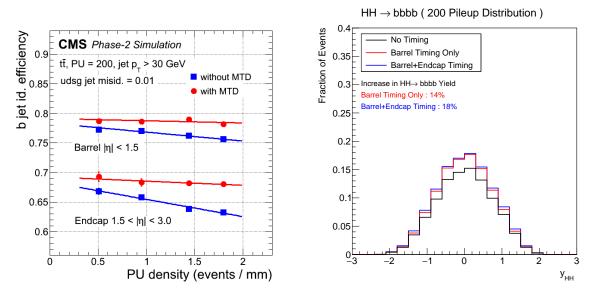

The performance of b-jet identification is improved by the removal of pileup contributions close in angle to the candidate signal particles. The gain is particularly effective in the search for di-Higgs production, which can result in many combinations of complex physics objects because of all the possible decay modes of the Higgs boson, and consequently in the direct measurement of the self coupling of the Higgs boson, which is one of the highest priorities of the HL-LHC physics program. For example, precision timing increases the signal yields for constant background in HH  $\rightarrow b\bar{b}\gamma\gamma$  by 17% from the barrel alone, and 22% with hermetic coverage, as shown in Fig. 1.4). As discussed in Chapter 5, similar enhancements are predicted for all the relevant di-Higgs boson final states (bbbb,  $bb\tau\tau$ ,  $bb\gamma\gamma$ , bbWW, bbZZ). For an accumulated luminosity of 3000 fb<sup>-1</sup>, the MTD brings an improvement to the significance of at least 13%, which would require an additional 26% luminosity to be taken if there were no

MTD. Moreover, the MTD will enable the CMS Phase-2 detector to level the luminosity at 200 pileup interactions and accumulate more luminosity than assumed in this study.

In the case of final states with  $H \rightarrow \tau \tau$  decays, additional substantial gain arises from the improved quality of the  $p_T^{\text{miss}}$  reconstruction. The 10–12% improvement in  $p_T^{\text{miss}}$  resolution at 200 pileup interactions from using time information for charged tracks yields a proportional gain in the resolution of  $\tau \tau$  mass reconstruction and in the signal-to-background ratio, and counteracts much of the performance degradation observed in the transition from 140 to 200 pileup events [3]. In addition, the use of time information reduces the rate of pileup jets by about a factor two, leading to an improved performance of Vector Boson Fusion (VBF) tagging, which is useful for the clean observation of some Higgs boson decay modes. More generally, the Higgs boson characterization will benefit from the improved efficiency for multi-object final states (H  $\rightarrow$  4 leptons or  $b\bar{b}$ ) and from the enhanced vertex identification in H  $\rightarrow \gamma \gamma$  decays [8], providing improved precision to the measurement of statistically limited differential distributions, which are sensitive to BSM physics [14].

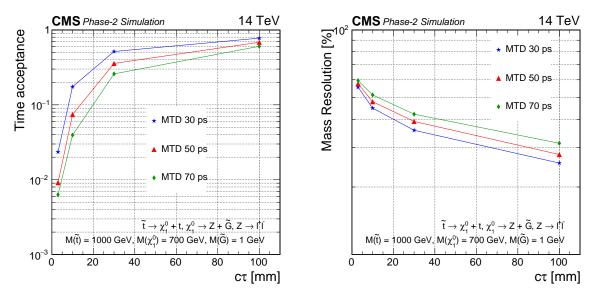

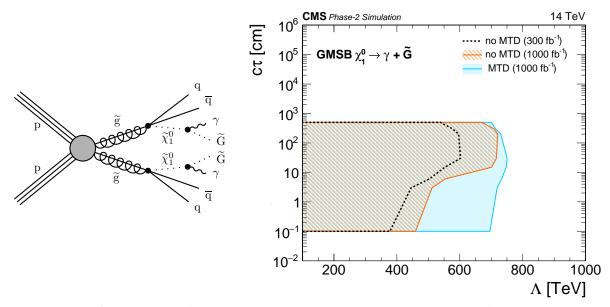

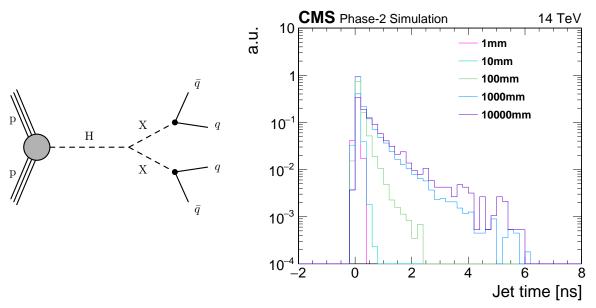

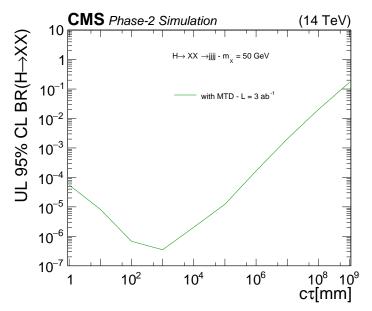

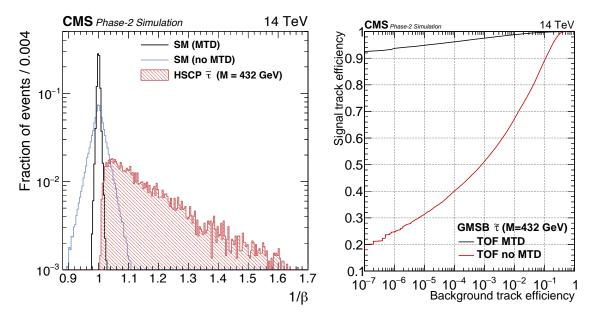

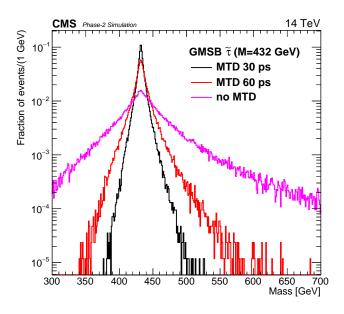

The sensitivity of several searches for new phenomena, including SUSY models, is largely driven by the  $p_T^{\text{miss}}$  resolution. The 10% gain in the  $p_T^{\text{miss}}$  resolution with track timing leads to a reduction by a factor of  $\approx 40\%$  in the tail of the  $p_T^{\text{miss}}$  distribution above 130 GeV (Fig. 5.15), which offsets much of the performance degradation of SUSY searches observed in the transition from 140 to 200 pileup [3]. Additional benefits of the precision timing are anticipated in multi-lepton signatures of BSM physics, owing to the increased efficiency in the selection of isolated leptons, and in signatures where a direct measurement of the time-of-flight (TOF) of heavy particles is exploited. For example, a TOF measurement with the MTD will reduce the model dependence in searches for heavy charged stable particles (HCSPs), now limited to particles that traverse the calorimeters [15]. Moreover, the track-time reconstruction opens a new avenue in searches for neutral LLPs, postulated in many extensions of the SM like Split-SUSY, GMSB, RPV SUSY, Stealth SUSY, SUSY models with compressed mass spectra, and many others discussed in Ref. [16] and references therein, even for cases in which the decays are partially invisible, leading to substantial increases in the sensitivity of such searches and providing a novel method to characterize any future discovery. The space-time information associated with the displaced decay vertex, constructed from the decay daughters that do not escape detection, provides the kinematic constraints that are needed to get a direct measurement of the LLP mass. This is shown for the case of a 700 GeV neutralino,  $\chi_1^0$ , in Fig. 1.4.

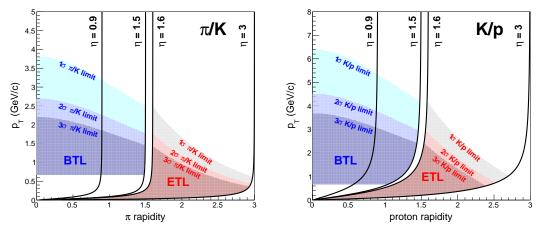

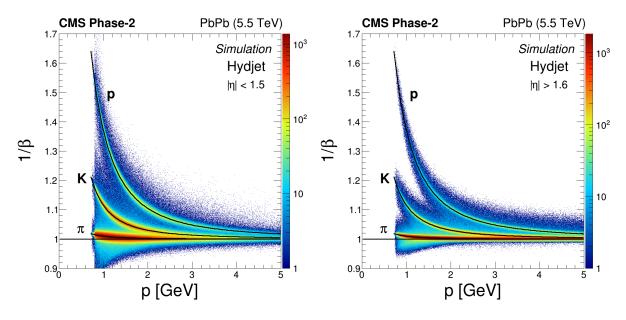

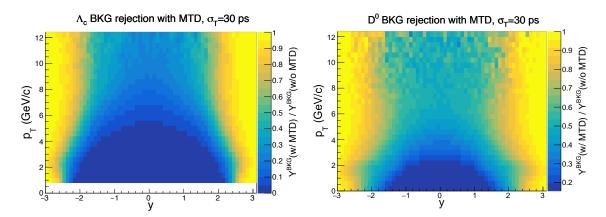

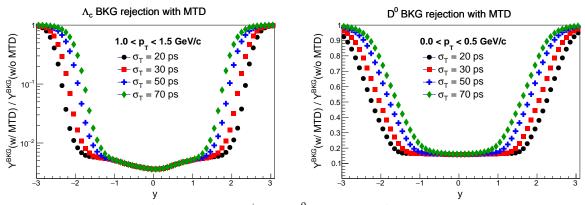

With precision timing, the MTD will also serve as an excellent TOF detector for charged particle (hadron) identification (PID), which is valuable in Heavy Ion physics and in certain specialized studies of low mass QCD and flavor physics. Since a Heavy Ion run is scheduled early in the HL-LHC program, it is appropriate to consider the impact of the MTD based on a time resolution of 30–40 ps. Combined with the wide coverage and full calorimetry of the CMS detector, the MTD will provide unique opportunities for studying the mechanism of interactions between hard colored probes and the quark-gluon plasma (QGP) medium over a wide range of angles, and detailed dynamics of heavy flavor particles over a wide rapidity range in heavy ion collisions. Figure 1.5 shows the expected performance in identifying charged pions, kaons, and protons, as a function of transverse momentum  $p_T$  and rapidity y, in the barrel region and the endcap region. In the barrel region, a minimal  $p_T$  of 0.7 GeV is required for particles to reach the timing detector. At midrapidity, proton identification up to  $p_T \approx 5$  GeV is achievable, while pions and kaons can be separated up to  $p_T \approx 2.5$  GeV. The PID capability will, in general, decrease toward high rapidity due to the rapid increase of total momentum and thus reduced TOF difference. Nevertheless, good performance can still be achieved out to  $|y| \approx 2$ .

Figure 1.4: Left: Impact on signal efficiency for HH  $\rightarrow b\bar{b}\gamma\gamma$  for no-timing, barrel only timing, and barrel plus endcap timing scenarios. The quantity  $y_{HH}$  is the rapidity of the di-Higgs system. Right: Mass peak of a 700 GeV neutralino,  $\chi_1^0$ , with three different lifetimes reconstructed from the kinematic closure of the secondary vertex using time information with 30 ps resolution.

Figure 1.5: Expected performance for charged particle identification in  $p_T$  and rapidity in an early run of the HL-LHC with the proposed MTD, with a time resolution of about 30 ps, which is achievable since there will not yet be significant radiation damage. Different colors of the shaded regions correspond to 1, 2 and 3  $\sigma$  separations. Left: The  $\pi/K$  separation vs  $p_T$  and rapidity y under the pion hypothesis. Right: The K/p separation vs  $p_T$  and rapidity y under the plots in pseudo-rapidity,  $|\eta|$ . The label BTL in these plots indicates the barrel timing detector and the label ETL indicates the endcap timing detectors.

The performance of particle identification for the proposed MTD is compared to that of the TOF systems in the STAR [17] and ALICE [18] experiments at midrapidity (|y| < 0.9-1.0). Table 1.2 summarizes key parameters of the TOF system in each experiment for the radius, r, of the cylindrical barrel region, which is directly related to the particle flight distance, L; the time resolution ( $\sigma_T$ ); and the ratio of r to  $\sigma_T$ , which characterizes the TOF PID capability. Although the CMS-MTD has the shortest flight distance, constrained by the available space in CMS, with the design time resolution of 30 ps, the PID performance is expected to be 40% better

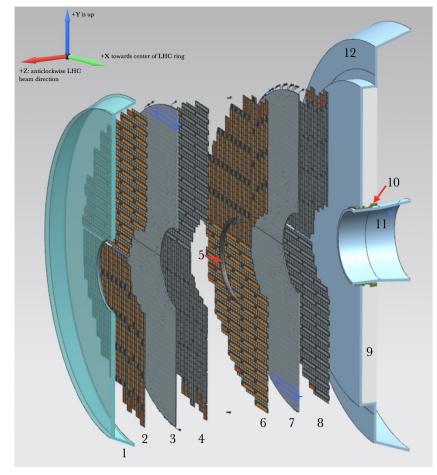

Figure 1.6: A schematic view of the GEANT geometry of the timing layers implemented in CMSSW [20] for simulation studies comprising a barrel layer (grey cylinder), at the interface between the tracker and the ECAL, and two silicon endcap (orange and light violet discs) timing layers in front of the endcap calorimeter.

than the STAR-TOF and about 40% worse than the improved ALICE-TOF performance [19] out to |y| < 0.9, where their coverage ends. More importantly, the wide acceptance of the MTD provides CMS a unique PID coverage out to high rapidity.

Table 1.2: Summary of key parameters of the time-of-flight system for different experiments.

| Experiment | r    | $\sigma_{\mathrm{T}}$ | $r/\sigma_{\rm T}$ (×100) |

|------------|------|-----------------------|---------------------------|

|            | (m)  | (ps)                  | $(m \times ps^{-1})$      |

| STAR-TOF   | 2.2  | 80                    | 2.75                      |

| ALICE-TOF  | 3.7  | 56                    | 6.6                       |

| CMS-MTD    | 1.16 | 30                    | 3.87                      |

# 1.3 Considerations and requirements for the design of the MTD

The design of the MTD is driven by scientific requirements which follow from the physics goals of the HL-LHC program and engineering requirements and constraints. It must conform to the requirements imposed on all detectors inside CMS, such as tolerance to magnetic fields and robust mechanical design that can survive for the full duration of the HL-LHC program. The need to fit within the existing CMS detector and conform to the HL-LHC upgrade schedule puts many additional constraints on the MTD. These key requirements and constraints and some conclusions that emerge from them are presented in this section.

#### 1.3.1 Time resolution

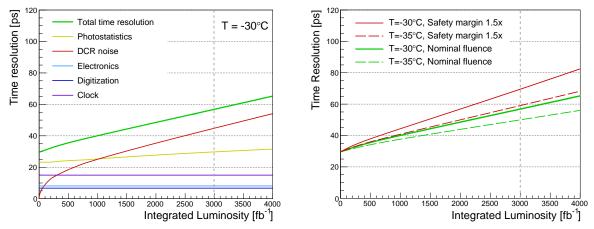

The requirement for the time resolution of the MTD is based on simulations that show that the impact of pileup is reduced significantly for a resolution of 30–40 ps, which is achievable at the beginning of HL-LHC operation, and continues to be effective even though, because of radiation damage, the resolution degrades to 50–60 ps by the end of HL-LHC operation.

#### 1.3.2 Space constraints for detectors and services

A broad range of physics studies motivates the need for nearly hermetic coverage with high efficiency. The overall geometric envelope and the service channels that provide cooling, power, and data-transmission to the already approved detectors for the HL-LHC cannot be changed. There are, then, only two locations where timing detectors can be installed: in the space between the last layer of the outer tracker (OT) and the beginning of the barrel electromagnetic calorimeter (ECAL), which will allow coverage of the barrel region; and in the gap between the Tracker bulkhead and the Phase-2 high granularity endcap calorimeter, (CE), which will permit coverage in the endcap region. In each of these locations, very little space is available for the MTD and its services. Alternatives to these locations were considered but were ruled out because of technical issues.

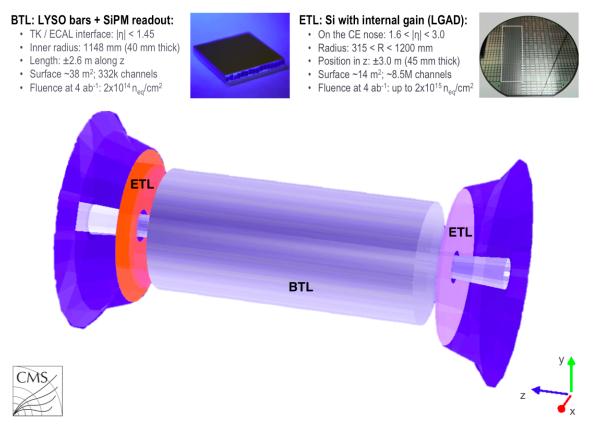

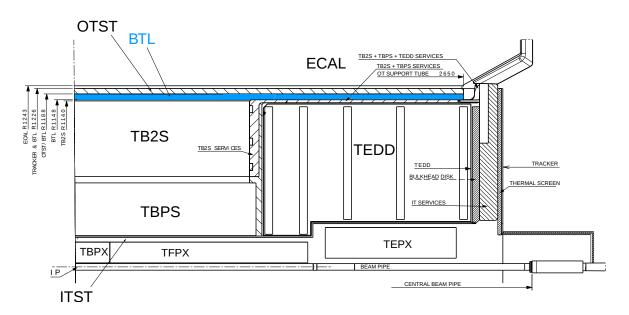

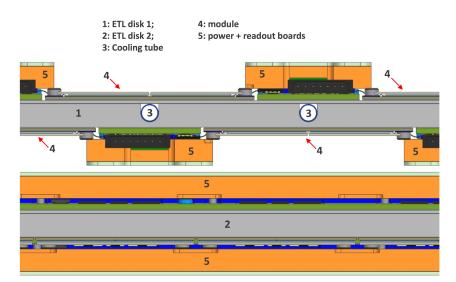

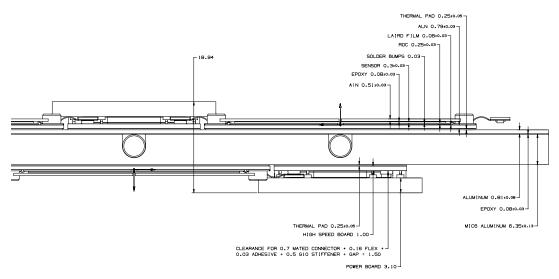

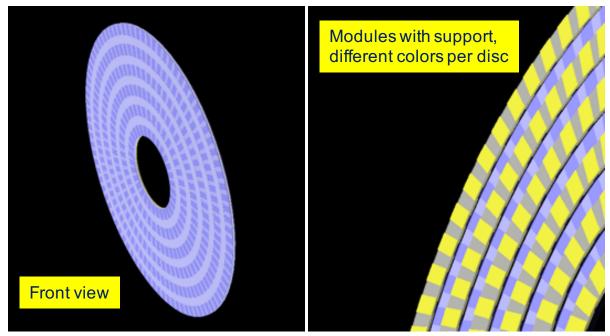

The MTD then must be divided into two sections, the Barrel Timing Layer (BTL) covering  $|\eta| < 1.5$  and the Endcap Timing Layer (ETL) covering  $1.6 < |\eta| < 3.0$ . This division follows the layout of the CMS detector and is necessary for the MTD to fit into the detector, be compatible with the way in which the detector is opened for maintenance, and have access to the service channels necessary for detector operations and readout. It is also driven by technical considerations, especially the significant difference in integrated radiation dose between the two sections.

These considerations lead to the following requirements and conclusions:

- The BTL shall be integrated into the support tube for the OT, occupying a limited space just inside its inner radius, and at larger radius than any of the barrel tracking layers. The space allotted for the BTL is defined to extend 40 mm inward towards the beam from the inner surface of the Tracker Support Tube (TST), a carbon fiber cylinder approximately 2 m in diameter and 5 m long. The BTL services (readout fibers, power cables and cooling pipes) will be integrated along with those of the OT.

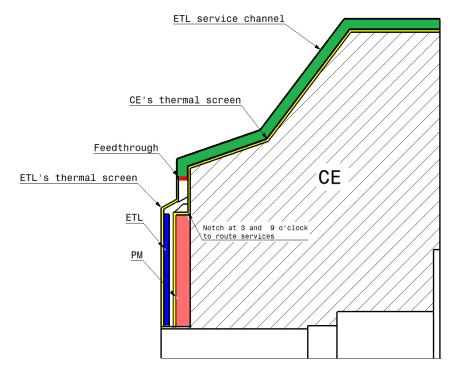

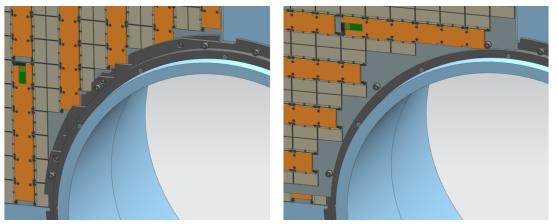

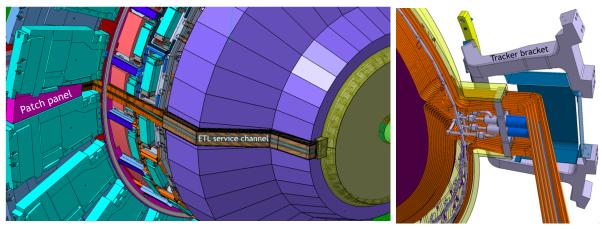

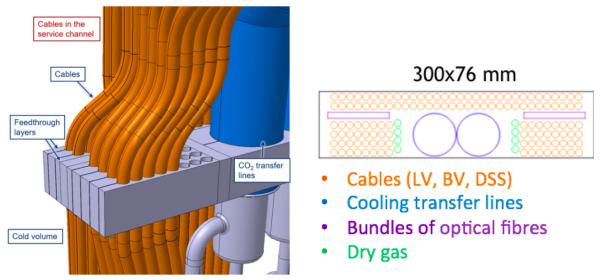

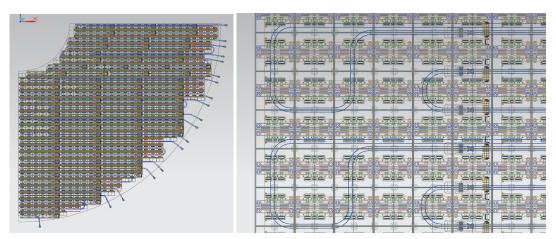

- The ETL shall be supported on the CE nose cone, between the Tracker and the CE, in a volume that is mechanically and thermally separated from the CE. The geometry of the nose cone prevents the ETL from extending to  $|\eta| > 3$ , so it cannot completely cover the full acceptance of the upgraded Tracker, which will reach to  $|\eta| = 4$  for the HL-LHC. Currently, a longitudinal space of 45 mm between the Tracker and the CE has been allocated for the ETL on each end of CMS. The ETL services shall fit into the channel just outside the CE.

Figure 1.6 shows a schematic view of the proposed MTD layout, comprising both BTL and ETL sections, as implemented in the GEANT simulation of the CMS detector.

#### 1.3.3 Impact on Tracker and CE integration and installation

The CMS Outer Tracker, which was part of the original CMS construction project, will be removed and replaced with a completely new device. Since the OT's silicon layers and the BTL both reside in the TST, the integration of the two detectors must be carefully orchestrated. The BTL installation has to be completed either before the integration of the Tracker into the TST has started or at specific points during the integration of the Tracker Barrel (TB). The integration of the BTL must be completed before the start of the integration of the Tracker Endcap Disks, which must proceed on schedule. The requirement that the BTL integration shall not interfere with the integration of the Outer Tracker has strong implications for the development and construction schedule of the BTL.

The ETL is mounted on the nose of the CE, which is also a completely new detector that will replace the current endcap calorimeter. However, since the ETL and CE occupy physically different volumes and are separated thermally (although possibly sharing the cooling plants), the two detectors can be integrated separately. The ETL can be installed on the CE when it is above ground and lowered with it or it can be installed in the experimental cavern after the CE is lowered. It is possible to install all or part of the ETL in a Technical Stop (LHC annual maintenance period of a few months) or Long Shutdown after the initial run of the HL-LHC. The ETL schedule is therefore not tightly coupled to the CE and it can potentially exploit a longer period to complete development and construction.

#### 1.3.4 Impact on the performance of other detectors

The presence of the BTL in the TST requires a reduction in the radius of the outermost barrel tracking layer. This has been shown to have only a negligible impact on the tracking performance and momentum resolution.

Since the BTL also shares the dry/cold volume with the tracker, it must not create thermal, electronic or mechanical problems that would affect tracker performance. Since the BTL is also quite close to the barrel ECAL, which requires precise temperature control, it must not disturb the ECAL's thermal environment.

In order for the ETL detector to be accessible for repairs and replacements of faulty components when the CMS detector is open during shutdowns, the ETL will occupy an independent cold and dry volume that is isolated and operated separately from the CE. ETL services will be routed near the CE and must not create thermal, electronic, or mechanical problems that would affect CE performance. While the ETL is in its own cold volume, it may share a cooling plant with the CE and, if so, must operate within specifications that guarantee that it will not affect the CE performance.

The electron and photon energy resolution of the calorimeters is degraded by the material in front of them. The additional material in the timing layers should not degrade the performance of the calorimeters in a significant way.

# 1.3.5 Segmentation/occupancy

In order to ensure that useful timing information is available for as many charged tracks as possible, the maximum sensor size must be compatible with an occupancy less than a few percent, ensuring a large probability for single hits needed for unambiguous time assignment. Dead area between sensors must be minimized to preserve the efficiency. The detector must also produce a manageable data volume.

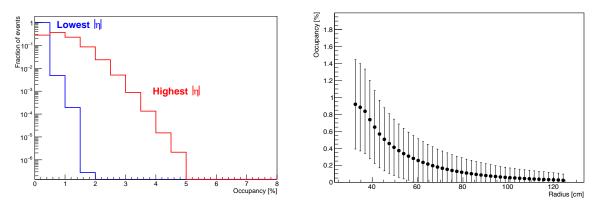

For both the BTL and ETL, the choice of the size of an individual detector element (cell) is also a compromise between occupancy, sensor characteristics, including electronics considerations such as input capacitance and manufacturing issues, total power needs (number of channels), and cost. A maximum per-channel area of order 1–2 cm<sup>2</sup> is suitable for the BTL. For the ETL, a sensor cell-size of  $\approx 2 \text{ mm}^2$  at  $|\eta| \approx 3$  is a good compromise between the spread in the time response within a channel, low occupancy, and low channel count rate. For the ETL, the occupancy is significantly less at lower  $\eta$ .

#### 1.3.6 Compatibility with CMS Trigger and Data Acquisition systems

The current CMS trigger uses two levels of selection: a first level, Level-1, based only on signals from the calorimetry and muon detectors, that uses dedicated hardware to do simple computations very quickly, in less than 4  $\mu$ s, on every bunch crossing and passes about 100 000 crossings/s with interesting events to the next level; and second, the High Level trigger (HLT), which uses the full information from the detector, including charged particle tracking, to do much more sophisticated computations on a cluster of thousands of advanced microprocessors to choose about 1000 crossings/s with most interesting events to record for detailed analysis.

The Level-1 trigger for the HL-LHC will add charged particle tracking based on the Outer Tracker to the information from the calorimeters and muon detectors. Level-1 will have a latency of 12.5  $\mu$ s and an average rate of acceptance of 750 kHz. The MTD electronics must be capable of delivering data registering the time at which a MIP traverses the sensitive volume, known as a time stamp, and other required information, such as pulse height for time-walk correction, upon receipt of a Level-1 Accept (L1-A) from the CMS trigger without introducing readout dead time. The format of the data from the MTD must conform to CMS standards. The readout must meet CMS performance requirements, including very low data loss. The electronics must be able to receive and respond to fast and slow control information, including throttling, reset and resync signals, and must produce and deliver the monitoring information needed to ensure proper operation.

There is a proposal to use timing information from the MTD in the Level-1 trigger. One key requirement for this new capability is that it does not add significantly to the cost, power consumption, or complexity of the MTD front-end or back-end electronics. This possibility is discussed in Section 4.3 and Appendix E, and briefly summarized in this introduction in Section 1.4.5.

#### 1.3.7 Operating temperature

The operating temperature of both the BTL and the ETL must be kept low because the time jitter caused by noise and leakage currents, which are strong functions of temperature, has a significant effect on the overall time resolution. Radiation exposure increases the noise or dark current rate (DCR) and may lower the signal from MIPs. Heavily irradiated detectors can partially recover from the radiation-induced damage if warmed to room temperature or above, during periods when there are no collisions, reducing the DCR.

Therefore, operating temperatures in BTL and ETL shall be maintained as close as possible to -30 °C, a level that can be comfortably achieved with cooling systems that have been used in CMS and which limits the noise-induced jitter to an acceptable level. In fact, 30 °C should be considered a conservative baseline and the possibility of going somewhat lower will discussed in a few places below. The cooling and temperature control, as well as the operational procedures for the MTD, shall allow the maintenance of the detectors at room temperature for extended periods of time, for example during LHC shutdown periods.

In order to achieve these goals, the design of the cooling system for the detector modules must ensure efficient heat removal from the sensors. Furthermore, the MTD modules and their supports will undergo several thermal cycles as part of testing as well as during operations; therefore the MTD modules shall provide a robust mechanical structure that shall not deteriorate in fit or function even after many thermal cycles from -30 °C to +20 °C.

#### 1.3.8 Radiation tolerance

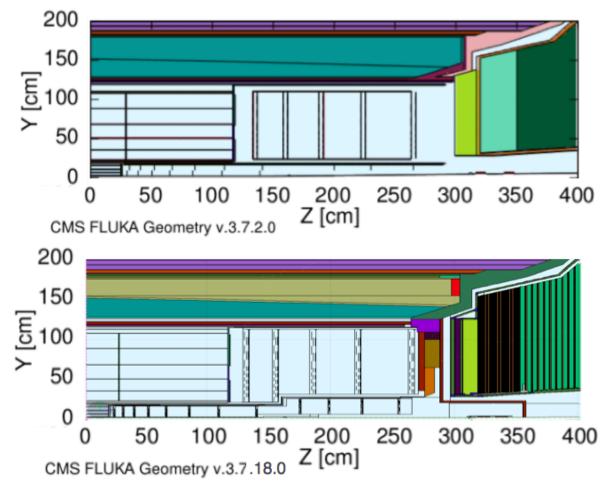

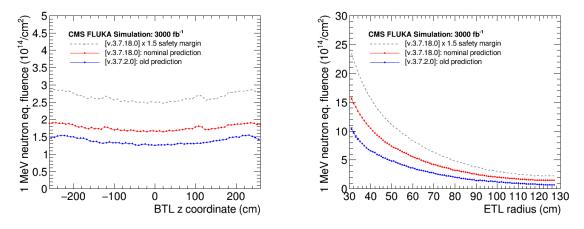

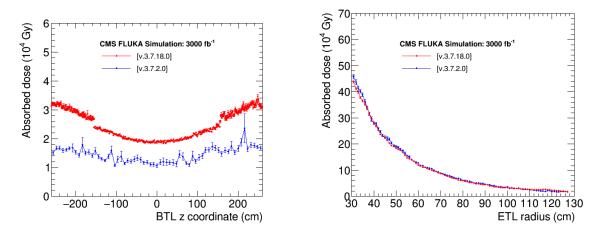

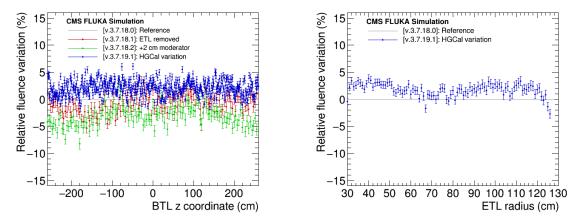

The CMS detectors for Phase-2 described in the CMS Upgrade TDR documents are designed to operate efficiently throughout the HL-LHC phase, up to an integrated luminosity of at least 3000  $\text{fb}^{-1}$ . The radiation level predictions at the location of each detector are based on the FLUKA Monte Carlo multi-particle transport code [21, 22], using a preliminary implementation of the Phase-2 CMS geometry, described in the CMS Tracker TDR [4]. The geometry model includes only minimal updates to the Phase-1 geometry model, such as the Phase-2 layer structure of the Tracker, an average description of the HGCal material without longitudinal segmentation, and the replacement of the CMS endcap preshower with an 18 cm thick neutron moderator. This model was also adopted for radiation level predictions in the MTD Technical Proposal [8], although it did not include the implementation of the MTD itself, and the neutron moderator in front of the endcap calorimeter was thicker than physically allowable with inclusion of the MTD. To cover the uncertainties in the predictions associated with the approximate geometry model, all CMS detectors were required to have a minimum margin of 1.5, without performance degradation compared to 3000  $\text{ fb}^{-1}$ . The reduction of the neutron moderator from 18 to 12 cm, to accommodate the endcap timing layer of the MTD, was checked to give an increase lower than 15% in the neutron fluence in the MTD and in the Tracker.

In this TDR, the radiation level predictions are based on a refined implementation of the CMS Phase-2 geometry, comprising the description of the MTD geometry; a neutron moderator with a thickness of 12 cm; an accurate description of the services in the transition region between the Tracker bulkhead and the CE and in the service channel between the barrel and the endcap; and up-to-date descriptions of the Phase-2 envelope of the endcap detectors, the HGCal longitudinal segmentation, and the beam pipe. The details of the model and of the uncertainties associated with the fluence and radiation dose predictions are described in Appendix A.

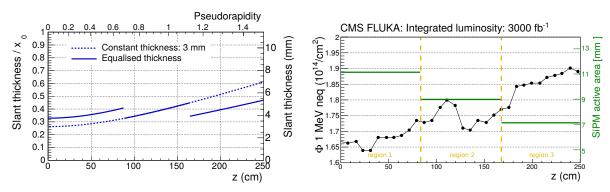

Table 1.3 shows the expected particle fluences and radiation doses at the location of the timing layers in the barrel and the endcaps, for an integrated luminosity of 3000 fb<sup>-1</sup>. At this integrated luminosity the detectors will have received radiation doses of up to about 30 kGy and a "1 MeV neutron equivalent fluence",  $n_{eq}/cm^2$ , of up to  $1.9 \times 10^{14} n_{eq}/cm^2$  in the barrel, and 450 kGy and  $1.6 \times 10^{15} n_{eq}/cm^2$  in the high- $\eta$  part of the endcap. For radiation tolerance qualification, all the MTD components are required to stand radiation levels at least a factor 1.5 (safety factor) larger than the nominal prediction. The fluence and the radiation doses corresponding to this safety factor are also given in the table. A safety factor of 1.5 covers the uncertainties in the predictions from the geometry model, the pp inelastic cross-section, and possible sensor-to-sensor variations, as discussed in Appendix A.

The MTD sensor technologies shall be validated up to  $3 \times 10^{14}$  and  $3 \times 10^{15} n_{eq}$ /cm<sup>2</sup> in the barrel (Chapter 2 and Appendix B) and in the endcap (Chapter 3), respectively. The endcap design, with the combination of two hits per track, enables the ETL to be operated up to these radiation levels with a constant per-track resolution of 35 ps. The BTL, instead, will experience a linear degradation in the time resolution, at the conservative working conditions of -30 °C, combined with annealing at room temperature during the winter shutdowns. Operation at lower temperature or short annealing periods at +50 °C would enable mitigation of the effect, as discussed in Appendix B. The above figures provide a safety margin of 1.6 and 1.8 for BTL and ETL respectively, for an integrated luminosity of 3000 fb<sup>-1</sup> at the point with largest radiation level. The addition of the MTD will enable CMS to level the HL-LHC luminosity at 200 collisions per beam crossing, thus providing the potential to integrate up to 4000 fb<sup>-1</sup> of luminosity, including 300 fb<sup>-1</sup> from Phase-1. In this case, the safety margin would be reduced to a factor of about 1.3.

|        |          |               |               |                       | 1            |                                  |                       |

|--------|----------|---------------|---------------|-----------------------|--------------|----------------------------------|-----------------------|

|        |          |               |               | 3000                  | ) fb $^{-1}$ | 1.5×30                           | $100 \text{ fb}^{-1}$ |

| Region | $ \eta $ | <i>r</i> (cm) | <i>z</i> (cm) | $n_{eq}/cm^2$         | Dose (kGy)   | n <sub>eq</sub> /cm <sup>2</sup> | Dose (kGy)            |

| Barrel | 0.0      | 116           | 0             | $1.65 \times 10^{14}$ | 18           | $2.48 \times 10^{14}$            | 27                    |

| Barrel | 1.15     | 116           | 170           | $1.80 \times 10^{14}$ | 25           | $2.70 \times 10^{14}$            | 38                    |

| Barrel | 1.45     | 116           | 240           | $1.90 \times 10^{14}$ | 32           | $2.85 \times 10^{14}$            | 48                    |

| Endcap | 1.6      | 127           | 303           | $1.5 \times 10^{14}$  | 19           | $2.3 \times 10^{14}$             | 29                    |

| Endcap | 2.0      | 84            | 303           | $3.0 \times 10^{14}$  | 50           | $4.5 \times 10^{14}$             | 75                    |

| Endcap | 2.5      | 50            | 303           | $7.5 \times 10^{14}$  | 170          | $1.1 \times 10^{15}$             | 255                   |

| Endcap | 3.0      | 31.5          | 303           | $1.6 \times 10^{15}$  | 450          | $2.4 \times 10^{15}$             | 675                   |

Table 1.3: Nominal radiation doses and fluences at various locations of the timing layers after  $3000 \text{ fb}^{-1}$ . The last two columns show the radiation levels providing a safety margin of a factor 1.5. The fluence is normalized to 1 MeV neutron equivalent in silicon.

For the BTL, no maintenance access for repairs is possible for the lifetime of the HL-LHC while the ETL shall be designed to be accessible for repairs in situ and shall be capable of being removed from the collision hall, repaired, and reinstalled during an extended Technical Stop.

To ensure that the MTD, as a whole, can maintain the required performance through the lifetime of the HL-LHC, each component that will be located in the experimental cavern must be shown to function properly when exposed to the full expected radiation dose plus the additional amount corresponding to the safety factor. The silicon photomultipliers (SiPMs) chosen as the photosensor in the barrel shall maintain a DCR within specifications up to a fluence of  $3 \times 10^{14} n_{eq}/cm^2$  and the front-end BTL ASICs shall be radiation tolerant and single event upset (SEU) compliant to the same fluence. The low gain avalanche detectors (LGADs) chosen as the sensors in the endcap shall be tolerant to  $3 \times 10^{15} n_{eq}/cm^2$  at  $|\eta| = 3$ , and the ETL front-end ASIC shall be radiation tolerant and SEU compliant also up to  $3 \times 10^{15} n_{eq}/cm^2$ . When SEUs do occur, the system must be equipped with proper diagnostics and controls to detect them and reset them quickly.

# 1.4 Overview of the MIP Timing Detector design

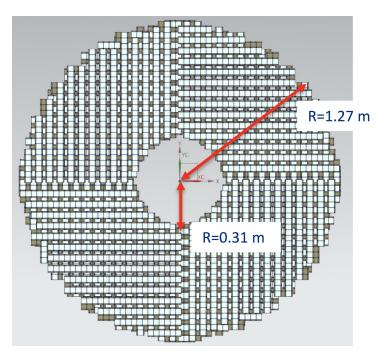

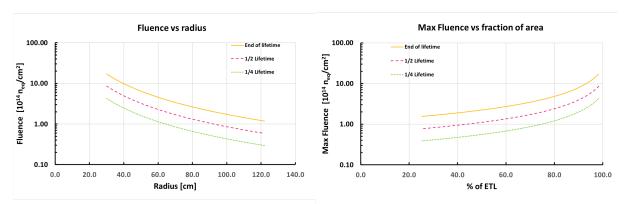

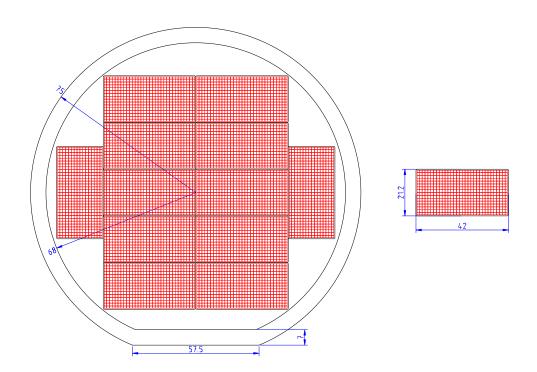

Mechanical constraints, performance, radiation tolerance, cost, and the upgrade schedule led to a detector design consisting of a thin layer between the Tracker and the calorimeters, divided into a barrel ( $|\eta| < 1.5$ ) and two endcap sections covering up to  $|\eta| = 3.0$ . The requirements on the MTD are rather different in the barrel and endcap regions. The radiation environments are quite dissimilar, with the outer radius of the ETL,  $\approx 1.2$  m, receiving about the same dose as the highest  $|\eta|$  part of the BTL but the inner radius, at  $\approx 0.3$  m, receiving nearly a factor of 30 more. Moreover, the surface area of the BTL is about 2.5 times the surface area of the two endcaps.

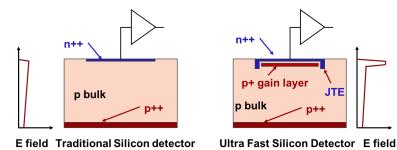

Five technologies were investigated and studied in dedicated beam tests and radiation exposures, building upon and extending long-standing R&D programs [23–33]. For the BTL, the best available technology is a crystal scintillator that is read out with SiPMs [23–25], which are pixelated avalanche photodiodes operating in Geiger breakdown mode. For the ETL, the best performance is achieved with LGADs [26–28], which are silicon sensors with internal gain of about 10–30.

The SiPM technology, used in the BTL, is not sufficiently radiation tolerant to work in the endcap and the cost of instrumenting the barrel with LGADs is prohibitive. The two different sensors also require rather different front-end ASICs. Moreover, the schedule constraints are also different. There is less time for development and construction for the BTL, requiring the

choice of a technology that needs relatively little R&D and for which production in industry is well-established. Consequently, in the detectors and the associated front end electronics, the synergy between the BTL and ETL is limited. The BTL and ETL do share common clock and backend systems, cooling, and detector slow controls and safety systems.

The following sections give a brief introduction and overview to the MTD design. Detailed descriptions are provided in the three chapters that follow.

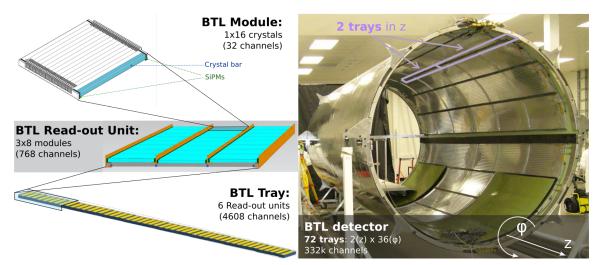

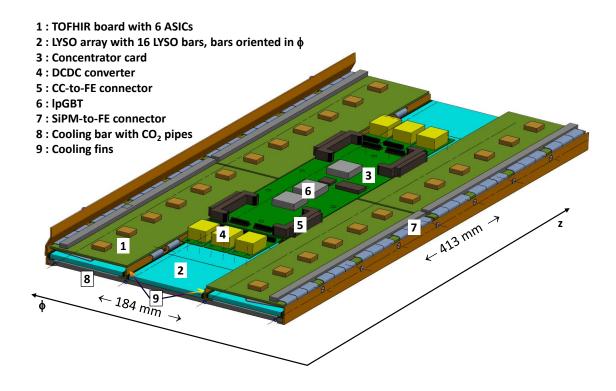

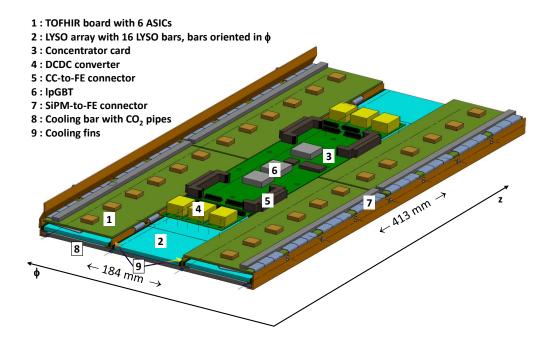

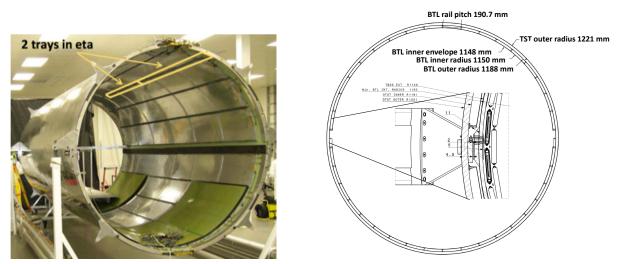

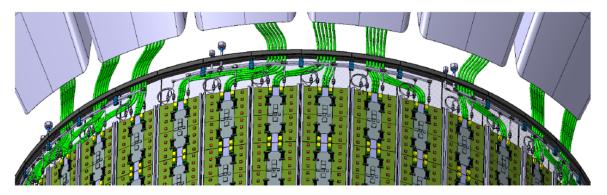

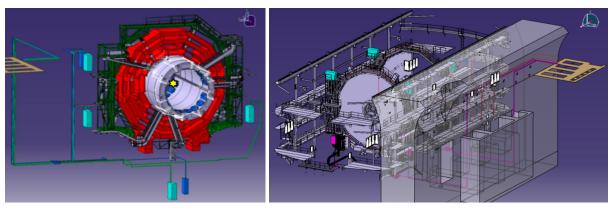

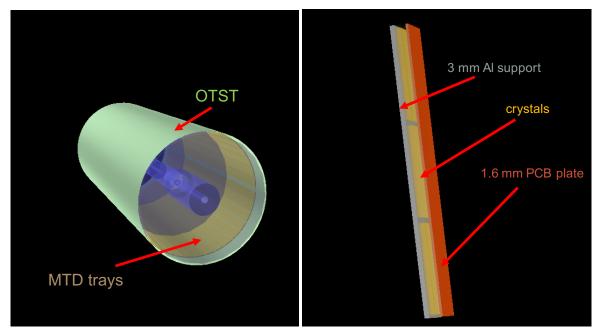

#### 1.4.1 Overview of the Barrel Timing Layer

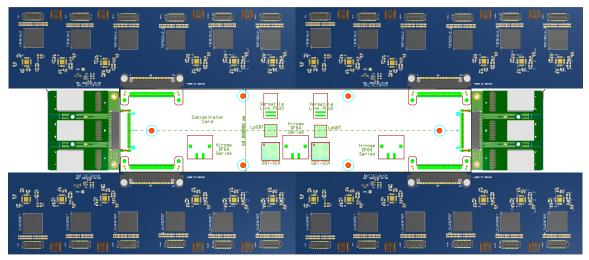

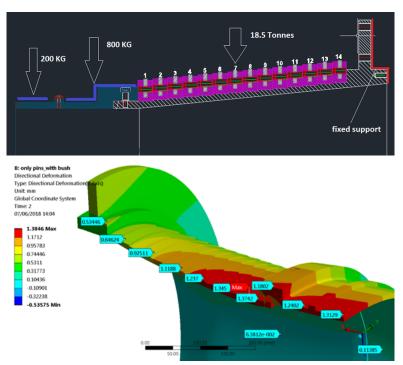

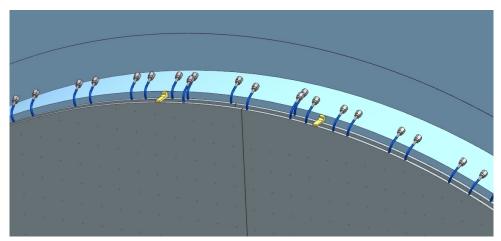

The Barrel Timing Layer is a thin, cylindrical detector that will be housed inside the TST, shown in Fig. 1.7, at its outer radius. The inner boundary of its radial envelope is 1148 mm from the beam and the outer boundary is at 1188 mm, for a maximum radial extent of 40 mm. Its overall active length in z is about 5000 mm. The total active surface is about 38 m<sup>2</sup>. The location of the BTL in the Outer Tracker volume imposes many constraints on its design and operation, described above. Importantly, the components of the BTL must be scheduled for installation and integration into the TST so as to not disrupt or delay the Tracker installation and integration. This places constraints on the construction of BTL on-detector components, which must be available for installation by the third quarter of calendar year 2023. Finally, the TST is embedded in CMS and cannot be removed or serviced during the lifetime of the HL-LHC so that the reliability of the BTL is a primary consideration, demanding excellent and robust design and careful testing and integration.

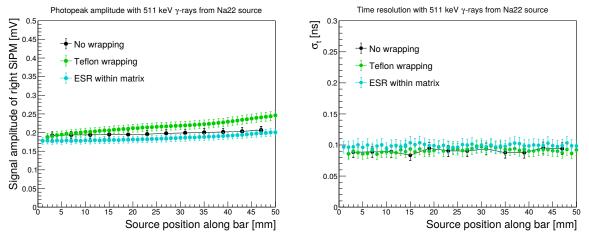

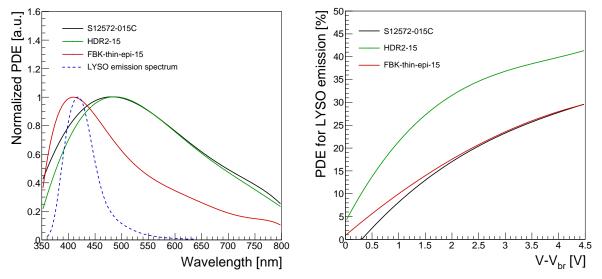

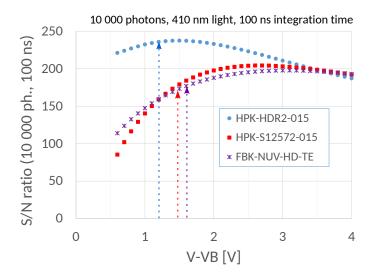

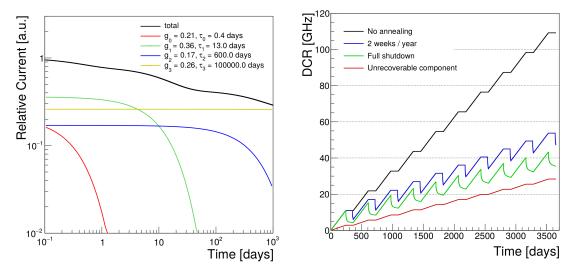

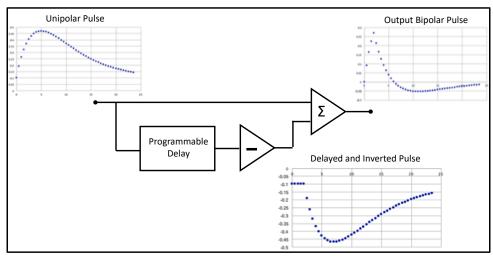

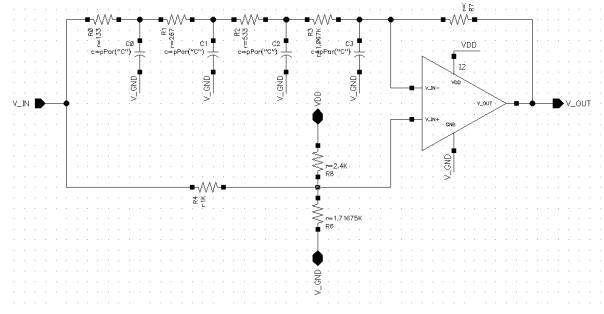

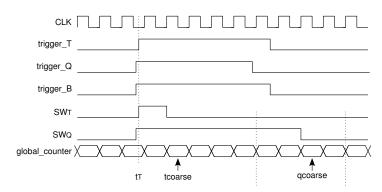

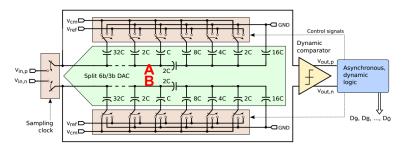

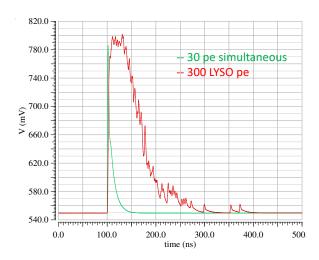

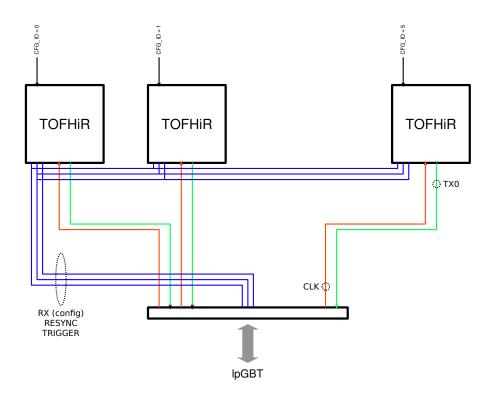

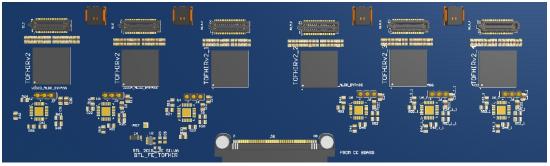

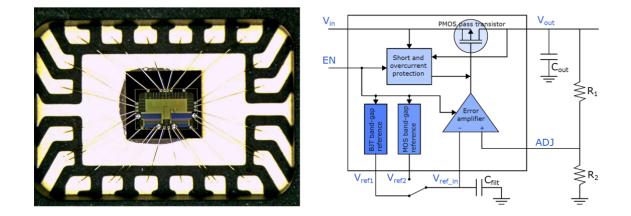

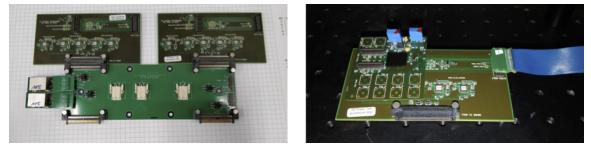

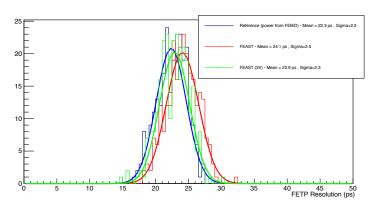

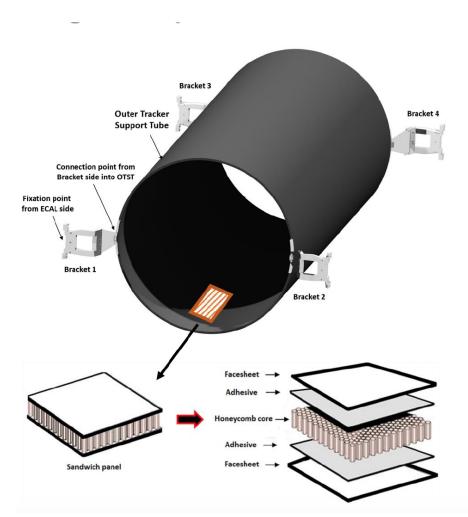

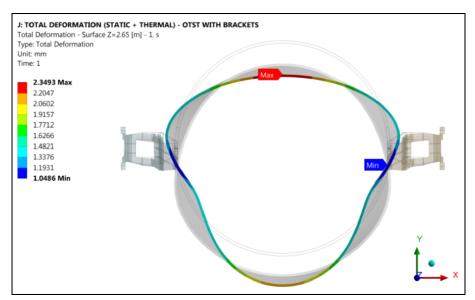

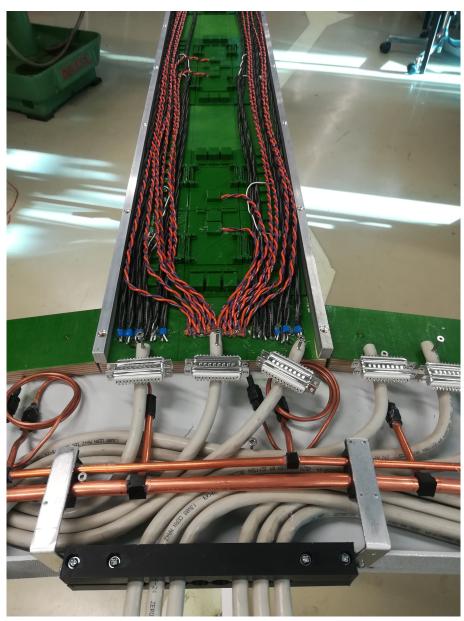

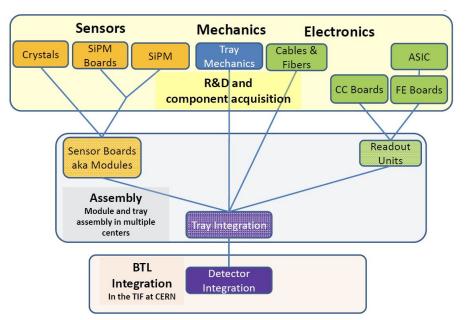

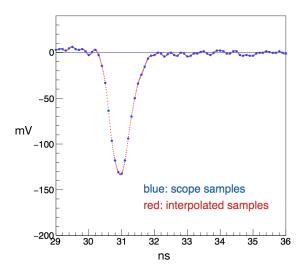

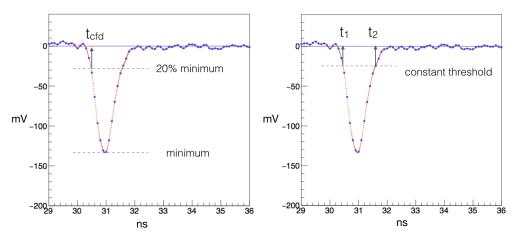

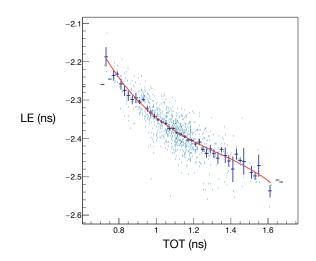

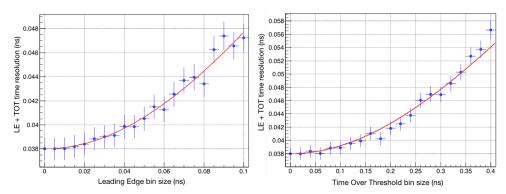

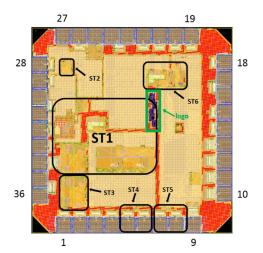

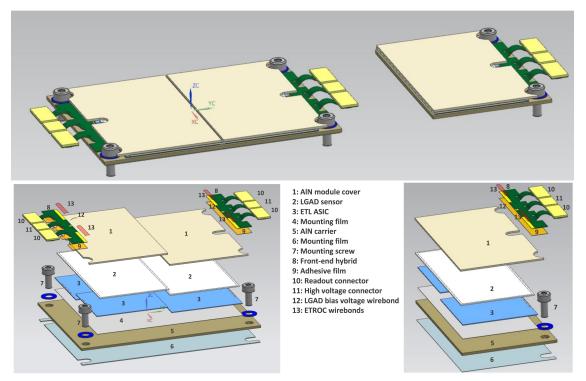

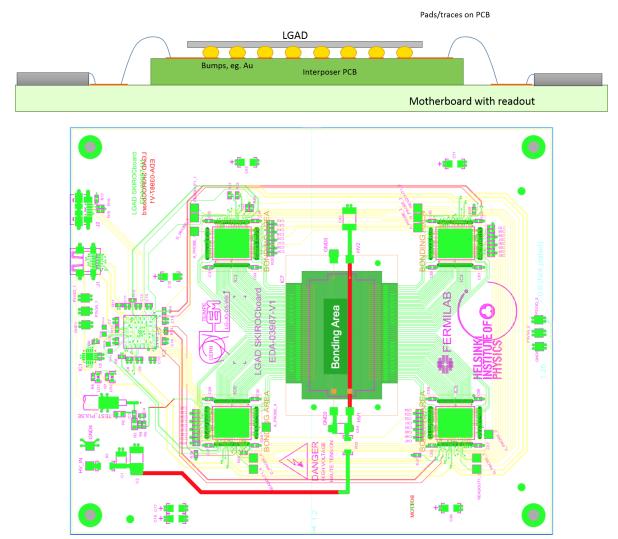

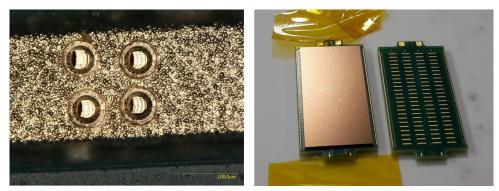

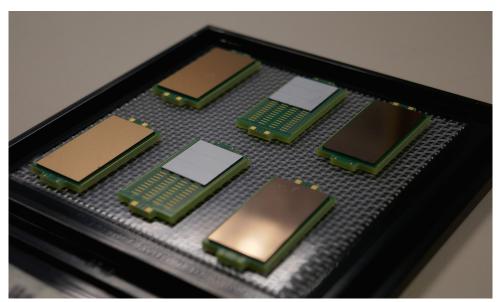

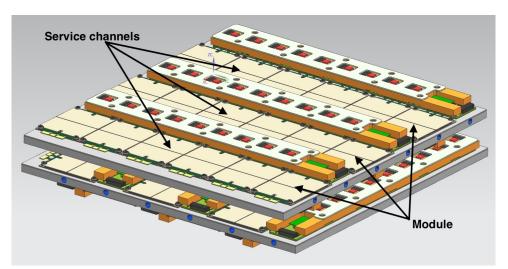

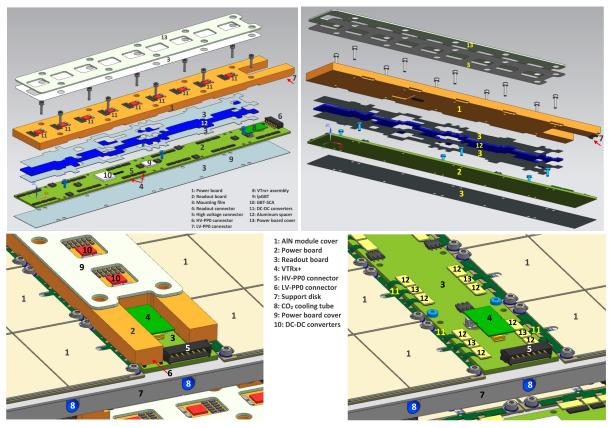

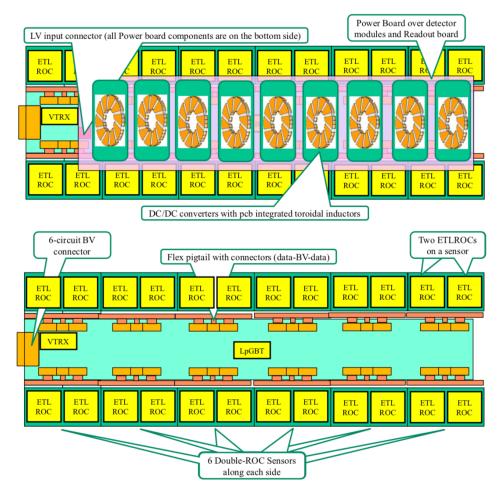

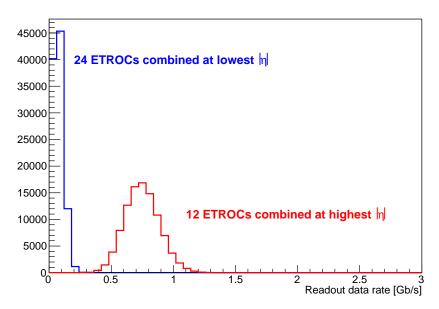

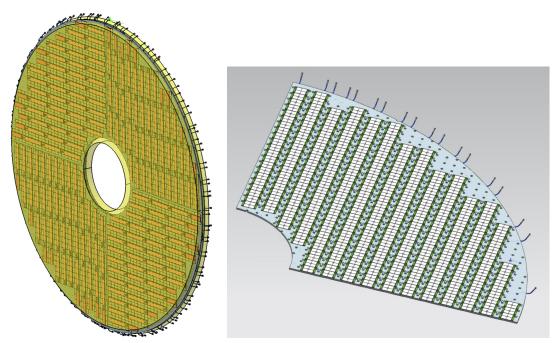

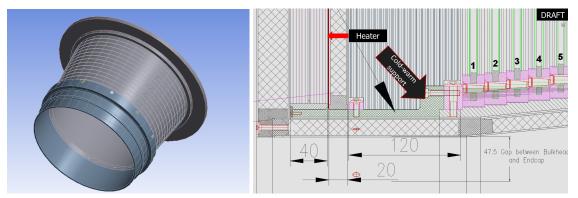

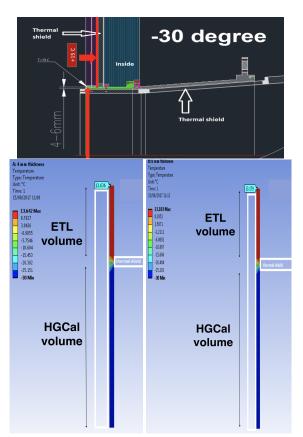

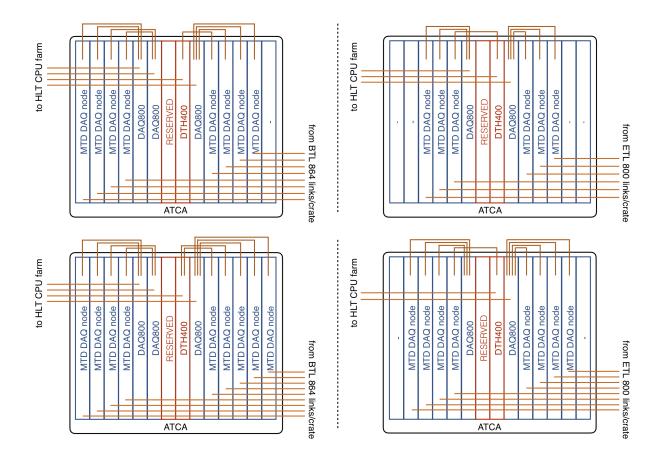

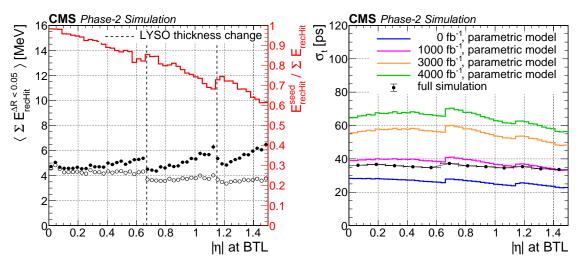

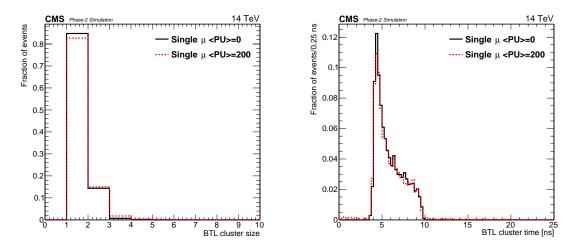

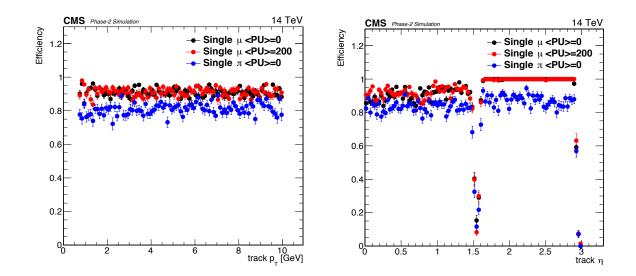

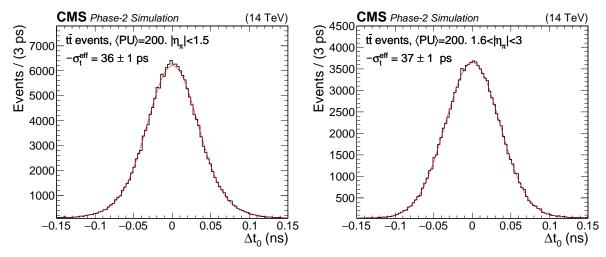

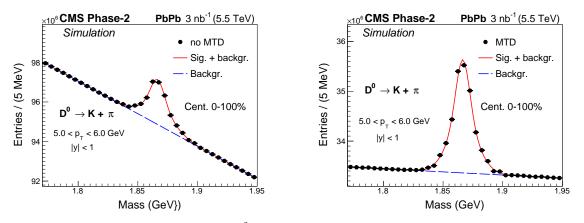

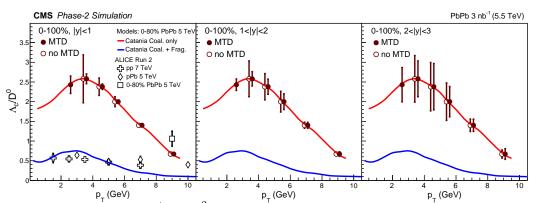

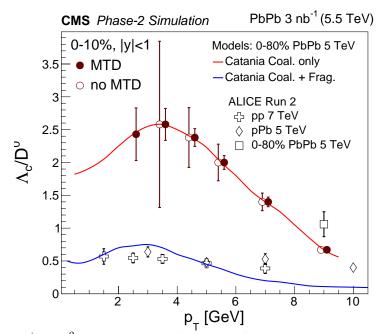

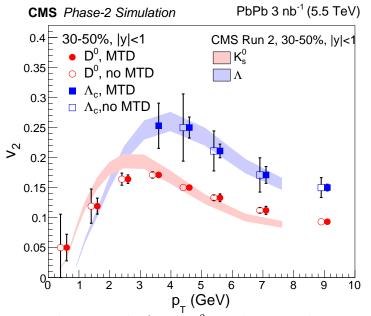

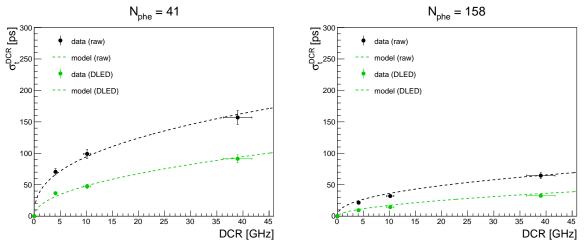

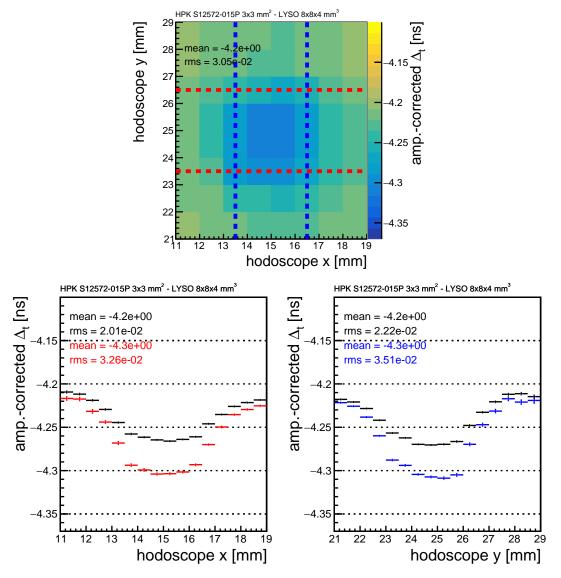

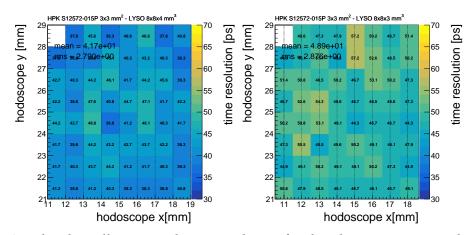

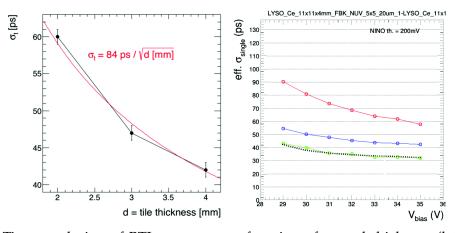

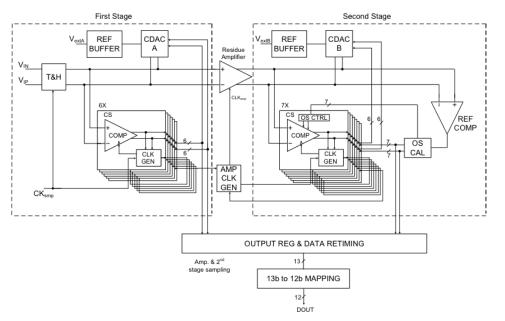

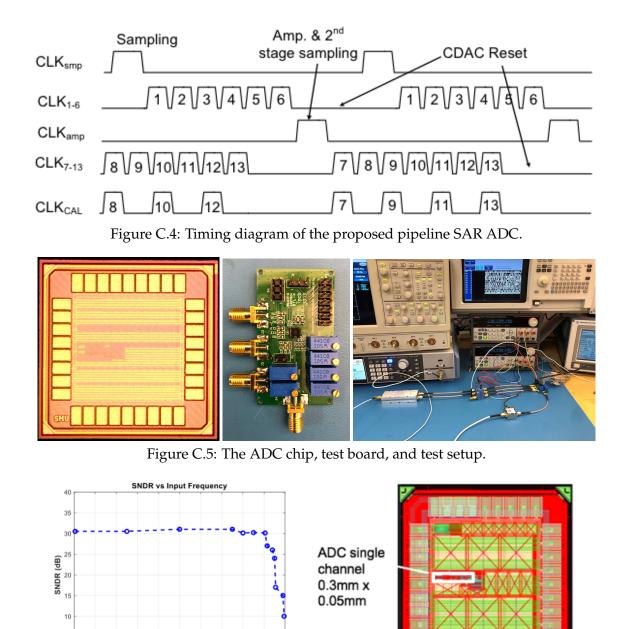

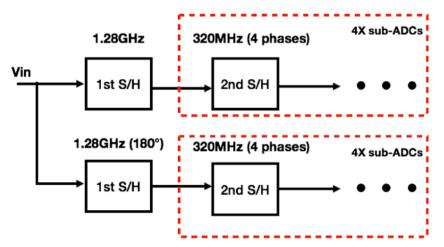

To satisfy the concerns related to schedule and accessibility, it was decided to choose technologies for the sensor that are well-established and with which CMS has experience. Both LYSO:Ce scintillating crystals and SiPM devices are technologies for which there are well-established production and assembly procedures and facilities in industry. The R&D for a precision timing application is well advanced, and small prototypes consisting of LYSO:Ce crystals read out with SiPMs have been proven capable of achieving time resolution below 30 ps [34]. Both the crystals and the SiPMs are already proven to be radiation tolerant up to a neutron equivalent fluence of at least  $2 \times 10^{14}$  cm<sup>-2</sup> and a total integrated dose of 25 kGy, when cooled to approximately -30 °C. The readout electronics can be adapted from existing positron emission tomography (PET) applications, which include time-of-flight (TOF-PET) measurement capability [35–37].