## Development and evaluation of prototypes for the Phase-II upgrade of the pixel detector of the ATLAS experiment

## Jonathan Thomas Taylor, on behalf of the ATLAS Collaboration

**Abstract**—The ATLAS tracking system will be replaced by an all-silicon detector in the course of the planned HL-LHC accelerator upgrade around 2025. The innermost five layers of the detector system will be pixel detector layers which will be most challenging in terms of radiation hardness, data rate and readout speed. A serial power scheme will be used for the pixel layers to reduce the radiation length and power consumption in cables. New elements are required to operate and monitor a serially powered detector including a detector control system, constant current sources and front-end electronics with shunt regulators. A prototype for the outer central pixel layers is built to verify the concept and operate multiple serial power chains as a system test. The evaluation of both the readout of multi-modules and mechanical integration are further aims of the prototyping campaign.

Index Terms—ATLAS, High Energy Physics, serial powering, silicon pixel detectors, shunt-LDO

THE ATLAS experiment [1] at the LHC is preparing for **L** an extensive modification of its detector in the course of the planned HL-LHC accelerator upgrade around 2026 which includes a replacement of the entire tracking system by an all-silicon detector (Inner Tracker, ITk). This new tracker will have both silicon pixel and silicon strip subsystems aiming to provide tracking coverage up to  $|\eta| < 4$ . In order to achieve excellent tracking performance, radiation hardness, and high rate capability, high performance readout electronics is essential. Moreover, services and stable, low mass mechanical structures are essential and present challenges for the system design. The ITk pixel detector will be instrumented with new sensors and readout electronics providing improved tracking performance and radiation hardness compared to the current detector. Because of the very high radiation level inside the detector, the first part of data transmission has to be implemented electrically with signals to be converted for optical transmission at larger radii. To save material in the servicing cables, serial powering is the baseline option for the ITk pixel system [2], [3], [4]. To this end, extensive tests are being carried out with modules based on the front-end chip FE-I4 developed for the Insertable B-layer (IBL) in ATLAS [5]. The suitability of FE-I4 for these tests is due to the dedicated shunt-regulators (Shunt-LDO) [6] contained on each chip that can be operated with the constant current needed for serial powering. In order not to lose a whole serially powered chain (in the occurrence of a single module failure), a special protection chip should be placed on the module flex that is being developed to switch on/off individual modules and for monitoring of the module parameters like temperature and low voltage. A full-scale prototyping campaign is ongoing for the outer

J. Taylor with the Department of Physics, University of Liverpool, L69 7ZE E-mail: jon.taylor@cern.ch

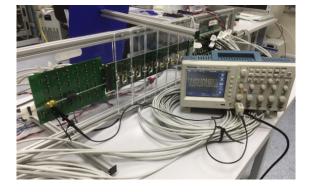

Fig. 1. A prototype developed for the central OB pixel tracker with seven quad pixel modules mounted on a carbon support including titanium cooling pipes. Powering is conducted as one serial powering chain and including the serial powering protection chip.

barrel (OB) and outer end-cap (EC) detector sections of the ITk. Prototypes based on FE-I4 modules with four or two readout chips bump-bonded to one silicon sensor are being built and tested. The campaigns for OB and EC include various elements of a full system from pixel modules, services, detector control system and interlock, to power supplies, readout systems and local supports. Full demonstrators will include multiple serial power chains with up to 16 AC coupled modules in one chain. The first OB prototype with seven quad modules is shown in Figure 1 and the EC demonstrator in Figure 2. The experience and results of the prototyping campaign show the high performance of the prototypes. The aim of the project is to define specifications for building and operating the detector system in a serial powering scheme with multiple silicon pixel modules. The identification of failure modes and the derivation of metrics for comparing different operating conditions allow planning for any needed update to the specifications for the future front-end chip and power supplies.

1

Fig. 2. A prototype developed for the EC using a carbon fibre straight local support with embedded Ti cooling pipe and six FE-I4 quad modules mounted on each side. Powering is conducted as two serial powering chains of six modules each that can also be connected together to form a single serial powering chain twelve modules long. Serial powering protection chips are not included.

## REFERENCES

- [1] The ATLAS Experiment at the CERN Large Hadron Collider, AT-LAS Collaboration, (2008) JINST 3 S08003

- [2] Serial powering of pixel modules, T. Stockmanns et al. (2003) NIM A511, 174-179

- [3] D. Bao Ta et al., NIM A557 (2006) 445-459

- [4] A serial powering scheme for the ATLAS pixel detector at sLHC, L. Gonella et al., (2010) JINST 5 C12002

- [5] The FE-I4 Pixel Readout Integrated Circuit, M. Garcia-Sciveres et al., (2010) NIM A636 S155.

- [6] An Integrated Shunt-LDO Regulator for Serial Powered Systems, Michael Karagounis et al., (2009) Proceedings of ESSCIRC