# Run Control Software for the Upgrade of the ATLAS Muon to Central Trigger Processor Interface (MUCTPI)

Ralf Spiwoks<sup>1</sup>, Aaron Armbruster<sup>1</sup>, German Carrillo-Montoya<sup>1</sup>, Magda Chelstowska<sup>1</sup>, Patrick Czodrowski<sup>1</sup>, Pier-Olivier Deviveiros<sup>1</sup>, Till Eifert<sup>1</sup>, Nick Ellis<sup>1</sup>, Philippe Farthouat<sup>1</sup>, Gorm Galster<sup>1,2</sup>, Stefan Haas<sup>1</sup>, Louis Helary<sup>1</sup>, Predrag Kuzmanovic<sup>1</sup>, Orestis Lagkas Nikolos<sup>1</sup>, Antoine Marzin<sup>1</sup>, Thilo Pauly<sup>1</sup>, Vladimir Ryjov<sup>1</sup>, Kristof Schmieden<sup>1</sup>, Marcos Silva Oliveira<sup>1</sup>, Joerg Stelzer<sup>1</sup>, Paschalis Vichoudis<sup>1</sup>, Thorsten Wengler<sup>1</sup>

<sup>1</sup>CERN, Switzerland <sup>2</sup>NBI Copenhagen, Denmark

> Abstract. The Muon to Central Trigger Processor Interface (MUCTPI) of the ATLAS experiment at the Large Hadron Collider (LHC) at CERN is being upgraded for the next run of the LHC in order to use optical inputs and to provide full-precision information for muon candidates to the topological trigger processor (L1TOPO) of the Level-1 trigger system. The new MUCTPI is implemented as a single ATCA blade with high-end processing FPGAs which eliminate double counting of muon candidates in overlapping regions, send muon candidates to L1TOPO, and muon multiplicities to the Central Trigger Processor (CTP), as well as readout data to the data acquisition system of the experiment. A Xilinx Zynq System-on-Chip (SoC) with a programmable logic part and a processor part is used for the communication to the processing FPGAs and the run control system. The processor part, based on ARM processor cores, is running embedded Linux prepared using the framework of the Linux Foundation's Yocto project. The ATLAS run control software was ported to the processor part and a run control application was developed which receives, at configuration, all data necessary for the overlap handling and candidate counting of the processing FPGAs. During running, the application provides ample monitoring of the physics data and of the operation of the hardware.<sup>\*</sup>

## 1 The ATLAS Experiment at the LHC

The ATLAS experiment is a general-purpose experiment at the Large Hadron Collider (LHC) at CERN [1]. It observes proton-proton collisions at an energy of 13 TeV. With about 39 interactions in every bunch crossing (BC) every 25 ns, there are more than  $10^9$  interactions per second. The trigger system selects those events which are interesting to physics and which can be recorded to permanent storage at a reasonable rate. The ATLAS

<sup>\*</sup> Copyright 2018 CERN for the benefit of the ATLAS Collaboration. CC-BY-4.0 license

trigger system consists of a Level-1 trigger based on custom electronics, which reduces the event rate to a maximum of 100 kHz, and a high-level trigger system based on commercial computers, which reduces the event rate to around 1 kHz on average.

## 2 The Level-1 Trigger System

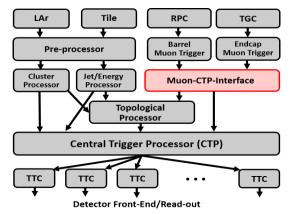

The first-level trigger of the ATLAS experiment uses reduced-granularity information from the calorimeters and dedicated muon trigger detectors, see Fig. 1. The trigger information is based on multiplicities and topologies of trigger candidate objects. The muon trigger is based on Resistive Plate Chambers (RPC) in the barrel region and Thin-Gap Chambers (TGC) in the end-cap region. The Muon to Central Trigger Processor Interface (MUCTPI) combines the muon candidate counts from the RPC and TGC, taking into account double counting of single muons that are detected by more than one chamber due to geometrical overlap of the muon candidate information to the Topological Processor and the muon counts to the Central Trigger Processor (CTP), which combines the trigger information from the calorimeter trigger, the MUCTPI, and the Topological Processor in order to make the final Level-1 decision.

Fig. 1. The Level-1 Trigger System.

# 3 The Upgrade of the MUCTPI

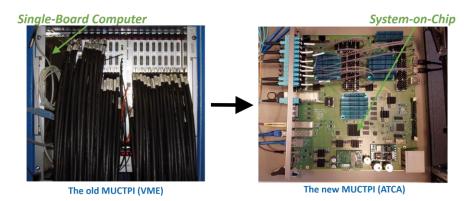

The MUCTPI upgrade to be installed for Run 3 is part of the overall upgrade of ATLAS on the road to High-Luminosity LHC [2]. The new MUCTPI will use optical links to replace bulky electrical cables. Those links will allow the muon trigger detectors to send more muon candidates with more precise information. The new MUCTPI will provide improved overlap handling and full-precision information to the Topological Processor. The new MUCTPI will be built as a single ATCA blade, see Fig. 2. It will receive 208 optical links and will use two FPGAs for the overlap handling, counting of muon candidates, and sending candidates to the Topological Processor. A third FPGA will provide the total count of muon candidates to the CTP and read out data to the data acquisition system. A System-on-Chip (SoC) will provide hardware control of the new MUCTPI and integrate it into the ATLAS run control system.

Fig. 2. The Upgrade of the MUCTPI.

# 4 The ATLAS Run Control on a System-on-Chip

The run control system [3] of the ATLAS experiment provides a framework for the control of the MUCTPI, e.g. start and stop commands, loading of configuration data, e.g. overlap lookup table (LUT) data, and collection of monitoring data, e.g. counter values. Due to the new technology (ATCA) new ways of communication between the MUCTPI and the run control system had to be investigated, which with the old MUCTPI were achieved using a single-board computer. An SoC, Xilinx Zynq 7Z030 [4], with a programmable logic part and a processor part will be used for the communication with the run control system and the processing FPGAs of the MUCTPI, see Fig. 3. The programmable logic provides the communication with the processing FPGAs using the Slave Serial protocol, and the configuration and monitoring of the MUCTPI hardware with its power, clock and optical modules using serial buses like I2C and SPI. The processor system runs embedded Linux and an ATLAS run control application, which uses low-level user application software developed for the access of all the hardware and processing FPGAs of the MCTPI.

Fig. 3. Run Control of the MUCTPI using a System-on-Chip.

#### 4.1 Build Linux with Yocto

The software for the operating system, including a kernel module for accessing memory performing DMA, and all of the user software are built and maintained using the framework of the Yocto Project from the Linux Foundation [5], which allows one to build a complete embedded Linux system. Recipes for building the user software have been developed, in order to fetch, configure, and compile the software, and create all images necessary to boot and run the processor system.

#### 4.2 Cross Compile Run Control

Yocto is used to provide a Software Development Kit (SDK), consisting of the cross compiler and all system libraries, see Fig. 4. These are used together with a toolchain file for cross compilation with CMake [6] in order to build the ATLAS TDAQ software [7] including external software packages it depends on, e.g. the ROOT software [8]. The executables and libraries are installed in a directory which is mounted on the processor system using NFS.

Fig. 4. Run Control Software Build Flow.

#### 4.3 Operate Run Control on the SoC

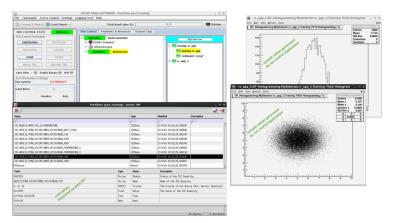

An ATLAS run control application runs on the SoC. It responds to state transition commands, receives configuration data, accesses the hardware of the MUCTPI, and produces monitoring information. The GUI to interact with this application is shown in figure 5, including examples of ROOT histograms produced for monitoring.

Fig. 5. ATLAS Run Control GUI and Monitoring Data from a standalone test of the MUCTPI.

## 5 Summary

A System-on-Chip is successfully used to provide communication between the ATLAS run control system and the new MUCTPI. The Linux kernel and a root file system are provided by Yocto, which is also used to build the user application software, which was developed in order to access the MUCTPI hardware. With the Software Development Kit provided by Yocto, and using a toolchain file, the ATLAS run control software is cross compiled for the Processor System of the SoC. A run control application runs on the MUCTPI, which controls and configures the MCTPI, and reads monitoring information, including ROOT

histograms. In the future it will be investigated to improve the building and maintenance of the software further by making use of a common Linux distribution like CERN CentOS.

### References

- 1. ATLAS Collaboration, "The ATLAS Experiment at the CERN Large Hadron Collider", Journal of Instrumentation, JINST 3 S08003 (2008).

- 2. M. Silva Oliveira et al., The ATLAS Muon to Central Trigger Processor Interface for the Upgrade of the ATLAS Muon Trigger for Run 3, Proc. Topical Workshop on Electronics for Particle Physics, 2018, in preparation.

- 3. ATLAS Collaboration, ATLAS High-Level Trigger, Data Acquisition and Controls Technical Design Report, CERN/LHCC/2003-22, 2003, see https://cdsweb.cern.ch/record/616089.

- 4. Xilinx Inc., Zynq-7000 All Programmable SoC, https://www.xilinx.com/products/ silicon-devices/soc/zynq-7000.html.

- 5. The Yocto Project, https://www.yoctoproject.org.

- 6. The CMake Software, https://cmake.org.

- 7. ATLAS TDAQ Software, https://gitlab.cern.ch/atlas-tdaq-software.

- 8. CERN ROOT Software, https://root.cern.ch.