### Faculty of Engineering

# Effects of Ultra-High Total Ionizing Dose in Nanoscale Bulk CMOS Technologies

*Author:* Mr. Henri Косн

Supervisors (CERN): Dr. Federico FACCIO Eng. Giulio BORGHELLO Supervisors (UMONS): Prof. Fortunato DUALIBE Prof. Patrice MÉGRET

A Master's Thesis Submitted in Fulfillment of the Master's Degree in Electrical Engineering

Academic Year 2017-2018

### Effects of Ultra-High Total Ionizing Dose in Nanoscale Bulk CMOS Technologies

Qualification of commercial CMOS technologies

#### Henri Koch

#### Abstract

Particle accelerators are an excellent instrument to investigate at the smallest scale in our universe. The last breakthrough was made by the Large Hadron Collider (LHC) with the observation of the Higgs boson (2012) at CERN. A future upgrade of the particle accelerator, called High-Luminosity Large Hadron Collider (HL-LHC), is planned to increase its potential for new discoveries in particle physics. The upgrade will produce a ten-fold increase in luminosity resulting in a significant increase in the number of collisions in the various detectors distributed along the particle accelerator. The higher number of collisions will increase the amount of interesting events for particle physicists. However, the important increase of particle collisions will result in an unprecedented level of radiation in the detectors. This high radiation level is a concern for the electronics in the detectors as radiation damages the transistors. The integrated energy deposited by ionizing radiation, called total ionizing dose (TID), exceeds by several orders of magnitude the typical requirements for the main concerned industry, space (hundreds of  $Mrad(SiO_2)$  vs. hundreds of  $krad(SiO_2)$ ). CERN developed the tools and knowledge to design radiation hardened application specific integrated circuits (ASICs) by characterizing the radiation response of selected commercial technologies and using hardening-by-design (HBD) techniques.

The characterization to total ionizing dose (TID) of the 65 nm CMOS technology used in the development of ASICs for the High-Luminosity Large Hadron Collider (HL-LHC) was realized. The characterization was performed within the temperature range of interest  $(-30 \,^{\circ}\text{C}, 0 \,^{\circ}\text{C} \text{ and } 25 \,^{\circ}\text{C})$  up to 500 Mrad(SiO<sub>2</sub>). The different degradation mechanisms have been outlined. The data are used to create models that will allow integrated circuit (IC) designers to directly simulate the impact of total ionizing dose (TID) during the design of the ASICs. Four publications IEEE conference have been published based on the measurement performed during this work. In addition to these measurements, the radiation response of different foundries have been study in 65 nm. We showed that the effects known as Radiation-Induced Narrow Channel Effects (RINCEs) and Radiation-Induced Short Channel Effects (RISCEs) are also observed in at least three different foundries, which increases our confidence in the universality of the mechanisms.

The study of total ionizing dose effects in two smaller technological nodes began, namely 40 nm and 28 nm CMOS technologies, from different foundries in order to investigate the next viable technology.

Firstly, I would like to thanks Giulio Borghello for the stimulating and interesting discussions but also for your availability and patience during your countless explanation. Thank you very much for sharing your valuable experience and your unwavering sympathy.

I would like to express my deepest thanks to Federico Faccio for having been my supervisor during this master's thesis. Under your supervision, I had a precious guidance and many advices which were always extremely valuable but also a great autonomy through your trust.

I would also like to express my gratitude to Stefano Michelis for all the advises and for answering all my questions.

I would like to thank very warmly all the Italian team, Giulia Bombardi, Davide Ceresa, Simone Scarfi', Alessandro Caratelli, Giacomo Ripamonti, Tommaso Vergine, Mustafa Beşirli (who is not Italian by the way) for their sympathy, their kindness and more importantly for the Foosball meeting after lunch. I am happy to have the opportunity to meet and talk with so many wonderful people.

My sincere thanks also goes to Prof. Fortunato Dualibe. You were always there when I needed help, guidance or advises. Thank you.

Furthermore, I would also like to acknowledge Prof. Patrice Mégret for its precious help in the organization of this special academic year for me. As well, I also want to thank Dean Pierre Dehombreux to have authorized this master's thesis under its particular conditions.

Many thanks go to Alexandre Quenon for your special radiation lessons but also for correcting this master's thesis.

Finally, I must express my very profound gratitude to my girlfriend, Sophie Aubry, for providing me with unfailing support and continuous encouragement. Thank you.

To the memory of Pierre Aubry

# Contents

| Li       | st of | Figur              | es                                                      | ii |

|----------|-------|--------------------|---------------------------------------------------------|----|

| Li       | st of | <sup>*</sup> Table | S                                                       | x  |

| Li       | st of | Acro               | ıyms                                                    | xi |

| In       | trod  | uction             |                                                         | 1  |

| 1        | Cor   | nplem              | entary metal-oxide semiconductor (CMOS) Technology      | 7  |

|          | 1.1   | Semic              | onductor Physics                                        | 7  |

|          | 1.2   | Curre              | nt-voltage Characteristic                               | 8  |

| <b>2</b> | Tot   | al Ioni            | izing Dose Effects in MOSFETs                           | 9  |

|          | 2.1   | Overv              | riew of Radiation Effects                               | 9  |

|          | 2.2   | Impac              | et of Ionizing Radiation in Oxides                      | 10 |

|          |       | 2.2.1              | Electron-Hole Pairs Generation                          | 12 |

|          |       | 2.2.2              | Oxide Traps                                             | 14 |

|          |       | 2.2.3              | Interface Traps                                         | 15 |

| 3        | Exp   | oerime             | ntal Setup                                              | 17 |

|          | 3.1   | Irradi             | ation and Measurements Facilities                       | 17 |

|          |       | 3.1.1              | Generation of Ionizing Radiation and Dose Rate          | 21 |

|          |       | 3.1.2              | Measurement Procedure                                   | 22 |

| 4        | 65 1  | nm Bu              | lk CMOS Technology Qualification to Total Ionizing Dose | 23 |

|          | 4.1   | Impac              | et of Ionizing Radiation in Nanoscale Technologies      | 23 |

|          | 4.2   | Exper              | imental Details                                         | 25 |

|          | 4.3   | STI-re             | elated Effects                                          | 26 |

|          |       | 4.3.1              | Radiation-Induced Narrow Channel Effects (RINCEs)       | 26 |

|          |       | 4.3.2              | Radiation-Induced Leakage Current                       | 32 |

|          | 4.4   | Radia              | tion-Induced Short Channel Effects (RISCEs)             | 33 |

| <b>5</b>     | $\mathbf{Stu}$ | dy of TID Effects in Advanced Nodes                                         | 41           |

|--------------|----------------|-----------------------------------------------------------------------------|--------------|

|              | 5.1            | 40 nm Technology                                                            | 41           |

|              | 5.2            | 28 nm Technology                                                            | 43           |

| Co           | onclu          | sion and Future Perspectives                                                | 45           |

| A            | ppe            | ndices                                                                      | Ι            |

| $\mathbf{A}$ | Eur            | opean Organization for Nuclear Research                                     | Ι            |

|              | A.1            | Conseil Européen pour la Recherche Nucléaire (CERN) Structure $\ . \ . \ .$ | II           |

|              | A.2            | CERN Finance                                                                | IV           |

| в            | Unc            | charted Radiation-Induced Effects                                           | VII          |

|              | B.1            | 1-6 Mrad Leakage Peak                                                       | VII          |

|              | B.2            | High Dose Induced Leakage                                                   | Х            |

|              | B.3            | Bias Dependence During Irradiation                                          | XI           |

|              | B.4            | Conclusion                                                                  | XV           |

| Bi           | bliog          | graphy                                                                      | Ι            |

| W            | ebog           | raphy                                                                       | $\mathbf{X}$ |

# List of Figures

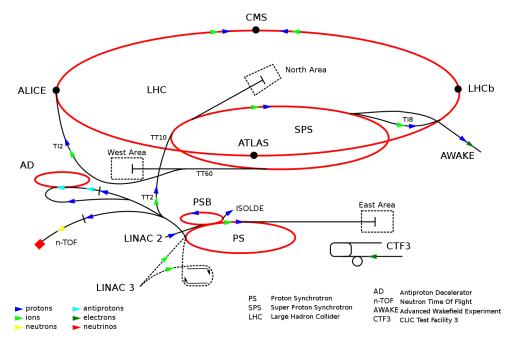

| 1   | Overview of the CERN accelerator complex. The Large Hadron Collider (LHC) corresponds to the largest red circle with the four experiments distributed around its contour (ATLAS, CMS, LHCb and ALICE) [Web7]                                                                                                                                                                                                                                                       | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

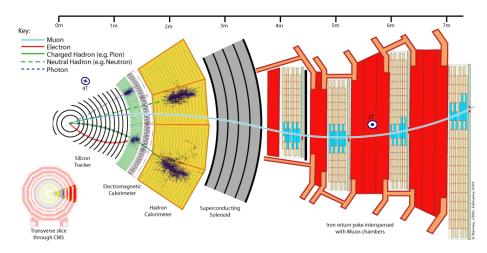

| 2   | Slice of the CMS detector [13]. Each layer of the experiment has a dedicated purpose for particle detection.                                                                                                                                                                                                                                                                                                                                                       | 3  |

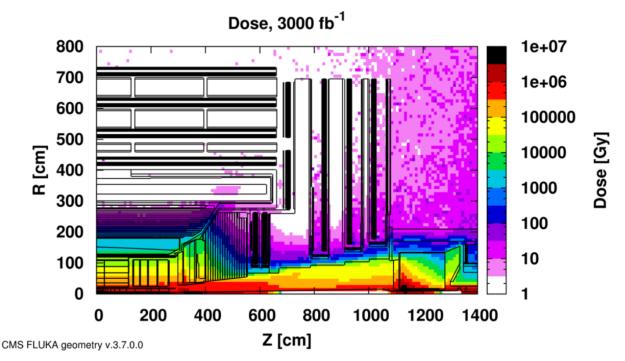

| 3   | Simulation of the total ionizing dose (TID) spatial distribution in Compact<br>Muon Solenoid (CMS) cavern expressed in Gy for a integrated luminosity<br>of $3000 \text{ fb}^{-1}$ [17, 18]. R is the transverse distance from the beam and Z is<br>the distance alongside the beam from the collision point ( $Z = 0$ and $R = 0$ ).                                                                                                                              | 4  |

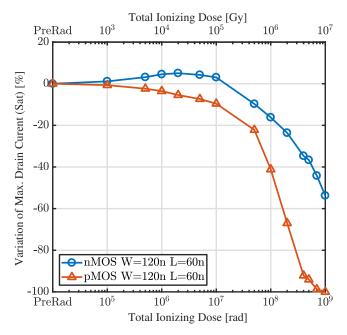

| 4   | Variation of the maximum drain current in minimum size transistors (p-<br>and n- channels) for a 65 nm technology during an irradiation performed at<br>$25 ^{\circ}$ C up to $1 \text{Grad}(\text{SiO}_2)$                                                                                                                                                                                                                                                        | 5  |

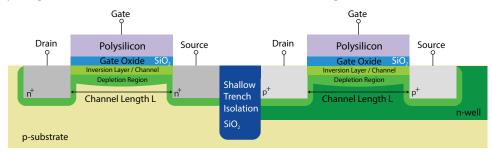

| 1.1 | Cross-section of a nMOS and pMOS in a CMOS technology where the dif-<br>ferent doping concentration are outlined (p- or n-doped)                                                                                                                                                                                                                                                                                                                                   | 8  |

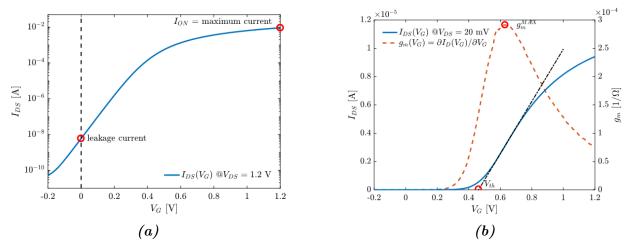

| 1.2 | Current-voltage $(I_D - V_G)$ characteristic of a nMOS transistor with the main<br>parameter extracted: leakage current, threshold voltage, maximum drain<br>current and maximum of transconductance.                                                                                                                                                                                                                                                              | 8  |

|     | 1.2a                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

|     | 1.2b                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

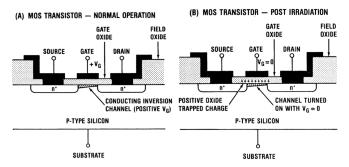

| 2.1 | Charge build-up (A) n-channel metal-oxide semiconductor field-effect tran-<br>sistor (MOSFET) in normal operation, positive voltage application ( $V_G > V_{TH}$ ) creates an inversion layer underneath the gate oxide turning on the<br>transistor. (B) n-channel MOSFET post irradiation, the accumulation of<br>charge from ionizing phenomena in the oxide maintains an inverted layer<br>while no gate voltage is applied ( $V_G = 0$ ). (After Oldham [29]) | 11 |

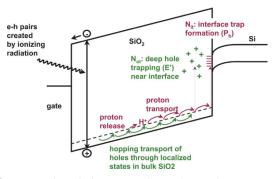

| 2.2 | Schematic of energy band diagram describing the creation of oxide traps and interface traps in the oxide and its interface with silicon induced by ionizing radiation. (After Schwank et al. [35])                                                                                                                                                                                                                                                                 | 11 |

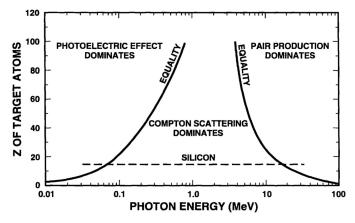

| 2.3 | Dominant effect in the photon interaction based on the energy of the incident photon and on the atomic number of the material. (After Evans [42])                                                                                                                                                                                                                                                                                                                  | 13 |

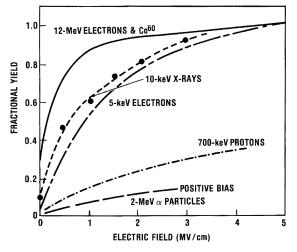

| 2.4 | Charge yield as a function of the electric field for different radiation source.<br>(After Oldham [29])                                                                                                                                                                                                                                                                                                                                                            | 13 |

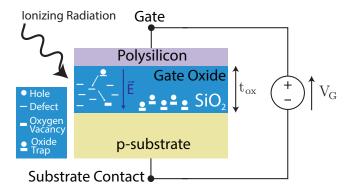

| 2.5 | Schematic view of the formation of oxide traps, the applied electric field causes the hole to drift towards the $SiO_2/Si$ interface through defects. When they reach the interface, they get trapped in deeper energetic defects and formed fixed positive charges called oxide traps |                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

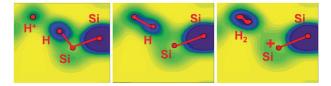

| 2.6 | React                                                                                                                                                                                                                                                                                  | ion of the hydrogen ions with SiH to form interface traps. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                             | 16 |

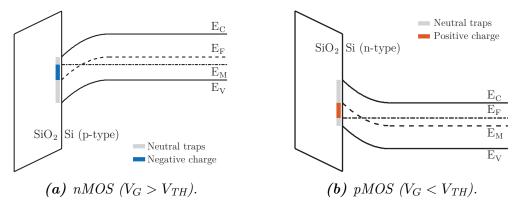

| 2.7 | .7 Filling of interface traps in both transistor type when the gate voltage is<br>higher than the threshold voltage. pMOS interface traps are filled with holes<br>(positive charges) and nMOS with electrons (negative charges). Courtesy of<br>Giulio Borghello.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16 |

|     | 2.7a                                                                                                                                                                                                                                                                                   | nMOS $(V_G > V_{\text{TH}})$ .                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

|     | 2.7b                                                                                                                                                                                                                                                                                   | pMOS $(V_G < V_{TH})$                                                                                                                                                                                                                                                                                                                                                                                                             | 16 |

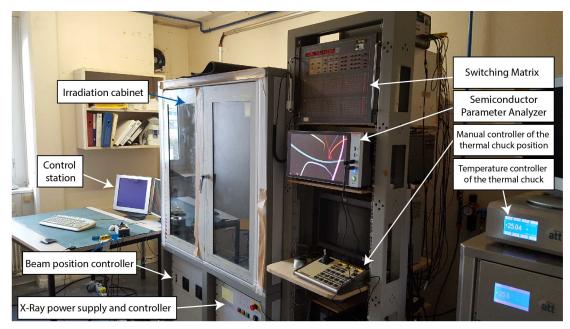

| 3.1 | puter)<br>matrix<br>is also<br>troller                                                                                                                                                                                                                                                 | N EP-ESE group X-ray irradiation facility: the control station (com-<br>) is used to automate measurements and is connected to the switching<br>x and semiconductor analyzer via a GPIB cable. The X-ray machine<br>o remotely controlled from the control station. The temperature con-<br>regulates the temperature of the thermal chuck inside the irradiation<br>et and its position can be adjusted by the manual controller | 18 |

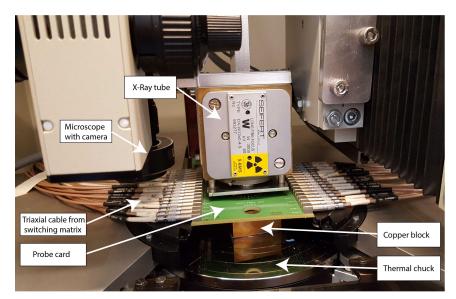

| 3.2 | card, which is connected to the switching matrix via Lemo cables. The device under test (DUT) is placed on the copper block and the thermal chuck is moved manually to reach contact with the device under test (DUT)                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18 |

| 3.3 | Probe                                                                                                                                                                                                                                                                                  | card and needles for contacting the custom test structures. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                            | 19 |

|     | 3.3a                                                                                                                                                                                                                                                                                   | Microscope view of the needles of the probe card $(2 \times 16)$ are just<br>above the metal pads of the ASIC. Each metal pad has a size of<br>70 µm by 100 µm                                                                                                                                                                                                                                                                    | 19 |

|     | 3.3b                                                                                                                                                                                                                                                                                   | Probe card with $2 \times 16$ Lemo cable connectors. The needles are situated in the center of the probe card.                                                                                                                                                                                                                                                                                                                    | 19 |

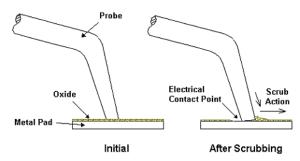

| 3.4 | Creati                                                                                                                                                                                                                                                                                 | ion of an electrical contact point with the ASIC                                                                                                                                                                                                                                                                                                                                                                                  | 19 |

|     | 3.4a                                                                                                                                                                                                                                                                                   | Microscope view of an ASIC embedding test structures of transistors<br>in 28 nm technology. The dark rectangle corresponds to the metal<br>pad (covered by oxide) allowing to probe the ASIC                                                                                                                                                                                                                                      | 19 |

|     | 3.4b                                                                                                                                                                                                                                                                                   | Once the contact is established with the probe, the friction removes<br>the oxide allowing the creation of an electrical contact point [56].<br>This can be seen in the microscope view (Figure 3.4a) on the top<br>right scratched metal pad of the IC where the metal is now visible.                                                                                                                                           | 19 |

|     |                                                                                                                                                                                                                                                                                        | inghe seracence metal part of the iC where the metal is now visible.                                                                                                                                                                                                                                                                                                                                                              | 19 |

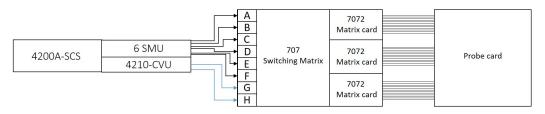

| 3.5 | semico<br>(SMUs<br>the 42<br>Matrix | iew of the experimental setup from the instruments point of view. A<br>onductor parameter analyzer 4200A-SCS has 6 source measure units<br>s) and 1 capacitance voltage unit (CVU). The measuring probe of<br>00A-SCS is connected to the 707 Switching Matrix embedding 3 7072<br>c card with a total of 36 outputs (only 32 are used) which are then<br>eted to the probe card | 20 |

|-----|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

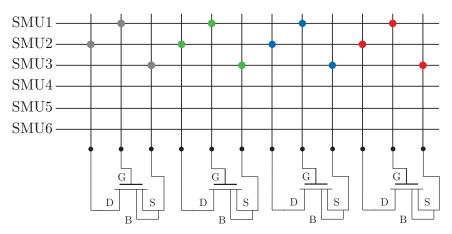

| 3.6 | trix all<br>the ma<br>sureme        | emiconductor parameter analyzer provides 6 SMUs, the switching ma-<br>lows to measure different transistors by commuting the contact inside<br>atrix. Each colored dot corresponds to one connection during mea-<br>ent while the others are not connected. Complex polarization config-<br>n may require up to 6 SMUs (not detailed)                                            | 20 |

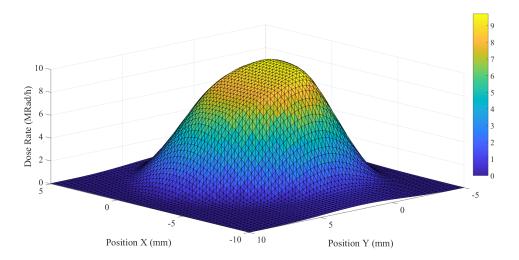

| 3.7 | ation                               | ation map of an X-ray tube at 2 cm from the target for the oper-<br>mode of 40 kV and 50 mA. The measured maximum dose rate is<br>ad $h^{-1}(SiO_2)$ .                                                                                                                                                                                                                           | 21 |

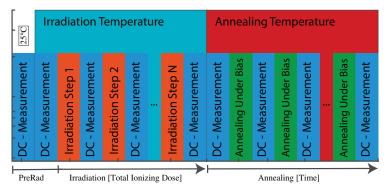

| 3.8 | sistors<br>measu<br>the irr         | al qualification procedure used during TID experiments [63]. The tran-<br>are irradiated to specific TID level and the irradiation is stopped to<br>re the transistor characteristic (e.g. $I_D - V_G$ measurements). Once<br>adiation reaches the last TID step, the measurement continues during<br>nealing phase                                                              | 22 |

| 4.1 |                                     |                                                                                                                                                                                                                                                                                                                                                                                  | 24 |

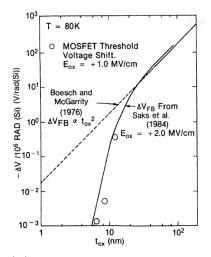

|     | 4.1a                                | Flatband voltage variation per Mrad dose for MOS capacitors as a function of the oxide thickness. From Saks, et al. [67]                                                                                                                                                                                                                                                         | 24 |

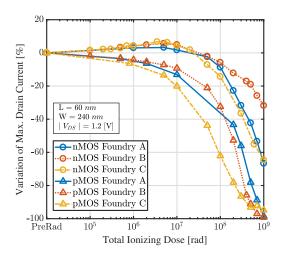

|     | 4.1b                                | Maximum drain current variation for transistors of the same size from three different foundries.                                                                                                                                                                                                                                                                                 | 24 |

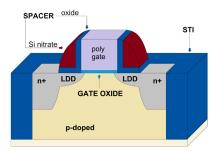

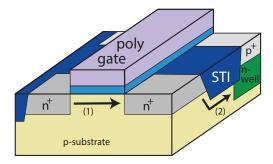

| 4.2 | lows th<br>reduce                   | ure of modern submicron n-channel MOSFET. The spacer oxides al-<br>ne implantation of the lightly doped drain (LDD) extensions needed to<br>the hot-carrier effect while the Shallow Trench Isolation (STI) is used<br>rease the inter-device leakage current. Courtesy of Giulio Borghello [70].                                                                                | 24 |

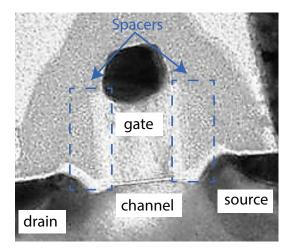

| 4.3 | Exam                                | ple of typical real transistors structure                                                                                                                                                                                                                                                                                                                                        | 25 |

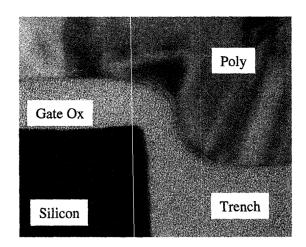

|     | 4.3a                                | TEM image of a transistor in 65 nm commercial technology. The spacers are outlined [Web12].                                                                                                                                                                                                                                                                                      | 25 |

|     | 4.3b                                | TEM image of the region close to the channel of the transistor (Sili-<br>con) with the gate oxide (Gate Ox) and the Shallow Trench Isolation<br>(STI) (Trench) [71]                                                                                                                                                                                                              | 25 |

|     |                                     |                                                                                                                                                                                                                                                                                                                                                                                  |    |

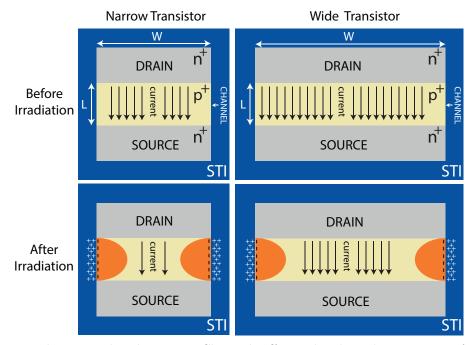

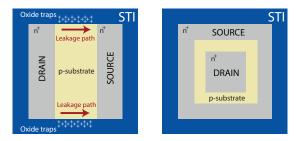

| 4.4 | Radiation-Induced Narrow Channel Effect related to the presence of the       |

|-----|------------------------------------------------------------------------------|

|     | Shallow Trench Isolation. The top left and right n-channel MOSFETs are       |

|     | non irradiated with two different widths while the two bottom left and right |

|     | n-channel are irradiated. The charges build up at and near the $Si/SiO_2$    |

|     | interface (oxide traps and interface traps).                                 |

27

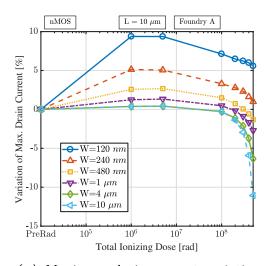

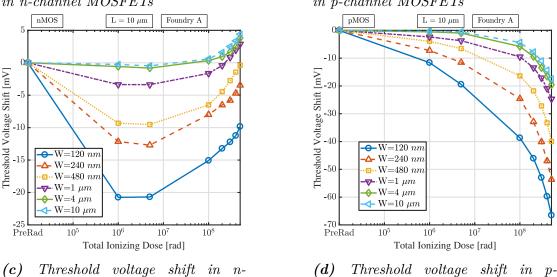

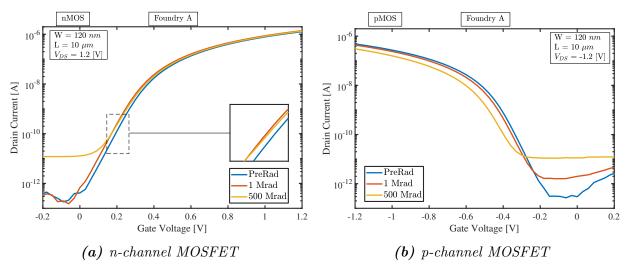

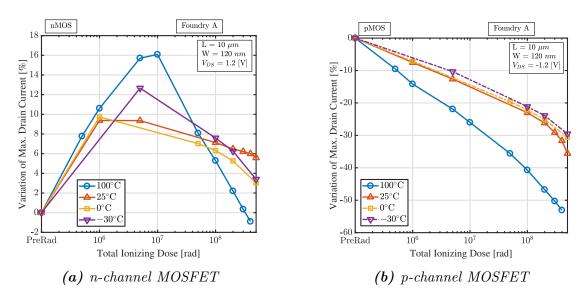

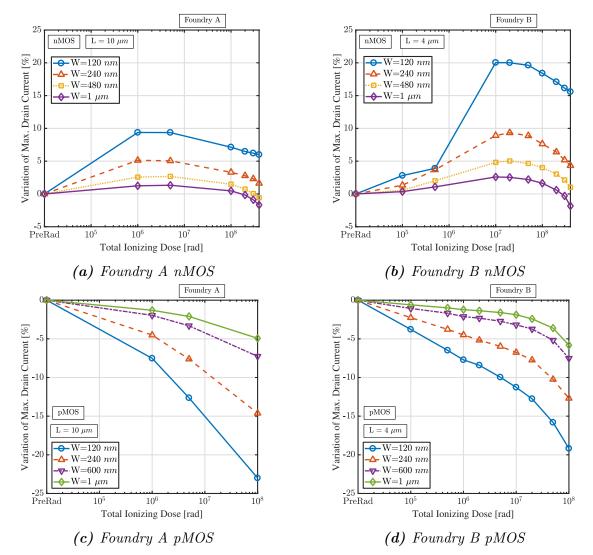

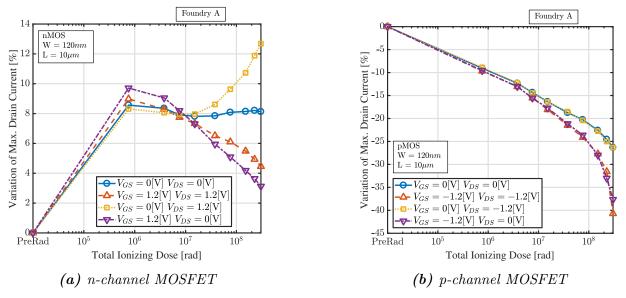

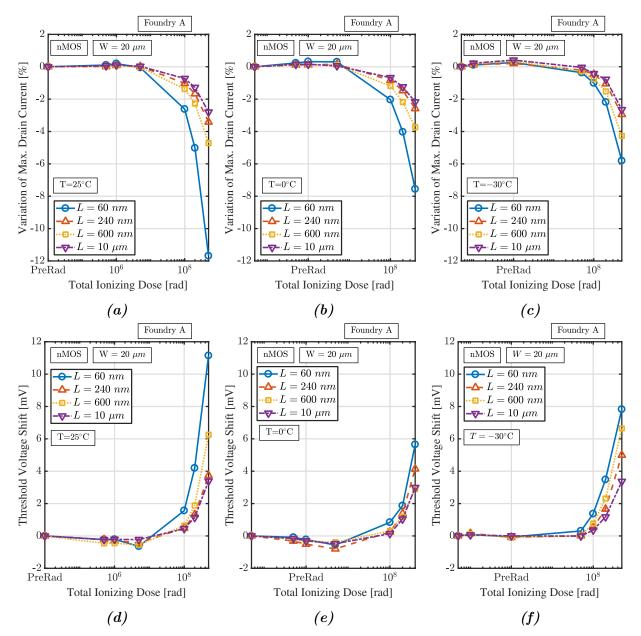

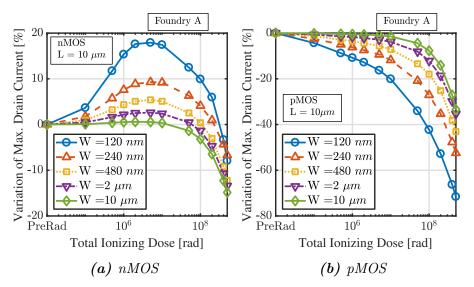

Variation in the maximum drain current in saturation  $(|V_{DS}| = 1.2V)$  and 4.5threshold voltage shift for n-channel MOSFETs (a and c) and p-channel MOSFETs (b and d) during irradiation up to 500 Mrad at 25 °C. The variation is strongly dependent on the channel width. The channel length of the transistor is fixed and very large to mitigate the spacer-related effects. The transistors were biased during irradiation in diode configuration 284.5aMaximum drain current variation in n-channel MOSFETs 28. . . . . 284.5bMaximum drain current variation in p-channel MOSFETs . . . . . 284.5cThreshold voltage shift in n-channel MOSFETs . . . . . . . . . . . . 4.5d28Threshold voltage shift in p-channel MOSFETs . . . . . . . . . . .  $I_D - V_G$  characteristics before irradiation, after 1 Mrad and 500 Mrad. . . . 294.64.6a n-channel MOSFET 294.6b p-channel MOSFET 29Influence of the temperature on the Radiation-Induced Narrow Channel Ef-4.7294.7an-channel MOSFET 29294.7bp-channel MOSFET Radiation-Induced Narrow Channel Effects (RINCEs) for two different foundries 4.8with transistors of the same channel width and a large fixed channel length 30 4.8a 30 4.8b30 4.8c 30 4.8d30 4.9Influence of the transistor bias during irradiation for RINCEs. . . . . . . 314.9a n-channel MOSFET 31 4.9bp-channel MOSFET 31

| 4.10 | Cross-section of an n-channel and p-channel MOSFETs. The build-up of<br>oxide traps in the STI can create a parasitic path between the source and<br>the drain in n-channel MOSFET (1) and between two n-doped silicon region<br>of different potential (2) |                                                                                                                                                                                                                                          |                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 4.11 | out tra                                                                                                                                                                                                                                                     | ard layout transistor (left) can present leakage current. Enclosed lay-<br>ansistor (right) is a hardening-by-design (HBD) technique that elimi-<br>ne impact of the Shallow Trench Isolation (STI) [70]                                 | 32              |

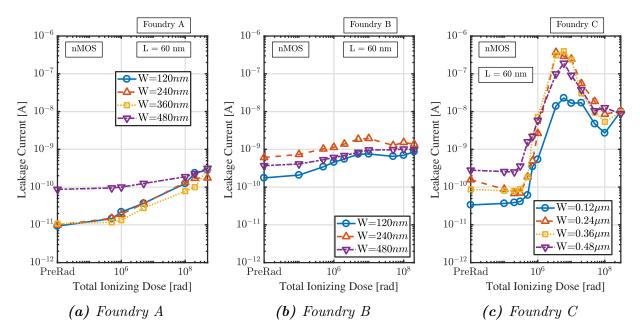

| 4.12 | and C.                                                                                                                                                                                                                                                      | ion of the leakage current in n-channel MOSFETs in foundry A, B<br>Foundry C has an important increase of the leakage current (3 orders<br>mitude) while foundry A and B present a negligible increase                                   | 33              |

|      | 4.12a                                                                                                                                                                                                                                                       | Foundry A                                                                                                                                                                                                                                | 33              |

|      | 4.12b                                                                                                                                                                                                                                                       | Foundry B                                                                                                                                                                                                                                | 33              |

|      | 4.12c                                                                                                                                                                                                                                                       | Foundry C                                                                                                                                                                                                                                | 33              |

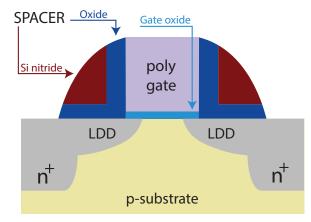

| 4.13 |                                                                                                                                                                                                                                                             | ation of the spacers situated near the gate of the transistor and com-<br>of silicon nitride $(Si_3N_4)$ and silicon dioxide $(SiO_2)$ .                                                                                                 | 34              |

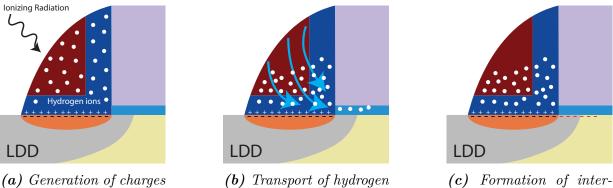

| 4.14 | Mecha                                                                                                                                                                                                                                                       | nisms involved in the Radiation-Induced Short Channel Effects (RISCEs)                                                                                                                                                                   | ). 34           |

|      | 4.14a                                                                                                                                                                                                                                                       | Generation of charges in the spacer and formation of oxide and in-<br>terface traps above the LDDs                                                                                                                                       | 34              |

|      | 4.14b                                                                                                                                                                                                                                                       | Transport of hydrogen ions from the spacer to the gate oxide. $\ldots$                                                                                                                                                                   | 34              |

|      | 4.14c                                                                                                                                                                                                                                                       | Formation of interface traps at the gate oxide interface                                                                                                                                                                                 | 34              |

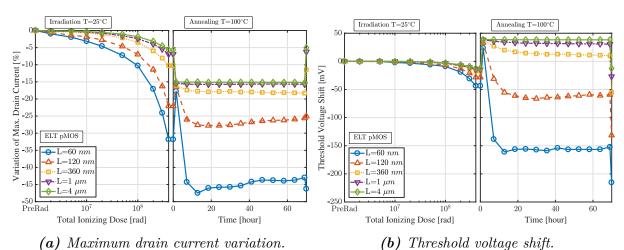

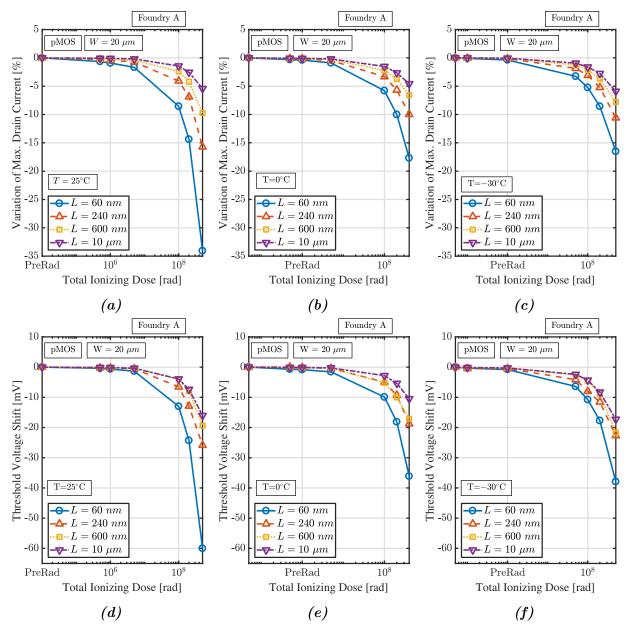

| 4.15 | and las<br>indicat                                                                                                                                                                                                                                          | As in enclosed layout p-channel MOSFETs in foundry A. The first<br>st point of the high temperature annealing are at room temperature<br>string that the increases of the threshold voltage due to temperature is<br>r when cooled down. | 25              |

|      |                                                                                                                                                                                                                                                             | Maximum drain current variation.                                                                                                                                                                                                         | $\frac{35}{35}$ |

|      | 4.15a<br>4.15b                                                                                                                                                                                                                                              | Threshold voltage shift.                                                                                                                                                                                                                 | 35              |

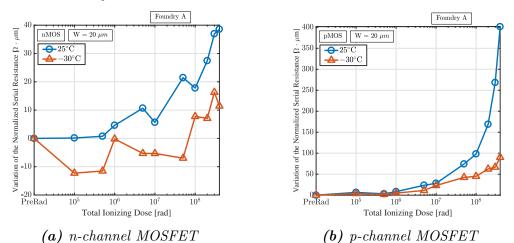

| 4.16 |                                                                                                                                                                                                                                                             | se of the series resistance of the transistors irradiated at different tem-                                                                                                                                                              | 55              |

| 4.10 |                                                                                                                                                                                                                                                             | re $[7]$                                                                                                                                                                                                                                 | 36              |

|      | 4.16a                                                                                                                                                                                                                                                       | n-channel MOSFET                                                                                                                                                                                                                         | 36              |

|      | 4.16b                                                                                                                                                                                                                                                       | p-channel MOSFET                                                                                                                                                                                                                         | 36              |

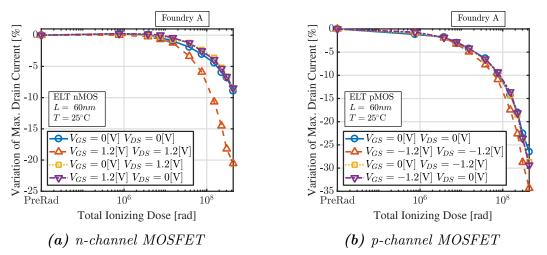

| 4.17 |                                                                                                                                                                                                                                                             | ce of the polarization during irradiation for the Radiation-Induced<br>Channel Effects (RISCEs).                                                                                                                                         | 36              |

|      | 4.17a                                                                                                                                                                                                                                                       | n-channel MOSFET                                                                                                                                                                                                                         | 36              |

|      | 4.17b                                                                                                                                                                                                                                                       | p-channel MOSFET                                                                                                                                                                                                                         | 36              |

| 4.18 | layout             | nold voltage shift and maximum drain current degradation in standard<br>nMOS transistors in due to Radiation-Induced Short Channel Effects<br>Es)                                                                                     | 37       |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | 4.18a              | <i>′</i>                                                                                                                                                                                                                              | 37       |

|      | 4.18b              |                                                                                                                                                                                                                                       | 37       |

|      | 4.18c              |                                                                                                                                                                                                                                       | 37       |

|      | 4.18d              |                                                                                                                                                                                                                                       | 37       |

|      | 4.18e              |                                                                                                                                                                                                                                       | 37       |

|      | 4.18f              |                                                                                                                                                                                                                                       | 37       |

| 4.19 | layout             | nold voltage shift and maximum drain current degradation in standard pMOS transistors in due to Radiation-Induced Short Channel Effects Es).                                                                                          | 38       |

|      | 4.19a              | ´<br>                                                                                                                                                                                                                                 | 38       |

|      | 4.19b              |                                                                                                                                                                                                                                       | 38       |

|      | 4.19c              |                                                                                                                                                                                                                                       | 38       |

|      | 4.19d              |                                                                                                                                                                                                                                       | 38       |

|      | 4.19e              |                                                                                                                                                                                                                                       | 38       |

|      | 4.19f              |                                                                                                                                                                                                                                       | 38       |

| 4.20 | and las<br>indicat | Es in enclosed layout p-channel MOSFETs in foundry B. The first<br>st point of the high temperature annealing are at room temperature<br>cing that the increases of the threshold voltage due to temperature is<br>r when cooled down | 39       |

|      | 4.20a              | Maximum drain current variation                                                                                                                                                                                                       | 39       |

|      | 4.20b              | Threshold voltage shift.                                                                                                                                                                                                              | 39       |

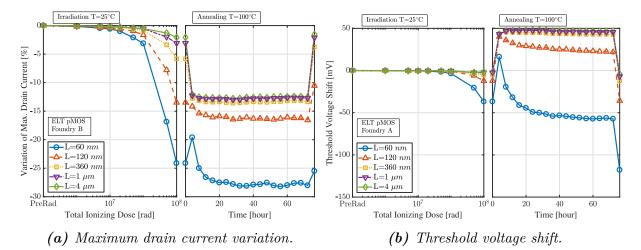

| 5.1  | nel len            | num drain current degradation for wide transistors with different chan-<br>gth in foundry A for 40 nm technology irradiated up to 500 Mrad at<br>comperature in diode configuration.                                                  | 41       |

|      | 5.1a               | nMOS                                                                                                                                                                                                                                  | 41       |

|      | 5.1b               | pMOS                                                                                                                                                                                                                                  | 41       |

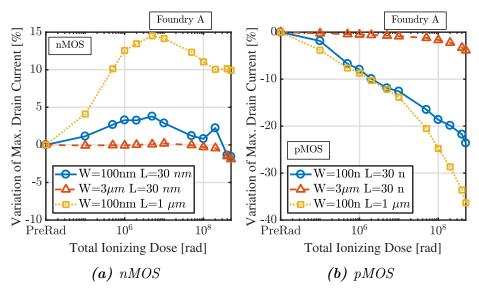

| 5.2  | nel wie            | num drain current degradation for long transistors with different chan-<br>dth in foundry A for 40 nm technology irradiated up to 500 Mrad at                                                                                         | 49       |

|      | 5.2a               | 1 0                                                                                                                                                                                                                                   | 42<br>42 |

|      | J.∠a               |                                                                                                                                                                                                                                       | 42       |

|     | 5.2b pMOS $\ldots$                                                                                                                                                                                                                                     | 42        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

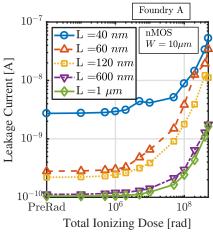

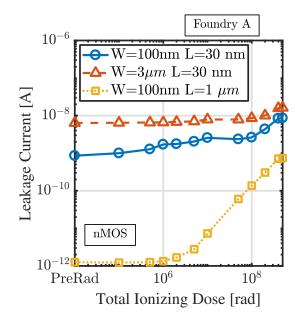

| 5.3 | Leakage current increases in foundry A for 40 nm technology                                                                                                                                                                                                                                                                             | 42        |

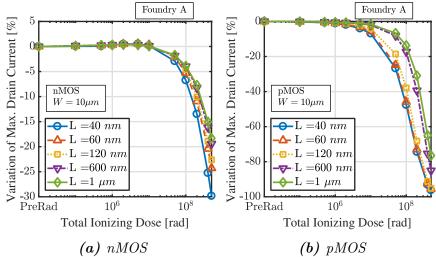

| 5.4 | Maximum drain current degradation for different transistors in foundry A for 28 nm technology irradiated up to 500 Mrad at room temperature in diode configuration.                                                                                                                                                                     | 43        |

|     | 5.4a nMOS                                                                                                                                                                                                                                                                                                                               | 43        |

|     | 5.4b pMOS                                                                                                                                                                                                                                                                                                                               | 43        |

| 5.5 | Leakage current increases in foundry A for 28 nm technology                                                                                                                                                                                                                                                                             | 44        |

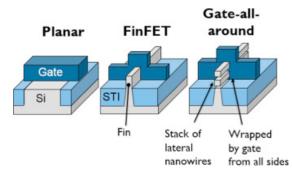

| 5.6 | Schematic illustration of different CMOS technologies. Planar corresponds to Bulk CMOS technology and two advanced node are shown, namely fin field-effect transistor (FinFet) and gate all-around field-effect transistor (GaaFe (From [103]).                                                                                         | t).<br>46 |

| A.1 | Solvay Conference in Brussels, 1927. In the picture can be found among<br>others: P. Ehrenfest, E. Schrödinger, W. Pauli, W. Heisenberg, L. Brillouin,<br>P. Debye, P.A.M. Dirac, L. de Broglie, N. Bohr, M. Planck, M. Curie, H.A.<br>Lorentz, A. Einstein, P. Langevin. Photograph taken by Benjamin Couprie<br>[Web15].              | Ι         |

| A.2 | Map of member states of the European Organization for Nuclear Research (coloured in blue) [Web16]                                                                                                                                                                                                                                       | III       |

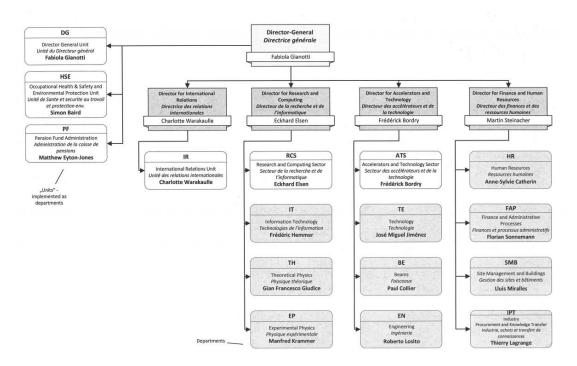

| A.3 | Management structure of CERN with the different departments [Web17]. $% \left[ \left( {{{\rm{Web}}} \right)^2 } \right]$ .                                                                                                                                                                                                              | IV        |

| A.4 | Contributions of the member states to the CERN budget for the financial year 2018 in million Swiss frances (CHF) [110].                                                                                                                                                                                                                 | V         |

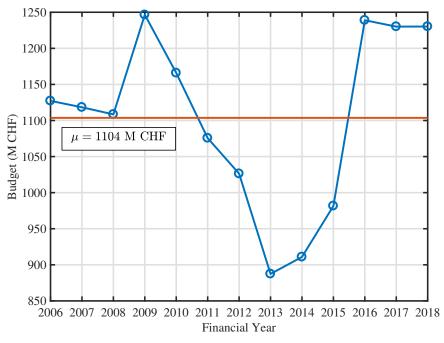

| A.5 | Evolution of the CERN budget from 2006 to 2018 (data extracted from [Web18]).                                                                                                                                                                                                                                                           | VI        |

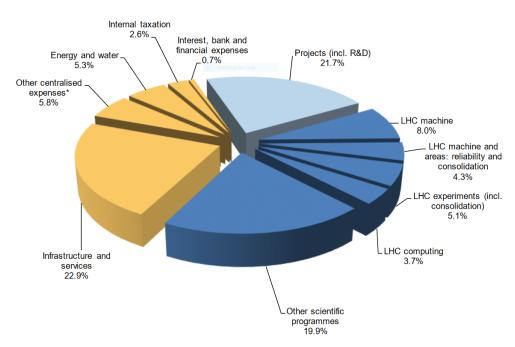

| A.6 | Breakdown of the budget for the financial year 2018 [110]. $\ldots$ $\ldots$                                                                                                                                                                                                                                                            | VI        |

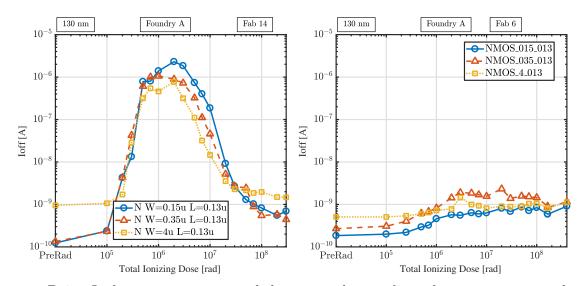

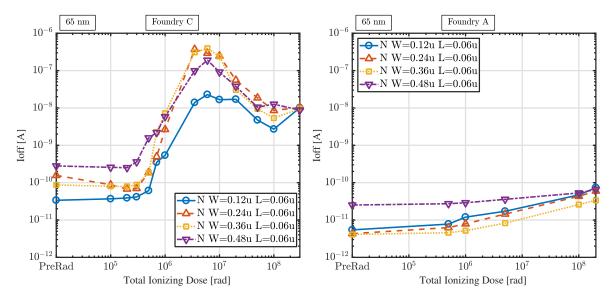

| B.1 | Leakage current measured during irradiation from the same commercial node (130 nm) but from two different fabrication plants (Fab). Left: the leakage current in the range of 1-6 Mrad increases by four order of magnitude. Right: the leakage current increases steadily during the irradiation but less than one order of magnitude. | VII       |

| B.2 | Leakage current measured during irradiation from the same commercial node $(65 \text{ nm})$ but from two different foundries                                                                                                                                                                                                            | VIII      |

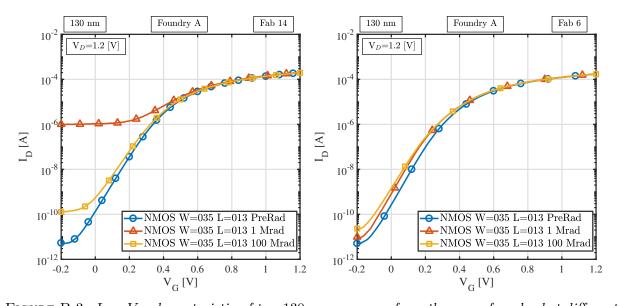

| B.3  | $I_D - V_G$ characteristic of two 130 nm processes from the same foundry but different fab. Left: with leakage peak. Right: without leakage peak. The threshold voltage shift is present in both cases while the increase of the leakage is only observe in one.                                                                                           | VIII  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

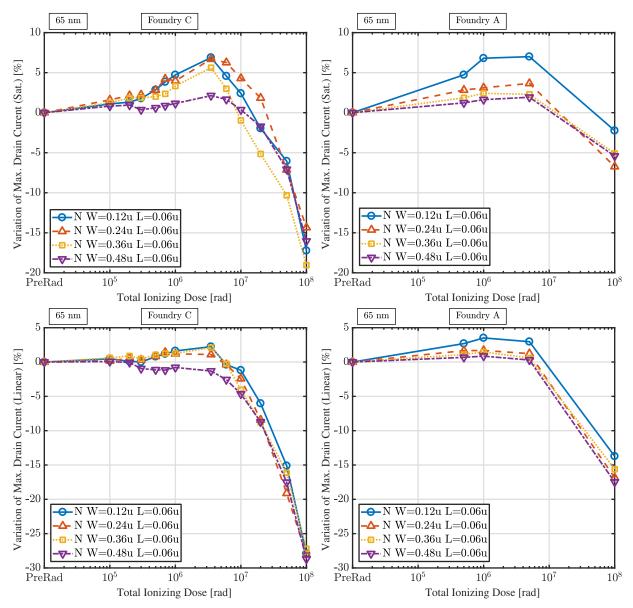

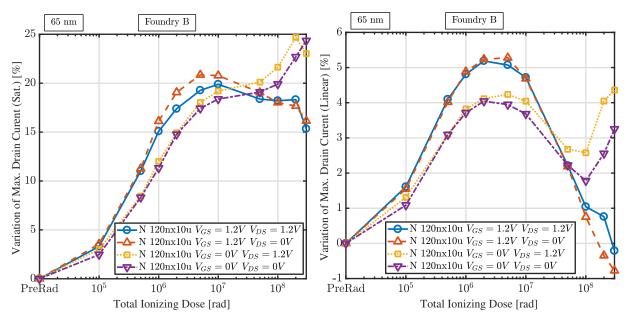

| B.4  | Evolution of the maximum drain current in both linear and saturation for<br>two different foundry in 65 nm technology. Top left: foundry C, saturation<br>region. Top right: foundry A, saturation region. Bottom left: foundry C,<br>linear region. Bottom right: foundry A, linear region                                                                | IX    |

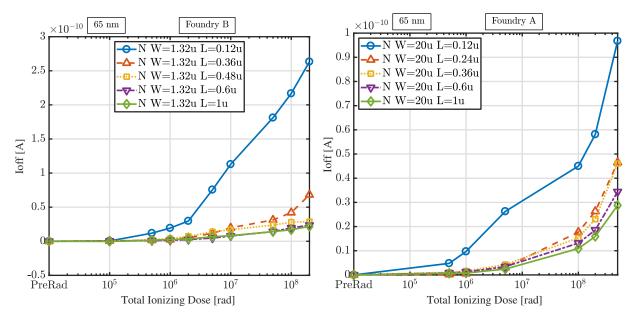

| B.5  | Increase of the leakage current at very high dose for two different 65 nm processes. Both show a channel length dependence.                                                                                                                                                                                                                                | Х     |

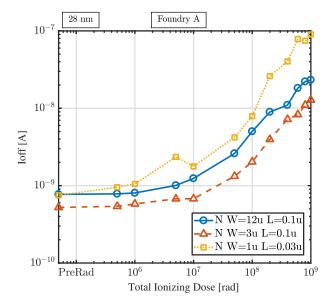

| B.6  | Increase of the leakage current at very high dose for a $28\mathrm{nm}$ process [92]                                                                                                                                                                                                                                                                       | XI    |

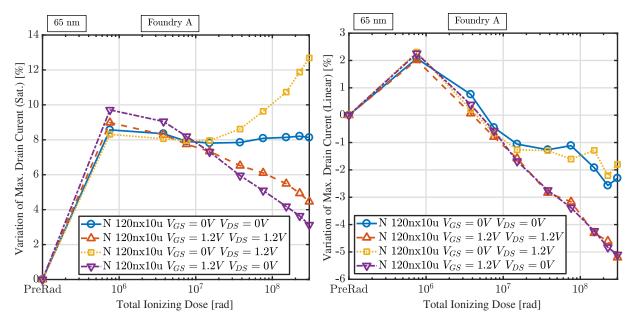

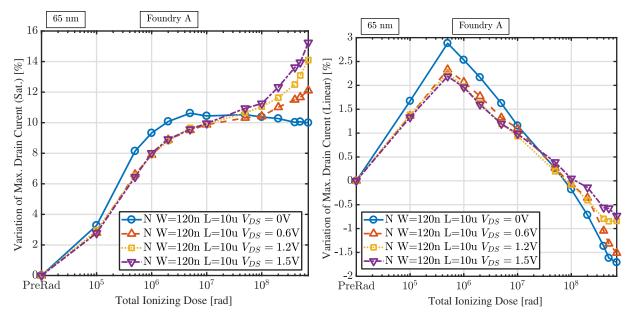

| B.7  | Irradiation of long and narrow nMOS transistors up to 300 Mrad with dif-<br>ferent biases in foundry A. Left: evolution of the maximum drain current in<br>saturation region. Right: evolution of the maximum drain current in linear<br>region                                                                                                            | XII   |

| B.8  | Irradiation of long and narrow nMOS transistors up to 200 Mrad with dif-<br>ferent biases in foundry B. Left: evolution of the maximum drain current in<br>saturation region. Right: evolution of the maximum drain current in linear<br>region                                                                                                            | XII   |

| B.9  | Influence of the drain bias during irradiation. Left: maximum drain current in saturation region. Right: maximum drain current in linear region                                                                                                                                                                                                            | XIII  |

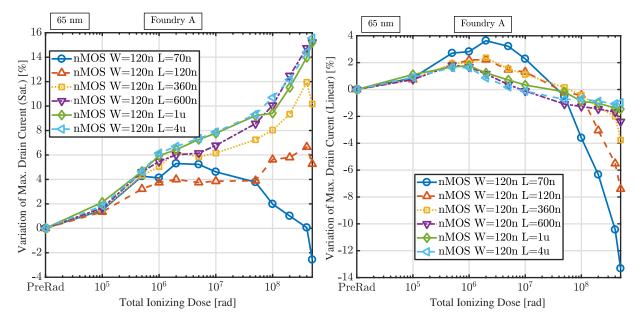

| B.10 | Influence of the channel length with narrow channel devices. The bias during irradiation was $V_{DS} = 1.2V$ and $V_{GS} = 1.2V$ . Left: maximum drain current in saturation region. Right: maximum drain current in linear region                                                                                                                         | XIII  |

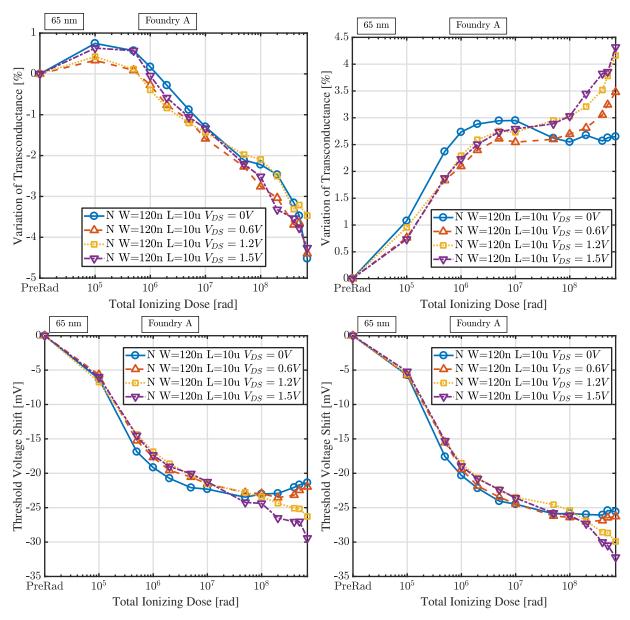

| B.11 | Variation of the transconductance and threshold voltage for different $V_{DS}$ bias alone ( $V_{GS} = 0V$ ) during irradiation. Top left: transconductance in linear region. Top right: transconductance in saturation region. Bottom left: threshold voltage shift computed in linear region. Bottom right: threshold voltage shift in saturation region. | XIV   |

|      |                                                                                                                                                                                                                                                                                                                                                            | 771 V |

# List of Tables

| 2.1 | Summary of the radiation effects in MOSFETs                                      | 9  |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | Classification of the different types of radiation according to their ionization |    |

|     | ability                                                                          | 12 |

### List of Acronyms

ALICE A Large Ion Collider Experiment. **ASIC** application specific integrated circuit. ATLAS A Toroidal LHC ApparatuS. **BX** bunch crossing. **CERN** Conseil Européen pour la Recherche Nucléaire. CLIC Compact Linear Collider. CMOS complementary metal-oxide semiconductor. CMS Compact Muon Solenoid. **CTRW** continuous time random walk. CVU capacitance voltage unit. **DD** displacement damage. **DG** Director-General. **DUT** device under test. ESD electrostatic discharge. **ESE** Electronics Systems for Experiments. FCC Future Cicular Collider. **FinFet** fin field-effect transistor. GaaFet gate all-around field-effect transistor. HBD hardening-by-design. **HEP** High Energy Physics. HL-LHC High-Luminosity Large Hadron Collider. **IC** integrated circuit.

**ITRS** International Technology Roadmap for Semiconductors.

LDD lightly doped drain.

**LEP** Large Electron-Positron Collider.

LHC Large Hadron Collider.

LHCb Large Hadron Collider beauty.

LOCOS LOCal Oxidation of Silicon.

${\bf MOS}\,$  metal-oxide semiconductor.

**MOSFET** metal-oxide semiconductor field-effect transistor.

**nMOS** n-type metal-oxide semiconductor.

**PIN** positive intrinsic negative.

**pMOS** p-type metal-oxide semiconductor.

**PS** Proton Synchrotron.

**RINCE** Radiation-Induced Narrow Channel Effect.

**RISCE** Radiation-Induced Short Channel Effect.

**SEB** single event burnout.

**SEE** single event effect.

**SEGR** single event gate rupture.

**SEL** single event latchup.

**SEU** single event upset.

SMU source measure unit.

**SPS** Super Proton Synchrotron.

${\bf STI}\,$  Shallow Trench Isolation.

TEM transmission electron microscopy.

**TID** total ionizing dose.

### Introduction

In 1962, the United States of America conducted several high-altitude nuclear tests from Johnston Atoll near Hawaï known as the operation Starfish Prime [1]. The main and unwanted aftereffect of this operation was the creation of radiation belts of MeV electrons around the Earth [2] that caused the first loss of a spacecraft, the satellite Telstar 1 [Web1], due to ionizing radiation-induced effects in on board semiconductor devices [3].

Radiation jeopardizes the reliability of electronic components that are now used in many applications. The first-line industry is the space industry where satellites have to survive in a harsh environment, exposed to solar winds, cosmic rays or to the Van Allen radiation belt. When particles enter the atmosphere they generate new particles in cascades. The radiation level increases with altitude [Web2] and so the avionics industry also has to face electronics reliability. At terrestrial altitude, the radiation level was often neglected but it is no more the case in advanced technologies, e.g. used in the memories [4]. The nuclear industry has also to address this problem [5] but it is not deeply affected as limited number of electronic components are exposed to radioactive area. However, it will not be the case for future thermonuclear fusion reactors where the plasma needs to be monitored and will produce a very high level of radiation [6].

High Energy Physics (HEP) accelerators and in particular the Large Hadron Collider (LHC) at CERN are now using more and more electronics in their experiments that are subjected to unprecedented radiation level [7]. The harsh radiation environment is created by the high particle collisions rate inside the detectors in which the electronics must continue to operate correctly. The integrated energy deposited by ionizing particles, called total ionizing dose (TID), exceeds by several orders of magnitude the typical requirements for space applications (hundreds of  $Mrad(SiO_2)^1$  vs. hundreds of  $krad(SiO_2)$ ) [8].

The development of a qualified radiation-hard state-of-the-art semiconductor technology requires an investment in multi-billion-dollar range [Web3]. Therefore, CERN chose another strategy to develop application specific integrated circuits (ASICs) based on the use of commercial CMOS technologies. CERN developed the tools and knowledge to design radiation hardened ASICs by characterizing the radiation response of selected commercial technologies and using hardening-by-design (HBD) techniques.

Since its creation, CERN has been challenging the field of research in particle physics. The latest breakthrough was done in 2012 with the observation of the Higgs boson with the ATLAS and CMS detectors [9, 10]. Now CERN's scientists want to go beyond the Standard Model of particle physics (New Physics) [Web4], looking after dark matter [Web5] and extra dimensions [Web6]. These investigations at the smallest scale of our universe are possible thanks to particle accelerators.

<sup>&</sup>lt;sup>1</sup>The rad is a unit to express the radiation absorbed dose still used by the semiconductor radiation community. The SI unit is the gray (Gy). The conversion is given by  $1 \text{ rad} = 0.01 \text{ Gy} = 0.01 \text{ J kg}^{-1}$ . We will see later also that we need to express TID in a given material, here silicon dioxide (SiO<sub>2</sub>).

#### The Large Hadron Collider and its Experiments

The Large Hadron Collider (LHC) is the largest and most powerful particle accelerator in the world with a ring of 27 km buried 100 m underground at the Franco-Swiss border [11]. The Large Hadron Collider (LHC) was launched in 2008 replacing the Large Electron-Positron Collider (LEP) accelerator and its development cost makes it the most expensive scientific experience in the world, around 9 billion euros [11].

Figure 1 illustrates the whole accelerator complex of CERN. There are several machines that accelerate particles with an increasing energy. The LHC is represented by the biggest red circle with the four main experiments (ATLAS, CMS, ALICE and LHCb) spread along its circumference. Two kinds of particles can be injected in the particle accelerators, protons and ions. Before being injected in the LHC, the particles are progressively accelerated through the two old, growing in size, accelerators: the Proton Synchrotron followed by the Super Proton Synchrotron. The particles are then injected in the Large Hadron Collider. Two beams of particles flow in opposite direction and are accelerated to reach 7 TeV and collided at different experiments with a total energy of 14 TeV. A strong magnetic field is applied (8.6 T) to generate a force in order to bend the trajectory of the particles in a circular motion. The particles are accelerated thanks to RF cavities placed along the LHC. When a bunch of particles crosses the cavities, the radio waves exchange with the bunch of particles some energy and push them forward [12].

FIGURE 1: Overview of the CERN accelerator complex. The Large Hadron Collider (LHC) corresponds to the largest red circle with the four experiments distributed around its contour (ATLAS, CMS, LHCb and ALICE) [Web7].

While the experiments ALICE and LHCb are dedicated to the study of specific tasks, ATLAS and CMS are two experiments of the same type. They are both general purpose detectors built to search for supersymmetry and exotic particles and to study the Higgs boson.

A slice of the CMS detector is presented in Figure 2 [13]. The experiment is composed of several different layers dedicated to particle detection [14]. The innermost part is made up of a silicon tracker allowing to record particles trajectory. The calorimeters give the energy of the particles. Finally, the outermost part consists of the iron return yoke interspersed with the muon chambers. It consists of a thick layer of iron, filtering the particles by interacting except the muons which can penetrate several meters, and the chambers that are able to detect muons [14].

FIGURE 2: Slice of the CMS detector [13]. Each layer of the experiment has a dedicated purpose for particle detection.

### High-Luminosity Large Hadron Collider (HL-LHC)

Two beams are injected inside the LHC, circulating in opposite direction, each beam contains approximately 2800 bunches of protons. There are  $10^{11}$  protons per bunch. When the protons have reached the nominal energy, the bunch of protons are collided. This event is called bunch crossing (BX) and it happens at a 40 MHz rate in the detectors [15].

The luminosity  $\mathcal{L}$  is a major parameter that characterizes particle accelerators. It is a measurement proportional to the number of collisions produced in a detector per cm<sup>2</sup> per second. Equation 1 yields some parameters showing its dependency on the number of protons in each bunch N, the collision rate f and the effective collision surface  $S_{\text{eff}}$ .

$$\mathcal{L} \approx \frac{f \cdot N^2}{S_{\text{eff}}} \tag{1}$$

Between each run of the LHC, the luminosity increases steadily and with it the quantity of interesting events to process. The instantaneous luminosity of the LHC has reached a new record at the value of  $2.06 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$  in November 2017 [Web8]. The timeintegration of the luminosity is hence proportional to the number of collisions and is usually expressed in inverse femtobarn (fb<sup>-1</sup>). The increase in the luminosity will increase the production of interesting events such as for example the Higgs boson which is now produced at about 20 000 per day [Web9]. The expected integrated-luminosity for the LHC is about  $300 \text{ fb}^{-1}$  while the value for HL-LHC will be of  $3000 \text{ fb}^{-1}$  [16].

This ten-fold increase in the number of collisions will create an unprecedented level of radiation, while the electronics inside the detectors must continue to operate properly. Therefore, radiation hard ASICs are designed to cope with this harsh environment. Two types of effects are present: cumulative effects (total ionizing dose and displacement damage) or transient effects (single event effects). The subject of this master's thesis focus on total ionizing dose whose accumulated level is several order of magnitude higher than in space applications. Figure 3 shows the simulation of the spatial TID distribution in the CMS detector for the HL-LHC ( $3000 \, \text{fb}^{-1}$ ). The expected TID will be of 10 MGy (1 Grad).

FIGURE 3: Simulation of the total ionizing dose (TID) spatial distribution in CMS cavern expressed in Gy for a integrated luminosity of  $3000 \text{ fb}^{-1}$  [17, 18]. R is the transverse distance from the beam and Z is the distance alongside the beam from the collision point (Z = 0 and R = 0).

#### Master's Thesis Outline

The research work of this thesis focuses on the characterization of different commercial CMOS nodes with total ionizing dose (TID). Single transistors of different size, shape and type from the interested technologies are directly embedded on an ASIC in test structures and irradiated up to a relevant TID, typically between 200 Mrad(SiO<sub>2</sub>) and 1 Grad(SiO<sub>2</sub>), while measuring the evolution of transistors electrical properties. Measurements are typically current-voltage characteristics from which typical features are extracted, e.g. threshold voltage, subthreshold swing or maximum drain current. The results are compared to the current state-of-the-art knowledge to provide an interpretation of the physical mechanisms responsible for the observed degradation. Therefore, this research envisages a fundamental study of the physical mechanisms that govern the behavior of transistors exposed to ionizing radiation.

Figure 4 shows the impact of TID up to  $1 \operatorname{Grad}(\operatorname{SiO}_2)$  in one of the transistor features, here it is the maximum current flowing through the transistor when it is turn on. The degradation is important and at  $1 \operatorname{Grad}(\operatorname{SiO}_2)$ : the p-channel transistor completely ceases to work while the n-channel transistor has reduced by more than half its current. The maximum drain current is only one parameter extracted from the whole characteristic. The complete behavior of the transistor is tremendously affected by the accumulation of ionizing radiation. Hence, the impact of TID in transistors is a major concern and the study of these effects helps the IC designers to anticipate and compensate the degradation.

FIGURE 4: Variation of the maximum drain current in minimum size transistors (p- and nchannels) for a 65 nm technology during an irradiation performed at 25 °C up to 1 Grad  $(SiO_2)$ .

The main contribution of this master's thesis is the characterization of the 65 nm technology currently used at CERN for the development of ASICs for the HL-LHC (a 130 nm technology is also used and already qualified [19]). The characterization involved the measurement of different transistors issued from the considered technology and the understanding of the underlying observed behavior. The measurements have been performed at CERN and lasted 6 months (November-April). The data obtained are used to model the degradation of the transistors electrical properties for three different TID values (100 Mrad, 200 Mrad and 500 Mrad). The creation of the models has been outsourced to the Technical University of Crete (TUC). So far, four publications in IEEE conference have been published based on the 65 nm measurements [20, 21, 22, 23]. The characterization of smaller technological CMOS processes has begun, namely 28 nm and 40 nm technologies, to investigate a potential replacement for the currently used technologies.

In chapter 1 (*CMOS Technology*), we will briefly review the basics of semiconductor physics applied to metal-oxide semiconductor field-effect transistors (MOSFETs), required to understand the content of this master's thesis.

The chapter 2, *Total Ionizing Dose Effects in MOS*, gives a detailed view of the physical mechanisms responsible for the degradation of the electrical properties of transistors caused by ionizing radiation in oxides. Before going into the detail of ionizing radiation effects, we will discuss the different radiation-induced effects, non-related in particular to ionizing radiation, that affect electronic component in general.

The chapter 3 called *Experimental Setup* provides the information about the experimental details, the irradiation facilities, the way the experiment parameters are controlled such as temperature and the equipment used to perform measurements.

The chapter 4 (65 nm *Bulk CMOS Technology Qualification to Total Ionizing Dose*) presents the data measured for the creation of the model in the 65 nm technology. We outline the different effects that take place in modern technologies in the range of TID expected for the particle accelerator upgrade.

In chapter 5 (*Study of TID Effects in Advanced Nodes*), we show the first measurement performed in smaller technologies (28 nm and 40 nm). We will present the performance against ionizing radiation in terms of degradation.

Finally, a conclusion reviews the work accomplished during the master's thesis and establishes a short and long term perspective for the future of CMOS technologies exposed to ultra-high total ionizing dose.

In addition to the main subject of this thesis, the interested reader can find in appendices a detailed chapter of interesting historical details about CERN (Appendix A). In appendix B, some radiation effects which are not yet fully understood are described.

### Chapter 1

### **CMOS** Technology

The complementary metal-oxide semiconductor (CMOS) technology is composed by two different transistors differentiated by the type of carriers flowing in their channel. The operating principle of transistors is based on semiconductor physics where the main material is silicon (Si). We will briefly review some basics of semiconductor physics as well as some important parameters of MOSFETs.

#### **1.1 Semiconductor Physics**