### UNIVERSITÀ DEGLI STUDI DI PERUGIA

Dottorato di Ricerca in Ingegneria Industriale e dell'Informazione - XXX Ciclo

**DIPARTIMENTO DI INGEGNERIA** VIA G. DURANTI 93 - 06125 - PERUGIA (I) TEL. 075-5853653 • FAX 075-5853654

### DESIGN AND OPTIMISATION OF LOW POWER HYBRID PIXEL ARRAY LOGIC FOR THE EXTREME HIT AND TRIGGER RATES OF THE LARGE HADRON COLLIDER UPGRADE

Ph.D. candidate: Sara Marconi

Supervisor: Ph.D. Pisana Placidi Ph.D. Coordinator: Prof. Ermanno Cardelli

Co-supervisor: Eng. Jørgen Christiansen

> A dissertation submitted for the degree of Doctor of Philosophy in Industrial and Information Engineering

> > A.A. 2017/2018

"Engineers like to solve problems. If there are no problems handily available, they will create their own problems." Scott Adams

## Preface

Digital design of integrated circuits in nanometer technology requires to address several design challenges. Among those, system complexity has to be handled with modern techniques and tools, power density needs to be considered as a major player in design choices (trade-off versus performance), clock distribution and timing closure require special attention due to large chip size (impact of interconnections) and variability issues demanding additional timing safety margins. These issues are common to multiple research and industry applications, among which the design of the readout electronics of next generation hybrid pixel detectors for the High-Luminosity Large Hadron Collider (HL-LHC) at CERN. In addition, in this application circuits operate in harsh radiation environments, experiencing performance degradation and various classes of hard/soft errors. Pixel detectors are devices capable of detecting different forms of radiation with high resolution (up to a few micrometers), thanks to the small size of the sensing element. In High Energy Physics (HEP) applications particles are detected based on their ionizing interaction with the sensor and collected information has to be readout through dedicated high density electronics. For applications demanding fast detection, tolerance of high radiation levels (above tens of Mrads), reliability with high input rates (in the order of few  $GHz/cm^2$ ), the sensor and the electronics are normally fabricated in separate substrates. Such a systems is referred to as Hybrid Pixel Detector (HPD).

This work is part of the effort to design the digital readout electronics of next generation hybrid pixel detectors. The most relevant examples are the pixel detectors for the HEP experiments A Toroidal LHC ApparatuS (AT- LAS) [1], Compact Muon Solenoid (CMS) [2] and A Large Ion Collider Experiment (ALICE) [3] at the LHC. New generation pixel detector systems and ASICs for High Energy Physics (HEP) applications will be a big step forward and will have to meet specifications in terms of smaller pixels to improve tracking resolution, much higher hit rates  $(3 \text{ GHz/cm}^2)$ , much higher output bandwidth and large integrated circuits with low power consumption and low power fluctuations. Their electronics will also have to work reliably for years under the hostile radiation conditions, requiring unprecedented radiation tolerance (up to 1 Grad). The PhD activity is part of the design effort to develop the digital readout electronics of such complex systems using commercial high-scaled technologies and requires to face challenges which are of common interest in the technological and scientific context, i.e. system complexity, low power consumption, reliability in hostile environments (shared also with space applications).

The design of next generation pixel detector systems has driven the creation of multiple collaborations and projects, to which the PhD activity has been an active contribution:

- RD53 [4], an international collaboration of universities and research institutes, targeted to design the next generation of hybrid pixel readout chips to enable the phase 2 pixel upgrades of the ATLAS (A Thoroidal LHC ApparatuS) and CMS (Compact Muon Solenoid) experiments. The readout chip, named RD53A, has been prototyped in August 2017;

- CHIPIX65 [5], an italian project born with the primary goal of developing an innovative CHIP for a PIXel detector, using a CMOS 65nm technology, for experiments with extreme particle rates and radiation (effort shared with the RD53 Collaboration). Such a chip has been prototyped in June 2016;

- AIDA-2020 (Advanced European Infrastructures for Detectors at Accelerators) [6], an European project aiming at pushing detector technologies beyond the state-of-the-art and offering highly equipped infrastructures for testing.

In the remainder the contents and the organization of the report will be described. In Chapter 1, an overview on the state of the art of hybrid pixel detectors is provided and the motivations and requirements of this work are introduced; Chapter 2 describes the contribution to the development and optimization of a simulation framework for complex integrated circuits, based on advanced verification methodology. The framework is aimed to handle system complexity, allow architectural studies for design optimisation and achieve extensive verification. In Chapter 3: first, the pixel readout chip architecture and floorplan choices are introduced; second, the contribution to the architecture optimization and comparison by means of the developed framework is summarized and results are reported for multiple stages of the design optimisation (behavioural level, initial architectures for small-scale prototypes, digital architectures for the RD53A chip). In Chapter 4, the focus moves to the power methodology defined for the optimization of the chip design and its critical serial powering scheme. Results from detailed power analysis and optimizations of the digital pixel array architecture are reported. Finally, Chapter 5 is centred on issues regarding radiation tolerance in the harsh environment and timing-related optimisations. Radiation effects and chosen design techniques are initially presented, in order to introduce the reader to the results of toplevel timing optimisation (including radiation degradation), clock distribution and tolerance to bit upsets.

## Contents

| Pı            | refac | e       |                                                        | 3         |

|---------------|-------|---------|--------------------------------------------------------|-----------|

| $\mathbf{Li}$ | st of | Figur   | es                                                     | 8         |

| $\mathbf{Li}$ | st of | Table   | 5                                                      | 15        |

| $\mathbf{Li}$ | st of | acron   | yms                                                    | 18        |

| 1             | Stat  | te of t | he art and requirements for next generation hybrid     | 1         |

|               | inte  | grated  | l chips in harsh environments                          | <b>22</b> |

|               | 1.1   | Hybrie  | d pixel detectors and applications                     | 22        |

|               |       | 1.1.1   | Silicon radiation sensor                               | 24        |

|               |       | 1.1.2   | ASIC Readout chip                                      | 25        |

|               |       |         | 1.1.2.1 The analog front-end                           | 25        |

|               |       |         | 1.1.2.2 Main concepts on digital readout architectures | 29        |

|               |       | 1.1.3   | Applications                                           | 32        |

|               | 1.2   | Phase   | 2 upgrade and requirements                             | 35        |

|               |       | 1.2.1   | Pixel chip requirements                                | 37        |

|               |       |         | 1.2.1.1 Requirements addressed in this work            | 37        |

| <b>2</b>      | Dev   | velopm  | ent and optimisation of a SystemVerilog framework      | £         |

|               | for   | the ar  | chitectural study, simulation and verification of the  | Э         |

|               | read  | dout el | lectronics                                             | 44        |

|               | 2.1   | State   | of the art and motivations                             | 45        |

|               | 2.2   | The V   | 'EPIX53 environment                                    | 48        |

|   |       | 2.2.1   | Universa         | l verification methodology components, testbench |     |

|---|-------|---------|------------------|--------------------------------------------------|-----|

|   |       |         | and tests        | 5                                                | 49  |

|   |       | 2.2.2   | Project of       | organisation for reusability and modularity      | 53  |

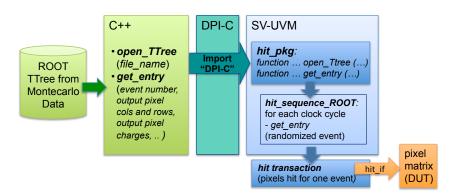

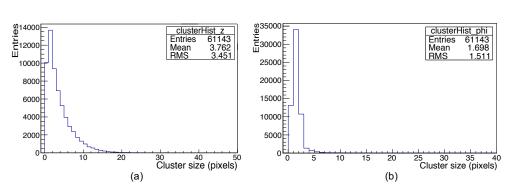

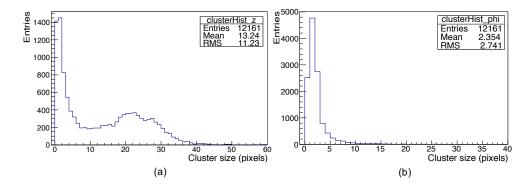

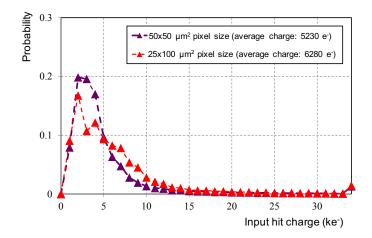

|   |       | 2.2.3   | Pixel hit        | stimuli generation                               | 55  |

|   |       |         | 2.2.3.1          | SystemVerilog interface to externally provided   |     |

|   |       |         |                  | Monte Carlo data                                 | 57  |

|   |       |         | 2.2.3.2          | Behavioural modelling of the analog front end    | 62  |

| 3 | RD    | 53A pr  | ototype          | for the phase-2 pixel upgrades: digital array    |     |

|   | arch  | nitectu | ral study        | <i>V</i>                                         | 66  |

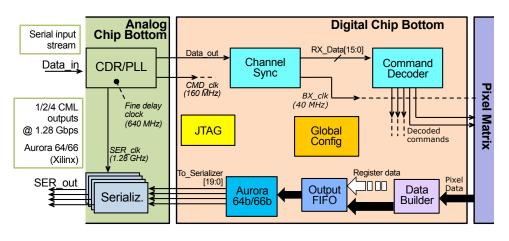

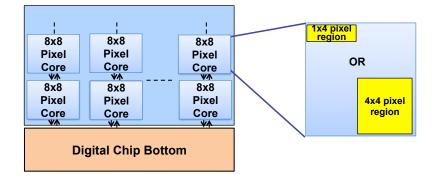

|   | 3.1   | RD53A   | A pixel re       | adout chip floorplan and architecture $\ldots$ . | 67  |

|   |       | 3.1.1   | Architec         | ture of main building blocks                     | 69  |

|   |       |         | 3.1.1.1          | Analog front ends                                | 71  |

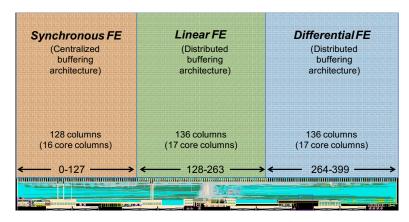

|   |       |         | 3.1.1.2          | Digital chip bottom                              | 73  |

|   | 3.2   | Digita  | l array ar       | chitectural study and choice                     | 75  |

|   |       | 3.2.1   | Architec         | tural exploration at behavioural level $\ldots$  | 75  |

|   |       | 3.2.2   | Optimisa         | ation and comparison of selected architectures   |     |

|   |       |         | impleme          | nted in small-scale prototypes                   | 80  |

|   |       |         | 3.2.2.1          | Architecture comparison: summary of results .    | 85  |

|   |       | 3.2.3   | Optimisa         | ation for the RD53A chip                         | 87  |

|   |       |         | 3.2.3.1          | Distributed Buffering Architecture               | 88  |

|   |       |         | 3.2.3.2          | Centralised Buffering Architecture               | 92  |

|   |       |         | 3.2.3.3          | Simulation performance results                   | 94  |

| 4 | Low   | -powe   | r metho          | dology and optimisation for operation with       |     |

|   | seria | al pow  | $\mathbf{ering}$ | 1                                                | 100 |

|   | 4.1   | Serial  | powering         | concept and motivations                          | 101 |

|   |       | 4.1.1   | Design c         | hallenges for low-power                          | 103 |

|   | 4.2   | Low p   | ower desig       | gn techniques                                    | 105 |

|   | 4.3   | Power   | analysis         | methodology                                      | 107 |

|   |       | 4.3.1   | Power es         | stimation for architectural choices              | 109 |

|   |       | 4.3.2   | Post-laye        | out power analysis                               | 110 |

|          |       | 4.3.3  | Validation of serial powering approach with digital power           |     |

|----------|-------|--------|---------------------------------------------------------------------|-----|

|          |       |        | profiles                                                            | 113 |

|          | 4.4   | -      | ower optimisation of the pixel array logic                          | 115 |

|          |       | 4.4.1  | Evaluation of architecture variations                               | 115 |

|          |       | 4.4.2  | Custom clock gating and local clock distribution choices            | 117 |

|          |       | 4.4.3  | Summary of results for RD53A architectures                          | 120 |

|          |       |        | 4.4.3.1 Studies on further power optimisation                       | 121 |

| <b>5</b> |       |        | timisation of the RD53A large format IC for timin                   | g   |

|          | and   | reliab | ility in harsh radiation environments                               | 128 |

|          | 5.1   | Radia  | tion effects on CMOS technologies                                   | 129 |

|          |       | 5.1.1  | Cumulative effects: Total Ionizing Dose                             | 129 |

|          |       | 5.1.2  | Single Event Effects                                                | 133 |

|          | 5.2   | Desigr | ${\bf n}$ approach for reliability in the radiation environment $~$ | 135 |

|          |       | 5.2.1  | Performance degradation of the digital logic                        | 135 |

|          |       | 5.2.2  | Single Event Effects                                                | 140 |

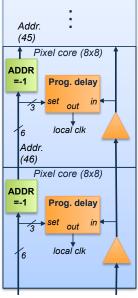

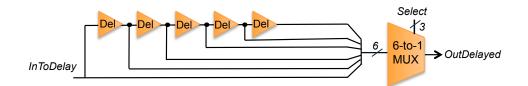

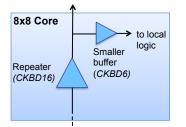

|          | 5.3   | Hierar | chical low-skew clock distribution along the column $\ . \ .$       | 143 |

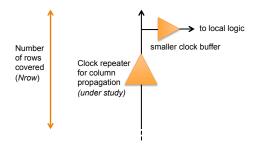

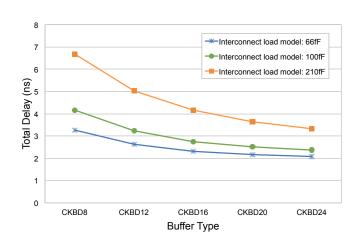

|          |       | 5.3.1  | Preliminary clock distribution study                                | 145 |

|          |       | 5.3.2  | Implemented clock distribution scheme and results $\ . \ .$         | 148 |

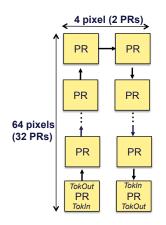

|          | 5.4   | Optim  | isation for top-level system timing closure                         | 152 |

|          |       | 5.4.1  | Preliminary study on signal propagation across pixel re-            |     |

|          |       |        | gions                                                               | 153 |

|          |       | 5.4.2  | Optimised RD53A design and results                                  | 155 |

|          |       |        | 5.4.2.1 Timing critical input signals to the array                  | 156 |

|          |       |        | 5.4.2.2 Arbitration scheme and data readout timing .                | 161 |

|          | 5.5   | Single | event upset tolerance of RD53A digital pixel matrix                 | 163 |

|          |       | 5.5.1  | Pixel configuration                                                 | 163 |

|          |       | 5.5.2  | SEU tolerance of the digital pixel array logic $\ldots \ldots$      | 168 |

| Co       | onclu | isions |                                                                     | 172 |

| Bi       | bliog | graphy |                                                                     | 176 |

# List of Figures

| 1.1  | Basic building block (i.e. pixel) of a hybrid pixel detector: sen-<br>sor and the readout electronics are separate and feature a bump              |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $connection. \ldots \ldots$ | 23 |

| 1.2  | Cross section of a single-sided p-in-n silicon sensor, with n-bulk                                                                                 |    |

|      | and p+ implant. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                              | 24 |

| 1.3  | Generic pixel detector: active area and periphery circuitry                                                                                        | 26 |

| 1.4  | Block diagram of a generic PUC                                                                                                                     | 26 |

| 1.5  | Preamplifier signals (amplitude vs time) obtained with constant                                                                                    |    |

|      | current feedback.                                                                                                                                  | 28 |

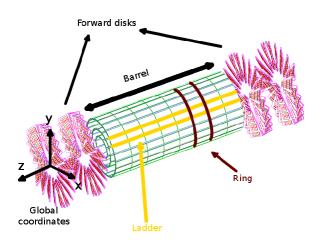

| 1.6  | Three-dimensional view of the CMS pixel layout                                                                                                     | 33 |

| 1.7  | Tracking example of a decay topology with collision vertex V                                                                                       |    |

|      | and decay vertex D. Tracks are measured by three pixel detec-                                                                                      |    |

|      | tors and detected hit pixels are highlighted. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                  | 33 |

| 1.8  | Hybrid pixel detector application for X-ray radiation imaging                                                                                      | 34 |

| 1.9  | Plan for the LHC in the next 10 years                                                                                                              | 36 |

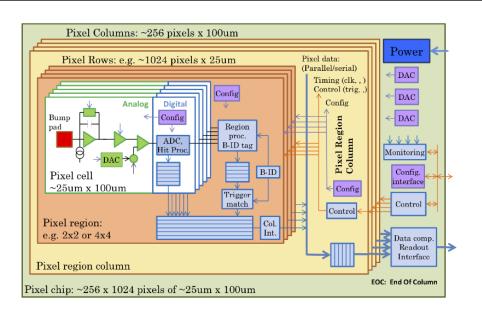

| 1.10 | Diagram of the hierarchical organisation in a 3rd generation                                                                                       |    |

|      | pixel chip, showing how pixels are grouped in regions, regions                                                                                     |    |

|      | in columns, and column pairs in a full matrix                                                                                                      | 40 |

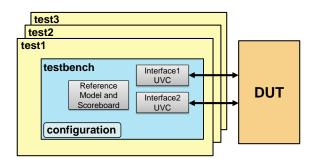

| 2.1  | Hierarchical Layers of a UVM testbench: reuse of the same test-                                                                                    |    |

|      | bench for different tests                                                                                                                          | 50 |

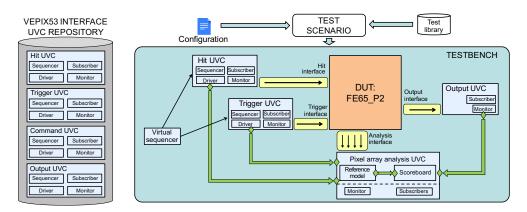

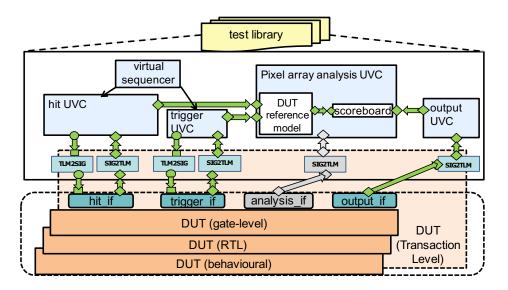

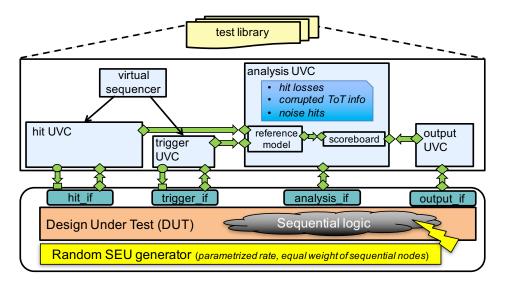

| 2.2  | Block diagram of the VEPIX53 simulation and verification en-                                                                                       |    |

|      | vironment, highlighting a set of the developed UVCs                                                                                                | 51 |

| 2.3  | Example code: factory override of the basic reference model and   |     |

|------|-------------------------------------------------------------------|-----|

|      | analysis environment with custom ones                             | 53  |

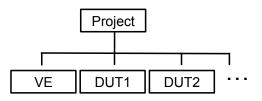

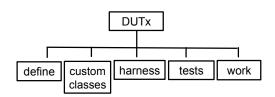

| 2.4  | Top level project directory organisation                          | 53  |

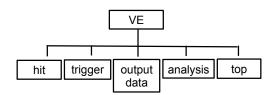

| 2.5  | Verification Environment directory organisation                   | 54  |

| 2.6  | Specific DUT directory organisation.                              | 54  |

| 2.7  | VEPIX53 block diagram emphasising its support for DUTs de-        |     |

|      | scribed at TL, behavioural, RTL and gate-level                    | 55  |

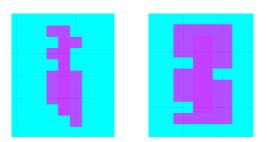

| 2.8  | Example of the signal generated by a single particle on a group   |     |

|      | of pixels                                                         | 56  |

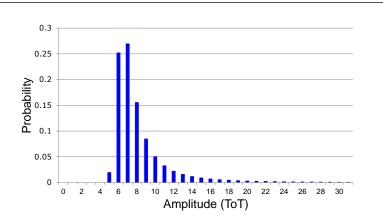

| 2.9  | Distribution of amplitude imposed to fired pixels in the SV envi- |     |

|      | ronment based on a non-uniform distribution provided through      |     |

|      | a file (example provided from detailed sensor simulations)        | 58  |

| 2.10 | Implemented DPI C++/SV interface for the generation of hit        |     |

|      | transactions                                                      | 59  |

| 2.11 | Cluster size histograms for modules in the center of the bar-     |     |

|      | rel (obtained from CMS ROOT TTrees). Sizes both along z           |     |

|      | direction (a) and $\phi$ direction (b)                            | 60  |

| 2.12 | Cluster size histograms for modules in the edges of the barrel    |     |

|      | (obtained from CMS ROOT TTrees). Sizes both along z direc-        |     |

|      | tion (a) and $\phi$ direction (b)                                 | 60  |

| 2.13 | Monitored pixel charge amplitude distribution for CMS Monte       |     |

|      | Carlo data with different pixel sizes                             | 61  |

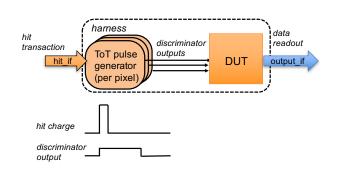

| 2.14 | Block diagram of the chip harness containing multiple ToT pulse   |     |

|      | generators                                                        | 62  |

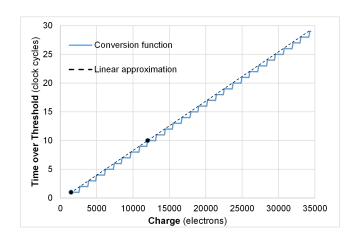

| 2.15 | Charge to ToT conversion function for the analog front-ends: a    |     |

|      | linear relation between charge and discriminator pulse duration   |     |

|      | is defined. The duration is then digitized to the number of clock | C A |

|      | cycles (ToT value).                                               | 64  |

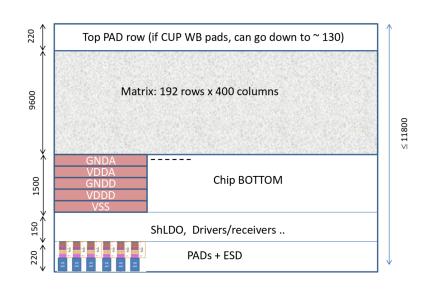

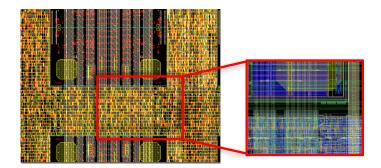

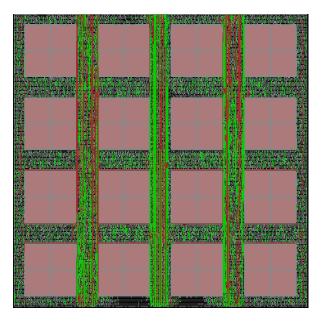

| 3.1  | RD53A floorplan organisation showing the pixel matrix, the chip   |     |

|      | bottom including power regulators (ShLDO), drivers/receivers,     |     |

|      | chip PADs and ESD protection as well as a row of top pads         | 68  |

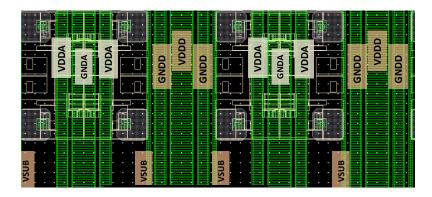

| 3.2  | Power distribution scheme for the analog (VDDA, GNDA) and                 |    |

|------|---------------------------------------------------------------------------|----|

|      | digital (VDDD, GNDD) power within the pixel matrix                        | 69 |

| 3.3  | Zoom on analog bias distribution along the matrix, using M6               |    |

|      | for bias and M5/M7 for shielding                                          | 69 |

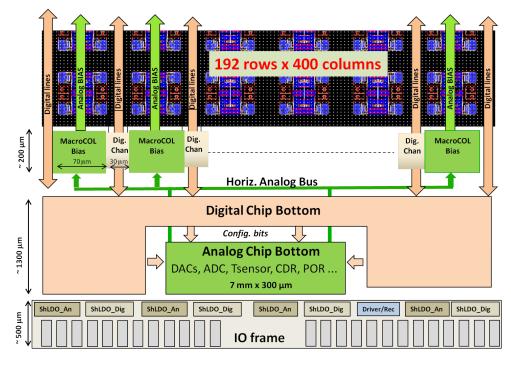

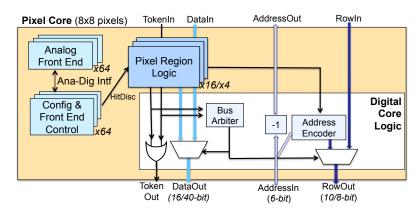

| 3.4  | RD53A floorplan functional view                                           | 70 |

| 3.5  | Arrangement of front end flavours in RD53A. The pixel column              |    |

|      | number range of each flavour is shown along the bottom. The               |    |

|      | type of digital architecture used in each flavour is also written         |    |

|      | in parenthesis                                                            | 72 |

| 3.6  | Block diagram of the digital chip bottom and its interface to the         |    |

|      | pixel matrix and ACB                                                      | 74 |

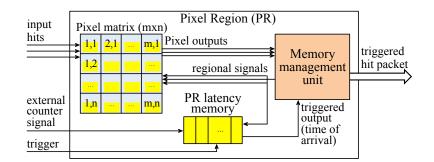

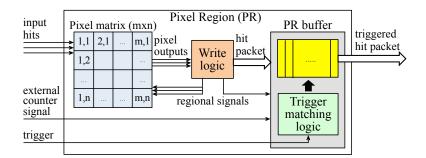

| 3.7  | Block diagram of the distributed counters buffering architecture.         | 77 |

| 3.8  | Block diagram of the centralised FIFO buffering architecture.             | 77 |

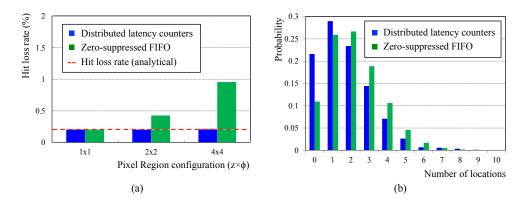

| 3.9  | (a) Hit loss rate in pixel region due to dead-time; (b) Occupancy         |    |

|      | histograms of trigger latency buffers for a $2 \times 2$ pixel region     | 79 |

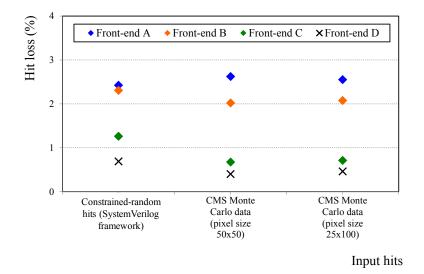

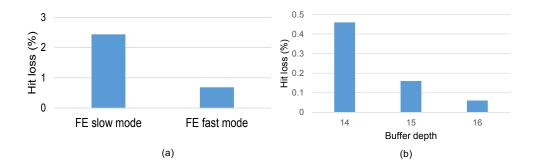

| 3.10 | Monitored hit loss due to dead-time for different analog front            |    |

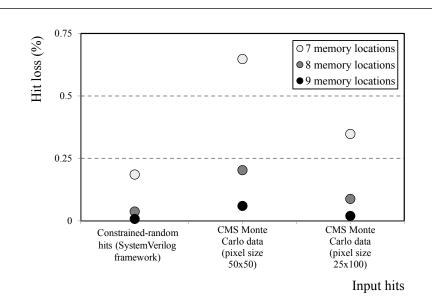

|      | ends and input hit charge distributions.                                  | 81 |

| 3.11 | Monitored hit loss due to buffer overflow for different numbers           |    |

|      | of locations and input hit charge distributions.                          | 82 |

| 3.12 | Centralized $4 \times 4$ pixel region architecture of the CHIPIX65 small- |    |

|      | scale prototype                                                           | 84 |

| 3.13 | Centralised architecture performance results.                             | 84 |

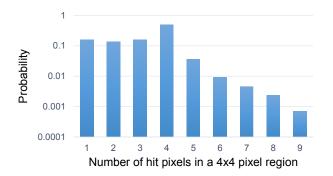

| 3.14 | Histogram of number of hit pixels per pixel region (4x4) simu-            |    |

|      | lated with external Monte Carlo data in the extreme scenario              |    |

|      | at the edges of the barrel                                                | 85 |

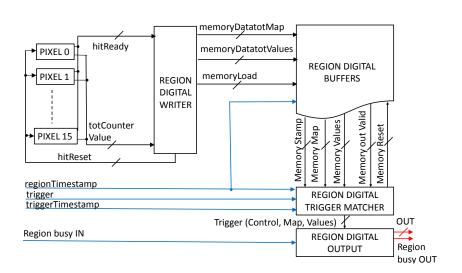

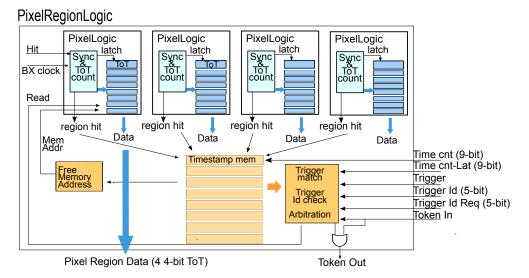

| 3.15 | Block diagram of the PR logic of the DBA architecture                     | 88 |

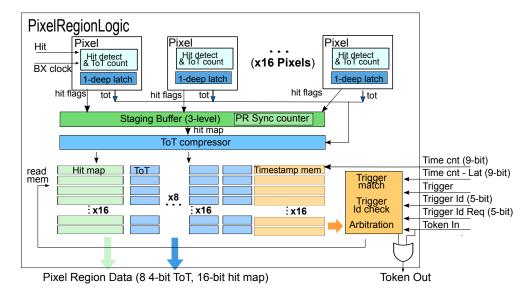

| 3.16 | Block diagram of the PR logic of the CBA architecture                     | 93 |

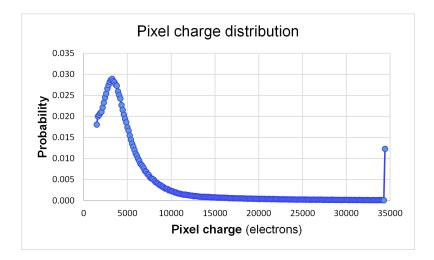

|      | Pixel charge probability distribution of CMS Monte Carlo data             |    |

|      | in the center of the barrel (pixel size $50 \times 50 \mu\text{m}^2$ )    | 97 |

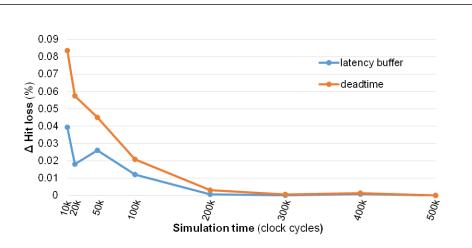

| 3.18 | Absolute difference $(\Delta)$ of hit loss percentage results with re-    |    |

|      | spect to value measured at the end of the simulation, both in             |    |

|      | the case of dead-time and latency buffer overflow                         | 98 |

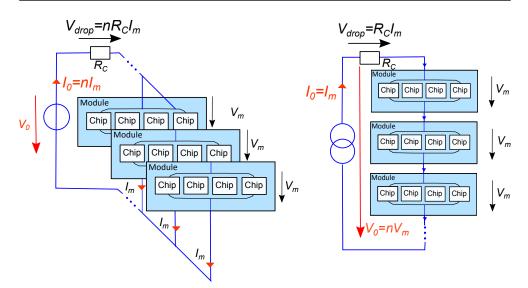

| 4.1  | Power cable losses in parallel and serial powering                               | 103 |

|------|----------------------------------------------------------------------------------|-----|

| 4.2  | Block diagram of a serial powered chip with integrated regula-                   |     |

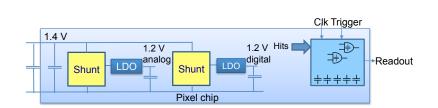

|      | tors for analog and digital domains                                              | 104 |

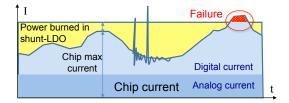

| 4.3  | Sketch showing the effect of power variations in a serial powering               |     |

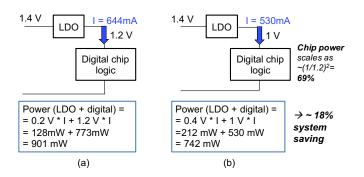

|      | scheme.                                                                          | 104 |

| 4.4  | Power estimations of the power budget improvement obtainable                     |     |

|      | with a reduced power supply for the digital domain. For the                      |     |

|      | overall power gain both the digital chip and LDO power con-                      |     |

|      | sumption are considered                                                          | 107 |

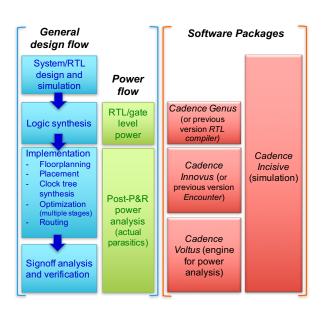

| 4.5  | Digital design flow and Cadence software packages used for the                   |     |

|      | design, power analysis and optimisation.                                         | 108 |

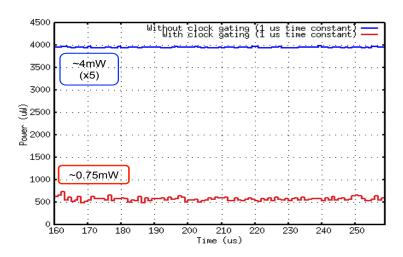

| 4.6  | Gate-level power profiles of small $4 \times 64$ pixel matrix for clock          |     |

|      | gating evaluation.                                                               | 110 |

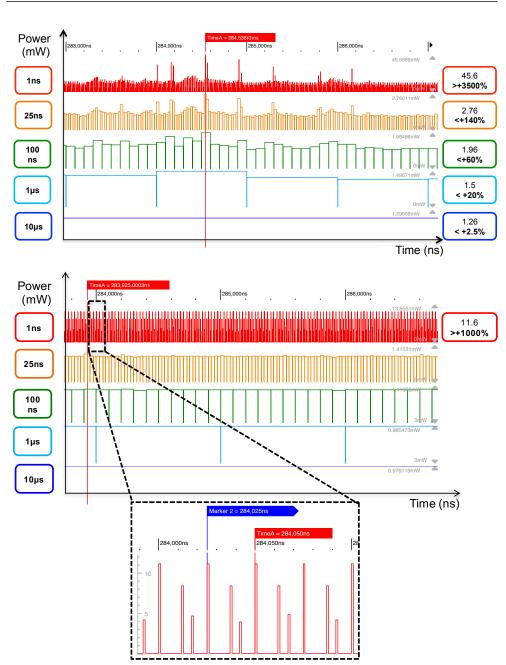

| 4.7  | Power profiles of a $4 \times 64$ pixel array at different time scales:          |     |

|      | at the top with high activity $(3\mathrm{GHz/cm^2}$ hit rate and $1\mathrm{MHz}$ |     |

|      | trigger rate) and at the bottom with low activity (only clocking                 |     |

|      | digital logic)                                                                   | 112 |

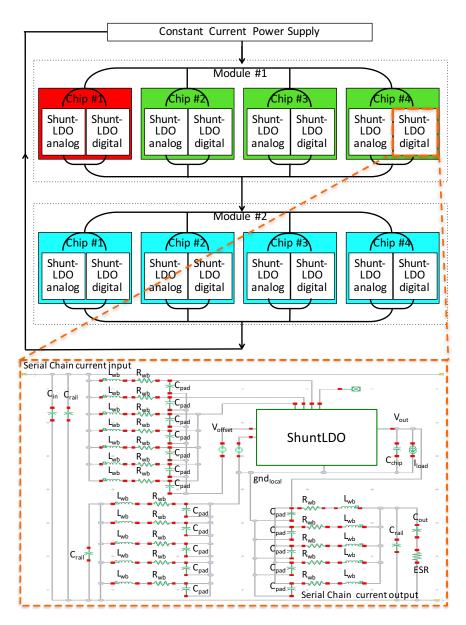

| 4.8  | Serial powering topology: two modules powered in series with                     |     |

|      | the four chips within a module and the two SLDOs per chip                        |     |

|      | powered in parallel. Detailed schematic of the basic unit is also                |     |

|      | shown                                                                            | 114 |

| 4.9  | Impact of the digital activity of a chip to the digital power do-                |     |

|      | main of the chips in a serial power chain                                        | 115 |

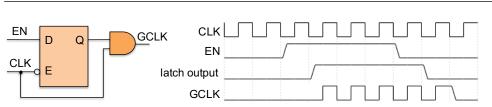

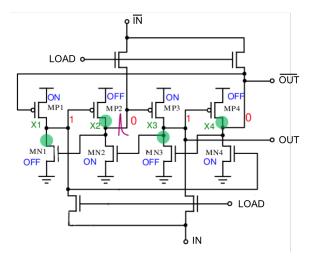

| 4.10 | Clock gating cell including an AND cell and a negative-level                     |     |

|      | sensitive latch to prevent glitches                                              | 118 |

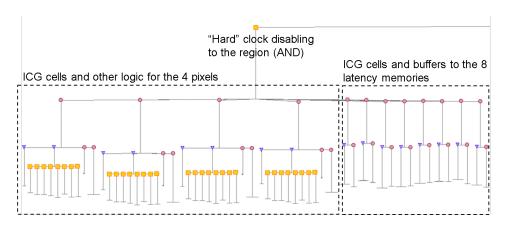

| 4.11 | Local clock distribution down to the sinks for one pixel region                  |     |

|      | made of 4 pixels. Clock gating cells are shown in red, buffers                   |     |

|      | in purple and other combinatorial logic along the clock tree in                  |     |

|      | orange                                                                           | 122 |

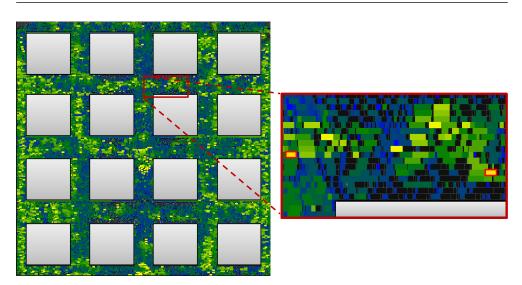

| 4.12 | Instance power map of the pixel core: the AND cells hard dis-                    |     |

|      | abling the clock (highlighted) are among the few cells with a                    |     |

|      | dark yellow colour.                                                              | 124 |

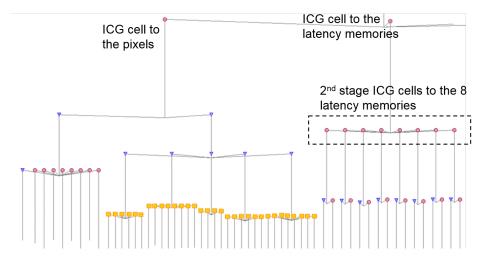

| 4.13 | Local clock distribution for one pixel region in case $#4$ from Table 4.7, after the first stage of clock buffers in the core                                                                                                                                                                 | 125 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

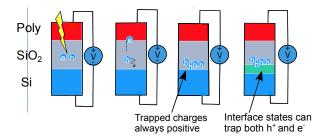

| 5.1  | Electron-hole pair generation in the silicon oxide, induced by radiation, leads to oxide-trapped holes and interface-trapped charges.                                                                                                                                                         | 130 |

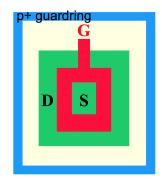

| 5.2  | NMOS transistor laid out in enclosed geometry to prevent tran-<br>sistor leakage                                                                                                                                                                                                              | 131 |

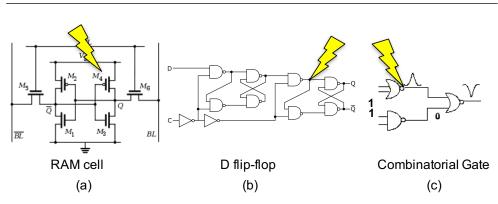

| 5.3  | Examples of SEE: SEUs on a RAM cell and on a flip-flop and a SET causing a glitch on combinatorial logic are shown respectively in (a), (b) and (c)                                                                                                                                           | 134 |

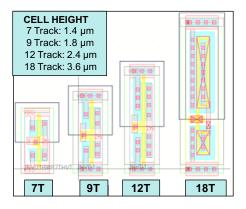

| 5.4  | Cell height for different sized digital libraries integrated in the DRAD chip: 7, 9, 12 and 18 track                                                                                                                                                                                          | 136 |

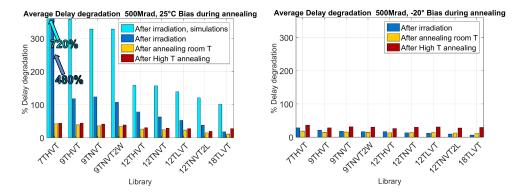

| 5.5  | Average delay degradation of standard cells from different li-<br>braries integrated in the DRAD test chip                                                                                                                                                                                    | 137 |

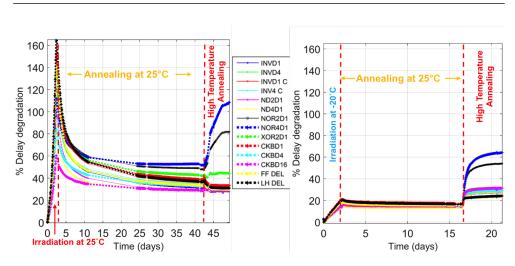

| 5.6  | Measurements of delay degradation for standard cells from 9-<br>track normal $V_t$ library after irradiation and with annealing<br>with bias                                                                                                                                                  | 138 |

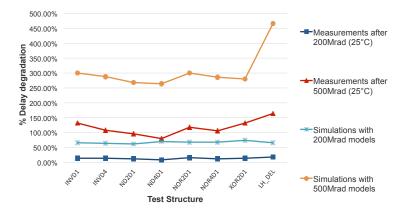

| 5.7  | Percentage delay degradation of standard cells from 9-track nor-<br>mal $V_t$ library after irradiation with respect to the ones before<br>radiation. Measurements results of the DRAD chip at differ-<br>ent temperatures are compared with results from correspondent<br>simulation models. | 139 |

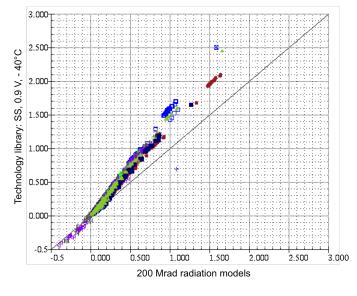

| 5.8  | Graphical library comparison between 200 Mrad radiation models and the SS, $0.9V$ , $-40^{\circ}C$ technology corner.                                                                                                                                                                         | 140 |

| 5.9  | FE-I4 clock distribution along a double column. Rectangular cells represent different delays used to compensate for the clock skew.                                                                                                                                                           | 144 |

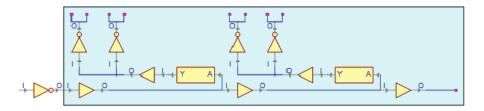

| 5.10 | Basic clock unit with one clock repeater every $Nrow$ pixel rows.                                                                                                                                                                                                                             | 146 |

| 5.11 | Propagation delay of different clock repeaters "placed" every $Nrow=20$ pixel rows, assuming 3 wire load scenarios                                                                                                                                                                            | 148 |

| 5.12 | Pixel array hierarchy, with a pixel core as building block. The                                       |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | sizes of the different pixel region architectures integrated in the                                   |     |

|      | chip are also shown.                                                                                  | 149 |

| 5.13 | Block diagram showing the core row address calculation and                                            |     |

|      | clock skew adjustment schemes for the pixel cores                                                     | 150 |

| 5.14 | Block diagram of the clock skew adjustment for the pixel cores                                        |     |

|      | (ProgrammableDelay), with static dely selection based on the                                          |     |

|      | hierarchical core-row address calculation scheme.                                                     | 150 |

| 5.15 | Propagation of the token signal across a double PR column                                             |     |

|      | $(4 \times 64 \text{ pixels})$ featuring the $2 \times 2$ PR distributed architecture                 |     |

|      | from the FE65-P2 chip prototype                                                                       | 153 |

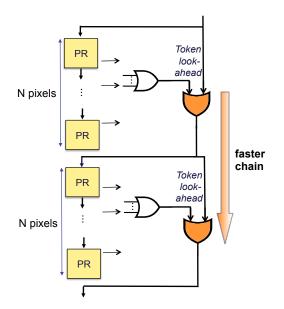

| 5.16 | "Token-look-ahead" approach proposed to speed-up data propa-                                          |     |

|      | gation along columns (critical specially including radiation degra-                                   |     |

|      | dation)                                                                                               | 155 |

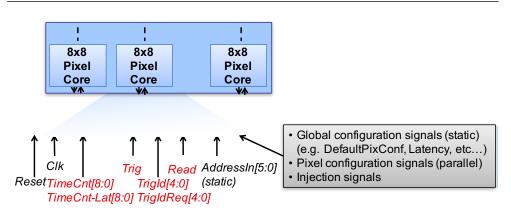

| 5.17 | Pixel array inputs to each core column, with emphasis on signals                                      |     |

|      | whose timing is critical for correct data readout (highlighted in                                     |     |

|      | red)                                                                                                  | 156 |

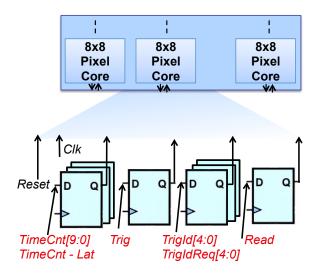

| 5.18 | Pixel array timing critical inputs being re-synchronised in each                                      |     |

|      | column, to partition the timing paths from the chip bottom to                                         |     |

|      | the matrix. $\ldots$ | 157 |

| 5.19 | Signal propagation of timing critical inputs to the array, both                                       |     |

|      | from core to core and locally. $\ldots$ . $\ldots$ . $\ldots$                                         | 158 |

| 5.20 | Routing of vertical nets connecting input and output pins for                                         |     |

|      | signals propagating from one core to the other along the column.                                      |     |

|      | Vertical metals M3 and M5 are shown respectively in green and $% \mathcal{M}$                         |     |

|      | red                                                                                                   | 159 |

| 5.21 | Block diagram of the readout of the pixel core. It includes 64                                        |     |

|      | pixels, made of 64 AFEs and dedicated AFE control and pixel                                           |     |

|      | configuration logic                                                                                   | 161 |

| 5.22 | Data packet propagated at the core column level for the DBA.                                          | 162 |

| 5.23 | DICE latch structure and functionality. $\ldots$                                                      | 164 |

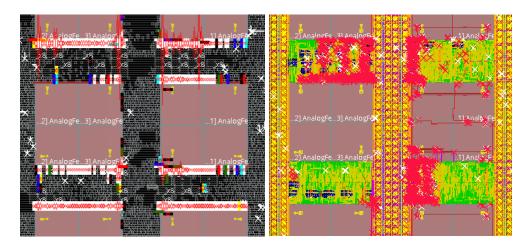

| 5.24 | Zoom of the central area of the core where most of DICE latches                                       |     |

|      | are automatically placed by tools                                                                     | 166 |

\_\_\_\_

| 5.25 | Floorplan regions assigned to each DICE latch, close to the cor-   |     |

|------|--------------------------------------------------------------------|-----|

|      | respondent analog front end and distant from each other. $\ . \ .$ | 166 |

| 5.26 | Block diagram of the simulation framework highlighting features    |     |

|      | for SEU injection                                                  | 169 |

## List of Tables

| 1.1 | Demonstrator pixel chip specifications                                                                                                                                                                        | 38  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | SystemC and SystemVerilog complementary design capabilities<br>and support of emerging methods including TLM and assertion-<br>based verification (ABV).                                                      | 47  |

| 3.1 | Main characteristics of the $65 \mathrm{nm}$ technology                                                                                                                                                       | 67  |

| 3.2 | Hit loss rate due to buffer overflow                                                                                                                                                                          | 79  |

| 3.3 | Occupation of area for different pixel memory sizes                                                                                                                                                           | 83  |

| 3.4 | Comparative table between centralised and distributed buffer architecture.                                                                                                                                    | 86  |

| 3.5 | Area utilisation reduction achieved with a latch-based imple-                                                                                                                                                 |     |

|     | mentation of the ToT memories.                                                                                                                                                                                | 90  |

| 3.6 | Area reduction achieved with the 4-bit latch full-custom block.                                                                                                                                               | 91  |

| 3.7 | Buffer performance improvements thanks to a $4 \times 1$ PR pixel region shape.                                                                                                                               | 92  |

| 3.8 | Comparative table between centralised and distributed buffering architectures.                                                                                                                                | 95  |

| 4.1 | Average power results for the typical corner at 1.2 V under a variety of activity conditions.                                                                                                                 | 111 |

| 4.2 | Results for the typical corner at $1.2 \text{ V}$ on average power con-<br>sumption, peak power (averaging at $1 \mu \text{s}$ time scale) and digital<br>area utilisation for different pixel architectures. | 116 |

|     | T                                                                                                                                                                                                             | -   |

| 4.3 | Results of the clock gating optimisation with adoption of ICG            |     |

|-----|--------------------------------------------------------------------------|-----|

|     | cells and additional automated clock gating with variable num-           |     |

|     | ber of flip flops indicated in parenthesis (FF)                          | 119 |

| 4.4 | Results for the typical corner at $1.2\mathrm{V}$ on average power con-  |     |

|     | sumption, peak power (averaging at $1 \mu s$ time scale) and digital     |     |

|     | area utilisation for the final RD53A architectures                       | 121 |

| 4.5 | Percentage contribution of global and local clock distribution           |     |

|     | to power consumption. The values shown apply to the DBA                  |     |

|     | architecture integrated in RD53A with the LFE                            | 122 |

| 4.6 | Average power consumption of each class of cells along the clock         |     |

|     | distribution for a PR, excluding buffers down in the tree                | 123 |

| 4.7 | Results for the typical corner at $1.2\mathrm{V}$ on average power con-  |     |

|     | sumption, peak power (averaging at $1 \mu s$ time scale) and digital     |     |

|     | area utilisation for different clock gating implementations              | 124 |

| 5.1 | Total propagation delay as function of different distance between        |     |

|     | repeaters, load net capacitances and buffers. Results are based          |     |

|     | on the technology corner: SS, $1.08 \text{ V}$ , $125^{\circ}\text{C}$ . | 147 |

| 5.2 | Column clock skew results of the RD53A chip prototype, across            |     |

|     | multiple technology corners. The slowest corner is at cold tem-          |     |

|     | perature since at the low supply voltage $(0.9 V)$ the adopted           |     |

|     | technology experiences temperature inversion                             | 152 |

| 5.3 | Propagation delay of the trigger and of the bunch crossing count         |     |

|     | accumulated along the RD53A core column (192 pixels)                     | 160 |

| 5.4 | Power consumption of the core-based distribution of the two              |     |

|     | bunch counts, both as absolute value and in percentage with              |     |

|     | respect to the digital pixel array. $\ldots$ . $\ldots$ . $\ldots$ .     | 160 |

| 5.5 | Propagation delay of the token, data and address accumulated             |     |

|     | along the RD53A core column (192 pixels) for the DBA. For                |     |

|     | multi-bit signals, the worst case is reported. $\ldots$ . $\ldots$ .     | 162 |

| 5.6 | 8-bit DICE latch area overhead versus 8 standard latches                 | 165 |

| 5.7 | Observed hit losses, corrupted charge data, noise hits during            |     |

|     | simulation with SEU injection of the DBA architecture. $\ldots$ .        | 170 |

# List of acronyms

| ACB           | Analog Chip Bottom                        |

|---------------|-------------------------------------------|

| ASIC          | Application-Specific Integrated Circuit24 |

| BCR           | Bunch Counter Reset73                     |

| CBA           | Centralised Buffering Architecture        |

| CDR           | Clock Data Recovery                       |

| CDC           | Clock Domain Crossing74                   |

| CMD           | CoMmand Decoder                           |

| $\mathbf{CS}$ | Channel Synchroniser73                    |

| CTS           | Clock Tree Synthesis                      |

| DAQ           | Data Acquisition System 30                |

| DBA           | Distributed Buffering Architecture        |

| DCB           | Digital Chip Bottom70                     |

| DFE           | Differential Front End                    |

| DICE          | Dual Interlocked storage CEll             |

| DPI           | Direct Programming Interface              |

| DUT           | Design Under Test 109                     |

| ECC           | Error Correction Coding141                |

| ECR           | Event Counter Reset                       |

| ELT           | Enclosed Layout Transistor                |

| EOC           | End of Column                             |

| FIFO          | First-In First-Out                        |

| FE            | Front End                                 |

| FSM  | Finite State Machine                             |

|------|--------------------------------------------------|

| HDVL | Hardware Description and Verification Language45 |

| HEP  | High Energy Physics                              |

| HLS  | High Level Synthesis                             |

| HPD  | Hybrid Pixel Detector                            |

| IBL  | Insertable b-Layer                               |

| ICG  | Integrated Clock Gating117                       |

| LDO  | Low-DropOut                                      |

| LFE  | Linear Front End71                               |

| MBU  | Multi Bit Upset                                  |

| MMMC | Multi Mode Multi Corner 138                      |

| MIP  | Minimum Ionising Particle                        |

| OOP  | Object-Oriented Programming45                    |

| OVM  | Open Verification Methodology                    |

| P&R  | Place&Route                                      |

| PLL  | Phase Locked Loop71                              |

| PR   | Pixel Region                                     |

| RTL  | Register Transfer Level                          |

| SAIF | Switching Activity Interchange Format            |

| SEB  | Single Event Burnout133                          |

| SEE  | Single Event Effect                              |

| SEGR | Single Event Gate Rupture                        |

| SEL  | Single Event Latch-up133                         |

| SET  | Single Event Transient                           |

| SEU  | Single Event Upset                               |

| SFE  | Synchronous Front End71                          |

| SLDO | Shunt and Low Drop Output                        |

| SPEF | Standard Parasitic Exchange Format               |

| SDC  | Synopsis Design Constraints                      |

| SOI           | Silicon on Insulator               |

|---------------|------------------------------------|

| STA           | Static Timing Analysis             |

| STI           | Shallow Trench Isolation131        |

| $\mathbf{SV}$ | SystemVerilog                      |

| TCF           | Toggle Count Format110             |

| TID           | Total Ionising Dose                |

| $\mathbf{TL}$ | Transaction Level                  |

| TMR           | Triple Modular Redundancy141       |

| тот           | Time over Threshold                |

| UVM           | Universal Verification Methodology |

| VCD           | Value Change Dump110               |

| VCO           | Voltage Controlled Oscillator      |

### Chapter 1

# State of the art and requirements for next generation hybrid integrated chips in harsh environments

The sensing and readout components of state of the art hybrid detectors are introduced in Section 1.1 and their applications are described. Moreover, Section 1.2 presents the requirements of next generation hybrid pixel detectors, highlighting challenges which are addressed in this work.

### 1.1 Hybrid pixel detectors and applications

The notion of pixel comes from image processing applications and it describes the smallest discernible element in a given device. A pixel detector is therefore able to detect an image and the size of the pixel corresponds to its granularity. Devices used in everyday life such as photo cameras, video cameras and X-ray films are basic examples of such systems composed of a sensing element (pixel) which interacts with photons of different energies and generates an intensity distribution i.e. the image. For HEP applications, images or patterns are not generated by visible light, but by charged particles or photons in the keV to MeV energy range, which experience an ionizing interaction with the detector.

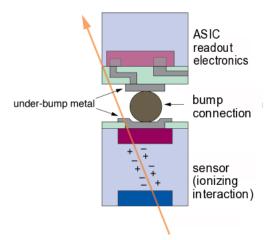

HEP experiments demand the use of the so-called HPD, since they are particularly fast and able to detect high-energy particles and electromagnetic radiation [7]. Detection is performed through different devices with specific functions: i) a sensor converts part of the energy of the radiation into an electric signal, *ii*) the signal is pre-processed by the front-end electronics and further treated by a digital readout circuitry, *iii*) eventual processing and storage allow for later inspection and data analysis. The peculiarity of "hybrid" pixel detectors comes from the fact that the sensor and the readout ASIC are fabricated separately and are then joined together through a process called bump bonding, as shown in Figure 1.1 for one single pixel. Such a process is characterised by a rather high cost, but they are also capable of standing high radiation levels and suitable for high resolution and high rate applications. The main characteristic of a hybrid pixel detector is the high density connectivity between the sensing elements and the readout electronics. For this reason it is required that the connectivity is vertical, that there is exact match between the size of the pixel and the size of the front-end electronics channel and that the electronic chip is very close (tens of  $\mu m$ ) to the sensor [7].

Figure 1.1: Basic building block (i.e. pixel) of a hybrid pixel detector: sensor and the readout electronics are separate and feature a bump connection [8].

Section 1.1.1 summarises the sensor functionality, while the Application-Specific Integrated Circuit (ASIC) and applications are presented in Section 1.1.2 and 1.1.3.

### 1.1.1 Silicon radiation sensor

At the state of the art, many different kinds of radiation sensors based on different materials have been developed (e.g. gas electron multipliers, silicon strips, pixels and drift detectors, CCDs, active pixel sensors, vacuum tube photomultipliers, avalanche photodiodes, etc.) [9]. In particular, planar silicon sensors are considered as they have been adopted for previous generation experiments (e.g. [10]) and constitute a valuable option for future detector upgrades. Nevertheless, it can be at the same time highlighted that other materials (e.g. diamond) and technologies (e.g 3D) are also being evaluated within the HEP community [11]. The geometry of the cross-section of a singlesided p-in-n silicon sensor, is shown in Figure 1.2 as a basic example: a large

Figure 1.2: Cross section of a single-sided p-in-n silicon sensor, with n-bulk and p+ implant.

area  $p^+$  implantation is placed in a n-bulk and a positive bias is applied to the back side through a ohmic  $n^+$  contact and metal layer. The electric field in the generated depletion zone allows the collection of the signal charge (electron and holes) liberated by ionizing particles. The sensor acts therefore as a reversed-biased p-n junction. The collected charge is fed to the analog frontend in the ASIC readout chip through the bump-bond connection, i.e. by DC-coupling. P<sup>+</sup>-in-n sensors have been extensively used for their simplicity, above all for applications where radiation damage is not too significant [7]. Other planar silicon sensors topologies have been also implemented and optimised for parameters such as maximum charge collection, spatial resolution, radiation harness. To provide an example, the current CMS barrel pixel detector features a so-called double-sided n-in-n approach [10] and implements special layout inter-pixel isolation techniques, which assure better radiation tolerance and spatial resolution. It is anyway not the purpose of this work to describe in details all possible sensor topologies and layouts, but it can be mentioned that for CMS upgrade a different topology (i.e. a single-sided n-in-p approach [11]) is currently identified as the silicon planar sensor candidate.

#### 1.1.2 ASIC Readout chip

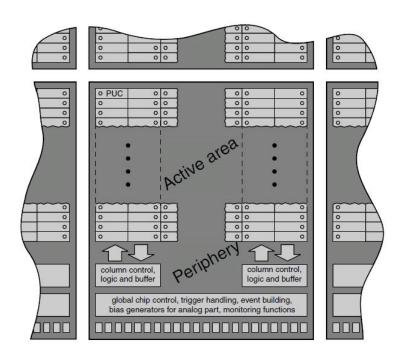

Pixel detectors readout chips feature different geometries, readout approaches and analog devices, but the main properties and the hierarchy are common to most of them. They are indeed composed of an active area which contains a repetitive matrix of elementary pixels directly interfacing the sensor and of a chip periphery, in charge of global control, data buffering and readout and global configuration. The described hierarchy is shown in Figure 1.3.

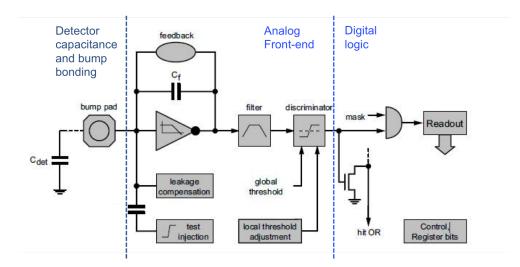

The active area, also referred to as pixel matrix or pixel array, is composed of elementary electronic units called Pixel Unit Cells (PUCs). In the small pixel size, a PUC integrates an analog front-end, required to perform analogto-digital conversion of the charge collected in the sensor, and digital processing, possibly including data storage. A basic block diagram is reported in Figure 1.4, where the interface between analog and digital logic is highlighted. Its components are described more in detail in Section 1.1.2.1 and 1.1.2.2.

#### 1.1.2.1 The analog front-end

An analog front end is usually implemented with a cascade of a few amplifying stages. The first stage is the preamplifier, while the following ones are band-limited and determine the frequency spectrum of the output pulse and its shape, forming the filter or pulse shaper. This filtering is required as detector signals are very fast and their shape cannot be preserved with limited band-

Figure 1.3: Generic pixel detector: active area and periphery circuitry [7].

Figure 1.4: Block diagram of a generic PUC [7].

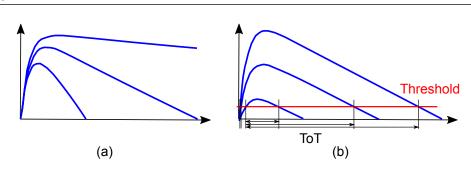

width and power consumption. Different front-end architectures are available in literature and they have been used for different applications and requirements [9]. The most relevant front-end architecture is the one whose generic scheme, without implementation details, is showed in Figure 1.4. The output of the analog circuitry is fed to a discriminator, which outputs a digital signal. This can be either considered a binary hit, as done in a few cases in literature (e.g. [12], [13]), or a further amplitude measurement can be performed. In the analog front end, an inverting amplifier with feedback capacitance converts the input charge to a voltage. The preamplifier is a crucial part of the circuit and it is designed taking into account many metrics (e.g. gain, bandwidth, power, noise, etc.). In circuits where the preamplifier output is directly interfaced with the discriminator (without a separate filter), the discharge must be completed before the next signal arrives, to avoid overlap. On the other hand, a fast discharge can lead to a reduction of the peak amplitude if it starts before the signal has reached its peak. This concept can be noticed in Figure 1.5 (a), where discharges with different feedback time constants are shown. Analog to digital conversion of the collected charge is performed through a Time over Threshold (ToT) measurement, where the ToT is the number of clock cycles during which the signal is higher than the discriminator threshold. Ideally the pulse width is supposed to be proportional to the input charge. Digitization into a defined number of bits can be done with simple approaches, i.e. using a clock signal and a digital counter for each channel. Alternatively a clock counter can be centralised and its output is latched into local registers when the leading and trailing edge transitions are detected by the single channels and the ToT is obtained by difference. Either way, the time constant of the discharge is defined based on the digital ToT counting speed capabilities (dependent on the clock period). Aiming to obtain a linear behaviour, a constant current discharge is normally adopted to extend the preamplifier output pulse. The concept is shown in Figure 1.5 (b) for multiple charge amplitudes.

Dead-time is introduced in the measurement due to the limited ToT counting speed. Dead-time is an important metric, since it is source of hit losses that can become severe when high hit rates are encountered. In the field of radiation detection [14], dead-time is usually modelled either by a paralyzable

Figure 1.5: Preamplifier signals (amplitude vs time) obtained with constant current feedback. A variation in the feedback time constant is shown (a). ToT measurments for different input charges with fixed time constant are displayed (b).

or non-paralyzable system. In the first case, events occurring during the dead period are not recorded, but still extend the dead-time duration. In the second case, events received during the dead-time are lost and do not have an effect on the detector behaviour. The first model resembles more the behaviour of the system of interest, since additional charge extends the ToT pulse width. For a paralyzable system the distribution of intervals between random events occurring at an average rate n is  $P_1(T)dT = ne^{-nT}dT$  [14]. The probability of intervals larger than  $\tau$  is obtained by integration:

$$P_2(T) = \int_{\tau}^{\infty} P_1(T) dT = e^{-n\tau}.$$

(1.1)

The recorded input rate m corresponds to the true rate n multiplied by this factor. In terms of first-order losses the two dead-time models are equivalent and differ only for very high input rates. For  $n \ll 1/\tau$ , both non-paralyzable and paralyzable models can be approximated to:

$$m \cong n(1 - n\tau). \tag{1.2}$$

Even if  $\tau$  is not a fixed value for the system of interest (as it varies with the input charge) the average dead-time can be used as a reference to estimate correspondent losses. An example related to the target application is provided, considering a pixel as the paralyzable system, a 75 kHz input rate and a bunch crossing period of 25 ns. If an average ToT=4 is assumed, this leads to deadtime losses of

$$\frac{n-m}{n} = n\tau = 75 \, kHz \cdot 100 \, ns = 0.75\%. \tag{1.3}$$

In general, the amount of tolerable dead-time depends on the particular application. Requirements related to this work will be discussed in Section 1.2.1.

Besides dead-time, other key parameters of analog front-end designs are [9]:

- peaking time, the time required for the signal to swing from the baseline to the peak: it has to be fast enough for the signal to go above threshold in the right cycle;

- gain, ratio between the peak of the output voltage and the input charge;

- noise, due to intrinsic disturbances generated within the sensor and the front-end amplifier;

- time resolution, with an accuracy that strongly depends on the application;

- power consumption is also a central metric and constitutes a trade-off with speed and analog performance.

#### 1.1.2.2 Main concepts on digital readout architectures

The readout architecture of the ASICs of HPDs depends very much on the target application. Position, time and possibly the corresponding pulse amplitude, of all hits belonging to an interaction must usually be provided in HEP. The choice of a suited architecture depends on a number of factors, e.g. on the available chip technology and on the acceptable hit losses.

General aspects of digital readout architectures will be introduced in the following paragraphs, while a detailed evaluation of architectures suitable for this work will be presented in Chapter 2.

Architectures with zero suppression In hybrid pixel detector ASICs, digital architectures typically process only pixels with amplitudes above a threshold, in order to reduce the size of buffers which are often required to store data for a certain amount of time. This readout approach, where only a reduced number of pixels of the full pixel matrix are processed, is referred to as zero suppression [7]. Ideally, the aim of any architecture is to read out exclusively non-zero hits to optimise the use of local buffering and readout bandwidth.

**Trigger-less and triggered architectures** Experiments with low input rates can afford to read out all the impinging pixel hits immediately after the interaction. If higher rates are involved, on-detector data reduction is needed in order to obtain a feasible data rate towards the Data Acquisition System (DAQ). For this reason, usually a trigger signal is used for selection of hits of interest. The generation of the trigger signal is based on the analysis of many sub-detectors of the experiment. This analysis has to happen within a fixed latency after the particle has been detected, for the trigger to be correctly produced. Storage logic is required to maintain the data until the trigger latency has expired. Trigger latency is currently in the order of around 100 cycles (correspondent to bunch crossing interactions) and will be incremented in the future detectors, see Section 1.2). Moreover, depending on the trigger rate and possible bursts of consecutive triggers, chips must be capable of accepting new triggers before data of the previous ones are fully read out. Some relevant references of trigger-less architectures, each of one supporting different input rates, are the following: Timepix [15], CLICpix demonstrator [16], ToPix [17], Timepix3 [18] and Velopix [19]. The details of these architectures will not be reported, since the focus of this thesis is on triggered readout architectures for very high hit rates.

As far as triggered architectures are concerned, data buffering can be implemented with different approaches and storage elements can be located in different parts of the pixel chip (End of Column (EOC), single PUC, region of certain number of PUCs), implementing different readout schemes. Moreover, limited buffering constrained by the area available, can be a substantial source of hit loss unless this issue is properly addressed at design time. For the target application this point will be analysed in Chapter 2. An overview of state of the art triggered readout architectures [20] and their evolution over the years is herein summarised. In the so-called "timer architecture" [21], an analog timer delay is used to perform a coincidence with the trigger signal, identifying the pixels to be read out. Readout architectures have evolved to a digital implementation of the the trigger matching mechanism. In particular a "digital delay", in form of a timestamp counter has been used with different implementation approaches. For many relevant architectures, such counters are located in the EOC. In particular, the initial development of the Front End-A chip of the ATLAS group features counters in the EOC and implements a "conveyor belt architecture", since pixel hits are transported uniformly to the periphery: each clock cycle hit addresses are moved from the pixels to the EOC where they are assigned a timestamp counter, counting the remaining clock cycles to reach the latency. In order to avoid hit data loss during the trigger latency without increasing pixel area with local storage a "column drain architecture" has been similarly used by the CMS pixel chip [22] and the ATLAS FEI-3 [23]. The peculiarity of this approach is that buffering during the trigger latency is performed in the column periphery, whereas in the PUC only one hit at the time is stored. To this end, pixel data are moved to the EOC as quickly as possible. This reduces the pixel dead-time and makes the latency loss only dependent on the EOC buffering. The main difference between the CMS and the ATLAS approach is in the way the timestamp is made available to the pixels. Association of the timestamp to the pixels is performed with a pointer mechanism or with distribution of the bus to the whole chip. An alternative approach, i.e. with a 2-deep buffer and trigger matching logic in the pixel, was used by the ALICE chip [24]. In this case both the timestamp bus and the trigger are distributed to all the pixels: the timestamp is expressed as a particular 8-bit up-down counting time pattern which is stored locally and later compared to the time pattern itself to assess the expiration of the trigger latency.

The second generation of ATLAS [25] and CMS [26] pixel chips also implement a triggered readout, but with different schemes. The CMS PSI46DIG pixel chip keeps the architecture concept almost unaltered, but changes the readout implementation from analog to digital and increases the EOC buffering in order to cope with increased input and trigger rates. ATLAS FE-I4 has successfully explored the possibility of introducing a regional readout architecture, which combines digital processing and triggerring logic from every group of 4 pixels into one synthesized logic block. Placing most digital processing within the pixel matrix makes it possible to sustain higher hit rates while reducing digital power, because most hits are held within their respective region until the trigger latency expires, and then erased, with no need for high data bandwidth between pixels and periphery. Moreover, this chip has profited from a more scaled technology (130 nm vs the previous generation 250 nm), which has allowed the required storage resources to fit in the pixel array. The drawback of local digital processing is the need to distribute clock and trigger signals throughout the pixel matrix, with potential digital noise injection into the front ends [27].

### 1.1.3 Applications

The main applications of pixel detectors can be found in particle physics but their use has spread in a variety of other fields related to imaging. An brief description of both fields is provided in this section.

HEP applications can be found in the context of the Physics Program of the experiment at the LHC, which is aimed at answering fundamental questions in particle physics (e.g. the origin of elementary particle masses, nature of the dark matter, fundamental forces, difference between matter and antimatter, etc.). To this purpose, protons are accelerated up to 7 TeV (design value) and circulate in a 27 km-long accelerator vacuum pipe 100 m underground: one beam of protons rotates clockwise, and the other beam counterclockwise in separate but close orbits and they can be forced to collide in specific regions around which the experiments are located [7]. Collisions cause the so called events, i.e. fundamental interaction between subatomic particles, occurring in a very short time span, at a well-localized region of space. Therefore, individual charged particles, usually triggered by other subdetectors, have to be identified with high demands on spatial resolution and timing. Most of the mentioned LHC-collider-detectors at CERN, i.e. ALICE, ATLAS, CMS, LHCb, as well as fixed target experiments (e.g. NA62 [28]) employ the hybrid pixel technique to build pixel detectors covering large scale surfaces ( $\sim \text{few m}^2$ ). The detectors are normally arranged in cylindrical barrels layers and disks, as shown in the example from the CMS detector in Figure 1.6.

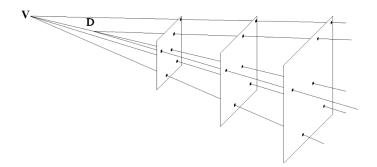

The main purpose that these detectors must serve is particle tracking in order to allow i identification of short lived particles, ii pattern recognition and event reconstruction, iii momentum measurement [30]. An example of

Figure 1.6: Three-dimensional view of the CMS pixel layout [29].

Figure 1.7: Tracking example of a decay topology with collision vertex V and decay vertex D. Tracks are measured by three pixel detectors and detected hit pixels are highlighted [7].

a decay of a short-lived particle is shown in Figure 1.7. It is required that tracks emerging from the fast decay are measured as close as possible to the interaction point. Time and spatial resolution are therefore important for such an application, as well as good granularity, which helps to distinguish the track of interest from many others which may confuse the picture (above all in a high rate context). Figure 1.7 shows this concept by using three pixel detectors to reconstruct the desired particle track, by finding positions of charged particles at a number of key points and therefore recording their paths. Pixel detectors for particle tracking are very demanding since they need to reconstruct a huge number of charge particle trajectories in three dimensions, whereas the time

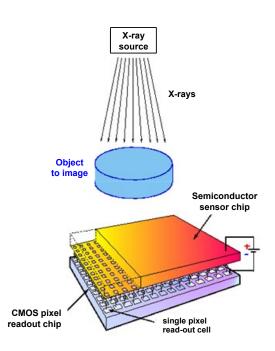

Figure 1.8: Hybrid pixel detector application for X-ray radiation imaging [31].

between two beam crossings is only a fraction of a microsecond. The most critical part of these detectors consists in the inner layers that are usually referred to as the "vertex detector" or "Inner tracker". In this context, which is related to the subject of this thesis, the use of hybrid "pixelated" detectors, is necessary.

Although these devices were developed for high-energy ionizing particles and radiation beyond visible light, they have been also adopted in many other areas. In particular, radiation imaging has become one fundamental target for hybrid pixel detectors. The basic detection mechanism is shown in Figure 1.8: the object to be imaged is placed between the X-ray source and the detector and a certain amount of X-ray is absorbed by the object (depending on its density and composition). The X-rays that pass through the object are captured by the detector, which is capable of reconstructing the image and possibly also determine properties of the material. X-ray imaging performed by hybrid pixel X-ray cameras has represented an advancement with respect to usual CCD or CMOS cameras and numerous applications have been opened in material sciences (crystallography), non-destructive control, biomedical imaging and clinical imaging leading to a growing industrialization [32]. Moreover, neutron transmission radiography has also shown to be a valuable application for structures which are hardly distinguishable with X-ray radiography, thanks to the different attenuation factors in the two cases [33]. The interest shown from these communities has pushed experts to develop hybrid pixel circuits dedicated imaging applications, such as X-ray detection. The Medipix collaboration at CERN has been one outstanding example of this effort and it has delivered a whole family of chips [15], [34], [35]. These ASICs will not be described in further details, as the main application of this thesis is particle tracking for next generation high energy physics experiments.

### 1.2 Phase 2 upgrade and requirements

A description of the pixel detector upgrade conditions and quantitative requirements is herein provided [36], as it defines the specifications for the readout chip subject of this work [37]. Within the LHC, protons acceleration and control of their trajectories is achieved by grouping them into bunches which cross each other with constant frequency. An important parameter in accelerator experiments is the number of events that one can expect for a particular reaction. For fixed-target experiments the interaction rate  $\phi$  depends on the rate of beam particles *n* hitting the target, the cross section for the reaction under study,  $\sigma$ , and the target thickness *d* (in cm) according to where  $\sigma$  is the cross section per nucleon,  $N_A$  Avogadro's number and  $\varrho$  the density of the target material (in g/cm<sup>3</sup>) [38]:

$$\phi = \sigma \cdot N_A \; [mol^{-1}]/g \cdot \varrho \cdot n \cdot d \; . \tag{1.4}$$

Equation 1.4 can be written by defining a reference quantity L called luminosity

$$\phi = \sigma \cdot L \,, \tag{1.5}$$

which can be seen as the interaction rate for unitary cross section. In collider experiments luminosity definition adds a level of complexity as it is a combination of two particle beams which are one the target of the other. It is out

Figure 1.9: Plan for the LHC in the next 10 years [42].

of the scope of this work to give a detailed physics explanation, which can be found in [38] and [39].

In the first major physics run (Run 1) in 2011 and 2012, the collider reached a peak luminosity of  $7.7 \ge 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup>. The pile-up, i.e the number of interactions per bunch crossing, has reached a peak of almost 40 in 2012 [40]. Each of its two general purpose experiments ATLAS and CMS, have acquired and processed a huge amount of data which has yielded a vast quantity of physics results [41]. Nevertheless, many physics studies and research are needed to expand the physics potential of the LHC, in particular for rare and statistically limited standard model (SM) and beyond standard model (BSM) processes. Major revisions to the machine and the experiments are therefore necessary and a series of long periods of data-taking (referred to as Run 1, Run 2, etc.) interleaved with Long Shutdowns, designated LS1 (2013-2014), LS2 (2019-2020), LS3 (2024-2025), have been planned, as shown in Figure 1.9.

Run 2 is ongoing at the time of writing, reaching pile-up peaks of 70-80 [43], whereas this thesis is part of the effort for developing electronics systems for the LS3, also referred to as High Luminosity LHC or Phase 2 upgrade. The proposed operating scenario is to level the instantaneous luminosity at  $5 \ge 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> for a further 10 years of operation, with potential peaks of  $2 \ge 10^{35}$  cm<sup>-2</sup> s<sup>-1</sup> [41]. The foreseen pile-up for the ATLAS and CMS experiments is much higher than previously, i.e. 200. The HL-LHC is expected to run at

a centre-of-mass energy of 14 TeV and with a bunch spacing of 25 ns i.e. at 40 MHz frequency. As a general remark concerning the upgrade of hybrid pixel detectors for the Inner Tracker, closest to the interaction point, the increase in radiation levels requires improved radiation hardness, while the larger particle density requires higher detector granularity, increased bandwidth to accommodate higher data rates, and improved trigger capability to keep the trigger rate at an acceptable level while not compromising physics potential. ATLAS and CMS are carrying out a common development in the framework of RD53 collaboration [4] to develop a pixel readout integrated chip in 65 nm CMOS technology for the for extreme rate and radiation. Aforementioned operating conditions have an impact on the requirements of the sensor and readout electronics: the latter, subject of this work, will be described in detail in 1.2.1.

#### 1.2.1 Pixel chip requirements

Phase 2 upgrade operating conditions, with high instantaneous luminosity and consequently high pile-up, contribute to define a set of requirements for the ASIC readout chip. The specifications of the pixel chip demonstrator object of this work are summarised in Table 1.1 for completeness. Requirements addressed by this work are described more in detail in Section 1.2.1.1.

#### 1.2.1.1 Requirements addressed in this work

**Hit rate and efficiency** One of the most challenging design requirements for the readout electronics is to be capable of withstanding a hit rate of  $3 \text{ GHz}/cm^2$  with negligible losses (<1%). For a readout ASIC, the hit rate ( $R_H$ ) indicates the flux of particle on a certain area on the active area of the sensor:

$$R_H = \frac{N_{hit \ pixels}}{T \cdot A_{chip}} , \qquad (1.6)$$

where  $N_{hit \ pixels}$  indicates the number of pixels hit in the area  $A_{chip}$  over the time period T. The high hit rate requirements poses challenges on guaranteeing the target hit efficiency for the overall pixel chip  $E_H$ , defined as the ratio

$$E_H = \frac{N_{readout \, pixels}}{N_{hit \, pixels}} \tag{1.7}$$

| Technology                                 | $65\mathrm{nm}\mathrm{CMOS}$                                        |

|--------------------------------------------|---------------------------------------------------------------------|

| Chip size                                  | $20 \mathrm{x} 11.8 \mathrm{mm^2}$                                  |

|                                            | $(\sim half size of final chips)$                                   |

| Pixel size                                 | $50 \text{x} 50  \mu \text{m}^2,  25 \text{x} 100  \mu \text{m}^2$  |

| Detector capacitance                       | $< 100{ m fF}$                                                      |

|                                            | (200 fF for edge pixels)                                            |

| Detector leakage current                   | $< 10\mathrm{nA}$                                                   |

|                                            | $(20 \mathrm{nA} \text{ for edge pixels})$                          |

| Detection threshold                        | $< 600\mathrm{e}^-$                                                 |

| In-time threshold                          | $< 1200\mathrm{e}^-$                                                |

| Hit rate                                   | $< 3{ m GHz/cm^2}$                                                  |

| Noise hit occupancy                        | $< 10^{-6}$                                                         |

| Charge resolution                          | 4 bit ToT                                                           |

| Hit loss                                   | $< 1\% \mathrm{~at}~ 3 \mathrm{~GHz/cm^2}$                          |

| Trigger rate                               | $\leq 1\mathrm{MHz}$                                                |

| Readout data rate                          | $< 5.12{ m Gb/s}$                                                   |

| Radiation tolerance                        | $500 \operatorname{Mrad} (\operatorname{TID})$                      |

|                                            | $10^{16} \mathrm{~n}_{eq}/\mathrm{cm}^2$ at $-15^{\circ}\mathrm{C}$ |

| SEU affecting whole chip                   | $< 0.05/{ m hr/chip}$                                               |

|                                            | at 1.5 $\rm GHz/cm^2$ particle flux                                 |

| Power consumption at max. hit/trigger rate | $< 1{ m W/cm^2}$                                                    |

| Temperature range                          | $-40^{\circ}\mathrm{C} \text{ to } +40^{\circ}\mathrm{C}$           |

Table 1.1: Demonstrator pixel chip specifications

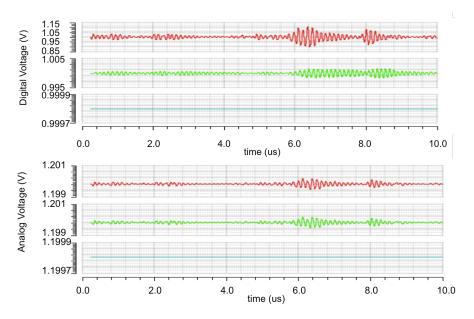

between the number of pixel correctly read out at the output of the chip  $N_{readout \ pixels}$  and the number of hit pixels  $N_{hit \ pixels}$ . Losses are composed of a combination of dead-time of the analog front-end and digital losses due to limited buffering for hit storage.