## Università degli Studi di Napoli Federico II DIPARTIMENTO DI FISICA "ETTORE PANCINI" Dottorato di Ricerca in Fisica Fondamentale ed Applicata

XXVIII ciclo

2013-2016

PhD Thesis

### Development of FPGA-based High-Speed serial links for High Energy Physics Experiments

Supervisors

Prof. Mariagrazia Alviggi Dr. Raffaele Giordano Dr. Vincenzo Izzo Candidate Sabrina Perrella

CERN-THESIS-2016-381

#### CONTENTS

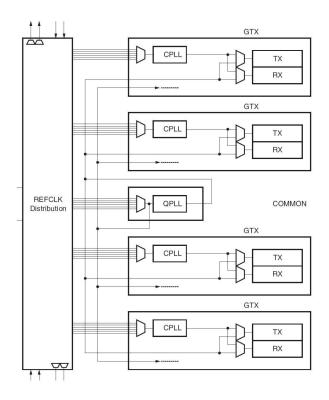

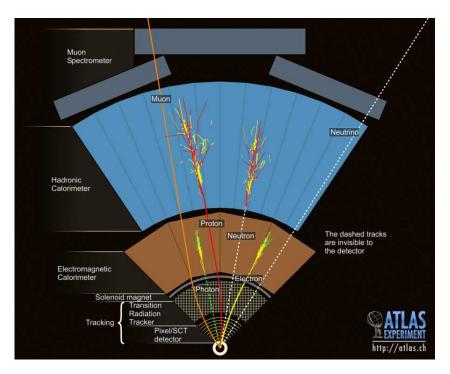

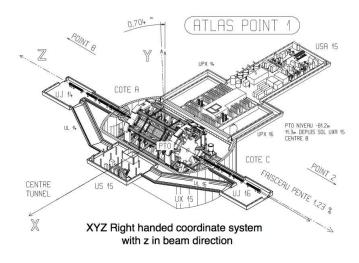

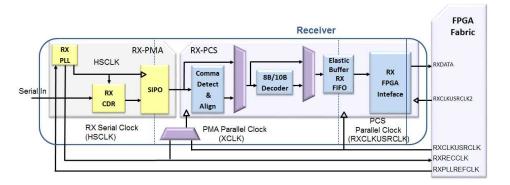

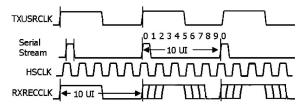

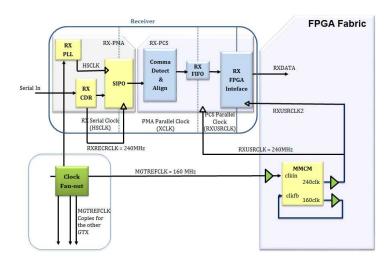

INTRODUCTION 1 1 SERIAL LINK 2 5 Serial versus parallel transmission 2.1 6 Binary coding of data 2.2 8B/10B Encoding 2.2.1 9 Conditional Inversion Master Transition protocol: CIMT 2.2.2 9 Scrambling 2.2.3 10 2.3 Transmission media 11 **Electric lines** 2.3.1 11 2.3.2 Fiber optics 12 2.4 Clock and Data Recovery 13 2.5 Serial to Parallel and Parallel to Serial Conversion: SerDes 16 2.6 Equalization 16 2.7 Link performance: Bit Error Ratio Test and Jitter Tolerance 17 BER 2.7.1 17 **Equipment and Procedures** 2.7.2 18 **Jitter** 2.7.3 19 2.8 Legacy High-speed serial links in HEP: G-Link and S-Link 24 State-Of-Art of High Speed Data Links in HEP 2.9 27 An ASIC SerDes: the GBT 28 2.9.1 2.9.2 **Off-The shelf SerDes** 30 SELF ADAPTIVE SERIAL LINK 33 3 3.1 State of the Art and Motivation 34 3.2 Field Programmable Gate Array, FPGA 36 FPGA's Technologies 3.2.1 36 **Design** Flow 3.2.2 37 3.2.3 MGTs in Xilinx FPGAs: GTP and GTX 39 3.3 Implementation 44 Handshake Mechanism 3.3.1 44 The Resynchronization procedure 3.3.2 46 TX and RX Module Architecture 3.3.3 47 Line rate validation procedure 3.3.4 49 Test Setup and result 3.3.5 50 ATLAS 55 4 The Large Hadron Collider 56 4.1 4.2 Physics at LHC 58 4.2.1 The Standard Model 58 The ATLAS Detector 61 4.3

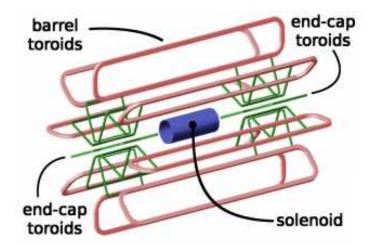

- 4.3.1 ATLAS Magnets 63

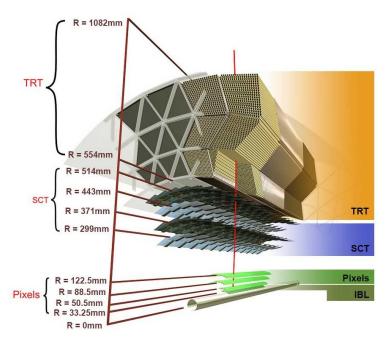

- 4.3.2 The Inner Detector 64

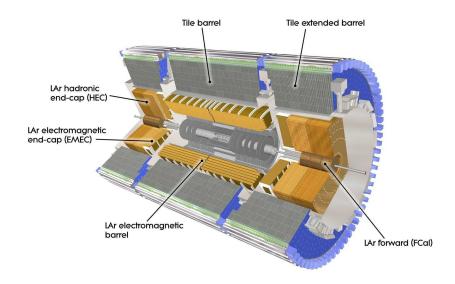

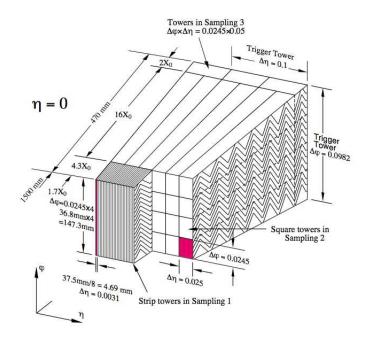

- 4.3.3 The Calorimetric System

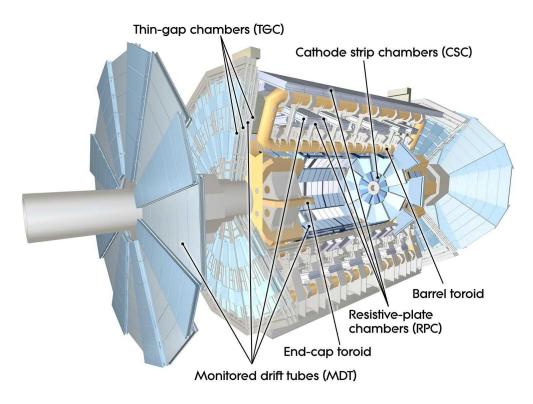

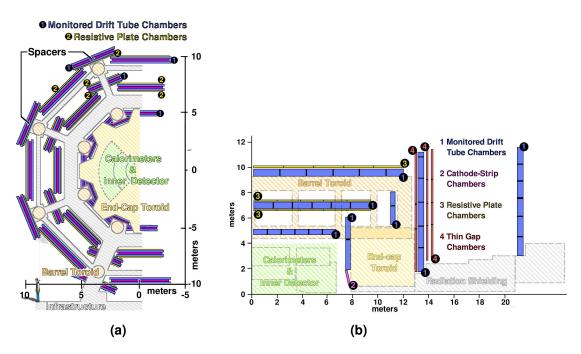

- 4.3.4 The Muon Spectrometer 67

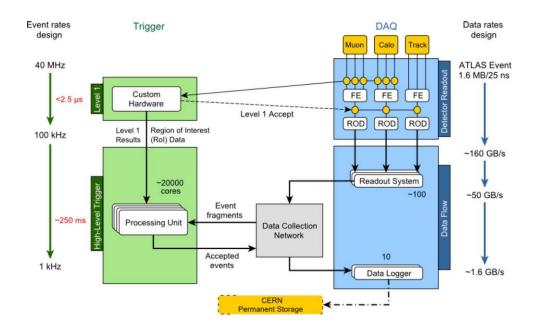

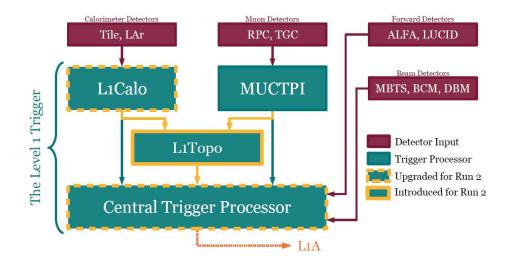

- 4.3.5 Trigger and Data Acquisition System 69

- 4.3.6 The Detector Upgrades 70

#### 5 SERIAL LINKS FOR ATLAS TDAQ UPGRADES 73

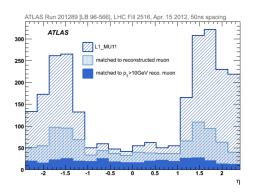

5.1 A high-speed serial link for the Barrel Level-1 muon trigger 74

65

- 5.1.1 Level-1 Trigger 74

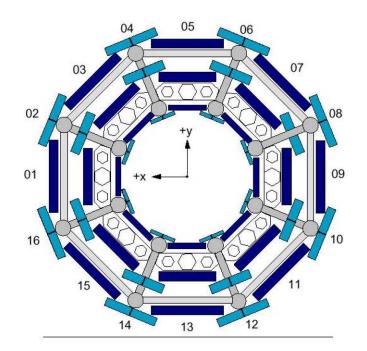

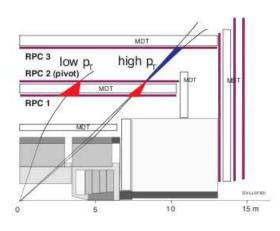

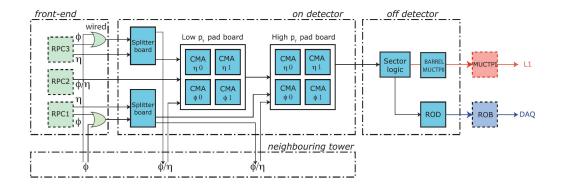

- 5.1.2 The Barrel Trigger System 75

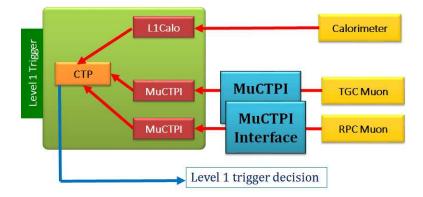

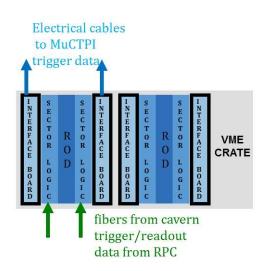

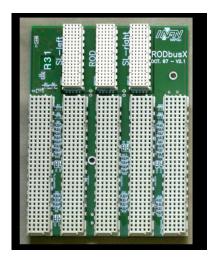

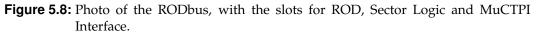

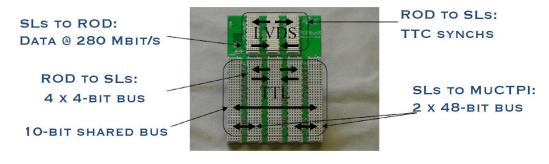

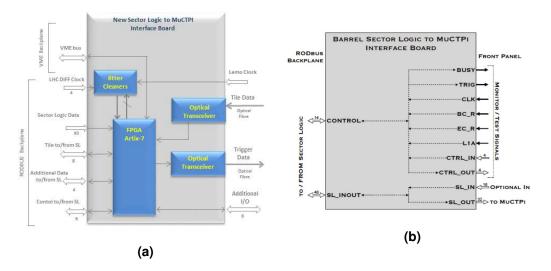

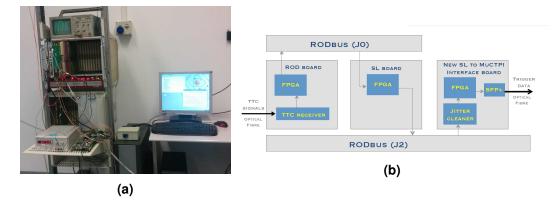

- 5.1.3 The MUCTPI Interface Board 77

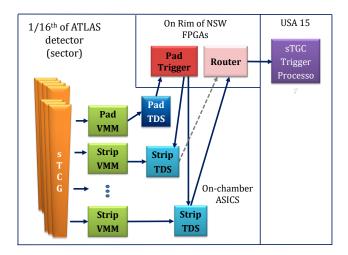

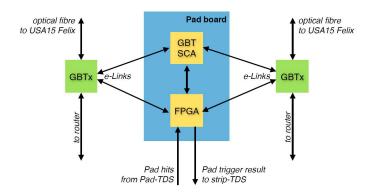

- 5.2 Serial Interface for the Pad Trigger Board 84

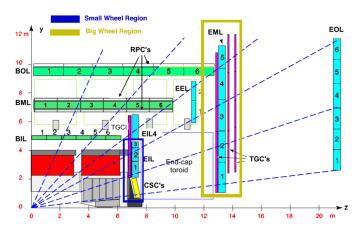

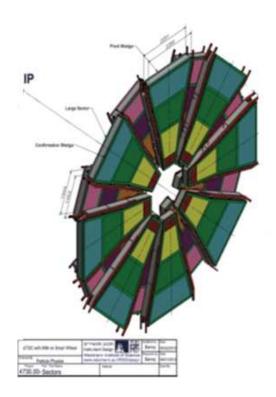

- 5.2.1 New Small Wheel Project 84

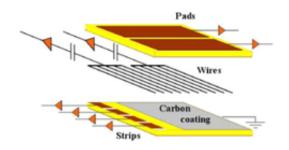

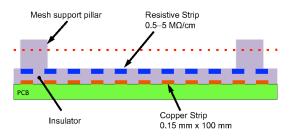

- 5.2.2 sTGC 87

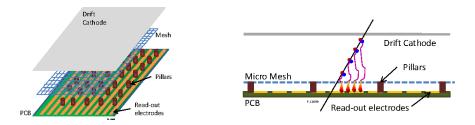

- 5.2.3 Micromegas 87

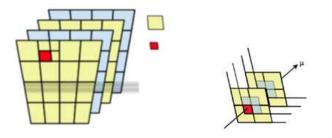

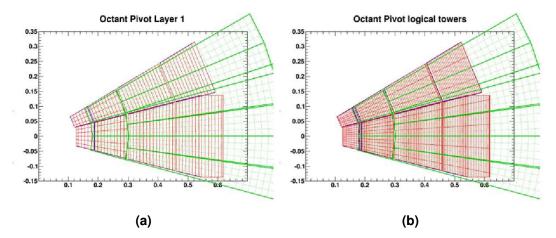

- 5.2.4 sTGC trigger system 89

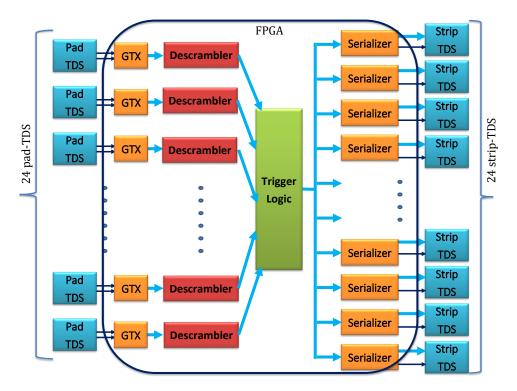

- 5.2.5 Pad Trigger Logic board 91

- 6 CONCLUSIONS 103

Bibliography 105

#### INTRODUCTION

During this PhD work, I focused on the study of the state-of-art High-Speed serial links in reprogrammable electronics devices, specifically in Field Programmable Gate Arrays (FPGA). During this work, I describe and discuss the main properties of a serial link and the most important features of its architecture, when implemented in FPGA.

Data transmission technology over serial links, on copper cables or optical fibre, makes possible to transfer the data acquired by an experimental apparatus of large dimensions over a relatively small number of acquisition channels. In this way it is possible to achieve a high density in connections between the experimental apparatus and the acquisition environment, along with an almost total absence of noise, when using fibres.

In this PhD work, I developed three different high-speed serial links oriented to be used in High Energy Physics (HEP) experiments. High Energy Physics experiments generate high volumes of data which need to be transferred over long distance.

Due to their extreme high bandwidth, serial links have been extensively used in Trigger and Data Acquisition (TDAQ) systems of HEP experiments. For example, many experiments at Large Hadron Collider (LHC) at CERN, intensively employed serial links, both for transmission of Timing, Trigger and Control signals (TTC) [1] and for trigger and data readout [2, 3]. Their use in the framework of trigger systems is particularly interesting from the research point of view since, in these architectures, serial links have to guarantee a fixed latency. Originally, they were designed and deployed by using custom Application Specific Integrated Circuits (ASICs). However, recent studies [4, 5] show that last generation Field Programmable Gate Array devices (FPGAs) allow to implement the same links in cost-effective designs. In addition, being built around an FPGA device they represent a powerful solution in the replacement of out-of-the-art (but still used) links, whose commercial components has become obsolescent [aloisio2010emulating:proc, 6].

In this thesis will be presented the serial links I developed:

- a high-speed self-adapting serial link, which can be easily used in different application fields;

- the serial in/output interface of two electronic boards in the read out system of the muon spectrometer of ATLAS Experiment.

The frequency agile, auto-adaptive serial link, deployed in this work, is capable to analyse the incoming data stream, by scanning the Unit Interval, and to find the highest transmission line rate, according to a given failure rate. It uses a new feature (*RX eye margin analysis*) of the Receiver (*RX*) side of the Xilinx 7

#### INTRODUCTION

series FPGAs high-speed transceivers (GTX), in order to measure and graphically display the quality of the link. The original contribution of this work consists in the build-up, design and optimization of a full architecture, which drives the GTX in order to modify the line rate of the link, runs consecutive eye scans for various line rate and analyses the results of the different scans, in order to find the maximum line rate sustainable by the link. The application can be deployed as a monitoring tool in HEP experiments, in order to remotely monitor a transmission system or detect issues in the serial link physical layer. Besides, it can be easily adapted in different frameworks, as it can be used on top of any user's existing link, as it has no specific requirement about link specification or protocol.

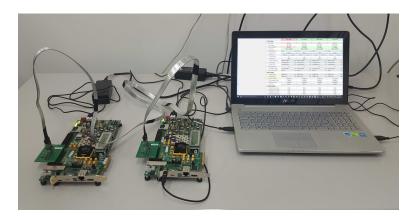

The other two serial interface developed in this PhD project are in the framework of the so called Phase-I upgrades of ATLAS experiment.

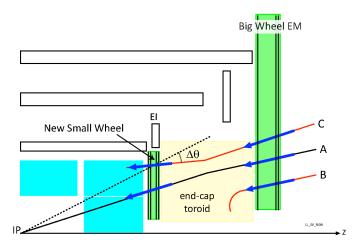

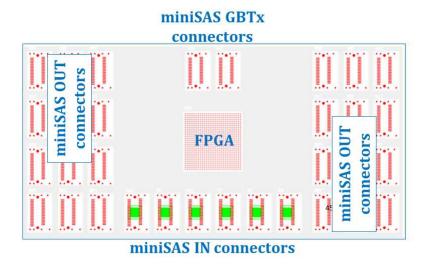

The main focus of Phase-I upgrade is on the Level-1 muon trigger, where upgrades are planned to be completed by 2019. In particular, for the end-cap region of the muon spectrometer, the installation of a new set of precision tracking and trigger detectors was approved (New Small Wheels). It will be instrumented with micro-mesh gaseous structure detectors (MM) and small-strip Thin Gap Chambers (sTGC). With their introduction, new electronics need to be developed, in particular new trigger electronics for both the MM and sTGC. I was involved in the development of serial interface of the Xilinx Kintex-7 FPGA-based sTGC trigger board that uses information from the coarse sTGC readout pads. Hence, in this thesis will be outlined my contribution to the design of the first prototype of the board and to the development of the serial interfaces with either the ondetector electronics board (for which fixed-latency constraints are required) and the monitoring and controlling chips.

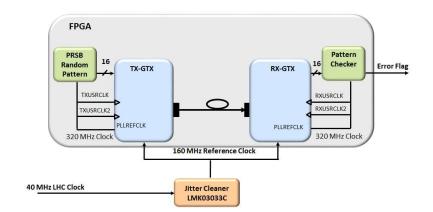

Another Phase-I Level-1 trigger upgrade consists of a new Muon to Central Trigger Processor Interface (MUCTPI). The MUCTPI receives muon candidate information from each of the muon detectors, selects muon candidates and sends them to the Central Trigger Processor (CTP). In the first runs of ATLAS, the L1 Barrel trigger candidate data were transferred to the MuCTPI via copper cables. In order to cope with the trigger upgrade, serial optical links are necessary. The optical links will provide a much higher bandwidth (up to 6.4 Gbps) which will be used to transfer additional information from the off-detector trigger modules. I developed the new Interface board between the new MUCTPI and the Resistive Plate Chambers (RPC) muon trigger, using the Xilinx Artix-7 FPGA GTP transceivers. Then it will be illustrated the work done in designing the PCB board, for which particular attention was paid to the FPGA power supply and the clocking tree distribution (in order to allow the GTP FPGA internal transceiver to work correctly). Beside the fixed-latency link, developed for studying the feasibility of the new serial link will be described.

The fist chapter of this work provides an introduction to serial and parallel link architectures and to the working principles of the serializer-deserializer devices. Various examples of serial links used in HEP Experiments are presented. In the second chapter, the FPGAs internal architecture is described as a background for the description of the implementation of the high-speed auto-adaptive serial link. Its internal architecture and the tests carried out are provided.

In the third chapter, after a brief introduction on the SM, the LHC complex and the ATLAS detector are described.

The four chapter covers the work done in the ATLAS Upgrades framework. In order to contextualize the project, an overview on the improvements foreseen for the Muon spectrometer is given. Hence, after an introduction to the Level-1 Muon Barrel Trigger system, the MUCTPI Interface board is introduced, and internal architecture of the new Interface board is illustrated. In the second part of the chapter, the purposes of NSW project are outlined. Finally, the pad trigger board, the interface logic implemented for it on FPGAs and the tests done are presented.

# 2

#### SERIAL LINK

High-speed serial links are nowadays widely used in many applications. For example, computer networks for office communications, serial buses, building and manufacturing automation, Internet and also ISDN. However, historically, for high-speed communication, the most used system was the parallel one.

Starting from the 90's, the decreasing cost of integrated circuits, combined with greater consumer demand for higher speed and longer distance, has led to the replacement of parallel links by serial ones: in hard disks, the Integrated Drive Electronics (IDE) [7] commonly known as AT Attachment with Packet Interface (ATA/ATAPI) [8] has been completely overcome with Serial AT Attachment (SATA) [9]; analogously IEEE-1284 [10] bi-directional parallel communications have been replaced by Universal Serial Bus (USB) [11] standard.

The driven factors which led to this change are strictly related to the features of this two kind of data transmission.

This chapter provides an introduction to serial and parallel link architecture and the State-of-the-Art of serial links of fundamental importance in order to have an outline of the thesis, which is mostly devoted to the development of a frequency agile, auto-adaptive serial link and high-speed, fixed-latency serial links for High Energy Physics (HEP) applications.

#### 2.1 SERIAL VERSUS PARALLEL TRANSMISSION

Digital data transmission can occur in two basic modes: serial or parallel. The type of transmission mode used generally depends upon distance and required data rate.

Figure 2.1: Data Transmission Methode.

In a serial transmission, data is sequentially transferred, one bit at a time, over a single transmission line. This means a simplified transmissive channel in spite of a more complex transmitter ad receiver devices required for synchronization and the flow control.

In parallel transmission, multiple bits (usually a byte or an its multiple) are simultaneously sent on different channels and synchronized to a clock.

In a parallel transmission, data can therefore be transferred in words of one or more bytes at a time. As a result, at a first glance, parallel bit rate results higher than the serial bit rate. However, this is not always true and, a further and deeper look into the features of serial transmission easily shows why. Indeed, in spite of this misconception, in many application, especially when data needs to be transferred over long distances, serial communication is preferred to parallel one. The reasons can be found in the following advantages:

- 1. In parallel links, since all bits of a data are transferred at the same instant, separate wires are used to carry each bit. Hence, the physical layer in the parallel links use many wires. On the other hand, serial links use a limited amount of wires. In the worse case, in order to guarantee a better transmission, a differential protocol is preferred, and only in this case a serial transmission uses two wires; otherwise a single wire is enough.

- 2. In parallel links the length of the connection can be an issue. When signal are carried over long distance, using cables, electromagnetic interference creates problems at higher data rates. Each wire acts as an antenna and capture a lot of noise from the environment: it corrupts data to be transferred. Since serial communication only use a limited number of wires, it can use long wires with less interferences. Since the space between two line can be greater than in a parallel link, the signal can be protected from electromagnetic interference by shielding the wires.

- 3. Besides, other factors limited the transmission rate in a parallel communications, that causes it to be sometimes slower than the serial one. As anticipated, a superficial comparison between a parallel and a serial link shows that, if both them operate at the same frequency, data transfer of a n-bit parallel link is n times higher than the serial link. The higher value of *throughput* <sup>1</sup> seems clearly in favour of a parallel transmission. However, in practical designs, the *clock skew* <sup>2</sup> among the parallel wires reduces the speed of data transmission to the slowest of all of the parallel transmission wires. Finally, the clock skew limits the speed of data transmission in a parallel link in respect to a single serial link.

Then, although a serial link may seem inferior to a parallel one, since it can transmit less data per clock cycle, it is often the case that serial links can be clocked considerably faster than parallel links so they can achieve a higher data rate. Summarizing, the following factors allow serial link to be clocked at a higher rate:

- 1. clock skew between different channels is not an issue;

- 2. crosstalk is not a much significant issue, because there are fewer conductors in proximity and a better isolation of the single channels is allowed;

<sup>&</sup>lt;sup>1</sup> The *throughput* is one of the characteristic features of a transmission system. It is a measure of the effective used transmission capacity. The throughput must not be confused with channel capacity of the link. The latter is the maximum rate at which information can be reliably transmitted over a communications channel for any given degree of noise contamination (as defined by Shannon's theorem) while the throughput is the useful rate of the transferred data. Both the quantities are measured in bits per second (bits or bps)

<sup>2</sup> Clock skew is defined as the variation in the clock commutation edges in function of different position of the components in the same integrate circuit (IC). An IC displays skew when clock length paths are not perfectly balanced. By definition, the skew value is the same for every clock cycle, for this reason it doesn't affect the value of the clock period, but it only determines a constant shift. In a synchronous digital system clock skew between two point i and j is defined as t<sub>skew</sub>(i;j) = t<sub>i</sub> - t<sub>j</sub>; where t<sub>i</sub> and t<sub>j</sub> are the time distances between the real clock front end edge on the i and j component, respect to the ideal reference clock edge

- 3. in many cases, serial is a better option because it is cheaper to implement;

- 4. many ICs can have fewer pins and become less expensive.

The outcome of this conditions has made serial communication more and more often preferred over a parallel one and consequently more and more serial I/O methods and standards have been developed.

One of the fundamental characteristic of a transmission system are:

- 1. the data flow direction: if data flow in one direction, from the transmitter to the receiver (simplex) or in both simultaneously (full-duplex);

- 2. maximum data rate: it determines the capacity of a link, measuring the speed at which the data can be transmitted. The data rate is characterized by the number of bits transmitted per time unit and is measured in bits per second (bps).

- 3. the latency i.e. the amount of tame it take a bit to be transmitted from source to destination;

- 4. the number of extra data transmitted, in addition to the real data information, such as flow control signals, error signals and so on.

#### 2.2 BINARY CODING OF DATA

Binary coding of data defines how the two binary values ('o' and '1') are distinguished. Indeed, in the transmission medium these value are assigned, according to the data format, to an *High* signal or to a *Low* signal. If the zero is represented by the *Low* signal while the one by the *High* signal, the logic is called positive on the contrary the logic is negative. Besides, more than one option exists on how the *High* and *Low* signals are define, according to different values and definition of the following variables:

- 1. amplitude values;

- 2. edges (level changes);

- 3. phase relationship;

- 4. frequencies

Among the most common data format there are: Non-Retun-to-Zero format (NRZ) and Return-to-Zero format (RZ), Manchester coding, 8B/10B encoding and scrambling/descrambling.

Depending on the particular application, a data format is preferred over the others. For example, in certain kind of transmission (synchronous data transmission) there is the necessity of transmitting clock from the sender to the receiver. This information can be transferred using an extra line or can be included in the data. When the latter is the case, only a coding which permit the receiver to recover the clock rate from data flow, by ensuring a minimum number of transitions, can be used.

Another characteristic to take into account is the value of the DC component of the signal. In some application, indeed, DC component is forced to be zero. In order to reach a DC balancing, different types of coding can be used:

- 8B/10B encoding;

- scrambling/descrambling.

It could be more appropriate to refer to them as conversions, since they transform a data sequence of bits (also NRZ and RZ coding) into another one, according to fixed rules. The new sequence guarantees a DC-free serial signal and a minimum number of transitions which helps the clock recovery from data.

#### 2.2.1 8B/10B Encoding

The 8B/10B Encoding [12] was developed by IBM and it converts each 8 bits of a sequence into 10 bits.

In order to achieve a DC-free signal, every 10-bit sequence should have the same number of ones and zeros, i.e. zero (or neutral) disparity. However, according to the 8B/10B Encoding process, some 8 it words can be converted in two possible sequence of 10 bits: one with two more 1 bits (disparity = +2), and one with two more zeros (disparity = -2). In order to identify them the concept of positive and negative Running Disparity (RD) has been introduced. Then, depending on the running disparity of the current word, since the total number of ones and zeros is monitored, the next 10-bit character is chosen based on what is needed to bring the DC balance back in line.

In the conversion 8B/10B, 12 special characters are allowed. They are called control word or K-characters and are used for control function or for synchronization). For example, the 7-bit pattern '1100000' provides such a sequence that can only be found in three of the control characters. One of these three control characters can be chosen as a boundary for data, or comma as it is commonly called. Commas preceding data enable the receiver to correctly synchronize to the sequence of data words.

The inconvenience of this kind of coding is the introduction of an overhead of 25% not always compatible with the application since it reduces data rate .

Just for example, Fig. 2.2 shows a simplified version the 8B10B Encoding, 3B4B Encoding, which convert a 3-bit word in a 4-bit word.

#### 2.2.2 Conditional Inversion Master Transition protocol: CIMT

The Conditional Inversion Master Transition (CIMT) protocol was introduced together with the G-Link chipset (see 2.8) in the Hewlett-Packard Journal in 1992 [13]. The coding scheme is designed to transmit a stream which is made of either 20 or 24 bit-wide data words. Each word contains 16 or 20 data bits

| 3B Input Data | 4B Output Data |  |

|---------------|----------------|--|

| 000           | 0011           |  |

| 001           | 0101           |  |

| 010           | 0110           |  |

| 011           | 1001           |  |

| 100           | 1010           |  |

| 101           | 1100           |  |

| 3B Input Data | 4B Output Data |           |  |

|---------------|----------------|-----------|--|

|               | Even Words     | Odd Words |  |

| 110           | 0100           | 1011      |  |

| 111           | 0010           | 1101      |  |

| SyncA         | 0111           | 1110      |  |

| SyncB         | 1000           | 0001      |  |

Figure 2.2: Simple 3B/4B code example.

(D-Field) and 4 control bits (C-Field). The efficiency can be as high as 21/24 or 87.5% [14].

The DC balance of the frame is guaranteed by the transmitter which conditionally inverts words in such a way to minimize the bit disparity. On the receiver side, in order to restore the original information, an inversion is performed again, if necessary: the decision being made by reading the C-Field content.

The protocol guarantees a transition in a fixed position of the C-Field and the receiver checks for this transition in received data in order to to restore frequency and phase of the low frequency clock. Bit clock is reconstructed by dividing the frame clock by 20 or 24. This allows synchronization and word alignment avoiding the need for periodical interruption of the service in order to send synchronization characters. The four control bits have the additional function of flagging each word as a data word, a control word or an idle word. Idle words are used, at link start-up, in order to synchronize the link and to perform an initial handshake mechanism (which is able to notify the transmitter the receiver is locked on the stream). During the normal operation, instead, they help to keep the link phase-locked.

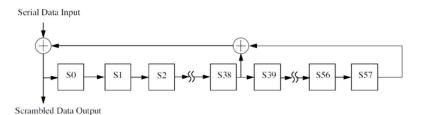

#### 2.2.3 Scrambling

Another, coding technique is the bit scrambling which uses Linear Feedback Shift Register, LFSR<sup>3</sup> [15], to produce pseudo-random bit sequences. The benefit in using a scrambler is the possibility of rearrange the bits (the original sequence) in order to improve the quality of data communication. The LFSR is opportunely chosen sash as:

<sup>3</sup> A Linear Feedback Shift Register is a sequential shift register whose input bit is a linear combinational function of its previous state. Commonly, the function is the exclusive-or (XOR) of single bits. The bit positions that affect the next state are called the taps. The choice of taps determines how many values there are in a given sequence before it repeats. Besides, once the initial value of the LFSR is chosen the stream is uniquely determined. However, an LFSR with a well-chosen feedback function can produce a sequence of bits which appears random and which has a very long cycle. The behaviour of the LFSR is well described by the finite fields theory also called Galois algebra.

- 1. a too long sequence of the same characters (zeros or ones), which complicates clock recovery on the receiver side, is overcome;

- 2. DC-balanced of the signal is improved.

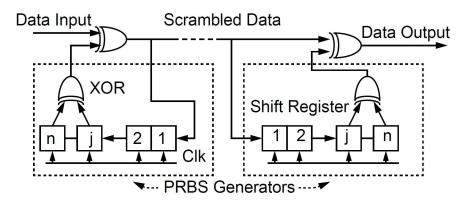

Then, since transmitted data are converted at the transmitter side, in order to recover the information, at the receiver side, a descrambler has to be used. In Fig. 2.3 show the working scheme of a scrambler followed by a descrambler.

**Figure 2.3:** Scrambling. A feedback shift register is used to randomize data and in order to restore original data another register, which reverses the process, is used at receiver.

#### 2.3 TRANSMISSION MEDIA

For serial data transmission, different transmission supports can be used, depending on the application. The signals can be transmitted either electrically, as light pulses or via radio waves. The choice of the medium is influenced by several factors:

- 1. costs and installation effort;

- 2. transmission safety: interference susceptibility, error probability, etc.;

- 3. maximum data rate;

- 4. distances among the devices to be connected.

#### 2.3.1 Electric lines

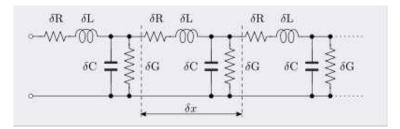

Electric lines are simple and cost-effective, however, attenuation of signals and interference susceptibility (dependent on which kind of cable is used and on the interface specification) can be great disadvantages. The action of an electrical line on the transmitted signal is generally described by the equivalent circuit in Fig. 2.4. In this model an infinite series of sub-networks (made of resistors, capacitors, and inductors all expressed in their unit per unit length) come one after the other. The

#### SERIAL LINK

resistors take into account the distributed resistance which cause the drops of the static signal level. The capacitors and inductors represent the distributed inductance and the capacitance C between the two conductors, respectively. Together with the resistor they create the filters which take into account the effects on the signal edge transitions.

Figure 2.4: Equivalent circuit diagram of a transmission cable.

Examples of electrical cables are:

- 1. Conductor in a printed circuit board (PCB), Microstrip: a transmission line on a PCB is a thin flat conductor which is parallel to a ground plane, obtaining with a strip of copper on one side of a printed circuit board (PCB) or ceramic substrate while the other side is a continuous ground plane. The width of the strip, the thickness of the insulating layer (PCB or ceramic) and the dielectric constant of the insulating layer determine the characteristic impedance;

- 2. Coaxial cable: Coaxial cable is an unbalanced line where an inner conductor is surrounded by an insulating layer plus a braided conducting shield. However, on short distances, line rate can reach values of many Gbps.

- 3. Twisted pair: twisted pairs, like Ethernet LAN cable, are commonly used for telephonic communications. In such cables, many pairs are grouped together. The format is also used for data network distribution inside buildings, but the cable is more expensive because the transmission line parameters are tightly controlled. Their purposes is that of cancelling out electromagnetic interference (EMI) from external sources; for instance, electromagnetic radiation from unshielded twisted pair (UTP) cables, and crosstalk between close pairs. It was invented by Alexander Graham Bell;

#### 2.3.2 Fiber optics

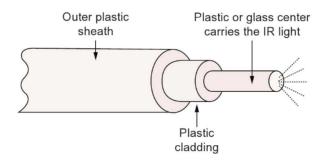

An optical fiber consists of a transparent core (usually made by drawing glass, silica) surrounded by another glass cladding with a lower index of refraction and an external plastic cladding (Fig. 2.5). The different value of refraction indexes is such that the light is confined to the core by total reflection. The reflections are almost free of any loss and thereby the light is conveyed within the core fiber only. The total diameter of a typical optical fiber is 0.1 mm, however the internal

Figure 2.5: Structure of a an optical fiber cable.

core can vary between 5  $\mu$ m and 60  $\mu$ m. Since transmitted signal consists of on-off light pulses, on the optical transmission link ends (boundaries), devices converting electrical signals (serial binary data) are foreseen. Usually, optical carrier are generated by a LED on the transmitter side and converted back to electrical signal by photosensitive semiconductor on the receiver side. Due to optical loss dependency on the wavelength value, typical value of light wavelength are in the near infrared (IR), where the attenuation is at its minimum.

Fiber optic cables are widely used for transmission at extremely high data rates and over very long distances, since signals are resistant to electromagnetic interferences and only slightly attenuated.

#### 2.4 CLOCK AND DATA RECOVERY

Independently from the used technique both transmitter and the receiver requires a synchronization clock signal.

In an asynchronous transmission, two separate clock source (one on the transmitter side and the other receiver side) running at the same frequencies are usually allowed. Indeed, when data flow is synchronized by start/stop bit flags, small frequency differences are not a big issue.

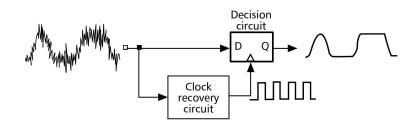

For a synchronous transmission, for which this situation has to be avoided, two methods exists in order to compensate a little clock frequency difference. If the use of a separate line, in addition to data line, is feasible, the transmitter can provide clock signal to the receiver. Otherwise, as anticipated, there is the possibility for the receiver of extracting the clock from data: the recovered clock. In this case, the technique used by receiver in order to generate the clock from data stream is called clock and data recovery (CDR). CDR algorithm needs a reference clock, whose frequency is approximately the same frequency of the transmitter clock. Hence, for clock recovery, the receiver phase aligns the reference clock to the transitions on the incoming data stream. Then, for data recovery, data on serial lines is sampled with the recovered clock.

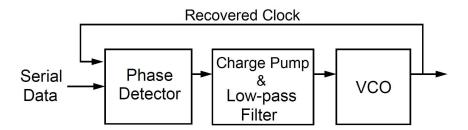

The basic working scheme of a CDR is shown in Fig. 2.6: it includes a clock recovery and data retiming blocks.

Figure 2.6: The role of a CDR circuit in retiming data.

The function of the clock recovery circuit is to detect the transitions in the received data and generate a periodic recovered clock. This recovered clock must satisfy the following conditions:

- its frequency must be equal to the input data rate;

- it should have reasonable timing with respect to the input data: the rising edge of the recovered clock should sample at the centre of the data bit, to provide maximum margin for jitter<sup>4</sup> and other time uncertainties;

- it should exhibit a minimum jitter because the jitter of the clock contributes to the retimed data jitter.

The data retiming circuit uses a Delay Flip Flop (DFF), which is triggered by the recovered clock to retime the received data. A Phase-Locked Loop (PLL) is

Figure 2.7: An example of CDR implementation.

usually used at the receiver to recover the clock from the data. A PLL is a negative feedback system where a clock generated by the Voltage Controlled Oscillator (VCO) is phase and frequency locked to an input data. The basic building blocks of PLL is shown in Fig. 2.7.

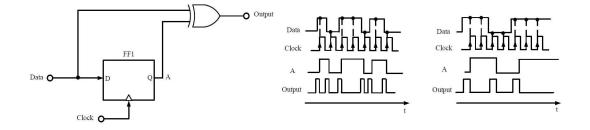

The function of the phase detector is to measure the phase difference between two incoming signals. One DFF with an XOR gate is a simple example of linear phase detector (PD), for which the output is linearly proportional to the phase

<sup>4</sup> Jitter is defined as the amount of variation in the waveform from their ideal position at zero crossing on the time axis. It will be better analyze in the section 2.7.3

Figure 2.8: Basic linear phase detector (left) and output waveforms (rigth).

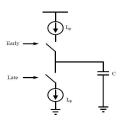

Figure 2.9: Charge pump in PLL.

difference, Fig. 2.8. A combination of two FF is able to determine whether the clock is earlier or later than the input data.

The function of the Charge Pump (CP) is to convert the output voltage of the phase detector to current. This current is then fed to a Low Pass Filter (LPF), where a capacitor is either charged or discharged depending on the phase detector output. The circuit diagram of the charge pump with a capacitor is shown in Fig. 2.9.

When the early node is high, closing the early switch, the capacitor starts charging and continues to charge until the early node goes low, opening the early switch. Similarly, when the late node goes high, the capacitor starts to discharge and will continue to discharge until the late node goes low. Designing a charge pump is not an easy task, because to achieve zero net voltage on the capacitor, the charging current should be equal to the discharging current. Even if the charging and discharging currents are designed to be close to equal, there will still be leakage current through the charge pump circuit, resulting in an offset voltage on the capacitor. One way to minimize this offset voltage is to calibrate the charge pump circuit by using a feedback loop circuitry. The function of the low pass filter (LPF) is to convert the charge pump current into control voltage. The function of the VCO is to generate the clock signal at its output, the frequency of which can be changed by varying the input control voltage. A signal, produced by the Phase detector when no frequency or phase difference occurs, force the LPF to fix its output DC value and consequently the frequency of the VCO signal. In order for this circuit to work well, transitions on the serial data must be enough frequent to guarantee the PLL to remain locked. For this purpose, often, a suitable cod-

#### SERIAL LINK

ing method, which guarantees a minimum number of transitions of the signal, is chosen.

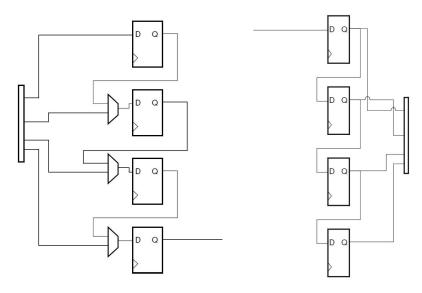

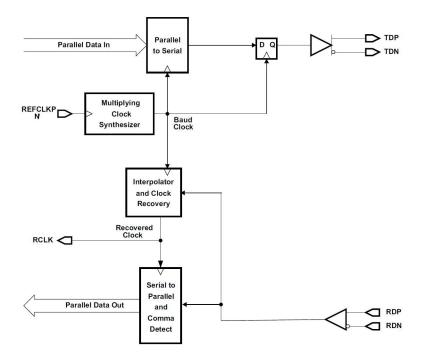

#### 2.5 SERIAL TO PARALLEL AND PARALLEL TO SERIAL CONVERSION: SERDES

The increasing requests for reliable high speed transmission over long distances has often made serial link preferred over parallel ones. However, since data elaboration is often parallel, data needs to be serialized on the transmitter side and deserialized on the receiver side. Circuit specialized for doing this conversion has been designed and are constantly developing; they are called SerDes. The

Figure 2.10: Working principles of a PLL in a CDR circuit.

basic working principle of a SerDes is relatively simple (Fig. 2.10). A parallel data is clocked into the parallel register synchronously to a slow clock and shift out, one bit at a time, at a higher serial clock rate. This block is called PISO (Parallel Input to Serial Output). The reverse operation is carried out by the SIPO (Serial Input to Parallel Output) block. It is simply composed by two registers. A shift register which receives data one bit after the other and transmits its contents to a storage register used to hold the data for the slower, parallel clock. The shift register needs to be clocked on the high serial clock (in such application the recovered clock form CDR circuit). Clearly, this scheme can work well only if the transmitter and receiver clocks are perfectly synchronized.

#### 2.6 EQUALIZATION

Since the transmission medium generally acts like a low pass filter, the signal at the receiver side of a link can be significantly distorted. Equalization is the process used to compensate signal degradations at the transmitter and/or at the

receiver. It works in such a way as to distort the signal with the only aim of ensuring a proper decoding.

#### 2.7 LINK PERFORMANCE: BIT ERROR RATIO TEST AND JITTER TOLERANCE

In order to evaluate the data integrity at the end of the link, the most important measure is called the Bit Error Ratio, or BER.

#### 2.7.1 BER

The BER can be defined as the estimate of error probability, e.g. the probability that any bit transmitted through the system will be erroneously received. In practical tests, the BER is measured by transmitting a finite number of bits through the system and counting the number of errors received. The ratio between the number of bits received in error and the total number of bits transmitted is the BER.

$$BER = \frac{Errors}{\text{Total Number of Bits}}.$$

(2.1)

The quality of the BER estimation increases as the total number of transmitted bits increases untill, in the limit of infinity transmitted bits, the BER becomes a perfect estimate of the *true* error probability P(E). However, in practical tests, finite testing times are required and then a less than perfect BER estimation must be accepted. Since the BER is a statistical average, it is possible to introduce the BER confidence level (CL) in order to quantify the quality of the estimate. CL is defined as the probability, based on E detected errors out of N transmitted bits, that the *true* BER (BER) would be less than a specified ratio, BER<sub>Limit</sub>:

$$CL = P(BER < BER_{limit}), \text{ given E and N.}$$

(2.2)

In this discussion, the *true* BER is the BER that would be measured if the number of transmitted bits was infinite. The formula tells, once the BER<sub>limit</sub> and CL are fixed, if after N transmitted bits, E errors are found, there is a CL percent confidence that the true BER is less than BER<sub>limit</sub>. Statistical methods, involving the binomial distribution function and Poisson theorem, help to calculate how many bits need to be transmitted in order to have the desired CL:

$$N = \frac{1}{BER_{limit}} \left( -\ln(1 - CL) + \ln\left(\sum_{k=1}^{E} \frac{(N * BER_{limit})^k}{k!}\right) \right), \quad (2.3)$$

In the equation ln() is the natural logarithm, while the other variables represent the quantities previously introduced. The details of the calculations and derivations are known in literature [16] and are beyond the scope of this work.

To better understand how the equation (2.3) [23] can be used, an example can be explicative in which it must be determined how many bits must be transmitted in order to have a 95% CL that the *true* BER is less than  $10^{-10}$ , if no error has been

| N * BER |          |          |          |  |  |

|---------|----------|----------|----------|--|--|

| Errors  | CL = 90% | CL = 95% | CL = 99% |  |  |

| 0       | 2.30     | 3.00     | 4.61     |  |  |

| 1       | 3.89     | 4.74     | 6.64     |  |  |

| 2       | 5.32     | 6.30     | 8.40     |  |  |

Table 2.1: N \* BER for confidence levels of 90%, 95%, and 99%.

detected. In this simple example,  $BER_{limit} = 10^{-10}$ , CL = 0.95 and E = 0, so the second term of the equation is null. The result is

$$N = \frac{1}{10^{-10}} \left( -\ln(1 - 0.95) \right) \approx 3/10^{-10} = 3 * 10^{10}$$

(2.4)

or defining the normalized number of bits as NxBER<sub>limit</sub>

N \* BER<sub>limit</sub> =

$$(-\ln(1 - 0.95)) \approx 3$$

(2.5)

Table 2.1 shows the normalized number of bits that must be transmitted, N x BER, in order to get a BER estimate with different values of CL (90%, 95% and 99%) and for 0, 1 or 2 transmission errors. By dividing the values in the table by the desired BER, it is possible to obtain the number of bits to be transmitted for a specific confidence level and bit error.

#### 2.7.2 Equipment and Procedures

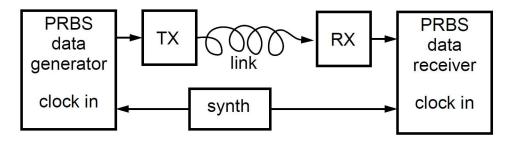

The conventional method for BER testing utilizes a pattern generator and an error detector (2.11). The pattern generator transmits the test pattern into the system, while the error detector counts the number of bit received with errors. For checking the correctness of the data it usually replicates the test pattern of the generator and performs a bitwise comparison between this data and the data received from the link. In order to accurately compare the bits received from the pattern generator with the bits received from the system under test, the error detector must be synchronized to both bit streams and it must compensate for the time delay through the system under test. Test results depend on the particular

Figure 2.11: Typical BER Test set-up.

test pattern (bit sequences) sent into a system, different rate of bit errors may

occur. Usually, a particular stressful test pattern is chosen, which is intended to emulate random data like Pseudo-Random Bit Sequences (PRBSs), which are based on Galois' Algebra. In some cases, however, a replica of the kind of data that is expected to occur during normal operation is more useful.

#### 2.7.3 Jitter

Together with BER, jitter is an increasingly important quantity in the development and specification of serial data links. Indeed, as clock speeds and communication channels run at ever higher frequencies, the analog nature of digital signals (binary data is no more then a digital waveform) reveals itself and jitter becomes critical in designing digital synchronous systems.

Jitter can be defined in different ways [17]: from an analog point of view, jitter can be seen as phase noise [18] while in a digital communications channel, it is the time deviation from ideal timing of a signal transition through a decision threshold or more simply, how early or late a signal transitions with reference to when it should transition. As a consequence, there are different domains of analysis: the time domain (jitter amplitude versus time), the modulation domain (phase versus time), and the frequency domain (amplitude of jitter components versus their frequency, or analysis of phase modulation sidebands). Jitter measurements can be quantified in the same fashion as all time varying signals using either RMS or peak-to-peak displacement in the time domain. Alternatively it can be also quantify, in the frequency domain, in terms of power spectral density over a given bandwidth.

Jitter impacts the maximum frequency of a synchronous system (reducing the timing budget for basic operations), as well as the quality of a transmission (data errors can result from sufficiently large time deviations from ideal). Any part of a system which generates, transmits or receives signals, can be source of jitter [19, 20]. As a result, in order to determine the total performances of a system it is of primary importance to evaluate how much jitter every elements of the system introduces. In this scheme it has become fundamental to characterize, model, simulate and estimate all the jitter sources.

Digital definition of jitter allows many ways of representing measuring it [21–23] because of the ambiguity in the choice of the reference, ideal transition: it can be the transition through a decision threshold of a reference or reconstructed clock, but arithmetic quantity can be used too, like the nominal bit period ad a given frequency. The following are the major types of jitter:

- Long Term Jitter: it measures the change in a clock's output from the ideal position, over several consecutive cycles. It represents the cumulative effect of jitter on continuous clock cycles over a long time interval.

- 2. Absolute jitter: it is Root Means Squared (RMS) evaluation of many edge measurements from an expected location or absolute time reference;

- 3. Period Jitter: it is the deviation of a clock signal with respect to the ideal period over a number of randomly selected cycles;

- 4. Cycle to Cycle Period Jitter: it measure the variation of a signal between consecutive cycles, over a random sample of adjacent cycle pairs. Its peak value defines the maximum difference between two rising edge of any two consecutive clocks and it can be expressed in ps as well as in RMS;

- 5. Time Interval Error (TIE): it is the time deviation of an edge of the signal from a reference point position which is obtained using the actual transmitter clock or a reconstruction of it from the data sampled. In effect, TIE is the discrete time domain representation of phase noise expressed in seconds;

- 6. Phase Noise Jitter: it is described as either a set of noise values at different frequency ranges, or as a continuous noise plot over a unique range of frequencies. Usually, in a square wave, most of the energies are located at the frequency carrier ( $f_c$ ). However, some signal energies are significant also over a range of frequencies on both sides of the carrier (since the signal is assumed to be symmetric). Phase jitter is the integration of phase noises over a certain spectrum and expressed in seconds or RMS.

#### Types of Jitter

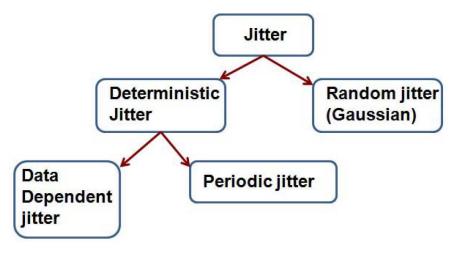

Conventionally two general categories of jitter are defined: deterministic jitter (DJ) and random jitter (RJ).

DJ is often bounded, periodic, non-Gaussian, and has a specific cause. It can be further classified into periodic jitter and data-dependent jitter, as Fig. 2.12 shows. Examples of deterministic jitter are:

- 1. Duty-Cycle Distortion (DCD): from asymmetric risefall times;

- 2. Intersymbol interference (ISI): from channel dispersion or filtering;

- 3. Sinusoidal: from power-supply switching;

- 4. Uncorrelated: from crosstalk by other signals.

RJ is Gaussian and it is often referred to as background or thermal noise, although it can easily be the most significant contribution to total jitter. Because random jitter is modelled as a Gaussian distribution, its unbounded: the probability of some values is very small, but not zero. In the light of the foregoing, the total jitter is the result of both random component and deterministic one, but it is not the simple sum of them. Indeed, while the RJ has a Gaussian distribution and its peak-to-peak value has no sense, for the DJ the opposite is true. Then, if in the phase domain, the total phase error function can be written as:

$$\phi_{j}(t) = \phi_{j}(t)^{\mathsf{R}} * \phi_{j}(t)^{\mathsf{D}}, \qquad (2.6)$$

Figure 2.12: Types of Jitter.

where  $\phi_j(t)^R$  is the random component and the  $\phi_j(t)^D$ , the deterministic one, for the evaluation of the performances of a system it is more useful to speak of jitter in terms of Probability Density Function, PDF (the function which gives the probability of a logic transition occurring at a given time, x). Then a measurement of the jitter PDF can be performed measuring, separately, each component of the jitter distribution, including RJ and all types of DJ. Indeed, assuming RJ e DJ are independent, the PDF of the total jitter, TJ(x) is the convolution of the single terms

$$TJ(x) = RJ(x) * DJ(x).$$

(2.7)

However, in this approach it is necessary to know the PDF of each components. For the random jitter it is relatively simple since the PDF is a Gaussian function defined by the formula:

$$PDF_{RJ}(x) = \frac{1}{\sqrt{2\pi\sigma}} \exp\left(-\frac{x^2}{2\sigma^2}\right)$$

(2.8)

Then, from a histogram with the appropriate value of samples, it is possible to estimate the values of  $\mu$  and  $\sigma$  and from this, the expected RJ value. It is worth to remember that in a Gaussian distribution the peak-to-peak value is infinite, since the distribution is no limited. However, once the number of samples or the BER is fixed, the jitter of a signal whose only aggression is of random kind, can be defined as [24]:

$$J_{RMS}^{R} = N_{BER} \sigma, \qquad (2.9)$$

with  $N_{BER}$  depending on the agreed upon BER [25].

For the deterministic component,  $J_{pp}^{D}$ , the situation is more complicate: a separation and identification of the single causes of jitter it is necessary, but not always possible. The study of how the single component influence the digital system is important, however it is not generally possible to separate a single attack from another one. On the other hand, it is usually possible and simpler to measure the total jitter in which all the contributions are superimposed. This is the reason

why, together with the decomposition model, which pretend to obtain an estimate of the total jitter starting from its single component, other models have been developed [26]. Among these, the Dual-Dirac Model [27] is the most universal accepted.

#### Dual-Dirac model

The dual-Dirac model is based on the following hypothesis:

- 1. The total jitter can be decomposed in RJ and DJ;

- 2. RJ is completely described in terms of the width of the Gaussian function 2.8,  $\sigma$ ;

- 3. DJ is limited;

- 4. DJ is the simple sum of two Dirac delta functions;

- 5. jitter is a stationary phenomenon.

According to this model, the dual-Dirac PDF for DJ is the simple sum of two Dirac delta functions, one centred at  $\mu_L$  and one at  $\mu_R$ ,

$$PDF_{dual-Direc}DJ(x) = \delta(x - \mu_L) + \delta(x - \mu_R).$$

(2.10)

If, like the model suppose, the distributions of different components of jitter that are independent, like RJ and DJ, it is possible to combine their PDF through convolution. Since, the PDF for RJ is well described by 2.8, for the total distribution is:

$$\begin{split} \mathsf{PDF}(\mathbf{x}) &= \mathsf{PDF}_{\mathsf{RJ}}(\mathbf{x}) * \mathsf{PDF}_{\mathsf{dual}-\mathsf{Direc}}\mathsf{DJ}(\mathbf{x}) \\ &= \int [\mathsf{DF}_{\mathsf{dual}-\mathsf{Direc}}\mathsf{DJ}(\mathbf{u}) * \mathsf{PDF}_{\mathsf{RJ}}(\mathbf{x}-\mathbf{u})] \, \mathsf{du} \\ &= \frac{1}{\sqrt{2\pi\sigma}} \int [\delta(\mathbf{u}-\mu_{\mathsf{L}}) + \delta(\mathbf{u}-\mu_{\mathsf{R}})] \exp -\frac{(\mathbf{x}-\mathbf{u})^2}{2\sigma^2} \, \mathsf{du} \\ &= \frac{1}{\sqrt{2\pi\sigma}} \Big[ \exp \left(-\frac{(\mathbf{x}-\mu_{\mathsf{L}})^2}{2\sigma^2}\right) + \exp \left(-\frac{(\mathbf{x}-\mu_{\mathsf{L}})^2}{2\sigma^2}\right) \Big]. \end{split}$$

Once we have the jitter PDF, BER(x) can be calculated as the probability that an error will occur if the sampling point is positioned at the time-delay position, x. Then, BER(x) is given by

$$BER(x) = \rho_T \int_x^{+\infty} PDF(u) \, du + \rho_T \int_{-\infty}^x PDF(u-T) \, du \qquad (2.12)$$

where  $\rho_T$  is the ratio of the number of transitions to the number of bits (logic transition density). Plugging the dual-Dirac model, Eq. 2.11 into Eq. 2.12, get:

$$TJ(BER) = 2 Q_{BER} J^{R}_{\delta-\delta} + J^{D}_{\delta-\delta}, \qquad (2.13)$$

| BER               | $Q_{\text{BER}}$ |

|-------------------|------------------|

| 10 <sup>-10</sup> | 6.35             |

| 10 <sup>-11</sup> | 6.70             |

| 10 <sup>-12</sup> | 7.05             |

| 10 <sup>-13</sup> | 7.35             |

| 10 <sup>-14</sup> | 7.65             |

Table 2.2: Minimum values of QBER for different BERs

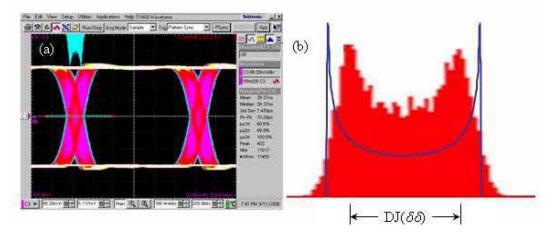

Figure 2.13: An eye diagram (left) and the corresponding TJ histogram (right).

where,  $Q_{BER}$  is a factor that relates the BER to the distance from the centre of the Gaussian, and  $J_{\delta\delta}^{D}$  is a model dependent parameter that is easy to define and can be measured in many different ways.  $Q_{BER}$  is listed in Table 2.2 for different BER values. In conclusion the dual-Dirac model provides an easy way to estimate TJ(BER) by measuring the RJ, which is given by  $\sigma$ , and DJ,  $J_{pp}^{D}$ , which is given by the separation of the two Dirac-delta functions,  $\mu_{R} - \mu_{L}$ :

$$TJ(BER) = 2 Q_{BER} \sigma + (\mu_R - \mu_L).$$

(2.14)

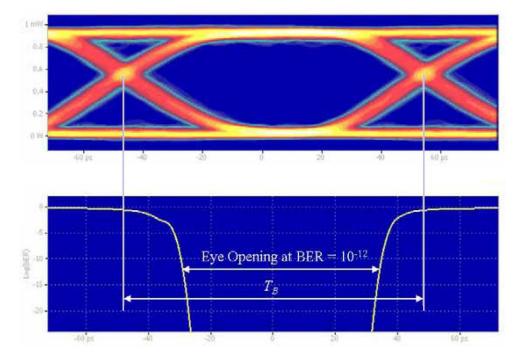

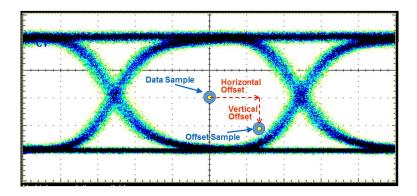

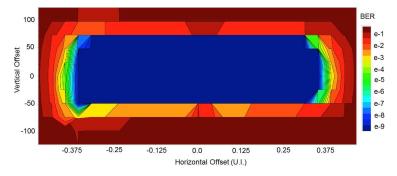

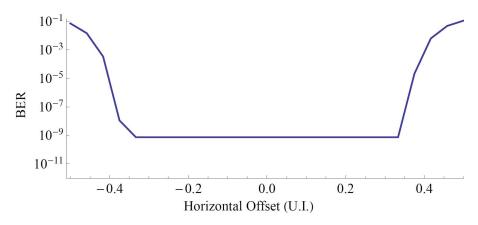

#### Measuring jitter

Measurements of jitter can be obtained using an oscilloscope capable of providing an Eye Diagram of the signal, which is a composite view of all the bit periods of a captured waveform superimposed upon each other and of making a histogram of the crossing point (Fig. 2.13). A bathtub plot (bottom of Fig. 2.14) can be used too, since it represents a measurement of the BER as a function of the time-delay position of the sampling point, BER(x). In this case, TJ(BER) is the amount of eye closure at a given BER, that is the nominal bit period,  $T_B$ , less the eye opening at that BER (the distance between the two sloping curves in Fig. 2.14) at the desired BER:

$$TJ(BER) = T_B - eye opening(BER).$$

(2.15)

**Figure 2.14:** An eye diagram (top) and the corresponding bathtub-plot: The bit error ratio as a function of the time-position of the sampling point with respect to the ideal logic transition time, BER(x).

From this discussion, it could be seem very simple to measure TJ(BER): it is only necessary to do a measure of BER(x), as in Fig. 2.13 and 2.14. Another technique will be describe in the chapter 3.2.3. However, in all the cases, measuring BER(x), with a fixed CL, which gets sufficient statistic to reference eyes closure to BER, can take a long time, as previously discussed.

#### 2.8 LEGACY HIGH-SPEED SERIAL LINKS IN HEP: G-LINK AND S-LINK

Current Field Programmable Gate Arrays devices, FPGAs<sup>5</sup>,offer integrated digital transceivers with very high data rates which has lead to the implementation of many high speed serial link, based on the FPGA technology. The application field are wide: portable devices, medical devices, wireless, wire line and military markets [28, 29] as well in scientific research (Applications of Field-Programmable Gate Arrays in Scientific Research [30], Compressed Baryonic Matter experiment [31], the Positron Emission Tomography system [32], and the future KM<sub>3</sub>NeT undersea network [33]). Data acquisition systems of HEP experiments have been often based on serial link. In this section, two serial link protocols will be described: G-Link and S-Link. Both of them show how an FPGAembedded MGTs based solution can be even more suitable than an implemen-

<sup>5</sup> A field-programmable gate array is an integrated circuit designed to be configured by a customer or a designer after manufacturing, hence *field-programmable*. It will be better described in the section **3.2**

Figure 2.15: G-Link chipset.

tation based on commercial MGTs. Such an implementation takes advantage of the re-programmability of the FPGAs as well as of their embedded MGT devices, giving the user the possibility of increasing the performances of the link in terms of bandwidth, BER, or adding features like the fixed latency.

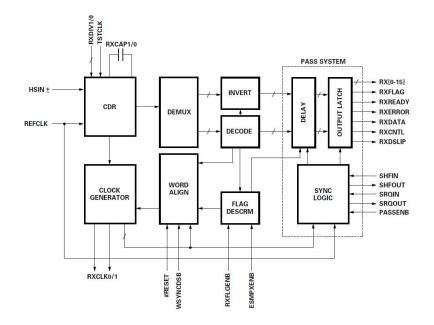

#### The G-Link chip-set

The G-Link chip-set, for instance, has been deployed in the Alice [34], AT-LAS [35], Babar [36], CDF [37], CMS [38] and Nemo [39] experiments and due to its popularity CERN produced a radiation hard serializer compatible with it [40]. The original Agilent GLink chip-set (Fig. 2.15) consists of a transmitter (HDMP-1032A) and a receiver (HDMP-1034A). They are used together to implement a high-speed data link for point-to-point communication with line rates up to 1 Gbps. The chip uses the CIMT scheme (2.2.2) to encode data and to ensure the DC balance of the link. In order to read serial data, the receiver extracts a clock from the CIMT stream and locks its phase to the master transition. The recovered clock synchronizes all the internal operations of the receiver and it is available as an output named RXCLKo/1 (Fig. 2.16). Received data, RX(0:15), is transmitted synchronously with the recovered clock. One of the strong points of the chip-set architecture relies in the deterministic latency of the entire link. Moreover, the receiver structure is such that, thanks to a dedicated Parallel Automatic Synchronization System (PASS), it is also capable of synchronizing the output data with a local receiver clock, while guaranteeing a constant phase relationship with the transmission clock.

#### A Simple Link Interface: the S-LINK

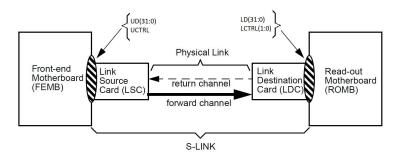

S-LINK [41] is a custom and high-performance data transmission protocol developed at CERN, which has been used in some of the data acquisition systems of the LHC experiments (Alice [34], ATLAS [35], CMS [38]).

S-LINK is based on a simple FIFO-like user interface, which remains independent of the technology used to implement the physical layer. Indeed, several versions of S-LINK have been built that using optical fibers and electrical cables and that use different components driving the links. For examples the S-LINK transmitter implementation, High-speed Optical Link for ATLAS or HOLA, and the S-Link64 (a 64-bits version of the protocol) have been extensively used in ATLAS and CMS, respectively. In particular, HOLA, used the general purpose SerDes TLK2501 by

Figure 2.16: Block Scheme of the Receiver chip in G-Link.

Texas Instruments.

The specification [42] describes the interface between the Front-end Motherboard (FEMB) and the Link Source Card (LSC) and the interface between the Link Destination Card (LDC) and the Read-out Motherboard (ROMB). The S-LINK data format is different for the transmitting lines on the LSC and on the LCD (the return channel). However, for both of them, a 32-bits bus of data is serially sent from the FEMB, UD(31..0), and from ROMB, LD(31..0). In parallel to data extra lines, UCTRL and LCTRL(1:0), are used for the handshaking mechanism and for synchronization.

In addition to simple data movement, S-LINK includes: error detection, a self-test function and a return channel for transmitting flow control commands.

The S-LINK concept is shown in the Fig. 2.17.

Figure 2.17: S-LINK Concept and data format.

Unfortunately, these serial links suffered the fact that a few years ago the production of the G-LINK chip-set and the TLK2501 Serdes were discontinued. In order to find replacements for them, alternative solutions were investigated: in both the cases, FPGA embedded solutions were explored [6, 40]. The new architectures were based on last-generation Xilinx FPGAs, with high-speed serial transceivers in the multi Gbps domain. Their success relies in the characteristics inherited from FPGAs, in terms of re-programmability, portability and versatility. Indeed, specific implementation flavors target different requirements: increasing the bandwidth performances of the link, keeping it backward compatible with the previous ASIC version, or adding fixed-latency for real-rime critical operations.

#### 2.9 STATE-OF-ART OF HIGH SPEED DATA LINKS IN HEP

As the demand for bandwidth and speed increases, not only in the telecommunication but in every field of electronics industry (military, medical, networking, video, etc.), a constant improvements in I/O design has demanded. Multi-gigabit serial I/O are the dominant implementation of I/O interfaces at speeds of 1 Gbps and higher. Multi-Gigabit Transceivers (MGTs) are an improved version of the simple SerDes described in the previous sections. Indeed, beyond the serialization and deserialization functions, Multi-Gigabit Transceivers incorporate additional technologies, such as:

- Differential signalling,

- Phase-locked loops,

- Clock and Data Recovery,

- Emphasis,

- Encoding/Decoding,

- Channel bonding.

Most of this functions has been described in the previous section, and it is clear the fundamental (critical) role they play in data link designs, when operations at high line rate has to be guarantee. Due to their intrinsic capacities, MGTs are increasingly being used for communications because they provide extremely fast, efficient and reliable communication data links. These are the reason why many industrial standards such as:

- FiberChannel (FC);

- PCI Express;

- RapidIO Serial;

- Serial ATA;

- 1-Gb Ethernet and 10-Gb Ethernet (XAUI);

- Infiniband,

Figure 2.18: Radiation-hard optical link architecture.

use multi-gigabit SerDes. Regarding the implementation of MGTs for a particular application, a number of possibilities are available, using:

- 1. an ASIC;

- an off-the-shelf IC (Application Specific Standard Product or ASSP), eventually with an external FPGA;

- 3. an FPGA with its embedded MGT.

Usually, the key factor to take into account (is tempered by several factors) for the decision are: cost, volume, form-factor and flexibility.

ASICs offer the most flexibility for power optimization, packaging and volume cost reduction, but come with prohibitive up-front, non-recurring engineering expenses.

ASSPs have been a popular choice for designs, especially when there is either no additional logic is needed or it is small enough that it can be implemented into a small external FPGA. This solution is not suitable and unattractive for the increase in the device's physical size and absorbed power, as well as for the cost of a two-chip solution. Besides, for most of the actual high-speed serial link, it has become rather common the request of adding a complex extra logic. Then FPGA vendors presented FPGA equipped with re-programmable MGTs. Serial links completely FPGA-based offer a single-chip solution, similar to ASSPs, with all the advantages related to the re-programmability of an FPGA devices: flexibility, timing and testability.

Finally, depending on the case one among the previous solutions prevailed over the other. Examples of different implementations of serial links will be described which are of special importance for High Energy Physic Experiments (HEP).

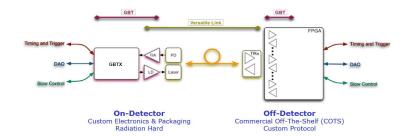

#### 2.9.1 An ASIC SerDes: the GBT

The GigaBit Transceiver (GBT) architecture and transmission protocol has been proposed for data transmission in the physics experiments of the upgrade of the LHC accelerator, SLHC. Due to the high beam luminosity planned for the SLHC, the experiments will require high data rate links and electronic components capable of sustaining high radiation doses. The GBT ASICs is a radiation-hard bidirectional 4.8 Gbps optical fibre link for the transmission between the counting

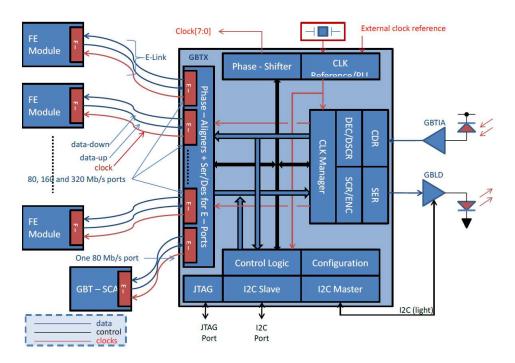

Figure 2.19: A simplified block diagram of the GBTx.

room and the experiment. The basic architecture of the GBT protocol is shown in Fig. 2.18.

One half of the system resides on the detector and hence in a radiation environment, therefore requiring custom electronics. It consists of the following components: GBTx, a serializer-de-serializer chip for data; GBTIA: a trans-impedance amplifier receiving the 4.8 Gbps serial input data from a photodiode; GBLD: a laser-driver ASIC to modulate 4.8 Gbps serial data on a laser; GBT-SCA: a chip to provide the slow-controls interface to the front-end electronics.

The other half of GBT is off-detector then, it is free from radiation and can use commercially-available components: consists of a Field-Programmable-Gate-Array (FPGA), programmed to be compatible with the GBT protocol and to provide the interface to off-detector systems. A parallel project, the Versatile Link project, has been started in order to produce a system of opto-electronics components for the optical data transmission.

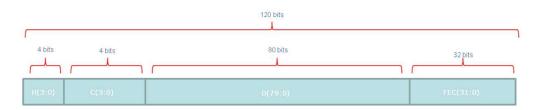

In Fig. 2.19 a simplified block diagram of the GBT is reported. Some of the blocks are typical components of transceivers (CDR and PISO/SIPO converters), others are specific to the trigger functions (trigger logic and bunch emulator), perform control of error conditions that are common in HEP environments only (for example, Single Event Upset (SEU) monitor, watchdog), or help testability. Many parallel and serial ports following well established industrial standards are available: 1–Wire, I2C, JTAG. The format of the GBT data packet is shown in Fig. 2.20. A fixed header (H) is followed by 4 bits of slow control data (C), 80 bits of user data (D) and the Reed-Solomonforward error correction (FEC) code of 32 bits. The coding efficiency is therefore 88/120 = 73%, and the available

Figure 2.20: GBT frame format.

user bandwidth is 3.2 Gbps. Even though, the real the GBTx is an ASIC chip, together with the GBT project, the GBT-FPGA project started too, with the intend of emulating the GBTx serial link and test the first GBTx prototypes. Thanks to this project, now there is a full library [43], targeting FPGAs either from Altera and Xilinx, which allows the implementation of GBT links on FPGAs.

#### 2.9.2 Off-The shelf SerDes

Due to their importance and extensive use many vendors offer commercial SerDes solutions, capable of supporting wide input frequency and data ranges, and thereby support wide data ranges covering most of the applications mentioned.

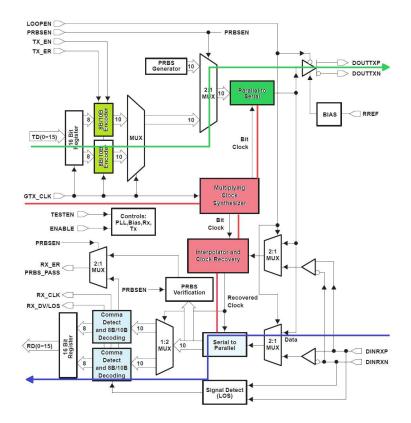

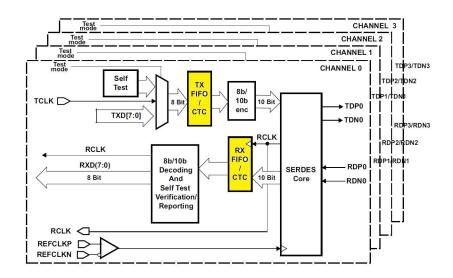

Texas Instruments (TI), for example, produces general purpose SerDes, such as the TLK1501, TLK2501 and TLK1501, which can be used for high-speed bidirectional transmission. They cover a range of line rate from 0.6 Gbps to 3.125 Gbps. The block diagram is almost the same for all the devices and it is shown in Fig. 2.21, where the blocks already mentioned can be easily identified. On the top there is serializer block. Data, TX(15:0), are first stored in a register and then encoded (if this functionality is enabled). Finally, data are serialized by the Parallel To Serial Block and differentially transmitted. On the bottom, the deserialized section is presented which provide to the opposite function. In the centre, the block for clock and data recovery is shown.

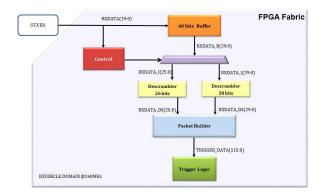

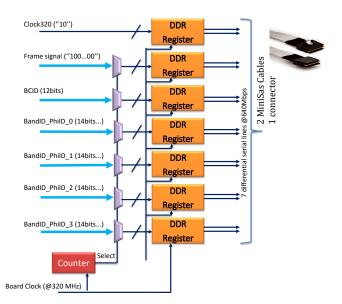

For applications such as Gigabit Ethernet, fibre channel, 10G Ethernet, advanced SerDes needs to be development, such as the TLK3134 by TI. The TLK3134 is a flexible four-channel independently configurable serial transceiver which is ideal for bidirectional point-to-point data transmissions up to 30 Gbps data rate. It can be configured to be compliant with the 10Gbps Ethernet XAUI specification and the 1000Base-X 1Gbps Ethernet Specification. In the Fig. 2.22 the basic functions of a MGT can be easily recognized. For the XAUI core, a high level description of the TLK3134 is shown in Fig. 2.23. The structure is more complicated and four channel are contemporary used to handle the amount of data. In Fig. 2.23, two new blocks RXFIFO/CTC and TXFIFO/CTC are used. In the receive data path, a FIFO (RXFIFO/CTC) is placed on the output of the serial to parallel conversion logic. It compensates for channel skew, clock phase and frequency tolerance differences between the recovered clocks for each serial links and the re-

Figure 2.21: TLK1501 Block Diagram.

Figure 2.22: Core Block Diagram of the TLK3134 SerDes.

Figure 2.23: Block Diagram of LK3134 SerDes for XAUI1000BaseX applications.

ceive output clock, RCLK, synchronous with the recovered parallel data, RD(31:0). Besides, the two blocks provide for Clock Tolerance Compensation (CTC). Indeed, although the XAUI interface is defined to allow for separate clock domains on each side of the link, the reference clocks for two devices on a XAUI link cannot have the same exact frequencies. The slight differences in clock frequencies is compensated via the insertion or the removal of special characters on all channels. This technique avoid the FIFOs on the receiver/transmitter to over or under run.

# 3

# SELF ADAPTIVE SERIAL LINK

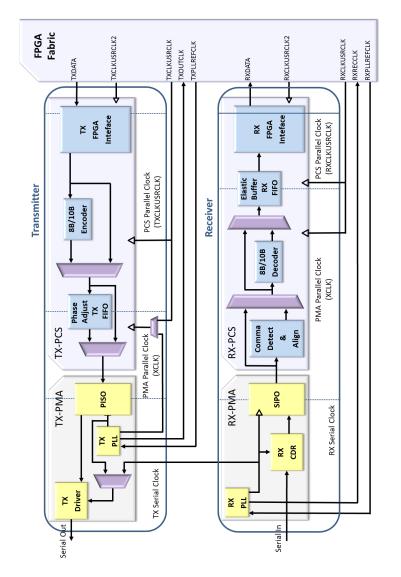

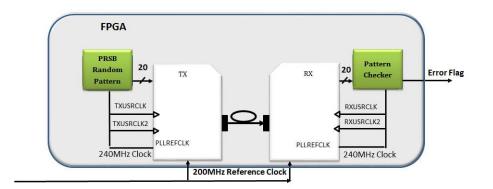

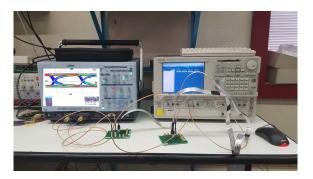

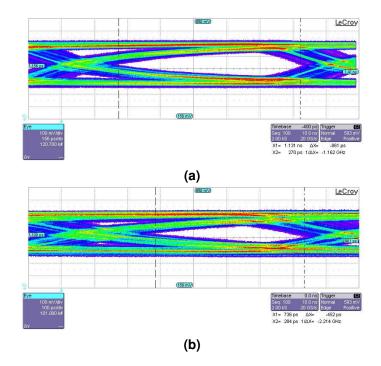

In this chapter a frequency agile, auto-adaptive serial link is presented [44]. The system is intended as a proof-of-concept of a more general adaptive serial link, which is capable to analyze the incoming data stream and to find the highest transmission line rate, according to a given tolerated BER. In particular, it is designed around an FPGA-embedded microprocessor, which drives the programmable ports of an embedded Multi-Gigabit Transcever (MGT) in order to control the quality of the received data and to easily calculate the Bit Error Ratio (BER) in each sampling point of the eye diagram. Besides, the link is able to reconfigure the MGT parameters in order to fully benefit from the available link bandwidth, by setting the highest line rate.

This architecture can be used whenever it is crucial to have prompt information about the maximum sustainable line rate of a connection, such as on test beam sites, where the user could be forced to adapt dynamically his setup to the cabling resources available on site. The system can be also used as a monitoring tool in HEP experiments, where the connections are subject to ageing and insertion losses, and the fibres can increase their attenuation because of radiation; it can also be implemented whenever it is necessary to remotely monitor a transmission system, in order to detect issues in the serial link physical layer. As an application example, it can be proposed some of the many experiments at Large Hadron Collider (LHC) at CERN, which have been intensively using different serial links, both for transmission of Timing, Trigger and Control signals (TTC) [1] and for trigger and data readout [2, 3]. Some of the listed serial links were required also to be fixed-latency links, for transmission of trigger data, and were originally designed and deployed in the field by using custom ASICs. However, recent studies [40, 45] show that last generation FPGA features permit to implement the same links in cost-effective designs, in order to overcome the obsolescence of some component of the original link and to permit the integration in the new hardware, designed for the different upgrades of the LHC physics program [46, 47]. The solution proposed could be easily adapted in this framework, as it can be used on top of any user's existing link, as it has no specific requirement about link specification or protocol.

The first part of the chapter focuses on the state of the art in the field of adaptive serial links. Hence an introduction to FPGA devices, and the description of some architectural details of the embedded MGT, which the link is based on, are presented. Finally, the self-adaptive link project, the description of the test bench used and the experimental results are described and discussed .

## 3.1 STATE OF THE ART AND MOTIVATION

Different adaptive link strategies are explored in literature, mostly proposing architectures that define low power or low error solutions, as we will describe later. The main task of the link developed in this paper, on the other hand, is to provide the best performances in terms of bandwidth, compatible with the physical layer. State-of-the art research activity in electronics is presently focusing on adaptive serial links capable to perform traffic-driven rate adaptation in wireless networks or Ethernet. Different adaptive link rate (ALR) mechanisms can be found in literature [48, 49], which allow to lower the link rates when the network traffic request is reduced, thus lowering the power consumption, with little impact on network performances [50, 51]. Moreover, wireless application also have to face with the poor quality of the channel; these applications must adapt the data transmission to the link-level error rate and provide techniques to recover from transmission errors. To be more specific, as an example, it can be investigated on the Bluetooth [52] specification, which provides two techniques in order to overcome link-level transmission errors, due to the poor channel quality, which causes a relatively high error rate (typically around  $10^{-2}$ ). The two recommended techniques are:

- Forward Error Correction (FEC) coding, which adds overhead on the data payload in order to detect and correct transmission bit errors;

- Automatic Repeat reQuest (ARQ) transmission scheme, which informs the source that the last data transfer was successful or failed, thus allowing for a retransmission of data.

Unfortunately, these two schemes has the following drawback:

- FEC coding always adds overhead on the data, thus reducing the throughput of the link, even when the transmission is error free;

- ARQ scheme can typically introduce additional and variable delays due to the retransmission, which are not suitable for real-time applications, such as fixed latency trigger paths.

Another activity of research in the field of serial links concerns the power saving techniques in the serial communication between Integrated Circuits (IC) chips, mounted on supercomputer or server motherboards, with high data-processing demands, or in high-speed network routers which require a large number (~ hundreds) of links. Indeed, simulations and experiments show that most Ethernet links are underused and the energy consumption of the link could be reduced by simply operating them at a lower line rate. In order to save power, by lowering the line rate, one of the suggested techniques [53] is the use of adaptive power control. When the peak performance is not needed, adaptive power-supply regulation lowers the power consumption by reducing the supply voltage of the serial-link chips to the minimum supply value required to support the transmission

Figure 3.1: Overview of FPGA architecture.

frequency. Since the power dissipation of a CMOS is proportional to  $V^2 f$ , lowering both the supply voltage V and the frequency f greatly reduces the overall power dissipation. Adaptive power supply regulation techniques usually rely on analog feedback circuits, which adjust the supply voltage of an oscillator (thus increasing/reducing its internal propagation delays) so that the modified frequency fits with the desired transmission frequency. This approach is usually adopted in ASIC chips, while it cannot be followed in an FPGA-based serial link design, where constraints on the power supply are very tight.

Different from the state-of-art research activity, this proposal aims at obtaining the maximum line rate link performances. However, since this architecture is principally designed to meet the requests of the HEP experiments, its principal goal is to obtain a safe transmission at the highest line rate for a given physical layer. In order to work at the highest line rate, without the possibility of using the FEC technique or retransmitting data, an error-free transmission has to be guaranteed. Due to its intrinsic nature and in contrast with the links previously described, this architecture can easily fit in TDAQ systems of HEP experiments with realtime requirements, as neither extra delay is added to the main functionality of the serial link nor overhead is added to the payload. It has been also intended for implementation in Xilinx SRAM FPGA, thus gaining from the flexibility and re-programmability of the device, and it can be added on top of any user's custom serial link, as it has no requirement about link specification or underlying protocol.

Before going into the detailed description of the architecture, a general description of FPGAs is given, as a background for a better understanding of the projects.

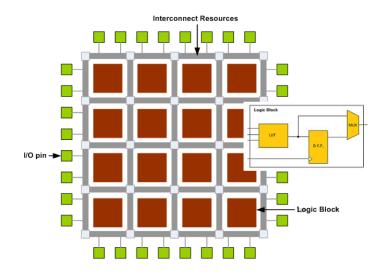

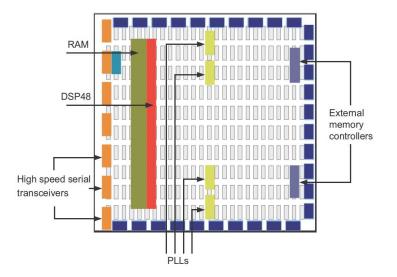

## 3.2 FIELD PROGRAMMABLE GATE ARRAY, FPGA

Field Programmable Gate Array devices, FPGAs, are integrated circuits containing logic blocks which can be programmed by the user *in the field* [54]. Logic blocks contain a wide set of programmable logic gates and memory elements (simple flip-flops or more complex block of memories). FPGAs contain also interconnect resources, which allow the blocks to be *wired* together and to implement almost any kind of digital circuit or system.

The basic structure of an FPGA (3.1) includes the following elements:

- 1. Look-up table (LUTs): blocks which performslogic operations;

- 2. Flip-Flop (FFs): register elements which can store the result of the LUT;

- 3. wires: interconnection resources;

- 4. IO pads: physically ports that get data in and out of the FPGA.

Although this structure allows the implementation of a wide range of digital system, in order to improve their efficiency, contemporary FPGAs incorporate additional elements, which implement specific functions such as:

- 1. embedded memories for distributed data storage (BlockRAMs);

- 2. Phase-locked loops (PLLs) for driving the FPGA fabric at different clock rates;

- 3. external and/or embedded microprocessors;

- 4. Digital Signal Processors (DSPs).

The final FPGA architecture result in a more complicate scheme shown in Fig. 3.2. For low to medium volume productions, FPGAs provide a cheaper and faster time to market solution with respect to Application Specific Integrated Circuits (ASIC). Indeed, while obtaining the first ASIC prototype normally requires a lot of resources in terms of design time and financial resources, an FPGA is ready to use and to be configured (in less than a minute) and its cost is reasonable low. In the latest FPGAs, to improve their flexibility a further, useful feature is present. In this devices is possible, a partially reconfiguration of a portion of FPGA (through the Dynamically Reconfiguration Ports, DRP) while the rest of it is still running.

## 3.2.1 FPGA's Technologies

The reconfigurability and reprogrammability of an FPGA underlies on the technology used to implement the logic blocks and the interconnections. There are a number of technologies including static memory (SRAM), flash and anti-fuse.

1. SRAM-based FPGAs: They store logic cells configuration data in the static memory which are organized as an array of latches. SRAM-based technology is the most widely used approach, because of the re-programmable

#### 3.2 FIELD PROGRAMMABLE GATE ARRAY, FPGA

Figure 3.2: Detailed internal FPGA architecture, including macroblocks.

capability and the use of standard CMOS process technology (which means higher and higher integration and speed, and lower and lower dynamic power consumption). However, its large area, as compared to other technologies, and its volatile nature are the main drawbacks. 5

- 2. Flash-based FPGAs: The flash-based FPGAs uses flash or EEPROM as a primary resource for configuration storage. This technology has several advantages: it is less power and area consumptive, non volatile, and more tolerant to radiation effects. However it cannot be reconfigured an infinite number of times and its technology is based on non-standard CMS process.

- 3. Antifuse-based FPGAs: Antifuse-based FPGAs are different from the previous mainly because they can be programmed only once. Its primary advantage relies in its lower area occupancy as well as in the presence of low parasitic capacitance. The antifuse is a device that doesn't conduct current initially, but can be *burned* to conduct current. The antifuse-based FPGA can't be then reprogrammed since there is no way to return a burned antifuse into the initial state.

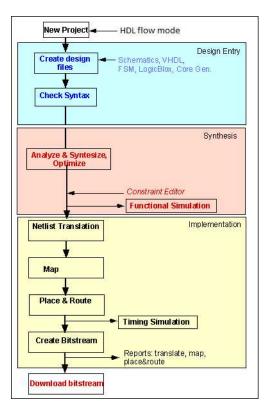

## 3.2.2 Design Flow

Design flow of FPGA starts with the behavioural description of the circuit to implement. It is usually used a hardware description language, HDL (*Very-High-Speed-Integrated-Circuit*-HDL, VHDL, or Verilog) more then a schematic design. In any case, they allow the user either to design digital systems and to simulate its operation with different level of accuracy. An automation tool (usually a company's proprietary software) is used to compile the hardware description code and convert it into a stream of bits, bitstream, which is eventually loaded into the FPGA to configure the logic blocks and the interconnections. The complete

## SELF ADAPTIVE SERIAL LINK

Figure 3.3: Overview of design flow of a Xilinx FPGA device.

development process is depicted in more details in 3.3 [55].

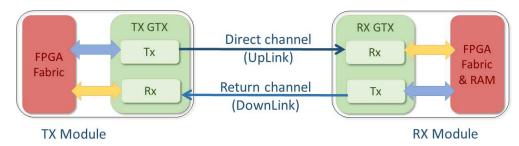

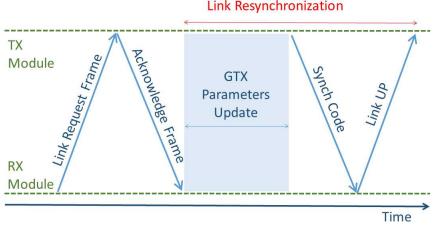

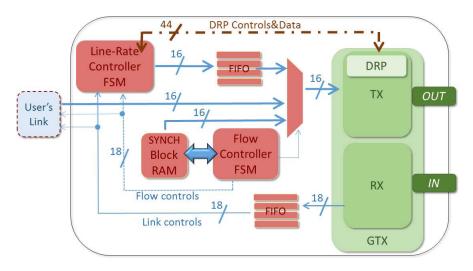

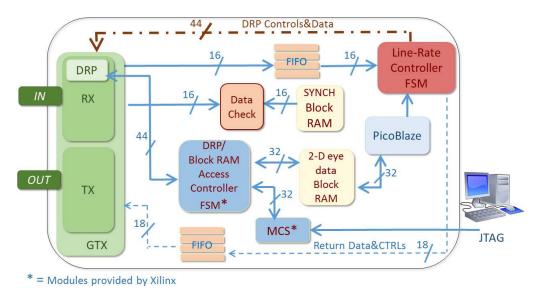

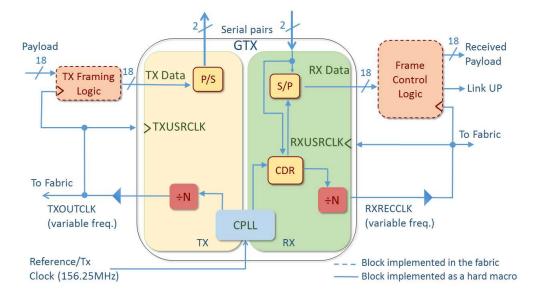

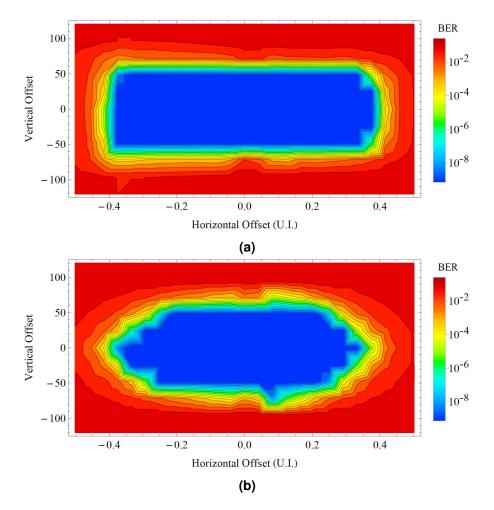

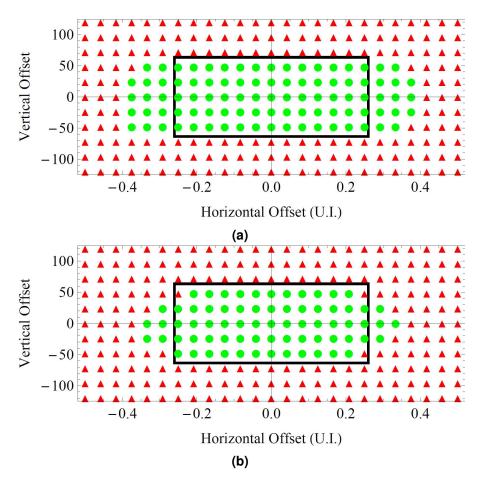

Once, the logic circuit has been developed using an HDL language, a synthesizer transforms the code into a gate-level netlist, using the components included into basic libraries. The netlist, which is a description of the various logic gates in the design with their interconnection, is device independent. The synthesis tool can optimize the network in terms of area, speed or power consumption. At this stage behavioural simulation can and must be done in order to check the proper operation of the circuit, however information about switching delays is not included, yet.