# Development of the readout for the IBL Upgrade Project of the ATLAS Pixel Detector

## Dissertation

zur Erlangung des mathematisch-naturwissenschaftlichen Doktorgrades

"Doctor rerum naturalium"

der Georg-August-Universität Göttingen

$im\ Promotions programm\ ProPhys$

der Georg-August University School of Science (GAUSS)

vorgelegt von

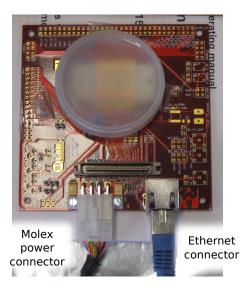

Nina Krieger

aus Achim

Göttingen, 2012

II. Physik-UniGö-Diss-2012/08

#### Betreuungsausschuss

- 1) Prof. Dr. A. Quadt, Elementarteilchenphysik/Top Physik, II. Physikalisches Institut

- 2) Priv. Doz. Dr. J. Große-Knetter, Elementarteilchenphysik/Detektorphysik, II. Physikalisches Institut

- 3) Prof. Dr. A. Frey, Elementarteilchenphysik/B-Physik, II. Physikalisches Institut

#### Mitglieder der Prüfungskommission

Referent: Prof. Dr. A. Quadt, Elementarteilchenphysik/Top Physik,

II. Physikalisches Institut

Korreferent: Priv. Doz. Dr. J. Große-Knetter, Elementarteilchenphysik/Detektorphysik,

II. Physikalisches Institut

Weitere Mitglieder der Prüfungskommission:

- 1) Priv. Doz. Dr. H. Peter, Dynamik der Sonne, Max-Planck-Institut für Sonnensystemforschung

- 2) Prof. Dr. A. Reiners, Magnetische Aktivität von Sternen und Planeten, Institut für Astrophysik

- 3) Prof. Dr. E. Bodenschatz, Hydrodynamik, Strukturbildung und Biokomplexität, Max-Planck-Institut für Dynamik und Selbstorganisation

- 4) Prof. Dr. S. Luther, Biomedizinische Physik, Max-Planck-Institut für Dynamik und Selbstorganisation

Tag der mündlichen Prüfung: 28.09.2012

## Development of the readout for the IBL Upgrade Project of the ATLAS Pixel Detector

by

Nina Krieger

The LHC luminosity is upgraded in several phases until 2022. The resulting higher occupancy degrades the detector performance of the current Pixel Detector. To provide a good performance during the LHC luminosity upgrade, a fourth pixel layer is inserted into the existing ATLAS Pixel Detector. A new FE-I4 readout chip and a new data acquisition chain are required to cope with the higher track rate and the resulting increased bandwidth. Among others, this includes a new readout board: the IBL ROD. One component of this board is the DSP which creates commands for the FE-I4 chip and has to be upgraded as well.

In this thesis, the first tests of the IBL ROD prototype are presented. A correct communication of the DSP to its external memory is verified. Moreover, the implementations for an IBL DSP code are described and tested. This includes the first configuration of the FE-I4 with an IBL ROD. In addition, a working communication with the Histogrammer SDRAM and the Input FIFO on the IBL ROD are demonstrated.

# Contents

| 1 | Intr                                            | roduction                                           | 1  |  |  |  |

|---|-------------------------------------------------|-----------------------------------------------------|----|--|--|--|

| 2 | The                                             | e Standard Model and beyond                         | 3  |  |  |  |

|   | 2.1                                             | The Standard Model                                  | 3  |  |  |  |

|   | 2.2                                             | The limits of the Standard Model                    | 5  |  |  |  |

| 3 | Particle interaction with matter                |                                                     |    |  |  |  |

|   | 3.1                                             | Fundamental interactions                            | 7  |  |  |  |

|   | 3.2                                             | Particle detection                                  | 10 |  |  |  |

|   | 3.3                                             | Silicon as sensitive detector material              | 12 |  |  |  |

|   | 3.4                                             | The effects of radiation on silicon                 | 15 |  |  |  |

| 4 | Experimental setup 17                           |                                                     |    |  |  |  |

|   | 4.1                                             | The Large Hadron Collider                           | 17 |  |  |  |

|   | 4.2                                             | The ATLAS Detector                                  | 19 |  |  |  |

|   |                                                 | 4.2.1 The ATLAS trigger system                      | 24 |  |  |  |

| 5 | The                                             | e current ATLAS Pixel Detector                      | 25 |  |  |  |

|   | 5.1                                             | The ATLAS Pixel Module                              | 26 |  |  |  |

|   |                                                 | 5.1.1 The sensor material                           | 27 |  |  |  |

|   |                                                 | 5.1.2 The FE-I3 chip                                | 28 |  |  |  |

|   | 5.2                                             | The Pixel Detector readout chain                    | 31 |  |  |  |

|   | 5.3                                             | The Read Out Driver                                 | 33 |  |  |  |

|   | 5.4                                             | The Digital Signal Processor on the ROD             | 35 |  |  |  |

|   |                                                 | 5.4.1 The tasks of the Master DSP                   | 36 |  |  |  |

|   | 5.5                                             | Data Acquisition                                    | 36 |  |  |  |

| 6 | The                                             | e Insertable B-Layer Upgrade                        | 41 |  |  |  |

|   | 6.1                                             | Physics at the High-Luminosity-LHC                  | 41 |  |  |  |

|   | 6.2                                             | ATLAS Detector upgrades for the High-Luminosity-LHC | 42 |  |  |  |

|   | 6.3                                             | The Insertable B-Layer                              | 43 |  |  |  |

|   | 6.4                                             | The ATLAS IBL Module                                | 44 |  |  |  |

|   |                                                 | 6.4.1 The IBL sensor material                       | 44 |  |  |  |

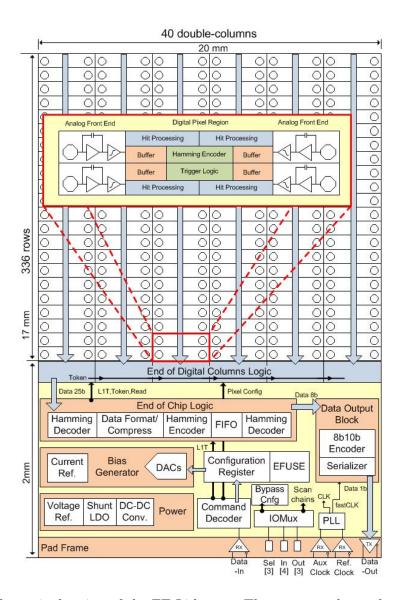

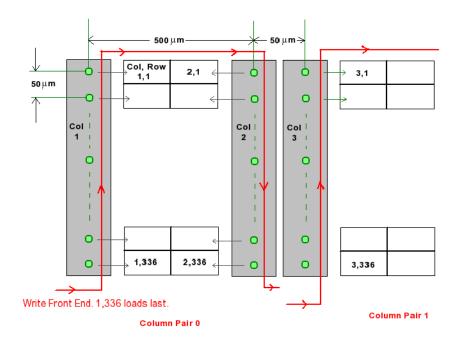

|   |                                                 | 6.4.2 The FE-I4 Chip                                | 47 |  |  |  |

|   | 6.5                                             | The IBL readout chain                               | 50 |  |  |  |

|   | 6.6                                             | The IBL Read Out Driver                             | 55 |  |  |  |

|   | 6.7                                             | The IBL Data Acquisition                            | 58 |  |  |  |

| 7 | The Digital Signal Processor for the IBL ROD 61 |                                                     |    |  |  |  |

|   | 7.1                                             | Introduction                                        | 61 |  |  |  |

|   | 7 2                                             | The DSP code                                        | 62 |  |  |  |

|                  |      |                                                   | 52<br>57     |  |  |

|------------------|------|---------------------------------------------------|--------------|--|--|

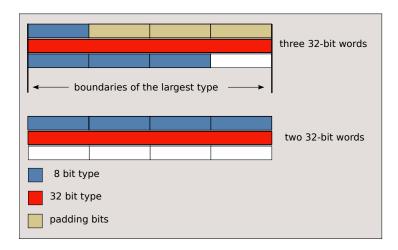

|                  |      | 7.2.3 DSP memory and address management           | 71           |  |  |

|                  | 7.3  | The challenges of the DSP code development        | $^{\prime}2$ |  |  |

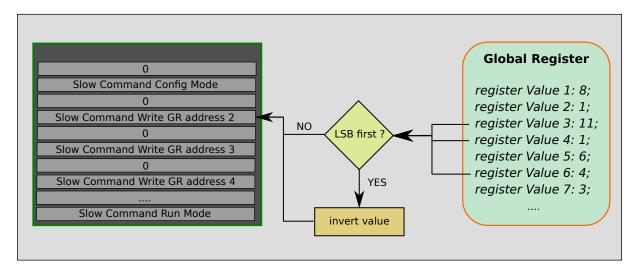

|                  | 7.4  | Code adaptations and implementation for FE-I4     | 73           |  |  |

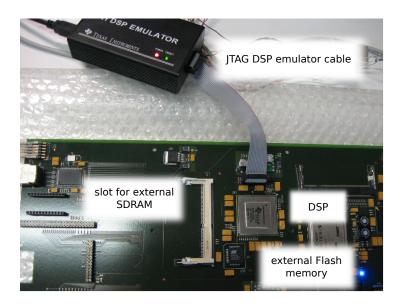

| 8                | Firs | tests of the IBL readout chain 7                  | 7            |  |  |

|                  | 8.1  | First IBL ROD hardware tests                      | 7            |  |  |

|                  |      | 3.1.1 Code Composer Studio                        | 7            |  |  |

|                  |      | 8.1.2 DSP memory tests                            | 8            |  |  |

|                  | 8.2  | Preliminary tests of the IBL DSP code             | 80           |  |  |

|                  | 8.3  | Tests of the IBL DSP with the IBL ROD prototype B | 32           |  |  |

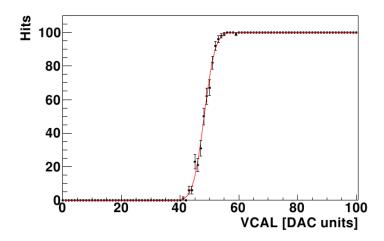

|                  |      | 8.3.1 Pixel Register configuration                | 35           |  |  |

|                  |      | 8.3.2 First FE-I4A configuration with an IBL ROD  | 37           |  |  |

|                  |      | 8.3.3 Global Register readback                    | 37           |  |  |

|                  |      | 3.3.4 Scan implementation issues                  | 92           |  |  |

| 9                | Con  | lusion and outlook 9                              | 3            |  |  |

| Appendix         |      |                                                   |              |  |  |

| A                | Acr  | nyms 9                                            | 7            |  |  |

| Bibliography     |      |                                                   |              |  |  |

| List Of Figures  |      |                                                   |              |  |  |

| List Of Tables   |      |                                                   |              |  |  |

| Acknowledgements |      |                                                   |              |  |  |

## 1 Introduction

During the last century a physics model was developed which explains the basic processes of elementary particle physics. This so called Standard Model made predictions which could be verified with measurements by detectors at high energy particle accelerators. A lot of parameters of this theory are already well described. However, there are still some open issues. One of the main challenges is the question about the origin of mass which is described by the Higgs mechanism. An evidence for the existence of this mechanism is the Higgs particle which is one of the main focusses of the today's high energy particle physics experiments.

To improve the precision of the Standard Model and find hints for physics beyond the Standard Model the Large Hadron Collider (LHC) was built at the CERN<sup>1</sup> research facility in Geneva, Switzerland. Here, two proton beams are collided at a nominal centre of mass energy of presently  $\sqrt{s} = 7$  TeV. In these collisions new particles are produced which are detected by high energy particle detectors. One of the main experiments to measure these particles is the ATLAS<sup>2</sup> Detector. It consists of subdetectors which are specialised to give information about the different types of particles.

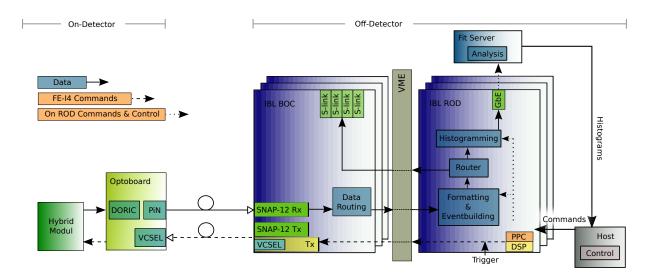

The innermost subdetector is the ATLAS Pixel Detector. It is made up of an on-detector part which measures the hit information of traversing particles and an off-detector part which is used to transmit the data off the detector and processes it further.

To extent the physics potential the LHC luminosity is upgraded in several phases until 2022. This leads to an increased track density which in particular influences the performance of the innermost ATLAS Pixel Detector layer. Furthermore, radiation damages and detector failures which occurred during operation degrade the Pixel Detector. A fourth detector layer is inserted into the current Pixel Detector to guarantee a good detector performance during the upgrade. This Insertable B-Layer (IBL) is planned to be installed in the first phase of the LHC luminosity upgrade in 2013.

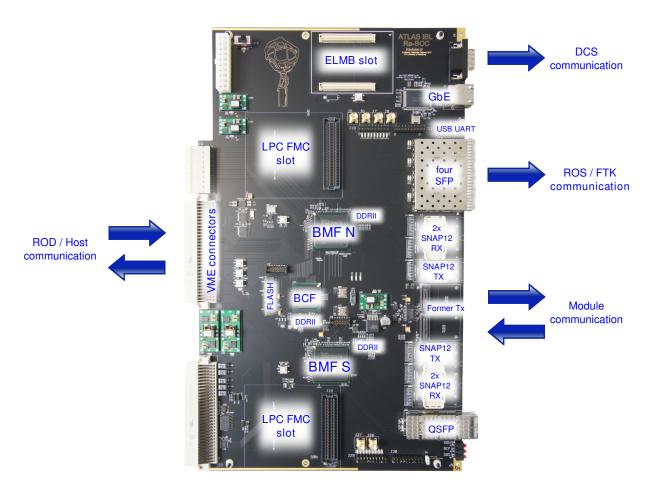

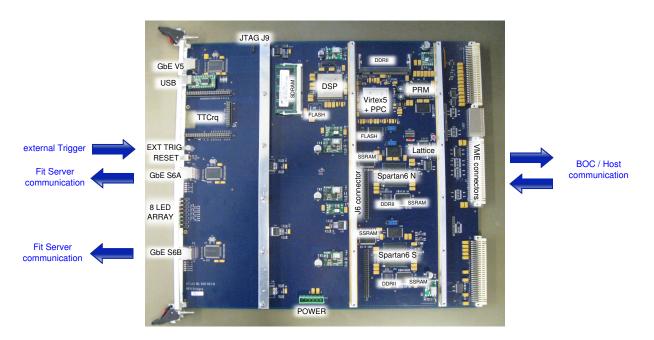

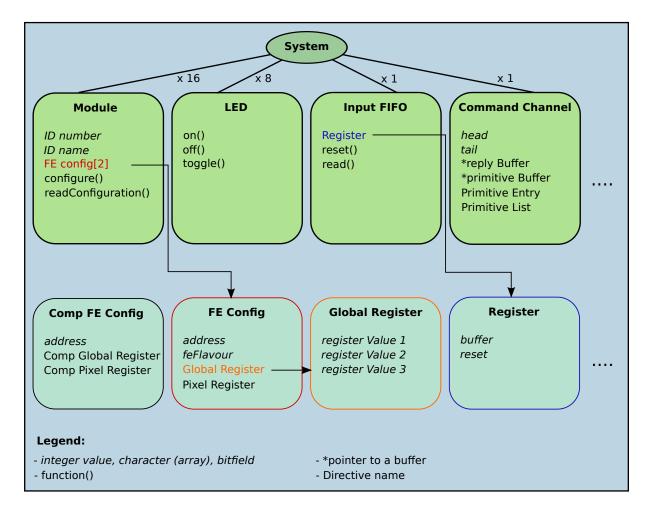

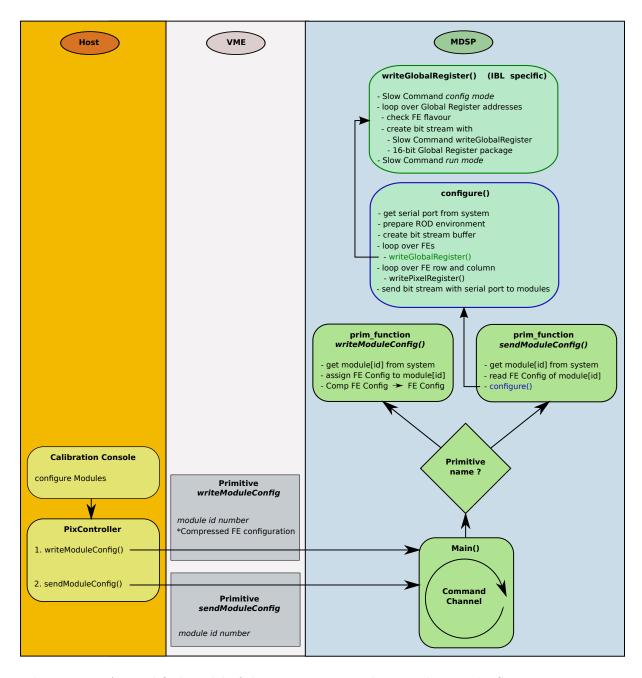

The distance of the IBL to the interaction point is smaller than the distance of the current innermost Pixel Detector layer. This and the higher luminosity lead to an increased track rate which requires a new sensor with higher granularity. In addition, a new readout chip has to account for the increased amount of hit data. To cope with the higher bandwidth which is necessary to transmit the hit data off the detector, a new readout chain is required as well. As a baseline the Read Out Driver (ROD) of the current Pixel Detector is used. This board histograms and analyses the hit data when the detector is calibrated. It also contains a Digital Signal Processor (DSP) which communicates with the readout chips when they are configured or scanned. For the IBL a new enhanced ROD is developed to fulfil the requirements of the IBL.

One improvement of the IBL ROD is the capability to handle four times the data processed by the ROD. Furthermore, the bandwidth of the interface which is used to send the analysed hit information off the ROD has to be increased. On the IBL ROD a Gigabit Ethernet link is used to send the data to an external PC where it is further processed.

To account for the changes in communication with the new readout chip the software of the

<sup>&</sup>lt;sup>1</sup>Conseil Européen pour la Recherche Nucléaire

<sup>&</sup>lt;sup>2</sup>A Toroidal LHC Apparatus

DSP has to be changed as well. New configuration streams and an adjusted scan procedure have to be implemented into the IBL DSP software. In addition, the host software which sends commands to the IBL DSP to control the detector has to be adapted.

This thesis gives a short introduction about the Standard Model and physics beyond the Standard Model in Chapter 2. In Chapter 3 is explained how particles interact with matter. An overview of the LHC and the ATLAS Detector is given in Chapter 4.

In Chapter 5 the Pixel Detector is introduced, specifying the relevant physics processes which require a good performance of the B-Layer. Then the ATLAS Pixel Module and the readout chain are described. Moreover, an introduction about the DSP is given. In Chapter 6 the IBL upgrade project is explained.

Chapter 7 is dedicated to the IBL DSP. First, the IBL DSP software code is described, followed by the challenges experienced during the development. Finally, the necessary implementations are pointed out which were done with the IBL DSP code. First hardware tests carried out with an IBL ROD prototype board are described in Chapter 8. Moreover, the implementations of the first version of the IBL DSP code are tested. A conclusion and an outlook are given in Chapter 9.

# 2 The Standard Model and beyond

Although in every day life people are rarely faced with the field of high energy particles physics this part of science seeks to answer one of the most exciting questions of physics: What is today's matter and why is it like that?

To answer this question the ancient Greek philosopher Demokrit started in 400 B.C. with the postulation of the atom. Many years later in 1897, Joseph John Thomson discovered the electron and in the 1920s Quantum mechanics was developed by Erwin Schrödinger, Werner Heisenberg, Max Born and many other physicists. Among the latter, Max Planck proposed the Planck constant to define discrete energy values and Wolfgang Pauli introduced the spin of a particle as a new Quantum number. At the same time Quantum Field Theory was developed to describe the elementary particles and their interactions.

While these discoveries have been made by a handful of people, nowadays experiments are made by collaborations of thousands of people organised by research facilities like CERN or KEK<sup>1</sup>. More than 20,000 people from all over the world joined in large groups to discover more and more about particle physics<sup>2</sup>, building huge detectors to discover the properties of the smallest particles.

To come to a deeper understanding of how the world is made up a theory was developed which explains the basics of elementary particles. This so called Standard Model (SM) is further explained in Section 2.1. Although the SM was verified many times and led to the prediction and discovery of new particles the model has reached its limits which are listed in Section 2.2.

## 2.1 The Standard Model

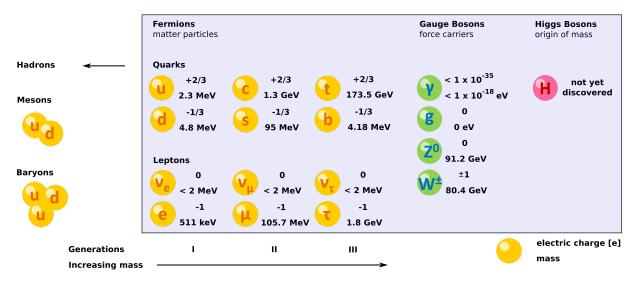

The Standard Model (SM) combines the electroweak and strong force into one theory. It explains the elementary particles as well as the interactions between them. All particles can be categorised by their properties like electric charge, colour charge, spin or mass. These properties define the individual behaviour of each particle. Furthermore, conservation laws such as energy, spin or charge conservation are predicted by the SM which characterises the decay of particles into other particles. All SM particles are listed in Figure 2.1.

The individual force carriers are gauge bosons with integer spin: the photon  $\gamma$  is the interaction particle for the electromagnetic force; the  $Z^0$ - and  $W^{\pm}$ -boson mediate the interactions of the weak force and the gluon g for the strong force. They all have spin 1.

The photon is massless and therefore the range of the electromagnetic force, acting on all charged particles, is infinite. The force carriers of the weak force are massive and thus the weak interaction has a finite range of  $10^{-18}$  m. Both, the electromagnetic and the weak interactions are unified within the electroweak theory.

<sup>&</sup>lt;sup>1</sup>High energy accelerator research organisation located in Tsukuba, Japan.

<sup>&</sup>lt;sup>2</sup>Just to mention the members belonging to the CERN Experiments of ATLAS, CMS, ALICE and LHCb (15,600 members) [1], as well as the institutes of Fermilab (2,000 members) [2], Brookhaven National Lab (3,000 members) [3] and KEK (600 members) [4]. The list is not complete because larger collaborations are mentioned only.

The strong interaction is the force which binds quarks into hadrons. It acts on all particles carrying a colour charge: quarks and gluons. Quarks carry one of three possible colour states. Gluons are one of eight different linear combinations of two of three possible colour states. The range of this force is about  $10^{-15}$  m. If the distance between bound quarks increases due to external interactions the energy in the field of the strong force gets so strong that new quark-antiquark-pairs are generated. This effect is called confinement.

Figure 2.1: The elementary matter particles (yellow) and their interaction particles (green) with their electric charge and mass [5]. The fermions and gauge bosons are already measured particles of the SM. The higgs boson (pink) is still a hypothetical particle to complete the list of elementary particles in the SM.

The particles interacting through these forces are the matter particles of the SM. They are fermions with half-integer spin. The matter particles can be categorized into three generations with increasing mass. For each particle there is an identical partner with opposite electrical charge which is called its antiparticle. Fermions can also be separated into quarks and leptons.

Quarks interact via the strong, electromagnetic and weak force. They carry a so called "colour" which can be one of three states or their anti-states. As there are only colour-neutral particles in nature they never exist as single particles but in colourless compound states which are called hadrons. Hadrons can be separated into mesons and baryons. Mesons contain a quark-antiquark pair with a colour and an anti-colour state, respectively. Baryons consist of three quarks. The three quarks are either the three colour states or the three anti-colour states in order to be colour neutral. Although they are all called matter particles only the u- and d-quarks and the electron  $e^-$  form the matter we see in every day life. The most common hadron seen in every day life is the proton, consisting of two u- and one d-quark, and the neutron, consisting of one u- and two d-quarks. The different type of quark is also called "flavour" which can only be changed via the weak force. As the t-quark has the highest mass with 173.5 GeV/ $c^2$  it decays immediately after being produced [6, 7]. Therefore, it does not hadronise.

Leptons contain the electron, the muon and the tau particle and their chargeless neutrinos. The first three interact through the weak and the electromagnetic force. Because neutrinos carry no electric charge they only interact by the weak force and have a very low cross section. Thus, they rarely interact with matter.

Basic parameters of the SM could be verified at the LHC after the first years of data taking. In the following some examples are listed. The full range of measurements cannot be stated here as it would go beyond the scope of this thesis.

At CMS, the W<sup>+</sup>W<sup>-</sup> production cross section in pp collision data at  $\sqrt{s} = 8$  TeV was measured to be  $\sigma_{\rm ww} = 69.9 \pm 2.8$  (stat.)  $\pm 5.6$  (syst.)  $\pm 3.1$  (lumi.) pb with an integrated luminosity of 3.54 fb<sup>-1</sup>. This result is consistent with the SM prediction of  $\sigma_{\rm ww} = 57.3$  ( $^{+2.4}_{-1.6}$ ) pb [8].

With an integrated luminosity of 2.9 pb<sup>-1</sup> and an assumed t-quark mass of 172.6 GeV, a  $t\bar{t}$  cross section of  $\sigma_{t\bar{t}}=145~\pm~31^{+42}_{-27}$  pb could be measured at the ATLAS Detector in pp collisions at  $\sqrt{s}=7~{\rm TeV}$  [9]. This is as well in agreement with the SM predictions of  $\sigma_{t\bar{t}}=164^{+11.4}_{-15.7}$  pb [10].

Furthermore, the LHCb detector measured the CP-violating phase  $\phi_s$ , the  $B_s^0$  decay width  $\Gamma_s$  and the decay width difference  $\Delta\Gamma_s$  of the heavy and light mass eigenstates of the  $B_s^0 - \bar{B}_s^0$  system in  $B_s^0 \to J/\Psi \phi$  decays at 0.37 fb<sup>-1</sup> of pp collisions at  $\sqrt{s} = 7$  TeV [11]:

$$\phi_s = 0.15 \pm 0.18 \text{ (stat.)} \pm 0.06 \text{ (syst.) rad,}$$

$$\Gamma_s = 0.657 \pm 0.009 \text{ (stat.)} \pm 0.008 \text{ (syst.) ps}^{-1},$$

$$\Delta \Gamma_s = 0.123 \pm 0.029 \text{ (stat.)} \pm 0.011 \text{ (syst.) ps}^{-1}.$$

These results also agree with SM predictions [12, 13].

#### 2.2 The limits of the Standard Model

In an energy range of up to several TeV the Standard Model describes physics very well as was shown in Section 2.1. Particles like the t-quark could be predicted and have been discovered<sup>3</sup>. Still there are many open questions which show the limits of the SM. Some examples are listed in the following.

The SM cannot explain the origin of the masses of the particles. One possibility which is not yet proven is the higgs mechanism. It describes how particles interacting with the higgs field obtain their masses. A hint for the validity of this mechanism is the higgs boson, an excitation of the higgs field. First measurements of a possible candidate of the higgs boson have been undertaken by the CDF and DØ collaborations with an excess around 120 GeV/ $c^2$  in July 2012 [14]. Furthermore, the ATLAS and CMS collaborations could also substantiate the theory of the higgs mechanism in July 2012. As a preliminary result for a possible higgs boson the ATLAS collaboration showed an excess at a mass of 126.5 GeV/ $c^2$  [15]. A new boson with a mass of 125.3 GeV/ $c^2$  was also observed by the CMS collaboration [16]. To prove that this new boson corresponds to the higgs boson, further measurements have to be accomplished in the next years of LHC data taking.

Another example for the incompleteness of the SM is the matter-antimatter asymmetry. According to the model of the Big Bang the universe contained an equal amount of matter and antimatter. This is based on the theory that fermions are always produced in particle-antiparticle pairs. Evidence for a deviation in matter-antimatter symmetry is the fact that we see matter in the universe. This excess of matter with respect to antimatter requires the violation of charge and parity conservation also known as CP-violation within the SM. In this theory particles and antiparticles do not decay in the same manner. But CP-violation within

$<sup>^3</sup>$ 1973 Makoto Kobayashi and Toshihide Maskawa predicted the t-quark and 1995 it was discovered at Fermilab at the CDF and DØ experiment [17, 18] .

the SM appears not to be large enough to explain the complete matter-antimatter imbalance. To explain the full asymmetry, physics beyond the SM has to be considered.

The observed flavour oscillations of neutrinos are also not described by the SM. This transmission stems from a very low but non-zero mass and is in conflict with the SM prediction where neutrinos are massless.

As explained in Section 2.1, three of the four fundamental forces, the electromagnetic, the weak and the strong force, are described by the SM. Only gravity is not included in the SM.

Furthermore, dark matter and dark energy cannot be explained by the SM. As it is estimated that most of the universe is made up of dark energy and dark matter and only 4% of visible matter there is still a high discovery potential in particle physics.

A possible theory of new physics which would also include the SM particles is Supersymmetry (SUSY). If realised it would provide a better unification of the couplings of the electromagnetic, weak and strong interaction and could give a dark matter candidate. The fundamental particles of SUSY do not only include the SM particles but also their SUSY-partner which are called sparticles. As these super-partners have a much higher mass than the SM particles discoveries of these are more likely to happen with much higher centre of mass energies than  $\sqrt{s}=8$  TeV.

## 3 Particle interaction with matter

To measure particles they have to interact with matter in a certain way. Depending on the type of particle, being charged or neutral, very heavy, light or even massless, it generates different signals in the detector material. The measured hits in tracker systems and the deposited energy in calorimeters can be used to reconstruct particle tracks and thus find the point of origin and the properties of the particles. The following chapter describes how particles interact with matter, see Section 3.1, gives an overview about detectors used in high energy physics, see Section 3.2, and leads to the use of silicon material as detector material, see Section 3.3. Finally, it describes the effects of high irradiation to silicon in Section 3.4.

#### 3.1 Fundamental interactions

To measure an incident particle it has to interact with the medium it traverses. This can be via bremsstrahlung, elastic and inelastic scattering or pair-production.

A particle is deflected from its original path by the electric field of a nucleus while traversing close by to it. Due to this deflection it radiates bremsstrahlung. The effect is proportional to the square of the inverse of the particle's mass:

$$\sigma \propto \left(\frac{e^2}{mc^2}\right)^2 \ . \tag{3.1}$$

Elastic scattering deflects the particle's track without energy loss inside the detectors. This leads to multiple scattering and is an unwanted effect in track reconstruction. To achieve as little energy loss by multiple scattering as possible it is very important to reduce this effect and as a consequence to avoid dense material inside the detector.

For particle detection the inelastic scattering is more relevant. Through this interaction the atoms of sensitive detector materials can be ionised and thus create electron-ion pairs. These charge carriers can move through the material. With an external electric field the initial charges can generate secondary charge carriers and thus enhance the number of ionised atoms. This can be measured by detector electrodes. The mean energy loss during ionisation and as a function of particle momentum is described by the Bethe-Bloch formula [19, 20]:

$$-\frac{dE}{dx} = 2\pi N_a r_e^2 m_e c^2 \rho \frac{Z}{A} \frac{z^2}{\beta^2} \cdot \left[ ln \left( \frac{2m_e \gamma^2 v^2 W_{max}}{I^2} - 2\beta^2 - \delta - 2\frac{C}{Z} \right) \right], \tag{3.2}$$

with the values described as follows:

$N_a = 6.022 \times 10^{23} \text{ mol}^{-1}$ : Avogadro's Number  $r_e = 2.817 \times 10^{-13} \text{ cm}$ : classical electron radius

$m_e = 511 \text{ keV}$  : electron mass

$ho = 2.33 \ {

m gcm^{-3}}$  : density of absorbing material silicon  $I \approx 173 \ {

m eV}$  : average effective ionisation potential

Z=14 : atomic number of absorbing material silicon [e] A=28 : atomic weight of absorbing material silicon [u]

$\begin{array}{lll} z & \propto {\rm e} & : {\rm charge\ of\ incident\ particle} \\ \beta & = v/c & : {\rm speed\ of\ incident\ particle} \\ \gamma & = 1/\sqrt{1-\beta^2} & : {\rm Lorentz\ factor} \\ \delta & : {\rm density\ correction} \\ C & : {\rm shell\ correction} \\ W_{max} \approx 2m_ec^2\beta^2\gamma^2 & : {\rm maximum\ energy\ exchanged\ during\ a\ collision\ of\ particles} \\ & & {\rm with\ } M \gg m_e \end{array}$

The Bethe-Bloch formula is not valid for electrons as here the main energy loss due to brems-strahlung has to be taken into account. This is not the case for particles with higher mass than the electron mass. Here bremsstrahlung has to be considered at much higher energies. For muons for example at an energy of about 1 TeV.

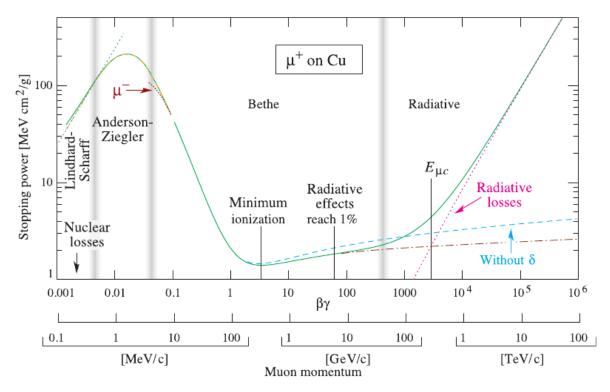

The functional behaviour of the Bethe-Bloch formula can be separated into three parts, see Figure 3.1. For the low energetic part the formula is dominated by the term  $1/\beta^2$  and leads to

**Figure 3.1:** The mean energy loss or stopping power of antimuons in copper described by the Bethe-Bloch formula as a function of  $\beta\gamma$  (solid curve). Additionally, the ranges for very low and very high stopping power where the Bethe-Bloch formula is not valid anymore is shown [6].

a decrease of the mean energy loss until a minimum for ionisation at  $v \approx 0.96~c$  with a mean energy loss or stopping power of 1.5 MeVcm²/g is reached. Particles having such velocity are therefore called minimal ionising particles (m.i.p.). The position of the minimum is dominated by the charge of the particles rather than the mass. This leads to the fact that most particles are considered as a m.i.p. At even higher energies the logarithmic part dominates and leads to a slow increase of energy loss.

The density effect  $\delta$  considers the polarisation of the atoms inside a material along the path of the incident charged particle. The electrons of the atom which have a higher distance to

the charged particle are thus shielded and do not feel the full charge of the incident particle. The shielding is even more effective if the material is denser. Therefore, the correction is called density effect. This decreasing energy loss is especially important for relativistic energies as the range of the transverse electric field increases as well. The density correction also leads to the saturation of the Bethe-Bloch formula at relativistic energies.

The shell correction C becomes effective if the velocity of the incident particle is very small. For the Bethe-Bloch formula without any corrections it was assumed that the electrons of the material's atoms are stationary with respect to the incident particle. This is not valid anymore if the incident particle has a velocity which is smaller than the velocity of the bound electrons of the atom.

At very low and very high values of  $\beta\gamma$  the Bethe-Bloch formula is also not valid anymore. A particle in the low energy range temporarily captures electrons on its way through the material. The particle then acts as a neutral particle. This effect of a changing charge of the incident particle is not taken into account in the Bethe-Bloch formula [21].

In a range of  $0.01 < \beta \gamma < 0.05$  the phenomenological description by Andersen and Ziegler predicts the mean energy loss quite well [22, 23]. For particles moving slower than  $v \approx 0.01c$  the gradient of the mean energy loss is explained by Lindhard-Scharff and is proportional to  $\beta$ . For even lower energies the main energy loss is caused by nuclear recoil [24].

The  $\mu^-$  in Figure 3.1 denotes the Barkas effect which points out the difference in stopping power between positive and negative muons [25].

At  $\beta\gamma > 1,000$  radiative losses mainly caused by e<sup>+</sup>e<sup>-</sup>-pair production and bremsstrahlung become dominant [26].

High energetic charged particles also lose energy due to Cherenkov-radiation and transition radiation. As only the latter effect is used in the frame of this thesis the Cherenkov-effect will not be described here. Transition radiation occurs as soon as a high energetic charged particle crosses the boundary between two media of different dielectric constants. The charged particle polarises the first medium while traversing it and thus produces an electromagnetic field. As soon as the particle reaches the next medium the field from one to the other medium has to change. To compensate for the continuous change of the electric field x-rays are emitted at the boundary layer of the two media [27].

As already stated, the Bethe-Bloch formula describes the mean energy loss of an incident charged particle. However, the functional behaviour of the actual energy loss is described by the Landau distribution. It takes the additional energy loss produced by the statistical fluctuations of further collisions into account. The latter is provoked by high energetic electrons which are knocked out of the atom due the initial incident particle. These  $\delta$ -electrons have such a high kinetic energy that they are able to ionise other atoms and evoke so called secondary ionisation [20]. To account for all energy losses except ionisation, for example phonon excitation, the Fano factor F is introduced. It determines the deviation of a fixed value of Energy E needed for creating N electron-hole pairs [28]. The fluctuation of the number of generated electron-hole pairs is described as

$$\langle \Delta N^2 \rangle = FN = F \frac{E}{w} . \tag{3.3}$$

For semiconductors and gases F < 1 is obtained [20, 29].

Due to energy loss electrons cover a certain distance through matter which is dependant on the number of nucleons inside a material and its density. After this so called radiation length  $X_0$  the energy of the particle is reduced to 1/e due to radiation and can be described by the

following formula:

$$X_0 = \frac{716.4 \,\mathrm{g \, cm^{-2}} \,A}{Z(Z+1) \ln(287/\sqrt{Z})} \ . \tag{3.4}$$

Z and A are the atomic number and nucleon number, respectively. High energy photons can loose their energy by pair-production in creating an  $e^+e^-$ -pair or due to the photoelectric effect and Compton scattering. The mean free path for such a photon is defined by:

$$\lambda = \frac{9}{7} X_0 \quad . \tag{3.5}$$

A corresponding relation for hadrons, for instance a proton, can be described by the nuclear interaction length:

$$\lambda_n = 35 \,\mathrm{g \, cm}^{-2} A^{1/3} \ .$$

(3.6)

#### 3.2 Particle detection

#### **Tracking Detectors**

On the basis of the particle interactions with matter, described in Chapter 3.1, properties like mass or momentum of the particles can be determined.

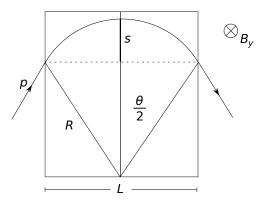

The momentum of charged particles can be measured by their bent trajectory inside a magnetic field  $\vec{B}$ . This can be done by calculating the sagitta of the curve. An explanation of this relation can be seen in Figure 3.2. The particle path can be described by connecting two points of the curve with a straight line of length L. The curve is a sector of a circle with an opening angle of  $\theta$  and a radius R. The deviation of a charged particle with momentum p flying in z-direction is thus sensitive to the y-component of the magnetic field  $B_y$  [30]:

$$s = \frac{eB_y L^2}{8p} (3.7)$$

To measure the curved trajectory of the charged particle a tracking detector is needed which is placed inside a magnetic field.

**Figure 3.2:** The curved track of a charged particle with momentum p in a magnetic field. The deflection angle  $\theta$ , the radius R, the length L and the sagitta s are shown.

Tracking detectors in current experiments are mainly made of solid state material, for example silicon, see Chapter 3.3. With such a sensor it is possible to gain a high granularity which leads

to a good position resolution. This is particularly important if the particle flux is high which is the case close to the interaction point. The resolution of the position x of a traversing particle can be calculated by

$$\sigma = \left[ \frac{1}{d} \int_{-d/2}^{+d/2} x^2 \, \mathrm{dx} \right]^{1/2} = \frac{d}{\sqrt{12}} , \qquad (3.8)$$

with d being the pitch of the sensor. In this formula a homogeneous distribution of the particle flux between -d/2 and +d/2 is assumed. If not only the hit information of the single hit is used but the additional charge distribution within a cluster is available, the resolution can even be increased.

A magnet surrounding the tracking detector can be used to deflect a charged particle by the Lorentz force:

$$\vec{F} = \pm e(\vec{E} + \vec{v} \times \vec{B}) . \tag{3.9}$$

With measuring this curved trajectory the momentum p can be determined.

#### Calorimeters

The energy of particles is measured in so called calorimeters. Electrons, positrons and photons are measured in electromagnetic calorimeters, whereas hadrons are measured in hadronic calorimeters. Both are explained in the following.

Electrons have to penetrate a material with high atomic number to highly interact with it. A sequence of e<sup>+</sup>e<sup>-</sup>-pair-production and bremsstrahlung induced by a high energetic particle initiates an electromagnetic shower. Finally, only low energetic electrons and photons are left which mainly loose their energy due to ionisation and are thus fully absorbed by the calorimeter. A scintillator directly placed at the absorbing material measures the energy of all shower particles which is equal to the energy of the primary particle. Photons are measured in a similar way.

Knowing the radiation length  $X_0$  for charged particles, see Equation 3.4, the optimal size of such a calorimeter can be determined. Two possible setups are used in high energy physics: a sampling and a homogeneous calorimeter. A sampling calorimeter consists of alternating layers of a dense material with high atomic number, lead or steel, and a sensitive material like a scintillator. A homogeneous calorimeter consists of crystals with a high atomic number which serve as absorber and sensitive material at the same time. To receive a measurable quantity, photomultipliers convert the energy of the photons received by the scintillator or the crystal into a current.

The longitudinal distance of electromagnetic showers is dominated by the high energy of the initial particle. To determine the transversal behaviour the Molière radius is used:

$$R_M = 21 \text{ MeV } \frac{X_0}{E_c} ,$$

(3.10)

with  $E_c$  as the critical energy which defines the energy at which the ionisation loss per radiation length is equal to the initial electron energy [27].

To fully absorb hadronic particles with a calorimeter a denser absorber material than in the case of an electromagnetic calorimeter is needed. This can be explained by the longer hadronic radiation length  $\lambda_n$  stated in Equation 3.6. Charged hadrons can ionise the absorber nuclei or interact with it through the strong interaction. If an inelastic scattering process occurs secondary particles like charged or neutral pions or  $\eta$ -mesons are produced. The final state products are again photons and charged particles which can be measured in a similar way as it is done at electromagnetic calorimeters. Because of excitation and spallation processes inside the absorber

material some of the energy of the original particle stays inside the absorber and thus cannot be fully measured by the sensitive material. Iron and copper are suitable for the absorber material. The sensitive material may be scintillators or liquid ionisation chambers.

With the energy E deposited in calorimeters the particle's mass m can be calculated according to

$$E = \sqrt{(mc^2)^2 + (pc)^2} . (3.11)$$

#### Muon detector

A common particle detector consists of several layers of subdetectors so that a generated particle first traverses a tracker system and deposits its full energy inside the calorimeters. Only muons and neutrinos are able to traverse both tracker and calorimeters completely due to their low interaction cross sections. As the neutrino is not even charged it also traverses the Muon detector without being measured. As the muon is charged tracking detectors are used to detect the muon's track via ionisation loss at this part of the detector. Muon chambers are often made up of drift chambers. These consist of a gaseous volume, mostly argon, containing an anode wire. At the outer region the cathode wires are arranged.

#### Particle identification

With the above mentioned detectors energy, momentum and as a result the mass of a particle can be determined. Because particle detectors are often built as a  $4\pi$ -detector the collision point of two colliding particles can be completely surrounded. Thus, all final state particles of one collision event have to penetrate through the detector layers and can be measured. As the neutrino is not directly measured by any of the described detectors only its missing energy after a full event reconstruction can be calculated. Due to momentum conservation the sum of the transversal momentum  $\sum p_T$  of all measured particles in a  $4\pi$ -detector has to be zero. A deviation from this value therefore indicates that a particle traverses the detector without being measured. This is the case for a neutrino.

With a complete event reconstruction the physics processes occuring during such a collision can then be determined. An example of a  $4\pi$ -detector is the ATLAS Detector explained in detail in Chapter 4.2.

#### 3.3 Silicon as sensitive detector material

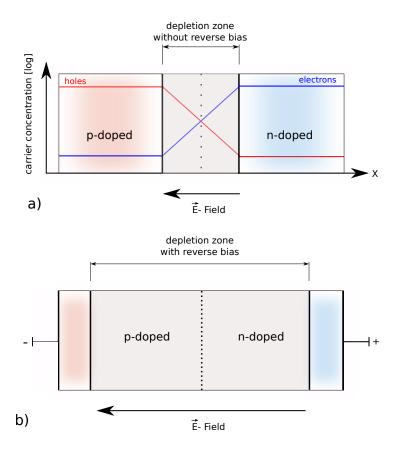

Crystal silicon is a good material used for tracking detectors. It has a small band gap and is a semiconductor which can therefore be depleted. Hence, it is suitable for detecting traversing charged particles as explained in the following. The sensor is made up of two differently doped areas. An n-doped area has implemented atoms with one more electron than silicon which are called donors. In case of silicon a donor would be phosphorus or arsenic. In contrast a p-doped area has an implemented atom with an electron less which is called acceptor. In case of silicon an acceptor would be boron. To establish an equilibrium state the free charge carriers drift to the oppositely doped area and built a space charge region, see Figure 3.3. In addition, an electric field opposite to the field between the doped areas arises. This zone is also called depletion zone because no free charge carriers are present.

If an external reverse voltage is applied to this pn-junction the space charge region expands. Is the reverse bias high enough, the doped areas are fully depleted and do not contain any free

Figure 3.3: a) The pn-junction without a reverse bias voltage. The coloured areas indicate the particular doped area in a non depleted state. They grey area is the depletion zone and contains no free charge carriers. b) The pn-junction with reverse bias voltage and increased depletion zone.

charge carriers. This bias voltage is called depletion voltage. The n- and p-doped areas together with an applied external electric field behave similar to a reverse-biased diode.

If a charged particle traverses this depletion area electron-hole pairs are created along the path of the incident particle and the generated free charge carriers can be measured. If no electric field is applied the electron-hole pairs would recombine immediately and thus do not contribute to the detector signal.

To determine the average number of electron-hole pairs N the absorbed energy E has to be divided by the average energy needed to create one electron-hole pair w which is 3.62 eV in silicon<sup>1</sup>. This is much higher than the band gap of silicon which is 1.12 eV. The excess of energy is transformed in lattice oscillations or phonons inside the silicon material and heats up the sensor. The fluctuation of the number of generated electron-hole pairs N is described by Formula 3.3. An electron or hole generated this way can be assumed to be a free charge carrier which can travel through the medium due to different effects. Diffusion occurs if there is a local excess of charge carriers inside the silicon material. This disequilibrium is compensated by moving charge carriers from one to the other excess region.

<sup>&</sup>lt;sup>1</sup>The creation of one electron-hole pair inside a gaseous detector is in the order of 20 eV.

More important for the detection of signals in silicon is the effect of charge drift. An external electric field accelerates the electrons and holes along the direction of the electric field  $\vec{E}$  and leads to a current per unit area:

$$\vec{J}_{n,drift} = -en\mu_n \vec{E} , \qquad \qquad \vec{J}_{h,drift} = en\mu_h \vec{E} . \qquad (3.12)$$

$\mu_n$  and  $\mu_h$  are the mobilities for electrons and holes, respectively. n is the carrier concentration and e the electron charge. The mobility depends on the temperature and the doping and impurity concentration of the material. Inside a high electric field the free charge carriers are accelerated until a saturation velocity is reached. The latter just depends on the mean free path or the mobility  $\mu$  inside the material. The applied voltage  $U_{\text{bias}}$  for particle detectors depends on the doping concentration and the sensor thickness and is slightly higher than the depletion voltage  $U_{\text{depl}}$ . This is done to establish a non-zero electric field at the electrodes which then can be reached by the drifting charge carriers. A common value for unirradiated sensors is  $U_{\text{bias}} = U_{\text{depl}} + U_{\text{a}} \approx 150 \text{ V}$ , in which  $U_{\text{a}}$  is the increase relative to the depletion voltage of about 30-50 V. While the charges are drifting due to the external electric field simultaneous diffusion causes a spread of the charges which is perpendicular to the direction of the electric field. This leads to charge sharing in which signal charges do not induce a charge on one pixel segment but on several ones.

In the presence of a magnetic field the carriers are deflected according to the Lorentz force described in Equation 3.9. The resulting deviation angle, or Lorentz angle  $\theta_L$ , can then be described via the Hall mobility  $\mu_{Hall}$ :

$$tan \theta_{L,n} = \mu_{Hall,n} B_{\perp} , \qquad tan \theta_{L,h} = \mu_{Hall,h} B_{\perp} .$$

(3.13)

$B_{\perp}$  is the magnetic field perpendicular to the velocity of the charge carriers. The Hall mobility can be described with the before mentioned mobility  $\mu_{Hall} = r\mu$ , with r being the Lorentz factor<sup>2</sup>. Due to the Lorentz angle, the charge sharing effect is increased. Thus, the Lorentz angle has an impact on the spatial resolution and the cluster size [31].

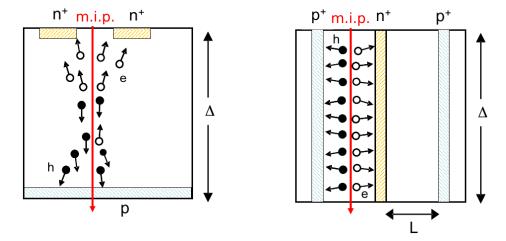

To realise a particle detector, n<sup>+</sup>-doped pixel implants are placed in the n-type bulk of the sensor, see Figure 5.3. As a result, an incident charged particle creates electron-hole pairs with the electrons being accelerated in the direction of the higher n<sup>+</sup>-doped implants on top of the sensor. The implants act as electrodes and measure an electrically induced signal according to Ramo's law while the electrons are moving towards them [32]:

$$i = E_v ev (3.14)$$

i is the current measured at the implant due to a single electron, e is the electron charge, v the velocity of the electron and  $E_v$  is the weighting field. A sensor with an n-bulk and n<sup>+</sup>-doped implants is called n<sup>+</sup>-in-n sensor and is used as sensitive material for the Pixel Detector discussed in this thesis. n<sup>+</sup>-doped implants provide a still n-doped area while the original n-doped bulk changed to a p-doped bulk at a certain radiation dose, see Section 3.4. A possibility to isolate the n<sup>+</sup>- and n-type zones from each other is the implementation of a p-doped zone called p-spray which is brought up between the two n-type zones [33]. Thus the implants are isolated in case the reverse bias is applied. Using such implants the granularity of a pixel detector can be very high. This is especially important for b-tagging as described in Chapter 5. Taking Equation 3.8 into account the resulting small distances, which are in the order of several  $\mu$ m, between the n<sup>+</sup>-doped implants yield a very good spatial resolution of charged particle's hits.

<sup>&</sup>lt;sup>2</sup>The Lorentz factor r is measured to be 1.15 for electrons and 0.72 for holes at a temperature of 0°C.

Electron-hole pairs can also be generated by thermal energy at the surface of the material or within the depleted bulk. This leads to a leakage current and is observable as noise when measuring a particle signal.

Applying a very high reverse bias voltage causes a so called breakdown in which a high leakage current occurs so that the sensor is badly damaged and signal detection is not possible anymore.

#### 3.4 The effects of radiation on silicon

Silicon has a crystalline structure which determines the behaviour of the material. This lattice structure as well as additional doping can be affected by a high radiation dose and hence change the behaviour of silicon. Due to these lattice defects of the material the efficiency in detecting particles decreases. The main effects causing such damages inside the silicon structure are explained in the following. Damages due to radiation can occur inside the sensor bulk and at the surface of the sensor. As the first is more crucial regarding the efficiency of particle detection merely defects inside the bulk are considered here.

A not reversible bulk damage is the displacement of a single silicon atom. For this a minimum energy of 25 eV is needed. This can be achieved by an electron with a minimal energy of 260 keV or a proton or neutron with a minimal energy of 190 eV. If the incoming particle has even more than the minimal energy the recoiling atom can induce further damage inside the sensor. With an energy of the silicon atom of more than 2 keV it can even damage a complete region inside the lattice and thus produce a cluster defect [28].

Point defects which come from radiation are for example silicon vacancies and interstitials. The latter are atoms inside the material which are not included inside the lattice structure but in between. Vacancies describe a missing atom inside the regular lattice structure. Depending on the temperature both defects can move through the lattice and may recombine with other defects. Still they can have an effect on the space charge inside the depletion region: They produce additional energy levels. If these are located inside the band gap of silicon the defects act as generation-recombination centres and increase the leakage current.

Another side effect of defects is charge trapping in which a signal charge is kept for a longer time than the usual charge collection time needed to produce the full signal. As a result, the final signal height measured at the electrodes is smaller than in an unirradiated sensor. After a dose of  $10^{15}$   $n_{\rm eq}/{\rm cm}^2$  the effect becomes relevant as about 50% of the signal will be lost due to charge trapping.

Moreover, charge defects have an impact on the reverse bias. To fully deplete the sensor after irradiation, a higher operation voltage is necessary. Hence, the leakage current increases and therefore the power dissipation is higher as well. This heats up the sensor which in turn leads to a higher leakage current. As a consequence, a higher operation power is needed which would again increase the leakage current. This cycle which further increases the operation voltage and the leakage current is called thermal runaway and makes the cooling of silicon inevitable.

Radiation also impacts the effective doping concentration. The ratio of donor- and acceptor-like states changes due to defects. Inside an n-type doped bulk the majority charge carriers are electrons which can be removed easier than holes inside a p-type bulk. Radiation damages thus alter the original n-type bulk to a p-type one. As a consequence of this type inversion the pn-junction moves to the n<sup>+</sup>-segmented pixel side and the growth direction of the depletion zone changes.

To describe the radiation damages independent of the particle type all deposited energy except the energy used for creating electron-hole pairs can be expressed by *Non-Ionising Energy Loss*

(NIEL). The NIEL caused by a certain flux of an arbitrary type of particle is normalised to the NIEL caused by 1 MeV neutrons. The unit is the neutron equivalent fluence  $n_{e\alpha}/cm^2$ .

Due to thermal energy defects are able to move through the sensor. To prevent this the sensors are cooled down in normal detector operation. If the sensor is exposed for several hours to higher temperature of about 30 to 60°C the annealing effect is increased. Differently charged defects can recombine due to thermal energy and become inactive. This is observable as the effect of trapping is decreasing after that time. In contrast, a longer annealing time of several weeks increases the effects of radiation damages. In this case the impact of defects in combination with higher temperature changes the crystal lattice in a more complex way. This effect is called reverse annealing [34]. Even in periods during which the sensor is not exposed to high radiation cooling is needed to avoid reverse annealing.

The described radiation damages have to be considered during detector operation with high irradiation and silicon as sensor material and lead to a necessary upgrade of the detector which is further explained in Chapter 6.

# 4 Experimental setup

## 4.1 The Large Hadron Collider

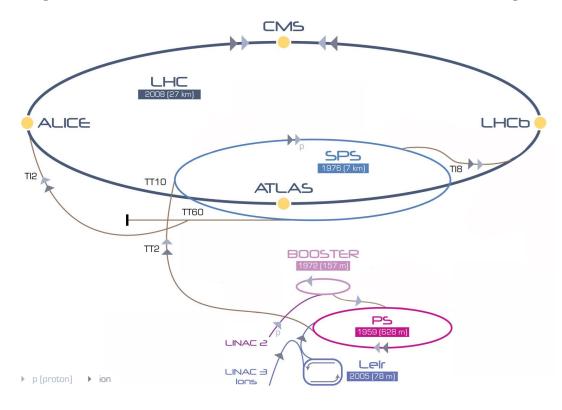

The Large Hadron Collider (LHC) is a proton-proton collider with a nominal centre of mass energy of 14 TeV and is located at CERN<sup>1</sup> in Geneva. A schematic drawing of the ring can be seen in Figure 4.1. The LHC is located inside a tunnel which is about 100 m underground and

*Figure 4.1:* A schematic of the LHC ring [35]. Shown are the pre-accelerators, the two proton injection points and the four main experiments ATLAS, LHCb, CMS and ALICE.

has a circumference of 27 km. It is built inside the former tunnel from the previous accelerator machine Large Electron-Positron (LEP) Collider which was in operation from 1989 until 2000.

With a complex system protons are injected into a subsequent order of different machines to accelerate the particles up to 7 TeV. The protons themselves are taken from a hydrogen bottle. After stripping off the electrons from the hydrogen the protons are accelerated up to an energy of 50 MeV by the 30 m long linear accelerator 2 (LINAC2). From there they are injected into the Proton Synchrotron Booster (PSB) and brought up to an energy of 1.4 GeV. In the following Proton Synchrotron (PS) and Super Proton Synchrotron (SPS) they are further accelerated to

<sup>&</sup>lt;sup>1</sup>Conseil Européen pour la Recherche Nucléaire

an energy of 25 GeV and 450 GeV, respectively. All three synchrotrons are circular accelerators with increasing circumferences of 50 m, 628 m and 7 km [36].

Finally, the protons are injected as bunches in two opposite directions into the LHC ring at the injection points TI 8 and TI 2 [37]. If the LHC is completely filled up each beam consists of 2808 bunches. Each bunch contains  $1.5 \times 10^{11}$  protons. With this setup every 25 ns a collision between two bunches takes place. This leads to a bunch crossing frequency of 40 MHz and determines the clock frequency for detector readout.

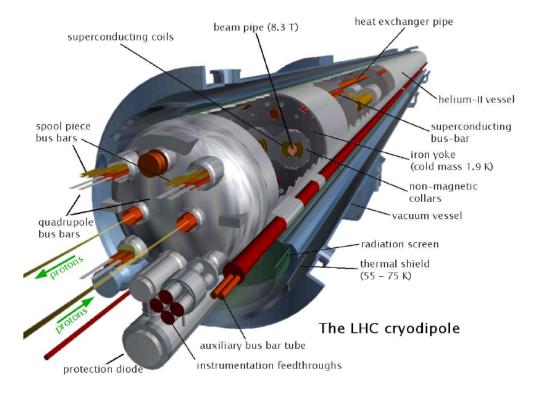

In the LHC the protons are accelerated by 16 cavities and focused with 858 quadropole magnets to counteract their electromagnetic repulsion. To keep the bunches on a circular track 1,232 dipole magnets are used. All these magnets are superconducting and have to be cooled down to temperatures of about 1.9 K. A drawing of a dipole magnet is shown in Figure 4.2.

Figure 4.2: A drawing of an LHC dipole [38]. The main elements are the two beam pipes which are enclosed by superconducting coils, a non magnetic collar and an iron yoke to gain a magnetic field of 8.3 T. To cool the superconducting magnets down to 1.9 K a helium-II vessel is used. An additional vacuum vessel surrounds the magnet and keeps an insulating vacuum [39]. Additionally, a heat exchanger and a thermal shield provide temperature compensation. Several bus bars interconnect the individual magnet elements.

The four main experiments making use of the collisions of the LHC are the ATLAS<sup>2</sup>-, CMS<sup>3</sup>, LHCb<sup>4</sup>- and ALICE<sup>5</sup> detectors. The first three mentioned record the data of proton-proton collisions.

<sup>&</sup>lt;sup>2</sup>A Toroidal LHC Apparatus

<sup>&</sup>lt;sup>3</sup>Compact Muon Spectrometer

<sup>&</sup>lt;sup>4</sup>Large Hadron Collider beauty

<sup>&</sup>lt;sup>5</sup>A Large Ion Collider Experiment

ATLAS and CMS are built as discovery machines: Both are  $4\pi$ -detectors which are sensitive to all detectable particles independent of their direction of flight. With up to 30 proton-proton collisions per bunch crossing ATLAS and CMS gain a high luminosity. The peak luminosity of both detectors is about  $6 \times 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> in August 2012 [40]. Having a flexible trigger system the produced particles and their decays can be analysed individually. These properties enable ATLAS and CMS to detect and analyse particles in different topics of high energy particle physics. More details about the ATLAS Detector can be found in Section 4.2.

The LHCb Detector only analyses one proton-proton collision per bunch crossing and thus has a better spatial resolution. Its main task are precise measurements in the field of b-quark physics.

Besides protons, also lead ions are collided inside the LHC which are especially analysed by the ALICE Detector. The aim of these heavy-ion collisions is the production of a quark gluon plasma and hence the generation of matter as it is thought of to be present in the early stages of the universe [41].

On 10th September 2008 the first proton beam circulated inside the LHC. Due to a mechanical damage which occurred during this event a long technical stop followed. The first proton-proton collisions took place on 23rd November 2009 with a centre of mass energy of 450 GeV. On 30th March 2010 the LHC started for the first 7 TeV collisions. Finally, the first 8 TeV collisions took place on 5th April 2012 and result in an already large amount of data.

A quantity to obtain the amount of data is the integrated luminosity. It is defined as the integration of the luminosity:

$$\mathcal{L}_{int} = \int \mathcal{L} \, dt = \int \frac{N_a \, N_b \, j \, v}{A \, U} \, dt, \qquad (4.1)$$

with  $N_a$  and  $N_b$  being the number of particles inside the storage ring, j the number and v the velocity of bunches, U the circumference of the storage ring and A the cross section of the beam during collision [42]. In 2011 the ATLAS Experiment reached an integrated luminosity of 5.6 fb<sup>-1</sup> with a centre of mass energy of 7 TeV. In 2012 the total integrated luminosity has already reached  $\sim 10 \text{ fb}^{-1}$  after the first half year of data taking with a centre of mass energy of 8 TeV.

## 4.2 The ATLAS Detector

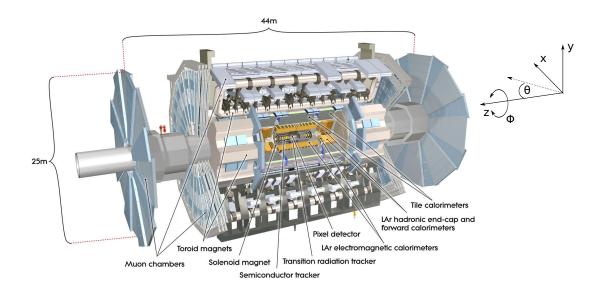

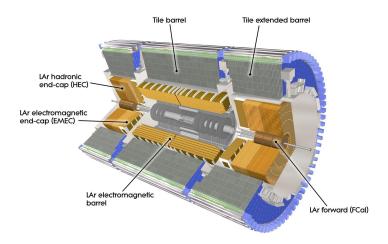

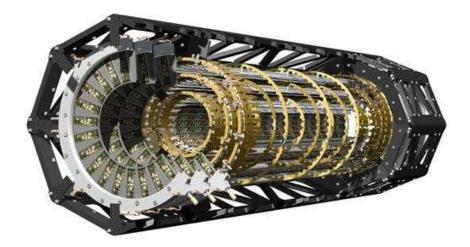

With a size of 42 m in length and 22 m in diameter the ATLAS Detector is the biggest of the LHC detectors. It is a  $4\pi$ -detector, meaning that the full solid angle surrounding the interaction point is completely covered by detector material. Thereby, it can be ensured that particles traversing from the interaction point towards the outer region are detected in any case. The detector consists of several subdetectors arranged in an onion-like structure as can be seen in Figure 4.3.

#### The Tracking Detectors

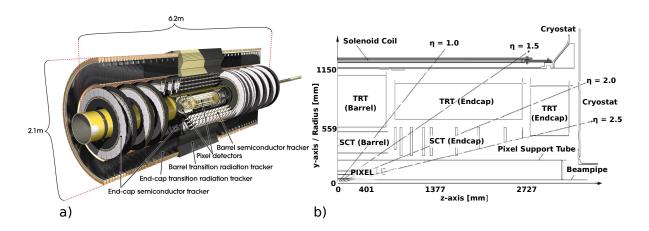

The innermost detector is the Inner Detector (ID) which is made up of the Pixel Detector, the Semi-Conductor Tracker (SCT) and the Transition Radiation Tracker (TRT). The complete ID is shown in Figure 4.4. All subdetectors of the ID are made for particle tracking purposes and as a consequence have a high spatial resolution. It is enclosed by a solenoid magnet with a central

Figure 4.3: The different layers of the ATLAS Detector [43]. The subdetectors and the ATLAS reference coordinate system are described. Two humans standing on the ATLAS radiation shield between the end cap Muon chambers give an imagination of the proportions of the ATLAS Detector.

magnetic field of 2 T. The outer radius of the ID is 2.1 m with a length of 6.2 m. The individual subdetectors are explained in the following in more detail.

The Pixel Detector is explained in Chapter 5 as this belongs to the main topic of this thesis. The SCT consists of silicon elements which are segmented into stripes with a size of  $80 \ \mu m \times 12.6 \ cm$ . Four barrels with radii of 30, 37.3, 44.7 and 52 cm cover a region<sup>6</sup> of  $|\eta| < 1.4$ . Two end caps each consisting of nine disks cover the region of  $1.4 < |\eta| < 2.4$ . In total there are 2,112 barrel modules and 1,976 end cap modules containing p-in-n stripe sensors [44]. Similar to the Pixel Detector the SCT experiences radiation damages due to an estimated flux of  $2 \times 10^{14} \ n_{eq}/cm^2$  after 10 years of operation [45].

The TRT is composed of drift tubes in which 52,544 axial tubes with a length of 150 cm are used for the barrel part and 319,388 radial tubes with a length of 39 cm to 55 cm build the end caps [46]. Each tube has a diameter of 4 mm and is filled with a gas mixture which mainly contains xenon and carbon dioxide. It consists of a 30  $\mu$ m gold-plated tungsten wire as anode as well as 60  $\mu$ m thick multi-layer film of carbon-polyimide as cathode [47]. The drift tubes are embedded inside a 15  $\mu$ m diameter polypropylene/polyethylene fibre radiator. A high energetic charged particle crossing the boundary between carbon dioxide and the polypropylene fibres or traversing the radiator itself then emits transition radiation as explained in Chapter 3.1. Besides the transition radiation, charged particles also directly ionise the gas inside the drift tubes. Measuring the time the produced electrons and holes drift from the point of ionisation towards the anode or cathode the path of the originating particle can be reconstructed. With these two effects traversing particles in an area of  $|\eta| < 0.7$  and  $0.7 < |\eta| < 2.5$  can be measured by the TRT barrels and end caps, respectively. A complete overview of the Inner Detector and its covered area is shown in Figure 4.4.

<sup>&</sup>lt;sup>6</sup>The pseudorapidity η is a spatial coordinate commonly used in  $4\pi$ -detectors and depends on the polar angle θ:  $\eta = -\ln[\tan\theta/2]$ .

Figure 4.4: a) A drawing of the three subdetectors of the ID [38]. b) The ID subdetectors Pixel Detector, SCT and TRT. Shown are the different layers and end caps of the detectors in the yz-plane of the ATLAS coordinate system. In the outer region the solenoid magnet coil is indicated. See Figure 4.3 for a description of the ATLAS coordinate system. Additionally, the corresponding pseudorapidity  $\eta$  and radius are shown [45].

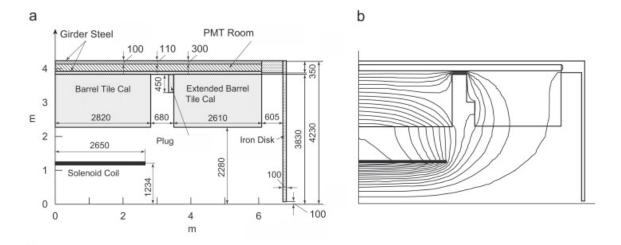

As already mentioned the ID is surrounded by a superconducting solenoid magnet, see Figure 4.4 b), providing a magnetic field of 2 T. The size of the bore is 2.3 m and the length is 5.3 m. To ensure that the solenoid interacts as little as possible with traversing particles it is made up of 44 mm thin high-strength aluminium [48]. Thus, a radiation length of 0.63  $X_0$  is achieved [49]. To return the magnetic flux of the solenoid the Tile Calorimeters are used, see Figure 4.5.

Figure 4.5: a) The solenoid magnet and the Tile Calorimeter. The ID and LAr Calorimeter are not shown in this drawing. The Tile Calorimeter is acting as return yoke for the magnetic field within the ATLAS xy-coordinate system. Further details of the Tile Calorimeter structure are explained in the text. b) The magnetic field lines within the detector components described in a) [50].

#### The Calorimeters

While the ID is mainly built for tracking the following calorimeters are important for measuring the energy of the particles. Right outside the solenoid the Liquid Argon (LAr) Calorimeter is placed. It consists of the LAr Electromagnetic Barrel and two end caps each containing the LAr Forward Calorimeter, the LAr Electromagnetic end cap and the LAr Hadronic end cap, see Figure 4.6. The barrel consists of 1.9 mm thick lead absorber layers with liquid argon as detecting medium in between [49]. The lead layers are arranged in an accordion structure to allow signal detection independent of the particle's incident angle. The barrel is 6.8 m long and covers a radius of 1.15 m < r < 2.25 m. It is placed inside an aluminium alloy with vacuum insulation. The end cap LAr Electromagnetic Calorimeter consists of an accordion structure, too. But here the amplitude of the accordion waves scales with the radius. Similar to the barrel an aluminium cryostat with vacuum isolation surrounds the end cap. The complete end cap has a length of 3.17 m and an outer radius of 2.25 m. The radial coverage of the complete electromagnetic LAr detector is  $|\eta|$  < 3.2.

The two wheels of the LAr Hadronic Calorimeter end caps have an outer radius of 2.03 m. They consist of two parallel copper plates as absorber which enclose Kapton electrodes. The spatial detection capability of the LAr Hadronic Calorimeter is  $1.4 < |\eta| < 4.8$ .

The LAr Forward Calorimeter is exposed to a high level of radiation and is therefore recessed by 1.2 m compared to the beginning of the LAr Electromagnetic end cap.

*Figure 4.6:* The complete calorimeter system of the ATLAS Detector. The grey area in the centre is the Inner Detector. Further out the LAr Calorimeter followed by the Tile Calorimeter are shown [38].

To measure hadronic particles the Tile Calorimeter builds the next subdetector layer. It uses steel plates as absorber. Due to its structure it is also called "girder steel" as referenced in Fig 4.5. As active material scintillating tiles placed in between the steel structure are used. Optical fibres transmit the light to photomultiplier tubes at the end of the calorimeter structure. The Tile Calorimeter is arranged in a 5.6 m long central barrel structure with an inner and outer radius of respectively 2.3 m and 4.2 m. In addition, there are two 2.9 m long extended barrels. The gap between the central and the extended barrel is used to lead the cabling of the ID and LAr Calorimeter out of the detector. The coverage of the central barrel is  $|\eta| < 1.0$  and for the extended barrels  $0.8 < |\eta| < 1.7$  [51].

#### The Muon Detector

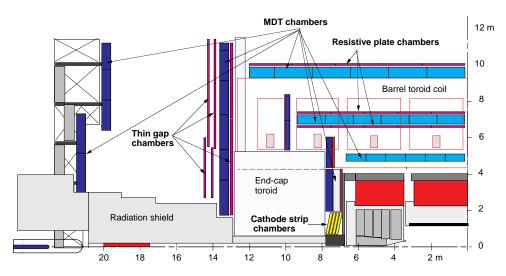

The outermost layer of the ATLAS Detector is the Muon Detector. At this point all particles except for muons and neutrinos already lost their energy within the previous detector layers. The Muon Detector consists of several subdetectors which use the detection principle of gas ionisation by charged particles. As a result, only muons are measured here. The subdetectors are especially built to provide a precise spatial resolution for track reconstruction or a precise time resolution for the trigger system.

The barrel region of the Muon Detector is built-up of three layers of Monitored Drift Tubes (MDTs) which are placed inside a toroidal magnetic field, see Figure 4.3 and Figure 4.7. The MDTs consist of drift tubes filled with a gas mixture mainly composed of argon. As anode a gold-plated tungsten wire is used. Three layers of MDTs are also placed inside the end cap. Thus they cover the main part of the Muon Detector with a pseudorapidity of  $|\eta| < 2.7$  and are mainly used for track reconstruction [52].

The MDTs are enclosed by Resistive-Plate Chambers (RPCs) which are used as a trigger unit. An RPC is made up of two parallel-plate electrodes which enclose a volume filled with tetrafluoroethane gas. To detect a signal metal strips with a width of 30 and 40 mm are placed orthogonal to each other on each plate [53]. The pseudorapidity coverage is  $|\eta| < 1$ .

Figure 4.7: A side view of one quadrant of the Muon Detector. The four subdetectors MDT, RPC, CSC and TGC can be seen as well as the area where the toroid coil is placed. The horizontal axis refers to the z-axis and the vertical axis to the y-axis of the ATLAS coordinate system, respectively [52].

The end cap layers consist of MDTs and Thin Gap Chambers (TGC). The latter is made up of two parallel graphite cathodes which enclose a gas volume of carbon dioxide and n-pentane ( $C_5H_{12}$ ). Multiple gold-plated tungsten wires between the two cathodes act as anodes. TGCs are used as triggering system similar to the RPCs and cover a region of  $1 < |\eta| < 2.4$ .

Close to the beam pipe the MDTs are replaced by Cathode Strip Chambers (CSC) to deal with the high radiation dose. The sensitive gas mixture contains argon and carbon dioxide. Anode wires of gold-plated tungsten and lithographically segmented cathode strips are used to measure the induced charge. The pseudorapidity range of the CSCs is  $2 < |\eta| < 2.7$ .

The magnet system of the muon spectrometer consists of three air-core superconducting toroids producing a magnetic field in the region  $0 < |\eta| < 2.7$ . The Barrel Toroid has a

length of 25 m and an inner and outer radius of 9.4 and 20.1 m, respectively. Its magnetic field peaks at 3.9 T. The two End Cap Toroids have a length of 5 m and an inner and outer radius of 1.65 and 10.7 m, respectively. Each of them has a magnetic field peak at 4.1 T. The complete magnet can be seen in Figure 4.3 and is also indicated in Figure 4.7 [54].

#### 4.2.1 The ATLAS trigger system

The LHC bunch crossing frequency is 40 MHz. Together with up to 30 possible proton-proton interactions per bunch crossing the event rate is about 1 GHz. To store the collision data on disk this event rate has to be reduced to a rate of 200 Hz. This can be achieved by a trigger system with three trigger levels.

The first-level trigger system uses information from the calorimeters and the Muon Detector to mark an event as special. Such a special event could for example be a higgs particle decaying into two Z-bosons: H  $\rightarrow$  ZZ  $\rightarrow$  2e + 2 $\mu$ . In this case the final decay products are two electrons and two muons. Thus two particle showers inside the electromagnetic calorimeter and two tracks inside the Muon Detector are detected. The first level trigger has a decision time of 2.5  $\mu$ s to reject or accept such an event and therefore reduces the event rate from 40 MHz to 75 kHz.

If an event is accepted a so called LV1 Accept signal is sent to all ATLAS subdetectors and the read out data is stored inside the buffers of the Read Out Subsystem (ROS). A more detailed description of the ROS can be read in the Data Acquisition hardware part of Section 5.5.

The second level trigger uses the data stored at the ROS. To decide if an event is rejected or accepted the second-level trigger uses limited information of so called regions of interest of all subdetectors. If an event is accepted it is further processed by the Event Builder which combines the fragments of the ROS to one event and sends it to the Event Filter. The event rate at this stage is 2 kHz.

Finally, an Event Filter reduces the data to a rate of 200 Hz so that it can be stored on disk. It uses the full detector information beyond the region of interests mentioned in context with the second-level trigger.

# 5 The current ATLAS Pixel Detector

The Pixel Detector is the innermost layer of the ATLAS Detector and is shown in Figure 5.1. It consists of 1,744 Pixel Modules arranged in three barrel layers at radii of 5.05 cm, 8.85 cm and 12.25 cm and three end cap disks at z = 49.5 cm, 58 cm and 65 cm on each side. It covers a pseudorapidity region of  $|\eta| < 2.5$  [55].

Each Pixel Module is a hybrid assembly made up of a particle detecting sensor area and an electronic readout area and is further described in Chapter 5.1. If a charged particle traverses the Pixel Detector a three dimensional hit information is recorded by measuring the z-position along the beam axis and the  $r\phi$ -position<sup>1</sup>.

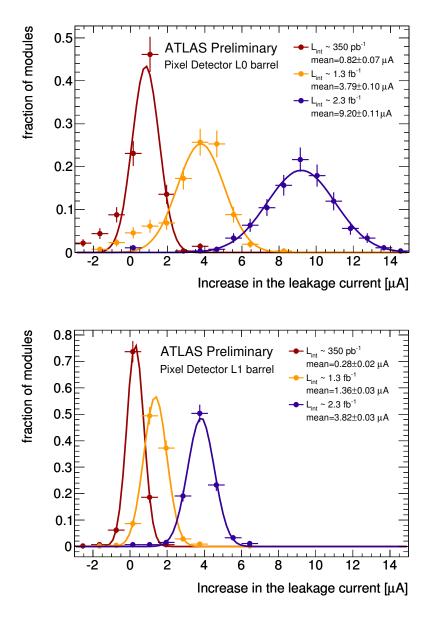

Due to its close proximity to the interaction point, especially the innermost layer is very important in vertex reconstruction for b-quarks, see Section 3.2 and below. This decay vertex is important to be measured as precisely as possible as it is used for b-tagging and is thus called "Layer 0" or "B-Layer". The central barrel layer is called "Layer 1" followed by "Layer 2" as the outermost layer.

To receive the hit information of each single pixel, roughly 80 million channels are handled by the ATLAS Pixel readout chain as explained in Chapter 5.2. A special role in data distribution and data handling is taken by the Read Out Driver (ROD) which is explained in more detail in Chapter 5.3. For communication with the front-end chip of the module the Digital Signal Processor (DSP) placed on the ROD is important. A general description of the DSP and its tasks is given in Chapter 5.4.

To integrate the Pixel Detector into the ATLAS Detector software environment the Pixel Detector specific software PixelDAQ is connected to the ATLAS Trigger and Data Acquisition (TDAQ) software. Using this software framework the whole Pixel Detector can be controlled and configured. More details can be found in Chapter 5.5.

Figure 5.1: Schematic view of the ATLAS Pixel Detector [56].

<sup>&</sup>lt;sup>1</sup>For an explanation of the ATLAS coordinate system see Chapter 4.2.

## **B-tagging**

Quark transitions due to the electroweak interaction are described by the Cabibbo-Kobayashi-Maskawa-mechanism (CKM-mechanism). The probability of the transformation between the different quarks is described by the CKM-matrix [6, 57]:

$$\begin{pmatrix} d' \\ s' \\ b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix} = \begin{pmatrix} 0.97 & 0.23 & 4.15 \times 10^{-3} \\ 0.23 & 1.01 & 40.9 \times 10^{-3} \\ 8.4 \times 10^{-3} & 42.9 \times 10^{-3} & 0.89 \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix}. \quad (5.1)$$

The probability of one quark decaying into another one is proportional to  $|V_{ij}|^2$ . The diagonal terms of the matrix are  $V_{ii} \approx 1$ . Thus the transition between quarks of the same generation is higher than between quarks of different generations.

The b-quark is the second heaviest quark with a mass of 4.91 GeV [58]. Its decay into the lighter u- or c-quarks is suppressed by the CKM-mechanism. As the t-quark is approximately 35 times heavier than the b-quark this transition is suppressed as well. Hence it follows, that the lifetime of mesons containing at least one b-quark is in the range of ps [59]. This leads to a distance of flight of up to  $\sim 7$  mm from the collision point and can be measured by particle detectors which are located close to the interaction point [60].

The measurement of the decay vertex of the b-quark is called b-tagging and is important for e.g. jet-reconstruction or general b-physics. This requires precise tracking detectors which are located as close as possible to the interaction point.

#### 5.1 The ATLAS Pixel Module

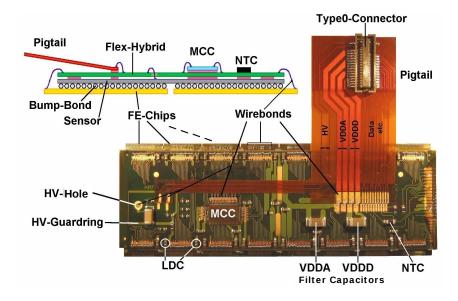

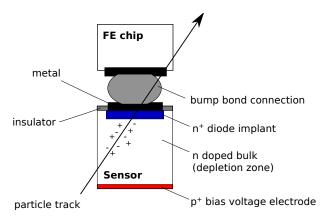

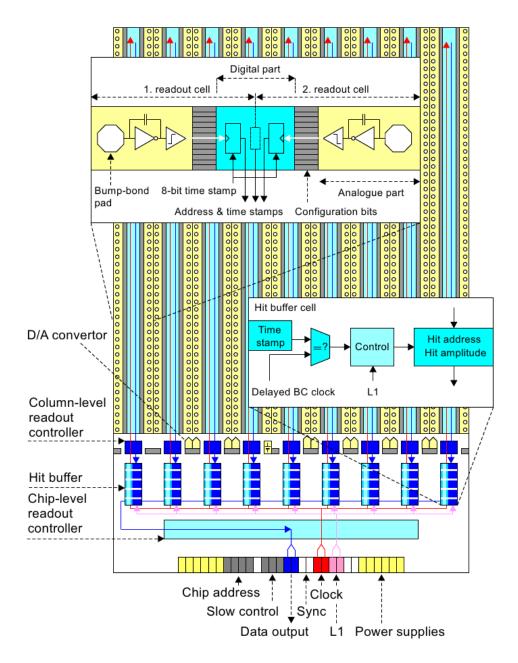

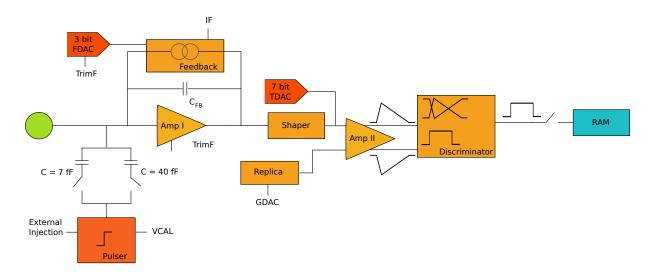

Each module consists of a particle detecting sensor and an electronical readout part, the so called front end (FE) chip, as can be seen in Figure 5.2. The sensor has a total size of  $63~\mathrm{mm}\times18.6~\mathrm{mm}$ , a thickness of 250  $\mu\mathrm{m}$  and is subdivided into several pixels. It is further described in Chapter 5.1.1. The electronical readout part is made up of 16 Front End-I3 (FE-I3) chips, one of each keeping 46,080 electronical readout circuits. With this setup almost each pixel cell of the sensor material is connected to its own electronical cell via a lead-tin bump bond connection and the analogue signal of the silicon material can immediately be digitised on the module, see Figure 5.3. The Front End chip is described in more detail in Chapter 5.1.2.

The signals of all 16 FE-I3 chips are fed into the Module Control Chip (MCC) which transmits them to the off-detector side. To connect FE chips and MCC a flexible Kapton foil with wirebonds, a so called "Flex-Hybrid" is used. The Kapton pigtail directs power and signal lines from the Type-0 connector to the Flex-Hybrid [61]. There are power supplies for the on-chip analogue and digital electronics which both are filtered by ceramic capacitors at the entry points of the external power lines. Local Decoupling Capacitors (LDC) are used for each supply between every FE pair.

To connect the HV<sup>2</sup>-line from the top of the Flex-Hybrid to the backside of the sensor a HV-Hole via with wirebond is used. A HV-Guardring surrounds the HV area to isolate this voltage lines from the remaining part of the Flex. Finally, an NTC<sup>3</sup> ceramic thermistor measures the temperature of the module.

<sup>&</sup>lt;sup>2</sup>High Voltage

<sup>&</sup>lt;sup>3</sup>Negative Temperature Coefficient

Figure 5.2: The ATLAS Pixel Module.

#### 5.1.1 The sensor material

The Pixel sensor is an n-in-n type sensor as described in Chapter 3.3. It is made up of 250  $\mu$ m thick diffusion-oxygenated float-zone silicon to improve the radiation hardness [62]. The sensor

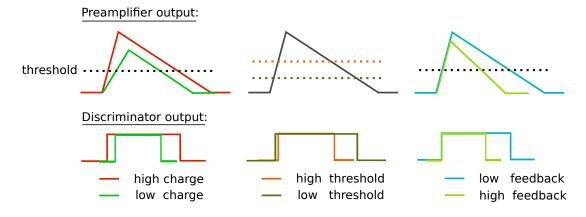

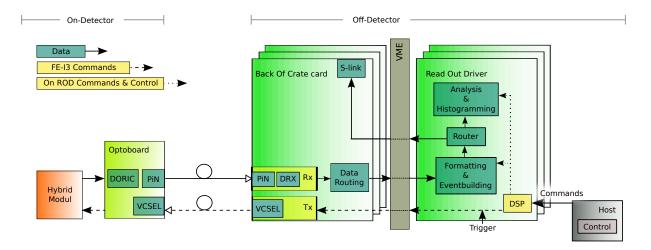

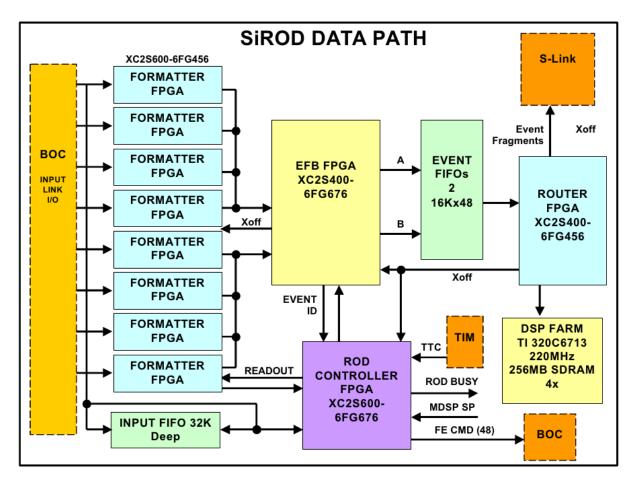

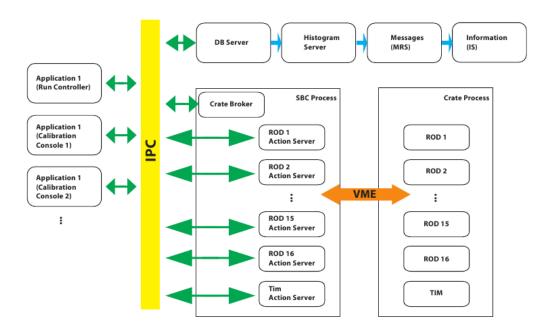

Figure 5.3: A schematic of the sensor pixel cell connected to the FE chip with a bump bond connection. If a reverse bias voltage is applied the sensor is completely depleted.