#### FIRST-LEVEL TRIGGER SYSTEMS FOR LHC EXPERIMENTS

I. Brawn, R.E. Carney, A. Connors, J. Garvey, D. Grant, R. Harris, S. Hillier, P. Jovanovic, I. McGill, D. Rees, R. Staley, A. Watson, P.Watkins School of Physics and Space Research, University of Birmingham, UK

O. Buyanov, A. Corre, N. Ellis<sup>\*</sup>), Ph. Farthouat, C. Jacobs, G. Schuler, H. Wendler *CERN, Geneva, Switzerland*

P. Hanke, A. Hoelscher, M. Keller, E.-E. Kluge, A. Mass, K. Meier, B. Rensch, M. Wunsch Institut für Hochenergiephysik der Universität Heidelberg, Germany

> P. Bodö, H. Hentzell, R. Sundblad, C. Svensson, J. Yuan Linköping University, Sweden

J. Fent, H. Oberlack, P. Schacht Max-Planck-Institut für Physik, Munich, Germany

E. Eisenhandler, M. Landon, J.M. Pentney, G. Thompson Queen Mary and Westfield College, University of London, UK

B. Green, J. Strong Royal Holloway and Bedford New College, University of London, UK

E. Gennari, A. Nisati, E. Petrolo, G. Piccinelli, S. Veneziano, L. Zanello Istituto Nazionale di Fisica Nucleare and Universita La Sapienza, Rome, Italy

R. Cardarelli, A. Di Ciaccio Istituto Nazionale di Fisica Nucleare and Universita Tor Vergata, Rome, Italy

J. Dowdell, J. Edwards, C.N.P. Gee, A. Gillman, R. Hatley, J. Leake, G. Lewis, V. Perera, S. Quinton, T. Shah *Rutherford Appleton Laboratory, UK*

C. Bohm, M. Engström, S. Hellman, S-O. Holmgren, E. Johansson, K. Prytz, N. Yamdagni, X. Zhao Stockholm University, Sweden

W.H. Smith, S. Dasu, C. Foudas, M. Jaworski, J. Lackey, D. Panescu, W. Temple University of Wisconsin, Madison, Wisconsin, USA

(\*) Spokesman

## **1. Introduction**

The RD27 project [1] was approved in June 1992 [2] to perform a broad-based study of firstlevel trigger systems. The progress of the project was reported in Summer 1993 [3] and in January 1995 [4]. Continuation of the project for a further year was approved [5] with the following milestones:

- Beam tests of a second-generation muon-trigger processor incorporating a coincidencematrix ASIC.

- Beam tests of bunch-crossing identification logic for the calorimeter based on FPGAs, using a new FADC system.

- Evaluation of key components of the central trigger processor in gate arrays.

- Development of demonstrators for key components of calorimeter trigger processors including evaluation of:

- fast optical links and integrated optics;

- fast electrical data transmission between boards and crates;

- fast high-density processing ASICs.

- Submission of a bit-serial demonstrator ASIC to a manufacturer.

Members of RD27 are very active in ATLAS [6] and CMS [7]. In particular, design work for the ATLAS calorimeter, muon and central trigger processors, and for the CMS calorimeter trigger processor, is being performed by RD27 groups. Members of RD27 (N. Ellis and W. Smith) are the trigger coordinators for the two proposed LHC experiments.

Given that the approval process for ATLAS and CMS is now well advanced, much of the work that was started within RD27 is now organised and funded by the LHC experiments. However, there are a number of areas where we consider that continued collaboration for one more year within RD27 will be valuable:

- High-speed, synchronous data links for transmitting data to trigger processors.

- High-speed custom backplanes for inter-module communication within trigger processors.

- Assessment of FPGAs as components for trigger processors, especially in the central trigger processor where the number of processing units required does not justify a custom circuit development.

- Evaluation of alternative ASIC technologies and designs.

All of the above are continuations of ongoing work. The results obtained will allow both ATLAS and CMS to benefit from a broader assessment of these items than would otherwise be possible. The use of resources will be optimised because R&D will not be duplicated in the two experiments, and some sharing of specialist test facilities may be possible. It is possible that, as a result of this collaboration, the two experiments will adopt common solutions within their trigger systems.

In this document we report on the work that has been performed and propose a programme of R&D for the next 12 months. It is our intention to complete the programme of work of RD27 in the coming year, after which we will submit a final status report documenting our work. In the longer term, we plan to continue to hold regular meetings between first-level trigger experts from ATLAS and CMS to promote the exchange of ideas and adoption of common

solutions where appropriate. In the following, we discuss in turn the muon, calorimeter and central trigger processors, and suggest milestones for the coming year. In each section, we indicate whether any continuation of the work is part of the proposed RD27 R&D programme, or whether it will be pursued within the ATLAS and CMS trigger projects.

# 3. Muon Trigger

The programme of work on the muon trigger processor, proposed in our last status report [4], was successfully carried out. A demonstrator system, incorporating a coincidence-matrix ASIC, was tested at the H8 test beam using signals from RPC detectors. More details of this work were reported [8] in the recent LERB workshop in Lisbon.

#### Programmable coincidence matrix ASIC

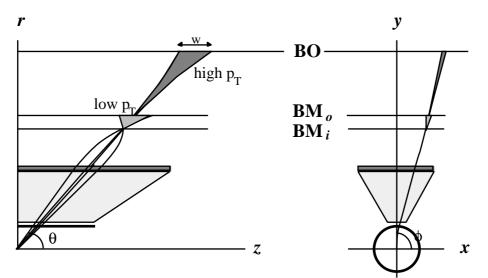

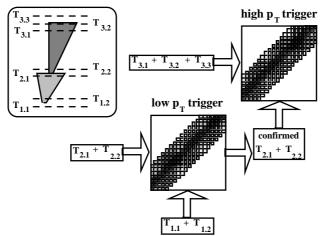

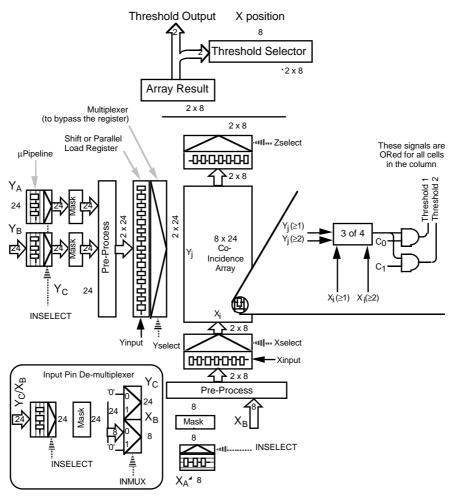

The coincidence-matrix ASIC [9] was developed by Rome with help from the RAL electronics group. It consists of 8×24 elements, each of which can be programmed for two independent coincidence conditions corresponding to different  $p_T$  thresholds. The ASIC can operate in two modes, corresponding to the low and high- $p_T$  muon trigger conditions in ATLAS (see Figs. 1 and 2). In the first mode it requires a three-out-of-four multiplicity in a pair of chamber double layers; in the second mode it requires a two-out-of-three multiplicity in a chamber triplet, in coincidence with the output from the low- $p_T$  logic.

The ASIC can be operated in fully-combinatorial mode which offers excellent time resolution for the trigger condition, with possible application for rejecting background on the basis of the time-of-flight between muon chamber layers. It can also be operated in pipelined mode, in which case the input signals can be delayed by a programmable number of clock cycles to compensate for different propagation delays upstream of the trigger logic; the delays for the *X* and *Y* inputs are programmable independently.

The ASIC was implemented in a 0.5  $\mu$ m CMOS gate array from Fujitsu (34k gates). The measured maximum skew is 1.8 ns, and the device can operate at clock speeds up to 130 MHz giving good time resolution even when operated in pipelined mode. A block diagram of the ASIC is shown in Fig. 3.

Figure 1: Conceptual design of the first-level muon trigger for ATLAS.

Figure 2. Muon trigger local logic for one projection. The symbols  $T_{i,j}$  refer to trigger chamber layers located at different points in the spectrometer. The inputs to the two axes of the coincidence-matrix circuits are the patterns of hits in the different chamber layers. The matrix is programmed to identify combinations of hits that correspond to valid tracks for the different  $p_T$  thresholds.

Figure 3: Block diagram of muon-trigger demonstrator ASIC.

#### Second-generation muon-trigger processor demonstrator

A muon-trigger processor demonstrator was implemented by the Rome group based on the coincidence-matrix ASICs. VME modules were manufactured, each supporting one ASIC.

Inputs to the ASICs arrive via front-panel connectors using ECL differential signals. The output signals leave the modules also via front-panel connectors using ECL differential signals. This modular system allows the ASICs to be configured in different ways to implement the so-called low- $p_T$  and high- $p_T$  trigger logic. Inputs to the system were discriminated signals from the muon-trigger chambers.

#### Beam tests at H8 test beam

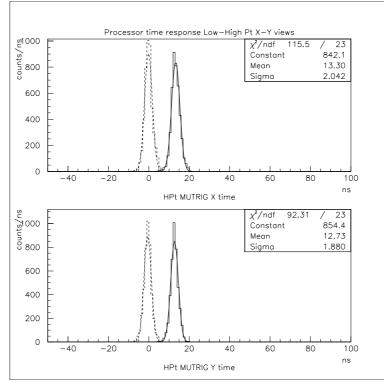

A total of eight of the demonstrator modules described above were used to implement a trigger at the H8 test beam, using signals from RPC chambers. The "trigger tower" measured about 50 cm by 50 cm, with seven layers per projection in a similar arrangement to the one planned for ATLAS. The system worked as expected, with excellent time stability (~2 ns) and low latency (about 30 ns in total, 15 ns for the low- $p_T$  trigger condition and a further 15 ns for the high- $p_T$  one), as illustrated in Fig. 4.

Figure 4: Real-time performance of the muon-trigger demonstrator prototype. The upper plot shows the time distribution of the output of the low- $p_T$  (dashed curve) and high- $p_T$  (solid curve) logic, for the *x*-coordinate RPC strips. The lower plot shows the same distributions for the orthogonal *y* projection.

During 1996 it is planned to use the same system to make tests with full-area trigger chambers, as part of the ATLAS first-level trigger project. This work will address the problems of synchronisation over large areas, making use of standard (RD12) TTC components when available.

### 3. Calorimeter Trigger

A large amount of work has been performed in the last year relating to the calorimeter triggers for ATLAS and CMS. Some of this work was reported at the recent LERB workshop in Lisbon [10–14]. As an aside, it is interesting to note that a substantial fraction of the work is being carried out following a formalised quality system based on ISO9001 [15].

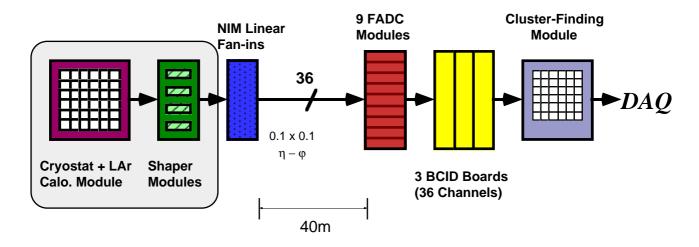

#### New FADC system

An ADC system has been constructed by the Heidelberg group for use in tests of calorimeter trigger processors. Each FADC board is a standard VME module containing four channels with 8-bit resolution. An external clock input allows sampling rates of more than 80 MHz. The key feature is the front-panel output of digitised data in real time to the subsequent trigger logic. So far 12 ADC modules have been built, and 11 more will be constructed.

In addition to the ADC function, each channel is equipped with a scrolling memory which records the most recent 256 samples. This memory can be read out when digitisation is stopped by a gate signal. The memory is read/write accessible from VME, and the modules can be used in "playback" mode in order to test the subsequent trigger logic.

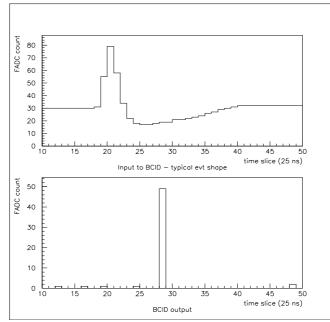

A detailed description of the FADC module can be found in Ref. [16]. An example of a recorded pulse from a prototype liquid-argon calorimeter is shown in the upper plot of Fig. 5.

Figure 5: Example of calorimeter pulse recorded with the ADC system. The upper plot shows the pulse as recorded by the FADC system. The lower plot shows the output of the real-time bunch-crossing-identification processing.

The new FADC system has been used to test prototype trigger systems, sending the data over a differential-ECL crate-to-crate link. This work will continue within the ATLAS first-level trigger project.

#### Bunch-crossing identification studies at the test beam

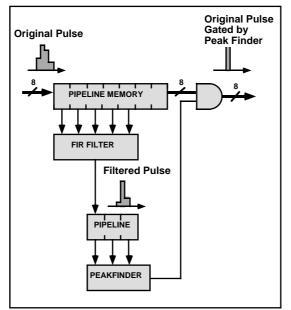

Given that the response time of calorimeters at LHC will be longer than the 25 ns interval between bunch crossings, it is necessary to perform bunch-crossing identification (BCID)

processing. Digital signal-processing algorithms are being studied in RD27 that convert a calorimeter pulse that spans several ADC samplings to a signal that appears only in a single time bin, corresponding to the bunch crossing that gave rise to the energy deposition. The algorithms that have been implemented consist of a finite impulse response (FIR) filter, followed by a peak finder, as illustrated in Fig. 6.

Figure 6: Block diagram of BCID logic.

In our last status report, we reported on initial studies with a single-channel demonstrator prototype based on discrete logic. During the last year, the UK groups have implemented a multi-channel demonstrator prototype based on FPGAs. Each 9U module handles 12 channels of 8-bit input data from the ADC system described above; each of three FPGAs handles BCID processing for four channels. In addition to the work with FPGAs, a first ASIC implementation of a four-channel BCID processor has been implemented by the Heidelberg group. The ASIC was designed so that it could replace the FPGA processing elements in the demonstrator system by using an adapter board.

Bunch-crossing identification has been successfully performed on calorimeter signals in real time using the FPGA system programmed with various algorithms, and using the ASICs. The test-beam setup is illustrated in Fig. 7. An example of the output from the BCID demonstrator is shown in the lower plot of Fig. 5. Good efficiency is obtained for energies above about 2 GeV, which is adequate for triggering at LHC. Work is continuing to optimise algorithms for very small and very large pulses. More details on the BCID studies can be found in Refs. [11, 14]. This work will be continued as part of the ATLAS first-level trigger project.

### Studies of fast input data links

A major challenge for the calorimeter trigger processors of ATLAS and CMS is the data rate into these systems. With about 8000 8-bit words of input data per 25 ns period, the total data rate is 2560 Gb/s to which must be added the overheads associated with framing, error detecting codes, etc. Special requirements for the first-level trigger are synchronous links with fixed low latency. In the Technical Proposal designs, both experiments assume ~ 1 Gb/s links each carrying data for two trigger cells; both experiments consider the possibility of using the HP G-link chipset (HDMP–1012/1014).

Figure 7: BCID evaluation system used in 1995 test-beam running

A number of developments are in progress within RD27 related to the fast data links. We are looking at the possible use of serial electrical links as an alternative to optical ones in case the digitisation system is placed in close proximity to the trigger processor.

An evaluation is currently being made of optical links using the HP G-link chipset and Finisar optical transmitter/receiver modules (FTM-8510 and FRM-8510). Demonstrator modules designed at RAL for the BaBar experiment were modified to operate in simplex mode for this work, and preliminary tests have been made running the links at 75 MHz with 20-bit frames and at 80 MHz using 16-bit frames. Initial results are encouraging and of considerable significance as they open the possibility of transmitting data from four, instead of two, trigger cells per link, with important implications for the cost of trigger systems.

An alternative to using the HP G-link chipset would be a custom solution making use of the availability of a common 40 MHz clock at the transmit and receive ends of the data links. This approach is addressed by the bit-serial test ASIC development discussed below.

Commercial optical/electrical components and chipsets tend to be physically quite large. Our application is unusual in the requirement to bring tens or even hundreds of optical fibres onto individual circuit boards. This has led us to consider novel solutions such as integrated optics and multi-chip modules (MCMs) containing unpackaged components (e.g. unpackaged G-link circuits).

During 1996, initial studies of the input data links will be made using a modular demonstrator system with discrete optical/electrical conversion and serial/parallel conversion components mounted on a daughter-board. However, provision has been made to include an MCM containing optical/electrical conversion and serial/parallel conversion at a later stage. A decision to proceed with an integrated-optics MCM awaits a choice within ATLAS on the location of the trigger digitisation system, in view of the significant non-recurring engineering cost and funding limitations.

While we have not yet manufactured an integrated-optics MCM, detailed design studies have been made for a four-channel circuit, including extensive consultation with industry. The result of these evaluations is that such circuits are feasible, and several companies have offered to build them. We also have recently contracted GEC-Marconi to perform a technology evaluation for a higher-density integrated-optics system.

In view of the common interest of the LHC experiments, it is proposed to continue this work during 1996 within the RD27 project.

#### Studies of high-speed backplanes

Studies are under way for high-speed custom backplanes for inter-module communication. The Wisconsin group and UK groups have designed 160 MHz backplanes based on differential-ECL and on BTL signal levels, respectively. The BTL backplane has recently been manufactured, and it will be evaluated during 1996. The ECL backplane will be built and evaluated during 1996. The Stockholm group is investigating the possibility of a 320 MHz backplane based on LVDS differential signals. All of the above backplanes are for point-to-point connections and use impedance-matched lines for the high-speed signal transmission. In the processor systems, they would be accompanied by conventional backplane buses for test, control, monitoring and readout. All the above are considered in the context of conventional 9U crate mechanics.

In view of the generic nature of the studies on high-speed custom backplanes, we propose to retain this work in the RD27 programme for 1996.

#### Development of fast, high-density processing ASICs

A number of ASIC developments related to calorimeter trigger processors have been made during the last year.

### High-speed adder ASIC

A very high-speed adder ASIC, designed by the Wisconsin group and illustrated in Fig. 8, has been manufactured using a 0.6  $\mu$ m GaAs process from Vitesse. This ASIC has eight operands of 13 bits, consisting of 10 bits of value, one bit of sign, one bit of input-value overflow and one bit of arithmetic overflow. The ASICs can be connected together to form an adder tree, propagating the information on the two kinds of overflow. A design requirement was that the ASIC should work at 160 MHz, allowing four sets of additions to be performed in every 25 ns period. In fact it has been tested to 200 MHz (limited by the available test facilities) and simulation shows that it should function correctly at above 300 MHz. The ASICs may be tested at higher speeds using specialist facilities in Heidelberg. The ASICs (and the design) are available for use by both ATLAS and CMS. More details on this ASIC can be found in Refs. [4, 10].

#### Dual-function multiplexer/demultiplexer ASIC

A dual-function multiplexing/demultiplexing ASIC, illustrated in Fig. 9, has been designed by the UK groups and manufactured. Used in its first mode, it multiplexes 16 bits of data at 40 MHz into four bits of data at 160 MHz. In its second mode it performs the inverse operation. These two functions were combined in a single device for reasons of economy in the demonstrator system. The purpose is to reduce by a factor of four the number of physical connections between components in the trigger system, by running at a speed four times higher than the bunch-crossing frequency. This ASIC was manufactured by ES2 in a 0.7  $\mu$ m CMOS process. Seventy packaged chips have been delivered and all have been successfully tested at RAL at 160 MHz; a subset of the chips is being tested at higher speeds in Heidelberg.

Eight Operand Adder Tree ASIC

Figure 8: Block diagram of high-speed adder ASIC.

# **Dual-function MUX/DeMUX ASIC**

Figure 9: Dual-function ASIC block diagram.

#### Bit-serial test ASIC

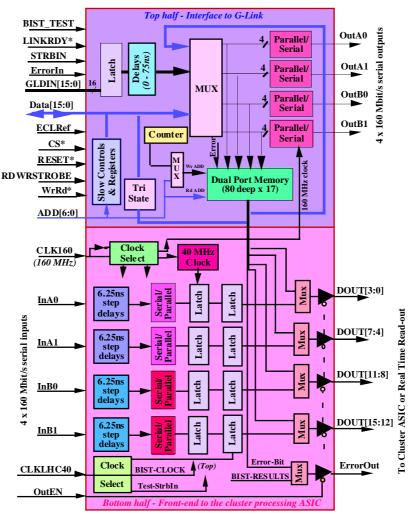

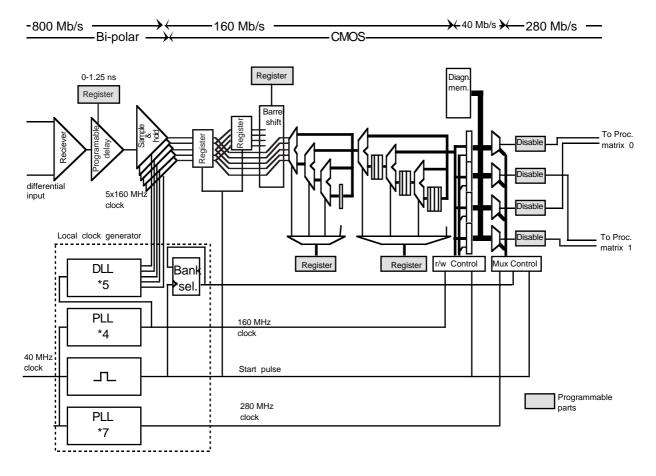

A test ASIC for the 800 MHz input part of the bit-serial processor development [13] has been designed by the Stockholm and Linköping groups, and submitted for manufacture. This will receive 16 serial inputs at 800 MHz, and perform serial-to-parallel conversion. As shown in Fig. 10, the input data are received differentially. The logic delays the signal with a suitable programmable delay of up to one bit in duration; this analog delay will be chosen such that the subsequent sampling unit will sense the signal at an optimal position for proper bit alignment. The sampling is controlled by five phase-delayed local 160 MHz clocks, generated from the 40 MHz master clock. The ASIC is being manufactured in a 0.6  $\mu$ m BiCMOS process by Ericsson, and delivery is scheduled for February 1996. Testing of this ASIC will be performed in Stockholm and in Heidelberg.

Figure 10: Block diagram of the input stage for one channel in the bit-serial development.

#### Bunch-crossing identification ASIC

The BCID ASIC discussed above and in Ref. [14] should also be mentioned here. This was designed in Heidelberg and manufactured in a 1  $\mu$ m process by ES2. It was tested in the laboratory and then successfully integrated in the demonstrator system at the test beam. It is planned to develop and manufacture a second-generation BCID ASIC that will include additional functions: look-up tables for calibrating the input data, pipelined readout with a derandomising buffer for deadtime-less operation, and a test facility consisting of "playback memory".

The ASICs described here, developed and evaluated in the context of the RD27 collaboration, will be included in demonstrator prototype systems for the first-level triggers of ATLAS and CMS.

# 4. Central Trigger Processor

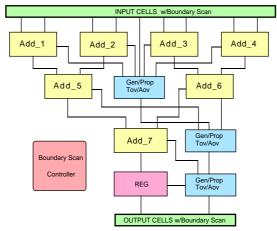

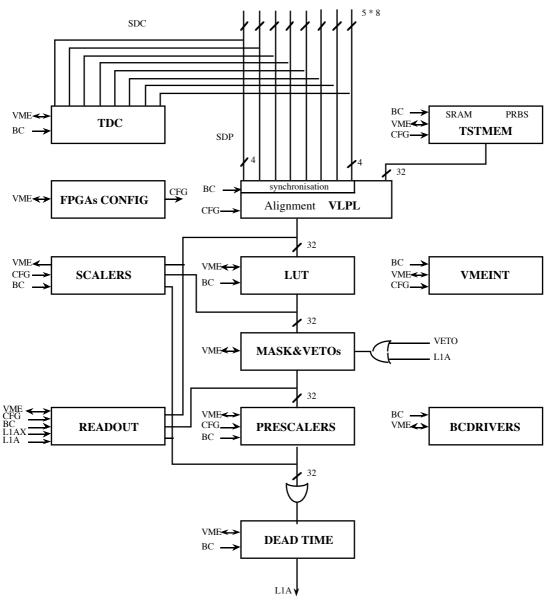

Design by the CERN group of a central trigger processor (CTP) demonstrator is well advanced. This demonstrator will contain all the essential elements of a final system, and will work at full speed with the required low latency ( $\leq 125$  ns). However, it will not have as many inputs or allow as many combinations as would be needed for a final system.

We had originally envisaged using custom gate arrays for the CTP. However, it was found that sufficiently large and fast FPGAs are now available to construct a compact system that can operate within the required low latency. A study has been performed of the feasibility of implementing the key components of the CTP in FPGAs. Following an initial evaluation [17], almost all of the system has been designed.

As for other parts of the trigger processor system, we are planning to install the CTP demonstrator at the H8 test beam where it will be connected to the calorimeter trigger processor. Such tests are useful to check the completeness and robustness of the system.

### Components of the CTP

A block diagram of the CTP demonstrator is shown in Fig. 11. Signals from subtrigger processors such as the calorimeter trigger processor arrive in groups of four, each group accompanied by a clock signal that indicates when the signals are stable. The first block in the CTP logic, labelled VLPL, is responsible for alignment of the different groups of signals in time. The synchronisation step latches the input on the leading or trailing edge of the local clock, the choice being made so that the input data are sampled when they are stable. The following alignment step allows one to introduce a delay of an integer number of bunch crossings. Alignment of the 32 input signals will be performed in a single FPGA circuit, reconfigurable in situ to adjust the delays.

The next block in the CTP, labelled LUT, performs the trigger algorithm which allows combinations of the inputs to be required in coincidence, veto or "don't care". It is implemented using a combination of SRAM and discrete logic. Up to 32 combinations of the 32 inputs can be defined, corresponding to 32 independent trigger conditions, the OR of which is the event trigger. We have also investigated a design for this logic using FPGAs; while this would also be feasible, we have chosen the SRAM solution for the demonstrator because of its flexibility, ease of programming and low latency.

Following the LUT, the next block contains mask and veto logic. This allows individual triggers to be masked, for example to introduce deadtime preferentially for low priority triggers, or for a global veto to applied. The latter can be used to impose deadtime globally; for example to introduce a minimum interval between consecutive first-level triggers.

Next in the data flow is the prescaler block that allows the 32 triggers to be prescaled by independently programmable factors. For the demonstrator, 12-bit prescalers will be provided, but larger factors could be implemented for a final system. Each FPGA will include 16 prescalers.

The final stages in the CTP are the OR over the 32 individual trigger conditions, followed by logic that determines when deadtime should be introduced as required by constraints in front-end electronic systems.

A number of essential additional facilities are included in the design. TDCs are provided that measure the phase of the clock signals accompanying the input data relative to the local

clock; these are needed to assist in setting up the timing of the system. A test memory is provided to generate a long pattern of input data, up to 25 ms at the nominal speed. A facility to generate pseudo-random bit sequences is also included.

Figure 11: Block diagram of the CTP demonstrator.

Scalers monitor the rates at various points in the system — each of the 32 inputs, each of the 32 trigger combinations and each of the 32 combinations after prescaling. The scalers are implemented using FPGAs. Each circuit contains 32 12-bit scalers with associated read-out registers. This allows scaling for a complete cycle of the LHC machine (88  $\mu$ s), with readout of the read-out register between cycles.

For triggered events, results will be read out from various parts of the system — the pattern of inputs, and the pattern of outputs before and after prescaling. This requires pipeline memories and derandomising buffers as for detector readout systems. The system will allow a time frame to be read out with a width programmable over the range 3–5 bunch crossings; this will be helpful when setting up the system. For the demonstrator system, the "derandomizer" will be implemented as a FIFO. For beam tests, the FIFO will be read out between bursts.

The status of the system is that all of the FPGA parts have been designed and simulated. The demonstrator will be implemented as a 9U VME module which will be tested in the laboratory and at the test beam during 1996. The results of these evaluations and the designs for the FPGAs will be available for use by the LHC experiments.

The CTP development is of general interest to the LHC experiments, all of which will need components such as prescalers, scalers, etc. In contrast to the calorimeter and muon trigger processors, the CTP design does not depend strongly on the particuliarities of the detectors. We therefore propose to continue the work on the CTP demonstrator within RD27 for a final year.

### **5.** Suggested milestones

We propose the following milestones for the final year of the project, focusing on items that are part of our ongoing programme and are of common interest across the LHC experiments:

- Tests of very high-speed (≥ 800 Mbit/s) synchronous serial data links for transmitting data to trigger processors.

- Tests of high-speed (≥ 160 Mbit/s) custom backplanes, based on BTL and differential-ECL signals, for communication between trigger-processor modules.

- Provision of demonstrator systems for central trigger processors based on FPGAs.

### 6. Request to CERN

We request funding from CERN at the level of 65 kCHF in 1995; there is no overlap of this request with the requests made by the ATLAS and CMS collaborations. We also request continued electronic-engineering support from ECP division at the same level as in 1995; this is required for the work on the central trigger processor demonstrator.

### Acknowledgements

We express our thanks to ATLAS and CMS, and to R&D groups with whom we have held useful discussions. We are particularly grateful to RD3, RD5, RD33, RD34 and to the ATLAS calorimeter and muon groups for their help and cooperation during joint beam tests. We would like to thank colleagues in BaBar for providing us with modules for evaluating high-speed optical data links. We have continued to work closely with RD12, and thank B.G. Taylor for his help and advice. Finally, we wish to acknowledge the work of J-P. Vanuxem and Y. Ermolin who worked with us until the end of 1994.

### References

- [1] RD27 proposal, CERN/DRDC/92-17.

- [2] Minutes of DRDC meeting 4 June 1992; minutes of Research Board 30 June 1992.

- [3] RD27 status report, CERN/DRDC/93-32.

- [4] RD27 status report, CERN/DRDC/94-52.

- [5] Minutes of DRDC meeting of 3 February 1995, CERN/DRDC 94-55;

minutes of Research Board of 20 February 1995, CERN/DG/Research Board 95-222.

- [6] ATLAS Technical Proposal, CERN/LHCC/94–43.

- [7] CMS Technical Proposal, CERN/LHCC/94–38.

- [8] R. Cardarelli et al., Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 213–217.

- [9] J. Dowdell et al., RD27 note 30 (unpublished).

- [10] W.H. Smith et al., Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 302–306.

- [11] I. Brawn et al., Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 293–296.

- [12] V. Perera et al., Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 297.

- [13] C. Bohm et al., Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 298–301.

- [14] A. Hölscher, A. Mass and K. Meier, Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 413.

- [15] S. Quinton, A. Grillo and W. Smith, Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 12–16.

- [16] P. Hanke et al., RD27 note 41 (unpublished).

- [17] O. Buyanov, RD27 notes 42 and 43 (unpublished).

# **Publications from RD27**

- N. Ellis et al., "A calorimeter-based level-one electromagnetic cluster trigger for LHC". Proc. CHEP92, CERN 92-07, pp. 210–213.

- B.G. Taylor, "Multichannel Optical Fiber Distribution System for LHC Detector Timing and Control Signals". Proc. CHEP92, CERN 92-07, pp. 689–692.

- B.G. Taylor, "Multichannel Optical Fiber Distribution System for LHC Detector Timing and Control Signals". Conf. Record IEEE Nuclear Science Symposium, Orlando, USA, 25–31 October 1992, pp. 492–494.

- E. Eisenhandler et al., "First level calorimeter trigger system for the LHC". Presented by V. Perera at IEEE Nuclear Science Symposium, Orlando, Florida, USA, 25–31 October 1992.

- E. Petrolo and S. Veneziano, Nucl. Instr. and Meth. A344 (1994) 194.

- I.P. Brawn et al., Nucl. Instr. and Meth. A349 (1994) 356.

- C. Bohm et al., "A bit-serial first-level calorimeter trigger for detectors at LHC". Presented by C. Bohm at 4th Int. Conf. on Calorimetry in HEP, Elba, 19-25 September 1993.

- I.P. Brawn et al., "First results from a prototype level-1 calorimeter trigger system for LHC". Presented by A. Gillman at 4th Int. Conf. on Calorimetry in HEP, Elba, 19–25 September 1993.

- B.G. Taylor, "Optical timing, trigger and control distribution for LHC", presented at IEEE Nucl. Science Symposium, San Francisco, 31 Oct 6 Nov 1993.

- I.P. Brawn et al., "Implementation of a first-level calorimeter trigger for use at the Large Hadron Collider at CERN". Presented by R. Staley at IEEE Nucl. Science Symposium, San Francisco, 31 Oct 6 Nov 1993.

- C. Bohm et al., "A bit-serial first-level calorimeter trigger for detectors at LHC". Presented by X. Zhao at CHEP94, San Francisco, 21–27 April 1994.

- S. Dasu et al., "The level-1 calorimeter trigger for the CMS detector". Presented by S. Dasu at CHEP94, San Francisco, 21–27 April 1994.

- I.P. Brawn et al., "A first-level calorimeter trigger for LHC experiments design studies and beam tests of a first prototype trigger system". Presented by A.T. Watson at CHEP94, San Francisco, 21–27 April 1994.

- W. H. Smith et al., "Level-1 Calorimeter Trigger for the CMS Detector", Proceedings of DPF '94, Albuquerque, NM, August, 1994, U. Wisconsin Preprint WISC-EX-94-340.

- S. Dasu et al., "Level-1 Calorimeter Trigger for the CMS Detector at the LHC", Proceedings of the International Conference on Calorimetry in High Energy Physics, Brookhaven, NY, September, 1994, U. Wisconsin Preprint WISC-EX-94-342.

- C. Bohm et al., Presented by C. Bohm at RTD'94, Dubna, Russia, 27 June 1 July 1994.

- I.P.Brawn et al., "Bunch Crossing Identification in a Level-one Calorimeter Trigger for LHC". Presented by Y.Ermoline at RTD'94, Dubna, Russia, 27 June 1 July 1994.

- V. Perera et al., "A first-level calorimeter trigger for the ATLAS experiment". Presented by V. Perera at IEEE 1994 Nuclear Science Symposium, Norfolk, Virginia, USA, Oct 30 – Nov 5, 1994.

- R. Cardarelli et al., "Trigger logic of the ATLAS first-level muon trigger". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 213–217.

- I. Brawn et al., "Bunch-crossing identification for the ATLAS first-level calorimeter trigger". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 293–296.

- V. Perera et al., "A first-level calorimeter trigger for the ATLAS experiment". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 297.

- C. Bohm et al., "Design study and demonstrator programme for a compact solution to the first-level calorimeter trigger for the ATLAS detector". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 298–301.

- W.H. Smith et al., "CMS calorimeter trigger circuits". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, pp. 302–306.

- A. Hölscher, A. Mass and K. Meier, "Design and test of an ASIC for bunch-crossing identification in the ATLAS level-1 trigger". Proc. first workshop on electronics for LHC experiments, CERN/LHCC/95-56, p. 413.

- J. Dowdell et al., "The RD27 muon trigger co-incidence array demonstrator ASIC". To appear in Proc. 1995 IEEE Nuclear Science Symposium.

### **RD27** notes

- 1. N. Ellis, Level-1 and level-2 triggering at LHC.

- 2. J. Garvey et al., A calorimeter-based level-1 em cluster trigger for LHC.

- 3. BG.Taylor, Multichannel optical fibre distribution system for LHC detector timing and control signals.

- 4. N. Ellis, Level-1 and level-2 triggering at LHC.

- 5. V. Perera et al., First level calorimeter trigger system for the LHC.

- 6. C. Bohm et al., A bit-serial first-level calorimeter trigger for an LHC detector.

- 7. N. Ellis, Ideas for a local/global level-2 trigger system.

- 8. V. Perera, A first-level calorimeter trigger processor for the LHC.

- 9. J.P. Vanuxem and H. Wendler, Central trigger processor for the first-level trigger for LHC experiments.

- 10. V. Perera, Crate readout controller (ROC).

- 11. I. Brawn, Preliminary investigations into bunch-crossing identification for the level-1 trigger.

- 12. R.E. Carney, The level-1 bit-parallel em trigger processor CERN beam tests November 1992.

- 13. A. Watson, Physics simulation studies of the first-level electron/photon trigger.

- 14. E. Petrolo, S. Veneziano, Use of GaAs circuits for first-level muon triggering at LHC.

- 15. A. Nisati, Accidental trigger rates in the ATLAS muon system.

- 16. S. Navas Concha, Data analysis for first-level trigger in ATLAS calorimeters.

- 17. R. Staley et al., Implementation of a first-level calorimeter trigger for use at the LHC at CERN.

- 18. B.G. Taylor, Optical timing, trigger and control distribution for LHC detectors.

- 19. A. Gillman, First results from a prototype level-1 calorimeter trigger system for LHC.

- 20. N. Ellis, Forward calorimetry and the level-1 trigger.

- 21. E. Eisenhandler, Level-1 triggers for LHC experiments.

- 22. I.P. Brawn et al., Beam tests of a prototype level-1 calorimeter trigger for LHC experiments.

- 23. U. Dickow, An analysis of the RD27 level-1 prototype calorimeter trigger processor test beam data.

- 24. N. Ellis, Distributed processing for fast triggering of DAQ.

- 25. P. Hanke, M. Keller, ROI Building, Results from a first demonstrator.

- 26. C. Bohm et al., A bit-serial first-level calorimeter trigger for detectors at LHC talk given at 4th int. conf. on calorimetry in HEP.

- 27. C. Bohm et al., A bit-serial first-level calorimeter trigger for detectors at LHC talk given at IEEE nuclear science symp.

- 28. S. Dasu et al., The level-1 calorimeter trigger for the CMS detector.

- 29. A. Watson et al., A first-level calorimeter trigger for LHC experiments Design studies and beam tests of a first prototype trigger system.

- 30. J. Dowdell et al., A coincidence array demonstrator ASIC for the RD27 muon trigger.

- 31. I.P. Brawn et al., Beam tests of a single-channel bunch-crossing identification module for the level-1 trigger November 1993.

- 32. S. Dasu et al., The level-1 calorimeter trigger for the CMS detector at LHC.

- 33. V. Perera et al., A first-level calorimeter trigger for the ATLAS experiment.

- 34. I.P. Brawn et al., The level-1 calorimeter trigger system for ATLAS.

- 35. I.P. Brawn, A demonstrator programme for the ATLAS level-1 calorimeter trigger.

- 36. G. Appelquist et al., An R&D programme for alternative technologies for the ATLAS level-1 calorimeter trigger.

- 37. J. Lackey et al., CMS calorimeter level-1 trigger conceptual design.

- 38. S. Dasu et al., CMS level-1 calorimeter trigger performance studies.

- 39. C. Jacobs et al., First-level central trigger processor for LHC experiments.

- 40. I.P. Brawn et al., Bunch-crossing identification in a level-1 calorimeter trigger for LHC.

- 41. P. Hanke et al., A flash ADC for trigger tests with ATLAS calorimetry.

- 42. O. Buyanov, Reconfigurable hardware approach to build the central trigger processor.

- 43. O. Buyanov, Central trigger processor.

- 44. I. Brawn et al., Bunch-crossing identification for the ATLAS first-level calorimeter trigger.

- 45. W. Smith et al., CMS calorimeter trigger circuits.

- 46. C. Bohm et al., Design study and demonstrator programme for a compact solution to the first-level calorimeter trigger of the ATLAS detector.

- 47. S. Veneziano et al., Trigger logic of the ATLAS first-level muon trigger.

- 48. J. Dowdell et al., The RD27 muon trigger co-incidence array demonstrator ASIC.

- 49. V. Perera et al., A first-level calorimeter trigger for the ATLAS experiment.