# Università degli Studi di Ferrara DOTTORATO DI RICERCA IN FISICA

CICLO XXIX

COORDINATORE Prof. Vincenzo Guidi

Development and Commissioning of the GigaTracker Data Acquisition and Control Systems for the NA62 Experiment at CERN

Settore Scientifico Disciplinare FIS/04

Dottorando

**Tutore**

Dott. Enrico Gamberini

Prof. Ferruccio Petrucci

# Contents

| In | trod           | action |                                                                                                                              | 5               |

|----|----------------|--------|------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1  | <b>The</b> 1.1 |        | al and Experimental Framework $\rightarrow \pi^+ \nu \bar{\nu} \text{ theoretical framework } \dots \dots \dots \dots \dots$ | 7               |

|    |                | 1.1.1  | CKM matrix and the Unitarity triangle                                                                                        | 8               |

|    |                | 1.1.2  | Branching Ratio of the $K^+ \to \pi^+ \nu \bar{\nu}$ decay                                                                   | 12              |

|    | 1.2            | Experi | imental Status                                                                                                               | 15              |

|    | 1.3            |        | experimental strategy                                                                                                        | 16              |

|    |                | 1.3.1  | Kinematic rejection                                                                                                          | 16              |

|    |                | 1.3.2  | Vetoes                                                                                                                       | 20              |

|    |                | 1.3.3  | Particle Identification                                                                                                      | 20              |

|    |                | 1.3.4  | Sensitivity                                                                                                                  | 21              |

| 2  | The            | NA62   | 2 experiment                                                                                                                 | 23              |

|    | 2.1            |        | for the experiment                                                                                                           | 23              |

|    | 2.2            | Detect | _                                                                                                                            | $\frac{25}{25}$ |

|    |                | 2.2.1  | KTAG                                                                                                                         | 28              |

|    |                | 2.2.2  | GigaTracker                                                                                                                  | 28              |

|    |                | 2.2.3  | CHANTI                                                                                                                       | 31              |

|    |                | 2.2.4  | LAV                                                                                                                          | 31              |

|    |                | 2.2.5  | Straw Tracker                                                                                                                | 32              |

|    |                | 2.2.6  | RICH                                                                                                                         | 33              |

|    |                | 2.2.7  | CHOD                                                                                                                         | 35              |

|    |                | 2.2.8  | New CHOD                                                                                                                     | 35              |

|    |                | 2.2.9  | LKr                                                                                                                          | 36              |

|    |                | 2.2.10 | MUV                                                                                                                          | 36              |

|    |                | _      | IRC and SAC                                                                                                                  | 36              |

|    | 2.3            |        | r and Data acquisition                                                                                                       | 37              |

| 3  | Gig            | aTrack | er                                                                                                                           | 39              |

| _  | 3.1            |        | sensor and bump-bonding                                                                                                      | 41              |

|    |                | 3.1.1  | Silicon sensor                                                                                                               | 41              |

|    |                | 3.1.2  | Bump bonding                                                                                                                 | 43              |

|    | 3.2            |        | ut ASIC                                                                                                                      | 43              |

|    |                | 3.2.1  | Design options                                                                                                               | 45              |

|    |                | 3.2.2  | ASIC architecture                                                                                                            | 47              |

|    |                | 3 2 3  | End-of-Column (EoC) architecture overview                                                                                    | 47              |

4 CONTENTS

|              | 3.3              | Electrical integration                              | 48  |  |  |  |

|--------------|------------------|-----------------------------------------------------|-----|--|--|--|

|              | 3.4              | Cooling                                             | 49  |  |  |  |

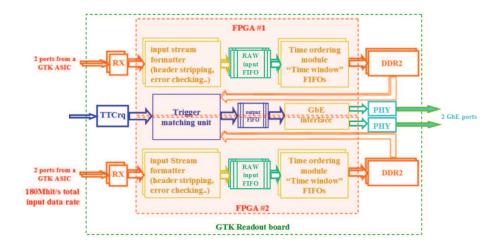

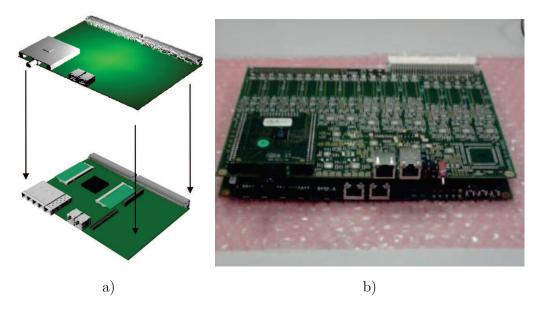

|              | 3.5              | Off-detector readout electronics                    | 51  |  |  |  |

|              |                  | 3.5.1 Memory device                                 | 54  |  |  |  |

|              |                  | 3.5.2 Input stream formatter                        | 54  |  |  |  |

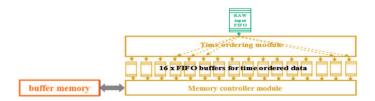

|              |                  | 3.5.3 Time ordering module                          | 54  |  |  |  |

|              | 3.6              | GigaTracker TTC interface                           | 55  |  |  |  |

| 4            | Giga             | aTracker DAQ and Control Systems                    | 59  |  |  |  |

|              | 4.1              | GigaTracker Data Acquisition System                 | 59  |  |  |  |

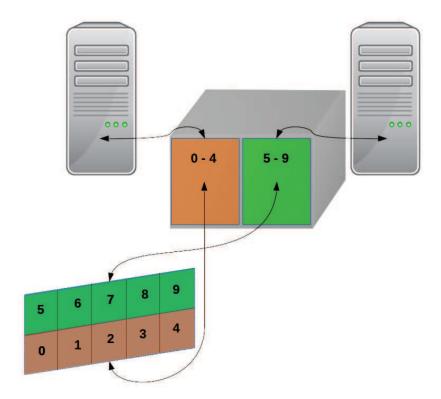

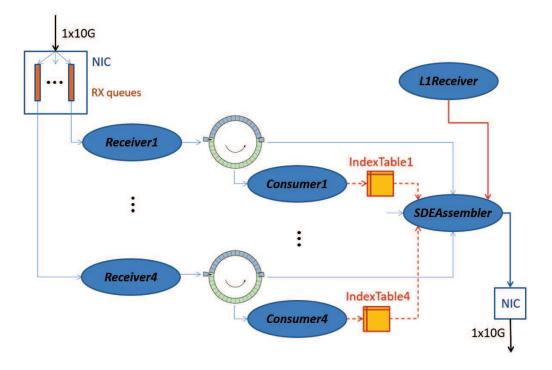

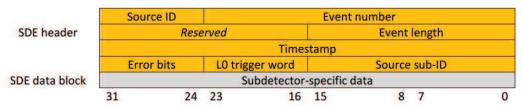

|              |                  | 4.1.1 Sub-detector PC DAQ software                  | 59  |  |  |  |

|              | 4.2              | GigaTracker Run Control System                      | 63  |  |  |  |

|              |                  | 4.2.1 TDCpix configuration                          | 63  |  |  |  |

|              |                  | 4.2.2 GTK-RO board configuration                    | 64  |  |  |  |

|              |                  | 4.2.3 GigaTracker Run Control Software              | 64  |  |  |  |

|              |                  | 4.2.4 GTK-TTC board Run Control                     | 65  |  |  |  |

|              |                  | 4.2.5 I <sup>2</sup> C controller for Carrier board | 66  |  |  |  |

|              | 4.3              | System Integration                                  | 66  |  |  |  |

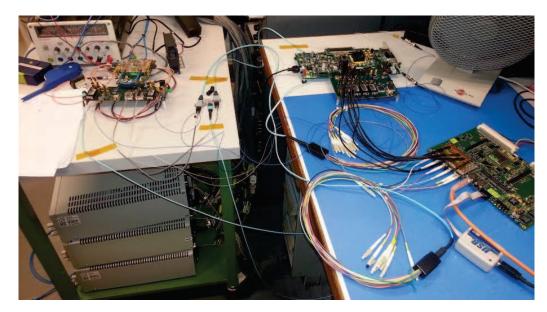

|              | 1.0              | 4.3.1 Single TDCpix chip integration                | 66  |  |  |  |

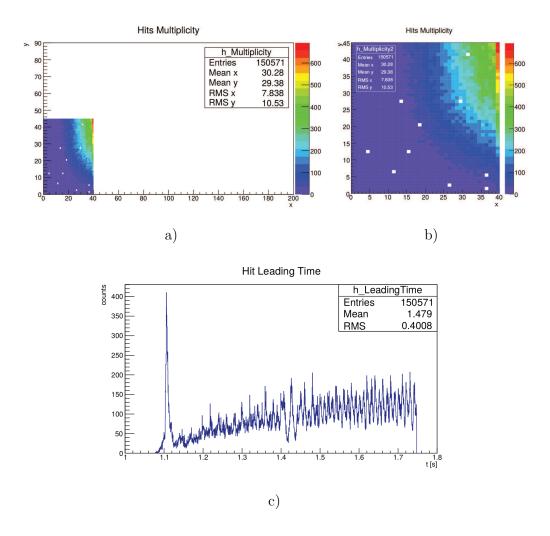

|              |                  | 4.3.2 NA62 Commissioning                            | 67  |  |  |  |

| 5            | Giga             | aTracker Performances                               | 79  |  |  |  |

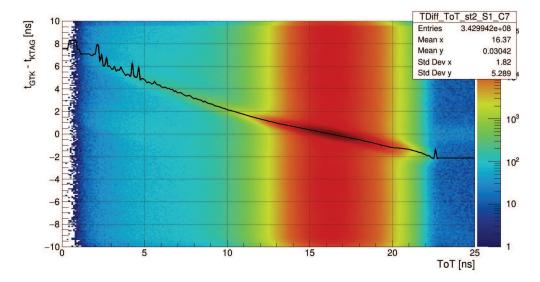

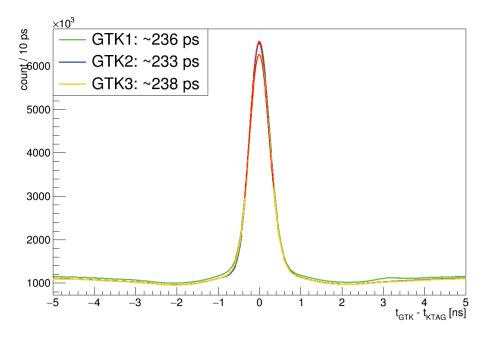

|              | 5.1              | Time Alignment and Time Walk Correction             | 79  |  |  |  |

|              |                  | 5.1.1 Automatic T0 Reconstruction Computation       | 80  |  |  |  |

|              |                  | 5.1.2 Timing corrections                            | 80  |  |  |  |

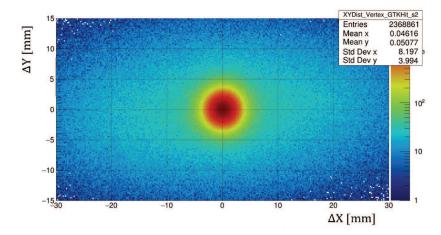

|              | 5.2              | Spatial Alignment                                   | 84  |  |  |  |

|              | 5.3              | Track association                                   | 86  |  |  |  |

|              |                  | 5.3.1 Track matching based on discriminants         | 90  |  |  |  |

| Co           | onclu            | asions                                              | 95  |  |  |  |

| $\mathbf{A}$ | Sing             | gle Event Upset Monitoring                          | 97  |  |  |  |

|              |                  | •                                                   | 00  |  |  |  |

| В            | 11018            | se identification                                   | 99  |  |  |  |

| $\mathbf{C}$ | Leve             | el 0 Trigger Processor                              | 103 |  |  |  |

| Bi           | Bibliography 106 |                                                     |     |  |  |  |

# Introduction

This thesis presents the results of years of work dedicated to the development, commissioning and testing of the NA62 GigaTracker data acquisition and control systems as well as analysis of the data for alignment and quality checking. The GigaTracker beam detector is part of the NA62 experiment at CERN-SPS. The experiment is proposed to provide an accurate measurement of the  $K^+ \to \pi^+ \nu \bar{\nu}$  rare decay branching ratio.

Flavour changing transitions, the understanding of which is one of the most important objective in particle physics, are described by the Standard Model by means of the Cabibbo-Kobayashi-Maskawa (CKM) unitary matrix. Present experimental data on hadron weak decays are in agreement with Standard Model predictions within theoretical and experimental uncertainties. Nevertheless new physics contributions cannot be ruled out since in most cases theoretical errors on decay amplitudes are large due to long-distance non perturbative contributions. The  $K^+ \to \pi^+ \nu \bar{\nu}$  however belongs to a limited class of decays in which the matrix elements can be extracted from experimentally well measured decay branching ratios. As a consequence the  $K^+ \to \pi^+ \nu \bar{\nu}$  branching ratio can be determined with an extremely high accuracy, allowing to determine the possible presence of contributions beyond the Standard Model.

The NA62 experiment aims to collect about  $100~K^+ \to \pi^+ \nu \bar{\nu}$  events with a signal to background ratio of S/B  $\approx 10/1$  in 2 years of data taking using the decay in-flight of a 75 GeV/c kaon beam. The latest Standard Model prediction for the  $K^+ \to \pi^+ \nu \bar{\nu}$  branching ratio is  $BR(K^+ \to \pi^+ \nu \bar{\nu}) = (7.81^{+0.80}_{-0.71} \pm 0.29) \times 10^{-11}$  whilst the only experimental result, based on 7 events, comes from the BNL E787/E949 collaborations and gives  $BR(K^+ \to \pi^+ \nu \bar{\nu}) = (1.73^{+1.15}_{-1.05}) \times 10^{-10}$ . The presence, in the final state, of two undetectable neutrinos imposes an experimental strategy based on precise timing, kinematic rejection, hermetic vetoes and particle identification to suppress the overwhelming background.

A crucial role in timing and kinematic rejection is performed by the beam spectrometer named GigaTracker. It consists of three stations of hybrid silicon pixels sensors with an overall resolution of 150 ps (RMS) on time,  $\sigma(p_K)/p_K \sim 0.2\%$  on momentum and  $\sim 16$  µrad on direction of the track. In addition the system will operate under a high rate of particles i.e. 0.75 GHz in total, with a peak of intensity around the centre of 1.3 MHz/mm<sup>2</sup>.

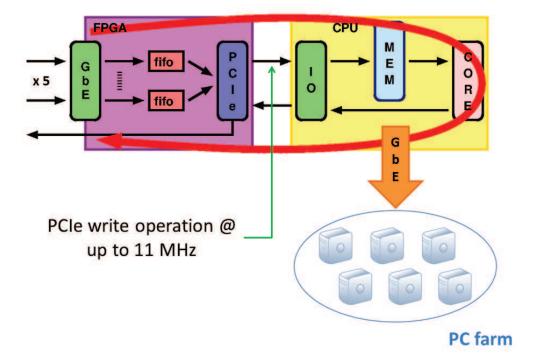

Each GigaTracker station is read out continuously by 10 on-detector chips con-

6 INTRODUCTION

nected to the same number of off-detector boards where the event data are stored waiting the trigger decision. The trigger-matched output from an entire station is estimated to reach  $\sim 900$  MB/s. A small farm of sub-detector PCs hosts the data acquisition software and the control software, both developed and maintained by the author; the first organizes data and performs higher level trigger matching, while the second controls and configure the front-end and off-detector electronics as well as the data acquisition software itself.

The layout of the thesis is the following: in Chapter 1 an overview of the physics motivations behind the  $BR(K^+ \to \pi^+ \nu \bar{\nu})$  measurement, present experimental status and a description of the NA62 experimental strategy to perform such measurement is given; Chapter 2 contains a description of the NA62 detector; in Chapter 3 a detailed overview of the crucial components of the GigaTracker such as the sensor, read-out electronics and cooling system is carried out; Chapter 4 contains a description of the data acquisition and control software characteristics and follows the commissioning of the GigaTracker's data acquisition system during the first three years of NA62 data taking; finally in Chapter 5 the work on the analysis of the GigaTracker's data is reported, with studies on alignment and quality checking.

# Chapter 1

# Theoretical and Experimental Framework

The main aim of the NA62 experiment is the study of the ultra rare decay  $K^+ \to \pi^+ \nu \bar{\nu}$ . The final goal is to measure the Branching Ratio of this process with a 10% accuracy, in order to provide a stringent test of the Standard Model (SM) predictions or lead to a discovery of deviations from the SM which turns into evidence of new physics

The theoretical framework of the  $K^+ \to \pi^+ \nu \bar{\nu}$  decay is described in Section 1.1. Among the many rare flavour changing neutral current (FCNC) K and B decays, the ultra rare decays  $K \to \pi \nu \bar{\nu}$  play a key role in the search for new physics through underlying mechanisms of flavour mixing. The Branching Ratio can be computed in the framework of the Standard Model to an exceptionally high degree of precision: the prediction for the  $K^+ \to \pi^+ \nu \bar{\nu}$  channel is  $(7.81 \pm 0.75 \pm 0.29) \times 10^{-11}$  [12]. The first error comes from the uncertainty on the CKM matrix elements, the second one is the intrinsic theoretical uncertainty. This decay is one of the best probes for new physics effects complementary to direct searches, especially within non Minimal Flavour Violation models [26]. Since theoretical cleanliness of these decays holds also in these scenarios, even deviations from the SM value at the level of 20% can be considered signals of new physics.

Within the SM, the Branching Ratio value provides a measurement of  $|V_{td}|$  free from hadronic uncertainties and independent from that obtained from B meson decays.

The present experimental status is reported in Section 1.2. The decay  $K^+ \to \pi^+ \nu \bar{\nu}$  has been observed by dedicated experiments E787 and E949 at the Brookhaven National Laboratory and the measured Branching Ratio is  $(1.73^{+1.15}_{-1.05}) \times 10^{-10}$  [7]. However only a measurement of the Branching Ratio with at least 10% accuracy can be a significant test of new physics.

Section 1.3 gives details of the NA62 experimental strategy. The goal is collecting about 100 events of the  $K^+ \to \pi^+ \nu \bar{\nu}$  decay, with a Signal over Background ratio (S/B) of 10/1, in two to three years of data taking.  $10^{13}~K^+$  decays are required, assuming a 10% signal acceptance and a  $K^+ \to \pi^+ \nu \bar{\nu}$  Branching Ratio of  $10^{-10}$ . The need of reducing the systematic uncertainty, requires a rejection factor for

8

generic kaon decays of the order of  $10^{12}$  and the possibility to measure efficiencies and background suppression factors directly from data.

## 1.1 $K^+ \to \pi^+ \nu \bar{\nu}$ theoretical framework

#### 1.1.1 CKM matrix and the Unitarity triangle

The Cabibbo-Kobayashi-Maskawa (CKM) matrix describes the quark flavourmixing in weak decays within the Standard Model [30]. It is a unitary  $3 \times 3$ matrix and connects the weak eigenstates (d', s', b') to the corresponding mass eigenstates (d, s, b):

$$\begin{pmatrix} d' \\ s' \\ b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix} \equiv \hat{V}_{CKM} \begin{pmatrix} d \\ s \\ b \end{pmatrix}$$

(1.1)

One notes that the CKM matrix unitarity ensures the absence of transitions governed by charged currents with flavour change at tree level; this means that elementary vertices involving neutral gauge bosons (gluons,  $Z^0$ ,  $\gamma$  and Higgs boson  $H^0$ ) conserves flavour. This property is known as GIM mechanism (S. Glashow, J. Iliopoulos, L. Maiani).

Various parametrization of the CKM matrix exists. The so-called Wolfenstein parametrization [43] foregrounds the hierarchical configuration of the CKM matrix elements absolute values: elements on the diagonal are close to unity, elements  $|V_{us}|$  and  $|V_{cd}|$  of order 0.2, elements  $|V_{cb}|$  and  $|V_{ts}|$  of order  $4 \cdot 10^{-2}$  and elements  $|V_{ub}|$  and  $|V_{td}|$  of order  $5 \cdot 10^{-3}$ .

It is an approximate parametrization of the CKM matrix in which every element is expanded in series of powers with respect to the parameter  $\lambda = |V_{us}| \sim 0.22$ :

$$\hat{V} = \begin{pmatrix}

1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\rho - i\eta) \\

-\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\

A\lambda^3(1 - \rho - i\eta) & -A\lambda^2 & 1

\end{pmatrix} + \mathcal{O}(\lambda^4) \tag{1.2}$$

The CKM matrix is therefore described by 4 independent parameters, in this case:

$$\lambda, \quad A = \frac{|V_{cb}|}{\lambda^2}, \quad \rho, \quad \eta$$

(1.3)

Including order  $\mathcal{O}(\lambda^4)$  and  $\mathcal{O}(\lambda^5)$  terms, one obtains the generalized Wolfenstein parametrization:

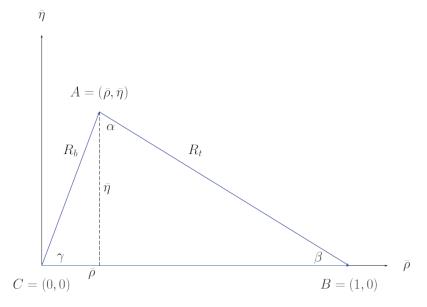

**Figure 1.1:** Unitarity triangle in complex plane  $(\bar{\rho}, \bar{\eta})$ .

$$V_{ud} = 1 - \frac{\lambda^2}{2} - \frac{\lambda^4}{8} , \qquad V_{us} = \lambda$$

$$V_{ub} = A\lambda^3(\bar{\rho} - i\bar{\eta}) , \qquad V_{cd} = -\lambda + \frac{1}{2}A^2\lambda^5[1 - 2(\bar{\rho} + i\bar{\eta})]$$

$$V_{cs} = 1 - \frac{1}{2}\lambda^2 - \frac{1}{8}\lambda^4(1 + 4A^2) , \qquad V_{cb} = A\lambda^2$$

$$V_{td} = A\lambda^3(1 - \bar{\rho} - i\bar{\eta}) , \qquad V_{ts} = -A\lambda^2 + \frac{1}{2}A\lambda^4[1 - 2(\bar{\rho} + i\bar{\eta})]$$

(1.4)

where  $\mathcal{O}(\lambda^6)$  terms are neglected and:

$$\bar{\rho} = \rho \left( 1 - \frac{\lambda^2}{2} \right) , \quad \bar{\eta} = \eta \left( 1 - \frac{\lambda^2}{2} \right)$$

(1.5)

After this choice the 4 independent parameters becomes:

$$\lambda, \quad A = \frac{|V_{cb}|}{\lambda^2}, \quad \bar{\rho}, \quad \bar{\eta}$$

(1.6)

The CKM matrix unitarity implies the existence of 6 independent orthogonality relations between its parameters, e.g.:

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0 (1.7)$$

Relation 1.7 can be represented by an unitarity triangle in  $(\bar{\rho}, \bar{\eta})$  plane. See Figure 1.1.

Length of sides  $R_b$  and  $R_t$  are expressed by relations:

$$R_{b} = \frac{|V_{ud}V_{ub}^{*}|}{|V_{cd}V_{cb}^{*}|} = \sqrt{\bar{\rho}^{2} + \bar{\eta}^{2}} = \left(1 - \frac{\lambda^{2}}{2}\right) \frac{1}{\lambda} \left|\frac{V_{ud}}{V_{cb}}\right|$$

$$R_{t} = \frac{|V_{td}V_{tb}^{*}|}{|V_{cd}V_{cb}^{*}|} = \sqrt{(1 - \bar{\rho})^{2} + \bar{\eta}^{2}} = \frac{1}{\lambda} \left|\frac{V_{td}}{V_{cb}}\right|$$

(1.8)

From relations 1.8 trivially derives that angles  $\beta$  and  $\gamma$  are directly bounded to the complex phases of CKM matrix elements:

$$V_{td} = |V_{td}|e^{-i\beta}$$

$$V_{ub} = |V_{ub}|e^{-i\gamma}$$

(1.9)

The 1.7 invariance with respect to any phase transformation implies that, under this transformation, the corresponding triangle is rotated in  $(\bar{\rho}, \bar{\eta})$  plane; since angles and sides in such triangle (given by CKM matrix elements moduli) remain unchanged, they are independent with respect to phase transformations and therefore are physical observables. Angles and sides of the Unitarity triangle can then be directly measured in dedicated experiments.

Let us also note that the areas  $A_{\Delta}$  of the 6 unitarity triangles that can be constructed from the 6 orthogonality relations are equal and related to the CP violation measure:  $|J_{CP}| = 2A_{\Delta}$ . The current knowledge of the CKM matrix, based on tree decays, such as semi-leptonic K and B decay, can be summarized as [31, 36]:

$$|V_{us}| = \lambda = 0.2252 \pm 0.0009 \,, \quad |V_{cb}| = (40.9 \pm 1.1) \times 10^{-3}$$

$\frac{|V_{ub}|}{|V_{cb}|} = 0.089 \pm 0.012 \,, \qquad |V_{ub}| = (4.15 \pm 0.49) \times 10^{-3}$

$$(1.10)$$

from which:

$$A = \frac{|V_{cb}|}{\lambda^2} = 0.817 \pm 0.015, \quad R_b = 0.40 \pm 0.06$$

(1.11)

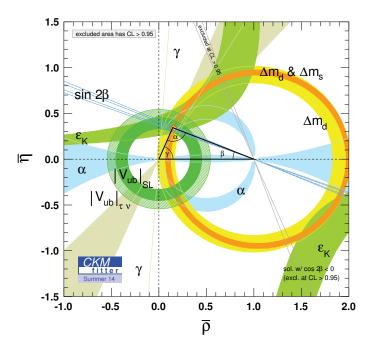

The informations enclosed in previous 1.10 and 1.11 indicates that the vertex A of the unitarity triangle lays on the dark-green band in Figure 1.2, which shows the so-called unitarity circle. Tree decays, from which are determined the values of  $|V_{us}|$ ,  $|V_{cb}|$ ,  $|V_{ub}|$  and consequently  $R_b$ , are essentially independent from new physics contribution: these values are then universal constant and valid in every extension of the Standard Model.

The study of other decays is required to determine the exact point where the vertex A lays inside the unitarity circle, most promising of which are the so-called "loop induced" decays and CP violating B decays, sensitive to  $\beta$  and  $\gamma$  angles and to  $R_t$ .

**Figure 1.2:** Constraints on the Unitarity triangle in the complex plane  $(\bar{\rho}, \bar{\eta})$  [19].

The determination of one of the parameters  $(R_t, \beta, \gamma)$  combined to the knowledge of the universal parameter  $R_b$ , or the determination of any parameter couple between  $(R_t, \beta, \gamma)$  is sufficient to build the unitarity triangle. This should allow to comprehend whether the Cabibbo-Kobayashi-Maskawa representation of the CP violation is correct and more generally if the Standard Model offers a proper description of hadron weak decays.

In the Unitarity triangle language this translates to understanding whether the curves in  $(\bar{\rho}, \bar{\eta})$  plane, extracted from various decays and transitions using SM formulas, intersect in the same point, and whether angles  $(\alpha, \beta, \gamma)$  in the corresponding triangle are in agreement with those extracted from CP violations in B decays and from B decays that conserves CP. Figure 1.2 shows an illustrative situation.

Every inconsistency in the  $(\bar{\rho}, \bar{\eta})$  plane can provide a hint of physics beyond the Standard Model.

In this context  $R_b$  plays a key role because of its universality, while the other parameters  $(R_t, \beta, \gamma)$  are in general sensitive to new physics contribution. This means that, assuming the CKM matrix built from 3 quark generations to be unitary and the Standard Model to be part of a wider theory, the Unitarity triangle vertex must lay inside the unitarity circle with radius  $R_b$ , determined by decays at tree level.

Thus, even in the case in which SM expression would put  $(\bar{\rho}, \bar{\eta})$  outside the uni-

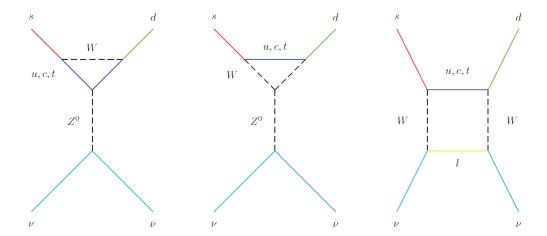

Figure 1.3: Graphs for  $s \to d\nu\bar{\nu}$  in the Standard Model.

tarity circle, the corresponding expressions of the wider theory would include properly new contributions capable to put  $(\bar{\rho}, \bar{\eta})$  back inside the dark-green band of the unitarity circle in Figure 1.2.

The better is the knowledge of  $R_b$ , the thinner becomes the unitarity circle band in Figure 1.2, making possible to select the correct theory. On the other hand a precise knowledge of  $|V_{cb}|$  is important since the branching ratios of CP violating rare decays depends significantly from the parameter A.

# 1.1.2 Branching Ratio of the $K^+ \to \pi^+ \nu \bar{\nu}$ decay

In the study of decay amplitudes, long-distance contributions contain low energy strong interaction contributes, not treatable in perturbative way and featuring the main theoretical uncertainty source.

However, rare meson decays exist, whose matrix elements can be extracted, thanks to isospin symmetry, from experimentally measured decay branching ratios. For this reason, the process  $K^+ \to \pi^+ \nu \bar{\nu}$  represents one of the theoretically clearer meson decays for the study of flavours dynamics.

Since the GIM mechanism is active, tree level processes that can activate this decay do not exist; therefore this process is described by box and penguin diagrams, which are sensitive to short range dynamics. This decay is then extremely useful for deepening the knowledge of flavour dynamics and CKM parameters, and it is a powerful SM test.

At quark level the process that describes this decay is  $s \to d\nu\bar{\nu}$ , which in the SM originates from electroweak penguins (the first two graphs in Figure 1.3) and box diagrams, the third graph. Since two neutrinos occur in the final state, electromagnetic penguin graphs do not contribute. As a consequence, this decay shows an hard GIM suppression, with a quadratic dependence on up-type quark masses. For this reason the decay amplitude is:

$$A_q \sim \frac{m_q^2}{M_W^2} V_{qs}^* V_{qd}, \quad q = u, c, t$$

(1.12)

It follows that up-quark contributions are negligible, as well as the long-distance contributions from the charm; the top-quark contribution dominates, so that  $s \to d\nu\bar{\nu}$  is essentially a short-distance process, well described by a low-energy effective Hamiltonian. Let us also note that, in the box diagram case, the exchanged lepton l mass is negligible with respect to quark masses if  $l=e,\mu$ . Instead, in the  $\tau$  case, its effects must be considered if the exchanged quark is q=c as  $\tau$  and c masses are comparable.

Generally, the  $s \to d\nu\bar{\nu}$  effective Hamiltonian can be written as [33]:

$$\mathcal{H}_{eff} = \frac{G_l}{\sqrt{2}} \sum_{l=e,\mu,\tau} (\bar{s}_L \gamma_\mu d_L) (\bar{\nu}_{lL} \gamma_\mu \nu_{lL}) + h.c.$$

(1.13)

where  $G_l$  is the effective coupling constant. Given  $G_l$ , the branching ratio is directly related by isospin to the well experimentally measured  $K_{e3}^+$  decay [13, 14]:

$$BR(K^+ \to \pi^+ \nu \bar{\nu}) = 6r_{K^+} BR(K^+ \to \pi^0 e^+ \nu) \frac{|G_l|^2}{G_E^2 |V_{us}|^2};$$

(1.14)

here,  $r_{K^+} = 0.901$  is an isospin-breaking correction that includes phase-space and QED effects. The effective coupling constant  $G_l$  can be expressed as the sum of two contributions, the first arising from an internal top-quark line, the second from a charm-quark [14]:

$$G_l = \frac{\alpha G_F}{2\pi \sin^2 \theta_W} [\lambda_t X_t + \lambda_c X^l]$$

(1.15)

where the  $X_i$  are the Inami-Lim functions, which parametrize short-distance contributions and  $\lambda_i = V_{is}^* V_{id}$ .

In terms of the leading-order (LO) contribution:

$$X = \frac{x}{8} \left[ \frac{x+2}{x-1} + \frac{3x-6}{(x-1)^2} \ln x \right]$$

(1.16)

with  $x = m^2/M_W^2$  and m is the mass of the exchanged fermion.

The X coefficients have been computed including several corrections [12]. The theoretical uncertainty on  $X^l$  is 2.5% after next-to-next-to-leading order (NNLO) QCD and next-to-leading order (NLO) electroweak corrections are taken into account, leading to a small resulting error on the branching ratio.

For the function  $X_t$ , unknown higher-order QCD corrections result in a 1% uncertainty while sub-leading electroweak contribution uncertainties have been calculated to be 0.134% including two-loop electroweak corrections.

The SM prediction for the decay branching ratio is therefore:

$$BR(K^+ \to \pi^+ \nu \bar{\nu}) = (7.81^{+0.80}_{-0.71} \pm 0.29) \times 10^{-11}$$

(1.17)

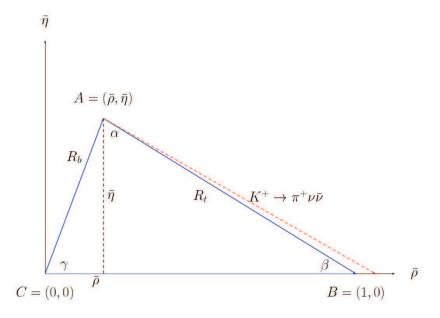

**Figure 1.4:** Unitarity triangle. The dashed line is proportional to  $BR(K^+ \to \pi^+ \nu \bar{\nu})$ .

where the uncertainties were separated in order to highlight the first contribution, which is due to the CKM input parameters [12].

The knowledge of  $BR(K^+ \to \pi^+ \nu \bar{\nu})$  is extremely important in the determination of the unitarity triangle. In fact this process offers a complementary study of the unitarity triangle with respect to the B physics. Since this decay is sensitive to the  $V_{td}$  coupling, its measure can provide a determination of the length  $R_t$  in the unitarity triangle, independent from B physics.

Particularly, identifying charm-quark exchange contributions and knowing the well-measured quantities  $V_{cd}$ ,  $V_{cs}$ ,  $V_{ts}$  in 1.15 from B decays,  $V_{td}$  can be experimentally determined (see 1.14) from the measurement of the  $K^+ \to \pi^+ \nu \bar{\nu}$  branching ratio. At this point, knowing  $V_{td}$  and the well known  $V_{cb}$ , is then possible to link the measurement of the branching ratio to  $R_t$  as in Figure 1.4.

A deviation from the expected measure would be a strong evidence of the presence of physics beyond the Standard Model.

Particularly, new physics contributions can be introduced through box or penguin diagrams which involve loops of new particle such as charged Higgs, charginos or other supersymmetric particles (Figure 1.5) that replace the W boson and the up-type quark in SM (Figure 1.3).

Figure 1.5: Graphs for  $s \to d\nu\bar{\nu}$  in supersymmetry.

# 1.2 Experimental Status

The study of the  $K^+ \to \pi^+ \nu \bar{\nu}$  decay is not new. The first experimental search for the decay took place in 1969 when experimentalists were looking for neutral currents. Camerini et al. looked at decays of kaons stopped in a bubble chamber filled with Freon and placed in a magnetic field [17]. The collaboration established the basic experimental techniques used in subsequent stopped kaon experiments. Three main criteria were used to disentangle the signal from the other backgrounds. First, a pion decaying at rest had to correspond to each stopped kaon. The pions were identified thanks to the  $\pi^+ \to \mu^+ \to e^+$  chain reaction. Second, no detector activity compatible with photons could be seen. Third, the  $\pi^+$  momentum, calculated by looking at its range, had to be away from the peaks corresponding to the  $K^+ \to \mu^+ \nu_\mu$  and  $K^+ \to \pi^+ \pi^0$  decays. The group reported  $BR(K^+ \to \pi^+ \nu \bar{\nu}) < 5 \times 10^{-5}$  with a 63% confidence level.

Two subsequent stopped kaon experiments were carried on at the Berkeley's Bevatron [28, 16], the advances of the electronics allowed them to record more kaon decays. The incoming particles were stopped in scintillation counters surrounded on one side by spark chambers and on the other side by lead glass Čerenkov counters. A stack of scintillation counters placed on top of the spark chambers was used to determine the range of the produced pion. A Čerenkov detector identified the pions and the kaons in the beam. The groups used the same criteria as the experiment of Camerini et al. to select the signal. They lowered the upper limit to  $5.6 \times 10^{-7}$  with a 90% confidence level.

A similar geometry was used by Asano et al. at KEK [8]. The spark chambers were replaced by multi-wire proportional chambers otherwise the analysis technique was similar as the three previous experiments. The group set the upper limit for the branching ratio at  $1.4 \times 10^{-7}$  with a 90% confidence level.

The E787 experiment and its successor, E949, moved to a " $4\pi$ " solid angle coverage [9] by equipping both detector hemispheres with drift chambers and stacks of scintillators. The whole apparatus was placed inside a uniform 1 T magnetic field directed along the beam axis. The experiment benefited from a 710-790 MeV/c

beam composed of 75% of kaons. Kaons were stopped in an active segmented target built with scintillating fibers. The photon rejection was assured by electromagnetic calorimeters placed between the target and the drift chambers. The particle momentum was extracted from the bending radius and from the number of triggered scintillator layers. A Čerenkov detector identified and tagged the beam particles. Combining their datasets, E787 and E949 reported the observation of  $7 K^+ \to \pi^+ \nu \bar{\nu}$  candidates and established the current best branching ration measurement [6]:

$$BR(K^+ \to \pi^+ \nu \bar{\nu}) = (1.73^{+1.15}_{-1.05}) \times 10^{-10}$$

. (1.18)

# 1.3 NA62 experimental strategy

The NA62 experiment main goal is to collect about  $100~K^+ \to \pi^+ \nu \bar{\nu}$  in two years of data taking, with a background contamination around 10% and a signal acceptance of at least 10%. These requirements can be achieved only using high energy kaons and tracking their decays in-flight. Assuming a 10% signal acceptance and a  $K^+ \to \pi^+ \nu \bar{\nu}$  branching ratio of  $10^{-10}$ , at least  $10^{13}~K^+$  decays are required to achieve the experiment objectives.

The presence of the two undetectable neutrinos in the final state motivates the necessity of a very accurate kinematic reconstruction to discriminate the various decay channels in order to achieve a signal to background ratio  $S/B \simeq 10/1$ . The experiment is then required to have the following features:

- 1. A precise timing to associate the downstream  $\pi^+$  to the parent  $K^+$ .

- 2. Kinematic rejection of two- and three-body decays.

- 3. An hermetic veto system to reject events with  $\gamma$  and  $\mu$ .

- 4. A system for the identification of  $K^+$ s in the charged beam and to distinguish  $\pi^+$  from  $\mu^+$  and  $e^+$  in the final state.

The suppression of  $K^+ \to \pi^+ \pi^0$  and  $K^+ \to \mu^+ \nu$  decays is extremely important since they have branching ratios up to  $10^{10}$  times larger than the expected signal. The two-body kinematics reconstruction can be affected from background tails due to the missing detection of photons coming from  $K^+ \to \pi^+ \pi^0$  or if the muons of the  $K^+ \to \mu^+ \nu$  decay are wrongly detected as pions. To limit the background caused by two-body decays, kinematic rejection must be employed together with the particle identification (PID). Also three- and four-body decay background can be potentially harmful.

Table 1.1 shows the most frequent  $K^+$  decays modes together with their rejection techniques.

## 1.3.1 Kinematic rejection

The signal reconstruction is based on one reconstructed track in the downstream spectrometer and one in the beam spectrometer. The kinematics of the decay

| Decay mode                                | BR     | Background rejection              |

|-------------------------------------------|--------|-----------------------------------|

| $K^+ \to \mu^+ \nu \ (K_{\mu 2})$         | 63.55% | $\mu$ PID, two-body kinematics    |

| $K^+ \to \pi^+ \pi^0$                     | 20.66% | Photon veto, two-body kinematics  |

| $K^+ \rightarrow \pi^+ \pi^+ \pi^-$       | 5.59%  | Charged particle veto, kinematics |

| $K^+ \to \pi^+ \pi^0 \pi^0$               | 1.761% | Photon veto, kinematics           |

| $K^+ \to \pi^0 \mu^+ \nu \ (K_{\mu 3}^+)$ | 3.353% | Photon veto, $\mu$ PID            |

| $K^+ \to \pi^0 e^+ \nu \ (K_{e3}^+)$      | 5.07%  | Photon veto, $E/p$                |

**Table 1.1:** The most frequent decay modes of the  $K^+$  meson.

**Figure 1.6:** Kinematics of the decay under study.

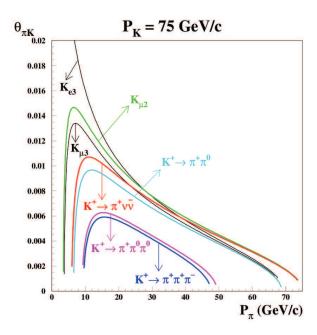

under study is sketched in Figure 1.6, where the incoming kaon momentum  $P_K$ , the momentum of the outgoing pion  $P_{\pi}$  and finally the angle between the parent and the downstream particle  $\theta_{\pi K}$ , are the only measurable quantities. The kinematics of the most frequent  $K^+$  decays are compared to that of the  $K^+ \to \pi^+ \nu \bar{\nu}$  in Figure 1.7.

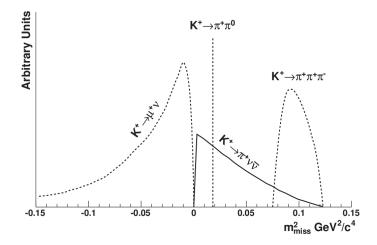

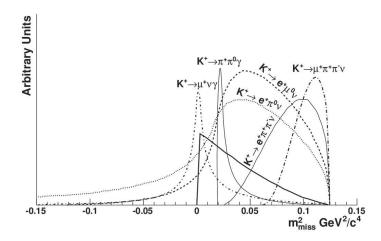

The squared missing mass is considered as the main kinematic variable, defined as  $m_{miss}^2 \equiv (P_K - P_{track})^2$ , where P are the 4-momenta of the particles and the track is assumed to be a  $\pi^+$ .

This quantity can be rewritten using the relation of the invariant mass  $m_{miss}^2 = E_{miss}^2 - \vec{P}_{miss}^2$  and then approximated as:

$$m_{miss}^2 \simeq m_K^2 \left( 1 - \frac{|P_{\pi}|}{|P_K|} \right) + m_{\pi}^2 \left( 1 - \frac{|P_K|}{|P_{\pi}|} \right) - |P_K| |P_{\pi}| \theta_{\pi K}^2$$

(1.19)

The squared missing mass can discern two categories of background: one is kinematically constrained (Figure 1.8) and the other is kinematically not-constrained (Figure 1.9). More than 90% of the total  $K^+$  branching fraction is composed by kinematically constrained decays. Among them, the signal  $K^+ \to \pi^+ \pi^0$  is the most insidious, being a line at  $m_{miss}^2 = m_{\pi^0}^2$  (ignoring mass resolution effects), lying within the signal region. The  $m_{miss}^2$  of three-body decays has a lower limit. The  $m_{miss}^2$  of  $K_{\mu 2}$  is not constrained to a line at  $m_{miss}^2 = 0$  since the muon is considered mis-identified as a pion and then depends on the final particle momentum and has  $m_{miss}^2 = 0$  as upper bound.

Since the  $K^+ \to \pi^+ \pi^0$  decay line is placed inside the signal region, it is necessary to split the signal acceptance into two regions:

- Region II:  $m_{\pi^0}^2 + (\Delta m)^2 < m_{miss}^2 < \min m_{miss}^2 (\pi^+\pi^+\pi^-) (\Delta m)^2$

**Figure 1.7:** A comparison of the charged track angle-momentum relation for the most frequent  $K^+$  decays and  $K^+ \to \pi^+ \nu \bar{\nu}$ . For the three-body decays, the curves indicate the kinematical limit.

**Figure 1.8:** Shape of the  $m_{miss}^2$  for signal (thick solid line) and background events under the hypothesis that the charged track is a pion. These background sources refer to decays which are kinematically constrained.

**Figure 1.9:** Shape of the  $m_{miss}^2$  for signal (thick solid line) and background events under the hypothesis that the charged track is a pion. These background sources refer to decays which are kinematically not-constrained.

where the  $\Delta m$  term depends on the  $m_{miss}^2$  resolution.

Background can then enter the signal region because of the finite resolution on  $m_{miss}^2$ . In order to minimize  $m_{miss}^2$  indetermination and consequently lower background contributions, low mass and high precision detectors placed in vacuum are required for the tracking.

The high particle rate on the beam detector (750 MHz) demands a close time correspondence and a good spatial resolution in order to associate the incoming kaon to the downstream pion track. Any missed correspondence between the two tracks causes a loss of kinematic rejection power. A Čerenkov Differential Counter (KTAG) placed on the beam line, the Gigatracker beam tracker (silicon pixel detector) and a RICH (Ring Imaging Čerenkov counter), provide the timing of the experiment. Notably the beam tracker must reconstruct the beam tracks with at least 150 ps time resolution.

The correspondence between the two tracks is reconstructed mainly (apart from timing) using a cut on the closest distance of approach (CDA) between the Gigatracker and the downstream spectrometer. The latter, called Straw Tracker, is positioned in vacuum and provides the track momentum measurement.

Geant4 simulations [23, 24] show a resolution on kaon momentum of about 0.2%, on kaon direction of about 16 µrad, on pion momentum of about (0.330  $\pm$  0.007)%× $P_{track}$  and on pion direction between 45 and 15 µrad. The expected kinematic rejection power against  $K^+ \to \pi^+ \pi^0$  and  $K^+ \to \mu^+ \nu$  decays is then about  $2 \times 10^4$  and  $2 \times 10^5$ , respectively. The limitation comes from the non-Gaussian tails from multiple scattering in the detector materials and from a possible  $K^+$  -  $\pi^+$  mismatching.

#### 1.3.2 Vetoes

The requested level of background suppression needs an additional factor coming from  $\gamma$  and  $\mu$  detection, since the kinematic rejection alone cannot respect the requirements. Particularly the rejection of the  $K^+ \to \pi^+\pi^0$  decay, with the requirement of a  $10^{-8}$  inefficiency for  $\pi^0$  detection, is the main point in the design of the photon veto system. A photon detector system that can hermetically cover an angular region up to  $\approx 50$  mrad around the beam axis is then required. The detectors designed for this purpose are, in order of increasing angular coverage: SAC (Small Angle Calorimeter) and IRC (Intermediate Ring Calorimeter) covering respectively forward and small angles ( $\lesssim 1$  mrad), the Liquid Krypton electro-magnetic calorimeter (LKr) covering the region between 1 and 8.5 mrad and finally 12 Large Angle photon Veto (LAV) detectors covering the region between 8.5 and 50 mrad.

The key points to fulfil the experimental goals are:

- A cut at 35 GeV/c in the maximum  $\pi^+$  momentum at analysis level to deal with  $\pi^0$  of at least 40 GeV/c as a consequence of the 75 GeV/c kaon momentum.

- A detection inefficiency below  $10^{-5}$  for  $\gamma$ s in the 1 10 mrad region above 10 GeV and, anyhow, within  $10^{-3}$  for  $\gamma$  down to 1 GeV.

Since the largest fraction of  $K^+$  decays contains muons in the final state, a muon veto system is mandatory. The Muon Veto system (MUV), placed at the end of the experimental apparatus, consists of two iron-scintillator hadronic calorimeter (MUV1 and MUV2) and, behind an iron wall, a plane of fast scintillators (MUV3). The MUV system is placed at the end of the apparatus. Monte Carlo simulations predict an overall inefficiency for muon detection of about  $10^{-5}$ , achievable by exploiting the electromagnetic and hadronic shower separation capability of the hadronic and LKr calorimeters together. Further muon rejection is provided by the Ring Imaging Čerenkov counter (RICH).

Finally a veto for charged and neutral particles placed just downstream of the last GTK station, provides additional rejection of the accidental background coming from hadronic interactions of the beam particles in the last GTK station. This detector, called CHANTI, consists of scintillators surrounding the beam.

#### 1.3.3 Particle Identification

Kinematically not-constrained backgrounds (Figure 1.9) are the 8% of the total branching and are shown partially in Table 1.2. These backgrounds cannot be suppressed by the kinematic rejection and vetoes alone. The needed additional  $10^2$  factor in the background rejection will come from a particle identification system complementary to the calorimeters. A RICH has been designed to fulfil such a goal: it should separate  $\pi^+$  from  $\mu^+$  with inefficiency below 1% in the relevant momentum range. It must also provide the timing of the event with a

| Decay mode                                      | Branching ratio               |

|-------------------------------------------------|-------------------------------|

| $K^+ \to \pi^0 e^+ \nu \ (K_{e3}^+)$            | $(5.07 \pm 0.04)\%$           |

| $K^+ \to \pi^0 \mu^+ \nu \ (K_{\mu 3}^+)$       | $(3.353 \pm 0.034)\%$         |

| $K^+ \to \mu^+ \nu \gamma \ (K_{\mu 2 \gamma})$ | $(6.2 \pm 0.8) \times 10^3$   |

| $K^+ \to \pi^+ \pi^- e^+ \nu \ (K_{e4})$        | $(4.09 \pm 0.10) \times 10^5$ |

| $K^+ \to \pi^+ \pi^- \mu^+ \nu \ (K_{\mu 4})$   | $(1.4 \pm 0.9) \times 10^5$   |

**Table 1.2:** Some  $K^+$  not-kinematically constrained decay modes.

resolution below 100 ps.

The LKr is a powerful particle identifier, not only for muons, as stated before, but also for positrons and electrons. It is, therefore, a viable option to complement the RICH in the suppression of final states with  $e^{\pm}$ . The  $\pi$  - e separation is possible, thanks to the LKr excellent energy resolution, by means of the E/p measurement.

Since about 93% of the beam particles are  $\pi^+$  or protons, the positive identification of the  $K^+$  is also important in the experiment. In fact these particles can produce a signature that can be associated to the signal by means of interaction with the residual gas contained in the vacuum tank. The  $K^+$  identification is achieved by the KTAG, operated to be blind to all particles but kaons of appropriate momentum.

The KTAG will also improve the rejection of candidates originating from pion and proton interactions on the last GTK station.

## 1.3.4 Sensitivity

A sensitivity analysis has been performed using Geant4 based simulations [24]. Results shows Region I acceptance to be  $\approx 3.5\%$  while Region II acceptance  $\approx 10.9\%$ . The overall acceptance is then about 14.4%, showing that the target of 10% of signal acceptance is safely achievable even taking into account efficiency losses caused by dead times and additional inefficiencies occurring in a real data taking.

The use of the RICH constrains the accepted pion tracks within the (15 – 35) GeV/c momentum range. The higher cut is an important loss of signal acceptance, but assures that events like  $K^+ \to \pi^+ \pi^0$  deposit at least 40 GeV of electromagnetic energy, making their rejection easier.

Many sources of background have been considered and just a simple counting of signal and background events in the signal regions indicates that the 10% background appears to be within reach.

# Chapter 2

# The NA62 experiment

In this Chapter, a brief description of the beam and main detectors of the NA62 experiment will be given. Main references used in this chapter are [23, 22].

# 2.1 Beam for the experiment

The charged kaon beam for the experiment is derived from the primary proton beam at 400 GeV/c of the SPS impinging a beryllium target. With the use of an empirical formula has been calculated that the maximum  $K^+$  production, per primary proton at fixed momentum  $p_0$ , occurs for  $p_K \approx 0.35 \times p_0$ . In addition  $K^+$  production increases as  $p_K^2$  (and also as  $p_0^2$ ).

It can be calculated that the maximum number of  $K^+$  decays, in the defined fiducial length constrained by detector geometry, is maximum when  $p_K \approx 0.23 \times p_0$  and it increases as  $p_K$  (and therefore as  $p_0$ ). Moreover, at higher energy, detectors like calorimeters, photon- and muon-veto counters, have better performances in terms of acceptance, resolution and efficiency. The choice of a positive kaon beam is motivated by the ratio of the production rates:  $K^+/K^- \approx 2.1$  (for a 400 GeV/c proton beam).

A kaon momentum of 75 GeV/c has been chosen as central value. This is a compromise of the parameters listed in Table 2.1.

The number of produced  $K^+$  and the percentage in the beam increases with the momentum, but there are other aspects to take into consideration: the distance of the decay region (102 m from target), the length of decay region itself (65 m) and the detector acceptance (particles near the beam pipe can not be detected).

The hadron beam is derived from the existing target station T10. The elements are installed along the K12 beam line in Hall ECN3 at SPS North Area.

The 102 m long beam line selects a 75 GeV/c, narrow momentum-band (1.2% RMS), beam with an average rate of 750 MHz distributed on a 14 cm<sup>2</sup> area. The secondary beam is positron-free and composed by  $\sim 6\%$  of  $K^+$ . The described beam line should produce  $5 \times 10^{12} K^+$  decays assuming a 65 m decay region and 100 run day at 60% efficiency.

| Beam characteristics                                                    |                            | 60  GeV/c | 75  GeV/c | 120  GeV/c |

|-------------------------------------------------------------------------|----------------------------|-----------|-----------|------------|

|                                                                         | $p \times 10^6$            | 89        | 171       | 550        |

| Fluxes at production for $10^{12}$ incident protons per s               | $K^+ \times 10^6$          | 40        | 53        | 71         |

| raixes at production for 10 medent protons per s                        | $\pi^+ \times 10^6$        | 353       | 532       | 825        |

|                                                                         | Total $\times 10^6$        | 482       | 756       | 1446       |

| Survival factor over 102 m                                              | $K^+$                      | 0.797     | 0.834     | 0.893      |

| Survival factor over 102 III                                            | $\pi^+$                    | 0.970     | 0.976     | 0.985      |

|                                                                         | $p \times 10^6$            | 89        | 173       | 550        |

| Fluxes at 102 m from target for 10 <sup>12</sup> incident protons per s | $K^+ \times 10^6$          | 32        | 45        | 63         |

| Fluxes at 102 in from target for 10 medent protons per s                | $\pi^+ \times 10^6$        | 343       | 525       | 813        |

|                                                                         | Total $\times 10^6$        | 464       | 743       | 1426       |

| Decays in 60 m fiducial length for $10^{12}$ incident protons per s     | $K^+ \times 10^6$          | 3.9       | 4.5       | 4.1        |

| becays in 60 in inducial length for 10 meldent protons per s            | $\pi^+ \times 10^6$        | 6.1       | 7.4       | 7.2        |

| $K^+$ decays / $\pi^+$ decays in 60 m                                   |                            | 0.64      | 0.61      | 0.57       |

| $K^+$ decays in 60 m / total hadron flux                                | $\times 10^{-3}$           | 8.4       | 6.1       | 2.9        |

| $K^+ \to \pi^+ \nu \bar{\nu}$ acceptance (Region I, no $p_{\pi}$ cut)   |                            | 0.08      | 0.11      | 0.11       |

| Accepted $K^+ \to \pi^+ \nu \bar{\nu} / 10^{12}$ protons per s          | $\times 10^6 \times BR$    | 0.31      | 0.50      | 0.45       |

| Accepted $K^+ \to \pi^+ \nu \bar{\nu} / \pi^+$ decays in 60 m           | $\times BR$                | 0.052     | 0.067     | 0.062      |

| Accepted $K^+ \to \pi^+ \nu \bar{\nu}$ / total hadron flux              | $\times 10^{-3} \times BR$ | 0.67      | 0.67      | 0.31       |

**Table 2.1:** Criteria for the choice of the beam momentum.

The beam line design employs a triplet of radiation-resistant acceptance quadrupoles to focus the beam to the mid-point of a front-end achromat, which is composed of four dipole magnets to provide momentum selection and recombination. In the middle of the achromat the wanted beam is displaced vertically downwards by 100 mm, allowing its momentum band to be defined and primary protons and unwanted secondary hadrons to be dumped in the two motorized dump/collimator units (TAX), among which the  $e^+$  radiator is located. A subsequent quadrupole triplet refocuses the beam through a collimation and muon-sweeping stage.

A quadrupole doublet then renders the beam parallel, matching it to the KTAG differential Čerenkov counter. A final quadrupole doublet is used to match the beam to the spectrometer and tracking system, whilst limiting the beam size in the apertures of the downstream detectors.

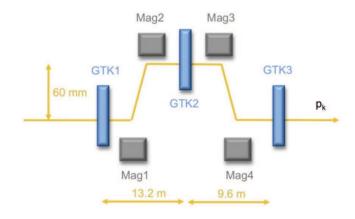

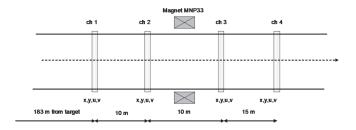

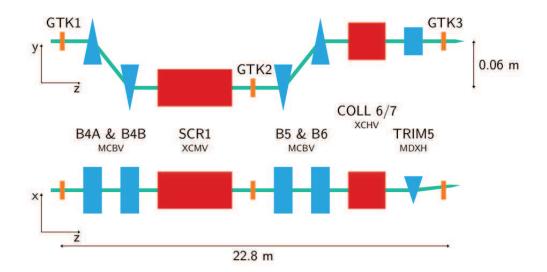

The beam tracking system consists of three GigaTracker (GTK) stations installed in vacuum. These are rearranged so that the space between GTK 1 and 3 is occupied by a toroidally magnetized muon scraper and a second achromat of four C-shaped dipole magnets, with their yokes arranged so as to enhance the defocusing action of the scraper for  $\mu^+$ . In the middle of the second achromat, where GTK 2 is located, the magnets cause a parallel displacement of the 75 GeV/c beam by +60 mm in the horizontal plane to provide the momentum measurement. GTK 3 is placed after the final (variable) cleaning collimator and is followed by a guard-ring of scintillation counters (CHANTI) mounted in vacuum.

The opposite deflections of the last two magnets of the second achromat are actually so tuned that the beam is centred at GTK 3, but is directed away from the axis by -1.2 mrad in the horizontal plane. This angle is chosen so that the subsequent Single Spectrometer magnet will deflect the beam back into the central aperture of the LKr calorimeter.

The magnet provides a  $p_T$ -kick of +270 MeV/c, giving a +3.6 mrad deflection to the +75 GeV/c beam. In conjunction with the upstream deflection of -1.2 mrad, the beam thereby converges to the undeflected beam axis at a point near the exit of the LKr calorimeter.

The beam is finally deflected to the side by a 3 m long dipole magnet which provides a  $+1620 \text{ MeV}/c p_T$ -kick (+21.6 mrad deflection) and dumped in a concrete plug inside an hole at the end of Hall ECN3.

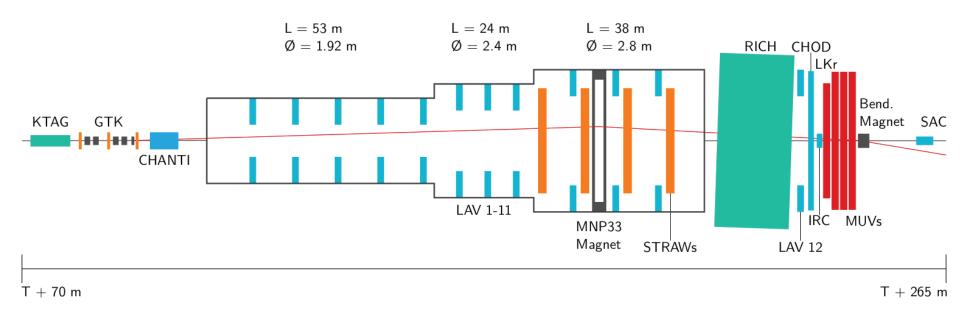

### 2.2 Detectors

In this section will be given a description of each sub-detectors. The following detectors and features are incorporated in the NA62 layout (see Figure 2.1).

To better understand Figure 2.1 refer to the acronyms list below:

#### • KTAG

A differential Cerenkov counter placed on the incoming beam to tag the

minority particles of interest (kaons).

#### • GigaTracker (GTK)

Thin silicon micro-pixel detectors for direction and momentum measurement of the incoming beam particles with sub-nanosecond time resolution to provide a tight time coincidence between the incoming kaon and the outgoing pion before entering the decay region.

#### • CHANTI (Charged ANTI counter)

A set of six ring scintillation anti-counters positioned after the last GTK station to form a guard-ring at the beginning of the decay region to provide a veto to charged particles outgoing from the collimator and produced from strong interactions in GTK 3.

#### • LAV (Large Angle Veto)

A set of 12 ring-shaped scintillation anti-counters surrounding the vacuum tank and providing full coverage for photons originating from the decay region with angles between 8.5 and 50 mrad.

#### • Straw Tracker

A magnetic spectrometer measuring the direction and momentum of the outgoing charged decay products. Four chambers of straw tubes are used as the tracking detector for their capability to operate in vacuum along with a dipole magnet.

#### • RICH

A gas Ring Imaging Čerenkov counter providing muon/pion separation.

#### • CHOD (Charged Hodoscope)

A charged-particle hodoscope, positioned between the RICH and the LKr calorimeter, covering the acceptance and providing a veto for interactions in the RICH material.

#### • LKr (Liquid Krypton Calorimeter)

An high-resolution electromagnetic calorimeter acting as photon veto in 1 to 8.5 mrad region.

#### • MUV (Muon Veto)

Two-part hadron calorimeter followed by an additional iron and a fast scintillator muon veto. This system supplement and provides redundancy with respect to the RICH in the detection and rejection of muons and to measure pion energy.

• IRC (Intermediate Ring Calorimeter) and SAC (Small Angle Calorimeter) Intermediate ring and small angle photon veto calorimeters covering the angular regions around and in the beam.

Figure 2.1: Longitudinal view of the NA62 experimental setup.

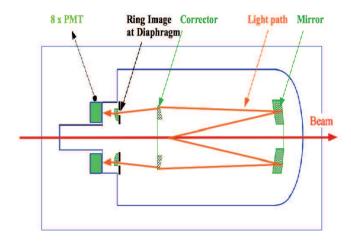

Figure 2.2: Schematic layout of KTAG detector.

#### 2.2.1 KTAG

The KTAG consists of a pressure vessel of 558 mm diameter and  $\sim 5$  m long, filled with gas maintained at a precisely controlled pressure. A spherical Mangin mirror placed at the downstream end of the vessel reflects the Čerenkov light onto a ring-shaped diaphragm of 100 mm radius with adjustable aperture width, located at the beginning of the vessel as in Figure 2.2. Eight sectors equipped with 48 photo-multipliers are placed behind the slit; the coincidence of at least 6 of them will indicate the passage of a particle of the wanted mass since Čerenkov angle of the light produced by the particles traversing the vessel is function of their masses. Trimming the pressure of the gas it is possible to transmit through the diaphragm only the light produced by a  $K^+$  particle at a given angle, whilst light associated to protons and pions will be stopped. The rate in the detector is limited to 50 MHz, which corresponds to the kaon rate in the beam.

Finally, to increase the efficiency of the light collection, a system of corrector lenses redirect the light rays to the diaphragm with the same radius independently on the wavelength and point of emissions.

NA62 uses an updated version of the West CEDAR built for the SPS secondary beams. The main characteristics are listed in Table 2.2. The KTAG detector is required to achieve a kaon efficiency of at least 95%, with a time resolution of 100 ps. Multiple photo-detectors were developed to achieve a singles rate on each pixel not higher than 3 MHz mm<sup>-2</sup>. The KTAG includes upgraded optics, photo-detectors, associated mechanics and electronics.

## 2.2.2 GigaTracker

The beam spectrometer is one of the key elements for the NA62 experiment. It has to provide a precise time, angle and momentum measurement of all the incoming particles in the 75  $\,\mathrm{GeV}/c$  beam. In particular the GTK has to measure

| Gas type                                                                   | $\mathrm{H}_2$            |

|----------------------------------------------------------------------------|---------------------------|

| n-1                                                                        | $\sim 142 \times 10^{-6}$ |

| Nominal pressure for kaons                                                 | 3.85 bar                  |

| $\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;$ | 30.9  mrad                |

| Kaon rate                                                                  | 50  MHz                   |

| Time resolution                                                            | $< 100 \; ps$             |

| $\Delta\theta/\theta$                                                      | $4.8 \times 10^{-3}$      |

| $\Delta \beta / \beta$                                                     | $5 \times 10^{-6}$        |

| Number of photons per kaon                                                 | 100                       |

| Rate per photomultiplier                                                   | 3 MHz                     |

Table 2.2: Characteristics and resolutions of the KTAG.

Figure 2.3: Layout of the GigaTracker stations.

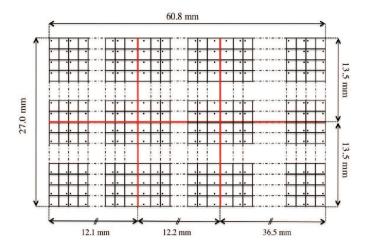

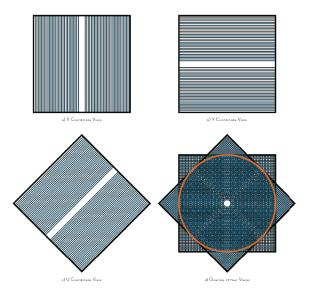

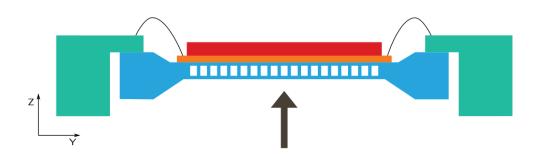

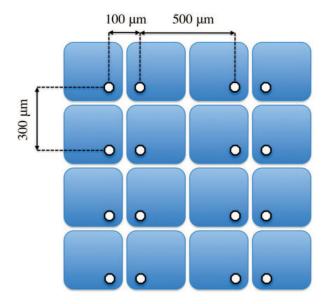

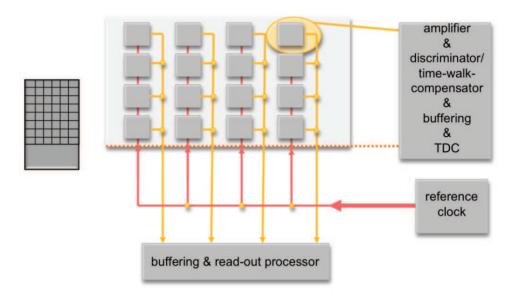

the momentum with relative resolution of  $\sigma(p_K)/p_K \sim 0.2\%$  and the direction with a resolution of  $\sim 16~\mu rad$ . The detector is exposed to a very high and non-uniform beam rate of 0.75 GHz in total, with a peak of intensity around the centre of 1.3 MHz/mm<sup>2</sup>. The GigaTracker is composed of three stations of hybrid silicon pixels sensors mounted on the beam around four dipole magnets and inside the vacuum tank as in Figure 2.3. The distance between GTK1 and GTK2 is 13.2 m, between GTK2 and GTK3 is 9.6 m. To compensate the vertical bending of the beam at the achromat the GTK2 is displaced vertically by 60 mm. Each station covers an area of 60.8(x) mm  $\times 27.0(y)$  mm, matching the expected beam dimension, and is subdivided in  $(300 \times 300) \mu m^2$  hybrid p-in-n (or n-in-p) pixels with 200  $\mu$ m thickness. Pixels are arranged in 10 12.0(x) mm × 13.5(y) mm matrix, each with 1800 pixels as in Figure 2.4. The pixel thickness is a compromise between the request of a small material budget to avoid multiple scattering and the need of a sufficient charge yield ( $\approx 15000 \ e^{-}$ ). Table 2.3 summarizes the material budget of the active components in the beam. The required time resolution of the GTK on every single track is  $\approx 150$  ps (RMS) to resolve the high intensity beam. The stringent time resolution requires a design where the

Figure 2.4: Layout of the GigaTracker sensors.

| Component    | Material | Thickness [µm] | $X_0[\%]$  |

|--------------|----------|----------------|------------|

| Sensor       | Si       | 200            | 0.22       |

| Bump bonds   | Pb-Sn    | $\sim 25$      | 0.001      |

| Readout chip | Si       | 100            | 0.11       |

| Cooling      | Si       | $\sim 200$     | $\sim 0.2$ |

Table 2.3: Material budget of sensor, read-out chip and bump bonds per station.

on-pixel front-end is optimized to enhance the time performances and obtain a time resolution of 200 ps for each pixel hit (RMS).

Each component of the hybrid silicon pixel is optimized in terms of material budget and performance. For the on-detector read-out system integration the following parameters are optimized:

- Material budget in active beam area.

- Read-out chip size and active matrix size

- Accessibility to power and I/O connections on the chip

- Particle rate per pixel

- Heat dissipation and cooling

The main topics regarding the GigaTracker will be studied in detail in Chapter 3.

#### 2.2.3 CHANTI

The general veto design foresees a six ring anti-counter after the last GigaTracker station (GTK3) in order to detect the charged particles produced by inelastic interactions of the beam with the collimator and the GTK stations. The necessity of such a system arises from the fact that pions, or other charged particles, produced at small angles, can reach the Straw Tracker and mimic a kaon decay in the fiducial region.

The detector consists of 6 stations made up of two rectangular layers (x and y) composed by two sub-layers of scintillator bars. Each bar is triangularly shaped and staggered bars are arranged in order to face oppositely in order to fill intergaps. Light is collected by means of one WLS (Wave Length Shifter) fiber placed inside each bar and read at one side by a silicon photomultiplier.

The CHANTI, by itself , is able to veto about 95% of all inelastic interactions of  $K^+$  in GTK3 regardless of the final state. This vetoing efficiency reach almost 99% if one restricts to potentially signal-like events.

#### 2.2.4 LAV

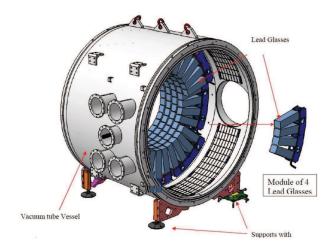

The Large Angle Veto is made of 12 stations placed along z axis between 120 and 240 m (see Figure 2.1) inside the vacuum decay tube except the last one.

These detectors are composed of lead glass crystals with attached photo-multipliers (PM) from the OPAL electromagnetic calorimeter. Each lead glass block is a 370 mm long truncated prism of SF57 lead glass. The light is collected by an Hamamatsu R2238 PMT glued to the crystal through a lead glass light guide. The guide and the PM are enclosed by an external mu-metal shield.

Crystal detectors (lead glass crystals + PMs) are assembled radially inside the vacuum tube to form a complete ring of lead glass blocks. Each LAV station

**Figure 2.5:** LAV: Complete station layout.

Figure 2.6: The Straw Tracker layout.

is made up of 4 or 5 rings, which are staggered in azimuth providing complete hermeticity of at least three blocks (20  $X_0$ ) in the longitudinal direction. The layout of a complete station is shown in Figure 2.5.

The LAV has been optimized to detect photons with inefficiency lower than  $10^{-4}$  well suited by the measured inefficiency of the lead glass blocks (studied at Daphne BTF in Frascati) and a timing resolution lower than 1 ns.

#### 2.2.5 Straw Tracker

The downstream magnetic spectrometer is essential to measure the momentum and angle of secondary particle tracks and it consists of four chambers intercepted in the middle by an high aperture dipole magnet providing a vertical B-field of 0.36 T (Figure 2.6).

Two principal performance requirement follow from  $\Delta P/P \leq 1\%$  and  $\Delta \theta_{K\pi} \leq$  60 µrad. This implies the minimization of the amount of material crossed by the particles. It means that every straw chamber has a limit of  $\leq 0.5\%~X_0$ . In addition, to reduce the multiple Coulomb scattering, the tracker must operate in vacuum and so it will be installed in the decay region.

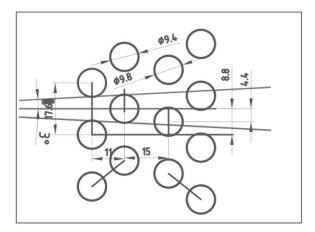

Figure 2.7: Schematic layout of the four views of a chamber.

Each straw chamber is made of four views (x,y,u,v) rotated with respect to the following by 45° providing measurement of four coordinates and enhancing the spatial resolution per space point  $\leq 80~\mu m$  (Figure 2.7). Finally each view consists of four staggered layers of 112 straw tubes of 2.1 m length (in Figure 2.8), increasing the coordinate resolution beside solving left-right ambiguity and maintaining a material budget of  $\sim 0.1\%~X_0$  per view. A region free of tubes, 12 cm large, in the middle of each view-plane form an octagonal hole in each chamber where the intense charged beam of undecayed particles pass through. The dipole magnet, placed after the second chamber, gives a 256 MeV/c momentum kick in the horizontal plane to allow momentum measurement. The chambers are displaced in the bending plane according to the 75 GeV/c positive beam path. Straw tubes are composed by a cylindrical Mylar 9.75 mm diameter tube, internally metallised with gold-plated copper; Mylar wall thickness is 36  $\mu$ m. Inside the tube is placed a 30  $\mu$ m diameter gold-plated Tungsten wire. Each straw tube is filled with a gas mixture of CO<sub>2</sub> (80%), Isobutan C<sub>4</sub>H<sub>10</sub> (10%), CF<sup>4</sup> (10%).

#### 2.2.6 RICH

The Ring Imaging Cerenkov counter is needed to:

- Provide separation of  $\pi^+$  from  $\mu^+$  between 15 and 35 GeV/c momentum providing a muon suppression factor of at least  $10^{-2}$ ;

- Measure the pion crossing time with a resolution of about 100 ps or better;

- Produce the L0 trigger for a charged track.

Figure 2.8: Straw staggered layers.

The detector is placed between the last Straw chamber and the LKr (Figure 2.1). It consists of a steel cylindrical vessel 17 m long and 3 m large around the beam pipe. The vessel is filled with neon gas at a slight overpressure w.r.t. the external atmosphere.

A charged particle of velocity  $\beta$  crossing the gas volume, with index of refraction n, emits a cone of radiation with angle  $\theta_c$  with respect to the particle trajectory:

$$\cos \theta_c = \frac{1}{n\beta} \tag{2.1}$$

The momentum threshold for a charged particle of mass m to emit Čerenkov radiation is related to the index n by the equation:

$$p_t = \frac{m}{\sqrt{n^2 - 1}} \tag{2.2}$$

The neon gas has the right index of refraction to guarantee the maximum efficiency for a 15  ${\rm GeV}/c$  pion.

Inside the vessel is placed a 17 cm diameter beam tube used to let the undecayed particles to pass through in vacuum.

At the downstream end of the vessel a mosaic of mirrors is placed; in order to avoid the beam pipe shadow, Čerenkov photons are reflected by two groups of mirrors pointing to two different regions. The focal length of the mirrors is 17 m. Each focal region is equipped with about 1000 PMs Hamamatsu R7400-U03 with a pixel size of 18 mm, ensuring a quantum efficiency and time performances which fit the requirements, in a compact hexagonal packing. The active area of each PM is about 8 mm large and a Winston cone is used to direct the Čerenkov light from the 18 mm pixel size. The centre of each PMs region is about 1 m far from the beam pipe axis. The schematic layout of the RICH detector is shown in Figure

**Figure 2.9:** Schematic view of the RICH detector; the downstream section shows the mirror mosaic. The upstream section shows the 2 PM arrays with a magnification of one array.

2.9.

#### 2.2.7 CHOD

The NA48 charged hodoscope is composed by a system of scintillation counters with high granularity and excellent time resolution (200 ps). It is supposed to detect possible photo-nuclear reaction in the RICH mirror plane and back-up the RICH in the L0 trigger for the charged tracks.

The detector consists of 128 detection channels which are arranged in two plane (x-y) of 64 horizontal and vertical BC408 plastic scintillators covering a radius of 121 cm. The scintillation light is collected via a short Plexiglas fishtail light guide, followed by a Photonis XP2262B PM.

#### 2.2.8 New CHOD

A new charged hodoscope was designed and used for the first time in the 2016 run together with the old CHOD. The main reason to build the New CHOD is the high hit rate at which the long slabs (1 m) of the CHOD are exposed. The intrinsic dead time and the light transit time inside the scintillator are not compatible with the expected overall rate on the detector above 10 MHz.

The New CHOD is a two-dimensional array of 152 scintillator tiles installed after the LAV12. In each quadrant, a 30 mm thick plastic scintillator is divided into 38 tiles. The scintillation light is collected and transmitted by 1 mm diameter wavelength shifting fibres to be detected by arrays of  $3 \times 3$  mm<sup>2</sup> silicon photo-multipliers (SiPMs) on boards located on the periphery of the detector. A maximum rate of the order of 500 kHz is expected on the tiles close to the beam pipe. The signals are shaped using constant fraction discriminators to improve the time resolution.

#### 2.2.9 LKr

The electromagnetic calorimeter at liquid Kripton of NA48 will be used to cover intermediate region from 1 to 8.5 mrad for vetoing photons from  $K^+$  decays. In this region the photon detection inefficiency has to be  $10^{-5}$  for photons with energy above 35 GeV. The calorimeter is also supposed to provide trigger signals evaluating the energy deposition, in order to contribute reducing the L0 trigger rate.

The performances of the calorimeter as used in NA48 has been checked to be good for NA62 but, since the L0 rate is expected to be two order of magnitude larger, the old read-out system will no longer be usable. A CREAM (Calorimeter REAdout Module) has been designed for this end.

The TALK (Trigger Adapter for Liquid Krypton) board has been developed as an interface between the old and the new trigger system. In addition, other subsystem (e.g. the calibration system logic and software) will need updating.

Its efficiency for single  $\gamma$  detection above 2.5 GeV has been measured on data collected by NA48/2 in 2004 and during a test beam in 2006 and found in perfect agreement with the requirements (see Section 1.3).

#### $2.2.10 \quad MUV$

The target of the MUV system is to provide muon suppression with an overall inefficiency of about  $10^{-5}$ . The system consists of three distinct parts, called MUV1, MUV2 and MUV3 according to their longitudinal position along the beam axis. The first two, placed after the LKr, are classic iron-scintillator sandwich hadronic calorimeters for measurements of deposited energies and shower shapes of incident particles to distinguish hadronic from electromagnetic showers. MUV1 is composed by 24 layers of scintillator strips while MUV2 by 22.

After MUV1 and MUV2 and an 80 cm thick iron wall, the fast muon veto MUV3 module, has the aim of detecting non-showering muons and acts as muon veto detector at trigger level. To achieve the required time resolution of < 1 ns at each transversal position, a design is chosen, which employs scintillator tiles arranged to minimize differences in the light path trajectories.

#### 2.2.11 IRC and SAC

There are two types of small angle vetoes: Intermediate Ring Calorimeter (IRC) covering the beam tube between the LKr and the RICH, and the Small Angle Calorimeter (SAC) placed after the MUV and covering the region near zero degrees. Both detectors will be built using the shashlyk technique, which consists of lead-scintillator sandwiches and WLS fibers passing through them via holes, to collect the light.

Both the SAC and the IRC are exposed to photons with energies higher than 5 GeV. In order to achieve the necessary background suppression, both the SAC and the IRC have to provide detection inefficiency better than  $10^{-4}$ , achievable by a depth of at least  $16 X_0$ .

| Parameter                         | Value                         | Description                          |  |  |  |  |  |  |

|-----------------------------------|-------------------------------|--------------------------------------|--|--|--|--|--|--|

| $f(L0) \max$                      | 1 MHz                         | Maximum average L0 trigger rate      |  |  |  |  |  |  |

| $\Delta t(\text{L0}) \text{ min}$ | 75 ns                         | Minimum L0 trigger time separation   |  |  |  |  |  |  |

| $T(I \cap D)$ may                 | 100 на                        | Maximum latency for generation of    |  |  |  |  |  |  |

| $T(L0P) \max$                     | 100 μs                        | the L0 Trigger primitives            |  |  |  |  |  |  |

| $T(L0) \max$                      | 1 ms                          | Maximum total L0 trigger latency     |  |  |  |  |  |  |

| $f(L1) \max$                      | 100 kHz                       | Maximum average L1 trigger rate      |  |  |  |  |  |  |

| $T(L1) \max$                      | 1 s                           | Maximum total latency for L1 trigger |  |  |  |  |  |  |

| $f(L2) \max$                      | $\mathcal{O}(15 \text{ kHz})$ | Maximum average L2 trigger rate      |  |  |  |  |  |  |

| $T(L2) \max$                      | Spill period                  | Maximum total latency for L2 trigger |  |  |  |  |  |  |

|                                   |                               |                                      |  |  |  |  |  |  |

**Table 2.4:** Main TDAQ parameters.

## 2.3 Trigger and Data acquisition

The high hit rate and the consequent need of a good time resolution in order to have an efficient selection of the events, led the collaboration to use a TDC-based system for many detectors. Consequently most of the detectors of the experiment (KTAG, CHANTI, the LAVs, RICH, CHOD, NewCHOD and MUV3) are read out by a unified system built around TEL62 FPGA-based motherboards [5]. Depending on the requirements, up to four daughter boards can plugged in. Each TDCB daughter board interfaces four HPTDC chips [20]. The TEL62 memory buffers store the hits while waiting for a L0 trigger accept signal. The IRC, SAC, LKr, MUV1 and MUV2 are read out by CREAM boards [18]. Each module provide 32 channels connected to ADCs. The boards buffer the data while waiting for a L1 trigger decision. In parallel, it provides energy sums for triggering purposes.

The Straw Tracker electronics is based on the CARIOCA chips [11] integrated in custom FPGA-based cover front-end boards.

The GigaTracker employs as well its own readout chain that will be detailed in Sections 3 and 4.

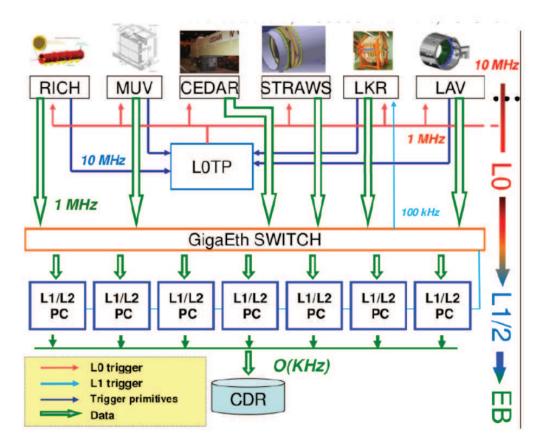

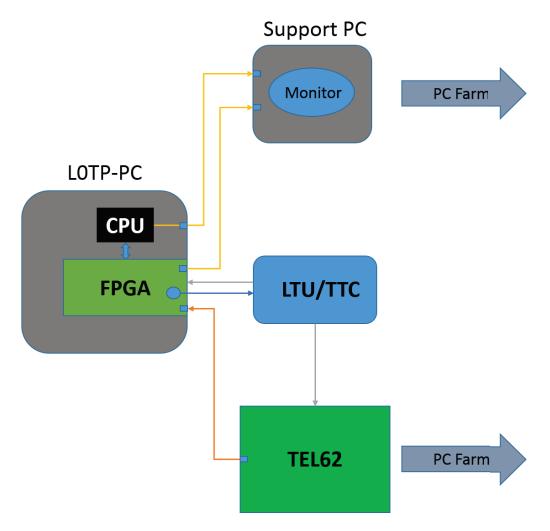

The interesting events are selected by a three-level fully digital trigger. The first level (Level-0 or L0) is implemented on FPGAs. The LAVs, RICH, CHOD, NewCHOD, LKr and MUV3 TEL62s are programmed to generate and send simple primitives to the Level-0 trigger processor (L0TP) [42]. A primitive is a 32-bit word built when a given set of conditions is met and immediately transmitted. The primitive generators apply subdetector-dependent time offsets to the generated primitives to ensure that they are aligned.

The L0TP stores the primitives from each subdetector in a RAM at the address defined by the primitive time. Next, it combines them and it looks for programmable matching conditions. For each match (or event), the L0TP sends a L0 trigger accept signal to all the subdetectors after a fixed latency of 1 ms. A 32-bit timestamp is assigned to the event using the time attached to the primitive

Figure 2.10: Logical scheme of the data-flow, trigger distribution and online farm.

coming from the reference detector. In response to the trigger accept signals, all the subdetectors, except CREAM-based ones and GTK, must send the corresponding hits to a PC farm for further evaluation. The CREAM readout and the GTK-PC store the data waiting for a L1 trigger decision.

The Level-1 (L1) and Level-2 (L2) trigger algorithms run on a off-the-shelf PC farm. The L1 routines have access to the complete data stream of individual subdetectors and can reconstruct higher level objects like tracks or clusters. Finally the L2 algorithms combines the information from all the subdetectors to make the final decision on whether to store the event or discard it. A summary of rates and the latencies is provided in Table 2.4.

The overall logical scheme of trigger and data acquisition is sketched in Figure 2.10.

## Chapter 3

# GigaTracker

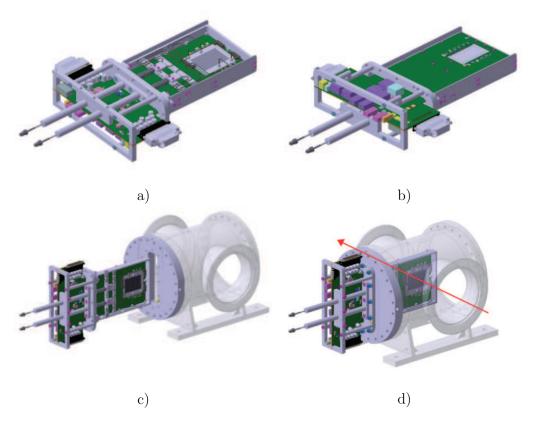

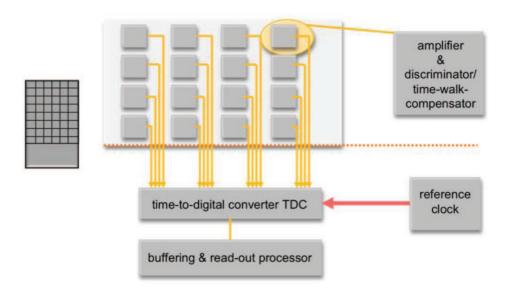

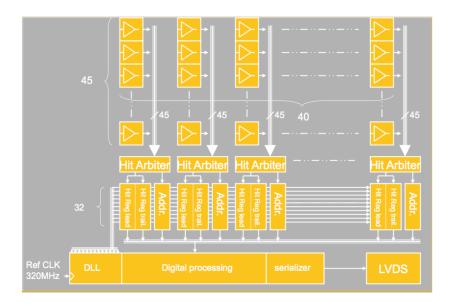

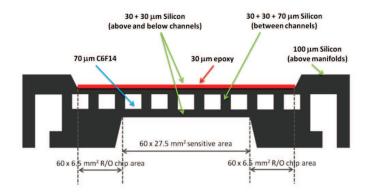

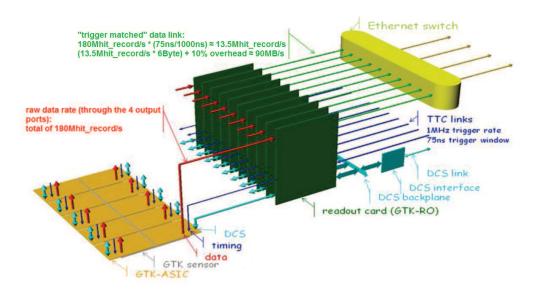

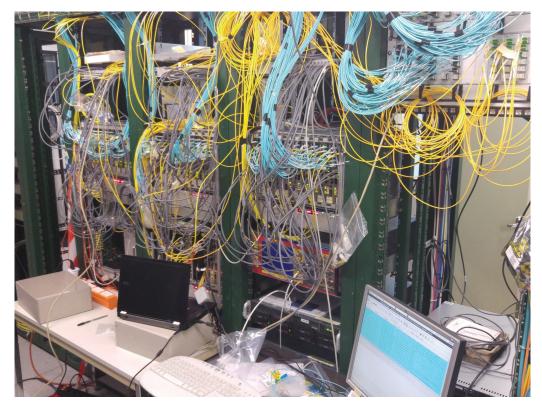

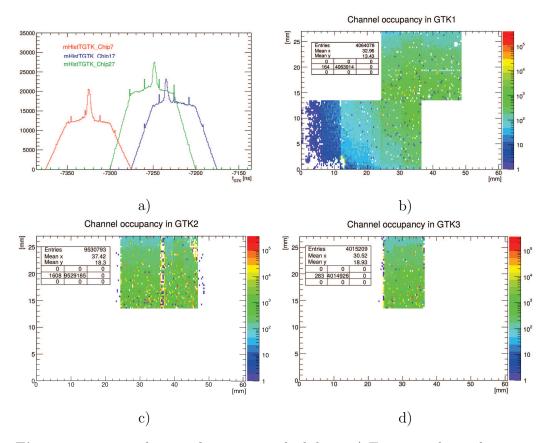

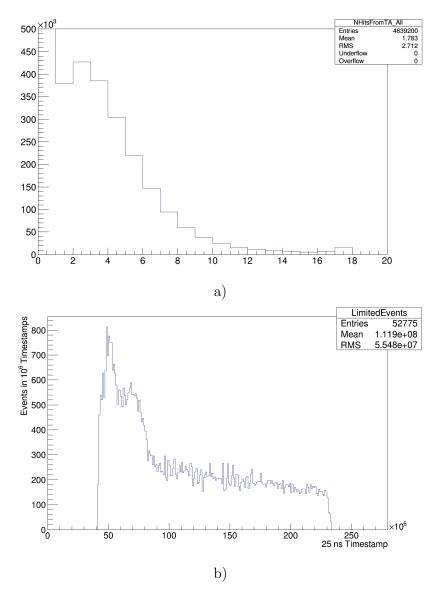

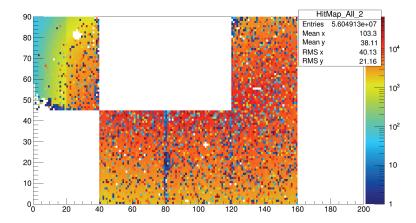

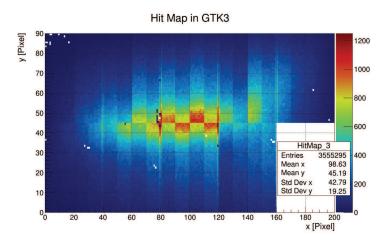

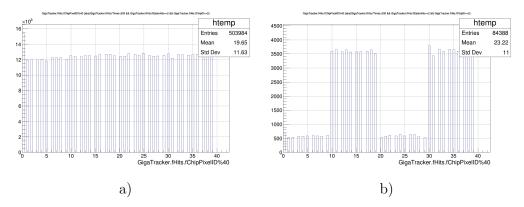

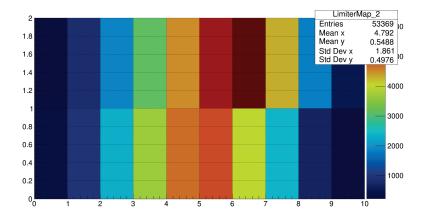

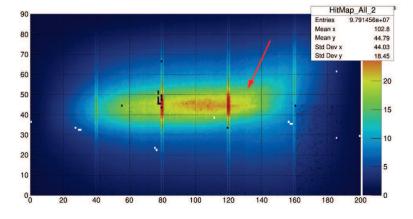

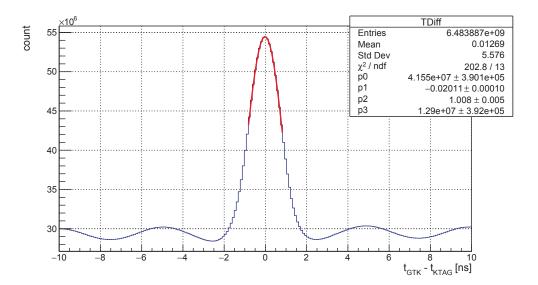

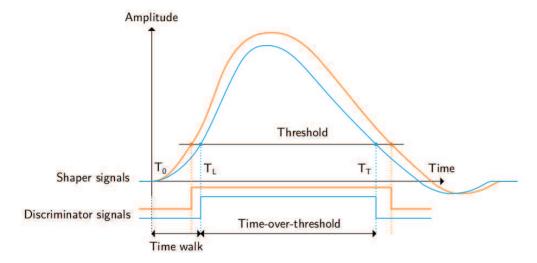

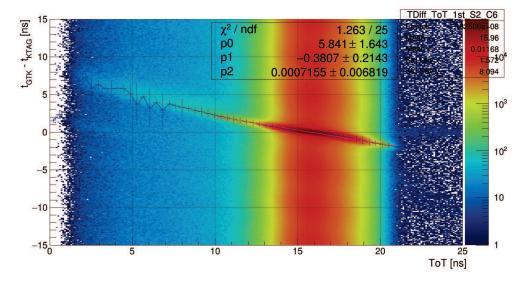

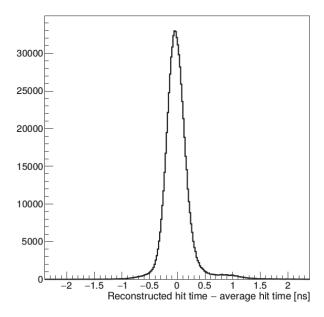

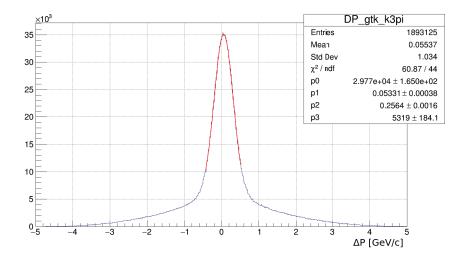

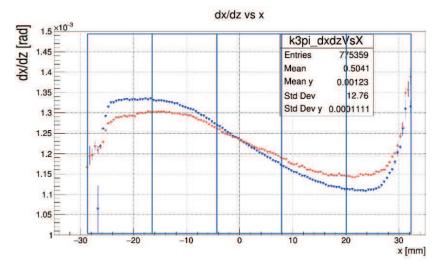

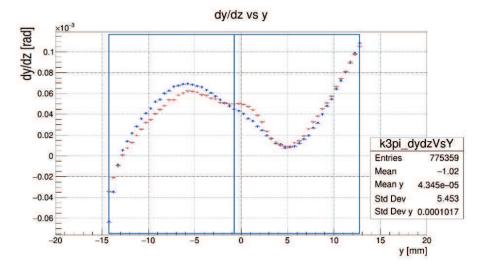

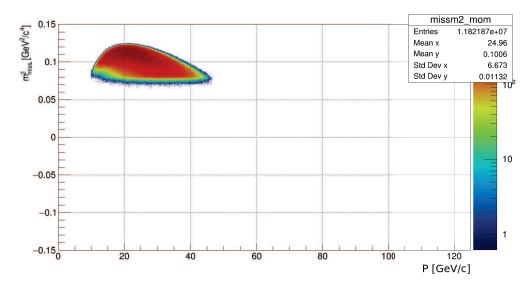

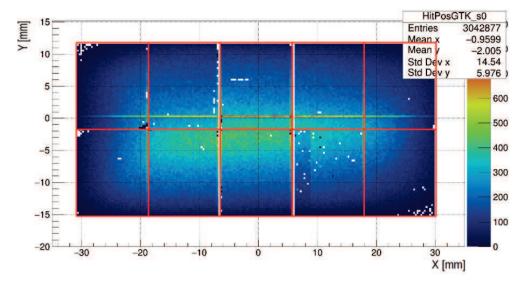

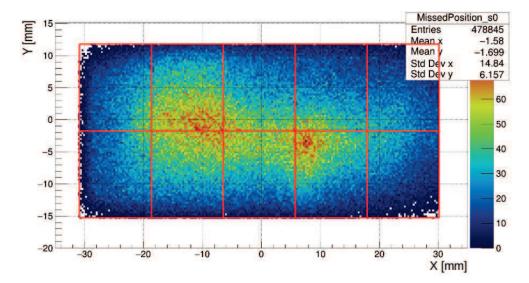

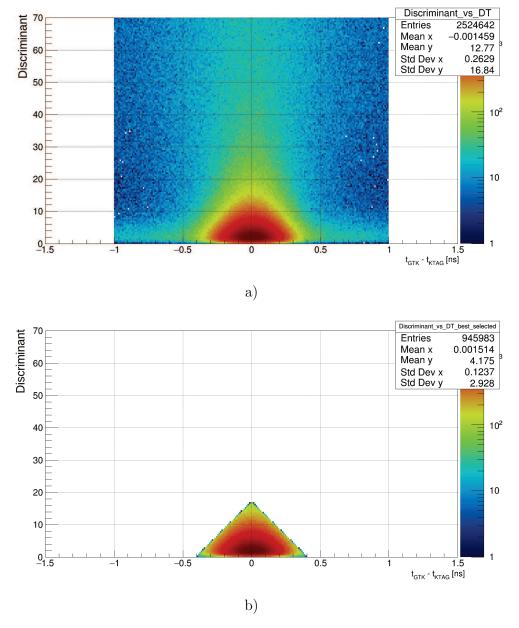

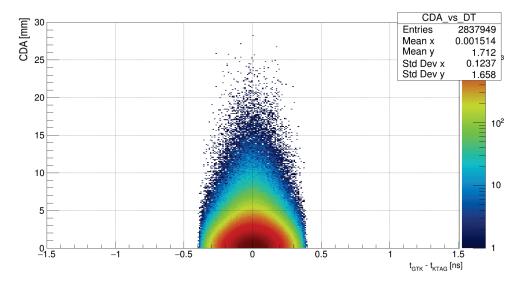

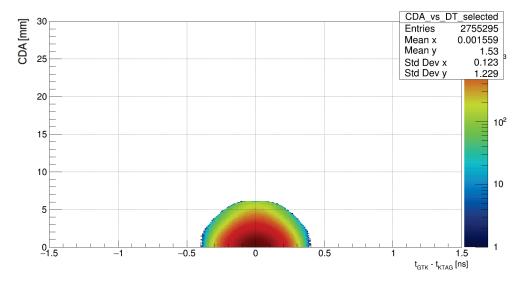

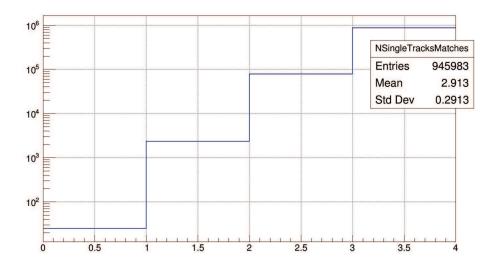

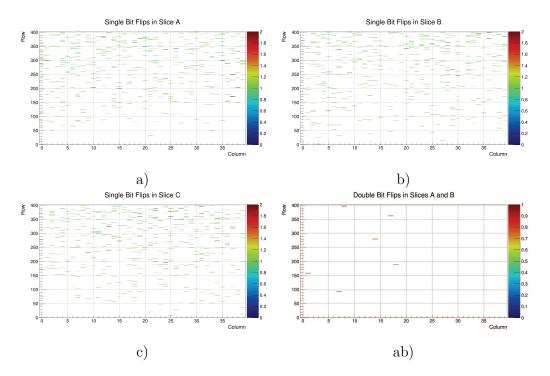

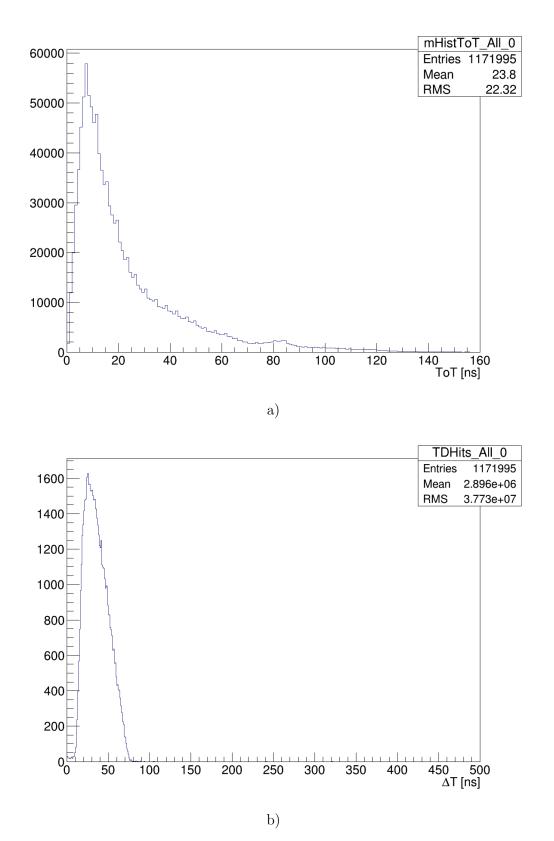

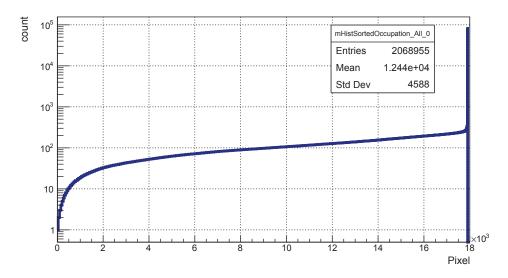

The GigaTracker (GTK) measures the momentum, the direction and the time of passage of all the NA62 secondary beam particles. Three constraints are immediately apparent: the detector has to cope with the high intensity hadron beam, the amount of matter in the beam path must be minimal to reduce the elastic and inelastic scatterings and the detector should be radiation hard.