# Radiation and Temperature Effects on the APV25 Readout Chip for the CMS Tracker

Etam Albert Noah Messomo

High Energy Physics Imperial College London Prince Consort Road London SW7 2BW

Thesis submitted to the University of London for the degree of Doctor of Philosophy

November 2002

## Abstract

The Compact Muon Solenoid (CMS) is one of four particle detectors designed for use at the Large Hadron Collider (LHC) currently under construction at CERN, the European Laboratory for Particle Physics in Geneva. The LHC will accelerate two counterrotating beams of protons to energies of 7 TeV and produce 10<sup>9</sup> proton-proton collisions per second at a bunch-crossing frequency of 40 MHz. These collisions occuring at the centre of CMS will generate a very hostile radiation environment.

The CMS sub-detector system closest to the collision point is the highly segmented Tracker, consisting of a silicon pixel detector with 45 million channels and a silicon microstrip detector with 10 million channels. The microstrip detector will be read out by the APV25, a custom-made chip manufactured in a commercial 0.25  $\mu$ m CMOS microelectronics process. Radiation and temperature studies are required to ensure that the APV25 can operate reliably in the CMS environment.

The radiation effects to which the APV25 could be susceptible are total dose effects and single event effects (SEE), such as single event upsets (SEU), single event gate ruptures (SEGR) and single event latchups (SEL). Approximately 75 000 chips will be used in CMS and confidence in total dose radiation tolerance will come from irradiating a subset of these chips to the radiation levels expected at CMS. For this purpose, a total dose radiation testing procedure was set up and the results obtained on a set of chips are presented, along with a detailed analysis of effects on discrete transistors. The need to periodically reset the chip during operation at CMS was determined from SEU tests. Along with transistor measurements, these also demonstrate immunity to SEGR and SEL.

The APV25 will be operated at -10 °C in CMS. Until recently, all testing of the chip was carried out at room temperature. An environmental chamber with a temperature range of 130°C to -40°C was used to investigate temperature effects on the APV25.

The measurements performed provide strong evidence that the APV25 will be fully functional throughout the lifetime of the CMS experiment. This is largely due to a combination of special design rules and intrinsic total dose radiation tolerance attributed to the thin gate oxide of the 0.25  $\mu$ m CMOS process.

## Acknowledgements

My stay in the HEP group is coming to an end and I am now slowly realising just how much I have benefited from working in it. I would like to thank Geoff Hall for his continuous support and for the trust he gave me throughout. Mark Raymond deserves a special mention for all the help he provided in every aspect of the work I undertook. His 'do it with a smile' approach will always be remembered.

I would like to express my gratitude to PPARC and RAL who jointly funded my research through the CASE award scheme. I sincerely hope it continues to provide support for research students well into the future. I would like to thank the many people at RAL involved with my work, in particular Mike Johnson and Marcus French.

Many people contributed to the work that is presented here. I worked closely with Jon Fulcher on SEU and consider myself fortunate that Jon is also a very good friend. I would like to thank Irving Dindoyal and David Johnson for their contributions to transistor measurements. I wish to thank Dario Bisello's team at Padova university for their help during beam tests and in particular Andrea Candelori for contributions to transistor irradiations. I would like to express my appreciation for the major contribution Markus Friedl made to the pion beam tests. Thanks are due to Maria and Sarah for bonding numerous chips and test structures and to Dave and Ian for their help in the lab.

The source of the motivation that led me to undertake this thesis is derived from many people and Dr Dolby, my 'A' level physics teacher, shares a large portion of the blame. I was also very lucky to meet Federico Faccio who first introduced me to the subject of commercial microelectronics in radiation environments during my stay in the Microelectronics group at CERN a few years ago.

I would like to dedicate this thesis to my 'second family', Steve, Fiona, Michele, Dean and Aubrey Thomas, who supported me during my first year in Christchurch and to my mum, dad, Melena, Monti and two grans. I would like to thank Jane for her love, support and patience.

I have had a lot of fun working in the 'Silicon lab', and enjoying the occasional one down Finnegans with Barry, Greg, Jon, Emlyn, Rob and Mat. I wrote this section in a hurry as is probably customary and it therefore does not do justice to all the many great friends I have, from the early years in Cameroon right through to the present, via Bournemouth, Bath and Geneva. You all deserve a big thank you.

| Contents |

|----------|

|----------|

| Abstract.    |                                                      | 2  |

|--------------|------------------------------------------------------|----|

| Acknowle     | dgements                                             | 3  |

| Contents.    |                                                      | 4  |

| List of Fig  | gures                                                | 7  |

| -            | bles                                                 |    |

| Introduct    | ion                                                  | 11 |

| Chapter 1    | The LHC, CMS and the APV25 Readout Chip              | 14 |

| _            | The Large Hadron Collider                            |    |

|              | The Compact Muon Solenoid                            |    |

| 1.3          | The CMS Tracker                                      | 16 |

| 1.3.1        | Tracker Layout                                       |    |

| 1.3.1        | Tracker Radiation Environment                        |    |

| 1.3.2        |                                                      |    |

| 1.3.3        | Strip Tracker Electronics                            | 19 |

| 1.4          | The APV Readout Chip                                 | 20 |

| 1.4.1        | The APV25 Analogue Chain                             |    |

| 1.4.2        | The APSP                                             |    |

| 1.4.3        | APV25 Output                                         |    |

| 1 4 4        | Additional Features of the APV25                     |    |

|              | Summary                                              |    |

|              | 2 MOSFET Operation                                   |    |

| Chapter 2    |                                                      |    |

| <b>2.1</b>   | MOS Device Physics                                   |    |

| 2.1.1        | Charge Carrier Transport                             | 24 |

| 2.1.2        | The p-n Junction                                     | 25 |

| 2.1.3        | The MOS Capacitor                                    | 27 |

| 2.1.4        | The MOSFET                                           | 28 |

| 2.1.         | 4.1 MOSFET Transconductance                          | 29 |

| 2.1.         | 4.2 MOSFET Subthreshold Current                      | 30 |

| 2.1.5        | Technological Trends                                 | 30 |

| 2.1.6        | Noise                                                |    |

| 2.1.         |                                                      |    |

| 2.1.         |                                                      |    |

|              |                                                      | 22 |

|              | Consequences of Radiation on MOSFET Operation        |    |

| 2.2.1        | Total Dose Radiation Effects                         |    |

| 2.2.         |                                                      |    |

| 2.2.         | · · · · · · · · · · · · · · · · · · ·                |    |

| 2.2.         |                                                      |    |

| 2.2.         | 8                                                    |    |

| 2.2.2        | Single Event Effects (SEE)                           |    |

| 2.2.<br>2.2. | <b>b i i i i i i i i i i</b>                         |    |

| 2.2.         |                                                      |    |

|              |                                                      |    |

| 2.3          | Гетрегаture Effects                                  |    |

| 2.3.1        | Temperature Dependence of Threshold Voltage          | 47 |

| 2.3.2        | Temperature Dependence of Mobility                   | 48 |

| 2.3.3        | Temperature Dependence of Transconductance and Noise | 48 |

| 2.4          | Summary                                              |    |

|              |                                                      |    |

| Chapter 3             | CMS Front-End Electronics                                                | 50 |

|-----------------------|--------------------------------------------------------------------------|----|

| 3.1                   | Гhe Pixel Tracker                                                        | 50 |

| 3.1.1                 | Pixel Readout Chip                                                       |    |

| 3.1.2                 | Readout Scheme                                                           |    |

| 3.1.3                 | Status of Pixel Electronics                                              |    |

| 3.2 §                 | Silicon Microstrip Tracker                                               |    |

| 3.2.1                 | Front-End Hybrids                                                        |    |

| 3.2.2                 | Optical Links                                                            |    |

| 3.2.3                 | Front-End Driver (FED)                                                   |    |

| 3.2.4                 | Control System                                                           |    |

| 3.2.5                 | Status of Tracker Electronics                                            |    |

|                       | Crystal Electromagnetic Calorimeter (ECAL)                               |    |

| 3.3.1                 |                                                                          |    |

|                       | <ul><li>1.1 Floating Point PreAmplifier (FPPA)</li><li>1.2 ADC</li></ul> |    |

| 3.3.2                 |                                                                          |    |

|                       |                                                                          |    |

| <b>3.4 I</b> 3.4.1    | Preshower<br>Preshower Front-End Electronics                             |    |

| 3.4.1                 | Status of Preshower Electronics                                          |    |

|                       |                                                                          |    |

|                       | Hadron Calorimeter (HCAL)                                                |    |

| 3.5.1<br>3.5.2        | HCAL Readout                                                             |    |

|                       |                                                                          |    |

|                       | Muon Endcap Cathode Strip Chambers (CSC)                                 |    |

| 3.6.1<br>3.6.2        | Overview of CSC Electronics                                              |    |

|                       | Status of CSC Electronics                                                |    |

|                       | Muon Barrel Drift Tube Chambers (DT)                                     |    |

| 3.7.1                 |                                                                          |    |

| 3.7.2                 | Status of DT Electronics                                                 |    |

|                       | Muon Resistive Plate Chambers (RPC)                                      |    |

| 3.8.1                 | The RPC Front-End Electronics                                            |    |

| 3.8.2                 | Status of RPC Electronics                                                |    |

| 3.9 8                 | Summary                                                                  |    |

| Chapter 4             | Total Dose Testing                                                       | 68 |

|                       | K-ray Irradiator for Total Dose Testing                                  |    |

| 4.1.1                 | Characteristics of the X-ray Irradiator                                  |    |

| 4.1.2                 | Determination of the Total Dose                                          |    |

| 4.2 7                 |                                                                          |    |

| <b>4.2</b> 1<br>4.2.1 | <b>Fotal Dose Tests on 0.25 μm Test Structures</b><br>Transistors Tested |    |

| 4.2.2                 | Experimental Procedure                                                   |    |

| 4.2.                  | 1                                                                        |    |

| 4.2.                  |                                                                          |    |

| 4.2.3                 | Static Parameter Degradation                                             |    |

| 4.2.                  |                                                                          |    |

| 4.2.<br>4.2.          | 8                                                                        |    |

| 4.2.                  | •                                                                        |    |

| 4.2.                  | 3.5 NMOS Subthreshold Swing and Transconductance                         | 81 |

|                       | Noise                                                                    |    |

| 4.2.                  |                                                                          |    |

| 4.2.                  |                                                                          |    |

|                       | Fotal Dose Tests on the APV25                                            |    |

| 4.3.1                 | Chips Tested                                                             |    |

| 4.3.2                                | 2 Experimental Procedure                                                                                                                                                                                                  |     |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.                                   | .3.2.1 Irradiation Procedure                                                                                                                                                                                              |     |

|                                      | .3.2.2 Annealing                                                                                                                                                                                                          |     |

|                                      | .3.2.3 Measurement Procedure                                                                                                                                                                                              |     |

| 4.3.                                 | 3 10 Mrad Irradiation Results                                                                                                                                                                                             |     |

|                                      | .3.3.1 Bias Registers                                                                                                                                                                                                     |     |

|                                      | .3.3.2 Externally Injected Pulse                                                                                                                                                                                          |     |

|                                      | .3.3.3 Internal Calibrate Pulse                                                                                                                                                                                           |     |

|                                      | .3.3.4 Noise                                                                                                                                                                                                              |     |

|                                      | .3.3.5 Standard Deviation of Pedestals                                                                                                                                                                                    |     |

|                                      | .3.3.6 Power Consumption                                                                                                                                                                                                  |     |

| 4.3.4                                | 8                                                                                                                                                                                                                         |     |

| 4.3.                                 |                                                                                                                                                                                                                           |     |

| 4.3.0                                | 6 100 Mrad results                                                                                                                                                                                                        |     |

| 4.4                                  | Summary                                                                                                                                                                                                                   |     |

| Chapter                              | 5 SEU and SEGR Results                                                                                                                                                                                                    | 101 |

| 5.1                                  | Single Event Upsets in the APV25                                                                                                                                                                                          |     |

| 5.1.                                 |                                                                                                                                                                                                                           |     |

| 5.1.2                                |                                                                                                                                                                                                                           |     |

| 5.1.2                                | •                                                                                                                                                                                                                         |     |

| 5.1                                  |                                                                                                                                                                                                                           |     |

| 5.2                                  | Single Event Gate Rupture Results                                                                                                                                                                                         |     |

| 5.2.                                 | 1 Speculative Oxide Breakdown Mechanism                                                                                                                                                                                   |     |

| 5.2.2                                | 2 SEGR in Discrete Transistors                                                                                                                                                                                            |     |

| 5.2.                                 | 3 SEGR in the APV25                                                                                                                                                                                                       |     |

| 5.                                   | .2.3.1 SEGR with Pions                                                                                                                                                                                                    |     |

| 5.                                   | .2.3.2 SEGR with Heavy Ions                                                                                                                                                                                               |     |

| 5.3                                  | Summary                                                                                                                                                                                                                   |     |

| Chanter                              | 6 Low Temperature Operation of the APV25                                                                                                                                                                                  | 116 |

|                                      |                                                                                                                                                                                                                           |     |

| 6.1                                  | Measurement Setup                                                                                                                                                                                                         |     |

| 6.2                                  | Transistor Results                                                                                                                                                                                                        |     |

| 6.2.                                 |                                                                                                                                                                                                                           |     |

| 6.2.2                                | e                                                                                                                                                                                                                         |     |

|                                      |                                                                                                                                                                                                                           |     |

| 6.3                                  | APV25 Results                                                                                                                                                                                                             |     |

| 6.3.                                 |                                                                                                                                                                                                                           |     |

| 6.3.2                                | 1                                                                                                                                                                                                                         |     |

| 6.3.                                 |                                                                                                                                                                                                                           |     |

| 6.3.4                                | 1                                                                                                                                                                                                                         |     |

|                                      | .3.4.1 External Pulse Shape                                                                                                                                                                                               |     |

| 6.                                   |                                                                                                                                                                                                                           | 100 |

|                                      | .3.4.2 Comparison with Simulations                                                                                                                                                                                        |     |

| 6.                                   | .3.4.3 Calibrate Pulse                                                                                                                                                                                                    |     |

| 6.<br>6.3.:                          | .3.4.3 Calibrate Pulse<br>5 Noise                                                                                                                                                                                         |     |

| 6.<br>6.3.:<br>6.                    | .3.4.3 Calibrate Pulse<br>5 Noise<br>.3.5.1 Digitisation Noise                                                                                                                                                            |     |

| 6.3.:<br>6.3.:<br>6.                 | .3.4.3       Calibrate Pulse         5       Noise         .3.5.1       Digitisation Noise         .3.5.2       Noise with Low Gain                                                                                       |     |

| 6.3.:<br>6.3.:<br>6.                 | .3.4.3 Calibrate Pulse<br>5 Noise<br>.3.5.1 Digitisation Noise                                                                                                                                                            |     |

| 6.3.:<br>6.3.:<br>6.                 | .3.4.3       Calibrate Pulse         5       Noise         .3.5.1       Digitisation Noise         .3.5.2       Noise with Low Gain                                                                                       |     |

| 6.3.:<br>6.3.:<br>6.<br>6.           | .3.4.3Calibrate Pulse5Noise.3.5.1Digitisation Noise.3.5.2Noise with Low Gain.3.5.3Noise with High Gain                                                                                                                    |     |

| 6.3.:<br>6.3.:<br>6.6.<br>6.4<br>6.5 | .3.4.3       Calibrate Pulse         5       Noise         .3.5.1       Digitisation Noise         .3.5.2       Noise with Low Gain         .3.5.3       Noise with High Gain <b>Radiation Damage at Low Temperatures</b> |     |

## List of Figures

| Figure 1.1: CMS and its subdetectors.                                                           | 16 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Schematic diagram of one quadrant of the CMS Tracker                                | 17 |

| Figure 1.3: Cross-section of the CMS Tracker detector system in the barrel region               | 18 |

| Figure 1.4: Radiation levels at selected radii in the CMS Tracker region.                       | 19 |

| Figure 1.5: Block diagram of the APV25 analogue chain, from [10]                                | 21 |

| Figure 1.6: APV25 layout and output.                                                            | 22 |

|                                                                                                 | 25 |

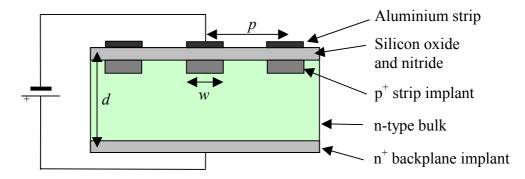

| Figure 2.2: Cross-section through an AC-coupled strip detector where w is the strip             |    |

| width, p is the strip pitch and d is the detector thickness [12].                               | 26 |

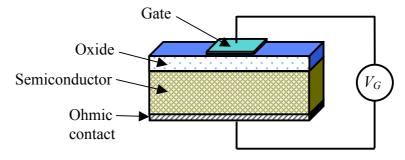

| Figure 2.3: Schematic of a MOS capacitor.                                                       |    |

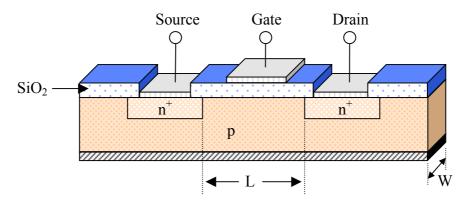

| Figure 2.4: Schematic diagram of an n-channel MOSFET.                                           | 28 |

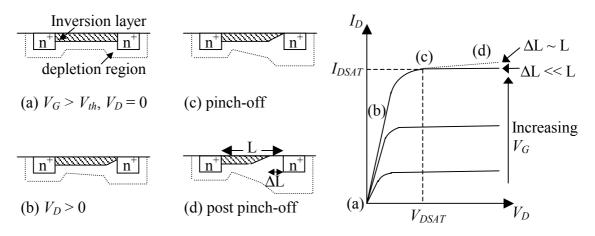

| Figure 2.5: $V_G > V_{th}$ in (a), (b), (c) and (d).                                            | 28 |

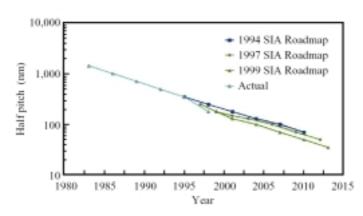

| Figure 2.6: Trends in lithographic resolution.                                                  |    |

|                                                                                                 | 31 |

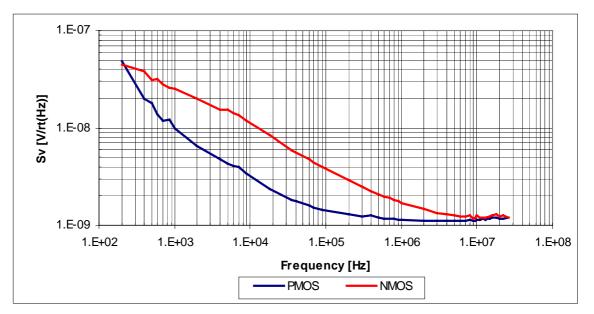

| Figure 2.8: Noise spectrum of PMOS and NMOS transistors from a 0.5 µm process.                  | 32 |

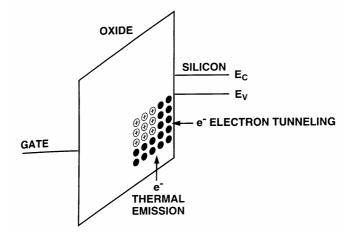

| Figure 2.9: Schematic diagram illustrating the neutralisation of oxide-trap charge by           |    |

| electron tunnelling from the silicon and by thermal emission of electrons from t                | he |

| oxide valence band.                                                                             |    |

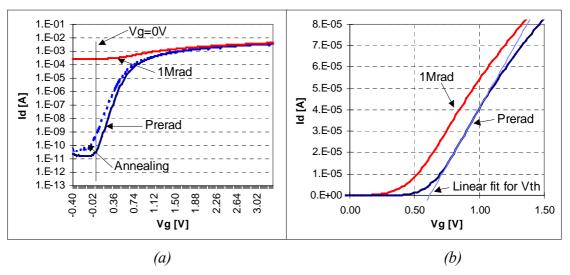

| Figure 2.10: Drain current as a function of gate voltage.                                       |    |

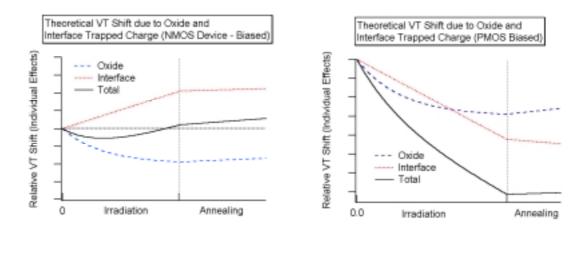

| Figure 2.11: V <sub>Th</sub> shift in biased (a) NMOS, and (b) PMOS transistors [31]            |    |

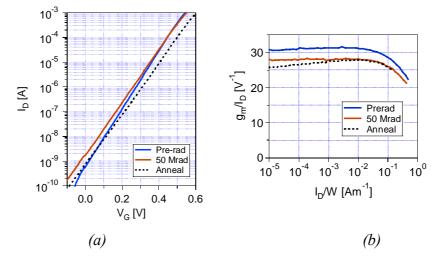

| Figure 2.12: NMOS transistor (a) Subthreshold swing and (b) Transconductance                    |    |

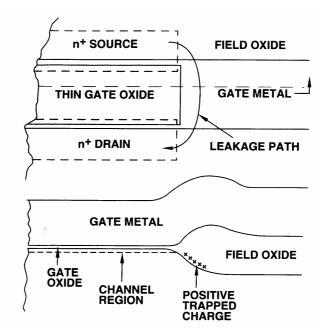

| Figure 2.13: Cross-section of a parasitic field oxide transistor showing the primary            |    |

| leakage current paths [34].                                                                     | 40 |

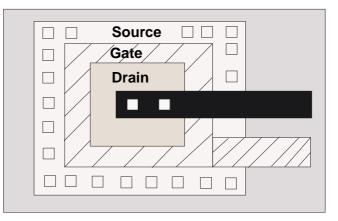

| Figure 2.14: Edgeless transistor.                                                               |    |

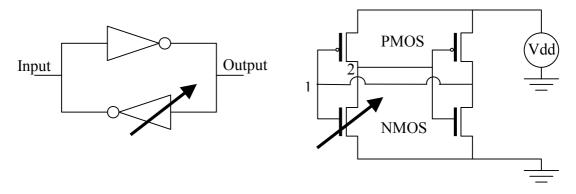

| Figure 2.15: A memory cell composed of two cross coupled inverters [39]. The arrow              |    |

| represents a heavy ion strike.                                                                  | 42 |

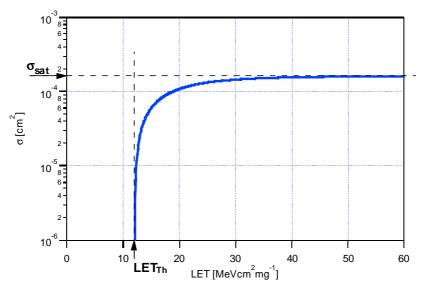

| Figure 2.16: A typical cross-section curve.                                                     | 43 |

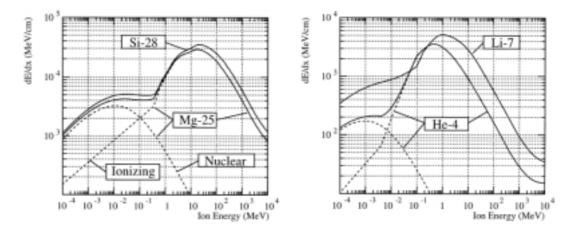

| Figure 2.17: Energy loss of some ion species in silicon as a function of the kinetic            |    |

| energy of the ion, from [52].                                                                   | 45 |

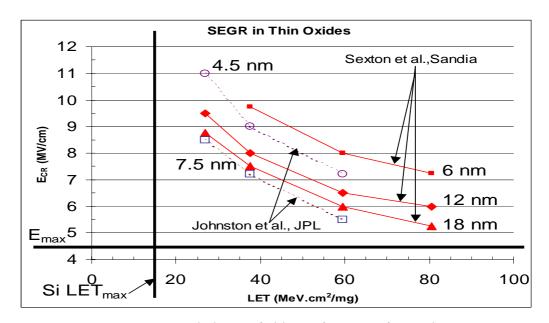

| Figure 2.18: Critical electric field as a function of particle LET.                             |    |

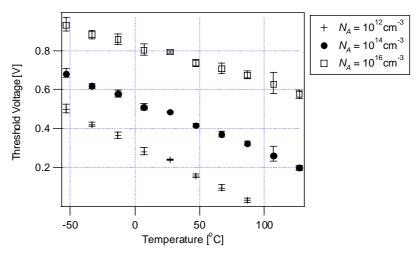

| Figure 2.19: Variation of V <sub>th</sub> with temperature for an NMOS transistor for different |    |

| values of N <sub>A</sub>                                                                        | 47 |

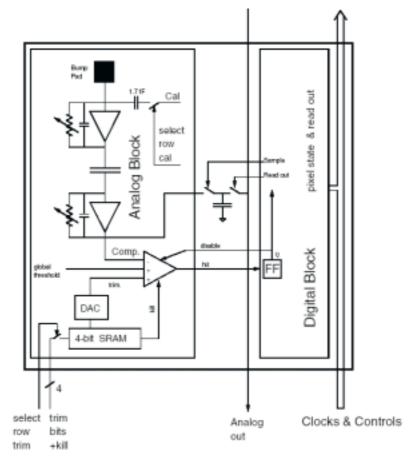

| Figure 3.1: Schematic diagram of a pixel unit cell (PUC).                                       | 51 |

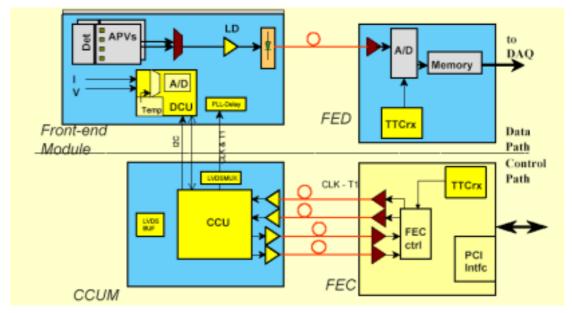

| Figure 3.2: Schematic diagram of the CMS SST readout and control system                         |    |

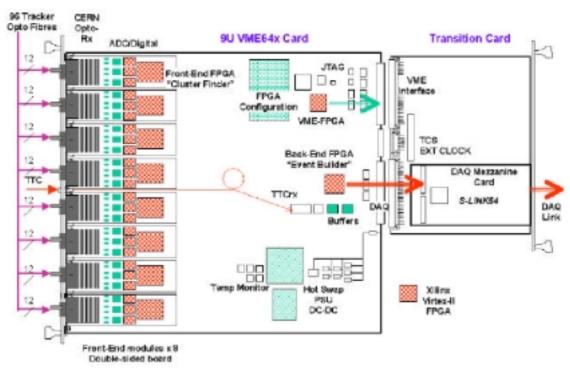

| Figure 3.3: The FED 9U VME layout and its transition card.                                      |    |

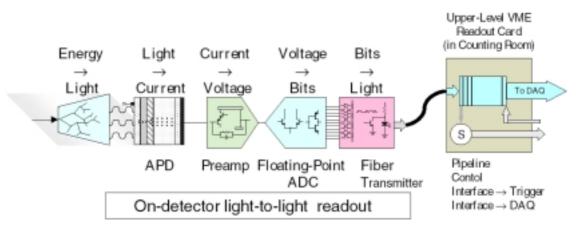

| Figure 3.4: Original scheme for the ECAL readout chain.                                         | 57 |

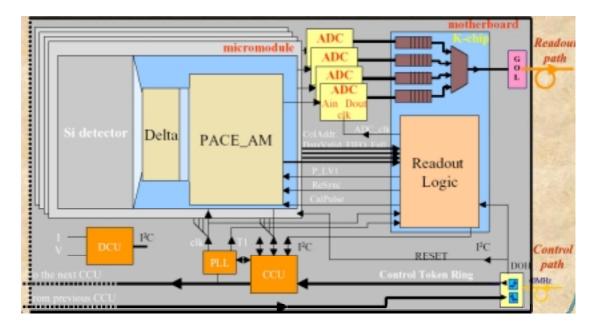

| Figure 3.5: Preshower electronics, from [87]                                                    | 59 |

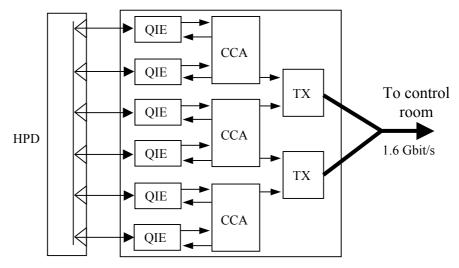

| Figure 3.6: HCAL front-end electronics. TX represents the Gigabit Optical Link and              | l  |

| the VCSEL.                                                                                      | 61 |

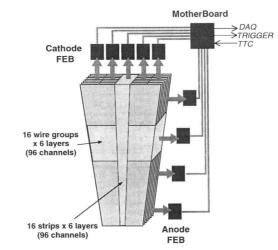

| Figure 3.7: Organisation of the CSC front-end electronics                                       | 62 |

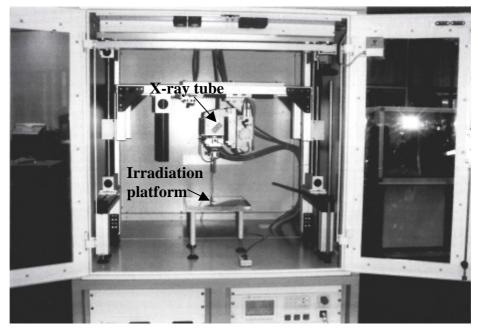

| Figure 4.1: X-ray machine cabinet with the X-ray tube and the irradiation platform              | 69 |

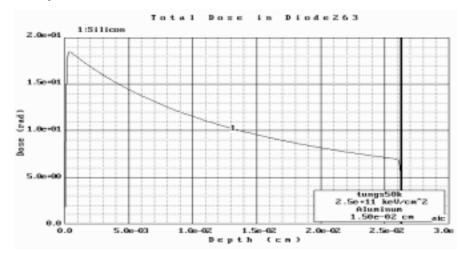

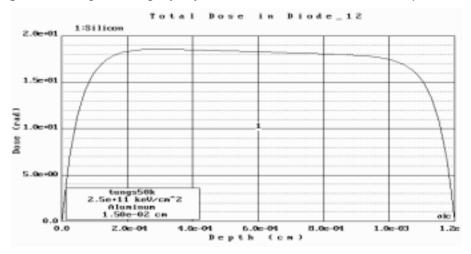

| Figure 4.2: Depth-dose profile for the total dose in the thick 263 µm diode                     | 71 |

| Figure 4.3: Depth-dose profile for the total dose in a 12 µm diode.                             |    |

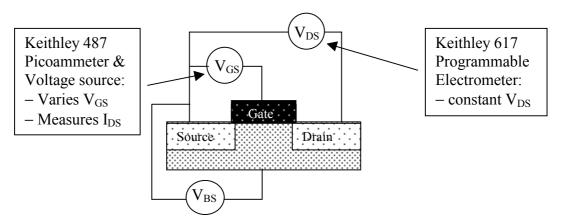

| Figure 4.4: Static parameter testing setup for transistors.                                     |    |

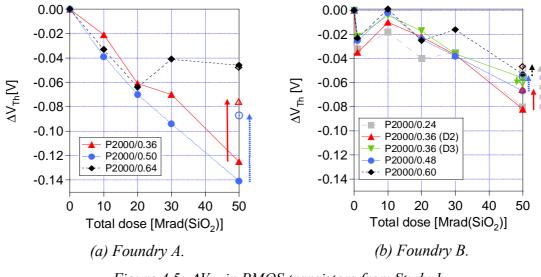

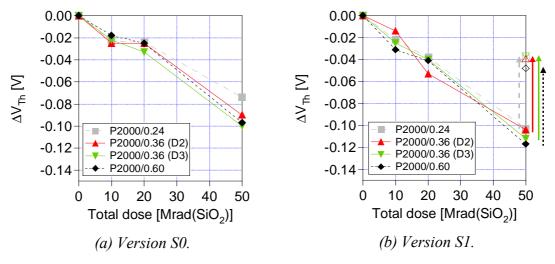

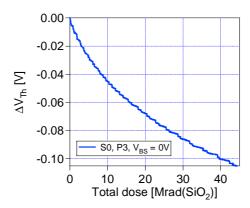

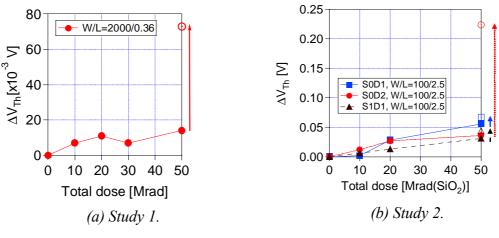

| Figure 4.5: $\Delta V_{Th}$ in PMOS transistors from Study 1                                    |    |

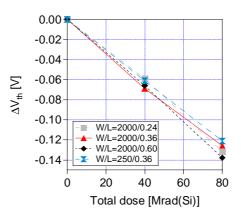

| Figure 4.6: $\Delta V_{Th}$ in PMOS transistors from Foundry B, Study 2                         |    |

|                                                                                                 |    |

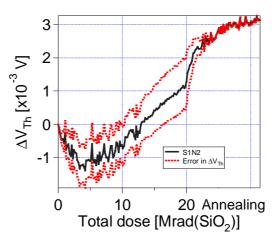

| Figure 4.7: Results from the continuous monitoring of $\Delta V_{Th}$ throughout the irradiation                  | on      |

|-------------------------------------------------------------------------------------------------------------------|---------|

| stage in a PMOS transistor, P3, W/L=2000/0.36 µm, version S0                                                      | 78      |

| Figure 4.8: $\Delta V_{Th}$ in PMOS transistors from electron beam irradiations.                                  | 78      |

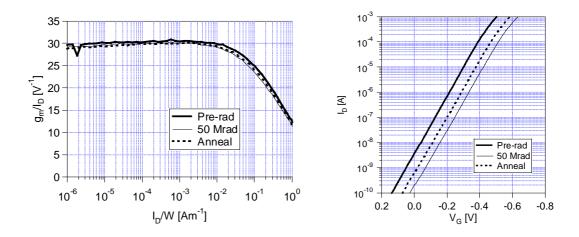

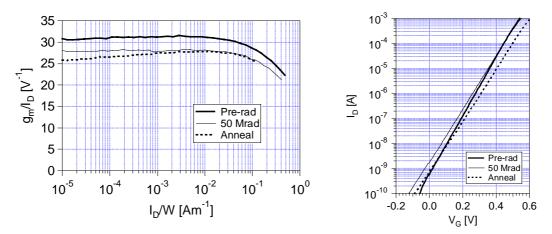

| Figure 4.9: PMOS transistor transconductance and subthreshold slope.                                              | 79      |

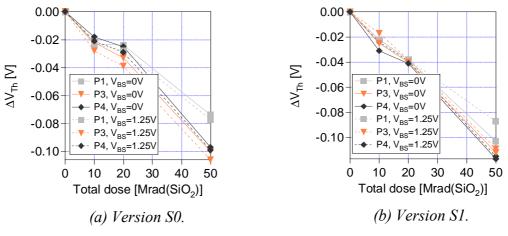

| Figure 4.10: Bulk bias dependence for PMOS transistors.                                                           | 79      |

| Figure 4.11: $\Delta V_{Th}$ in NMOS transistors.                                                                 | 80      |

| Figure 4.12: $\Delta V_{Th}$ in an NMOS transistor monitored continuously during irradiation.                     | 80      |

| Figure 4.13: NMOS transistor transconductance and subthreshold slope                                              |         |

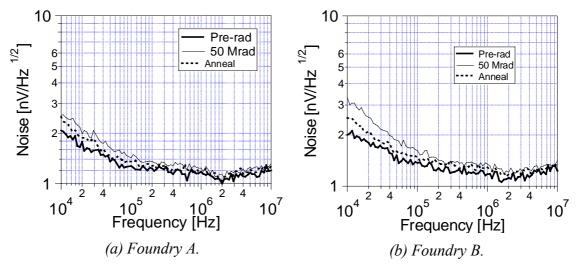

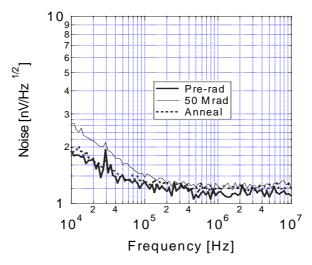

| Figure 4.14: PMOS transistor noise: Foundry A, Study 1, W/L=2000/0.36 µm.                                         |         |

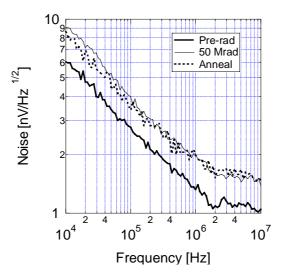

| Figure 4.15: PMOS transistor noise: Foundry B, Study 2, W/L=2000/0.36 µm                                          |         |

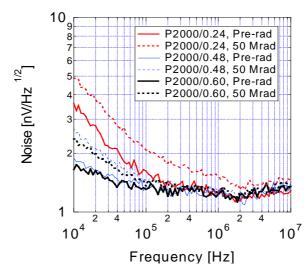

| Figure 4.16: Noise in PMOS transistors from Foundry B, Study 1, showing the                                       |         |

| dependence of noise on channel length.                                                                            | 83      |

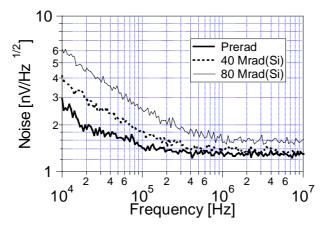

| Figure 4.17: PMOS transistor noise, Foundry B, irradiated with 8 MeV electrons                                    |         |

| Figure 4.18: NMOS transistor noise, Foundry A, Study 1                                                            |         |

| Figure 4.19: Wafer map from a wafer screening test. Failed chips are in grey                                      |         |

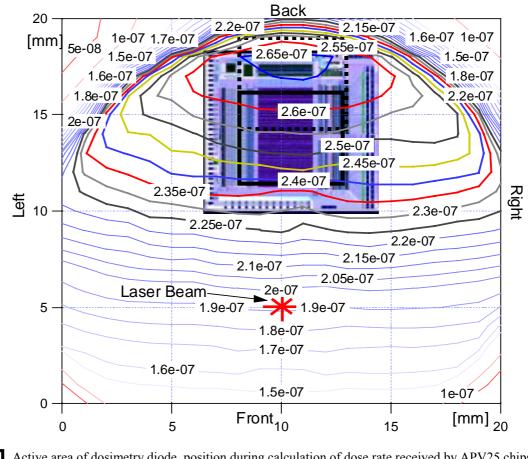

| Figure 4.20: Positioning of the APV25 during irradiation.                                                         | 87      |

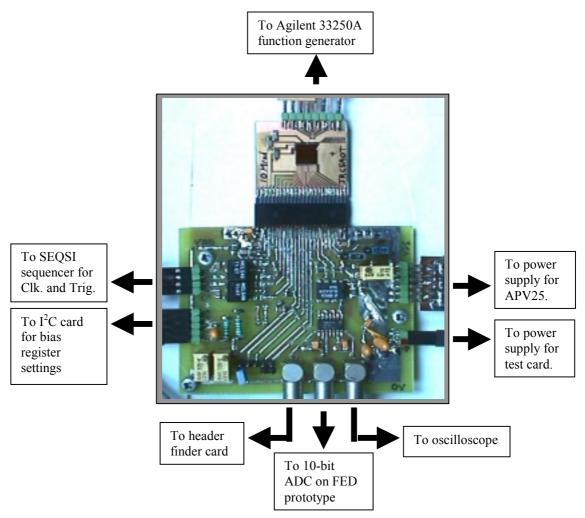

| Figure 4.21: APV25 on its daughter board connected to the test card.                                              |         |

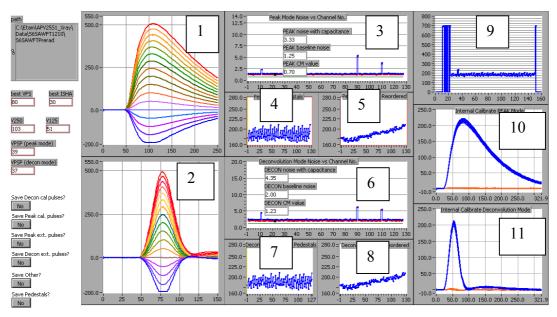

| Figure 4.22: LabVIEW output.                                                                                      |         |

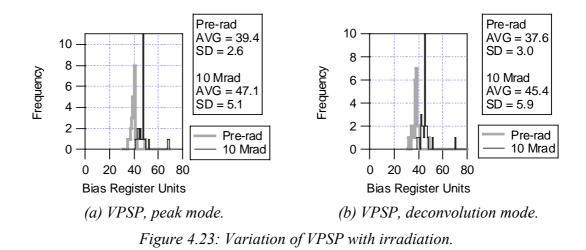

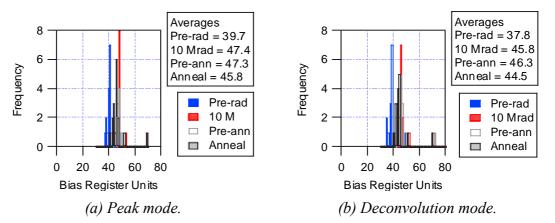

| Figure 4.23: Variation of VPSP with irradiation                                                                   | 91      |

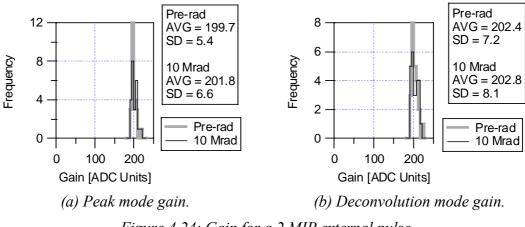

| Figure 4.24: Gain for a 2 MIP external pulse.                                                                     | 92      |

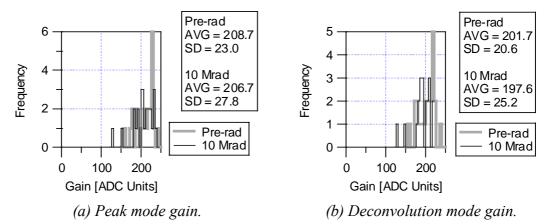

| Figure 4.25: Gain for a pulse injected with the internal calibrate pulse                                          | 92      |

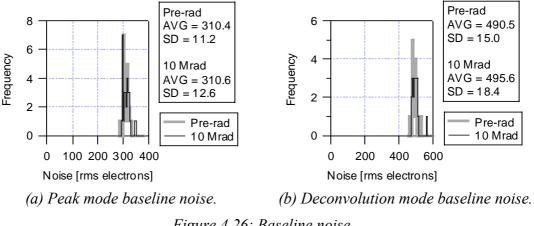

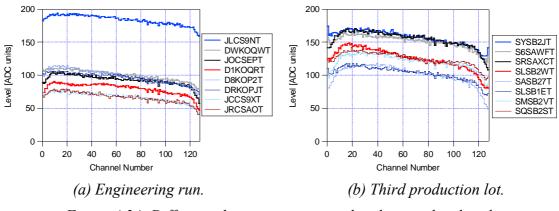

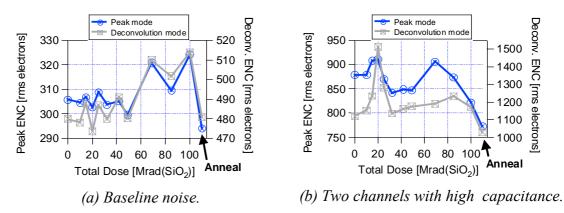

| Figure 4.26: Baseline noise.                                                                                      | 93      |

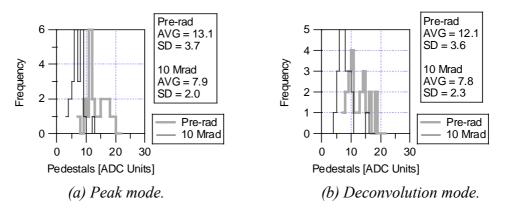

| Figure 4.27: Standard deviation of the 128-channel pedestals, indicating the spread of                            | of      |

| the pedestals within the analogue output frame.                                                                   | 94      |

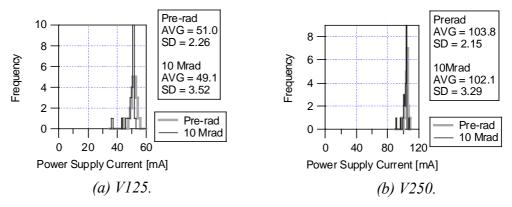

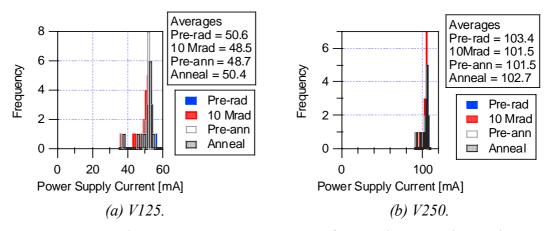

| Figure 4.28: Power supply currents.                                                                               | 94      |

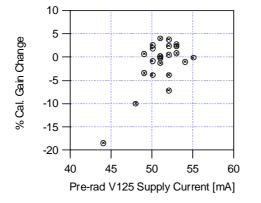

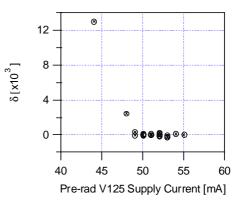

| Figure 4.29: Identifying chips that show higher than average radiation-induced change                             |         |

| in their characteristics                                                                                          |         |

| Figure 4.30: Changes in VPSP after irradiation and annealing                                                      |         |

| Figure 4.31: Changes in power consumption after irradiation and annealing                                         |         |

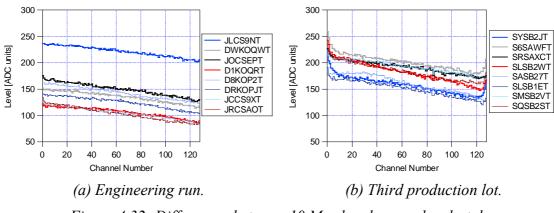

| Figure 4.32: Differences between 10 Mrad and pre-rad pedestals.                                                   |         |

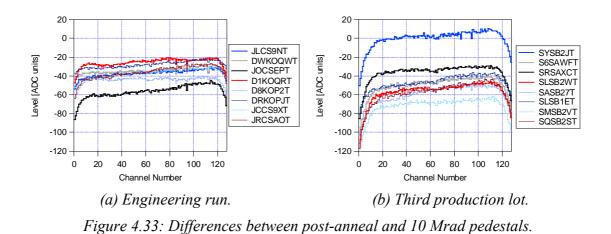

| Figure 4.33: Differences between post-anneal and 10 Mrad pedestals.                                               |         |

| Figure 4.34: Difference between post-anneal and pre-rad pedestals                                                 |         |

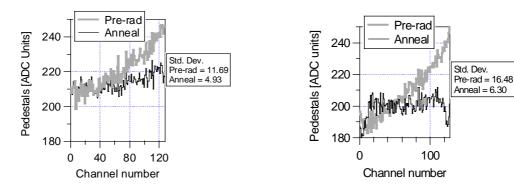

| Figure 4.35: Pedestals, pre-rad and after annealing.                                                              |         |

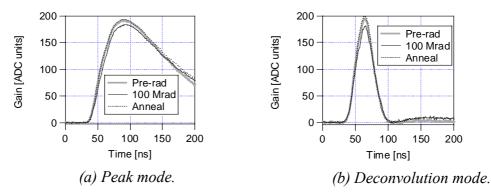

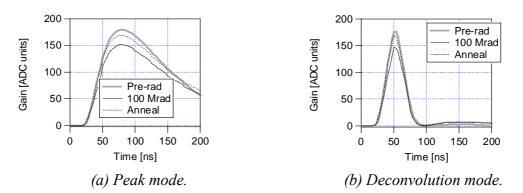

| Figure 4.36: Pulse shape following 100 Mrad exposure, 2 MIP.                                                      |         |

| Figure 4.37: Internal calibrate pulses following 100 Mrad exposure                                                |         |

| Figure 4.38: Noise dependence on total dose.                                                                      |         |

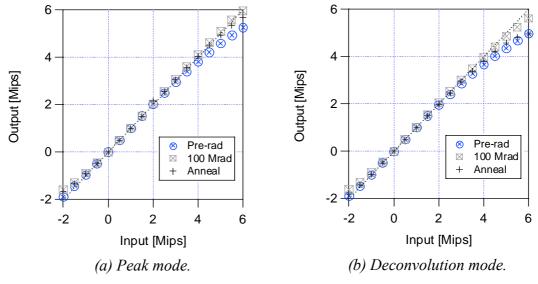

| Figure 4.39: Linearity                                                                                            |         |

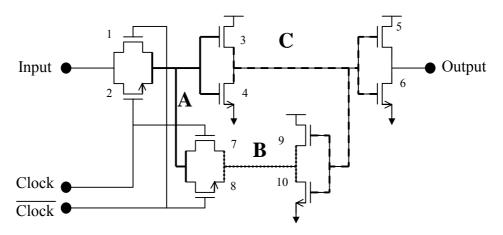

| Figure 5.1: Schematic of a simple DFF slave.                                                                      | .102    |

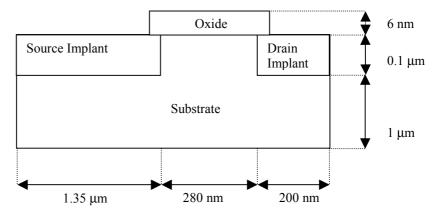

| Figure 5.2: Transistor geometry used in EVEREST simulations.                                                      |         |

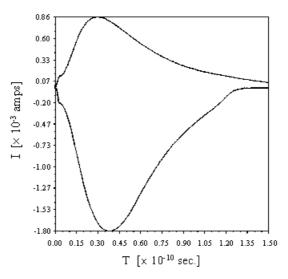

| Figure 5.3: EVEREST output after a charge deposition event of $1.5 \times 10^6$ electrons.                        |         |

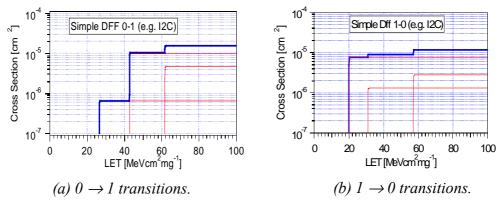

| Figure 5.4: SEU Cross-sections predicted by the model.                                                            |         |

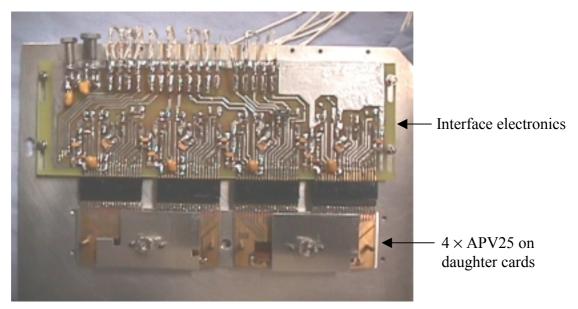

| Figure 5.5: APV25 SEU test board containing interface electronics, four APV25 chip                                |         |

| and precision-machined masks obscuring most of the APV25s                                                         |         |

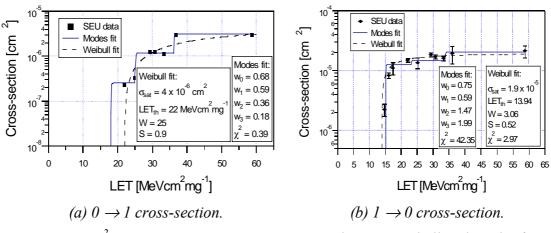

| Figure 5.6: 1 <sup>2</sup> C registers cross-section vs. LET, showing Weibull and Modes fits                      |         |

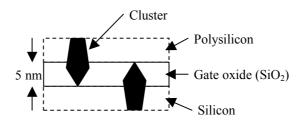

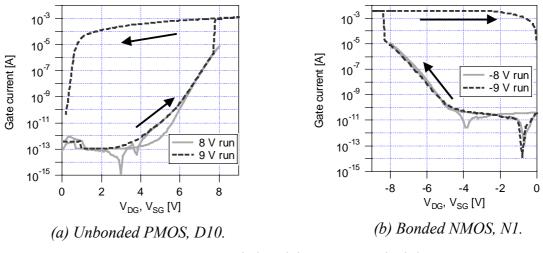

| Figure 5.7: Schematic diagram of cluster damage in the gate oxide<br>Figure 5.8: Oxide breakdown tests in the lab |         |

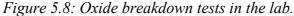

| Figure 5.9: Chip10, PMOS transistor current vs. Time for a 2 V gate bias. The pion                                | , 1 1 1 |

| beam is switched on at $250 \times 10^3$ s on the time scale shown here.                                          | 112     |

| Figure 5.10: PMOS transistor current vs. Time for a 2 V gate bias. The 10 keV X-ray                               |         |

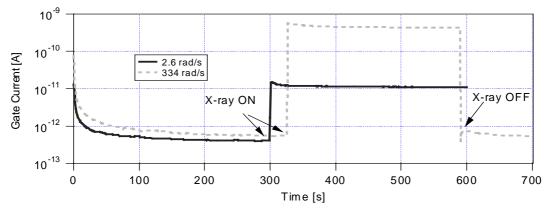

| beam is switched on around 300 s.                                                                                 |         |

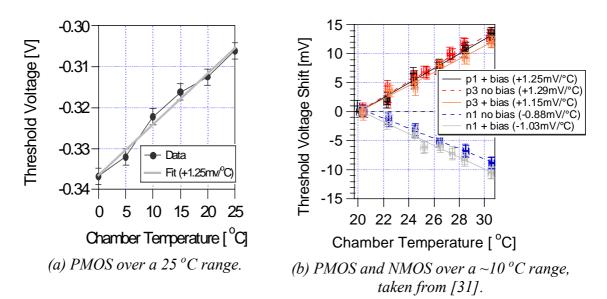

| Figure 6.1: (a) PMOS threshold voltage and (b) PMOS and NMOS threshold voltage                                    |         |

| shift                                                                                                             |         |

|                                                                                                                   | -       |

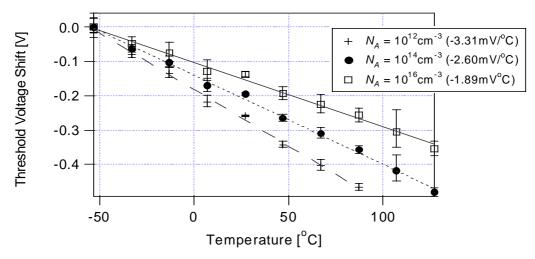

| Figure 6.2: NMOS threshold voltage shifts as a function of temperature as predict  | ted by |

|------------------------------------------------------------------------------------|--------|

| theory for different values of the drain and source doping concentrations          | 119    |

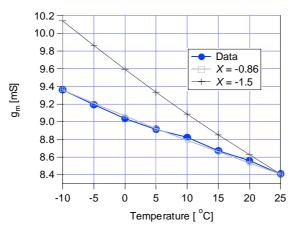

| Figure 6.3: Temperature dependence of transconductance in a PMOS transistor. T     | he     |

| data were collected for $I_D = 400 \ \mu A$                                        | 119    |

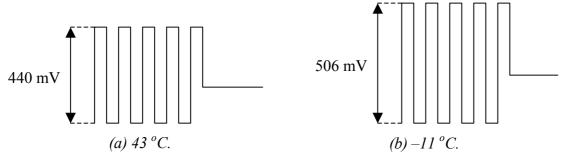

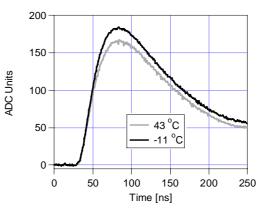

| Figure 6.4: Chip output at two different temperatures, (a) 43 °C, (b) –11 °C       | 120    |

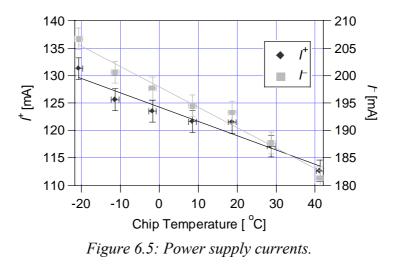

| Figure 6.5: Power supply currents                                                  | 121    |

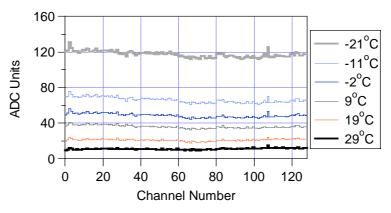

| Figure 6.6: Peak mode pedestals. The pedestals at 41 °C are subtracted from all of | ther   |

| pedestals.                                                                         | 121    |

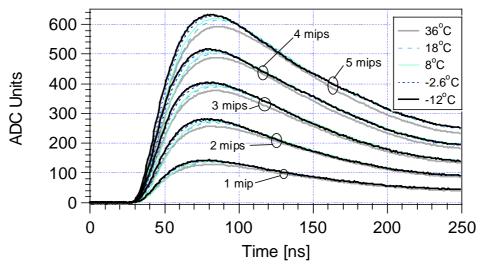

| Figure 6.7: External pulse shapes from 1 to 5 MIP in Peak mode for various         |        |

| temperatures.                                                                      | 122    |

| Figure 6.8: 2 MIP external pulse, tuned for the same rise time at -11 °C and 43 °C | 2122   |

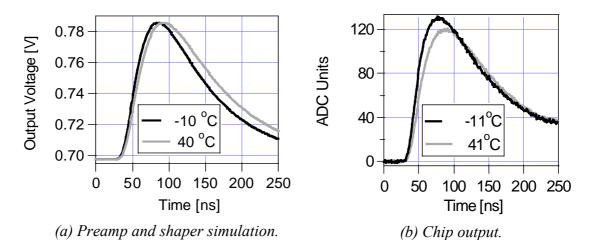

| Figure 6.9: Comparison between simulation and real chip output for a 1 MIP input   | ıt123  |

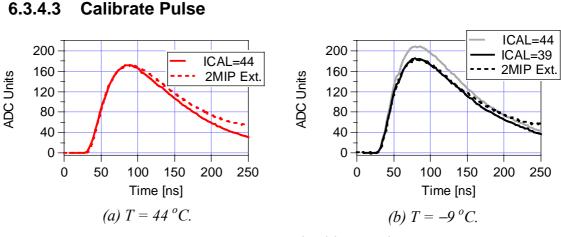

| Figure 6.10: Internal calibrate pulse.                                             | 123    |

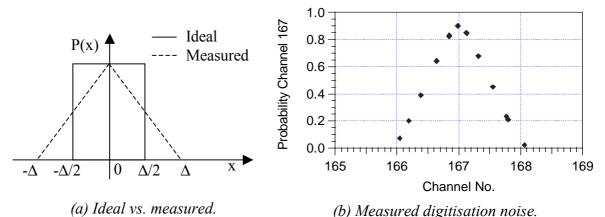

| Figure 6.11: Digitisation noise.                                                   | 125    |

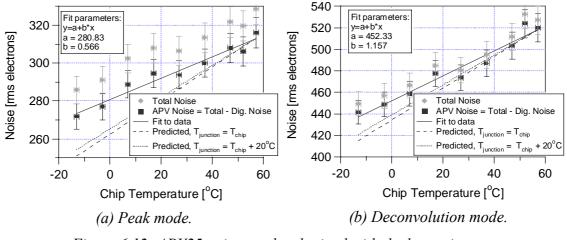

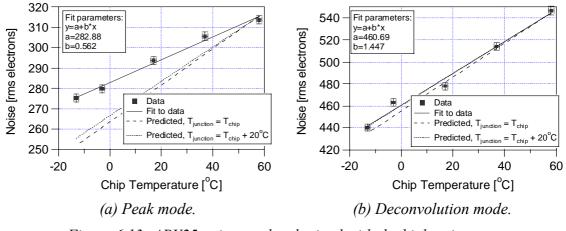

| Figure 6.12: APV25 noise results obtained with the low gain setup.                 | 126    |

| Figure 6.13: APV25 noise results obtained with the high gain setup.                | 127    |

|                                                                                    |        |

## List of Tables

| Table 2.1: Comparison of two Intel Pentium process generations.                      | 30    |

|--------------------------------------------------------------------------------------|-------|

| Table 3.1: Summary of the components used in the system with their functions         | 53    |

| Table 3.2: Summary of radiation levels and SEU rates in CMS electronics              | 66    |

| Table 4.1: Total dose in silicon slabs of various thicknesses.                       | 71    |

| Table 4.2: Dose rates in thin diodes.                                                | 72    |

| Table 4.3: Dimensions of the transistors tested.                                     | 73    |

| Table 4.4: Thermal noise levels and percentage increase w.r.t pre-rad values for PM  | OS    |

| transistors irradiated with X-rays.                                                  | 82    |

| Table 4.5: Thermal noise levels and percentage increase w.r.t pre-rad values for the |       |

| PMOS transistor irradiated with electrons.                                           | 83    |

| Table 4.6: Change in noise after 10 Mrad for all 23 chips                            | 93    |

| Table 5.1: Sensitive implants of the simple DFF.                                     | 102   |

| Table 5.2: Sensitive area and critical charge for six modes in a DFF slave           |       |

| Table 5.3: Fluences received by the four APV25 chips                                 | 106   |

| Table 5.4: Comparison between predicted and measured cross-sections                  | 108   |

| Table 5.5: Predicted upset rates in the CMS Tracker                                  | 108   |

| Table 5.6: Predicted SEU rates in the CMS Tracker calculated from the pion SEU cr    | ross- |

| sections.                                                                            | 109   |

| Table 5.7: Transistors exposed to the pion beam.                                     | 112   |

| Table 6.1: Changes in chip parameters in peak mode                                   |       |

## Introduction

In the early part of the twentieth century, the period extending through to the mid-1930s, a few fundamental particles were known to physicists; the proton, neutron, electron, positron and photon. This picture was believed to be complete though a rather difficult question remained to be answered: how did multiple positively charged protons co-exist in a nucleus without being repelled by the electromagnetic force between them? The search for the answers to this question and the discovery of many new unstable particles in the 1940s mark the birth of the subject of modern particle physics. By the end of the twentieth century, this field of physics had made tremendous progress in understanding the fundamental constituents of matter and their interactions, leading particle physicists to the currently held view that matter consists of two fundamental groups of particles, quarks and leptons, distinguished by the interactions in which they take part.

Four types of interactions are known to exist: the strong, electromagnetic, weak and gravitational forces, mediated by force carriers called gauge bosons. The gravitational force, which is the most familiar in the observable world and which affects large bodies separated by large distances, is by far the weakest and is usually considered negligible in particle physics. At the 1 fm scale, the strongest interaction is the strong force, responsible for the interactions between quarks. The weak force is responsible for processes such as nuclear beta decay that are forbidden by the conservation rules constraining the much stronger electromagnetic and strong forces. Another fundamental feature of particle physics is the existence of antimatter. Every particle has a corresponding antiparticle whose mass and spin are the same but whose charge and subset of internal quantum numbers take the opposite sign.

The six known leptons are usually paired up into three generations, each containing a charged member and a neutral member. All leptons are subject to weak interactions and, in addition, the charged leptons can interact via the electromagnetic force.

Six types of quarks exist, namely the up, down, strange, charmed, bottom and top. These spin  $\frac{1}{2}$  particles are also grouped into three generations. One peculiar feature of quarks (antiquarks) is that they carry a fractional charge of +2e/3 (-2e/3) and -1e/3 (+1e/3). Free quarks have never been observed in nature and are thought to be confined in quark-composite particles collectively known as hadrons. Hadrons can be split into two subgroups, mesons, which consist of a quark-antiquark pair, and baryons, which consist of three quarks. Hadrons participate in strong interactions, a property that

distinguishes them from leptons. Some hadrons consisting of identical quarks with parallel spins would violate the Pauli exclusion principle. To solve this anomaly, it was proposed that quarks possess a new property called colour. The six quark flavours can each have three "colours". The strong force therefore has six charge states (the three colours and their corresponding anticolours), in contrast with the electromagnetic force which has two, + and -.

Quarks and leptons have spin  $\frac{1}{2}$  and are therefore fermions whereas the force carriers have integer spin and are bosons. The well known massless, chargeless photon mediates the electromagnetic interaction. The W<sup>±</sup> and Z bosons which have mass are responsible for carrying the weak interaction. Massless particles called gluons are the carriers of the strong force. For completeness, the gravitational force is thought to be mediated by gravitons.

Many theories have been developed to explain the plethora of observations made in particle physics. The quantum theory of electromagnetism is expressed in the theory of quantum electrodynamics (QED). The main features of QED are those of renormalisability and gauge invariance. The theory of the strong force is called quantum chromodynamics (QCD). Particle physicists ultimately believe that at very high energies, all four forces are the same. This has led to the development of further theories attempting to progressively unify the forces such as the electroweak theory, which essentially makes no distinction between electromagnetic and weak forces at very high energies. Other important theories are the Standard Model, and Supersymmetric models which predict the existence of a superpartner for every particle.

Interestingly, the electroweak theory is at the heart of one of the most controversial questions in particle physics today, that of the origin of particle masses. Whilst the photon has no mass, the  $W^{\pm}$  and Z bosons do and this leads to the difference between electromagnetic and weak forces at low energies. The change in force properties from low to high energies is called symmetry breaking and can be explained within the framework of the electroweak theory by the existence of a particle called the Higgs boson, whose mass should be no more than 1 TeV.

The tools used by particle physicists in their quest for a better understanding of nature are accelerators and detectors. A new accelerator, the Large Hadron Collider (LHC), is currently under construction at the European Laboratory for Particle Physics (CERN) in Geneva, Switzerland. Four detectors will study the full range of physics made available by the high-energy collisions at the LHC. One of these is a general-purpose detector, called the Compact Muon Solenoid (CMS), which is constructed from a variety of

subdetector systems. Each sub-system performs a specific task, measuring one or more particle properties. For example, tracking detectors measure particle trajectories whilst calorimeters measure energy. Information from all systems is collected, analysed and used to identify particles and reconstruct events of interest.

At the LHC, two counter-rotating beams of protons will interact with a frequency of 40 MHz, generating up to 10<sup>9</sup> collisions per second. This rate, combined with the 14 TeV centre-of-mass collision energy will create a very hostile radiation environment. The CMS subdetector closest to the collision region is the Tracker, which must employ sophisticated on-detector readout electronics to condition signals from its silicon sensors, and to store and reduce the large amounts of data for an off-line analysis rate of 100 Hz. The survival against radiation effects of the readout electronics poses one of the many technological challenges of the CMS detector.

The Tracker is designed to provide position information and it achieves this by recording hits in several layers of silicon detectors, thus reconstructing the trajectory of particles. It is required to have high spatial resolution which leads to a large number of detector channels. In total, just under 10 million silicon microstrip channels will be read out by approximately 75 000 APV25 chips. These are Application Specific Integrated Circuits (ASICs) designed and manufactured in a commercial 0.25  $\mu$ m CMOS (Complimentary Metal Oxide Semiconductor) process. It is the evaluation of the APV25, prompted by concerns over the use of a commercial CMOS process in a hostile radiation environment on such a large scale for the first time that forms the basis of this thesis.

Chapter 1 presents the basic functional principles of the LHC and CMS, and it also provides a discussion of the main features of the APV25. The building block of the APV25 is the Metal Oxide Semiconductor Field Effect Transistor (MOSFET). Chapter 2 presents an account of the operating principles of the MOSFET, followed by the various radiation effects it is susceptible to and the consequences of operation at low temperature. The encouraging progress made in the adoption of the 0.25  $\mu$ m CMOS process for Tracker electronics has had a large impact on other sub-detector systems reviewed in Chapter 3.

Radiation testing results are presented in Chapters 4 and 5. The APV25 chips will be operated at -10 °C because of issues related to radiation damage in the silicon sensors. Chapter 6 presents results from low temperature studies conducted on the APV25.

#### **Chapter 1**

### The LHC, CMS and the APV25 Readout Chip

A brief discussion of the LHC and CMS serves as a good starting point in understanding some of the challenges that the operation of the APV25 will present.

#### 1.1 The Large Hadron Collider

The CERN council approved the LHC project in 1994 and, when completed, the LHC will be the most powerful particle accelerator in the world. To appreciate the scale of the LHC, it is useful to consider its predecessor at CERN, the Large Electron Positron (LEP) collider. The LEP ring was 27 km in circumference and the accelerator was designed to achieve centre-of-mass energies of 200 GeV. LEP revealed a few candidates for the Higgs boson, pointing to a possible mass of 114 GeV, before being decommissioned in 2000. LHC will explore physics beyond LEP by achieving centre-of-mass collisions with energies in the TeV range.

In circular accelerators, particles are constrained in a vacuum pipe with the help of electromagnets. The relation between the proton momentum p in GeV/c and the magnetic field B is

$$p = 0.3Br$$

..... eq. (1.1).

where r is the ring radius in metres. At the LHC the ring radius is defined by the costeffective approach of CERN requiring that the new accelerator be housed in the existing LEP tunnel, so the only parameter left to determine the maximum beam energy is B. The most advanced superconducting magnets with a maximum field of 8.33 T will be required to accelerate each proton beam to achieve collisions with centre-of-mass energies of 14 TeV.

The LHC bunch-crossing frequency is 40 MHz and it will start operating with a luminosity<sup>1</sup> of  $10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>, increasing to its full design luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> over a few years, and producing up to  $10^9$  proton-proton events per second.

The four detectors built to exploit LHC physics are optimised for various searches. Two general purpose detectors, CMS and ATLAS (A Toroidal LHC Apparatus) will identify and analyse the properties of the Higgs should it exist at LHC energies. A smaller

<sup>&</sup>lt;sup>1</sup> Luminosity in circular accelerators is given by  $L = fn \frac{N_1 N_2}{A}$ , where  $N_1$  and  $N_2$  are the numbers of particles in each bunch, *n* is the number of bunches in either beam around the ring, *A* is the cross-sectional area of the beams and *f* is the revolution frequency.

detector, LHCb, is optimised for the study of charge-parity (CP) violation, a mechanism that, if it exists, could provide insight into the dominance of matter over antimatter in the present universe. In addition to proton-proton collisions, LHC is designed to collide heavy ions such as lead with total collision energies in excess of 1250 TeV. The ALICE (A Large Ion Collider Experiment) detector is optimised to explore the physics of the quark-gluon plasmas generated with these heavy ion collisions. The nominal luminosity of the LHC,  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, combined with the 7 TeV beam energy will create an extremely hostile radiation environment.

#### **1.2 The Compact Muon Solenoid**

Although CMS [1] is optimised to detect the Higgs boson, it is actually a generalpurpose detector, designed to identify and precisely measure muons, electrons and photons over a large energy range and at high luminosity. In addition to searches for the Standard Model Higgs boson mentioned previously, CMS will address topics such as searches for the various Minimum Supersymmetric Standard Model (MSSM) Higgs bosons, gluino and squarks searches, CP-violation measurements in the B sector, observations of  $B_s^0$  oscillations, and possible signals for QCD deconfinement in heavy ion collisions.

The position, arrival time, and identity of particles are properties that all have to be determined by particle detectors, usually with a combination of sub-detector systems. Detection principles have remained the same over the past couple of decades and if one is searching for fundamental departures from old detector technologies, it is to be found in the adoption of increasingly complex electronics and computing systems. In this respect, CMS is typical of the new generation of particle detectors.

The CMS design is based around its 4 T solenoid magnet. Its strong field increases bending of charged particle tracks, thus enabling the determination of their momentum within a relatively small detector volume, hence the "compact" in CMS. In comparison, ATLAS is eight times the volume of CMS, but only half its mass.

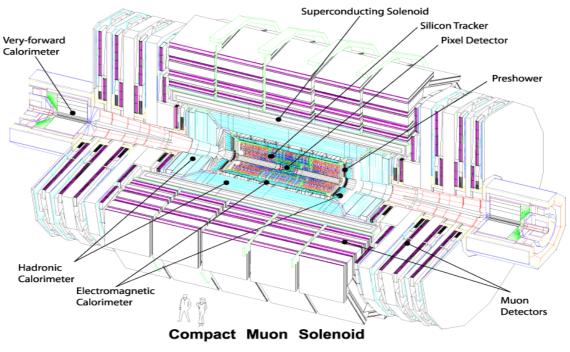

Figure 1.1: CMS and its subdetectors.

The detector sub-system closest to the collision point is the Tracker, which is followed by the electromagnetic calorimeter (ECAL), the hadronic calorimeter (HCAL) and the Muon detector, Fig. 1.1. These four main sub-detector systems consist of central sections, sometimes referred to as barrel regions, and sections at both ends of the solenoid, the endcaps. The solenoid itself has a length of 13 m and its inner radius of 2.95 m allows the full barrel calorimetry and Tracker to be located within it. The muon chambers lie outside the solenoid.

#### 1.3 The CMS Tracker

The central tracking system [2] will play a major role in all physics searches. Its aims are to reconstruct muon tracks with an efficiency better than 98 % over the full pseudorapidity<sup>2</sup> range  $|\eta| < 2.6$ ; charged hadron tracks (whose transverse momentum is above 10 GeV/c) with an efficiency of 95 %; and high-energy electron tracks with an efficiency of 90 %.

#### 1.3.1 Tracker Layout

The Tracker will use two detector technologies, silicon pixel and silicon microstrip detectors, covering a total area of ~ 220 m<sup>2</sup>. The layout outlined here is the result of

<sup>2</sup> Pseudorapidity is a measure of the angle from the interaction point and is given by  $\eta = -\ln(\tan(\theta/2))$

and  $\frac{r}{z} = \tan \theta$ .  $\theta = 90^{\circ}$  is perpendicular to and  $\theta = 0^{\circ}$  is parallel to the z-axis (beam axis).

intensive simulations taking into account requirements for track reconstruction and constraints such as material budget and cost, Fig. 1.2.

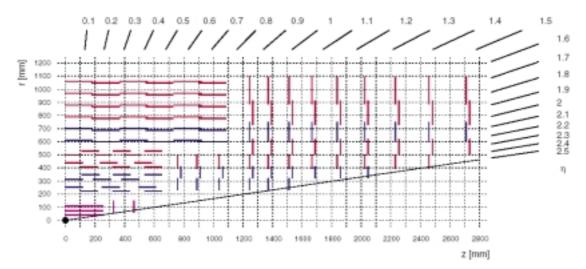

Figure 1.2: Schematic diagram of one quadrant of the CMS Tracker. The origin denotes the interaction point and the numbers on the top and right give the angle in units of  $\eta$ . Closest to the interaction point, the three horizontal layers and two vertical lines denote pixel detector layers. All other layers are silicon microstrip layers [3].

The region closest to the interaction point is instrumented with silicon pixel detectors offering a position resolution of  $10 \rightarrow 15 \,\mu\text{m}$ . The pixel detector system is composed of modules of pixelated sensor plates with integrated readout chips connected to them using the bump bonding technique. Due to the high radiation levels, pixel detectors within 10 cm of the interaction point cannot survive over the lifetime of CMS and will have to be replaced. For this reason, the pixel barrel system will be installed in two stages. At low luminosity, two layers will be installed, one at 4.3 cm and the other at 7.2 cm. At high luminosity, the layer at 4.3 cm will be removed and another will be placed at 11.0 cm. The two endcap disks are located at a mean distance to the interaction point of 32.5 cm and 46.5 cm. In the high luminosity configuration, the pixel detector will have an active surface of close to one square metre, instrumented with approximately  $45 \times 10^6$  channels.

The pixel detector is surrounded by a silicon microstrip detector, known as the silicon strip tracker (SST), consisting of ten barrel layers (from 22 cm up to 120 cm) and twelve endcap disks on either side of the barrel. These layers are numbered from the interaction point outwards.

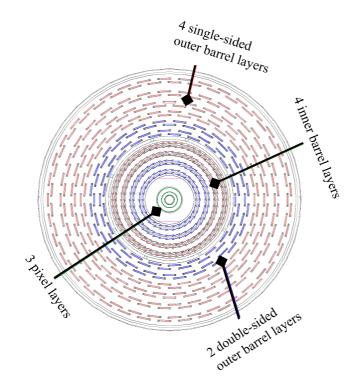

Figure 1.3: Cross-section of the CMS Tracker detector system in the barrel region.

Fig. 1.3 is a cross-section of the Tracker barrel, showing the SST to be composed of single-sided and double-sided layers. The double-sided layers are made of two single-sided sensors mounted back to back, one tilted by an angle of 100 mrad with respect to the other which effectively gives two-dimensional hit positions. The Tracker barrel region consists of four SST inner barrel layers (TIB) followed by six outer barrel layers (TOB). The first two layers of both the TIB and TOB are double-sided.

The endcap system consists of three inner endcap disks (TID) and nine outer endcap disks (TEC) on either side of the barrel.

The distinction between inner and outer regions is not made simply on the grounds of position. Due to the need to optimise the combination of three parameters, depletion voltage (explained in Chapter 2), signal-to-noise ratio and radiation tolerance, the sensors used in the two sections are actually different. The depletion voltage scales with thickness squared and inverse resistivity, but low-resistivity sensors are more radiation tolerant. In the inner section where the radiation levels are higher, the detectors are made of 320  $\mu$ m-thick low-resistivity sensors. Sensors in the outer regions are 500  $\mu$ m in thickness to compensate for the higher noise due to higher capacitance in their longer strips. Experimental measurements have determined that operating the detectors at high voltage in a -10 °C dry environment will limit the extent of radiation damage to the sensors.

#### 1.3.2 Tracker Radiation Environment

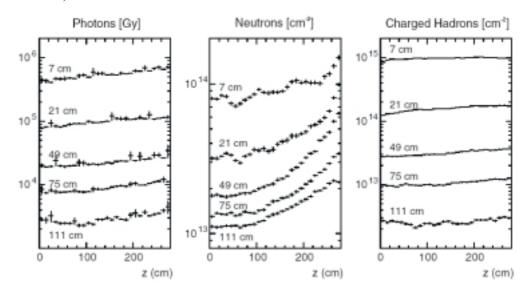

The radiation field within the Tracker is characterised by two distinct sources. Firstly, secondaries from the p-p interactions, the product of their interactions in the Tracker structures and some decay products, give the dominating contribution to the fluences at the inner layers of the Tracker. This component of the fluence is almost independent of the z-coordinate and behaves roughly as  $1/r^2$ , where r is the distance from the beamline. Almost all of the charged hadron fluence originates from the vertex. Secondly, a significant component of the neutron fluence is due to albedo from the surrounding electromagnetic calorimeter. The most intense source of albedo neutrons is the end-cap ECAL. While the fluence originating from the vertex is irreducible, a polyethelene moderator inserted in the bottom structure of the ECAL is shown to efficiently reduce the neutron fluence by a factor of 2.5. The radiation environment over a period of 10 years is presented separately for total dose (1 Gy = 100 rad), neutrons and charged hadrons, Fig. 1.4. To put into perspective the radiation hardness requirements of Tracker electronics, the total dose radiation environment is up to four orders of magnitude higher than the levels at which modern commercial components usually fail  $(5 \rightarrow 20 \text{ krad})$ .

Figure 1.4: Radiation levels at selected radii in the CMS Tracker region. All values correspond to 10 years of operation.

#### 1.3.3 Strip Tracker Electronics

The electronics system for the SST must fulfil the formidable requirements, in terms of particle fluences, magnetic field, material budget and inaccessibility, imposed by the environment in which it will operate whilst being capable of functioning at the level 1 trigger rate of 100 kHz. It is based on a uni-directional analogue readout chain and a bi-

directional digital control chain. Both chains consist of components located in close proximity to the silicon sensors, connected by optical fibres to components housed 100 m away in the experimental barracks. A Timing, Trigger and Control (TTC) system common to all LHC experiments provides clock and trigger information, ensuring the necessary level of synchronicity with the accelerator clock. The SST electronics system is described in more detail in Chapter 3 with an emphasis on radiation tolerance.

#### 1.4 The APV Readout Chip

Imperial College London and the Rutherford Appleton Laboratory (RAL) are responsible for developing the silicon microstrip detector readout chip, the APV (Analogue Pipeline Voltage mode). The APV chips will sample, amplify and store signals from their corresponding microstrip detectors.

In addition to radiation tolerance, the APV has to fulfil the important requirements of low noise and low power driven by the need to discriminate significant signals from the background and to keep the material budget (and consequently the cooling system) at a minimum.

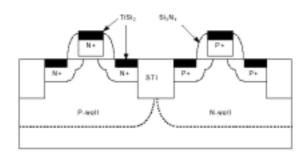

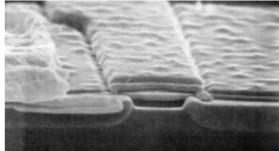

Since its conception in 1993, several versions of the APV chip have been built using different process technologies. Earlier versions such as the APV6 [4] and the APVD [5] were designed and manufactured in qualified radiation hard processes (1.2 µm Harris AVLSIRA process and 0.8 µm TEMIC DMILL process respectively). However, a decrease in defence-related systems acquisitions led to a dramatic drop in the number of radiation-hardened CMOS microcircuit fabrication lines [6]. This in turn led to an increasing disparity in performance, availability, and price of radiation-hardened parts compared to commercial CMOS microelectronics parts. In addition, the long turnaround time from design to production added pressure to the tight schedule for construction of the detector. Attention began to turn to commercial sub-micron technologies in 1997. The interest in these technologies comes from their excellent performance in terms of speed, density and noise, from potentially large cost savings and from increased radiation tolerance compared to their predecessors [7]. The final version of the chip, the APV25 [8], uses a 0.25 µm commercial process. Although no steps are taken in the fabrication process to harden the APV25 chip, it is radiation tolerant by its nature (the oxide layers are very thin) and by design (the chip features  $p^+$  guardrings and enclosed transistor geometries to suppress leakage current paths) [9]. These properties and design features are discussed in more detail in Chapter 2.

#### 1.4.1 The APV25 Analogue Chain

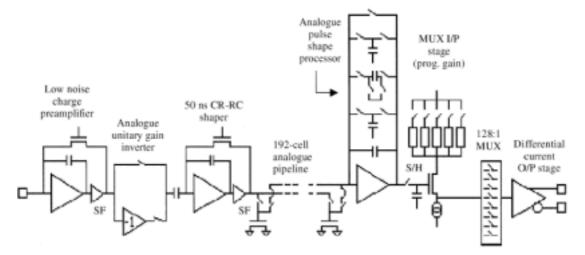

Figure 1.5: Block diagram of the APV25 analogue chain, from [10]. Each of the 128 channels has its own chain from preamp to multiplexer (MUX) stage.

The APV25 analogue block consists of 128 channels, each of which is designed to be bonded on the front side of the chip to a silicon microstrip. The signal from such a strip is first amplified by an integrating preamplifier, then passed through an inverter which can be optionally switched on or off before being shaped by a CR-RC shaper with a 50 ns peaking time, Fig. 1.5. Every 25 ns the shaper output (corresponding to 100 mV/MIP, where 1 MIP = 25000 e for a minimum ionising particle traversing a 300  $\mu$ m thick silicon sensor) is presented to the pipeline input. Up to 4  $\mu$ s worth of information can be stored in the 192 cells of the pipeline. The fate awaiting the information stored in each pipeline cell depends on the mode of operation of the chip and whether or not a trigger has been initiated. A digital pipeline control block consisting of write and trigger pointers sequences the writing, triggering, storing, and retrieval of data from the pipeline. When a trigger is received, useful data are marked after a programmable latency, and held in the pipeline until they can be read out. A 32 deep FIFO retains the addresses of pipeline columns holding marked data. When a signal is read from the pipeline it is processed by a switched capacitor filter, the analogue pulse shape processor (APSP).

#### 1.4.2 The APSP

The action taken by the APSP is determined by one of three modes of operation. The first mode of operation, *deconvolution*, is used in normal operation when data rates are sufficiently high such that the effects of pile-up are significant. In this mode the APSP removes the effects of pile-up to confine the signals to one 25 ns interval. The APSP implements the deconvolution algorithm on the charges from three consecutive pipeline

cells, storing them on three capacitors of different sizes (corresponding to the deconvolution weights). It then outputs a weighted sum of the contents of the three capacitors. The second mode, *peak*, is used when pile-up is not significant and a larger signal-to-noise ratio is required. Here the APSP acts simply as an amplifier and the charge from only one pipeline cell is passed onto the first APSP capacitor. The first capacitor is smaller in peak mode, ensuring that both modes of operation result in the same gain. Although both modes of operation have the same gain, the signal-to-noise ratio is better in peak mode. This is because the noise is higher (by a factor of ~ 1.7) in deconvolution mode since the rising edge of the shaper output, which is used for the third sample, is prone to slewing effects. The third mode, *Multi*, can be used when calibrating a pulse shape, and in this mode multiple consecutive pipeline columns can be triggered and read out without APSP filtering.

#### 1.4.3 APV25 Output

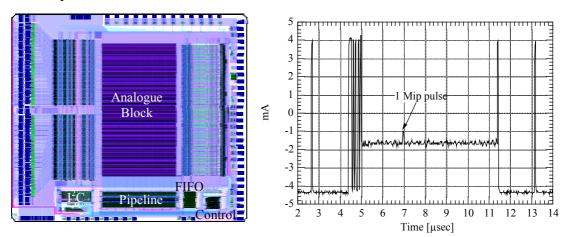

The outputs from all the 128 channel shaper stages are multiplexed (the order does not correspond to the natural channel order) and driven off the chip as a differential bidirectional current preceded by a digital stream. This consists of a 3-bit digital header, the 8-bit pipeline column address and an error bit. The amplitude of the digital header is +/-4 mA and the final analogue gain is +/-1 mA/MIP, Fig. 1.6 (a). Data can be read out at either 20 MHz or 40 MHz rates, and for the 20 MHz rate, interleaving allows for two-chip read-out at a rate of 40 MHz.

(a) APV25-S1 Layout. The total area (b) One line of the APV25 differential output. is  $8.06 \times 7.1 \text{ mm}^2$ .

#### Figure 1.6: APV25 layout and output.

The main digital blocks are indicated: the  $I^2C$  bias registers, pipeline pointers, FIFO and control logic.

#### 1.4.4 Additional Features of the APV25

An internal calibration circuit enables the testing of the analogue circuitry. It generates and injects a pulse of programmable amplitude into between one and eight groups of 16 channels. The timing of the calibrate pulse is adjustable in steps of 3.125 ns.

An on-chip bias generator controls the biases (current, voltage or charge) of the analogue stages of the APV25. A two-wire serial 'slow control' interface based on the Philips  $I^2C$  protocol is used to program the chip operation mode, internal bias registers and calibration settings. The  $I^2C$  interface also handles error states.

Since both clock and trigger lines to the chip are active during the sensitive acquisition time of the chip, they are implemented using low voltage differential signals (LVDS) to minimise interference. In addition to the normal trigger signal sent as a single pulse, a 1 on the *TRIG* line, reset and calibration request signals can also be sent. The reset signal consists of two pulses separated by one clock cycle, 101. This instructs the chip to clear any pipeline pointers and re-launches them with the programmed latency value. A calibrate request signal is a double pulse, 11, on the *TRIG* line. The different *TRIG* signals mean that normal triggers must be separated by at least two clock cycles.

Under normal running conditions the APV25 chip shows very good linearity, better than 5 % over a 5 MIP range, as well as substantial improvements in noise when compared with its predecessors (noise at 0 pF is 246 and 396*e* rms with a slope of 36 and 59.4*e* rms/pF in peak and deconvolution mode, respectively). Its power consumption is 2.3 mW/channel.

#### 1.5 Summary

The intense radiation field produced by the LHC and the requirement to operate the Tracker microstrip detectors at -10 °C define the operational environment of the APV25. Approximately 75 000 APV25 chips will be required to read out the  $\sim 10^7$  microstrip channels. Because the APV25 is manufactured in a commercial CMOS process, it has to be thoroughly evaluated before it can be deployed on such a large scale in CMS.

## Chapter 2 MOSFET Operation

The APV25 readout chip is manufactured in a commercial 0.25  $\mu$ m CMOS technology. To understand how the APV25 will perform in the CMS Tracker environment some knowledge of the operation of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET), the basic building block of the chip, is required. This chapter introduces the properties of the MOSFET and explores how radiation and temperature effects can change its behaviour.

#### 2.1 MOS Device Physics

The MOSFET is essentially a MOS capacitor with two p-n junctions placed adjacent to the channel. CMOS processes use silicon (Si) technology since it is the most mature among all semiconductor technologies. In addition, silicon is easily available, making it the cheapest semiconductor material. It can be doped with impurity atoms, changing its properties. For example, if an arsenic atom with five valence electrons takes the place of one Si atom in the lattice, four of its valence electrons form covalent bonds with surrounding Si atoms and the fifth electron is essentially free for conduction. The silicon is said to be n-type and the arsenic atom is called a donor. When a boron atom with three valence electrons takes the place of a silicon atom, all three valence electrons form covalent bonds and the absence of a fourth electron creates a hole. This is a p-type semiconductor, and the boron atom is an acceptor atom.

The energy at which the probability of finding an electron in a given electronic state is one half is called the Fermi level,  $E_F$ . In an n-type (p-type) semiconductor,  $E_F$  is closer to the conduction (valence) band. In a very pure slab of silicon the Fermi level is exactly half way between the valence and conduction band. The silicon is in its intrinsic state and its Fermi level is called the intrinsic Fermi level,  $E_i$ . The corresponding intrinsic carrier density is  $n_i$  ( $n_i = 9.65 \times 10^9$  cm<sup>-3</sup> at room temperature [11]).

#### 2.1.1 Charge Carrier Transport

The motion of charge carriers in MOS devices is the result of two basic transport phenomena, carrier drift and carrier diffusion.

Carrier drift arises in the presence of an electric field. Taking the case of an n-type semiconductor as an example, the charge carriers are electrons. With no applied field,

the thermal motion of an electron can be visualised as a succession of random scattering from collisions with lattice and impurity atoms and other scattering centres. Over a sufficiently long period of time, the net displacement is zero. The average time between collisions is called the mean free time,  $\tau_c$ . With an applied electric field,  $\xi$ , the electron experiences a force of  $-q\xi$  and is accelerated in the opposite direction to the field. The additional velocity component introduced is called the drift velocity,  $v_n$ . Conservation of momentum leads to the following expression for  $v_n$ :

$$v_n = -\left(\frac{q\,\tau_c}{m_n}\right)\xi \qquad \dots \qquad \text{eq. (2.1)}$$

where  $m_n$  is the effective electron mass which takes into account the influence of interactions with the positive ion cores. The factor  $\frac{q\tau_c}{m_n}$  is called the mobility,  $\mu_n$  (units cm<sup>2</sup>/Vs). Various scattering mechanisms contribute to the total mobility of which the most important are lattice scattering from thermal vibrations,  $\mu_L$ , and impurity scattering,  $\mu_I$ , when a charge carrier travels past an ionised impurity. The temperature and doping dependence of mobility will be discussed later. The total mobility is given by:

$$\frac{1}{\mu} = \frac{1}{\mu_L} + \frac{1}{\mu_I} \qquad \dots \text{eq. (2.2)}$$

Carrier diffusion arises from the movement of charge carriers from a region of high concentration to a region of low concentration, resulting in a diffusion current. The net current is a combination of drift and diffusion components.

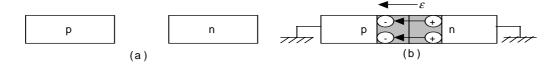

#### 2.1.2 The p-n Junction

The p-n junction is a diode since it allows current to flow only in one direction. It is formed by bringing into contact doped p- and n-type semiconductors, Fig. 2.1.

(a) Uniformly doped p-type and n-type semiconductors before junction is formed.(b) The electric field in the depletion region.

The large carrier concentration gradients at the junction cause carrier diffusion. Holes from the p-side diffuse into the n-side and electrons from the n-side diffuse into the p-

side. These recombine to remove all free carriers from a small region at the interface called the depletion region. Here, only ionised donors and acceptors remain with a resulting electric field directed from the positive charge to the negative charge.

The junction properties can be modified by applying an external bias. The junction is said to be forward-biased when a positive voltage is applied to the p-side with respect to the n-side. This reduces the depletion layer width and the reduced energy barrier for majority carriers leads to increased diffusion currents. The junction is reverse-biased when a positive voltage is applied to the n-side with respect to the p-side. Reverse bias increases the depletion region width. Fewer carriers have enough energy to diffuse over the higher energy barrier and the diffusion current is strongly suppressed. Only a very small net negative drift current remains. The ideal p-n junction diode equation is:

$$I = I_0 \left( e^{\frac{eV_A}{kT}} - 1 \right)$$

.....eq. (2.3).