## **University of Alberta**

## **Library Release Form**

Name of Author: Li Chen

**Title of Thesis:** Radiation Tolerant Design with 0.18-micron CMOS Technology

**Degree:** Doctor of Philosophy

Year this Degree Granted: 2004

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

Signature

606D Michener Park, Edmonton, Alberta Canada, T6H 5A1

## University of Alberta

| Radiation Tolerant Design with 0.18-micron CMOS Technology |

|------------------------------------------------------------|

|------------------------------------------------------------|

| by                                                                                               |

|--------------------------------------------------------------------------------------------------|

| Li Chen                                                                                          |

|                                                                                                  |

|                                                                                                  |

| A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the |

| requirements for the degree of Doctor of Philosophy                                              |

|                                                                                                  |

| Department of Electrical and Computer Engineering                                                |

Edmonton, Alberta Fall 2004

## **University of Alberta**

## Faculty of Graduate Studies and Research

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled **Radiation Tolerant Design with 0.18-micron CMOS Technology** submitted by **Li Chen** in partial fulfillment of the requirements for the degree of **Doctor of Philosophy**.

|       | Dr. Nelson G. Durdle (Supervisor)       |

|-------|-----------------------------------------|

|       | Dr. Douglas M. Gingrich (Co-Supervisor) |

|       | Dr. Igor Filanovsky                     |

|       | Dr. Bruce F. Cockburn                   |

|       | Dr. Kim Chow                            |

| Date: | _                                       |

#### Abstract

This thesis discusses the issues related to the use of enclosed-gate layout transistors and guard rings in a 0.18 µm CMOS technology in order to improve the radiation tolerance of ASICs. The thin gate oxides of submicron technologies are inherently more radiation tolerant than the thicker oxides present in less advanced technologies. Using a commercial deep submicron technology to build up radiation-hardened circuits introduces several advantages compared to a dedicated radiation-hard technology, such as speed, power, area, stability, and expense.

Some novel aspects related to the use of enclosed-gate layout transistors are presented in this thesis. A model to calculate the aspect ratio is introduced and verified. Some important electrical parameters of the transistors such as threshold voltage, leakage current, subthreshold slope, and transconductance are studied before and after being irradiation up to 70 kGy(SiO<sub>2</sub>). The analyzed electrical parameters shift a very limited amount after the irradiation. This research shows that a 0.18 µm CMOS technology (gate oxide thickness of 4.3 nm), combined with enclosed-gate layout transistors and guard rings can effectively resist total dose effects to a very high level (more than 70 kGy(SiO<sub>2</sub>)) with negligible performance degradation.

A digital library is developed with enclosed-gate layout transistors and a configurable SRAM architecture is introduced. Some low-power techniques are adopted, such as divided-word line structure, automatic power down function, and address transition detection. A SRAM test chip is designed and fabricated with the custom-designed library.

Single-event upsets become more significant in deep submicron technologies than the less advanced ones which have a larger feature size, because of the decreased charge needed to flip the state of a node in a circuit. There are many techniques for hardening the SRAM to guard against single-event upset. These hardening techniques are introduced and evaluated with the  $0.18~\mu m$  technology. An overall best solution is determined in terms of power, speed, and area.

# Table of Contents

| Intro | duct   | ion     |                                                                | 20 |

|-------|--------|---------|----------------------------------------------------------------|----|

| Chap  | oter 1 | l Intr  | oduction to Radiation Environments                             | 25 |

| 1     | .1     | The sp  | pace environment                                               | 25 |

| 1     | .2     | The gr  | ound level                                                     | 27 |

| 1     | 3      | The nu  | uclear reactor environment                                     | 28 |

| 1     | .4     | The ra  | diation processing environment                                 | 28 |

| 1     | .5     | The w   | eapons environment                                             | 29 |

| 1     | .6     | High-   | energy physics accelerators                                    | 31 |

| Chap  | oter 2 | 2 Intr  | oduction to Radiation Effects on MOS Devices and ICs           | 32 |

| 2     | 2.1    | Interac | ctions between radiation particles and matter                  | 32 |

| 2     | 2.2    | Total o | dose effects                                                   | 35 |

|       |        | 2.2.1   | Charge trapping in silicon dioxide                             | 35 |

|       |        | 2.2.2   | Charge trapping at the SiO <sub>2</sub> -Si interface          | 37 |

| 2     | 2.3    | Radiat  | tion effects on the electrical parameters of a MOS transistor  | 37 |

|       |        | 2.3.1   | Threshold voltage shift                                        | 38 |

|       |        | 2.3.2   | Change of leakage current: subthreshold and parasitic currents | 39 |

|       |        | 2.3.3   | Decrease of mobility and transconductance                      | 41 |

|       |        | 2.3.4   | Noise increase                                                 | 42 |

| 2     | 2.4    | Single  | -event effects                                                 | 42 |

|       |        | 2.4.1   | Soft upsets                                                    | 42 |

|       |        | 2.4.2   | Hard upsets                                                    | 45 |

| 2     | 2.5    | Summ    | ary                                                            | 47 |

| Chap  | oter 3 | 3 Dee   | p Submicron CMOS Technologies for Radiation Applications       | 48 |

| 3     | 3.1    | Techn   | ology scaling                                                  | 48 |

| 3     | 3.2    | Benefi  | icial radiation effects of the technology scaling              | 51 |

|       |        | 3.2.1   | Total dose tolerance                                           | 51 |

|       |        | 3.2.2   | Single-event latch-up.                                         | 52 |

| 3     | 3.3    | Detrin  | nental radiation effects of the technology scaling             | 53 |

| Chapter | 4 Rad   | liation-Hardening Techniques                           | 56     |

|---------|---------|--------------------------------------------------------|--------|

| 4.1     | Proces  | ss-related radiation-hardening techniques              | 56     |

| 4.2     | Layou   | t-related radiation-hardening techniques               | 57     |

| 4.3     | Circui  | t and system-related radiation-hardening techniques    | 61     |

| Chapter | 5 Mod   | deling of Enclosed-Gate Transistors                    | 64     |

| 5.1     | Aspec   | t ratio calculation                                    | 64     |

| 5.2     | Verific | cation                                                 | 68     |

|         | 5.2.1   | Test chip development                                  | 68     |

|         | 5.2.2   | Measurements and results                               | 71     |

| 5.3     | Aspec   | t ratio limitation                                     | 71     |

| 5.4     | Outpu   | t characteristics                                      | 73     |

|         | 5.4.1   | Output conductance asymmetry                           | 74     |

|         | 5.4.2   | Channel length modulation                              | 76     |

| Chapter | 6 Tota  | al Dose Effects on Enclosed-GateTransistors            | 78     |

| 6.1     | Radiat  | tion test procedures                                   | 78     |

| 6.2     | Radiat  | tion introduced threshold voltage shift                | 80     |

| 6.3     | Radiat  | tion induced subthreshold slope shift                  | 82     |

| 6.4     | Radiat  | tion introduced leakage current                        | 84     |

| 6.5     | Radiat  | tion induced transconductance shift                    | 85     |

| Chapter | 7 Nois  | se Performance of Enclosed-Gate Transistors            | 89     |

| 7.1     | MOSF    | FET noise                                              | 89     |

|         | 7.1.1   | Channel thermal noise                                  | 90     |

|         | 7.1.2   | 1/f noise                                              | 91     |

|         | 7.1.3   | Total noise power spectral density                     | 92     |

| 7.2     | Experi  | iment                                                  | 92     |

|         | 7.2.1   | Devices under test                                     | 92     |

|         | 7.2.2   | Measurement setup                                      | 93     |

|         | 7.2.3   | Measurement results                                    | 94     |

| Chapter | 8 Con   | figurable SRAM Macro Design to Resist Total Dose Effec | ts 100 |

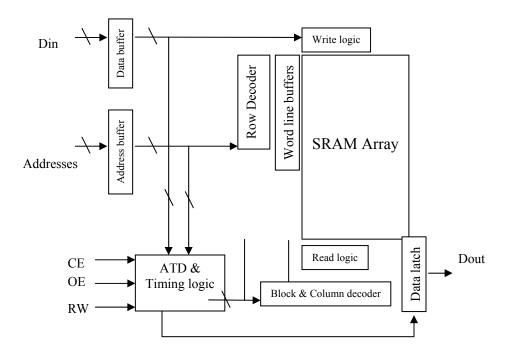

| 8.1     | Memo    | ory architecture                                       | 100    |

| 8.2     | Memo    | ory cell design                                        | 102    |

| 8.3      | A dig | tal library with ELTs and guard rings                     | 103 |

|----------|-------|-----------------------------------------------------------|-----|

| 8.4      | Divid | ed word line structure                                    | 105 |

| 8.5      | Auton | natic power down function                                 | 106 |

| 8.6      | Sense | amplifiers and equalization                               | 108 |

| 8.7      | Perfo | mance and other features                                  | 109 |

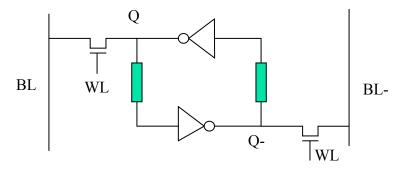

| Chapter  | 9 SR  | AM Design to Guard Again Single-event Effects             | 113 |

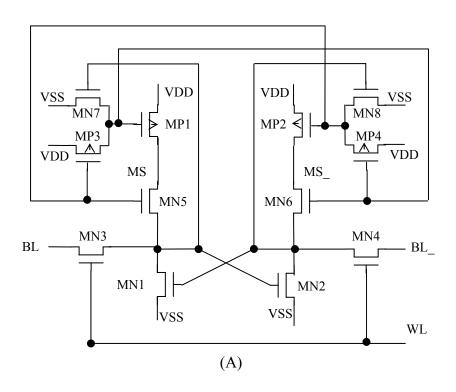

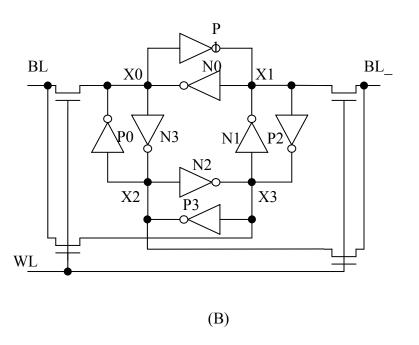

| 9.1      | SRAN  | 1 hardening techniques                                    | 113 |

|          | 9.1.1 | SRAMs using enhanced critical charge hardening techniques | 113 |

|          | 9.1.2 | SRAMs using redundant circuit hardening techniques        | 114 |

| 9.2      | Simul | ation results and discussions                             | 117 |

|          | 9.2.1 | Enhanced critical charge hardening techniques             | 117 |

|          | 9.2.2 | Redundant circuit hardening techniques                    | 119 |

| Conclus  | ions  |                                                           | 121 |

| Bibliogr | aphy  |                                                           | 124 |

# List of Tables

| Table 5.1: | The gate lengths and calculated widths for five sizes of enclosed-            |     |

|------------|-------------------------------------------------------------------------------|-----|

|            | gate transistors.                                                             | 70  |

| Table 5.2: | Differences between the calculated and measured aspect ratios                 |     |

|            | for five different sizes enclosed-gate transistors.                           | 71  |

| Table 5.3: | The measured output conductance values for the drain inside $(g_{\text{di}})$ |     |

|            | and outside (gdo) the gate with five different enclosed-gate                  |     |

|            | transistors. Their gate length and width are listed in the first              |     |

|            | column of the table. $V_{gs}$ of the transistors is 0.5 V                     | 75  |

| Table 6.1: | The width and length of enclosed-gate transistors in each chip                |     |

|            | under test.                                                                   | 78  |

| Table 6.2: | The radiation periods and radiation doses absorbed by each chip               |     |

|            | under test.                                                                   | 79  |

| Table 7.1: | Extracted channel thermal noise and Ka, from the enclosed-gate                |     |

|            | transistors (length is 1 $\mu m$ ) in DUT0 with different drain               |     |

|            | voltages, before and after 29 $kGy(SiO_2)$ absorbed dose                      |     |

|            | irradiation.                                                                  | 99  |

| Table 8.1: | Some characteristics for the SRAM. The timing parameters are                  |     |

|            | measured from simulation.                                                     | 111 |

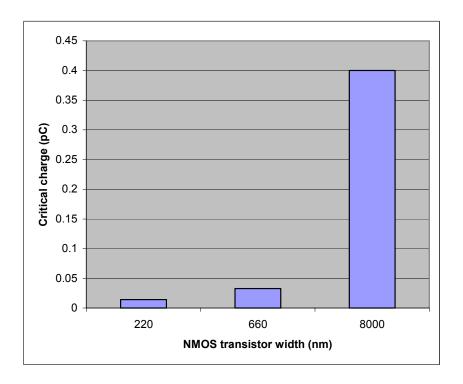

| Table 9.1: | Width versus critical charge of the NMOS transistors in a SRAM                |     |

|            | cell.                                                                         | 117 |

| Table 9.2: | Transistor sizes for the HIT cell.                                            | 119 |

| Table 9.3: | Parameters for each studied cell.                                             | 120 |

# List of Figures or Illustrations

| Figure 2.1: | Illustration of charge trapping in the gate oxide of a NMOS                  |    |

|-------------|------------------------------------------------------------------------------|----|

|             | transistor.                                                                  | 36 |

| Figure 2.2: | Illustration of the parasitic transistors that are in parallel to the        |    |

|             | main transistor and of the parasitic leakage paths in the shallow-           |    |

|             | trench isolation region or underneath the field oxide which                  |    |

|             | connects the source and the drain.                                           | 41 |

| Figure 2.3: | Illustration of charge collection profiles for a target node from the        |    |

|             | diffusion and combination of diffusion with funneling effects.               |    |

|             | The charge collection curves are in time scale; the circuit node             |    |

|             | array and particle track are shown in a cross-section diagram                | 44 |

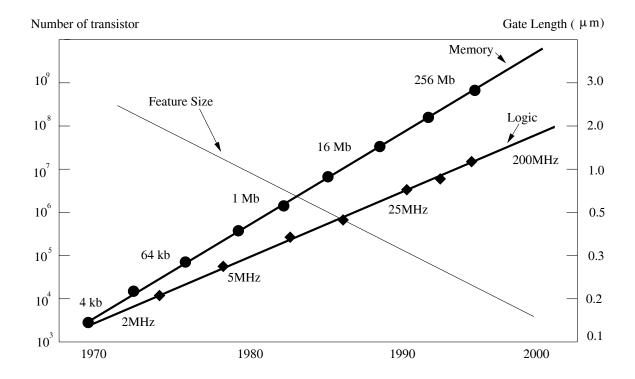

| Figure 3.1: | The plot shows how scaling density and speed vary with time (i.e.            |    |

|             | decreasing the minimum feature size). The data are taken from                |    |

|             | [Cit99]. The left side of Y-axis indicates the number of                     |    |

|             | transistors on a chip; the right side of Y-axis is the minimum gate          |    |

|             | length of transistors.                                                       | 49 |

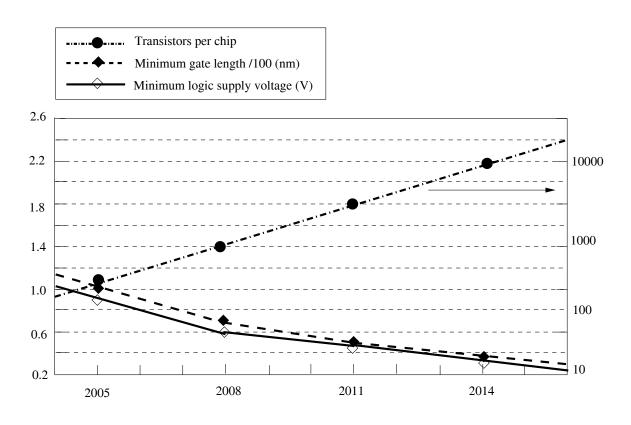

| Figure 3.2: | Technology trends foreseen for the next 10 years. The data are               |    |

|             | taken from [Ane99a]. The line with the round markers refers to               |    |

|             | the right axes (logarithmic scale), the others to the left axes              |    |

|             | (linear scale).                                                              | 50 |

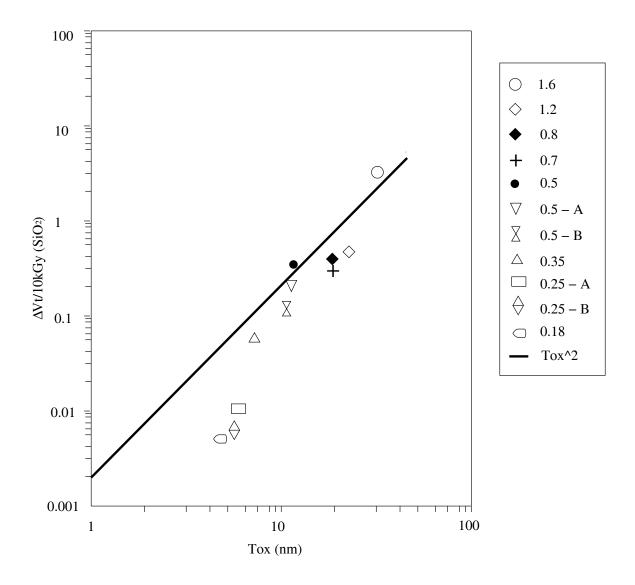

| Figure 3.3: | Threshold voltage variation per 10 kGy(SiO <sub>2</sub> ) dose as a function |    |

|             | of the oxide thickness. Some of the data are taken from [Ane99]              | 53 |

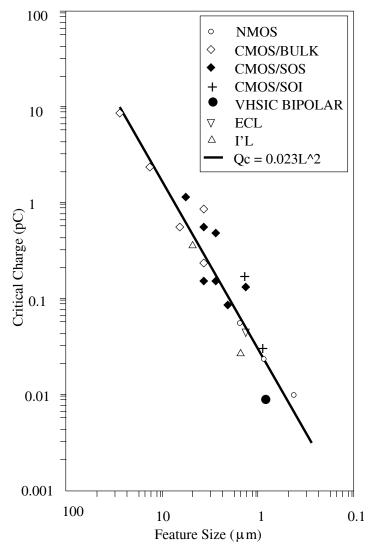

| Figure 3.4: | SEU critical charge versus feature size for various technologies.            |    |

|             | The data are taken from [Pet].                                               | 55 |

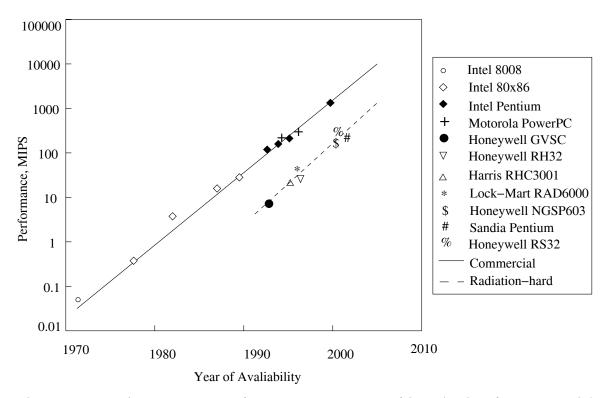

| Figure 4.1: | Micorprocessor performance versus year of introduction for                   |    |

|             | commercial and radiation-hard micorprocessors. The data are                  |    |

|             | taken from [Lac00].                                                          | 57 |

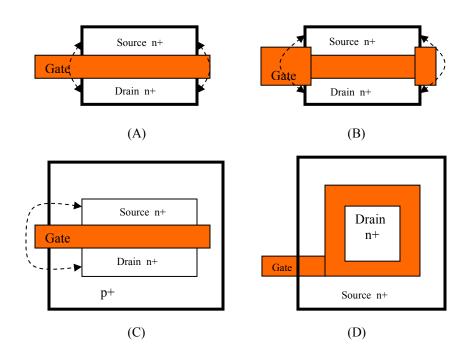

| Figure 4.2: | Layouts of a standard self-aligned NMOS transistor (A) and of                |    |

|             | three possible alternatives (B, C, and D) to inhibit the leakage             |    |

|             | paths shown in the standard transistor. The thin oxide areas,                |    |

|             | where there can be a creation of a radiation-induced parasitic             |    |

|-------------|----------------------------------------------------------------------------|----|

|             | path, are indicated with thick black lines. The leakage paths are          |    |

|             | represented with dash lines                                                | 59 |

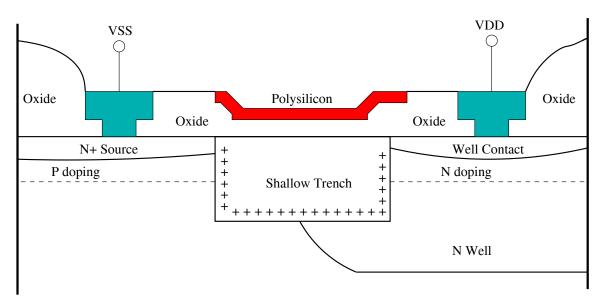

| Figure 4.3: | Illustration of a radiation induced parasitic path in an n-well            |    |

|             | CMOS technology with shallow-trench isolation. The well of a               |    |

|             | PMOS transistor, connected to the power supply, is leaking                 |    |

|             | toward the grounded source on an NMOS transistor. If a biased              |    |

|             | interconnection line (made of polysilicon in the case of the               |    |

|             | figure) passes over the thick oxide, it worsens the problem                | 60 |

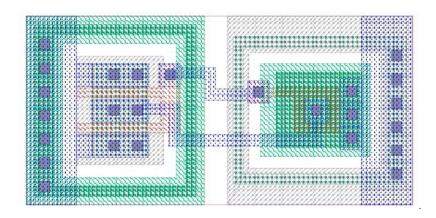

| Figure 4.4: | Layout of an inverter using the proposed radiation tolerant layout         |    |

|             | approach in a CMOS technology. The n-well layer is not shown               |    |

|             | in the figure.                                                             | 61 |

| Figure 4.5: | Schematic of a resistor hardened SRAM cell.                                | 62 |

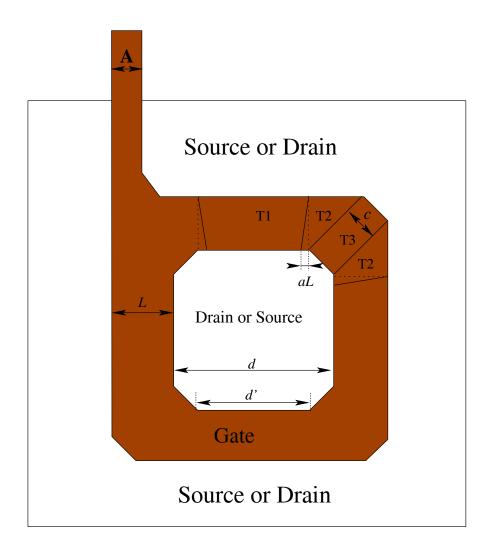

| Figure 5.1: | Diagram of an enclose-gate transistor. The transistor can be               |    |

|             | thought of as being formed by transistors of three different kinds         |    |

|             | in parallel, labeled in the picture T1, T2 and T3                          | 66 |

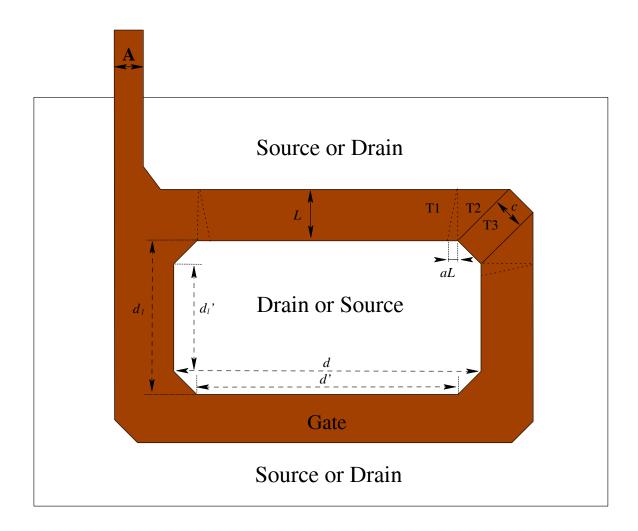

| Figure 5.2: | Shape of an enclosed-gated transistor stretched in one direction to        |    |

|             | achieve higher aspect ratio.                                               | 67 |

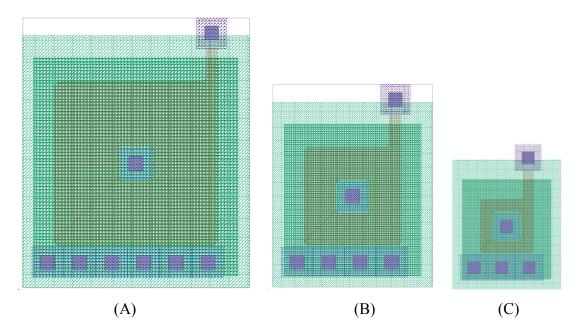

| Figure 5.3: | Layouts of three enclosed-gate transistors, whose gate lengths are         |    |

|             | 1 $\mu m$ (A), 0.5 $\mu m$ (B) and 0.21 $\mu m$ (C) respectively. For each |    |

|             | diagram, the blue square in the middle is the drain or source              |    |

|             | contact, surrounded with the gate (dark red). On the top of the            |    |

|             | layout, there are a gate contact and a piece of metal1 in square           |    |

|             | shape. There are several contacts covered with metal1 for the              |    |

|             | source or drain at the bottom of the layouts.                              | 69 |

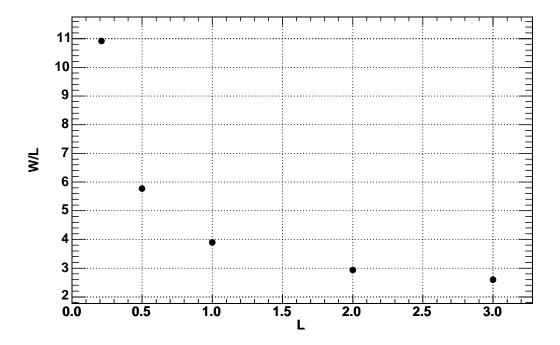

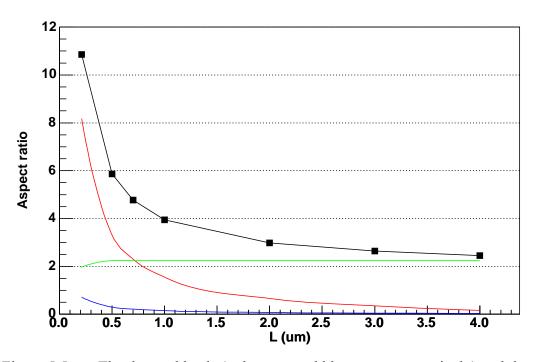

| Figure 5.4: | Calculated aspect ratio versus gate length for five different gate         |    |

|             | length enclosed-gate transistors.                                          | 70 |

| Figure 5.5: | The three addends (red, green and blue curve respectively) and             |    |

|             | the total in Equation 5.1 (black curve with square marks) as a             |    |

|             | function of the gate length.                                               | 72 |

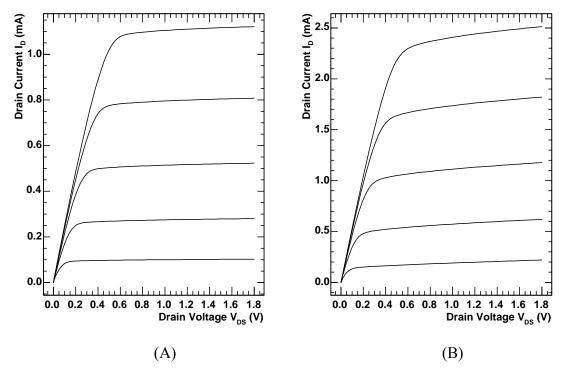

| Figure 5.6: | (A) $L = 2 \mu m$ , $W = 5.96 \mu m$ enclosed-gate transistor drain current            |    |

|-------------|----------------------------------------------------------------------------------------|----|

|             | versus drain voltage curves; (B) $L = 0.21 \mu m$ , $W = 2.34 \mu m$                   |    |

|             | enclosed-gate transistor drain current versus drain voltage curves.                    |    |

|             | In every plot, the gate voltages of the five curves from bottom to                     |    |

|             | top are 0.5 V, 0.6 V, 0.7 V, 0.8 V, and 0.9 V                                          | 74 |

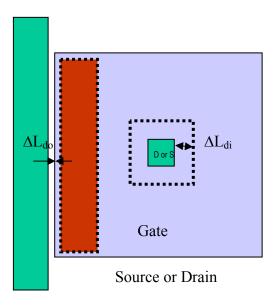

| Figure 5.7: | Illustration of the channel length modulation for an enclosed-gate                     |    |

|             | transistor with the drain is in or outside the gate. The dotted lines                  |    |

|             | on the gate of the enclosed-gate transistor indicate the position of                   |    |

|             | the pinch-off inside the channel for the two possible choices of                       |    |

|             | the drain. A square gate was taken here to simplify the                                |    |

|             | calculations                                                                           | 76 |

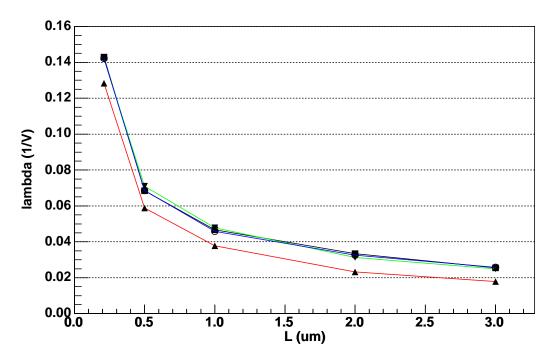

| Figure 5.8: | Channel length modulation data extracted from the standard                             |    |

|             | transistors (blue curve), enclosed-gate transistors with the drain                     |    |

|             | inside (green curve) and source inside (red curve) configurations.                     |    |

|             | For each type of transistors, there are five different gate lengths,                   |    |

|             | 3.0 μm, 2.0 μm, 1.0 μm, 0.5 μm and 0.21 μm.                                            | 77 |

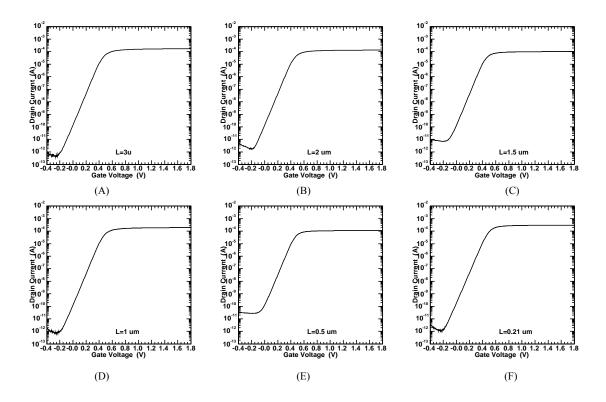

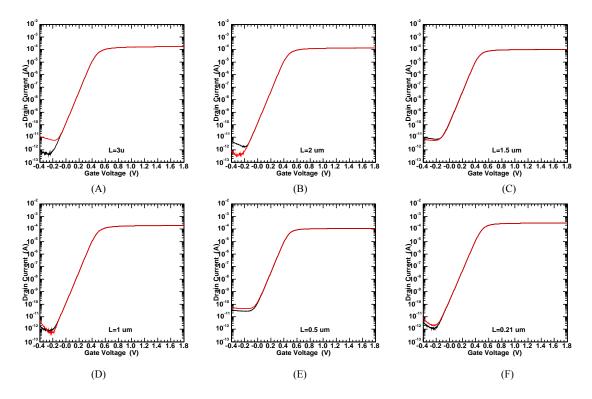

| Figure 6.1: | Drain current versus gate voltage data for six transistors whose                       |    |

|             | gate lengths are (A) 3 $\mu$ m, (B) 2 $\mu$ m, (C) 1.5 $\mu$ m, (D) 1 $\mu$ m, (E)     |    |

|             | $0.5~\mu m,\; (F)~0.21~\mu m$ in DUT4. The drain to source voltage is                  |    |

|             | 0.05 V.                                                                                | 80 |

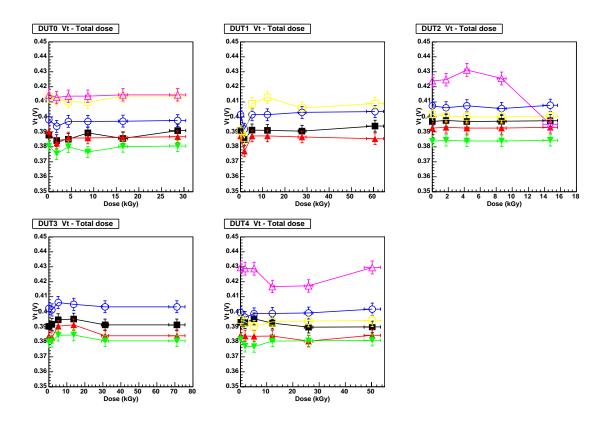

| Figure 6.2: | The threshold voltage shift as a function of the total dose for the                    |    |

|             | transistors in DUT0, DUT1, DUT2, DUT3 and DUT4. In each                                |    |

|             | diagram, the black, red, green, blue, yellow and pink curves                           |    |

|             | represent the data of $L = 3.0 \mu m$ , $L = 2.0 \mu m$ , $L = 1.5 \mu m$ , $L = 1.0$  |    |

|             | $\mu$ m, $L$ = 0.5 $\mu$ m, $L$ = 0.21 $\mu$ m enclosed-gate transistors               |    |

|             | respectively                                                                           | 81 |

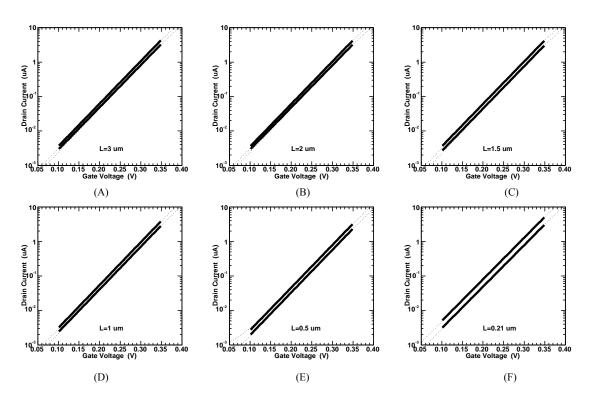

| Figure 6.3: | In the subthreshold region, drain current (on log scale) versus                        |    |

|             | gate voltage, fitted to a straight line for six types of transistors in                |    |

|             | DUT4. The gate lengths of the transistors are (A) 3 $\mu$ m, (B) 2                     |    |

|             | $\mu m,$ (C) 1.5 $\mu m,$ (D) 1 $\mu m,$ (E) 0.5 $\mu m$ and (F) 0.21 $\mu m.$ The two |    |

|             | lines represent data of drain current when gate voltages are 0.05                      |    |

|             | V and 1 V respectively. The line on the top is for $V_{gs} = 1$ V in                    |    |

|-------------|-----------------------------------------------------------------------------------------|----|

|             | each diagram                                                                            | 82 |

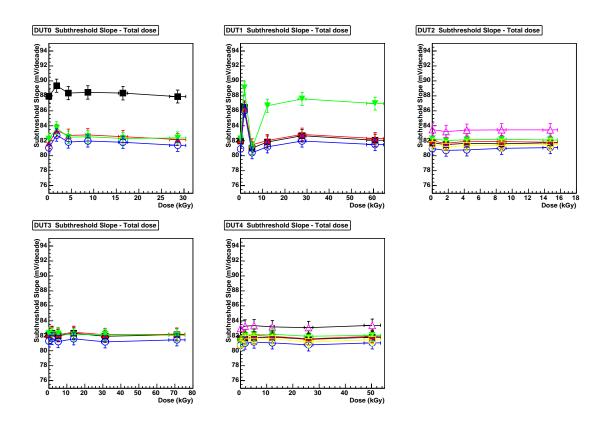

| Figure 6.4: | The extracted subthreshold slope as a function of the total dose                        |    |

|             | for the transistors in DUT0, DUT1, DUT2, DUT3 and DUT4. In                              |    |

|             | each diagram, the black, red, green, blue, yellow and pink curves                       |    |

|             | represent the data of $L = 3.0 \mu m$ , $L = 2.0 \mu m$ , $L = 1.5 \mu m$ , $L = 1.0$   |    |

|             | $\mu$ m, $L$ = 0.5 $\mu$ m, $L$ = 0.21 $\mu$ m enclosed-gate transistors                |    |

|             | respectively                                                                            | 83 |

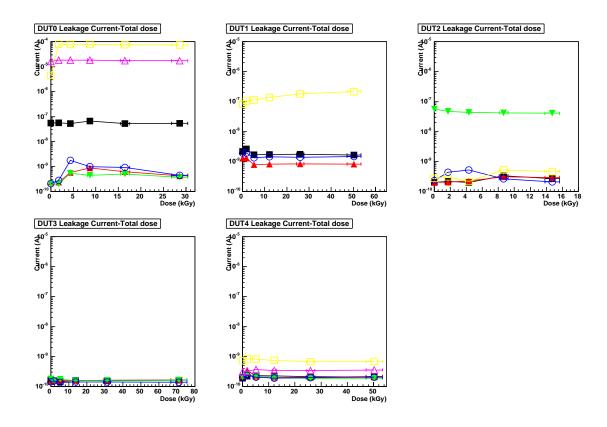

| Figure 6.5: | The leakage current as a function of the total dose for the                             |    |

|             | transistors in DUT0, DUT1, DUT2, DUT3 and DUT4. In each                                 |    |

|             | diagram, the black, red, green, blue, yellow and pink curves                            |    |

|             | represent the data of enclosed-gated transistors whose gate                             |    |

|             | lengths equal $3.0~\mu m,~2.0~\mu m,~1.5~\mu m,~1.0~\mu m,~0.5~\mu m$ and               |    |

|             | $0.21\mu m$ , respectively. The drain voltage is $1.0\ V$ , and the gate                |    |

|             | voltage is 0 V for each transistor.                                                     | 85 |

| Figure 6.6: | An example of drain current versus gate voltage curves before                           |    |

|             | (black curve) and after 50 kGy(SiO <sub>2</sub> -Si) irradiation (red curve)            |    |

|             | for six different sizes of transistors in DUT4. The gate lengths for                    |    |

|             | the tested transistors are (A) 3 $\mu$ m, (B) 2 $\mu$ m, (C) 1.5 $\mu$ m, (D) 1         |    |

|             | $\mu m,$ (E) 0.5 $\mu m,$ (F) 0.21 $\mu m.$ The drain voltage is 0.05 V                 | 86 |

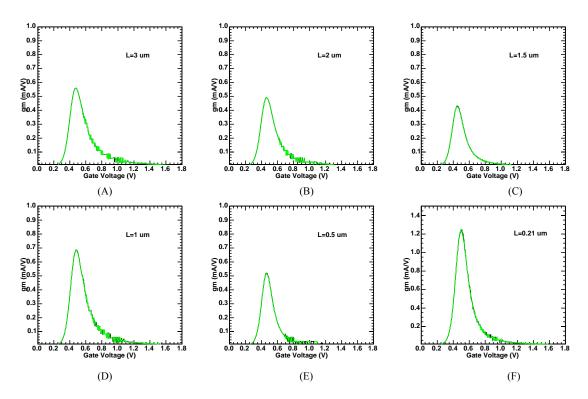

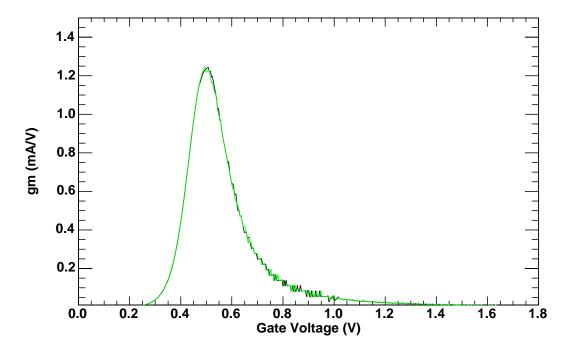

| Figure 6.7: | Extracted transconductance curves before (black) and after                              |    |

|             | (green) 50 kGy(SiO2) irradiation for different size enclosed-gate                       |    |

|             | transistors in DUT4. The gate lengths for the tested transistors are                    |    |

|             | (A) 3 $\mu$ m, (B) 2 $\mu$ m, (C) 1.5 $\mu$ m, (D) 1 $\mu$ m, (E) 0.5 $\mu$ m, (F) 0.21 |    |

|             | μm. The drain voltage is 0.05 V.                                                        | 87 |

| Figure 6.8: | Extracted transconductance curves before (black) and after                              |    |

|             | (green) 50 kGy(SiO <sub>2</sub> ) irradiation for an enclosed-gate transistor           |    |

|             | in DUT4. The gate length for the tested transistor is 0.21 $\mu m.$ The                 |    |

|             | drain voltage is 0.05 V.                                                                | 88 |

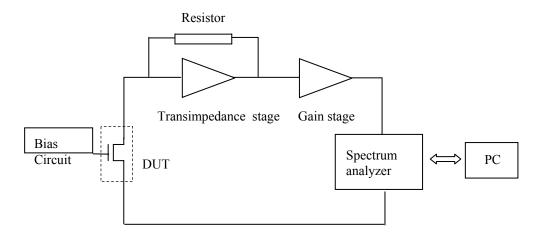

| Figure 7.1. | Schematic of noise measurement setup                                                    | 94 |

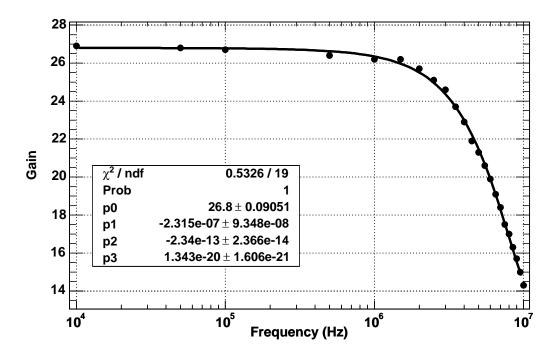

| Figure 7.2: | An example of gain versus frequency of an enclosed-gate                                                 |     |

|-------------|---------------------------------------------------------------------------------------------------------|-----|

|             | transistor in DUT1, $L = 0.5 \mu m$ , $W = 2.93 \mu m$ , $V_{gs} = 0.6 \text{ V}$ , $V_{ds} =$          |     |

|             | 0.2 V                                                                                                   | 95  |

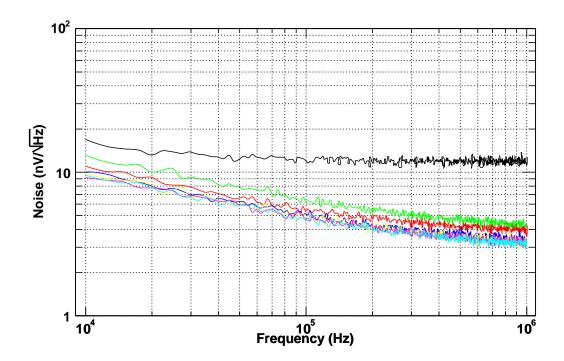

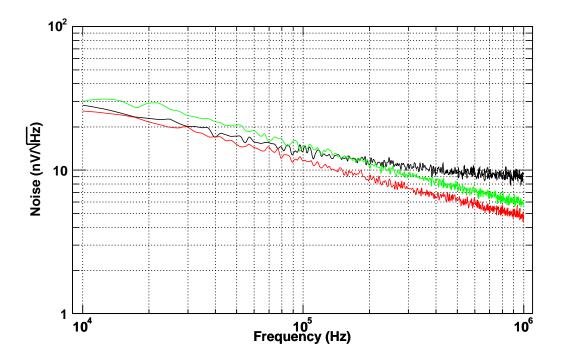

| Figure 7.3: | An example of noise versus frequency diagram of an enclosed-                                            |     |

|             | gate transistor in DUT0, $L = 1 \mu m$ , $W = 3.95 \mu m$ , $V_{gs} = 0.6 V$ ,                          |     |

|             | $V_{ds} = 0.1 \text{ V}$ (black curve), 0.2 V (green curve), 0.3 V (yellow),                            |     |

|             | 0.4 V (red curve), 0.5 V (dark blue curve), 0.6V (pink curve) and                                       |     |

|             | 0.7 V (light blue curve).                                                                               | 96  |

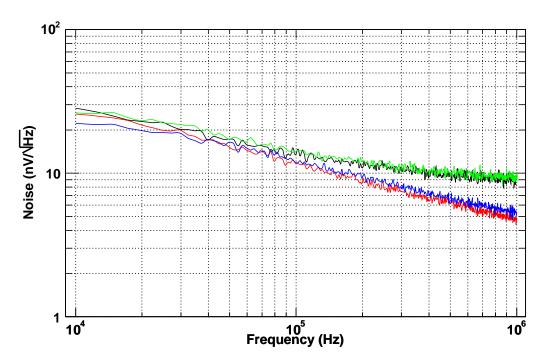

| Figure 7.4: | An example of noise versus frequency diagram of an enclosed-                                            |     |

|             | gate transistor in DUT0, $L = 0.21 \mu \text{m}$ , $W = 2.34 \mu \text{m}$ , $V_{gs} = 0.6 \text{ V}$ , |     |

|             | $V_{ds} = 0.1 \text{ V}$ (black curve), 0.2 V (green curve) and 0.3 V (red                              |     |

|             | curve)                                                                                                  | 97  |

| Figure 7.5: | An example of noise versus frequency diagram of an enclosed-                                            |     |

|             | gate transistor in DUT0, $L = 0.21 \mu \text{m}$ , $W = 2.34 \mu \text{m}$ , $V_{gs} = 0.6 \text{ V}$ , |     |

|             | $V_{ds} = 0.1 \text{ V}, 0.2 \text{ V}, \text{ before and after radiation, represented by}$             |     |

|             | black, green, red and blue curves, respectively                                                         | 98  |

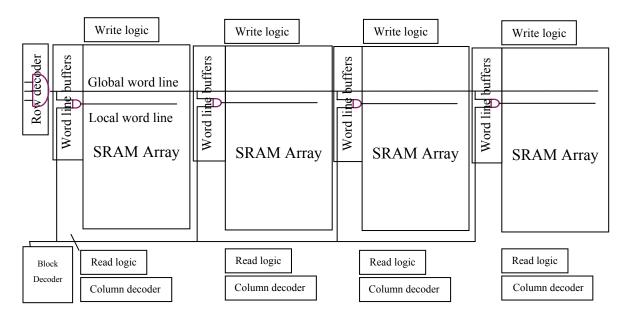

| Figure 8.1: | Block diagram of the SRAM architecture.                                                                 | 101 |

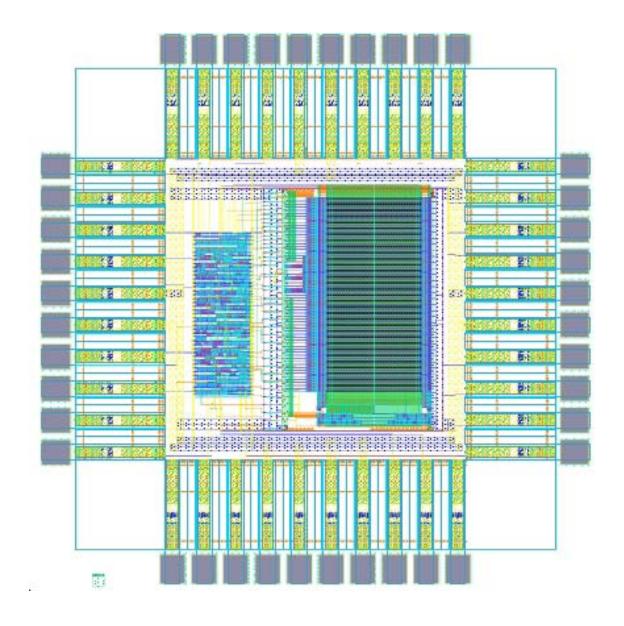

| Figure 8.2: | Layout of a SRAM cell with ELTs and guard rings                                                         | 102 |

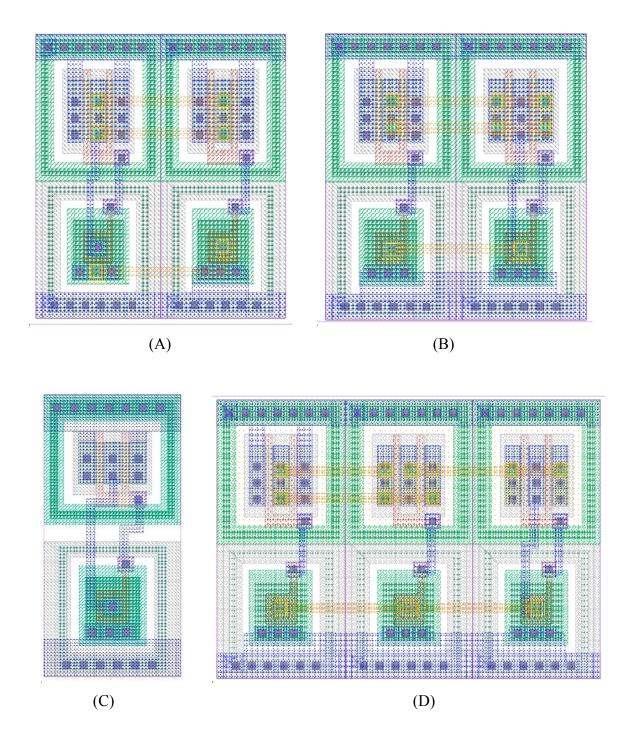

| Figure 8.3: | (A) Layout of a two-input NAND gate with one fanout of one; (B)                                         |     |

|             | layout of a two-input NOR gate with a fanout of one; (C) layout                                         |     |

|             | of an inverter with a fanout of one; (D) layout of three-input                                          |     |

|             | NOR gate with a fanout of one                                                                           | 104 |

| Figure 8.4: | Block diagram of the divided word line structure.                                                       | 105 |

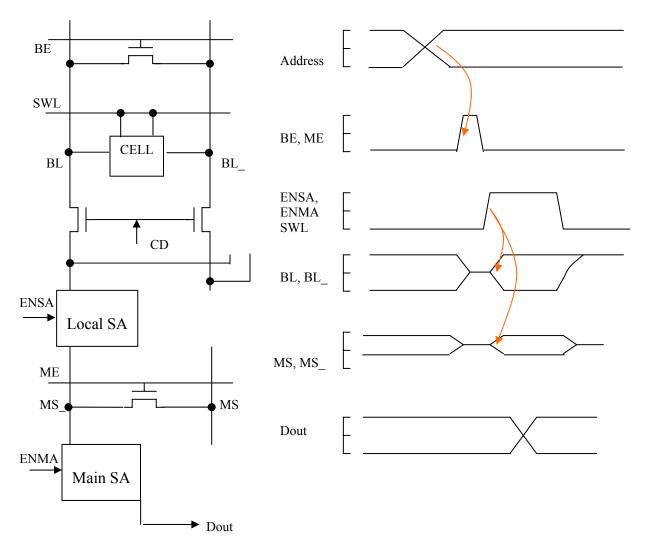

| Figure 8.5: | A schematic of the core part and a rough sketch of internal                                             |     |

|             | waveforms.                                                                                              | 107 |

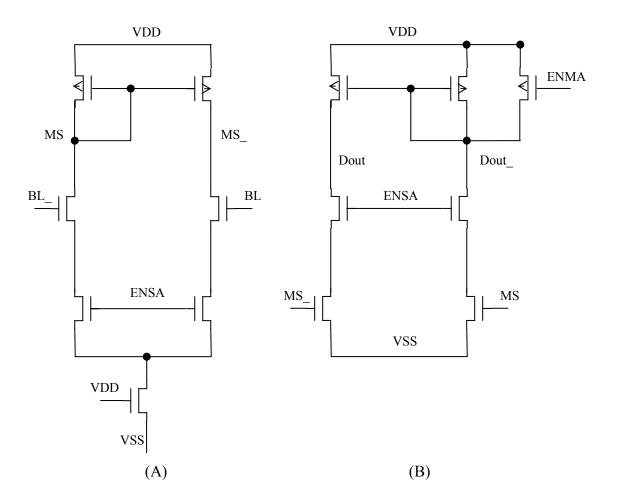

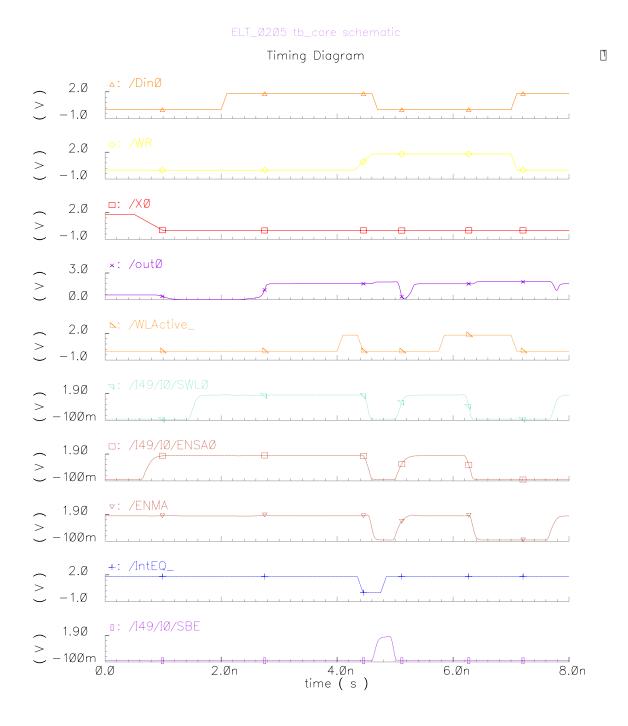

| Figure 8.6: | (A) The schematic of local current mirror sense amplifier; (B) the                                      |     |

|             | schematic of main current mirror sense amplifier                                                        | 109 |

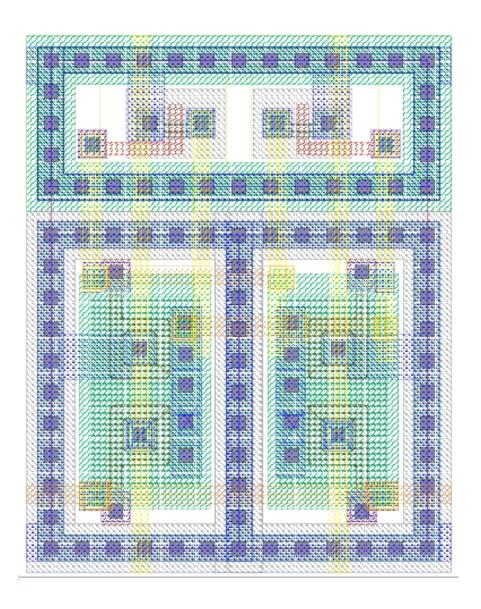

| Figure 8.7: | Layout of the $1k \times 9bit$ SRAM test chip. The right part in the core                               |     |

|             | is the memory arrays and row/column decoders; the left part is                                          |     |

|             | the peripheral circuits of the memory                                                                   | 110 |

| Figure 8 8. | The timing diagram for a write followed by a read operation                                             | 112 |

| Figure 9.1: | (A) Schematic of a HIT SRAM cell; (B) Schematic of a DICE    |     |

|-------------|--------------------------------------------------------------|-----|

|             | SRAM cell.                                                   | 116 |

| Figure 9.2: | NMOS transistors width versus critical charge in a SRAM cell | 118 |

# List of Symbols and Abbreviations

| Symbol             | Description                                         | Unit              |

|--------------------|-----------------------------------------------------|-------------------|

| $C_d$              | Depletion-layer capacitance per unit area           | F/cm <sup>2</sup> |

| $C_{it}$           | Interface trapped capacitance per unit area         | F/cm <sup>2</sup> |

| $C_{ox}$           | Oxide capacitance per unit area                     | F/cm <sup>2</sup> |

| $\Delta N_{ot}$    | The areal trapped charge density referred to the    |                   |

|                    | SiO <sub>2</sub> -Si interface                      | C/cm <sup>2</sup> |

| $\Delta V_T$       | Threshold voltage shift                             | V                 |

| $\Delta V_{it}$    | Threshold voltage shift introduced by the charge    |                   |

|                    | trapping in the interface                           | V                 |

| $\Delta V_{ox}$    | Threshold voltage shift introduced by the charge    |                   |

|                    | trapping in the silicon oxide                       | V                 |

| $\mathcal{E}_{ox}$ | Oxide permittivity (= $3.45 \times 10^{-13}$ F/cm)  | F/cm              |

| f                  | Frequency, clock frequency                          | Hz                |

| $\phi_B$           | Bulk potential                                      | V                 |

| $\phi_t$           | Thermal voltage (=0.0259 V, when 300°K)             | V                 |

| $g_d$              | MOSFET small-signal output conductance              | A/V               |

| $g_m$              | MOSFET small-signal transconductance                | A/V               |

| $g_{mb}$           | MOSFET small-signal bulk transconductance           | A/V               |

| $I_d$              | Drain Current in a MOSFET                           | A                 |

| $K_B$              | Boltzmann's constant (= $1.38 \times 10^{-23}$ J/K) | J/K               |

| L                  | Length, MOSFET channel length                       | cm                |

| $L_{e\!f\!f}$      | Effective channel length                            | cm                |

| λ                  | Channel length modulation                           | 1/V               |

| $\mu$              | Carrier mobility                                    | $cm^2/V-s$        |

| $\mu_0$            | Pre-radiation carrier mobility                      | $cm^2/V-s$        |

| $n_i$              | Silicon intrinsic carrier density                   | cm <sup>-3</sup>  |

| q                  | Electronic charge (= $1.6 \times 10^{-19}$ C)       | C                 |

| $Q_c$              | Critical charge for single-event upset              | C                 |

|                    |                                                     |                   |

| r          | Resistance                         | Ω                |

|------------|------------------------------------|------------------|

| $R_B$      | MOSFET substrate resistance        | Ω                |

| $R_G$      | MOSFET polysilicon gate resistance | Ω                |

| ρ          | Sheet resistance                   | $\Omega$ /square |

| S          | Second                             | second           |

| S          | MOSFET subthreshold slope          | V/decade         |

| $t_{ox}$   | Oxide thickness                    | cm               |

| T          | Absolute temperature               | K                |

| V          | Voltage                            | V                |

| $V_{bs}$   | MOSFET substrate voltage           | V                |

| $V_{ds}$   | MOSFET drain voltage               | V                |

| $V_{dd}$   | Power supply voltage               | V                |

| $V_{dsat}$ | MOSFET drain saturation voltage    | V                |

| $V_{gs}$   | MOSFET gate voltage                | V                |

| $V_T$      | Threshold voltage                  | V                |

| W          | MOSFET width                       | cm               |

## **Abbreviation Description**

| APD  | Automatic power down                           |

|------|------------------------------------------------|

| ASIC | Application-specific integrated circuit        |

| ATD  | Address transition detector                    |

| CAD  | Computer-aided design                          |

| CERN | The European Organization for Nuclear Research |

| CMOS | Complementary metal-oxide-semiconductor        |

| COTS | Commercial-off-the-shelf                       |

| CPU  | Central processing unit                        |

| CSR  | Centre for Subatomic Research                  |

| DDWL | Dynamic divided word line                      |

| DEAC | Error detection and correction                 |

| DICE | The dual interlocked storage cell              |

| DRAM | Dynamic random access memory                   |

DUT Device under test

ELT Enclosed-gate layout transistor

EMP Electromagnetic pulse

FPGA Field programmable gate array

IC Integrated circuit

LET Linear energy transfer

LHC The large hadron collider

LOCOS Local oxidation of silicon

MBU Multiple bit upset

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field effect transistor

NMOS N-channel metal-oxide-semiconductor

PMOS P-channel metal-oxide-semiconductor

SCR Silicon-controlled rectifier

SEBO Single-event burn out

SEE Single-event effect

SEFI Single-event functional interrupt

SEL Single-event latch-up

SEU Single-event upset

SEGR Single-event gate rupture

SHE Single hard error

SOI Silicon on insulator

SOS Silicon on sapphire

SRAM Static random access memory

STI Shallow-trench isolation

TID Total ionizing dose effect

TSMC Taiwan semiconductor manufacturing company

VLSI Very large-scale integration

## Introduction

Almost forty years ago, the effects of radiation on semiconductor devices were observed when the first satellite experienced serious problems caused by the high energy particles present in the Van Allen belts. Since then, the space and military communities have made efforts to study these effects on semiconductors. Currently, the interest in studying the circuits which can work in a radiation environment is increasing, driven by all the possible applications of this kind of technology, such as space missions, satellites, advanced weaponry, instrumentation for nuclear power plants and high-energy physics experiments. With the evolution of very large-scale integration (VLSI) technologies, the minimum feature size of a transistor is becoming smaller and smaller; at the same time, scientists have become aware that the radiation effects caused mainly by neutrons can no longer be ignored in VLSI devices even at ground level. These radiation environments will be discussed in chapter one.

Custom-designed radiation tolerant and hard technologies<sup>1</sup> have been developed by space and military communities, which have been dealing with these issues for many years, providing foundry-oriented solutions. The disadvantages of these solutions are that they are expensive, difficult to access and normally several generations behind current commercial technologies.

The part of MOS (metal-oxide-semiconductor) transistors that is the most sensitive to ionizing radiation effects is the gate oxide, as will be seen in chapter two. The charges induced by ionizing radiation are trapped in the oxide, which prohibits the traditional thick-oxide commercial technologies from being used in radiation environments. One way to reduce the effects of ionizing radiation in the gate oxide is to reduce its thickness, which is fortunately a natural trend in modern technologies. The market of computer memories, microprocessors and, in general, digital integrated circuits has driven a very fast technological evolution in the past 20 years which has led to today's deep submicron

<sup>&</sup>lt;sup>1</sup> Radiation hard normally refers to a higher level of radiation hardness than radiation tolerant [CER].

technologies with less than 5 nm gate oxide thickness. The inherent radiation tolerance of the gate oxide of modern commercial CMOS (Complementary MOS) technologies suggests the possibility of using them in a radiation environment without introducing or modifying any particular process step. This will be seen in chapter 3. Radiation hardening a technology by introducing special processing steps is generally not a convenient way to proceed, since the foundries would not modify their processes for a small market without raising prices considerably.

There are some other possible problems besides the gate oxide when irradiating an integrated circuit made in a standard deep submicron technology. The scaling down of CMOS technologies also brings some detrimental effects. It is necessary to adapt the layout and the architecture of the circuits and of the system to solve these problems. A specially shaped transistor called enclosed-gate layout transistors (ELTs, also called enclosed-gate transistors) as well as guard rings are introduced, as will be seen in chapter 4.

The European Organization for Nuclear Research (CERN) started to investigate the possibility of using a commercial CMOS technology to integrate the circuits to be used in the detectors of high-energy physics experiments. They studied MOS devices fabricated using 0.7 μm, 0.5 μm, and 0.25 μm technologies. Some layout techniques were also studied to increase their radiation tolerance. The results were very promising, as has been reported in the RD49 project Status Reports [RD49a, RD49b]. The successful results allowed the design of integrated circuits, which could withstand total doses of 300 kGy(SiO<sub>2</sub>) and beyond [Cam99, Jar99, Sno00].

With CMOS technologies scaling down, 0.18 µm and 0.13 µm CMOS processes have become the main-stream technologies used in commercial products. The radiation hardness perspectives for design of analog detector readout circuits in the 0.18 µm CMOS technology have been investigated by some researchers [Man02]. It shows that the increase of the leakage component in the NMOS drain-source current may affect the behavior of devices used for logic or switching functions in radiation environments.

Some layout techniques (ELTs and guard rings) have to be used to cure it. However, the characteristics of enclosed-gate layout transistors in radiation environments have not been studied thoroughly yet, and this prohibits them from being used in radiation tolerant applications. For example, the use of these short channel transistors in analog sections requires knowledge of parameters such as transconductance and noise, which may differ considerably from the theoretical predictions valid for long-channel devices. The radiation tolerance of these analog parameters is also an important issue in electronic circuits for detectors in high-energy physics. A 0.18 µm CMOS technology is used in this thesis. This thesis reports the work done in the development of a radiation tolerant layout approach. A model to calculate the aspect ratio of enclosed-gate layout transistors is introduced and verified. The transistor parameters are extracted, before and after irradiation to study the radiation hardness of the technology. Some techniques used to prevent single-event upset in a SRAM are also evaluated using the technology. A digital library with enclosed-gate transistors has been developed and a SRAM test chip has been designed and fabricated with this library. Techniques to design radiation-hard SRAM cells are also introduced and evaluated. These approaches, which are used to make them radiation tolerant, have a general validity. For example, they could be used to radiation harden circuits for space, military and other radiation applications, besides high-energy physics experiments. A description of the contents of the thesis, chapter by chapter, follows:

- Chapter 1: This chapter introduces the different radiation environments, which have radiation effects on semiconductor devices. These include the space environment, the ground level environment, the nuclear reactors environment, the radiation processing environment, the weapons environment and high-energy physics experiments.

- Chapter 2: This is an introductory section describing the radiation effects on semiconductors. There are two major effects on MOSFETs, namely total ionizing dose effects (TID) and single-event effects (SEE). The physical origin of the MOS transistor parameters degradation induced by the total radiation dose is

discussed, together with the single-event effects. MOS devices are not sensitive to displacement damage, so no detailed information is given for this effect. This chapter is fundamental to understanding the rest of thesis.

- Chapter 3: The first part of this chapter introduces the scaling laws of CMOS technologies. Both beneficial and detrimental radiation effects of the technology scaling are presented.

- Chapter 4: Different levels of radiation-hardening techniques are discussed in this chapter. Traditionally, radiation hardening is achieved by using radiation-hard foundries, which are generally used for space and military purposes. However, radiation hardening can also be achieved by using design techniques. At the transistor level, there are enclosed-gate transistors and guard rings. At the circuit and system levels, there are also various design techniques, which are introduced in this chapter.

- Chapter 5: ELTs are devices with an enclosed-gate geometry, with the drain and source contacts inside and outside, separated by a gate ring. They are used to prevent post-irradiation leakage currents between drain and source inside the NMOS transistors. In this chapter the work done on the modeling of these non-standard geometry devices is described.

- Chapter 6: Total dose effects on ELTs are thoroughly studied. The radiation hardness of MOSFETs in the technology with gate oxide thickness of 4.3 nm and with an enclosed gate and guard ring layout has been evaluated based on its electrical characteristics. Some important parameters have been measured or extracted in this chapter.

- Chapter 7: Noise is an important parameter in analog CMOS circuits. Radiation may affect the noise behavior of the devices. It is mandatory to evaluate the noise

performance of standard and ELT transistors before and after radiation in order to use them in analog circuits.

- Chapter 8: A digital library is developed with ELTs and guard rings. A configurable SRAM architecture is introduced aimed at radiation-hard ASIC designs. Some low-power techniques have been adopted. A 1k × 9bit SRAM test chip has been designed and fabricated with the technology.

- Chapter 9: Single-event upset in memories is studied in this chapter. Several approaches to radiation hardened SRAM cells are introduced and evaluated using the technology.

- Conclusions: This final chapter lays out the conclusions that can be drawn from this work. The main results and their significance are discussed, together with their possible applications in radiation environments.

## **Chapter 1 Introduction to Radiation Environments**

In this section, a brief overview of the various environments likely to have a degrading effect on electronic devices and systems is presented. It includes space, ground level, nuclear reactors, radiation processing, weapons and high-energy physics experiments.

#### 1.1 The space environment

The space radiation environment is composed of a variety of energetic particles with energies ranging from keV to GeV and beyond. These particles are either trapped by the Earth's magnetic field or are passing through the solar system. The main elements of the radiation environment are: the radiation belts, cosmic rays, and solar flares.

- The radiation belts. This consists of many different types of energetic charged particles trapped in the Earth's magnetic field, forming the radiation belts. It consists mainly of electrons of energy up to a few MeV and protons up to several hundred MeV.

- Cosmic rays. These are low fluxes of energetic heavy ions extending to energies beyond TeV and including all ions in the periodic table. There are three sources of cosmic rays: galactic, solar and terrestrial. Galactic cosmic rays are 'primary' cosmic rays which originate outside the solar system but are associated with the galaxy and provide a continuous low-flux component of the radiation environment. They are comprised of about 85 per cent protons, 14 per cent alpha particles and 1 per cent heavier nuclei with energies extending to 1 GeV. Solar cosmic rays not only produce an intensive burst of both UV and X-rays, but also accelerate solar material to high velocities. These solar particles are similar to galactic cosmic rays but, due to their different origin, are not identical in composition. The primary cosmic radiation which penetrates the Earth's atmosphere is rapidly transformed by interactions which produce a cascade of secondary radiation. These cascades take place in the main body

of the atmosphere and the secondary particles produced are the principal components of cosmic radiation at the Earth's surface, which are called terrestrial cosmic rays.

Solar flares. Protons from solar flare, together with electrons and alpha particles in smaller quantities, are emitted by the sun in bursts during solar storms. Their fluxes, besides being intermittent, vary overall with the solar cycle.

In addition, space is pervaded by a plasma of electrons and protons with energies up to about 100 keV. Within the trapped radiation belts, these particles merely represent the low-energy extremes of the trapped electron and proton populations. In the outer zones of the magnetosphere and in interplanetary space, these particles are associated with the solar wind, and considerable fluxes will be encountered at very high altitudes. The low-energy particles are easily stopped by very thin layers of material and hence only the outer-most surfaces such as thermal control material and solar cell cover slips are affected. The low-energy plasma can cause spacecraft charging and the internal electronics may be affected by this charging and subsequent discharging.

The electronics in space experiences two types of radiation effects: one is caused by the accumulation of ionization over a period of time, which eventually leads to performance degradation and/or functional failure. The other one is due to a single high-energy particle as it strikes the sensitive nodes (or sensitive volumes) within the electronic device. It is primarily the results of currents generated as an energetic particle passes through circuit elements (the radiation effects on electronics are fully explained in next chapter). This type of effect is the main problem that needs to be addressed by the space community. There are two approaches for choosing the electronics in radiation environments: the first one uses qualified radiation-hard electronics; the second one uses commercial electronics, the so-called radiation tolerant electronics, which has to be evaluated by the customer.

In conclusion, the space environment has a very wide range of radiation levels depending on the type of space missions. The electronics in each mission will endure different doses of radiation introduced by various fluxes of particles.

#### 1.2 The ground level

The radiation effects on VLSI at ground level were first reported by T. May and M. Woods [May78], in discovering errors in RAM chips due to upsets caused by the alpha particles released by the contaminants within the chip packaging material. Chip vendors managed to find some specific solutions to reduce them to tolerable levels, mainly by reducing the alpha particle flux emitted by packaging and processing materials [Has92].

On the other hand, cosmic rays also exit on the ground, even if their intensity and energy are reduced compared to those of in the space. The secondary particles produced by cosmic rays are primarily neutrons. The others include protons and pions. The atmospheric neutrons are believed to be the major cause of the upsets occurring in VLSI [Eng96, Zie96]. The neutron environment at ground level can be defined in terms of the models for the atmospheric neutron flux at higher altitudes which are mainly based on neutrons in the energy range of greater than 1 MeV and less than 10 MeV. It is shown by a number of studies that the shape of the energy spectrum of the atmospheric neutron flux does not change with altitude or latitude, even through its absolute magnitude does vary with location and altitude around the Earth. Some data [Nor93] shows that 10-100 MeV flux of neutrons falls off approximately linearly with altitude. Very few measurements of the neutron spectrum at ground level have been made. However, one set of most recent terrestrial spectral measurements [Nak87, Hew78] shows that the ground spectrum is roughly 1/300 of that at 40,000 ft. An upset rate in the range of 1-2×10<sup>-12</sup> upset/bit-hour was shown to be representative of the rate that most SRAMs and DRAMs in actual field applications are experiencing [Eng96]. The impact due to the upsets caused by the neutrons, include: improving the reliability of large computer system; applying error mitigation techniques to RAMs used in biomedical, commercial, and industrial products, etc.

#### 1.3 The nuclear reactor environment

Three levels of radiation severity need to be considered for nuclear fission power plants: within the reactor core and cavity, in the containment, in the containment under accident conditions.

The major radiation sources in the reactor environment are neutrons and gamma rays (Kak86). The most important environment for equipment and components is 'in containment' and, while the gamma dose rate and neutron flux are moderate, the requirement for 40 years operating life results in significant accumulated levels. Safety equipment is required to operate at the end of a specified lifetime. Such equipment must also operate during and after a radioactive accident. Other stress factors must be taken into account in conjunction with radiation effects in order to arrive at a true estimate of the life expectancy and to define adequate qualification tests.

## 1.4 The radiation processing environment

Radiation processing is a branch of radiation technology, which involves the deliberate introduction of radiation damage into materials for beneficial purposes. The aspect of radiation processing which has caught the attention of the public in recent years concerns the irradiation of food products in order to eradicate harmful organisms and extend shelf-time. This is a small part of what is now becoming a major application in industry. Examples include the following:

- Modern consumer-oriented society generates a large amount of waste, and radiation processing is a potential solution for many of the problems involved in waste treatment and the cleansing of water supplies.

- Radiation processing is used in the medical field for the sterilization of a number of products such as dressings, hypodermic needles, and catheters.

- Industrial applications are increasing, particularly in the field of materials modification. The polymer industry uses radiation for the cross-linking of polymers to produce durable insulation for wires and cables particularly for submarine use. Current investigations center around polymer grafting, with particular reference to the controlled delivery of drugs.

- The semiconductor industry is beginning to use radiation processing for the modification of starting materials, particularly silicon.

- Many developing nations benefit from radiation processing. The economy of such nations frequently depends on a single perishable crop. Radiation processing is used to delay ripening and extend the period during which the scopes may be brought to the market-place.

A wide range of radiation sources is used in the processing industry, such as gamma sources, electron accelerators, etc. For further reading, see the bi-annual proceedings of the International Radiation Processing Symposium (RPC 1990).

#### 1.5 The weapons environment

A nuclear weapon based on fission is constructed with a configuration of fissionable material slightly below the critical point. A nuclear detonation is triggered when the configuration is made supercritical. This may be achieved either by driving two pieces of subcritical material together or by imploding a spherical shell of material.

The energy associated with a nuclear weapon requires a special classification scheme. Nuclear yields are expressed in equivalent kilotons (kt) or megatons (Mt) of TNT explosive. 1 kt TNT generates 10<sup>12</sup> cal, which should be compared with the requirement of only 56 g of U-235 to release the same amount of energy. In less than 1 µs the detonation energy of a weapon has escaped into an air mass many hundreds of times larger than the mass of the device itself.

The energy from the weapon is transferred by four mechanisms: thermal (fire ball), blast, nuclear radiation, and electromagnetic pulse (EMP).

The thermal and blast components are independent of the weapon construction; the radiation and the EMP component are determined by the weapon construction and materials and are independent of the external environment. The energy partition of a typical weapon detonated in the atmosphere is:

Blast/shock 50 per cent

Thermal radiation 35 per cent

Delayed nuclear radiation 10 per cent

Prompt nuclear radiation 5 per cent

The time division between prompt and delayed radiation is taken as 1 minute.

The radiation consists of neutrons, X-rays, gamma rays, alpha particles, electrons and secondary particles. Some 90 percent of the neutrons generated by the fission-fusion reactions are absorbed within the bomb case. Neutron fluence is roughly proportional to yield.

The gamma rays originate from two principal sources:

- Prompt gammas generated in the first few milliseconds which come from a nucleus excited by capturing a neutron and then falling back to ground state;

- Delayed gammas generated by the decay of radioactive fission fragments.

The gamma spectrum extends to 12 MeV with most of the fluence in the range up to 0.75 MeV. As with neutrons, the gammas undergo geometrical attenuation as well as exponential attenuation in materials. The gamma dose can be enhanced by the lowered density of the air during the blast.

## 1.6 High-energy physics accelerators

Current high-energy physics research is carried out with beams of electrons or protons having very high energies, often operated so that the two beams collide and produce short-lived particles of interest in determining subatomic structure. For example, the Large Hadron Collider (LHC) under construction at CERN in Geneva is a circular accelerator and consists of two adjacent 26.7 km rings in which two proton beams run in opposite directions. The proton beams will collide in four points along the circumference at a centre of mass energy of 14 TeV. Many magnets and RF power sources are used to guide and accelerate the beam, and the target areas are surrounded by very large arrays of radiation detectors of the most advanced type, including high-speed, ultra-sensitive electronic detection circuitry.

At high luminosity the proton-proton collisions at the LHC will produce an extremely hostile radiation environment. Many simulations have been performed in order to obtain realistic expectations. The total dose contribution is mainly due to the primary flux of particles coming from the interaction region. The secondary radiation that escapes from the accelerator tube consists mainly of photons and neutrons of high energy. The dose rates are of the order of  $10^5$  Gy(SiO<sub>2</sub>) per year. The consequences for some parts and materials to withstand  $10^6$  Gy(SiO<sub>2</sub>) opens up a new range of requirements generally higher than those needed in space radiation or the military environments.

## **Chapter 2** Introduction to Radiation Effects on MOS Devices and ICs

The interaction of radiation with matter is a very broad and complex topic. In this chapter, the basic mechanisms of radiation effects on MOS devices are described, with the aim of explaining the important aspects which are essential for a physical comprehension of the degradation observed in MOS devices and circuits when they are irradiated. In section 2.1, the interaction between particles and matter in radiation environment is explained. Total dose effects in the MOSFET materials are listed in section 2.2 and the consequence degradation of electrical parameters are presented in section 2.3. The single-event effects are described in section 2.4.

## 2.1 Interactions between radiation particles and matter

Particles can be divided into two groups for simplicity: charged particles and neutral particles. The principal characteristic of charged particles is that they interact mainly through Coulomb interactions with the electronic clouds of the target atoms. The charged particles of interest are protons, heavy ions and electrons. The uncharged particles are mainly neutrons and photons.

Protons give origin to the following phenomena:

- Coulomb interaction, which can induce ionization or atomic excitation (the latter for protons energy less than 100 keV);

- Collisions with the nuclei, which can cause their excitation or displacement;

- Nuclear reaction, which can occur for protons energies higher than about 10 MeV.

Heavy ions give origin, qualitatively, to phenomena similar to those induced by protons.

Electrons, which can be present in the radiation environment or be produced by interaction of other particles with the material, can interact in two different manners, namely:

- Coulomb interaction, which can induce, as in the case of protons, ionization or atomic excitation;

- Scattering with the nuclei, which can cause their displacement if the energy of the incoming electron is high enough and if enough energy is transferred to the nucleus.

Neutrons and photons differ from the charged particles because they do not experience the Coulomb force. According to their energy level, neutrons are divided into slow (energy less than 1 eV), intermediate and fast (energy greater than 100 keV), and give origin to three different phenomena of interaction with the atomic nuclei:

- Nuclear reactions: the incident neutron is absorbed by the nucleus, which afterwards emits other particles (protons, alpha particles, gamma rays). It is possible that nuclear fission can occur;

- Elastic collisions: the incident neutron collides with the nucleus and continues its

path. If the energy given to the nucleus is sufficient, displacement of the nucleus can

occur and the displaced nucleus can in turn cause ionization or nuclear displacement;

- Inelastic collisions: the phenomenon is similar to the previous one, but in addition there is excitation of the nucleus, which afterwards decays, emitting gamma rays. The relative probability of these phenomena depends strongly on the neutron energy.

Slow neutrons give origin mainly to nuclear reactions or elastic collisions and fast neutrons mainly to elastic collisions. For very high energies the inelastic collisions dominate.

Photons interact with matter in the three different ways described below:

- Photoelectric effect, in which the incident photon ionizes the target atom and is completely absorbed. In addition, as the photoelectric electron is emitted, an electron in an outer orbit of the atom will fall into the spot vacated by the photoelectron, causing a low energy photoelectric photon to be emitted;

- Compton effect, in which an electron of the target atom is set free and a photon is emitted. The energy of the incident photon is divided between the two products of the interaction;

Creation of electron-positron pairs. The incident photon is completely annihilated.

This phenomenon never happens for energies of the incident photon less than 1.024 MeV. This value increases with decreasing atomic mass.

The probability of these three effects changes with the energy and also strongly depends on the atomic number of the target. The photons used in the radiation test of this work were X-rays with maximum energy of 320 keV.

The radiation effects of both charged and neutral particles on matter, can be grouped into two classes: ionization effects and nuclear displacement. These phenomena may be caused directly by the incident particle or from secondary particles produced by it, and represent the overwhelming majority of the events which happen in the irradiated matter. Neutrons mainly cause nuclear displacement, whereas photons and electrons are responsible for ionization effects.

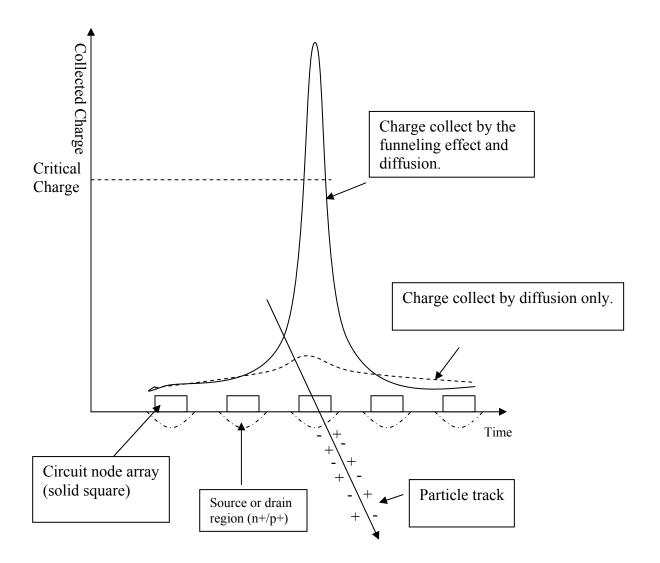

Ionizing radiation may be defined as charged particles that possess enough energy to break atomic bonds in the absorbing material, thus creating electron-hole pairs. The number of pairs created is proportional to the energy deposited in the material, which is the total absorbed dose. These charged particles may include protons, electrons and atomic ions with energies greater than the material band gap. Ionizing radiation can cause two primary effects in microelectronics: total ionizing dose effects (TID) and single-event effects (SEE). Total ionizing dose effects are caused by the accumulation of ionization over a period of time, which eventually leads to performance degradation and/or functional failure in microelectronics. Single-event effects refer to ionizing effects due to a single high-energy particle as it strikes the sensitive nodes (or sensitive volume) within the electronic device. It is primarily the result of currents generated as an energetic particle passes through circuit elements.

Atomic displacement causes a neighboring interstitial atom and vacancy, which are called a Frenkel pair. In silicon dioxide at room temperature, 90 per cent of the pairs recombine within a minute after the end of irradiation. A main effect of the atomic displacement is the reduction of the lifetime of the minority carriers in the bulk. CMOS transistors are almost entirely insensitive to displacement damage, because their conduction is based on the flow of majority carriers below the SiO<sub>2</sub>-Si interface, a region that does not extend deep into the silicon bulk. To study displacement damage, neutrons sources are generally used.

#### 2.2 Total dose effects

In this section, two sources that cause total ionizing dose effects are introduced: charge trapping in the silicon dioxide and at the Si-SiO<sub>2</sub> interface.

## 2.2.1 Charge trapping in silicon dioxide

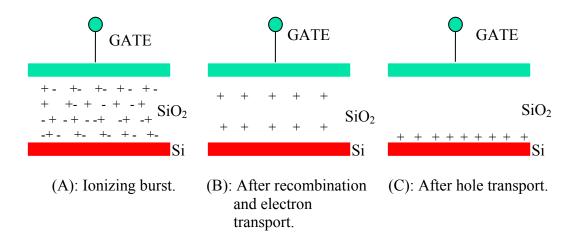

MOS transistors are sensitive to ionization. The silicon dioxide is the sensitive part to the ionizing radiation as it traps charge induced by irradiation, which is shown in Figure 2.1. As ionizing particles pass through a MOS device, electron/hole pairs are generated (shown in Figure 2.1A). In the gate and the substrate the pairs quickly drift away because of the low resistance. On the other hand, electrons and holes have different behaviors in the oxide, which is an insulator. A fraction of the electron-hole pairs recombine immediately after being created. Mobile electrons move quickly through the oxide, but holes have a very low effective mobility in the oxides and are trapped in the gate oxide and field oxide (shown in Figure 2.1B). If the gate has a positive voltage, the holes move towards the SiO<sub>2</sub>-Si interface. Close to the interface, but still in the oxide, some of the holes may be trapped, building a fixed positive charge in the oxide (shown in Figure 2.1C).

Figure 2.1: Illustration of charge trapping in the gate oxide of a NMOS transistor.

When the radiation-induced holes have crossed of the oxide, they can be trapped close to the  $SiO_2$ -Si interface. This phenomenon generally dominates over other radiation-induced phenomena, such as for example the trapping of electrons in silicon dioxide. As will be seen later, the trapping of holes in the oxide gives origin to a negative threshold voltage shift  $\Delta V_{ox}$  which is not sensitive to the surface potential in the silicon and which can stay for a period of time varying from milliseconds to years. The amount of trapped charge is proportional to the number of defects in the silicon dioxide. For this reason one of the important steps for the fabrication of radiation-hardened technologies is to improve and control the gate oxide quality.

These trapped holes give rise to a threshold voltage shift,  $\Delta V_{ox}$ , given by:

$$\Delta V_{ox} = -\frac{1}{C_{ox}} \int_{0}^{t_{ox}} \frac{x}{t_{ox}} \rho(x) dx = -\left(\frac{q}{\varepsilon_{ox}}\right) t_{ox} \Delta N_{ot}, \qquad (2.1)$$

where q is the electron charge,  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is the oxide capacitance,  $\varepsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub> and  $t_{ox}$  is the thickness of the oxide,  $\rho(x)$  is the spatial distribution of the oxide charge density, and  $\Delta N_{ot}$  is the trapped charge density referred to the SiO<sub>2</sub>-Si interface.

Trapped holes can be removed (or neutralized by compensating electron trapping) either by thermal annealing or by tunneling of electrons from the silicon substrate (or gate). Complete thermal annealing often requires temperatures of up to 300°C or so [Dre98]. The distribution of energies inside the SiO<sub>2</sub> band gap for the trapped holes is quite similar for thermally grown oxides fabricated by a wide variety of process (dry, wet, soft, hard, etc.). The shallower the trap level, the lower the temperature required to annihilate the trap (lower thermal activation energy).

Tunnel annealing can be used to explain the roughly linear with logarithmic time dependence often observed for the removal of trapped holes at moderate temperatures. This type of annealing can only affect those holes trapped within approximately 4-5 nm of the substrate or gate electrode, because of the rapid decrease in tunneling probability with distance. However, this also means that significant neutralization of the trapped holes could occur via tunnel annealing in a relatively short time interval, for thin oxide (less than 10 nm).

# 2.2.2 Charge trapping at the SiO<sub>2</sub>-Si interface

Another effect of radiation on CMOS devices is the increase by several orders of magnitude of the trapped hole density at the  $SiO_2$ -Si interface. This phenomenon has been studied for many years and several models have been introduced. Experiments indicate that both for NMOS and PMOS transistors the threshold voltage increases ( $\Delta V_{it}$ , in absolute value) after irradiation due to the creation of new interface traps. It is strongly dependent on the processing steps of MOS devices, and there is generally not significant annealing of the generated traps at room temperature.

### 2.3 Radiation effects on the electrical parameters of a MOS transistor

In this section, the consequence degradation of electrical parameters caused by radiation effects is discussed. To be specific, these parameters are threshold voltage, subthreshold slope, leakage current, mobility, transconductance and noise.

## 2.3.1 Threshold voltage shift

The threshold voltage of a MOS transistor changes when the device is irradiated. This change has two contributions,  $\Delta V_{ox}$  and  $\Delta V_{it}$ .

In a NMOS transistor, the trapped positive charge causes negative shifts of the threshold voltages. This is shown in Equation 2.1. This can easily be understood qualitatively: for an NMOS transistor, for example, the positive charge trapped in the oxide repels the holes in the channel. This means that to re-create the same inversion condition one will need to apply a less positive potential to the gate, i.e. the threshold voltage is higher. For a PMOS transistor, it is opposite to this.

The increasing trapped charge at the interface is a relatively slower phenomenon than the build-up of positive charge in the oxide. For this reason,  $V_{it}$  can change later than  $V_{ox}$ . This can also explain why the threshold voltage shift for NMOS transistors as a function of the total dose or the annealing time can be negative at the beginning and become positive at a later time (this effect is known as rebound). The slower temporal evolution of the radiation-induced interface states also plays an important role in the annealing of the irradiated circuits, since this will decrease  $V_{ox}$  but will probably increase  $V_{it}$  both for NMOS and for PMOS transistors, affecting in this way the bias conditions of the circuit.

The measured threshold voltage shift  $\Delta V_T$  is the sum of the two previously described contributions  $\Delta V_{ox}$  and  $\Delta V_{it}$ . To understand the behavior of both the trapped oxide charge and the interface traps it is interesting to separate the measured threshold voltage shift for the two contributions. There are several ways of doing this [Doy93, Var91, Gro84, Bru69]. Our preference, also due to its simplicity, is the method described by McWorther and Winokur [Mcw86], based on the variation of subthreshold slope before and after irradiation.

The  $\Delta V_{it}$  can be calculated from the subthreshold slope measurement [Mcw86],

$$\Delta V_{it} = \frac{\Delta Q_{it}}{C_{ox}} = \frac{q\Delta D_{it}\phi_B}{C_{ox}} = \Delta S \cdot \frac{q\phi_B}{\ln(10)k_B T} , \qquad (2.2)$$

where  $\Delta D_{it}$  is the variation of the interface state density, expressed in V<sup>-1</sup>cm<sup>-2</sup>. S and  $\phi_B$  can calculated by the following Equations,

$$S = \ln(10) \frac{K_B T}{q} \left( 1 + \frac{C_d + C_{it}}{C_{ox}} \right), \tag{2.3}$$

$$\phi_B = \frac{\left(E_i - E_F\right)}{q} = \frac{K_B T}{q} \cdot \ln\left(\frac{N_D}{n_i}\right). \tag{2.4}$$

S is subthreshold swing, which is determined by the unit area capacitance of the oxide capacitance ( $C_{ox}$ ), interface trap capacitance ( $C_{it}$ ) and depletion-layer capacitance ( $C_d$ ). The typical value of S is 70-100 mV/decade. From the Equation 2.3, it is shown that S is rather insensitive to device parameters, except for a slight dependence on bulk doping concentration through  $C_d$  and  $C_{it}$ .  $\Delta S$  is the variation of the subthreshold swing.  $\phi_B$  is the bulk potential.  $N_D$  is the doping concentration and  $n_i$  is the silicon intrinsic carrier concentration, that is equal to  $1.45 \times 10^{10}$  cm<sup>-3</sup> at  $300^{\circ}$ K.

Measuring  $\Delta S$  and  $\Delta V_T$  one is then able to calculate the threshold voltage shift given by the interface trapped charges  $\Delta V_{it}$ , and also  $\Delta V_{ox}$ . This is very useful when one wants to have information on the quality of the oxide and of the oxide-silicon interface, and also if one wants to study the annealing of the holes trapped in the oxide and of the interface states.

### 2.3.2 Change of leakage current: subthreshold and parasitic currents

The "off-state" current in a NMOS transistor is defined as the current which flows from drain to source when  $V_{gs}=0$ , and is also called "leakage current". Leakage current changes as subthreshold and parasitic currents change when an MOS transistor is irradiated.

The change in the subthreshold current is from two components. The first one is the change of the threshold voltage. The second is the radiation-induced decrease of the subthreshold slope. For NMOS transistors, its leakage current increases if the threshold voltage shift is negative.

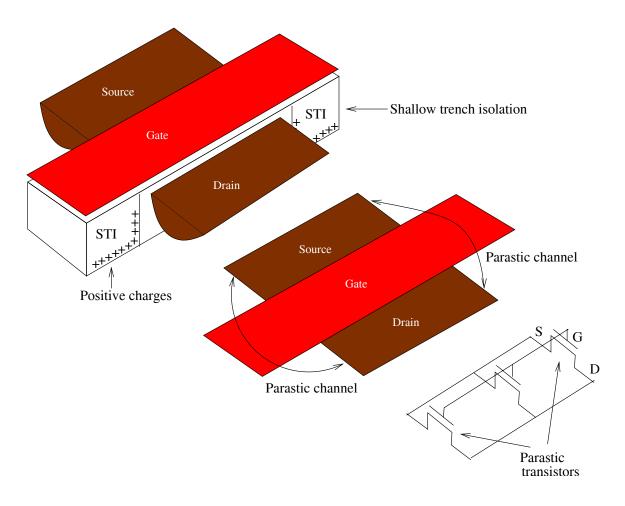

In addition to the transistors drawn in Figure 2.2, parasitic CMOS transistors also occur during irradiation. In the past, local oxidation of silicon (LOCOS) has often been adopted for transistor isolation. Two parasitic paths are generated under the region called "bird's beak" or further way from the device, underneath the thick field oxide. In recent years, many commercial CMOS IC suppliers have replaced their LOCOS isolation with shallow-trench isolation (STI) for advanced submicron technologies to remove the lateral encroachment (no LOCOS bird's beak). However, the two parasitic paths still exist for STI, as illustrated in Figure 2.2. These parasitic elements cause leakage currents to flow around the edges of the drawn NMOS gate regions, from drain to source, between drain/source regions of adjacent NMOS transistors, and from n-channel drain/source regions to the n-well/n-substrate. This contribution to the total leakage current dominated over that one due to the subthreshold current in the deep submicron CMOS technologies [Ane99a, Sha98]. In chapter 6, the experiments done in this thesis also demonstrate this. The shift of subthreshold currents caused by irradiation is very limited, due to the very small value of  $\Delta V_{\rm T}$ .

Figure 2.2: Illustration of the parasitic transistors that are in parallel to the main transistor and of the parasitic leakage paths in the shallow-trench isolation region or underneath the field oxide which connects the source and the drain.

# 2.3.3 Decrease of mobility and transconductance