# An IPMI-compliant control system for the ATLAS TileCal Phase-II Upgrade PreProcessor module

P. Zuccarello, F. Carrió Argos, A. Valero Biot, on behalf of the ATLAS Tile Calorimeter System Instituto de Física Corpuscular (Universitat de Valéncia- CSIC, Valencia, Spain)

52

1

Abstract-The electronics of the hadronic calorimeter of th<sup>44</sup>

2

ATLAS detector (TileCal) is being redesigned as part of the work<sup>45</sup>

3

that will lead to the High Luminosity Large Hadron Collider (HL<sub>46</sub>

4

LHC).

47

5 TileCal electronics is divided in front and back-end sub-6 systems. While the front-end will be inside the detector, the back-7 end is planned to be off-detector inserted in an ATCA shelf. The 8 main objective of this paper is to describe the work being carried 9 out in the hardware management aspects of the back-eng-10 electronics of TileCal. 51

#### I. INTRODUCTION

12 TileCal is the central hadronic calorimeter of the ATLAS 13 experiment at the Large Hadronic Collider (LHC) [1]. The LHC upgrade program, currently under development, will culminate 14 15 in the High Luminosity LHC (HL-LHC), which is expected to 16 operate at about five times the LHC nominal instantaneous 17 luminosity. Under this scenario, the readout electronics of the Tile calorimeter is being redesigned introducing a new read-out 18 19 strategy in order to cope with the new HL-LHC parameters 20 [2,3].

The data generated inside the detector at every bunch crossing will be transmitted to the PreProcessor (PPR) boards [4] before any event selection is applied. The PPRs, planned to be located off-detector, will provide preprocessed trigger information to the ATLAS first level trigger (L1) [5].

The PPR is the main interface between the Trigger and Data Acquisition System (TDAQ) and Detector Control System (DCS) and the on-detector electronics, it needs to be remotely controlled and monitored to prevent failures or, in case some<sub>3</sub> failure occurs, to accurately diagnose the problem. With this4 purpose in mind, the PPR is included in an Advanced Telecommunications Computing Architecture (ATCA) [6]5 shelf that, not only provides high-speed communicationa capabilities, but also includes an out-of-band contro57 architecture compliant with the Intelligent Platforma Management Interface (IPMI) [7] specification. 59

This document describes the hardware management features

being implemented for the back-end electronics Phase-161

upgrade of the Tile calorimeter.

In Section II the main features of the TileCal upgrade<sup>63</sup>

electronic architecture are described, in Section III the ATC<sup>64</sup>

shelves and some of the hardware management aspects ar<sup>65</sup>

introduced; the main characteristics of the PPR are als<sup>66</sup>

Manuscript received November 30, 2016. This work was supported project FPA2015-65652-C4-2-R from the Ministry of Economy and Competitiveness of the Spanish Government and ERDF funds.

explained. Section IV describes the IPMI system software being designed at the Instituto de Física Corpuscular (IFIC). In Section V the conclusions are presented.

#### II. TILECAL PHASE-II UPGRADE

TileCal is a steel-scintillator calorimeter essential for the triggering and reconstruction of hadrons produced in the LHC collisions inside the ATLAS detector.

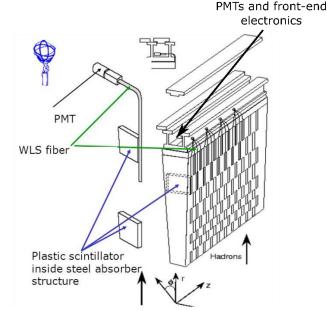

Fig. 1 Principle of a TileCal module.

TileCal is divided into 4 barrels, which are then divided into 64 modules each. A diagram of one of the modules can be seen in Fig.1 where its components are described. Every 25ns LHC particle bunches collide inside ATLAS. When the particles from the collisions hit the scintillator material, light is produced. This light signal is collected by Wave-Length Shifting (WLS) optical fibers and amplified by a photomultiplier (PMT). The PMTs deliver to the front-end electronics an analog electronic signal that is conditioned, digitized, properly formatted and transmitted off-detector to the back-end electronic system. A schematic view of the readout electronics is depicted in Fig.2.

11

67

68 Fig. 2 Functional scheme of the TileCal Phase-II readout, where TTC is Timing

69 and Trigger Control and GBT stands for GigaBit Transceiver.

In the back-end, the PPR provides preprocessed information

to L1 trigger and stores the digital samples in pipelined

memories. If a certain event is selected by the trigger system,

its samples are processed and transmitted to the ATLAS global

data acquisition (DAQ) system.

75

# 76 III. HARDWARE MANAGEMENT IN ATCA SHELVES AND TILECAL 77 BACK-END ELECTRONICS

The core of the back-end electronics for the Phase-II Upgrade9

are the PPR boards. This device has been designed to operate0

within an ATCA shelf.

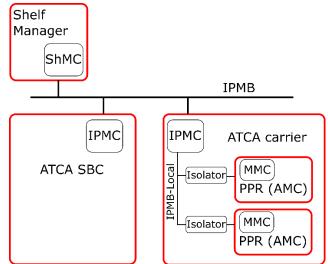

# 81 A. ATCA shelf and PICMG set of specifications 122

The ATCA is defined by a set of PCI Industrial Computer, 82 83 Manufacturers Group (PICMG) specifications, denoted PICMG 3.x [6,8], that propose an open multi-vendor<sup>124</sup> 84 architecture targeted to fulfill the requirements for carrier grade 85 26 high-performance communications equipments. 86 Besides the high-performance communications links, the<sup>1</sup> 87 PICMG 3.x specifications include extensive in-band and  $out^{28}$ 88 band hardware control and management capabilities. Out-of-89 90 band management guarantees the access to the hardware even when the operative system (OS) is powered off or unresponsive. 13191 This is achieved by setting up a direct network connection  $13^2$ 92 the hardware rather than to the OS. This aspect of the  $ATCA^{3}$ 93 134 94 specification is mainly based on the IPMI specification [7]. An ATCA crate is a shelf structure that includes several  $^{135}$ 95 ATCA-compliant boards with different communications and 96 computing functionalities that are interconnected via the same 13797 hardware platform management bus. In the IPMI environment, 98 this is an I2C bus called Intelligent Platform Management Bus 99 40 100 (IPMB). Fig.3 shows the structure of the ATCA being used at  $CER_{N}^{141}$ 101

101 Fig.5 shows the structure of the ATCA being used at CERN 102 and IFIC laboratories to test and develop the TileCal 103 hardware/firmware back-end electronic system. 143

The Shelf Manager assures proper operation of the shelf  $b_{y_{\perp}}^{44}$ 104 managing its power, cooling, interconnects, responding to event 105 messages and performing monitor and control tasks over the 106 other boards in the crate. The Single Board Computer (SBC) 15 107 a general purpose computer board, while the ATCA carrier  $^{148}$ 108 controls and gives connectivity services to a set of Advanced 109 Mezzanine Cards (AMC) [8] inserted in it. Intelligent Platform  $^{150}$ 110 Management Controllers (IPMCs) are intelligent devices. 111 usually implemented in small microcontrollers, embedded  $\frac{152}{10}$ 112 153 ATCA boards with hardware management features. 113 The Shelf Manager Controller (ShMC) and the Module<sup>4</sup> 114 hardware<sup>155</sup> 115 Management Controller (MMC) are also

116 management controller devices. While all share some basic<sup>156</sup></sup>

functionality, they have different levels of responsibility within the IPMI infrastructure.

Fig. 3 Illustration of the ATCA shelf infrastructure.

The PPR prototype was designed in an AMC-compliant format.

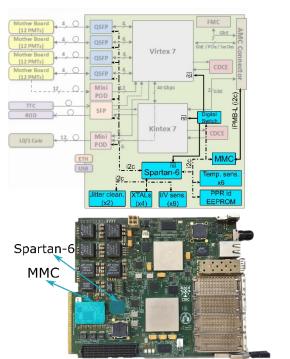

#### B. PPR prototype board

The PPR prototype board, shown in Fig.4, is a custom design module which includes one Virtex7 and one Kintex7 FPGAs for data processing.

With a bidirectional bandwidth of 280 Gbps is able to process one TileCal front-end drawer equipped with up to 48 PMTs. It includes 4 QSFP connectors, which provide full duplex communication with the front-end electronics. The 16 input optical links, running at 9.6 Gbps, are used to receive the PMTs data as well as to monitor information from the on-detector electronics. The 16 output optical links running at 4.8 Gbps are used to transmit the clock and configuration and control commands to the front-end electronics.

The PPR design includes a series of sensors that allow monitoring its status continuously. Table I shows a list of sensors and the number of bytes needed to read their state records.

The hardware management devices and links of the PPR are highlighted in Fig.4. A small board with an ATMega128 microcontroller fulfills the functionalities of IPMI-MMC. The temperature sensors, the EEPROM that holds the PPR id number, a GPIO chip -accessible via I2C protocol and labelled as Digital Switch in Fig.4- used to activate the reset signals of the three FPGAs and the Spartan-6 FPGA are directly connected to one of the I2C buses of the MMC. QSFP, MiniPOD and SFP connectors, the jitter cleaners, the I/V sensors and the XTALs configuration are connected to one of the I2C buses of the Spartan-6, therefore, when the MMC needs to communicate with these devices, the messages have to be bridged through the Spartan-6 FPGA.

Through the MMC, via the IPMB, the status of the different sensors can be retrieved and configuration commands to different devices in the PPR can be issued. A list of control/configuration devices is included in Table I. 157

#### 191 158 IV. SYSTEM SOFTWARE FOR HARDWARE MANAGEMENT 192

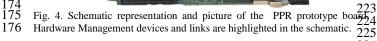

An IPMI system software was designed at IFIC. The main<sup>3</sup> 159 194 160 goals of this software are:

- To visualize, in real time, the state of the ATCA crate<sup>5</sup> 161 196 boards, sensors and alarms. 162

- To send commands, via the IPMI hardware? 163 management links, to the PPRs inserted in the crate.<sup>198</sup> 164

- 165 To keep historical records of the performance (power consumption, communications links status and failure, 166 167 temperature, etc.) of the different boards, in particular 168 of the PPR.

169 The software relies on OpenIPMI and IpmiTool libraries for

- the IPMI connectivity features and on MySQL database for 170

- 171 recording all collected data. The graphical user interface (see 199 200

- 172 Fig.5) is based on Qt-C++ libraries. 173

- the ATCA carrier to the IPMB-Local (see Fig.3 and [8]). 179

- 180

# 181

182

# V. CONCLUSIONS

183 The electronic systems of the hadronic calorimeter of the ATLAS detector, TileCal, is being redesigned for the operation  $\frac{1}{38}$ 184 185 at the HL-LHC. The core component of the back-endo 186 electronics, the PPR, has been designed to operate inside 240 ATCA shelf. One of the main features of ATCA crates is  $t_{H_{2}}^{41}$ 187 IPMI-compliant hardware management infrastructure. In the 153188 189 work, the IPMI hardware management features of the back-ead4

electronics developed for the TileCal Phase-II Upgrade have been described. Under this project, a custom MMC board (hardware and firmware) has been designed and implemented at CERN so that it operates embedded in the PPR. A system software that gathers all the information of the ATCA shelf (sensors, boards and blades presence and status, alarms and events) specifically oriented to communicate, configure and read the status of the PPR has been designed at IFIC.

|         | - Michiele eitr | 144 | N-SO #1       |        | er.         |                |                   |                 |          |         |                       |           |                         |           |                  |                                             |

|---------|-----------------|-----|---------------|--------|-------------|----------------|-------------------|-----------------|----------|---------|-----------------------|-----------|-------------------------|-----------|------------------|---------------------------------------------|

| APARTAL |                 |     | andore        |        |             |                |                   |                 |          |         |                       |           |                         |           |                  |                                             |

|         |                 |     |               |        |             |                | _                 |                 |          |         |                       |           |                         |           |                  |                                             |

|         | *********       |     | anital        |        |             |                |                   |                 |          |         |                       |           |                         |           |                  |                                             |

|         |                 |     | In the second | ×      |             |                |                   |                 |          |         |                       | Generates |                         |           |                  | 0                                           |

| ~       | *******         |     | NUCREMOCE     |        |             | 112.52         | NUMP.             | second of       | 500.0000 | 100.000 |                       | N.07      | Now Mr                  |           | NAME OF A        | maile board                                 |

|         |                 |     | Insertinger   |        | the name    |                |                   |                 | 141      | -       | PRACTICAL DESCRIPTION | NOCTOR    |                         |           | ******           | INCOMPANIES INCOMPANIES - DOWNER            |

|         |                 |     | A POST A POST |        |             |                | CTUS Hot Swap0    | 90.106.00249    |          | 20      | INSCREMENTS           |           | A*GAT stawas            | TRUNCT    | CONSTRUCTED      | FM_DEV_304040_T/TEJE-604_31070-versionax    |

|         |                 |     |               | 201-01 | the text of | ent war wagen  | HER BETWEEN       | passesses (     | 141      |         | 00000000000           |           | ArtAwarmag              | NUMBER    | *****            | PROVIDENTIAL PROPERTY AND A DESCRIPTION OF  |

|         |                 |     |               | 38.9   | 106.100.6   | 124            | 127               | (100.301.0)     | 106      | 71      | PM, \$26503,717       | 0,5945362 | -10.00                  | TRUNCT    | PC/VDUTS         | FM_DEVE_SCHOOL_FITE_THESHOLD-Envelope       |

| 1722    | 22              |     | 9             | 200 0  | the terap   | WE HER NEW     | AND HER NAME      | passasag        | 141      |         |                       |           | inclusion in the second | HIGHLE    |                  | INCOMPANY AND INCOMPANY AND A DATA OF       |

| 67      | 94<br>1         | 1.1 |               | 211.9  | 106.100 (0  | Dual for Swept | CTUG Het Swept    | (100.307.0)     | 136      | 17      | INDETERMINED          |           | ATCA I STIMUS           | TRUNCT    | nc,usercence     | FM_DEV_SDADNO_T/TELEVEDIL_STOTE-INTERVEDI   |

| × 162   | 25              |     | 0             | 211.0  | the terap   | 98742          | 199212            | 10.10.0004      | 141      | 26      | INCOME.               | -         | tespectrar              | PROMO     | A DESCRIPTION OF | PROVIDENTIAL OPPOSITE CONTRACTOR            |

| 192     | **              |     |               | 11.9   | 106.100.001 | 000289         | UHE20CD           | (100.307.0)     | 106      | 71      | IN SHOLD              | CONCERNO2 | Improve                 | TRUNCT    | 2,2239200,27     | PM_DEV_304090_TPT_TRESIO_D-metrick          |

| s 163   | 55              |     | 3             | 212.0  |             | 997.64         | 199714            | passage and     | 141      | A       | IN NUMBER OF          | -         | Improver                | PROPERTY. | A LEADERS I      | the party estimation the needed in the date |

| 112     | **              |     |               | 11.9   | 106.100.001 | 98200K         | LANSON .          | 0.06.00.00      | 06       | 73      | IN SHOLM              | 200422VCL | Incompany of            | TYLINGT   | 0.2000000.0      | THE DEVELOPMENT OF THE STOLE-INVESTIG       |

| 102     | 52              |     | 3             | 212.0  | 110.10.10   | 10110-002      | HER HAR SHARE     | 0.10.101        | 195      | 18      | INTRINATION OF        |           | Archevenes              | PRIME     |                  | IN INTERVIEW IN THE SEALE SECIES SHOW OF    |

| 114     | 211             |     |               | ۰.,    |             | _              | -                 | _               | _        |         | _                     |           | _                       |           |                  |                                             |

| 4 162   | 55              |     | 3             |        |             | (0.126106.2)   | THE DATES         | Ombiget.        | . 126    | 136     | 0                     | 4         | o )                     | iara san  | 421404           |                                             |

| 1.12    | **              |     |               |        |             | etranete       | PR PUT            | Bard street.    | 10       |         | 0                     | 4         | 0                       |           |                  |                                             |

| 103     | 101             |     | 3             |        |             | (0.136/00.5)   | PHERICAL CONTRACT | Goord-lattipet. | 136      | 6       | 0                     | 211712007 | 0                       |           |                  |                                             |

| 111     | 10              |     |               |        |             | 0113819530     | PR PUTCH          | Bard street.    | 139      | 10      | 0                     | manna     |                         | 29 M      | en l             |                                             |

| × 103   | 100             |     |               |        |             |                | INF FUTTY         | Doerd-ort spec  | 154      | 4       | 0                     | 211701207 | 6                       |           |                  |                                             |

Fig. 5. IPMI System Software graphical interface.

190

201 202 203

220 221

222

230

231

232 233

234

235

TABLE I. PPR SENSORS AND CONFIGURABLE/READABLE DEVICES VIA IPMB

| 203 | TABLE I. PPK SENSORS AND | CONFIGURABLE/READABLE DEVICES VIA IPMB |  |  |  |  |  |

|-----|--------------------------|----------------------------------------|--|--|--|--|--|

| 205 | Device                   | N.devices x N.registers per device     |  |  |  |  |  |

| 206 | Supply voltage           | 8x1 (sensor, r)                        |  |  |  |  |  |

| 207 | Supply Current           | 8x1 (sensor, r)                        |  |  |  |  |  |

| 208 | QSFP (link on/off state) | (4x4) links x1 (control, r/w)          |  |  |  |  |  |

| 209 | QSFP (link optic. pwr)   | (4x4) links x1 (sensor, r)             |  |  |  |  |  |

| 210 | SFP (on/off state)       | 1x1 (control, r/w)                     |  |  |  |  |  |

| 211 | SFP (optical power)      | 1x1 (sensor, r)                        |  |  |  |  |  |

| 212 | MiniPOD (on/off state)   | 2x12 (control, r/w)                    |  |  |  |  |  |

| 213 | MiniPOD (optical power   | 2x12 (sensor, r)                       |  |  |  |  |  |

| 214 | Temperature Sensor       | 6x1(sensor, r)                         |  |  |  |  |  |

| 215 | XTALs config.registers   | 4x4 (control, r/w)                     |  |  |  |  |  |

| 216 | Jitter cleaners          | 2x2 (control, r/w)                     |  |  |  |  |  |

| 217 | FPGAs remote reset       | 3x1 (control, w)                       |  |  |  |  |  |

| 218 |                          |                                        |  |  |  |  |  |

| 219 | TOTAL OF 'read' BYTH     | ES 125                                 |  |  |  |  |  |

| 220 | TOTAL OF 'write' BYT     | ES 65                                  |  |  |  |  |  |

#### REFERENCES

- The ATLAS Collaboration, "The ATLAS Experiment at the CERN Large [1] Hadron Collider", Journal of Instrumentation, vol.3, no.8, pp. S08003, 2008, IOP Publishing. http://stacks.iop.org/1748-0221/3/i=08/a=S08003

- [2] B. Schmidt, "The High-Luminosity upgrade of the LHC: Physics and Technology Challenges for the Accelerator and the Experiments", Journal of Physics: Conference Series, vol.706, no.2. pp. 022002, 2016, IOP Publishing, doi:10.1088/1742-6596/706/2/022002.

- [3] F. Tang et al., "Design of the front-end readout electronics for the ATLAS tile calorimeter at the sLHC," IEEE Trans.Nuc.Science, V.60, N.2.1255-1259, Apr.2013.

- [4] F. Carrió et al. "The PreProcessor for the ATLAS Tile Calorimeter Phase II Upgrade", IEEE NSS 2015, San Diego (USA-CA) Oct./Nov.2015.

- [5] R. Achenbach et al., "The ATLAS Level-1 Calorimeter Trigger", Journal of Instrumentation, vol.3, no.3, pp. S03001, 2008, IOP Publishing. http://stacks.iop.org/1748-0221/3/i=03/a=S03001

- [6] PICMG 3.0 Revision 2.0 AdvancedTCA Base Specification. http://www.picmg.org.

- Intelligent Platform Management Interface Specifications v1.5 and v2.0. [7] http://www.intel.com/content/www/us/en/servers/ipmi/ipmi-home.html

- [8] PICMG Advanced Mezzanine Card (AMC) Base Specification. https://www.picmg.org/openstandards/advanced-mezzanine-card/