PIGE ENS

17. Menter

CERN/EF/EHS/TE 78-2 14 February 1978

## TESTS OF THE VIENNA DRIFT CHAMBER ELECTRONICS

N. Bosco, Ch. Ljuslin, G. Neuhofer, M. Pernicka, H. Stradner

#### 1. DESCRIPTION OF THE MODULES

### 1.1 Clock-module and Converter Module

These are already described in note CERN/EF/EHS/TE 77-5.

### 1.2 Clock-stop-module (CSM)

This module, from the performance and the logic point of view, is unchanged, but the clock distribution has been moved to the crate-controller.

# 1.3 Drift-time-module (DTM)

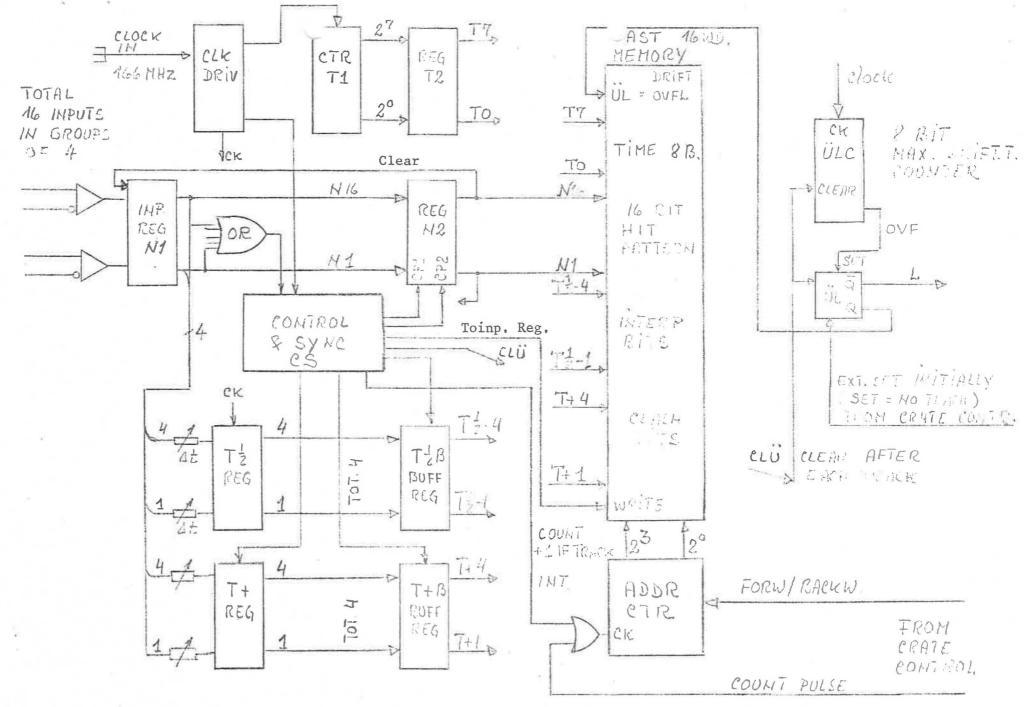

This is a single slot CAMAC module with card-edge connector, 16 inputs, 1 clock input and external test input. A block diagram is shown in Fig. 1. The module allows one to measure drift times up to  $\sim 1.5~\mu s$  with a bin width of 3 ns. The major difference compared to the prototype module is that the number of interpolators and correction bits have been increased. Four adjacent inputs share one interpolator. This is a major improvement for multihit events. The memory is 33 bits wide and 16 words deep. The words read out have the following format:

|    | 16             | 15             | 14             | 13             | 12   | 11                  | 10                  | 9 | 8    | 7   | 6   | 5   | 4  | 3  | 2  | 1       |

|----|----------------|----------------|----------------|----------------|------|---------------------|---------------------|---|------|-----|-----|-----|----|----|----|---------|

|    | T <sub>4</sub> | T <sub>3</sub> | T <sub>2</sub> | T <sub>1</sub> | T4 4 | $T_3^{\frac{1}{2}}$ | $T_2^{\frac{1}{2}}$ |   | T128 | T64 | Т32 | T16 | т8 | Т4 | T2 | T1      |

| 17 | 16             | 15             |                |                |      |                     |                     |   |      |     |     |     |    |    |    | 1       |

| UL |                |                |                |                |      |                     |                     |   |      |     |     |     |    |    |    |         |

|    |                | <u> </u>       | J              | <u> </u>       |      |                     |                     | ~ |      |     |     |     |    |    |    | <u></u> |

Hit pattern

16 bits are used for the hit pattern and 8 bits for the coarse time measurement. There are 4 T bits which are the measurements of the 4 interpolators and there are 4 T + bits which indicate when two hits in one interpolator were close together. They are used as correction bits. There is also 1 bit UL (overflow) which acts as a time out bit.

### 1.4 Controller

The controller conforms to CAMAC standards. Seen from the CAMAC branch highway, it looks like a normal CAMAC-crate-controller. It serves also for clock-distribution. It accepts the following CAMAC commands: Start, Stop, Reset, Set, read UL-pattern

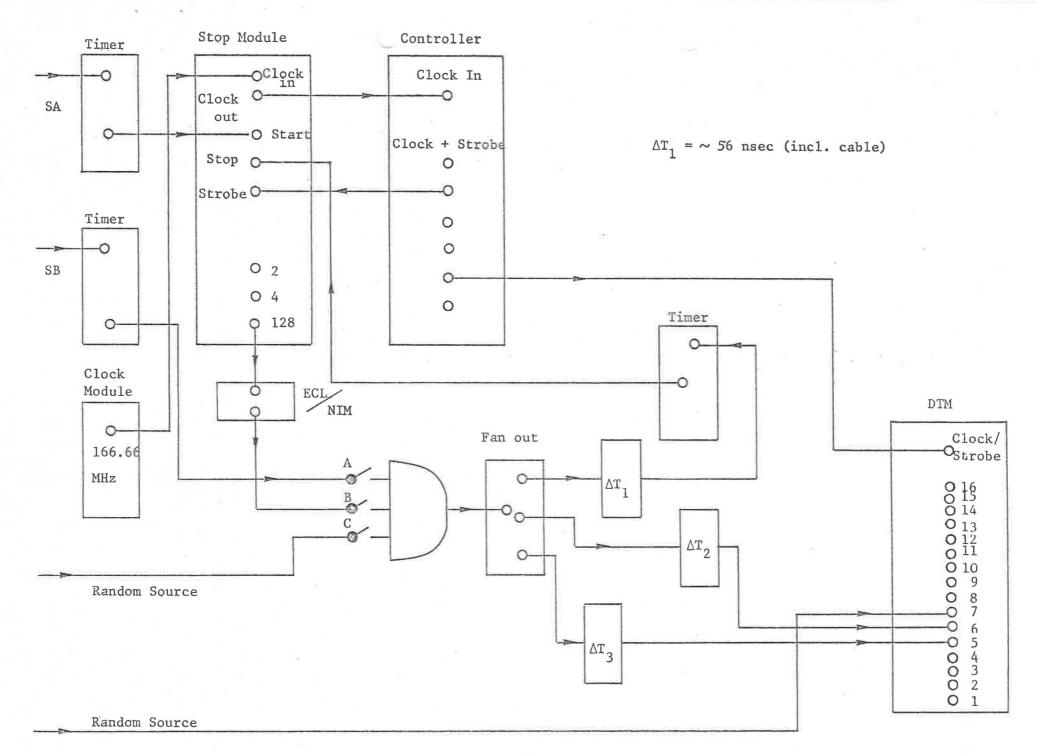

#### 2. SET-UP

The set-up (Fig. 2) of the test is the following: all modules are located in a modified CAMAC crate, which is connected to the computer via the controller.

A test-cycle is started with a computer-generated signal SA and stopped with the coincidence signal of SB and the random source (switches A and C closed) or with a signal from the random source alone. Signal SB arrives about 2 ms after SA. The output of this coincidence acts also as an event generator for the DTM.

#### 3, RUNNING UP

No discrepancies between write-up and hardware were observed, but the controller generated non-standard BTB signals.

### 4. TEST RESULTS OF THE CLOCK-STOP-MODULE (CSM)

#### 4.1 Test of the Interpolator

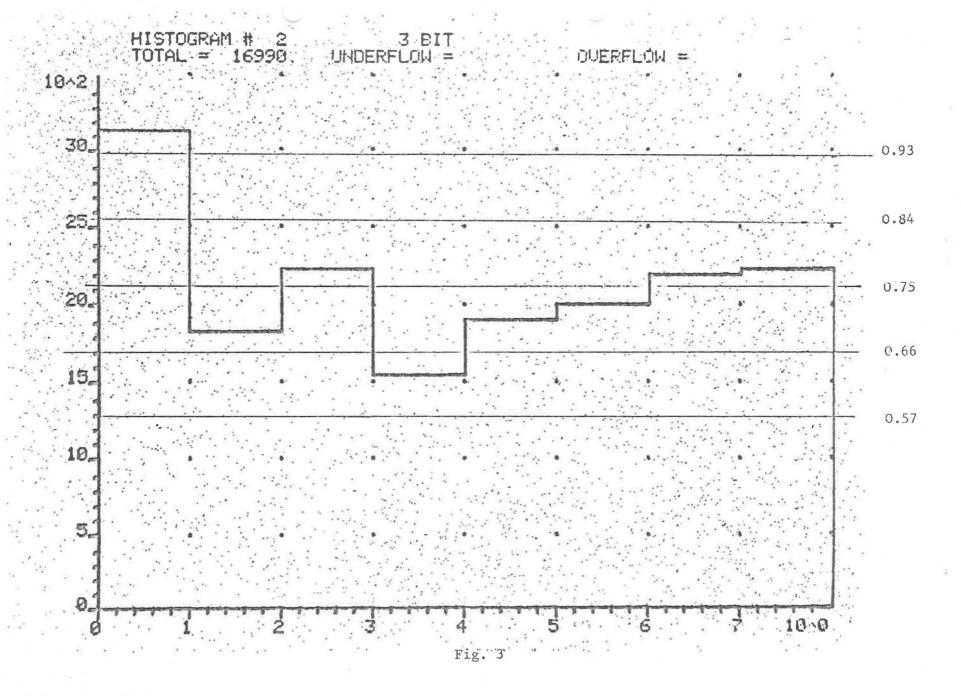

The CSM was started via the computer and after some delay stopped randomly. The last 3 bits of the time-counter were histogrammed (Fig. 3).

The distribution should be flat in an ideal case. The maximum deviation from the expected 750 ps is about 200 ps. No further timing tests were done.

# 4.2 Thermal Stability

The pattern reproduced within statistics even after a long power off.

# 5. TEST RESULTS OF THE DRIFT-TIME-MODULE (DTM)

# 5.1 Maximum Input Rate

Data were lost only at input frequencies higher than 100 MHz !!

#### 5.2 Cross-talk Test

All, except one channel, were fired at the same time. In 5000 events the open channels showed no hits. Only channels 5 and 6 showed some 0.3% cross-talk.

#### 5.3 Interpolator Test

The least significant bit of each channel was histogrammed. Two typical cases are shown in Fig. 4. Interpolators 1 and 4 were not very well tuned.

#### 5.4 Time Resolution

The time difference between the pulse to the DTM and the stoppulse is constant, but the pulses arrive at random with respect to the

clock pulses. The value "Stop-time - Drift-time" was histogrammed

(Fig. 5): the bin-width is 0.75 nsec. The expected theoretical distribution should be 5 bins wide. The measured distribution shows a full

width of 5 to 6 bins, which means there are nowhere essential jitters

in the circuitry.

# 5.5 The "3 - 9 nsec Problem

The electronics set-up is shown in Fig. 2. 7 series of measurements have been performed in the following way:

- (a) AT<sub>2</sub> delay was set such that one just saw an even number for the drift-time, which means one had just crossed the edge of the clock-pulse.

- (b)  $\Delta T_3$  was set to the same value and then stepped up by 1 ns increments, the time difference between input A and B was registered. After 20 25 increments  $\rightarrow$

- (c)  $\Delta T_2$  was incremented by 1 ns. Point 2 was repeated; after 7 series one is sure that one has covered the range of a full clock-pulse.

The results are given in the following table which shows the measured time differences in ns.

|                           |    | $\Delta T_2$ . Lin | s]   |    | 4   |    |    |     |      |

|---------------------------|----|--------------------|------|----|-----|----|----|-----|------|

| $\Delta T_3 - \Delta T_2$ |    | 2                  | 1    | 2  | 3   | LI | 5  | 6   |      |

| [ns]                      | Ø  | a                  | Ø    | Ø  | Ø   | Ø  | Ø  | Ø   |      |

|                           | 1  | Ø                  | Ø    | Ø  | Ø   | Ø  | 9+ | Ø   |      |

|                           | 2  | P                  | Ø    | Ø  | Ø   | 9+ |    | Ø   |      |

|                           | 3  | Ø                  | Ø    | 9+ | 9 + |    |    | Ø   |      |

|                           | 4  | Ø                  | Ø    |    | 1   |    |    | Ø   |      |

|                           | 5  | 0                  | 12 + |    |     |    | 9+ | Ø   |      |

|                           | 6  | 12 +               |      |    | 1   | 9+ | 9  | 12+ |      |

|                           | 7  | - 1                |      | 9+ | 9+  | 9  |    |     |      |

|                           | 8  |                    | 12 + | 9  | 9   |    | 9  | , 1 | - 1  |

|                           | 9  |                    | 12   |    |     |    | 12 | 12+ | أستد |

|                           | 10 | 12+                |      | 1  |     | 9  | =  | 12  |      |

|                           | 11 | 12                 |      | 9  | 9   | 12 | _  | ,   |      |

|                           | 12 | 1                  | 12   | 12 | 12  |    |    | l   |      |

The symbol + indicates that the T bit was on. One has to correct these values by 6 nsec.

# 5.6 Hang-up Test

The system was started and stopped within a short time interval (100 ns) with a repetition rate of  $\sim 2$  s. No hang-ups were observed.

### 6. CONCLUSIONS

# 6.1 Clock-stop Module

This module works very well, the stability is good.

# 6.2 Drift-time Module

The "3 - 9 nsec" problem looks much better than the last test in July 1977.

In addition, it is worth mentioning that its occurrence is strongly reduced by using 4 interpolators. A minor bug was found, namely that the  $T^{\dagger}$  turns on already with the first word. But this error is recoverable by software.

VIENNA DRIFT-TIME MODULE - PRIMCIPLE

FIG. 1

19 12 17. Th

Fig. 2

### HISTOGRAM # 31 LAST 2 BIT DTM CF 3

| CHAN. | LW.EDGE                | CONT.        | 1111111111111111122222222222222233333333                                                |

|-------|------------------------|--------------|-----------------------------------------------------------------------------------------|

| 1 2   | .000<br>1.000<br>2.000 | 467.<br>533. | І <del>макання компексите по </del>                 |

|       | .2.000                 | 6            | TOTAL NUMBER OF EVENTS PER * (FULL CASE) UNDERFLOW *NOT INCLUDED OVERFLOW *NOT INCLUDED |

| erae  | 1.033                  |              | MEAN VALUE OF THE DISTRIBUTION                                                          |

# HISTOGRAM \$ 26 LAST 2 BIT DTM C'T

| CHAN |     | LW.EDGE | CONT, | 11111111111222222222222223333333333344444444                                                         |

|------|-----|---------|-------|------------------------------------------------------------------------------------------------------|

|      |     |         |       | <b>12344567889012234566789001234</b> 456788901223456678900123445678890122345667890012344567889012234 |

|      |     |         |       | <b>86420864208642086420864208642086</b> 4208642086420864208642086420864208642086                     |

|      |     | 34      |       |                                                                                                      |

|      | 1 . | .000    | 655.  | I 最美美球等的转换的 医克格特氏 医克格特氏 医克格氏 医克格氏 医克格氏 医克格氏 医克格氏 医克格氏 医克格氏 医克格                                       |

|      | 2   | 1.000   | 345.  | $\mathbf{I}$ %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%                                                    |

|      |     | 2:000   |       |                                                                                                      |

|      |     |         | 1000. | TOTAL NUMBER OF EVENTS                                                                               |

|      |     |         | . 8   | PER * (FULL CASE)                                                                                    |

|      |     |         | 0     | UNDERFLOW ,NOT INCLUDED                                                                              |

|      | - 3 |         | 0     | OVERFLOW ,NOT INCLUDED                                                                               |

|      |     | .845    |       | MEAN VALUE OF THE DISTRIBUTION                                                                       |

OVERFLOW , NOT INCLUDED

84-144

MEAN VALUE OF THE DISTRIBUTION