# The FTK to Level-2 Interface Card (FLIC)

R. Wang\*, J. Anderson, B. Auerbach, R. Blair, G. Drake, A. Kreps, J. Love, M. Oberling, J. Proudfoot,

J. Zhang

HEP Division, Argonne National Laboratory, 9700 S. Cass, Argonne, IL 60439, USA

\*Email: rwang@anl.gov

1 3 in the FTK chain of custom electronics to connect the system 52 implemented (central region only) in spring, 2016. 4to the High-Level trigger (HLT). The FTK performs full event Stracking using the ATLAS Silicon detectors for every Level-1(L1) <sup>53</sup> 10 commercial PC blades, making use of the 10 Gb Ethernet full 11 mesh ATCA backplane.

12 15 to global module identifiers using look up tables stored in static 16 RAM (SRAM). After processing, the event records are sent 18 LINK) protocol at 2 Gbps. The data processing is handled 64 as on b-tagging and primary vertex finding efficiency. 19in two Xilinx Virtex-6 FPGAs, with two additional Virtex-6 20 FPGAs communicating with the processor blades over the ATCA  $^{21}$  backplane. The four FPGAs are connected via a full internal mesh  $^{\,65}$ 22 of high speed GTX lines. This paper reports the design goals, 66A. Functionality 23 implementation, and testing results of the FLIC.

### I. INTRODUCTION TO THE ATLAS TDAQ AND FAST 24 TRACKER SYSTEM 25

THE ATLAS [1] trigger system is deployed to reduce the 71 HLT. 26 27 event rate from the Large hadron collider (LHC) bunch 72 Each FLIC board receives the upstream event record from 28 crossing frequency of 40 MHz to about 1000 Hz for permanent 73 the eight optical links in the front panel. Each link receives 29 storage. For Run 2, the architecture is a two tier trigger 74 data with a bandwidth of bandwidth is 2Gbps (tested up to 30 system, consisting of a custom hardware-based Level-1 (L1) 753Gbps). Because the FTK has its own coordinates for the 31 trigger [2] and a computer-based High-Level trigger (HLT) 76 hit clustering, local identifiers have to be converted to the 32[3]. The L1 trigger system uses custom-made electronics to 77 coordinate system used by HLT algorithms. The two FLIC 33 determine the regions of interest (RoI) from the calorimeter 78 boards do the conversion using lookup tables, and insert the 34 and muon spectrometer coarse signals. The L1 trigger reduces 79 corresponding ATLAS global module identifier into the event 35 the event rate from 40 MHz to 100 kHz with a latency of 80 record during data processing. The event record is reformatted 362.5 µs. The HLT then runs trigger algorithms with near- 81 to the ATLAS standard record format before it is sent out to 37 offline reconstruction quality on either the RoIs or the full 82 the HLT. 38 event information with an off-the-shelf CPU farm. This further 83 The FLIC communicates with the multiple processor blades 39 reduces the event rate from 100 kHz to about 1000 Hz with 84 housed in the same ATCA shelf using the full backplane 40 an average latency of 0.3 s.

41 In Run 2, as the luminosity and pile-up increases, the 86the multiple blades. 42 rapid growth of the event sizes will push the load on the 43 HLT because only a finite number of RoIs can be processed. 44 Without selection using tracks, this results in a reduced <sup>87</sup>B. Data Processing, Control and Monitoring 45 efficiency or higher trigger thresholds for the objects to be 88 The FLIC board is composed of the input card and the rear 46 considered. Global event information, such as the location of 89 transition module (RTM). Two FLIC boards occupy the hub 47 the hard interaction vertex or number of primary vertices in the 90 slots of an ATCA shelf, with processor blades in payload slots. 48 event, is useful for object selections, corrections or background 91 This allows the full event record to be sent to any of the blades 49 rejection. To provide track information to the HLT before full 92 via 10 Gb Ethernet.

Abstract—The Fast TracKer (FTK) to Level-2 Interface Card 50 reconstruction, a hardware-based track finder (Fast TracKer) 2(FLIC) of the ATLAS FTK trigger upgrade is the final component 51 has been designed to run at the L1 rate. It will be partially

The Fast TracKer (FTK) [4] is a custom electronics system 6 accepted event at 100 kHz. The FLIC is a custom Advanced 54 that rapidly finds and reconstructs tracks in the inner-detector 7 Telecommunications Architecture (ATCA) card that interfaces 55 layers for every event that passes the L1 trigger. It provides 8 the upstream FTK system with the ATLAS trigger and data 56 global track reconstruction so that the HLT has access to early 9 acquisition (TDAQ) system, and allows for event processing on 57 tracking information. The track reconstruction is performed in 58hardware with massive parallelism of associative memories The FLIC receives data on eight optical links at a bandwidth 59 and FPGAs. Since tracks from FTK closely match to offline 13 of about 1 Gbps per channel, reformats the data to the ATLAS 60 tracks, a pre-selection can be done before full track recon-14standard record format, and performs a conversion from local 61struction. The performance has been studied with FTK tracks 62 implemented in the trigger chains [4]; a large improvement 17 out to the TDAQ system using the simple link interface (S- 63 can be seen on the ability to identify single particles, as well

### II. THE FTK TO LEVEL-2 INTERFACE CARD

The FTK to Level-2 Interface Card (FLIC), shown in Figure 681, is the final component of the FTK system. It is a custom Ad-69vanced Telecommunications Computing Architecture (ATCA) 70card that interfaces the upstream FTK components with the

85bandwidth. This enables event processing and monitoring by

Fig. 1. The FLIC production board.

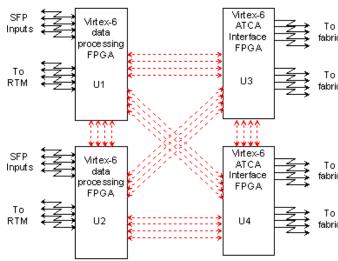

The input card is divided into two areas, the data processing<sub>131</sub>then pulled out by the receiver state machine. The internal 93 94 area and the management area. In the data processing area, 132 processing uses a faster clock (3.2 Gbps for each pipeline) to 95 there are four Xilinx Virtex-6 FPGAs. Two are used to handle<sub>133</sub> insure that, ON AVERAGE, no more than one event's worth of % the data processing (processing FPGA) with the other two134 data will be stacked in the FIFO. Each processing FPGA has 97 communicating with the processor blades over the ATCA13532 Mb of fast SRAM per input link performing the conversion 98 backplane (interface FPGA). The four FPGAs are connected to 136 of the module identifier (ID) from the FTK local ID to ATLAS 99each other via a full internal mesh of high speed low-voltage137global ID. The address for the lookup is built from the header 100 differential signaling (LVDS) lines (designed to run at 4 Gpbs)<sub>138 of</sub> each track. The lookup is performed in parallel with the (Figure 2).

to another one using four high speed GTX lines.

101

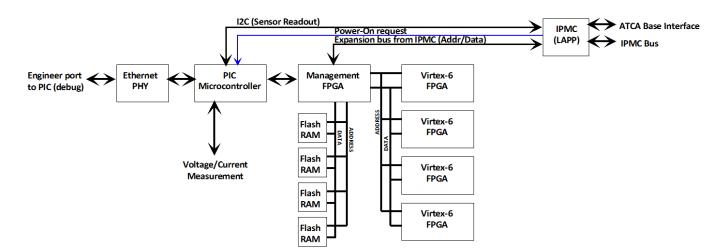

105 four Flash RAMs and one Intelligent Platform Management 106Controller (IPMC) card made by LAPP [5], shown in Figure 1073). The small FPGA provides level translation and bus control 108logic to interface the microprocessor and Flash RAMs to the 109 Virtex-6 FPGAs. When requested, it loads the firmware for 110each FPGA from the Flash RAM for configuration. Data for 111the SRAM fast lookup tables used by the Virtex-6 FPGAs 112is also stored in the Flash RAM. The PIC monitors volt-113age, current and temperature of the board directly using its 114internal Analog-to-digital converter (ADC). The PIC receives 115 commands over the front panel Ethernet port, performing the 116 required register and data accesses to all other devices by 117 controlling the small FPGA. All transactions on the front 118panel Ethernet port are acknowledged. A secondary Inter-119Integrated Circuit (I2C) interface connects the LAPP IPMC, a 120 custom mezzanine card, to the PIC. Through this interface 121 all monitoring information may be transferred through the 122 IPMC to the shelf manager. Main board power is controlled 123in accordance with ATCA specifications by the IPMC. The 124power enable signal from the IPMC is sent to the PIC, which 125then re-drives the enable to the DC-DC converter. This allows 126 the FLIC to be bench tested using a power supply.

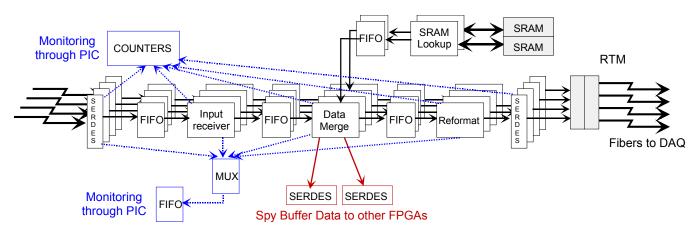

127 Data processing in each processing FPGA is divided into 128 four pipelines. Each pipeline processes data received from one 129small form-factor pluggable (SFP) on the front panel (Figure 1304). The upstream data is buffered immediately after arrival,

139 track processing, which ensures that the global ID is ready to 140be inserted to the track record before processing finishes. The 141 global module ID is inserted into the event record on the fly in fabric 142the merge state machine. Event records are then reformatted to 143 the ATLAS standard record format, sent out from the RTM to 144the HLT. In total eight 2 Gbps S-LINK protocols are used for fabric 145 the RTM and readout card communication. A second version 1460f firmware that emulates the output of the FTK system has 147been developed at Argonne to test the performance of the 148board as a function of the size of event records, event rate, 149 and stability over time.

150 Monitoring of each pipeline is performed by the use of fabric 151 diagnostic counters and a multiplexed capture FIFO, all acces-152sible by the PIC using register I/O as mentioned above. Each 153 pipeline implements multiple counters showing the number fabric 154 of records and/or the number of fragments that have been 155 processed. The multiplex capture FIFO may be used to capture 156 data at multiple points along each pipeline, saving a copy of Fig. 2. Then internal mesh between the four FPGAs. Each FPGA is connected <sup>157</sup>raw data as it passes through the pipeline. Both the counters

158and capture FIFO can be read using the front panel port. The 159spy buffer functionality has been implemented in the FLIC

The management area provides the slow control and mon-160as well using the two interface FPGAs. They copy fragments 102 103 itoring of the FLIC board. It consists of one small Spartan-3161 of the selected event from the processor FPGAs using the 104 FPGA, one Microchip peripheral interface controller (PIC), 162 internal mesh. Those fragment are then assembled, formed into

Fig. 3. Then slow control of the FLIC board.

Fig. 4. The data processing pipeline in the processing FPGA.

163Ethernet packets, and sent to multi-processor blades through 164the ATCA backplane. Analysis of these events by the blades in 165the shelf may then provide advanced monitoring or triggering 166options as appropriate software is developed.

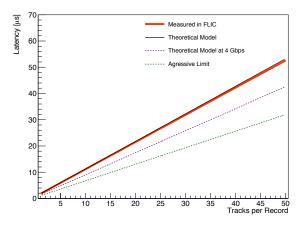

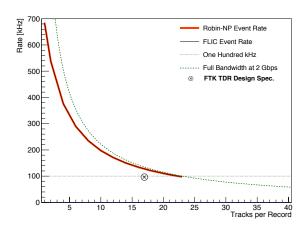

## 167 C. Performance study

Two prototype FLIC boards have been tested for all re-168 169 quirements and demonstrated to perform at or above design 170 specification. For the data processing inside the FLIC, the 171 Chipscope measurements show the SRAM lookup takes a 172 maximum of 139 ns to resolve for all detector layers, while 173 processing of each track takes 160 ns. The latency has been 174 measured as a function of the number of tracks per event 175 (Figure 5). Good agreement can be seen between measurement 176 and theoretical model predictions (the time taken to write the 177 event record into the various FLIC FIFOs as the data expands 178 within the board). In the specification, the Run 2 event record 179 contains an average of 17 tracks, which corresponds to a 180 latency of about 20  $\mu$ s. The event rate from the FLIC to the 181 HLT has also been studied. Figure 6 shows the measured event 182 rate as a function of the number of tracks per event record. For 183 an event with 17 tracks, the rate is about 120 kHz, above the

Fig. 5. Latency of the FLIC data processing as a function of the number of tracks per event record. The red line is the rate that FLIC sends event records. The black line is calculated based on the theoretical model. The rate for a 4 Gbps output link (purple dashed line) and aggressive limit (using full bandwidth, green dashed line) are also shown.

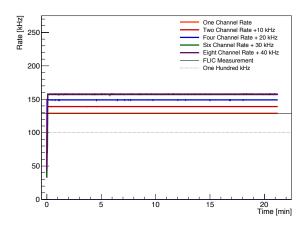

184100 kHz HLT requirement. As all pipelines are independent, 185 the rate per pipeline does not change when processing multiple

Fig. 6. The FLIC to HLT event sending rate as a function of the number of tracks per event record. The black line shows the event record rate of FLIC sending date while the red line is the receiving rate on the HLT side. The green dashed line shows the maximum rate when using the full 2 Gbps bandwidth. The cross shows the FTK specification which is 100 kHz of 17 tracks per event record.

Fig. 7. The rate at which the FLIC sends events to the HLT is measured with a fixed number of tracks per event record in each output channel. Measurements have been performed using one (orange line), two (red line), four (blue line), six (green line), and eight (purple line) output channels. The measured rate using multiple output channels have been shifted up for better visibility. The rate limit in the specification is 100 kHz (dashed line).

186 channels (Figure 7).

187

## III. SUMMARY

The FLIC is an interface between the FTK and the High 188 189 Level Trigger built with all necessary and desired functionality. 190 It does the data dispatching to HLT with geometry description 191 conversion, as well as the data monitoring and processing on 192 ACTA blades. It has been extensively tested, meets or exceeds 193 all the specifications.

### REFERENCES

- 195[1] ATLAS Collaboration, The ATLAS Experiment at the CERN Large

- 196 Hadron Collider 2008 JINST 3 S08003 1-407

- ATLAS Collaboration, ATLAS Level-1 Trigger Technical Design Report 197[2]

- CERN/LHCC/98-014 (1998) 198

194

- 199[3] ATLAS Collaboration, ATLAS High-Level Trigger Data Acquisition and

- Controls Technical Design Report CERN/LHCC/2003-022 (2003) 200

- 201[4] ATLAS Collaboration, Fast TracKer (FTK) Technical Design Report Tech. Rep. CERN-LHCC-2013-007, ATLAS-TDR-021, CERN, Geneva, 202 203

- June, 2013. ATLAS Fast Tracker Technical Design Report

- 204[5] Atlas LAPP, Annecy. LAPP IPMC Mezzanine 2013, http://lappwiki.in2p3. fr/twiki/bin/view/AtlasLapp/ATCA 205