# gFEX, the ATLAS Calorimeter Level-1 Real Time Processor

Shaochun Tang, Michael Begel, Hucheng Chen, Francesco Lanni, Helio Takai and Weihao Wu on behalf of the ATLAS Collaboration

Abstract-The global feature extractor (gFEX) is a component5 of the Level-1 Calorimeter trigger Phase-I upgrade for the ATLAS experiment. It is intended to identify patterns of energy associated with the hadronic decays of high momentum Higgs,

- 5 W, & Z bosons, top quarks, and exotic particles in real time at the LHC crossing rate. The single processor board will be packaged in an Advanced Telecommunications Computing<sup>0</sup> Architecture (ATCA) module and implemented as a fast reconfigurable processor based on three Xilinx Vertex Ultra-

- 10 scale FPGAs. The board will receive coarse-granularity information from all the ATLAS calorimeters on 276 optical fibers with the data transferred at the 40 MHz Large Hadron Collider (LHC) clock frequency. The gFEX will be controlled by<sup>5</sup> a single system-on-chip processor, ZYNQ, that will be used to

- 15 configure all the processor Field-Programmable Gate Array (FPGAs), monitor board health, and interface to external signals. Now, the Prototype 1 board which includes one ZYNQ and one Vertex-7 FPGA has been designed for testing and verification. After the elementary technologies have been verified in the

- 20 Prototype 1, a more advanced prototype with three Vertex Ultrascale FPGAs is being designed. Although the board is being designed specifically for the ATLAS experiment, it is sufficiently generic that it could be used for fast data processing at other high energy physics or nuclear physics experiments. 65

## I. INTRODUCTION

HE Large Hadron Collider (LHC) will undergo a series I of upgrades, which allow luminosity increases in next ten years. In Table 1 the different phases are shown. The ATLAS0 experiment also [1] will follow the same upgrade steps. During the so-called Phase-I upgrade, the ATLAS first level trigger (level-1) will be updated with a new component in the calorimeter system (called L1Calo): the gFEX. It is one of the new components designed to maintain 5 trigger acceptance against increasing luminosity. The gFEX is used to select large-radius jets, typical of Lorentz-boosted objects, by means of wide-area jet algorithms refined by subjet information.

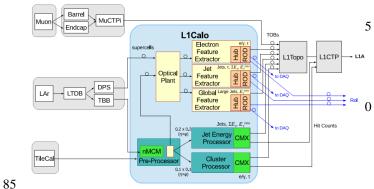

The L1Calo system processes signals from electromagnetigo and hadronic calorimeters. As shown in the Fig.1, the L1Calo before this upgrade has three major subsystems (marked with green color): the Cluster Processor Subsystem (CP) comprising Cluster Processor Modules (CPMs) [4] and Common Merger Extended Modules (CMXs) [5]; the Jet/Energy Processor Subsystem (JEP) comprising

S.Tang, M.Begel, H.Chen, F.Lanni, H.Takai and W.Wu are with the Brookhaven National Laboratory, Upton, NY 11973 USA (telephone: 631-344-2863, e-mail: stang@bnl.gov).

Jet/Energy Modules (JEMs) [6] and CMXs; and the Preprocessor Subsystem, comprising Preprocessor Modules (PPM). The CPM is used to identify electrons and taus, while jet energy and  $E_T^{miss}$  are measured in the JEMs. Three additional feature identification systems will be installed during Phase-I: the Electron Feature Extractor (eFEX) [7], the Jet Feature Extractor (jFEX) [8], and the gFEX. The eFEX and jFEX provide similar functionalities to the CPM and JEM, respectively, albeit with finer granularity and more advanced algorithms. Each system consists of multiple modules that operate on limited regions of the calorimeter. The gFEX, in contrast, has the entire calorimeter data available in a single module and thus enables the use of full-scan algorithms.

The Preprocessor receives shaped analog pulses from the electromagnetic and hadronic calorimeters, digitizes and synchronizes them, identifies the bunch collision from which each pulse originated, scales the digital values to yield  $E_T$ , and prepares and transmits the data to downstream elements. In LHC Run 3, the electromagnetic calorimeter will provide L1Calo with both analog signals (for the CP and JEP) and digitized data (for the FEXes). The hadronic calorimeter will continue to send analog signals. These are digitized on the Preprocessor and then transmitted optically to the FEXes through an optical fiber plant. Initially at least, the eFEX and jFEX will operate in parallel with the CP and JEP. The older analog subsystems will be decommissioned once the performance of the FEXes has been validated.

The Phase-II upgrade project includes substantial changes in the trigger electronics, which will be installed during the so called Long Shutdown 3 (LS3). Calorimeter input to L1Calo will be in digital format. The Preprocessor, CP, and JEP subsystems will be removed, and the FEX subsystems, with modified firmware, will be relabeled as L0Calo in a possible two stage (L0/L1) real-time trigger. Hence, the FEX subsystems must be designed to meet both the Phase-I and Phase-II upgrade requirements including the still to be specified Phase-II timing and control signals.

TABLE I. TABLE WITH LHC UPGRADE PHASES AND LUMINOSITY [2][3]

|               | Start time | End time | Luminosity (cm <sup><math>-2</math></sup> s <sup><math>-1</math></sup> ) |

|---------------|------------|----------|--------------------------------------------------------------------------|

| Run 1         | 2011       | 2012     | $8 \times 10^{33}$                                                       |

| LS1- Phase-0  | 2012       | 2015     | N/A                                                                      |

| Run 2         | 2015       | 2018     | $1 \times 10^{34}$                                                       |

| LS2- Phase-I  | 2019       | 2020     | N/A                                                                      |

| Run 3         | 2021       | 2023     | $2 \times 10^{34}$                                                       |

| LS3- Phase-II | 2024       | 2026     | N/A                                                                      |

| Run 4         | 2026       | 2029     | $5 \times 10^{34}$                                                       |

Fig. 1. The L1Calo system following completion of the Phase-I upgrade

#### II. MOTIVATION

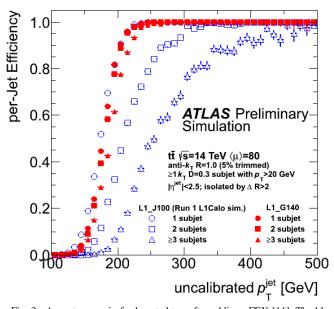

The high  $p_T$  bosons and fermions are a key component of 90 the ATLAS physics program. As shown in Fig. 2, the ATLAS Level 1 trigger was designed for narrow jets with limited acceptance for large objects. Acceptance for large radius (large-R) jets will be greatly enhanced by the inclusion of the gFEX in the trigger. Figs. 3 shows the acceptance gains 95 for boosted top.

> Anti-k, R = 1.0 ATLAS Preliminary Simulation Calorimeter clusters  $\rightarrow t\bar{t}$  event,  $m_{r'} = 1.75$  TeV Subjets, C/A R = 0.2 = 77.3 GeV, mush = 186.5 GeV W boson b jet Top radiation ISR 1.5 0.5 0 0.5

Fig. 2. Effect of jet acceptance with gFEX, compared with current L1 algorithm [9]. The red circle area (R<1) is the L1 narrow jet, and the black 100 circle is the large-R jets with gFEX.

## III. FUNCTIONALITY OF GFEX 130

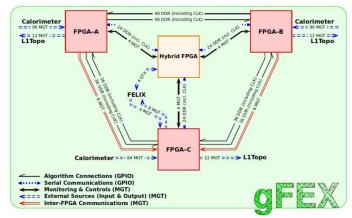

The gFEX has a single module with several large Field-Programmable Gate Arrays (FPGAs) for data processing and a 105 combined FPGA & CPU System-on-Chip (Hybrid FPGA) for control and monitoring. A special feature of the gFEX is that it received data from the antire colorimeter applying that

- receives data from the entire calorimeter enabling the sidentification of large-radius jets and the calculation of wholeevent observables. Each processor FPGA has  $2\pi$  azimuthal ( $\varphi$ )

- 110 coverage for a slice in pseudorapidity ( $\eta$ ) and executes all feature identification algorithms. The processor FPGAs communicate with each other via low-latency GPIO link $\frac{40}{500}$

while input and output to the board are via Multi-Gigabit Transceiver (MGTs). A simplified functional representation of the module is shown in Fig. 5. The gFEX is a customized ATCA module based on the PICMG ® 3.0 Revision 3.0 specification [10]. The gFEX module will likely be placed in a sparsely populated ATCA shelf so that it can occupy two slots if needed: one for the board and one for cooling (e.g., large heat sinks), fiber routing, etc.

Fig. 3. Acceptance gain for boosted top after adding gFEX [11]. The blue curves show the acceptance without gFEX. The 140 GeV gFEX trigger threshold is chosen to match the L1 J100 single subjet turn-on curve. After adding gFEX, the acceptance of two and more sub-jets is recovered and the resolution is nearly the same as that of one sub-jet.

Fig. 4. Block diagram of gFEX. FPGA A, B, and C are the same ultrascale FPGAs; the Hybrid FPGA is ZYNQ FPGA. The FELIX is a PCIe module designed for ATLAS System.

#### A. Input and output interfaces

5

The gFEX receives data from the electromagnetic and hadronic calorimeters via optical fibers. For most of the detectors, the towers — called gTowers — correspond to an area of  $\Delta \eta \times \Delta \varphi = 0.2 \times 0.2$ . As shown in Fig. 4, there are 276 MGTs signals from the calorimeters, which are converted from optical signals on board. The control and clock signals

are inputs and that at the end combined data are sent out via eight MGTs.

The real time data to the L1 Topological Trigger (L1Topo) [12] is sent by three processor FPGAs respectively with 12

145 MGTs. The data received by the processor FPGA A and B are sent to the FPGA C, and then combined with the data of processor FPGA C.

The link speed for L1Calo has not yet been decided. The baseline is 6.4 Gb/s. Alternative choices include 9.6 and 11.2

150 Gb/s. The final decision will be made following a combined integration test of L1Calo and electromagnetic calorimeter electronics in Q1 2016.

#### B. Feature Identification Algorithms

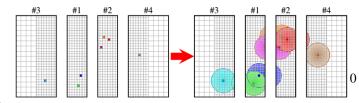

- The core trigger algorithms are implemented in the 155 firmware of the processor FPGAs. The input data, after deserialization, are organized into calibrated gTowers in the gTower-builder step; this procedure is common to all downstream algorithms. A seeded simple-cone jet algorithm is used for the large-area non-iterative jet finding. Seeds are

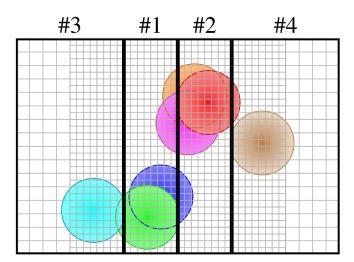

- 160 defined by gTowers over a configurable  $E_T$  threshold. An illustration of the seeds identified in an event is shown in Fig. 5. The gTower  $E_T$  in a circular region surrounding the seeds  $\frac{195}{100}$  summed. Portions of the jet area might extend into an  $\eta$  region on a neighboring processor FPGA. Part of the energy

- 165 summation must therefore take place on that FPGA necessitating the transfer of seed information with low latency parallel GPIOs. These partial sums are then sent to the original PPGA and included in the final  $E_T$  of the large-R jets as displayed in Fig. 6. Note that the jets are allowed to overlap.

- 170 This enhances the efficiency for events with complex topologies where multiple energy depositions are close together, as is typically found in events containing boosted 5 objects.

The architecture of the gFEX permits event-by-event local

- 175 pileup suppression for these large-R objects using baseline subtraction techniques [13]. Pileup subtraction is performed using the energy density  $\rho$  measured on the gTowers with  $n^{0}$ each processing region and is calculated on an event-by-event basis. The energy subtracted from each jet is determined by

- 180 the product of the area of each jet and the energy density from the associated region. Studies are ongoing to optimize the performance of pileup-subtracted jets.

215

185 Fig. 5. Left: Seeding step for identifying large-R jets by selecting towers over a threshold ET value. Right: Summing the energy around the seeds within  $\Delta R \le 1.0$ .

Fig. 6. The final large-R jets. Each jet is stored on the Processor FPGA that produced the seed.

#### C. Slow Control & Environmental Monitoring

A CACTUS/IPbus [14] interface is provided for high-level control of the gFEX. This allows algorithmic parameters to be set, modes of operation to be controlled and spy memories to be read. The IPbus protocol will be implemented in the Hybrid FPGA including the standard firmware modified to run on the FPGA part and the software suite from CACTUS for the Linux instance running on the ARM processor.

The Hybrid FPGA implements Intelligent Platform Management Controller (IPMC) [15], to monitor voltage and current of every power rail on the gFEX. They also monitor the temperature of all FPGAs via their embedded sensors, and of any areas of dense logic via discrete sensors where needed. These data can be transmitted to an external monitoring system by the Hybrid FPGA.

If any board temperature exceeds a programmable threshold, the IPMC powers down the board payload everything not on the management power supply. The thresholds at which this function is activated should be set above the levels at which the Detector Control System (DCS) will power down the module. Thus, this mechanism should activate only if DCS fails. This might happen, for example, if there is a sudden rapid rise in temperature to which the DCS cannot respond in time.

#### IV. IMPLEMENTATION OF PROTOTYPE 1

A first prototype has been designed to verify all the functionalities of the chosen technologies, to test power distribution and sequence, MGT link speed and high speed parallel GPIOs.

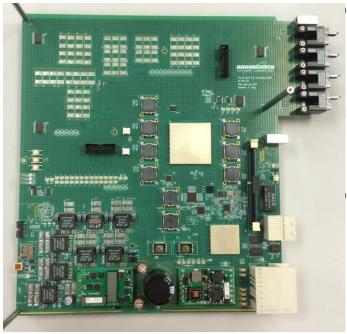

As shown in the Fig. 7, one Hybrid FPGA - ZYNQ and one processor FPGA are included in the Prototype 1. There are also several MiniPODs [16], MicroPODs [17], power modules and high speed parallel GPIOs.

225

25 Fig. 7. gFEX Prototype 1 board

## A. Power distribution and sequence

The gFEX is an ATCA module, so the power design should meet the requirements of ATCA standard. Firstly, two 230 negative 48 V inputs are ORed and inverted to one +48 V by a ATCA board power input module – PIM 400; and then the +48 V power is stepped down to 12V by a DC-DC converter produced by General Electric; at last, all the other power rails such as 1.0V, 1.2 V, 1.8 V, 2.5 V and 3.3 V are generated

- 235 from 12 V with different DC-DC power module respectively. To meet the large current and low ripple requirements of Xilinx FPGA, the power module LTM4630 is used to generate the core and MGT related voltages.

- Since the IPMC is not available yet, two configurable 240 sequencing devices ADM1066 that offers a single-chip solution for supply monitoring and sequencing are used in this board.

### B. MGTs design

There are two types of optical transceivers (MiniPODs and 245 MicroPODs) and two different MGTs (GTX and GTH) to be verified on the Prototype 1 board. So each MGT is connected to two kinds of optical transceivers. Moreover, the GTH to GTH loopback, GTX to GTX loopback, GTH to GTX loopback and GTX to GTH loopback are also included.

#### 250 C. High speed parallel GPIOs

280

The high speed parallel GPIOs are used to transfer data between FPGAs. It requires at least running at 480 Mb/s with 50 bits width. Three different 50 bits GPIOs are designed. The first one is from the processor FPGA High Performance (HP $_3$ 5)

255 banks to HP banks with LVDS differential interface, and the second is from processor FPGA HP banks to ZYNQ HP banks with LVDS differential interface, and the last is from processor FPGA HP bank to HP bank with single-ended HSTL interface.

# D. ZYNQ design

Two Giga-bit Ethernets, QSPI interface, 4Gb DDR3 memories, I2C interface, UART and SD card interface are design in the ZYNQ PS system.

# V. TEST RESULTS OF PROTOTYPE 1

The major functionality and performance tests for the Prototype 1 have been done. The power sequence and monitoring circuit work well as programmed, and the interface of ZYNQ are verified, such as the SD card boot mode and QSPI boot mode. All the hardware technologies are verified and work as expected.

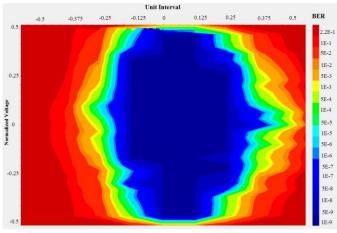

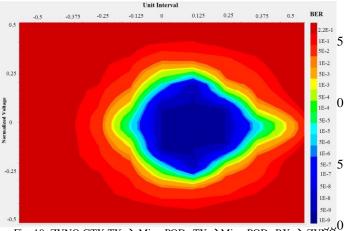

Fig. 8. Processor FPGA GTH TX  $\rightarrow$  MiniPODs TX  $\rightarrow$  MiniPODs RX  $\rightarrow$  Processor FPGA GTH RX. Eye diagram is obtained when the link is 12.8 Gb/s and all the 80 channel GTHs are turned on. The x-axis is for the time unit interval; the y-axis is the normalized voltage; the z-axis (in different color) is the BER rate.

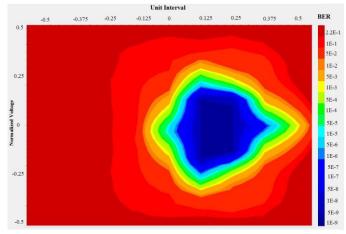

Fig. 9. ZYNQ GTX TX  $\rightarrow$  MiniPODs TX  $\rightarrow$  MiniPODs RX  $\rightarrow$  ZYNQ GTX RX. Eye diagram is obtained when the link is 12.8 Gb/s and all the 16 channel GTXs are turned on.

# A. Link speed test for MGTs

As explained in the previous MGTs design section, there are many different loop backs of MGTs. The link speed tests are done with the IBERT tool provided by the Xilinx Vivado. When all the 80 channel GTHs of processor FPGA and 16 channel GTXs of ZYNQ are turned on, all the links are stable 290 at 12.8 Gb/s with no error bit detected when Bit Error Rate  $< 10^{-15}$ .

The eye diagrams shown in Fig. 8 – Fig.10 are obtained for 5 different combinations of links, when they are all running at 12.8 Gb/s. Comparing all the eye diagrams, the GTH is much

better than GTX, and the MiniPODs is almost the same as 295 340 MicroPODs.

Fig. 10. ZYNQ GTX TX  $\rightarrow$  MicroPODs TX  $\rightarrow$  MicroPODs RX  $\rightarrow$  ZYNQ 300 GTX. Eye diagram is obtained when the link is 12.8 Gb/s and all the 16 channel GTXs are turned on.

#### 365 B. High speed parallel GPIOs

The three chosen 50-bit parallel GPIO are tested with

305 different data patterns (such as PRBS) to measure their stability and the extension of the stability window for each  $\mathfrak{S}_{0}$ them.

With the IP - IDELAYE2, the clock delay can be adjusted with 32 steps. Each step is about 78 ps.

- 310 All these three data buses are stable at 960 Mb/s. The stables range for the processor FPGA HP banks to processor FPGA HP banks LVDS and HSTL interface are about 0.78 ps, which is 75% of half cycle of 480MHz; for the processor FPGA HP banks to the ZYNQ HP banks LVDS interface, the stable0

- 315 range is about 0.702 ps, which is 67% of half cycle of 480MHz.

#### 385 VI. CONCLUSION AND NEXT STEPS

Prototype 1 has successfully verified the validity of the chosen technologies. The GTX and GTH links are stable at

- 12.8 Gb/s and the three high speed 50-bit parallel GPIOs are 320 stable when running at 960 Mb/s. Now a much more advanced prototype is on the way. The prototype will include all the functionalities of gFEX and three ultra-scale FPGAs are designed in. Currently the schematics design is completed and the routing and layout is about 40% finished. 325

#### REFERENCES

- [1] LHCC-I-020.ATLAS Collaboration. The ATLAS Experiment at the CERN Large Hadron Collider, JINST, v. 3, S08003 (2008).

- ATLAS Collaboration, Letter of Intent for the Phase-I Upgrade of the [2] 330 ATLAS Experiment, Tech. Rep. CERN-LHCC-2011-012. LHCC-I-020, CERN, Geneva, Nov, 2011. https://cds.cern.ch/record/1402470.

- [3] ATLAS Collaboration, Letter of Intent for the Phase-II Upgrade of the ATLAS Experiment, Tech. Rep. CERN-LHCC-2012-022. LHCC-I-023. CERN, Geneva, Dec, 2012. https://cds.cern.ch/record/1502664.

- [4] J. Bracinik, S. Hillier, and R. Staley, "ATLAS Level-1 Calorimeter Trigger Firmware Upgrade of Cluster Processor Module Project Specification." http://epweb2.ph.bham.ac.uk/user/bracinik/CPMPhase0/CPMPh0Spec.p

df. 01 August 2014 V1.0.13. [5] L1Calo CMX Collaboration, "ATLAS Level-1 Calorimeter Trigger CMX Module Project Specification."

- http://www.pa.msu.edu/hep/atlas/l1calo/cmx/specification/1\_preliminary \_design\_review/CMX\_Project\_Specification\_v1.0\_final.pdf. 8 August 2011; V1.0.

- U. Schäfer and S. Silverstein, "ATLAS Level-1 Calorimeter Trigger [6] Jet/Energy Processor Module Project Specification.' http://hepwww.rl.ac.uk/Atlas-L1/Modules/JEM/JEMspec12d.pdf. 15 February 2008 v1.2d.

- W. Qian and I. Brawn, "Technical Specification ATLAS Level-1 [7] Calorimeter Trigger Upgrade Electromagnetic Feature Extractor (eFEX) Prototype.' https://edms.cern.ch/ui/file/1419789/1/eFEX\_TechSpec\_v0.3.pdf. 6

October 2014; V0.3.

- S. Artz, S. Rave, U. Sch ä fer, and E. Torregrosa, "Technical [8] Specification ATLAS Level-1Calorimeter Trigger Upgrade Jet Feature Extractor (jFEX) Prototype." https://edms.cern.ch/file/1419792/1/jFEX\_spec\_v0.2.pdf. 06 October 2014: V0.2.

- [9] ATLAS Collaboration, "Performance of shower deconstruction in ATLAS-CONF-2014-003. ATLAS.' https://atlas.web.cern.ch/Atlas/GROUPS/PHYSICS/CONFNOTES/ATL AS-CONF-2014-003/. 17 February 2014.

- [10] CERN-LHCC-2012-022. LHCC-I-023. AdvancedTCA R Specification." http://www.picmg.org/openstandards/advancedtca.

- ATLAS Collaboration, "Global Feature Extraction (gFEX) Performance [11] ATL-COM-DAQ-2014-087. Plots." https://twiki.cern.ch/twiki/bin/view/AtlasPublic/JetTriggerPublicResults #Global\_Feature\_Extraction\_gFEX\_P. August 21, 2014

- [12] B. Bauß, U. Schäfer, and E. Simioni, "ATLAS Level-1 Topological Processor Project Specifications.' http://esimioni.web.cern.ch/esimioni/TPF/l1topoModSpecsV1.3.pdf. September 11, 2013; v1.3.

- [13] ATLAS Collaboration, "Pile-up subtraction and suppression for jets in ATLAS." ATLAS-CONF-2013-083.

- Protocol." [14] R. Frazier al., "The IPbus et https://svnweb.cern.ch/trac/cactus/browser/trunk/doc/ipbus protocol v2 0.pdf. IPbus version 2.0 Draft 6 (22 March 2013).

- [15] Intel Corporation, Hewlett-Packard Company, NEC Corporation, and Dell Inc., "Intelligent Platform Management Interface Specification Second Generation." http://www.intel.com/content/dam/www/public/us/en/documents/produc t-briefs/ipmi-second-gen-interface-spec-v2-rev1-1.pdf. V2 Revision 1.1 October 1, 2013.

- [16] Avago Technologies, "MiniPOD<sup>™</sup> AFBR-814VxyZ, AFBR-824VxyZ 14 Gbps/Channel Twelve Channel, Parallel Fiber Optics Modules, Product Brief." http://www.avagotech.com/docs/AV02-4039EN. AV02-4039EN — March 8, 2013.

- [17] Avago Technologies, "MicroPOD™, AFBR-77D4SZ, AFBR-78D4SZ, 14 Gbps/Channel, Twelve Channel Parallel Fiber Optics Modules." http://docs.avagotech.com/docs/AV02-4042EN. AV02-4042EN March 8, 2013.