# A New ATLAS Muon CSC Readout System with System on Chip Technology on ATCA Platform

R. Bartoldus<sup>*a*</sup>, R. Claus<sup>*a*</sup>, N. Garelli<sup>*a*</sup>, R. T. Herbst<sup>*a*</sup>, M. Huffer<sup>*a*</sup>, G. lakovidis<sup>*b*</sup>, K. Iordanidou<sup>*b,c*</sup>, K. Kwan<sup>*d*</sup>, M. Kocian<sup>*a*</sup>, A. J. Lankford<sup>*e*</sup>, P. Moschovakos<sup>*b,f*</sup>, A. Nelson<sup>*e*</sup>, K. Ntekas<sup>*b,f*</sup>, V. Polychronakos<sup>*b*</sup>, L. Ruckman <sup>*a*</sup>, J. Russell <sup>*a*</sup>, M. Schernau<sup>*e*</sup>, D. Su<sup>*a*</sup>, C. Valderanis<sup>*g*</sup>, M. Wittgen <sup>*a*</sup>, S. C. Yildiz<sup>*e*†</sup>

<sup>g</sup> Johannes-Gutenberg-Universitaet Mainz, 55099 Mainz, Germany

E-mail: cenk.yildiz@cern.ch

ABSTRACT: The ATLAS muon Cathode Strip Chamber (CSC) backend readout system has been upgraded during the LHC 2013-2015 shutdown to be able to handle the higher Level-1 trigger rate of 100 kHz and the higher occupancy at Run-2 luminosity. The readout design is based on the Reconfigurable Cluster Element (RCE) concept for high bandwidth generic DAQ implemented on the Advanced Telecommunication Computing Architecture (ATCA) platform. The RCE design is based on the new System on Chip XILINX ZYNQ series with a processor-centric architecture with ARM processor embedded in FPGA fabric and high speed I/O resources. Together with auxiliary memories, all these components form a versatile DAQ building block that can host applications tapping into both software and firmware resources. The Cluster on Board (COB) ATCA carrier hosts RCE mezzanines and an embedded Fulcrum network switch to form an online DAQ processing cluster. More compact firmware solutions on the ZYNQ for high speed input and output fiberoptic links and TTC allowed the full system of 320 input links from the 32 chambers to be processed by 6 COBs in one ATCA shelf. The full system was installed in September 2014. We will present the RCE/COB design concept, the firmware and software processing architecture, and the experience from the intense commissioning for LHC Run 2.

KEYWORDS: Data acquisition concepts; Electronic detector readout concepts (gas, liquid); Modular electronics .

<sup>&</sup>lt;sup>a</sup>SLAC National Accelerator Laboratory, Stanford, CA 94309 USA

<sup>&</sup>lt;sup>b</sup>Brookhaven National Laboratory, Upton, NY 11973, USA

<sup>&</sup>lt;sup>c</sup> University of Athens, 106 79 Athens, Greece

<sup>&</sup>lt;sup>d</sup> The Chinese University of Hong Kong, Hong Kong, China

<sup>&</sup>lt;sup>e</sup>University of California Irvine, Irvine, CA 92697, USA

<sup>&</sup>lt;sup>f</sup> National Technical University of Athens, 159 73 Athens, Greece

<sup>\*</sup>Current Address: Nevis Laboratory, Columbia University, Irvington NY, USA

<sup>&</sup>lt;sup>†</sup>Corresponding author.

# Contents

| 1. | The ATLAS Cathode Strip Chambers           |                                | 1 |

|----|--------------------------------------------|--------------------------------|---|

|    | 1.1                                        | Chambers                       | 1 |

|    | 1.2                                        | On-detector Electronics        | 2 |

| 2. | ATCA Based Generic Data Acquisition System |                                | 2 |

|    | 2.1                                        | Platform                       | 3 |

|    | 2.2                                        | Reconfigurable Cluster Element | 3 |

|    |                                            | 2.2.1 Protocol Plug-In Model   | 4 |

|    | 2.3                                        | Cluster-On-Board Card          | 4 |

| 3. | CSC Run-2 Off Detector Readout System      |                                | 4 |

|    | 3.1                                        | Overview                       | 4 |

|    | 3.2                                        | Integration with ATLAS         | 5 |

|    | 3.3                                        | Performance                    | 7 |

| 4. | l. Conclusion                              |                                |   |

# 1 1. The ATLAS Cathode Strip Chambers

## 2 1.1 Chambers

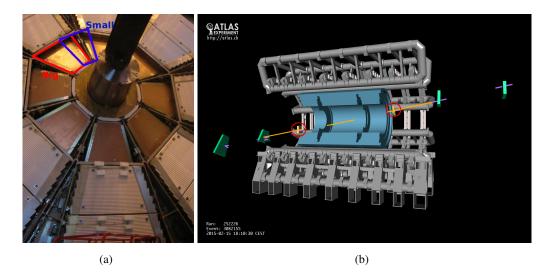

ATLAS[1] Cathode Strip Chambers (CSC) are multiwire proportional chambers designed to detect 3 muons in the high pseudorapidity region:  $2.0 < |\eta| < 2.7^{-1}$ . The system consists of two endcaps 4 placed in the ATLAS Small Wheel (Fig. 1(a)), with 16 chambers in each endcap (8 big, 8 small 5 chambers for seamless coverage). Each chamber has 4 precision ( $\eta$ ) layers with 192 strips in each 6 layer, with pitch 5.31 and 5.36 mm for big and small chambers, and 4 transverse ( $\phi$ ) layers with 48 7 strips in each[2]. As the CSC is very close to the interaction point, there is a high rate of particles 8 going through the chambers, making the readout a challenging task. The position of the CSC in 9 ATLAS can be seen in the display of the cosmic event in Fig. 1(b). 10

<sup>&</sup>lt;sup>1</sup>ATLAS uses a right-handed coordinate system with its origin at the nominal interaction point (IP) in the centre of the detector and the *z*-axis along the beam pipe. The *x*-axis points from the IP to the centre of the LHC ring, and the *y*-axis points upwards. Cylindrical coordinates  $(r, \phi)$  are used in the transverse plane,  $\phi$  being the azimuthal angle around the *z*-axis. The pseudorapidity is defined in terms of the polar angle  $\theta$  as  $\eta = -\ln \tan(\theta/2)$ .

**Figure 1.** (a) ATLAS Small Wheel and the CSC chambers. Small chambers are not seen in the photo as they overlap the big chambers from behind (b) Cosmic event that passes through the CSC detectors on both endcaps. The CSC chambers that were hit are shown in red circles.

#### 1 1.2 On-detector Electronics

The on-detector (or front-end) electronics of the CSC consist of 5 Amplifier Storage Module (ASM-2 II) board for each chamber. For each channel a bipolar pulse with 70 ns peaking time is created 3 and sampled every 50 ns. Each board handles 192 channels and stores the samples on a 144 cell Δ analog memory Switched Capacitor Array (SCA). Each sample is digitized to 12 bits of data, and 5 the front-end can ship two or more of those samples to the off-detector readout system, or so called 6 Readout Driver (ROD) via high speed fiberoptic G-Links. There are a total of 10 G-Links from a 7 chamber to ROD, that carry the data of 96 channels each, and 5 G-Links from ROD to chamber for 8 controlling ASM-II boards[3]. As there is no zero-suppression on the front-end, 5.76kB of data is 9 created per event, creating an input of 4.4Gbits/sec per chamber at 100kHz of Level 1 (L1) trigger 10 rate. The ROD then must perform threshold cut and cluster finding, resulting in a data reduction 11 up to a factor of 60. 12 The Run-1 ROD was limited to run at maximum rate of 75kHz, inducing high deadtime as L1 13

rates went beyond 75kHz[4].

For Run 2, LHC bunch spacing was to be decreased from 50ns to 25ns, energy to be increased to 13 TeV and luminosity increased by having higher number of collisions per bunch crossing. Thus development of a new ROD was needed to handle L1 rate of 100kHz and higher luminosity, that correspond to an average of 50 interactions per beam crossing (compared to average of 20 interactions per beam crossing in the Run 1) [5].

## 20 2. ATCA Based Generic Data Acquisition System

The development of the CSC Run-2 off-detector readout system was based on a generic Data Acquisition (DAQ) concept that has been developed at SLAC since 2007. This section will explain the concept, while the next section will focus on the implementation on the CSC.

## 2 2.1 Platform

Advanced Telecommunication Computing Architecture (ATCA), which was originally developed

for the telecommunication industry, was selected as the host platform for the development of the

<sup>5</sup> DAQ system. It is becoming increasingly popular in high energy physics due to the high speed

<sup>6</sup> backplane, its high availability, hot swapability of boards and the Intelligent Platform Manage-

7 ment Interface (IPMI) based shelf management infrastructure. The backplane is protocol agnostic,

8 providing pin-to-pin connections between cards, allowing the user to select the communication

9 protocol, and the Rear Transition Modules (RTM) allow separating the data processing from the

10 input/output.

12

13

14

15

16

17

18

19

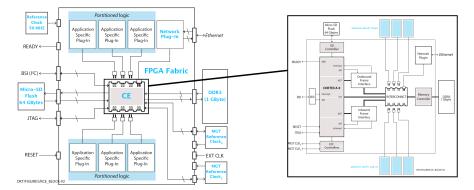

## 11 2.2 Reconfigurable Cluster Element

Reconfigurable Cluster Element (RCE) is the computational element, which is a bundled set of hardware, firmware and software components. It is based on System-On-Chip (SoC) technology (Xilinx ZYNQ) and aims to provide a high performance and efficient use of resources. It has a large FPGA fabric, high speed I/O channels, large memory banks, and a strong interconnect that allows the CPU to access all these resources at high speed. The heart of the RCE is the Cluster Element (CE) and it consists of a dual-core A-9 ARM processor clocked at 800 MHz, 1 GB of DDR3 RAM, and up to 64 GB of flash memory. One has several options to run as operating system such as: Real-Time Executive for Multiprocessor Systems (RTEMS), Linux or bare metal.

Figure 2. RCE and CE

RCEs are implemented in two forms. The Data Processing Module (DPM) RCE is used by the application and consists of a Zynq XC7Z045-2FFG900E with 16 Multi-Gigabit Transceivers (MGT) to perform data processing and high speed I/O. The Data Transfer Module (DTM) RCE consists of Zynq XC7Z030-2FBG484E with 4 MGTs. It is shared among several DPMs, and is responsible for distributing application specific signals to DPMs and managing the networking among the RCEs.

#### 1 2.2.1 Protocol Plug-In Model

2 Protocol Plug-in (PPI) is defined as an arbitrary set of application specific logic, that resides in the

<sup>3</sup> RCE's FPGA fabric and requires the exchange of information with its CE. The plug-ins work with

4 a plug and socket model. There are 8 predefined sockets on the RCE, and specific applications

5 can be implemented in the firmware/software and plugged into these sockets using a wrapper.

<sup>6</sup> The PPIs can either act as an I/O device, defining the data transfer protocol, or take advantage of

7 Digital Signal Processing (DSP) tiles and combinatoric logic of the FPGA to process data. The

8 whole model allows one to implement hardware solutions in firmware/software with much lower

9 footprint and power consumption.

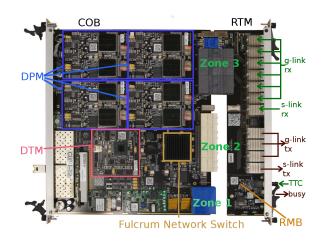

### 10 2.3 Cluster-On-Board Card

The carrier board developed to host RCEs is called the Cluster-On-Board (COB) card. It hosts up to 8 processing RCEs on 4 DPMs and one control RCE on DTM.

The COB has a Cluster Interconnect (CI) section that consists of an embedded 24-port 10GbE 13 low latency Fulcrum switch as its main feature. A network connection at the front panel Ethernet 14 port of a single COB in the ATCA shelf can be distributed to all RCEs on all COBs on the shelf. 15 The COB has 3 rear connection zones. The Zone 1 connector is used for power and management, 16 the zone 2 connector is the data transport interface for communicating between boards, and the 17 zone 3 provides connectivity between COB and RTM in a 96-channel high density connector. This 18 arrangement allows the active processing elements to remain on the COB as generic resources 19 while the RTM only hosts the system specific configuration of I/O connection ports. The COB can 20

<sup>21</sup> be seen in Fig. 3.

## 22 **3. CSC Run-2 Off Detector Readout System**

## 23 **3.1 Overview**

The CSC Run-2 ROD is an implementation of the RCE concept. The COBs that host the RCEs 24 reside in a standard 6 slot ATCA shelf, each COB hosting three active DPM bays (6 RCE, each 25 related to a single chamber), and one DTM bay (One RCE). The CSC specific RTM is the physical 26 interface between the chambers and the ATLAS Trigger and DAO (TDAO) system. For each DPM 27 RCE, there are 15 G-Link fiber connections to a CSC chamber, 10 to receive data from chambers 28 and 5 to send control signals to the on-detector electronics. Each DPM RCE also has two S-Links 29 to the Read Out Subsystem (ROS); one to receive commands, and one to transmit formatted event 30 fragments. Finally, for each COB, a single Busy signal is sent to the ATLAS Busy Module to halt 31 trigger in case any of the RCEs are busy; Trigger, Timing and Control (TTC) signal is received 32 from the TTCex module to be distributed to all DPM RCEs. 33 Each DPM RCE handles a single chamber and runs RTEMS as OS. There is a dedicated 34

firmware logic called the SCA controller for requesting 4 or more time slices from the front-end whenever there is a L1 trigger. The G-link PPI is used to decode the data, which is immediately sent to the feature extraction (FEX). The FEX PPI performs the threshold cut, while the FEX software

<sup>38</sup> does the clustering and builds the fragments according to the CSC data format. The formatted data

Figure 3. The CSC COB and RTM

is sent out to the ROS, using the S-Link PPI. The interaction with the TTC system is done via TTC

Receive and Busy PPIs, with the use of the DTM, which is shared by all DPMs in the COB.

The DTM runs Arch Linux as OS, and its main responsibilities are: managing the network traffic; combining all the Busy signals from the DPM RCEs; and directing it to the Busy output of the RTM, and receiving the TTC signal from the TTC input of the RTM and distributing it to the DPMs. Furthermore, a TTC emulator functionality is implemented in the DTM, allowing it to reproduce the functionality of the Local Trigger Processor (LTP) as an internal TTC source so that

<sup>8</sup> the COB can be a more versatile standalone system.

The G-Link PPI, S-Link PPI, and the DTM's ability to handle the TTC signal are perfect examples of how the large FPGA fabric is used to replace classical hardware solutions. For G-Links and S-Links, G-link ASICs and High-speed Optical Link (HOLA) cards are replaced by DPM firmware, while for the TTC handling, the former 9U VME TTC Interface Module is replaced by DTM firmware. All this allows not only to reduce the footprint, so that one can squeeze more components in unit space, but also to have much lower power consumption, so that these components don't generate more heat that system can handle.

The control processor (CP) is a server PC with dual network interface to act as a gateway between the ATCA shelf and the external world, interacting with both sides. Only a single COB is connected to the CP via a dedicated switch, while the network assignment of the remaining COBs are done internally in the ATCA fabric.

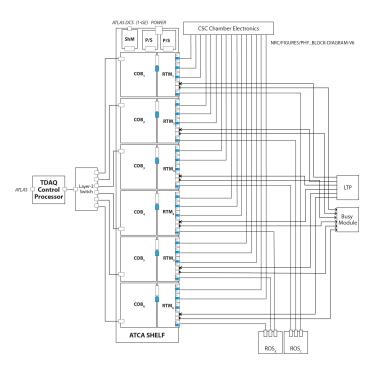

# 20 3.2 Integration with ATLAS

The system is integrated with the TDAQ infrastructure and Detector Control System (DCS). The ATLAS TDAQ is collection of systems that combine the triggering, event selection, data collection from detectors, event building and data recording. With all the filtering, the collisions at 40MHz are filtered down to 1kHz to be written to storage. On the other hand the DCS allow one to monitor and control the detectors and experimental infrastructure. 1 The TTC and Busy transmission between the CSC and the ATLAS Central Trigger Processor

<sup>2</sup> (CTP) is done through the intermediate unit LTP via the connections on the RTM.

<sup>3</sup> The formatted data is sent to the ROS via S-Links, where it is buffered, and sent out for event

<sup>4</sup> building upon request of High Level Trigger (HLT).

Figure 4. Schematics of the CSC off-detector readout system connections

The interaction with the ATLAS data taking finite state machine is done on the CP, which 5 communicates with the RCE in a server/client model using Remote Procedure Calls (RPC) as the 6 inter-process communication method. During an ATLAS data taking, each RCE is represented by 7 a separate process in the CP. The CP can send configuration parameters to RCEs, and retrieve the 8 status of each RCE. In addition, the status of a complete set of internal state registers are gathered and sent to the Information Service (IS is a ATLAS service that is used to share variables between 10 DAQ applications, and log them) every 5 seconds for debugging and diagnosis. The CSC system 11 makes use of ATLAS TDAQ automatic recoveries, such as resynchronizing an RCE during data 12 taking, or reconfiguring the whole system. 13

For the pedestal runs, a dedicated histogramming service runs on the FEX software to perform a fast calibration for threshold calculation.

Finally, the health of the ATCA shelf, COBs and RCEs is monitored in DCS via the shelf manager on the ATCA making use of the IPMI Controller of the COB based on the Pigeon Point System solution. Informations such as power supply status, COB health or temperature at several points on the shelf is monitored, with specific alarms implemented to warn experts if any of the parameters go out of working limits. All the connections between CSC off-detector readout system, CSC detector, LTP, ROS and the network are shown in Fig. 4.

## 3 3.3 Performance

<sup>4</sup> Performance depends on three fundamental components of the system: front end, FEX and ROS.

The front-end performance has not changed in the Run 2, because it depends on the buffering

capacity and G-link bandwidth, which limits the system to 111 kHz for 4 samples readout.

The data transfer speed to ROS depends on the Read Out Link (ROL) output bandwidth, which

was doubled by expanding to twice as many actual S-links. The S-link PPI driving at 100MHz has

also extended the individual S-link capacity to a maximum of 200MB/s.

The FEX performance is the main improvement in the Run-2 readout system. FEX on the new system is implemented both in the firmware and software, threshold cut being done on the FEX PPI, while clustering and formatting is done on the software. FEX uses On-Chip Memory (OCM) for faster access, and makes use of assembler for the most performance critical parts.

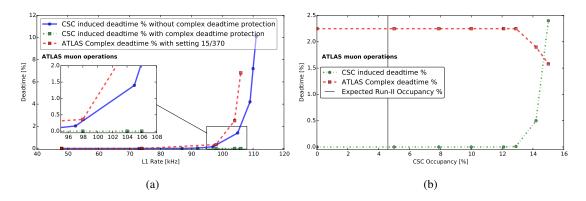

As the triggers are random during data taking, detector readout systems should be protected against a burst of triggers that would cause it to run out of front end buffers. In ATLAS, a complex deadtime mechanism that works in a leaky bucket model is used to provide this protection[6]. ATLAS complex deadtime system in Run 2 can have 4 different complex deadtime settings, where each setting is represented by two parameters: "bucket size" and "leak rate". The CSC has adapted the setting 15/370 that was already used by other systems, thus bringing no extra complex deadtime to data taking.

With the L1 rate of 100kHz, and expectation of 50 interactions per beam crossing (which 21 corresponds to 4.6% occupancy in the CSC) the readout system is required to perform without 22 inducing any additional deadtime. ATLAS in Run 2 so far hasn't reached such L1 rates and lu-23 minosities. Therefore, for the performance tests random triggers are generated on CTP to test the 24 system, and the CSC occupancy is set using specific threshold patterns that simulates fake clusters. 25 The system was tested with L1 rates up to 106kHz at Run-2 occupancy using the CSC complex 26 deadtime setting, and no additional deadtime was observed due to the CSC. Furthermore, fixing the 27 L1 rate at 100kHz, the CSC occupancy was varied from 0 to 15%, and no dead time was observed 28 due to the CSC until 14% occupancy, which is much higher than the Run-2 expectation for the CSC 29

30 (Fig. 5).

## 31 **4.** Conclusion

32 With the increased luminosity and L1 rate in ATLAS in Run 2, a new readout system was developed

<sup>33</sup> for the CSC. It is the first deployment of ATCA and RCE based modern DAQ systems in ATLAS.

<sup>34</sup> The main reason for development is performance improvements. The system features a powerful

<sup>35</sup> hardware, and matching firmware/software framework, to handle high rates and luminosities. The

<sup>36</sup> CSC Run-2 readout system has been running stably to date and has demonstrated the main goal of

running at 100kHz and Run 2 occupancies with no deadtime.

**Figure 5.** (a) The CSC induced deadtime and complex deadtime with Run-2 occupancy of 4.6%. With the complex deadtime protection of the CSC setting 15/370, no additional deadtime is induced by the CSC even at the maximum possible rate allowed by the complex deadtime setting. Without any protection, the CSC still runs without causing deadtime until 96kHz. Note that dashed and solid lines are obtained from two separate tests (b) The CSC induced deadtime vs. the occupancy of the CSC for L1 rate of 100 kHz. The CSC starts to induce deadtime in much higher occupancies compared to the expected occupancy in Run 2.

#### 1 Acknowledgments

- <sup>2</sup> We would like to thank our colleagues from the SLAC Advanced Instrumentation Research Divi-

- <sup>3</sup> sion for the development of the RCE, and for the implementation and support for the firmware/software

- <sup>4</sup> of the CSC off-detector readout system. We would also like thank to the ATLAS Muon commu-

- 5 nity for their help. This work has been supported by the U.S. Department of Energy and National

- 6 Science Foundation.

#### 7 References

- 8 [1] ATLAS Collaboration *The ATLAS Experiment at the CERN Large Hadron Collider*, 2008 JINST 3

9 S08003.

- [2] T. Argyropoulos et al., *Cathode Strip Chambers in ATLAS: Installation, Commissioning and in Situ Performance, IEEE Transactions on Nuclear Science* 56 (2009) 1568

- 12 [3] I. G. Eschrich et al., Readout Electronics of the ATLAS Muon Cathode Strip Chambers, in proceedings

- of *Topical Workshop on Electronics for Particle physics*, September 15–19, 2008, Naxos, Greece

- [4] R. Murillo et al., Software design of the ATLAS Muon Cathode Strip Chamber ROD, J. Phys.: Conf.

Ser. 396 (2012) 012031

- [5] N. Garelli et al., *The evolution of the Trigger and Data Acquisition System in the ATLAS experiment*, J.

*Phys.: Conf. Ser.* 513 (2014) 012007

- 18 [6] M. Stockton et al., The ATLAS Level-1 Central Trigger, J. Phys.: Conf. Ser. 331 (2011) 022041