# The Evolution of the Region of Interest Builder for the ATLAS Experiment at CERN

# B. Abbott<sup>*a*</sup>, R. Blair<sup>*b*</sup>, G. Crone<sup>*c*</sup>, B. Green<sup>*d*</sup>, J. Love<sup>*b*</sup>, J. Proudfoot<sup>*b*</sup>, O. Rifki<sup>*a*\*</sup>, W. P. Vazquez<sup>*d*</sup>, W. Vandelli<sup>*e*</sup>, J. Zhang<sup>*b*</sup>

<sup>a</sup> Department of Physics and Astronomy, University of Oklahoma, Norman, United States

<sup>b</sup> High Energy Physics Division, Argonne National Laboratory, Argonne, United States

<sup>c</sup> Department of Physics and Astronomy, University College London, London, United Kingdom

<sup>d</sup> Department of Physics, Royal Holloway University of London, Surrey, United Kingdom

<sup>e</sup> CERN, Geneva, Switzerland

*E-mail:* othmane.rifki@cern.ch

ABSTRACT: The ATLAS detector uses a real time selective triggering system to reduce the high interaction rate from 40 MHz to its data storage capacity of 1 kHz. A hardware first level (L1) trigger limits the rate to 100 kHz and a software high level trigger (HLT) selects events for offline analysis. The HLT uses the Regions of Interest (RoIs) identified by L1 and provided by the Region of Interest Builder (RoIB). The current RoIB is a custom VMEbus based system that operated reliably since the first run of the LHC. Since the LHC will reach higher luminosity and ATLAS will increase the complexity and number of L1 triggers, it is desirable to have a more flexible and more operationally maintainable RoIB in the future. In this regard, the functionality of the multicard VMEbus based RoIB is being migrated to a PC based RoIB with a PCI-Express card. Testing has produced a system that achieved the targeted rate of 100 kHz.

KEYWORDS: Data acquisition; Event building; PCI-express; Region of Interest Builder; ATLAS.

<sup>\*</sup>Corresponding author.

## Contents

| 1. | Intr              | roduction                          | 1 |

|----|-------------------|------------------------------------|---|

| 2. | VMEbus based RoIB |                                    | 2 |

|    | 2.1               | Hardware implementation            | 2 |

|    | 2.2               | System Performance and Evolution   | 3 |

| 3. | PC                | based RoIB                         | 4 |

|    | 3.1               | The Common Readout Receiver Card   | 4 |

|    | 3.2               | Readout System Firmware & Software | 4 |

|    | 3.3               | RoIB Software                      | 5 |

| 4. | Prototype Tests   |                                    | 6 |

|    | 4.1               | Standalone Tests                   | 6 |

|    | 4.2               | Full System Tests                  | 7 |

| 5. | Out               | look                               | 7 |

### 1 1. Introduction

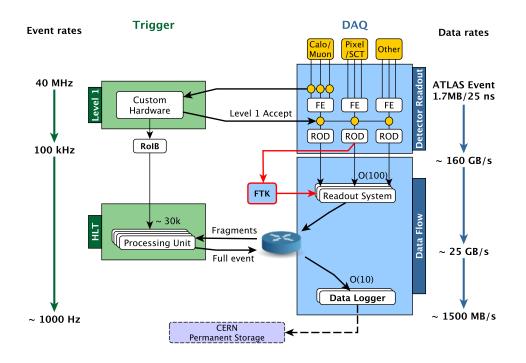

<sup>2</sup> The ATLAS [1] detector's data acquisition system, illustrated in Figure 1, makes use of a multi-

<sup>3</sup> tiered trigger to reduce bandwidth from the LHC proton bunch crossing rate of 40 MHz to the

<sup>4</sup> 1 kHz written to disk [2]. The first tier (Level-1 or L1) [3], implemented in real time with custom

5 electronics, makes an early event selection to determine if any objects of interest are present and

<sup>6</sup> reduces the data flow to 100 kHz. The second tier, referred to as the High Level Trigger (HLT) [4],

7 is implemented on a commodity computing cluster running custom triggering software. The HLT

<sup>8</sup> uses information from the hardware based L1 system to guide the retrieval of information from the

9 Readout System (ROS) [5].

Jet, electromagnetic and tau clusters, missing transverse momentum  $(E_T^{\text{miss}})$ ,  $\Sigma E_T$ , jet  $E_T$ , and 10 muon candidate information from L1 determine detector Regions of Interest (RoIs) that seed HLT 11 processing. These RoIs are provided to the HLT by a custom VMEbus based system, referred to 12 as the Region of Interest Builder (RoIB) [6]. The RoIB collects data from L1 trigger sources and 13 assembles the data fragments into a complete record of L1 RoIs. These RoIs are made available 14 to the HLT to initiate event processing. In order to improve maintainability and scalability, and 15 to minimize the amount of custom hardware needing to be supported, the RoIB will be imple-16 mented using commodity server hardware and an interface technology already deployed within the 17 ATLAS Trigger and Data Acquisition (TDAQ) system. The approach of implementing the RoIB 18 functionality in software has been investigated in the past and the conclusion at that time was that a 19

Figure 1. ATLAS TDAQ Architecture.

software based approach is possible but requires a higher rate readout card [7]. Since data readout 20 cards operating at high rates became available and the capabilities of computers have improved 21 with the increase in CPU clock speed and number of cores, it became possible to implement the 22 RoIB functionality using a PC based approach. The PC based RoIB must duplicate the functional-23 ity of the VMEbus based RoIB which means that the PC based solution must receive and assemble 24 the individual L1 fragments, and pass them as a single L1 result to the HLT. Modern computers 25 have multicore CPU architectures with the possibility of running multi-threaded application, a fea-26 ture which is being fully exploited in the RoIB software to achieve the desired performance of 100 27 kHz over 12 input links for fragment sizes of 400 bytes. This paper describes the evolution of the 28 RoIB from the VMEbus based system to the PC based system and gives details on the hardware, 29 firmware, and software designs used to achieve the full RoIB functionality. 30

### 31 2. VMEbus based RoIB

#### 32 2.1 Hardware implementation

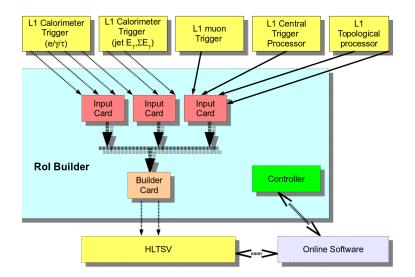

<sup>33</sup> The RoIB is implemented as a custom 9U VMEbus system that includes a controller which con-

<sup>34</sup> figures and monitors the system along with custom cards that receive and assemble the event frag-

- <sup>35</sup> ments and send them to the HLT. Figure 2 shows a block of the RoIB and its connection to external

- 36 systems.

**Figure 2.** Block scheme of the RoI Builder and overview of connections to external systems. The custom input and builder cards and the controller, a commercially available single board computer, are installed in a single 9U VMEbus crate. The controller connects to the Control Network to interact with the rest of the data acquisition system.

The RoIB contains four input cards and uses one builder card in the Run-2 configuration. Each 37 input card accepts three inputs from L1 subsystems. The builder card assembles the input data of 38 the events and passes the results via two optical links to another receiver card in a PC running the 39 HLT supervisor (HLTSV) application. The receiver card in the HLTSV is a TILAR card [9] that 40 implements four PCIe Gen1 lanes to interface with the two optical links. The HLTSV manages the 41 HLT processing farm by using L1 results provided by the RoIB, retrieves events from the ROS, 42 assigns events to HLT farm nodes, and handles event bookkeeping including requesting removal of 43 data from ROS storage when no longer required. 44 The fragments received by the RoIB are identified by a 32 bit identifier, the extended L1 ID 45

(L1ID). The RoIB input cards use the L1ID and the number of outputs enabled to assign keys to the various fragments and send them to the output channel in the builder card that was assigned that key value. The input data is transferred over a custom J3 backplane. The backplane operates at 20 MHz and transfers 16 data bits per clock cycle simultaneously for up to 12 inputs. The total maximum data throughput is therefore 480 MB/s, 40 MB/s per input. The maximum size of any single fragment is limited to 512 bytes imposed by resources available in the FPGA firmware. The

<sup>52</sup> current RoIB input links are listed in Table 1.

#### 53 2.2 System Performance and Evolution

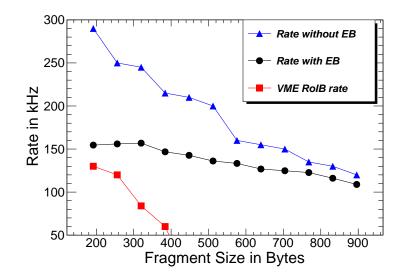

The custom VMEbus based RoIB operated reliably during the first run of the LHC, however, it is desirable to have a more flexible RoIB. In addition, the RoIB is getting close to its design limitation, as seen in Figure 6. For fragments of 400 bytes and inputs from eight L1 systems, referred to as channels, the current RoIB rate limit is 60 kHz which is below the required 100 kHz at L1. While the current fragment size coming from L1 are around 160 bytes, the sizes are expected to grow due to the increase of instantaneous luminosity and the complexity of L1 triggers. The current VMEbus

| Source                                              | Links |

|-----------------------------------------------------|-------|

| Central Trigger Processor (CTP)                     | 1     |

| L1 calorimeters $(e/\gamma, \tau, jet, \Sigma E_T)$ | 6     |

| Muon Trigger to CTP Interface (MUCTPI)              | 1     |

| Topological processor (L1Topo)                      | 2     |

| Spare                                               | 2     |

Table 1. L1 input sources to the RoIB.

system will be replaced by a PCI-express card hosted in the HLTSV PC with the possibility to

upgrade the commodity hardware (e.g. ability to upgrade CPUs). The new configuration simplifies

the readout architecture of ATLAS. The targeted rate for event building is 100 kHz over 12 input

channels for fragment sizes in the order of 400 bytes.

# 64 3. PC based RoIB

A custom PCIe card developed by the ALICE collaboration, the Common ReadOut Receiver Card (C-RORC) [10], was deployed as an upgraded detector readout interface within the ATLAS ROS with ATLAS specific firmware and software called the RobinNP [11]. The new PC based RoIB uses the RobinNP firmware and a dedicated API to facilitate the implementation of the RoIB functionality on a commodity PC. In this section, we describe the C-RORC hardware as well as the RobinNP firmware, API, and the event building software.

# 71 3.1 The Common Readout Receiver Card

The C-RORC implements 8 PCIe Gen1 lanes with 1.4 GB/s bandwidth to the CPU fed via 12 optical links each running 200 MB/s on 3 QSFP transceivers. It utilizes a single Xilinx Virtex-6 series FPGA that handles data input from the 12 links and buffers the data in two on-board DDR3 memories. It is also capable of processing and initiating DMA transfer of event data from the onboard memory to its host PC's memory. The major components of the C-RORC are annotated in the picture shown in Figure 3.

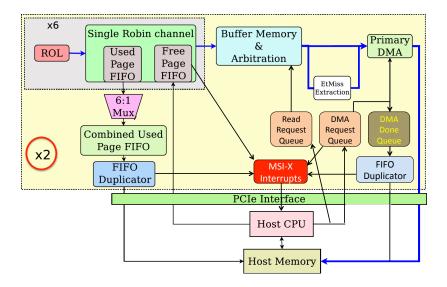

# 78 **3.2 Readout System Firmware & Software**

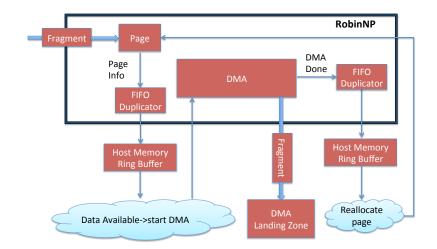

The RobinNP firmware used for the RoIB is identical to that used in the ATLAS ROS[5]. As shown 79 in the schematic of Figure 4, the logic is divided into two functional blocks, known as sub-ROBs, 80 each servicing six input links and one DDR3 memory module. Event data fragments arriving via 81 a link are subjected to a range of error checks before being stored in the memory module for the 82 relevant sub-ROB. At the same time a token representing the address of a region of the memory, 83 referred to as a page, is passed to a listening software process via a 'FIFO duplicator'. To avoid 84 a costly read across the PCIe bus, data is continuously streamed from firmware to software via 85 a chain of firmware and software FIFOs. Notification of new data arriving in the software FIFO 86 is managed via coalesced interrupts to allow for efficient use of CPU resources. For the RoIB 87 application, the receipt of page information immediately triggers a DMA of fragment data from the 88 RobinNP memory into the host PC memory. The fragments are then passed via a queue (one per 89

Figure 3. Photo of the C-RORC board with the major components and features annotated [11].

**Figure 4.** RobinNP firmware organization and flow of data from host CPU to the firmware (by means of programmed I/O) and from the firmware to the host memory (by means of DMA).

sub-ROB) to the RoIB process along with any relevant fragment error information. A schematic of this shortened dataflow path is presented in Figure 5. The API for the RoIB process consists of these queues, return queues for processed pages now available for re-use and a configuration interface. The software is implemented with multiple threads each handling specific tasks such as supply of free pages, receipt of used pages, DMA control and bulk receipt of fragment data.

### 95 3.3 RoIB Software

<sup>96</sup> The HLTSV is a multi-threaded application that obtains a L1 result from a variety of possible input

- <sup>97</sup> sources and exchanges information with the rest of the HLT computing farm. For the RoIB, the

- <sup>98</sup> L1 source is a RobinNP interface that performs fragment assembly and is used as a plug-in to

Figure 5. Layout of the readout system firmware and software specific to the RoIB.

the HLTSV application. The RobinNP plug-in has two receive threads, each thread services six qq channels by pulling fragments from the RobinNP on-board memories to the host PC. Fragments 100 with the same L1ID are copied to a contiguous memory space and a queue of completed events 101 is prepared. Upon request by the HLTSV, a pointer to the contiguous memory space is passed 102 back to the HLTSV process for further handling. In order to optimize concurrent access to RoIB 103 data structures, containers from the Intel threading building block (TBB) library were used. These 104 containers allow multiple threads to concurrently access and update items in the container while 105 maintaining high performance. 106

# 107 **4. Prototype Tests**

In order to understand the requirements for the underlying server PC, a validation system based 108 on Intel(R) Xeon(R) CPU E5-1650 v2 @ 3.5 GHz with six cores is being used to perform tests 109 of the PC based RoIB. The goal is to perform software based fragment assembly at a rate of 100 110 kHz over 12 channels for a typical fragment size of 400 bytes. The current system offers flexibility 111 in terms of the fragment size allowed which was not the case in the VMEbus based RoIB. The 112 initial tests were performed with a standalone application that implements a minimal interface for 113 event building. Once the system was validated, the relevant code modules were integrated into an 114 HLTSV process running within the full ATLAS TDAQ software suite with appropriately scaled test 115 hardware to represent the remaining elements of the system. 116

#### 117 4.1 Standalone Tests

The goal was to test input/output bandwidth limitations of the RobinNP and the rate of event building. Initial performance testing used a standalone RobinNP application and an external source that emulates the L1 trigger data in the form of 32-bit word fragments with 12 channels. In this test, the host PC was running the assembly routine with a single threaded application. Figure 6 shows the input rate without event building as a function of fragment size. For 400 byte fragments the input rate to the RobinNP is 215 kHz. The same figure shows the event building rate which is

**Figure 6.** Rate as a function of the fragment size (in bytes) with external source that emulates the L1 trigger input. The rates shown are for the input rate to the RobinNP without event building (EB) (triangle), rate with EB (circle), and for comparison, the current VMEbus RoIB rate is also shown (square).

124 150 kHz. This performance shows that the event building at the required rate of 100 kHz with 12

125 channels is achievable in a standalone application.

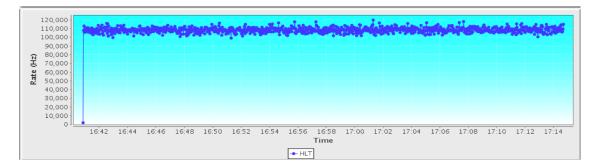

#### 126 4.2 Full System Tests

Since the HLTSV is performing tasks other than the event building, there is overhead associated 127 with additional operations that reduces the performance. For this reason, we use the full ATLAS 128 TDAQ software in a test environment that emulates the major components of the ATLAS data ac-129 quisition system shown in Figure 1. The setup includes an emulated input from L1 trigger sources, 130 the HLTSV and other PCs to simulate the HLT computing farm, and the ROS that buffers the full 131 event data. In this test setup, an external source sends data that emulates L1 RoIs via 12 links 132 connected to the RobinNP hosted by the HLTSV. When the HLTSV requests a built RoI event, the 133 software RoIB plug-in provides the RoI event which will be used to seed requests for the event 134 data to be processed. Figure 7 shows an event building rate of 110 kHz measured with 400 byte 135 fragments with the HLTSV application in a setup close to the ATLAS TDAQ system. 136

#### 137 5. Outlook

The RoIB will evolve from the VMEbus based system to the PC based system using a PCI-Express card and firmware shared with the ATLAS ROS. The new system will add flexibility and improve maintainability of the ATLAS TDAQ system. As the technology evolves, the PCs and CPUs can be upgraded and more channels can be included by adding more RobinNP cards while maintaining high readout rates. A full integration test of the readout performance of the ATLAS TDAQ system with the PC based RoIB will be performed during the 2015-2016 LHC winter shutdown in preparation for a system evolution.

**Figure 7.** Screenshot of a monitoring tool which shows the HLTSV processing rate using the ATLAS TDAQ software .

#### 145 **References**

- [1] ATLAS Collaboration, *The ATLAS experiment at the CERN Large Hadron Collider*, 2008 *JINST* 3

S08003.

- [2] N. Garelli (on behalf of the ATLAS Collaboration), *The Evolution of the Trigger and Data Acquisition* System in the ATLAS Experiment, J. Phys.: Conf. Ser. 513 (2014) 012007.

- 150 [3] ATLAS Collaboration, ATLAS Level-1 Trigger: Technical Design Report, ATLAS-TDR-12, 1998

- [4] ATLAS Collaboration, *ATLAS, High-Level Trigger, Data Acquisition and Controls* https://cds.cern.ch/record/616089 *CERN/LHCC/2003-022*, CERN Geneva 2003.

- [5] A. Borga et al., *Evolution of the ReadOut System of the ATLAS experiment*, in proceedings of

*Technology and Instrumentation in Particle Physics 2014*, June, 2–6, 2014 Amsterdam, the

Netherlands PoS (TIPP2014) 205.

- 156 [6] R. Blair et al., The ATLAS High Level Trigger Region of Interest Builder, 2008 JINST 3 P04001

- 157 [7] R. E. Blair et al., ATLAS TDAQ dataflow: Software RoI builder status report, ATL-DQ-TR-0020, 2012

- 158 [8] S. Ask et al., The ATLAS central level-1 trigger logic and TTC system, 2008 JINST **3** P08002.

- [9] CERN, http://www.cerntech.hu/products/15-tilar-express.html, October 15, 2015

- [10] H. Engel, U. Kebschull (For the ALICE Collaboration), *Common read-out receiver card for ALICE Run2*, 2013 *JINST* 8 C12016.

- [11] A. Borga et al., *The C-RORC PCIe Card and its Application in the ALICE and ATLAS Experiments*,

2015 JINST 10 C02022.