# Design of a Hardware Track Finder (Fast Tracker) for the ATLAS Trigger

Cavaliere V.,<sup>17</sup>

Adelman J.,<sup>11</sup> Albicocco P.,<sup>4</sup> Alison J.,<sup>2</sup> Ancu L. S.,<sup>5</sup> Anderson J. ,<sup>1</sup> Andari N.,<sup>11</sup> Andreani A.,<sup>9a,9b</sup> Andreazza A.,<sup>9a,9b</sup> Annovi A.,<sup>14a</sup> Antonelli M.,<sup>4</sup> Asbah N. ,<sup>3</sup> Atkinson M.,<sup>17</sup> Baines J.,<sup>15</sup> Barberio E.,<sup>8</sup> Beccherle R.,<sup>14a,7</sup> Beretta M.,<sup>4</sup> Bertolucci F.,<sup>14a,14b</sup> Biesuz N. V.,<sup>14a,14b</sup> Blair R.,<sup>1</sup> Bogdan M.,<sup>2</sup> Boveia A.,<sup>2</sup> Britzger D.,<sup>3</sup> Bryant P.,<sup>2</sup> Burghgrave B.,<sup>11</sup> Calderini G.,<sup>7</sup> Camplani A.,<sup>9a,9b</sup> Cavasinni V.,<sup>14a,14b</sup> Chakraborty D.,<sup>11</sup> Chang P.,<sup>17</sup> Cheng Y.,<sup>2</sup> Citraro S.,<sup>14a,14b</sup> Citterio M.,<sup>9a</sup> Crescioli F.,<sup>7</sup> Dawe N.,<sup>8</sup> Dell'Orso M.,<sup>14a,14b</sup> Donati S.,<sup>14a,14b</sup> Dondero P.,<sup>12a,12b</sup> Drake G.,<sup>1</sup> Gadomski S.,<sup>5</sup> Gatta M.,<sup>4</sup> Gentsos C.,<sup>16</sup> Giannetti P.,<sup>14a</sup> Gkaitatzis S.,<sup>16</sup> Gramling J.,<sup>5</sup> Howarth J. W.,<sup>3</sup> lizawa T.,<sup>18</sup> Ilic N.,<sup>19a,19b</sup> Jiang Z.,<sup>19a,19b</sup> Kaji T.,<sup>18</sup> Kasten M.,<sup>17</sup> Kawaguchi Y.,<sup>18</sup> Kim Y. K.,<sup>2</sup> Kimura N.,<sup>16</sup> Klimkovich T.,<sup>6</sup> Kolb M.,<sup>6</sup> Kordas K,<sup>16</sup> Krizka K.,<sup>2</sup> Kubota T.,<sup>8</sup> Lanza A.,<sup>12a</sup> Li H. L.,<sup>2</sup> Liberali V.,<sup>9a,9b</sup> Lisovyi M.,<sup>6</sup> Liu L.,<sup>17</sup> Love J.,<sup>1</sup> Luciano P.,<sup>14a,14b</sup> Luongo C.,<sup>14a,14b</sup> Magalotti D.,<sup>5,11,14</sup> Maznas I.,<sup>17</sup> Meroni C.,<sup>10a</sup> Mitani T.,<sup>19</sup> Nasimi H.,<sup>15a</sup> Negri A.,<sup>13a,13b</sup> Neroutsos P.,<sup>16</sup> Neubauer M.,<sup>17</sup> Nikolaidis S.,<sup>16</sup> Okumura Y.,<sup>3</sup> Pandini C.,<sup>8</sup> Petridou C.,<sup>16</sup> Piendibene M.,<sup>15a,15b</sup> Proudfoot J.,<sup>1</sup> Rados P.,<sup>9</sup> Roda C.,<sup>15a,15b</sup> Rossi E.,<sup>15a,15b</sup> Sakurai Y.,<sup>19</sup> Sampsonidis D.,<sup>16</sup> Saxon J.,<sup>3</sup> Schmitt S.,<sup>4</sup> Schoening A.,<sup>7</sup> Shochet M.,<sup>3</sup> Shojaii S.,<sup>10a,10b</sup> Soltveit H.,<sup>7</sup> Sotiropoulou C. L.,<sup>15b</sup> Stabile A.,<sup>10a</sup> Swiatlowski M.,<sup>3</sup> Tang F.,<sup>3</sup> Taylor P. T.,<sup>9</sup> Testa M.,<sup>5</sup> Tompkins L.,<sup>20a,20b</sup> Vercesi V.,<sup>13a</sup> Volpi G.,<sup>14a,14b</sup> Wang R.,<sup>1</sup> Watari R.,<sup>19</sup> Webster J.,<sup>1</sup> Wu X.,<sup>6</sup> Yorita K.,<sup>19</sup> Yurkewicz A.,<sup>12</sup> Zeng J. C.,<sup>17</sup> Zhang J.,<sup>1</sup> Zou R.,<sup>3</sup>

1 High Energy Physics Division, Argonne National Laboratory, Argonne IL, United States of America

- 2 Enrico Fermi Institute, University of Chicago, Chicago IL, United States of America

- 3 DESY, Hamburg and Zeuthen, Germany

- 4 INFN Laboratori Nazionali di Frascati, Frascati, Italy

- 5 Section de Physique, Université de Genève, Geneva, Switzerland

- 6 Physikalisches Institut, Ruprecht-Karls-Universität Heidelberg, Heidelberg, Germany

- 7 Laboratoire de Physique Nucléaire et de Hautes Energies, UPMC and Université Paris-Diderot and CNRS/IN2P3, Paris, France

- 8 School of Physics, University of Melbourne, Victoria, Australia

- 9 (a) INFN Sezione di Milano; (b) Dipartimento di Fisica, Università di Milano, Milano, Italy

- 10 Also at Università di Modena e Reggio Emilia, Italy

- 11 Department of Physics, Northern Illinois University, DeKalb IL, United States of America

- 12 (a) INFN Sezione di Pavia; (b) Dipartimento di Fisica, Università di Pavia, Pavia, Italy

- 13 Also at INFN Sezione di Perugia, Perugia, Italy

- 14 (a) INFN Sezione di Pisa; (b) Dipartimento di Fisica E. Fermi, Università di Pisa, Pisa, Italy

- 15 Particle Physics Department, Rutherford Appleton Laboratory, Didcot, United Kingdom

- 16 Department of Physics, Aristotle University of Thessaloniki, Thessaloniki, Greece

- 17 Department of Physics, University of Illinois, Urbana IL, United States of America

- 18 Waseda University, Tokyo, Japan

- 19 (a) SLAC National Accelerator Laboratory, Stanford CA, United States of America; (b) Department of Physics, Stanford University, Stanford CA, United States of America

viviana.cavaliere@cern.ch

ABSTRACT: The use of tracking information at the trigger level in the LHC Run II period is crucial for the trigger and data acquisition system and will be even more so as contemporary collisions that occur at every bunch crossing will increase in Run III. The Fast TracKer is part of the ATLAS trigger upgrade project; it is a hardware processor that will provide every Level-1 accepted event (100 kHz) and within 100 $\mu$ s, full tracking information for tracks with momentum as low as 1 GeV. Providing fast, extensive access to tracking information, with resolution comparable to the offline reconstruction, FTK will help in precise detection of the primary and secondary vertices to ensure robust selections and improve the trigger performance.

KEYWORDS: ATLAS, Trigger, tracking, hardware, FPGA.

<sup>\*</sup>Speaker, UIUC, CERN

## Contents

| 1. | Introduction                                       |                                               | 1 |

|----|----------------------------------------------------|-----------------------------------------------|---|

|    | 1.1                                                | FTK Challenges                                | 2 |

| 2. | The FTK hardware processing chain                  |                                               | 2 |

|    | 2.1                                                | Clustering reconstruction and data formatting | 2 |

|    | 2.2                                                | Processing Units                              | 3 |

|    | 2.3                                                | Second Stage Board and Interface to HLT       | 4 |

| 3. | 3. Stage of Integration and Commissioning schedule |                                               | 5 |

| 4. | . Conclusions                                      |                                               | 6 |

# 1. Introduction

The Large Hadron Collider (LHC) in Run-I, using only a fraction of the full LHC potential, was remarkably successful: the Higgs boson's discovery [2, 3] and strong limits on new physics phenomena. After a shut-down period of almost 2 years, the LHC will be able to provide 13 TeV collisions, almost twice the energy of the previous run, expecting to collect a luminosity of 40-60  $fb^{-1}$  per year, therefore increasing the discovery potential of the experiment. Greater instantaneous luminosity will provide an average number of contemporary collisions (pileup) up to 80. In order to achieve the required on-line data reduction in the trigger and data acquisition system (TDAQ), the LHC experiments are expected to increase the use of silicon detector information, reconstructing the track trajectories close to the interaction points, and allowing to distinguish between the contribution of each pileup collision. For this reason, the ATLAS experiment [1] has decided to include, within the existing multilevel trigger architecture, an electronic system designed to perform full track reconstruction from the hits observed in the Inner Detector (ID). The Fast TracKer (FTK) [4] processor will receive the ID data for each event accepted by Level-1, up to 100 KHz, and it will reconstruct charged-particle tracks with  $p_T > 1$  GeV, within the full tracker acceptance. This is expected to be of great importance for the high level trigger (HLT) computing farm, it will free resources and be more efficient on event topologies which are difficult to identify while maintaining a large rejection of the backgrounds.

### 1.1 FTK Challenges

For every event passing the Level-1 Trigger, FTK performs a hardware-based track reconstruction based on hit information from all channels of the ATLAS silicon detectors. The resulting tracks are sent to the HLT to be used in the software algorithms. In order to cope with event rates of up to 100 kHz the tracking performed by FTK has to be several orders of magnitude faster than offline tracking. Hence, the processing of the data is organised as parallel as possible. The signals from the detector volume are split into 64 regions, so-called towers, which are processed independently. Further, the data volume is decreased as much as possible by a custom clustering algorithm defining "hits" which are considered later on instead of the full pixel/strip information. In addition, the hit information is re-binned into coarse-resolution "superstrips" whenever appropriate.

FTK performs the tracking in two steps. At first, track candidates are identified by comparing the fired superstrips to predefined trajectories stored in memory. Such a "pattern" refers to a list of superstrips describing the trajectory of a simulated particle as it traverses the detector layers. These track candidates at coarse resolution (roads) seed a high resolution track fitting done by FPGAs. By considering only hits from the road the combinatorics is significantly reduced and hence makes the fit itself is much faster. The pattern matching procedure is implemented in a custom associative memory (AM) chip designed to perform it at very high speed. It allows to compare the incoming data simultaneously to all stored patterns. The parameters of the pattern matching can be adjusted. Narrow roads permit fast track fitting but require many patterns to be stored and searched in AM. Wide roads, on the other hand, allow for fewer patterns stored but the increased combinatorics within the matched roads slows down the track fitting. This choice is optimised by implementing the feature of variable resolution of the roads via ternary bits in the AM logic [5]. Furthermore, the number of matching layers is programmable.

The track parameters evaluation has been reduced to a set of scalar products. The same fitting formula, with different coefficients and numbers of coordinates, is used in coarse 8-layer patter matching and fitting as well as during the second stage 12-layer fit. A missing layer is allowed in both stages.

## 2. The FTK hardware processing chain

All the functionalities mentioned in the previous section are implemented in specific electronic boards and cards, designed using VME and ATCA standards. The final system will have about 8000 AM chips and 2000 FPGAs, from different vendors and of different models. This huge computing power will be distributed on 32 data formatter (DF) boards, 128 associative memory boards-serial link processors (AMBSLP or AMB) and auxiliary cards (AUX), 32 second stage boards (SSB), and 2 FTK to Level-2 interface cards (FLIC). A description of each board type is presented in the following sub-sections.

## 2.1 Clustering reconstruction and data formatting

The entry point of the system is composed of 32 ATCA boards called Data Formatters (DFs, see Fig. 1) [6]. Each DF receives data from the ATLAS inner detector read-out drivers (RODs) through up to 4 daughter cards, the FTK input mezzanine (FTK\_IM). Each FTK\_IM (see Fig. 1 b) receives

**Figure 1.** The pictures show a fully stuffed DF board (left), with 4 FTK\_IM installed. The right picture shows a detailed view of the a FTK\_IM prototype, with the two FPGAs close to the FMC connector. The DF is able to receive 16 fibers.

up to 4 fibers, with a data bandwidth of 2 Gbps each one. All FTK\_IMs will receive in total 380 links, equivalent to about 750 Gbps of raw ID data. The goal of the FTK\_IM is to find clusters in incoming data performing a major data reduction while at the same time improving track reconstruction precision [7].

The DF board geometrically organizes the incoming clusters. This board arranges the clusters in  $\eta - \phi$  projective towers, with a dimension of  $\delta\phi \times \delta\eta \sim 32^{\circ} \times 1.2$ , and in logical layers to be sent to the core crates. Each DF is expected to provide data to 4 core processors and 1 SSB board, equivalent to 2 FTK towers, with the possibility to send data to other DF boards in case the clusters belong to towers not served by the current DF. The connection with the processing units uses optical links placed on the RTM module. The connection with other DF boards on the same crate exploits the full-mesh backplane. The DF boards are distributed in multiple ATCA shelves and the inter-shelf communication is guaranteed by an extra link on the RTM. Summarizing the amount of data passing through the DF, each board receives up to 32 Gbps from the ID RODs, about 30 Gbps of data are sent to the core processors, while 40 Gbps of data can be sent to other DFs in the same shelf and about 25 Gbps to the DF in other shelves.

#### 2.2 Processing Units

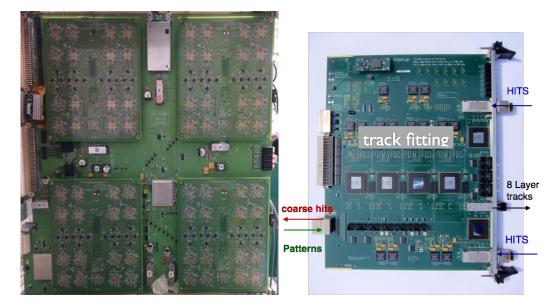

The central part of the FTK pipeline is the system composed by the pair of AM and AUX cards called collectively a Processing Unit (Fig. 2). The two boards perform the pattern matching and the first stage fit, which are the most computationally intensive steps of the pipeline. Data are received by the AUX card through SFP connectors, already organized by layers. Two main functionalities are implemented within the card: the data organizer (DO) and track fitter (TF). The DO is a smart database organizing all clusters according to a coarse resolution position identifier, the super-strip (SS). The SS is sent to the AM (called also AMBSLP) system for the pattern matching. The TF

**Figure 2.** The two pictures show a fully loaded AMBSLP board, with 4 LAMB cards installed for a total of 64 AM chips. Although the AM chips are not visible as they are mounted on the card, the socket footprint is clearly visible. The right picture shows an AUX card with the 4 Altera Arria V FPGAs, which are used for the linear fit.

receives the list of found roads from AMBSLP as well as the clusters associated to them from DF. According to the SS content of each road, the clusters are retrieved by the DO; the packet of hits belonging to each road are then sent to the TF. The TF builds all combinations of clusters in a road, with 1 cluster per layer, evaluating the  $\chi^2$  and then sends all good candidate tracks to the next board, the SSB. The AUX computation is distributed in 6 identical Altera Arria V FPGAs: 4 are devoted to the track fitter, while the other 2 respectively control the input and the output.

The AM board receives the SSs from the AUX and sends them to the AM chips. Internally, data are replicated to reach all the chips at the same clock cycle. The board is controlled by 4 FPGAs: 2 Xilinx Artix 7 which control the input and output logic, one FPGA controlling the VME interface, and 1 FPGA controlling the state of the board. The pattern matching function is done by 64 AM chips installed on 4 LAMBs.

Summarizing the data throughput, the AUX receives data at 6.4 Gbps from the DF and it has a 6.4 Gbps data channel toward the SSB. They are connected by P3, in which high speed serial links guarantee 12 Gbps as input from the AUX to the AMBSLP, and 16 Gbps as output from the AMBSLP to the AUX.

#### 2.3 Second Stage Board and Interface to HLT

The track candidates coming from the AUX card do not exploit the full precision of the ATLAS ID because they do not use some of the layers. The SSB shown in Fig. 3) improves the helix parameter resolution from 8-layer track fits using 12-layer fits and removes duplicate tracks. Each SSB receives the output from 4 AUX cards, the stereo SCT hits and IBL hits for the  $2 \eta - \phi$  towers associated with those AUX cards from the DF system. The maximum amount of data that are expected from the SSB is 6.4 Gbps/AUX, for a total of 25 Gbps. The board also shares track data

**Figure 3.** The left picture shows a recent prototype of the SSB. In the center of the board, the 4 FPGAs devoted to the final track fit are clearly visible. The right picture shows a FLIC board.

among other SSBs for overlap removal and merges FTK data within a core crate for output to the FTK Level-2 Interface via two fiber-optic connections.

The SSB primary functions are :

- *Extrapolator* which uses 8-layer track information to compute likely positions of hits in the other 4 layers for use in 12-layer track fitting.

- *Track Fitter (TF)* which determines best-fit helix parmeters from hits in roads using 12 silicon layers.

- *Hit Warrior (HW)* which removes duplicate tracks based on a requisite number of common hits and  $\chi^2$ .

In the current design, these functions are implemented in firmware loaded into separate Virtex 7 Xilinx FPGAs on each SSB.

Since the FTK towers have a generous overlap at the boundaries, a large number of duplicated tracks are found in these areas; in order to perform a cross tower duplicate removal, the output tracks are first moved to the SSB of the next tower, then sent to the system final board: the FLIC board.

The FLIC board's goal is to collect reconstructed tracks information from the SSB, reduce the data volume and convert them into a format compatible with the HLT software. The FLICs system has a total input and output maximum bandwidth of 32 Gbps.

# 3. Stage of Integration and Commissioning schedule

The FTK system is in a very advanced development status. All boards have either the green light for production or the production already started. The key component of the pattern matching, the AMChip06, has bee submitted for production, and the first few thousand chips are expected to be released in November 2015. A first full slice test is being carried out, testing all the pipeline and the firmware of each board. The full slice is expected to be fully functional by the end of 2015. At

the same time the installation of few boards in USA 15 in the ATLAS underground counting room has been started (1 DF and 4 IMs plus the FLIC). The DF is connected to the ATLAS data taking system and the IMs have received the first real data in August.

A fully working system, which will be able to reconstruct tracks in the whole barrel region, is expected early in 2016, with full inner detector coverage by the summer of 2016. The commissioning of the complete system (128 AM boards) is expected in 2018, but it can be anticipated if the luminosity provided by the LHC increases faster than expected.

# 4. Conclusions

The ATLAS FTK processor will be able to provide high quality tracks to the HLT algorithms at full Level-1 rate. Thanks to this information the HLT will be more efficient in collecting evens with  $\tau$ s or b jets. The hardware is ready for production and a first complete slice is being tested. The first production of boards is expected to cover the barrel region, with  $|\eta| < 1$ , by spring 2016, and full  $\eta$  coverage by the end of 2016.

#### Acknowledgments

The Fast Tracker project receives support from Istituto Nazionale di Fisica Nucleare; the US National Science Foundation and Department of Energy; Grant-in-Aid for Scientific Research from the Japan Society for the Promotion of Science and MEXT, Japan; the Bundesministerium fulLr Bildung und Forschung, FRG; the Swiss National Science Foundation; the European community FP7 People grants ARTLHCFE 254410 FP7-PEOPLE-2009-IOF and FTK 324318 FP7-PEOPLE-2012-IAPP; the Agence Nationale de la Recherche, project "FastTrack" n. ANR-13-BS05-0011, France; ARC, Australia; and GSRT, NSRF and IKY, Greece.

### References

- [1] [ATLAS Collaboration], *The ATLAS Experiment at the CERN Large Hadron Collider*, JINST 3 S08003 (2008).

- [2] [ATLAS Collaboration], Observation of a new particle in the search for the Standard Model Higgs boson with the ATLAS detector at the LHC Phys. Lett. B **716** (2012) 1. arXiv:1207.7214 [hep-ex]

- [3] [CMS Collaboration], Observation of a new boson at a mass of 125 GeV with the CMS experiment at the LHC, Phys. Lett. B 716 (2012) 30. arXiv:1207.7214 [hep-ex]

- [4] A. Annovi et al., Fast TracKer (FTK) Technical Design Report, CERN-LHCC-2013-007, ATLAS-TDR-021

- [5] A. Annovi et al., A new "Varuiable Resolution Associative Memory" for High Energy Physics ATL-UPGRADE-PROC-2011-004, http://cdsweb.cern.ch/record/1352152.

- [6] Y. Okumura et al., ATCA-based ATLAS FTK input interface system Journal of Instrumentation, 10 (2015) 04.

- [7] C.-L. Sotiropoulou et al, A Multi-Core FPGA-based 2D-Clustering Implementation for Real-Time Image Processing, iIEEE Trans. on Nuclear Science, vol. 61, no. 6, doi: 10.1109/TNS.2014.2364183.