#### International Doctorate School in Information and Communication Technologies

### DISI - University of Trento

## Development of enhanced double-sided 3D radiation sensors for pixel detector upgrades at HL-LHC

Marco Povoli

Advisor:

Prof. Gian-Franco Dalla Betta

Università degli Studi di Trento

January 2013

### Abstract

The upgrades of High Energy Physics (HEP) experiments at the Large Hadron Collider (LHC) will call for new radiation hard technologies to be applied in the next generations of tracking devices that will be required to withstand extremely high radiation doses. In this sense, one of the most promising approaches to silicon detectors, is the so called 3D technology. This technology realizes columnar electrodes penetrating vertically into the silicon bulk thus decoupling the active volume from the inter-electrode distance. 3D detectors were first proposed by S. Parker and collaborators in the mid '90s as a new sensor geometry intended to mitigate the effects of radiation damage in silicon. 3D sensors are currently attracting growing interest in the field of High Energy Physics, despite their more complex and expensive fabrication, because of the much lower operating voltages and enhanced radiation hardness. 3D technology was also investigated in other laboratories, with the intent of reducing the fabrication complexity and aiming at medium volume sensor production in view of the first upgrades of the LHC experiments. This work will describe all the efforts in design, fabrication and characterization of 3D detectors produced at FBK for the ATLAS Insertable B-Layer, in the framework of the ATLAS 3D sensor collaboration. In addition, the design and preliminary characterization of a new batch of 3D sensor will also be described together with new applications of 3D technology.

[This work was supported by INFN CSN V, projects "TREDI" (2005-2008) and "TRIDEAS" (2009-2011)]

#### Keywords

[3D detectors, ATLAS IBL, TCAD simulations, Device characterization]

## Acknowledgements

First of all I would like to thank my supervisor, professor Gian-Franco Dalla Betta, for the precious help and all the great opportunities he gave me. This work could not have been completed without his guidance. I would also like to thank all the people involved in 3D sensors fabrication and characterization at FBK, without whom many of the results described in this work would not have been possible.

I am also grateful to all the people I met in the framework of the "3D sensor collaboration" and during my stay at the University of Manchester for the fruitful discussions that helped me increasing my knowledge on may topics. The same goes for the people I collaborated with in Trento.

Last, but not least, I must thank my family and friend for the support they gave me during these years of hard work.

#### List of publications as author and co-author

- G. F. Dalla Betta, M. Boscardin, L. Bosisio, G. Darbo, G. Gemme, M. Koehler, A. La Rosa, U. Parzefall, H. Pernegger, C. Piemonte, M. Povoli, S. Ronchin, L. Wiik, A. Zoboli, N. Zorzi, "Characterization of 3D-DDTC detectors on p-type substrates", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS - MIC'09), Conference Record, paper N02-4, pp. 29-36, Orlando (USA), 25-31 Ottobre 2009.Available online at http://dx.doi.org/10.1109/NSSMIC.2009.5401897.

- A. La Rosa, M. Boscardin, G.-F. Dalla Betta, G. Darbo, C. Gemme, H. Pernegger, C. Piemonte, M. Povoli, S. Ronchin, A. Zoboli, N. Zorzi, E. Bolle, M. Borri, C. Da Vià, S. Dong, S. Fazio, P. Grenier, S. Grinstein, H. Gjersdal, P. Hansson, F. Huegging, P. Jackson, M. Kocian, F. Rivero, O. Rohne, H. Sandaker, K. Sjøbæk, T. Slavicek, W. Tsung, D. Tsybychev, N. Wermes, C. Young, "Preliminary results of 3D-DDTC pixel detectors for the ATLAS upgrade", Proceedings of Science - 9th International Conference on Large Scale Applications and Radiation Hardness of Semiconductor Detectors(RD09), Paper 032, 2010. Available online at http://arxiv.org/abs/0910.3788.

- G. F. Dalla Betta, A. Bagolini, M. Boscardin, L. Bosisio, P. Gabos, G. Giacomini, C. Piemonte, M. Povoli, E. Vianello, N. Zorzi, "Development of modified 3D detectors at FBK", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS - MIC'10), Conference Record, paper N15-3, Knoxville (USA), 30 Ottobre - 6 Novembre 2010. Available online at http://dx.doi.org/10.1109/NSSMIC.2010.5873785.

- G.-F. Dalla Betta, M. Boscardin, G. Darbo, C. Gemme, A. La Rosa, H. Pernegger, C. Piemonte, M. Povoli, S. Ronchin, A. Zoboli, N. Zorzi, "Development of 3D-DDTC pixel detectors for the ATLAS upgrade", Nucl. Instr. and Meth. A, vol. 638-S1, pp. S15-S23, 2011. Available online at http://dx.doi.org/10.1016/j.nima.2010.04.079.

- P. Grenier, G. Alimonti, M. Barbero, R. Bates, E. Bolle, M. Borri, M. Boscardin, C. Buttar, M. Capua, M. Cavalli-Sforza, M. Cobal, A. Cristofoli, G-F. Dalla Betta, G. Darbo, C. Da Vià, E. Devetak, B. DeWilde, B. Di Girolamo, D. Dobos, K. Einsweiler, D. Esseni, S. Fazio, C. Fleta, J. Freestone, C. Gallrapp, M. Garcia-Sciveres, G. Gariano, C. Gemme, M-P. Giordani, H. Gjersdal, S. Grinstein, T. Hansen, T-E. Hansen, P. Hansson, J. Hasi, K. Helle, M.Hoeferkamp, F. Huegging, P. Jackson, K. Jakobs, J. Kalliopuska, M. Karagounis, C. Kenney, M. Koehler, M. Kocian, A. Kok, S. Kolya, I. Korokolov, V. Kostyukhin, H. Krugger, A. La Rosa, C. H. Lai, N. Lietaer, M. Lozano, A. Mastroberardino, A. Micelli, C. Nellist, A. Oja, V. Oshea, C. Padilla, P. Palestri, S. Parker, U. Parzefall, J. Pater, G. Pellegrini, H. Pernegger, C. Piemonte, S. Pospisil, M. Povoli, S. Roe, O. Rohne, S. Ronchin, A. Rovani, E. Ruscino, H.

Sandaker, S. Seidel, L. Selmi, D. Silverstein, K. Sjøbæk, T. Slavicek, S. Stapnes,

B. Stugu, J. Stupak, D. Su, G. Susinno, R. Thompson, J-W. Tsung, D. Tsybychev,

S.J. Watts, N. Wermes, C. Young, N. Zorzi, "Test beam results of 3D silicon pixel sensors for the ATLAS upgrade", Nucl. Instr. and Meth. A, vol. 638, pp. 33-40, 2011. Available online at http://dx.doi.org/10.1016/j.nima.2011.01.181.

- A. Micelli, K. Helle, H. Sandaker, B. Stugu, M. Barbero, F. Huügging, M. Karagounis, V. Kostyukhin, H. Krüuger, J.-W. Tsung, N. Wermes, M. Capua, S. Fazio, , G. Susinno, B. Di Girolamo, D. Dobos, A. La Rosa, H. Pernegger, S. Roe, T. Slavicek, S. Pospisil, K. Jakobs, M. Köhler, U. Parzefall, G. Darbo, G. Gariano, C. Gemme, A. Rovani, E. Ruscino, C. Butter, R. Bates, V. Oshea, S. Parker, M. Cavalli-Sforza, S. Grinstein, I. Korokolov, C. Pradilla, K. Einsweiler, M. Garcia-Sciveres, M. Borri, C. Da Vià, J. Freestone, S. Kolya, C. H. Lai, C. Nellist, J. Pater, R. Thompson, S. J. Watts, M. Hoeferkamp, S. Seidel, E. Bolle, H. Gjersdal, K.-N Sjoebaek, S. Stapnes, O. Rohne, D. Su, C. Young, P. Hansson, P. Grenier, J. Hasi, C. Kenney, M. Kocian, P. Jackson, D. Silverstein, H. Davetak, B. DeWilde, D. Tsybychev, G.-F. Dalla Betta, P. Gabos, M. Povoli, M. Cobal, M.-P. Giordani, L. Selmi, A. Cristofoli, D. Esseni, P. Palestri, C. Fleta, M. Lozano, G. Pellegrini, M. Boscardin, A. Bagolini, C. Piemonte, S. Ronchin, N. Zorzi, T.-E. Hansen, T. Hansen, A. Kok, N. Lietaer, J. Kalliopuska, A. Oja, "3D-FBK Pixel sensors: recent beam tests results with irradiated devices", Nucl. Instr. and Meth. A, vol. 650, pp. 150-157, 2011. Available online at http://dx.doi.org/10.1016/j.nima.2010.12.209.

- A. Cristofoli, A. Dalla Costa, M. Boscardin, V. Cindro, G. F. Dalla Betta, F. Driussi, G. Giacomini, M. P. Giordani, P. Palestri, M. Povoli, S. Ronchin, L. Selmi and E. Vianello, "Simulations and Electrical Characterization of Double-side Double Type Column 3D Detectors", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS MIC'10), Conference Record, paper N10-5, Valencia (Spagna), 23-29 Ottobre 2011. Available online at http://dx.doi.org/10.1109/NSSMIC.2011.6154101.

- E. Vianello, A. Bagolini, P. Bellutti, M. Boscardin, G. F. Dalla Betta, G. Giacomini, F. Mattedi, C. Piemonte, M. Povoli, N. Zorzi, "Optimization of double side 3D detector technology for first production at FBK", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS MIC'10), Conference Record, paper N10-6, Valencia (Spagna), 23-29 Ottobre 2011. Available online at http://dx.doi.org/10.1109/NSSMIC.2011.6154102.

- G. F. Dalla Betta, A. Bagolini, M. Boscardin, G. Giacomini, M. Povoli, E. Vianello, N. Zorzi, "Development of Active and Slim Edge Terminations for 3D and Planar Detectors", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS)

- MIC'10), Conference Record, paper N24-5, Valencia (Spagna), 23-29 Ottobre 2011. Available online at http://dx.doi.org/10.1109/NSSMIC.2011.6154337.

M. Povoli, M. Boscardin, A. Bagolini, G. F. Dalla Betta, G. Giacomini, E. Vianello, N. Zorzi, "Development of planar detectors with active edge", Nucl. Instr. and Meth. A, vol. 658, pp. 103-107, 2011.

Available online at http://dx.doi.org/10.1016/j.nima.2011.04.050

- M. Povoli, A. Bagolini, M. Boscardin, G. F. Dalla Betta, G. Giacomini, E. Vianello, N. Zorzi, "Slim edges in double-sided silicon 3D detectors", Journal of Instrumentation, JINST 7, C01015, 2012. Available online at http://dx.doi.org/10.1088/1748-0221/7/01/C01015.

- G. Giacomini, C. Piemonte, G.-F. Dalla Betta, M. Povoli, "Simulations of 3D detectors", (Invited paper), Proceedings of Science 20th Workshop on Vertex Detectors (Vertex 2011), Paper 025, 2012.

- A. La Rosa, M. Boscardin, M. Cobal, C. Da Vià, G. F. Dalla Betta, G. Darbo, C. Gallrapp, C. Gemme, F. Huegging, J. Janssen, A. Micelli, H. Pernegger, M. Povoli, N. Wermes, N. Zorzi, "Functional characterization of irradiated 3D-DDTC pixel sensor prototypes fabricated at FBK", Nuclear Instruments and Methods A, Volume 681, 21 July 2012, Pages 25-33.

Available online at http://dx.doi.org/10.1016/j.nima.2012.03.048.

M. Povoli, A. Bagolini, M. Boscardin, G.-F. Dalla Betta, G. Giacomini, F. Mattedi, E. Vianello, N. Zorzi, "Impact of the layout on the electrical characteristics of doublesided silicon 3D sensors fabricated at FBK", Nucl. Instr. and Meth. A, Vol. 699, 21 January 2013, pp. 22-26.

Available online at http://dx.doi.org/10.1016/j.nima.2012.04.080.

- C. Da Vià, M. Boscardin, G.-F. Dalla Betta, G. Darbo, C. Fleta, C. Gemme, G. Giacomini, P. Grenier, S. Grinstein, T.-E. Hansen, J. Hasi, C. Kenney, A. Kok, A. La Rosa, A. Micelli, S. Parker, G. Pellegrini, D.-L. Pohl, M. Povoli, E. Vianello, N. Zorzi, S.J. Watts, "3D active edge silicon sensors: Device processing, yield and QA for the ATLAS-IBL production", Nucl. Instr. and Meth. A, Vol. 699, 21 January 2013, Pages 18-21. Available online at http://dx.doi.org/10.1016/j.nima.2012.05.070.

- E. Alagoz, M. Bubna, A. Krzywda, G.-F. Dalla Betta, M. Povoli, M. Obertino, A. Solano, A. Vilela Pereirah, K. Arndt, G. Bolla, D. Bortoletto, M. Boscardin, S. Kwan, R. Rivera, I. Shipseya, L. Upleggerg, "Simulation and laboratory test results of 3D CMS pixel detectors for HL-LHC", Journal of Instrumentation, 2012 JINST 7 P08023. Available online at http://dx.doi.org/10.1088/1748-0221/7/08/P08023.

- M. Povoli, A. Bagolini, M. Boscardin, G.-F. Dalla Betta, G. Giacomini, J. Hasi, A. Oh, N. Zorzi, "Functional characterization of planar sensors with active edges using laser and X-Ray beam scans", presented at the 12th Pisa Meeting, La Biodola, Isola d'Elba, Italy, 20-26 May 2012. Accepted for publication to NIMA, available online at http://dx.doi.org/10.1016/j.nima.2012.09.035.

- M. Obertino, A. Solano, A. Vilela Pereira, E. Alagoz, J. Andresen, K. Arndt, G. Bolla, D. Bortoletto, M. Boscardin, R. Brosius, M. Bubna, G.-F. Dalla Betta, F. Jensen, A. Krzywda, A. Kumar, S. Kwan, C.M. Lei, D. Menasce, L. Moroni, J. Ngadiuba, I. Osipenkov, L. Perera, M. Povoli, A. Prosser, R. Rivera, I. Shipsey, P. Tan, S. Terzo, L. Uplegger, S. Wagner, *3D-FBK pixel sensors with CMS read-out: first test results*, presented at the 12th Pisa Meeting, La Biodola, Isola d'Elba, Italy, 20-26 May 2012. Accepted for publication on NIMA, available online at http://dx.doi.org/10.1016/j.nima.2012.11.076.

- G.-F. Dalla Betta, M. Boscardin, G. Darbo, C. Da Vià, S. Grinstein, P. Grenier, J. Hasi, C. Kenney, A. Kok, C.-H. Lai, S. Parker, G. Pellegrini, M. Povoli, S. Watts, "Recent developments and future perspectives in 3D silicon radiation sensors", Journal of Instrumentation, 2012 JINST 7 C10006. Available online http://dx.doi.org/10.1088/1748-0221/7/10/C10006.

- G. Giacomini, A. Bagolini, M. Boscardin, G.-F. Dalla Betta, F. Mattedi, M. Povoli, E. Vianello, N. Zorzi, "Development of double-side full-passing-column 3D Sensors at FBK", submitted for publication to IEEE Transactions on Nuclear Science.

- The ATLAS IBL collaboration, "Prototype ATLAS IBL modules using the FE-I4A front-end readout chip", (2012) JINST 7 P11010

- M. Povoli, C. Betancourt, M. Boscardin, G.-F. Dalla Betta, G. Giacomini, S. Kuehn, B. Lecini, U. Parzefall, N. Zorzi, "Characterization of 3D-DDTC strip sensors with passing-through columns", 9th International Conference on Radiation Effects on Semiconductor Materials and Devices (RESMDD12), October 9-12, 2012, Firenze, Italy, submitted for publication on NIMA.

- M. Obertino, A. Solano, R. Rivera, E. Alagoz, A. Krzywda, D. Bortoletto, G.-F. Dalla Betta, J. Ngadiuba, L. Uplegger, S. Kwan, J. Andresen, K. Arndt, G. Bolla, M. Boscardin, R. Brosius, M. Bubna, F. Jensen, A. Kumar, C.M. Lei, D. Menasce, L. Moroni, I. Osipenkov, L. Perera, M. Povoli, A. Prosser, I. Shipsey, P. Tan, S. Terzo, A. Vilela Pereira, S. Wagner, "Performance of CMS 3D silicon pixel detectors before and after irradiation", 9th International Conference on Radiation Effects on Semiconductor Materials and Devices (RESMDD12), October 9-12, 2012,

Firenze, Italy, submitted for publication on NIMA.

- M. Povoli, A. Bagolini, M. Boscardin, G.-F. Dalla Betta, G. Giacomini, F. Mattedi, N. Zorzi, "Layout and Process Improvements to Double-Sided Silicon 3D Detectors Fabricated at FBK", IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS-MIC'12), Conference Record, paper N14-204, October 29 - November 3, 2012, Disneyland Hotel, Anaheim, California, USA.

- C. Da Vià, M. Boscardin, G.-F. Dalla Betta, G. Darbo, I. Haughton, P. Grenier, S. Grinstein, T.-E. Hansen, J. Hasi, C. Kenney, A. Kok, S. Parker, G. Pellegrini, M. Povoli, V. Tzhnevyi, S.J. Watts, "Future trends of 3D silicon sensors", presented at the International Workshop on Semiconductor Pixel Detectors for Particles and Imaging, September 3-7, 2012 in Inawashiro, Japan. Submitted for publication on NIMA.

- G. F. Dalla Betta, M. Povoli, C. Da Vià, S. Grinstein, A Micelli, S. Tsiskaridze, P. Grenier, G. Darbo, C. Gemme, M. Boscardin, G. Pellegrini, S. Parker, "3D silicon sensors: irradiation results", (invited paper), Proceeding of Science - 21<sup>st</sup> Workshop on Vertex Detectors (Vertex 2012). Paper 014, 2012.

#### List of presentations at conferences and workshops

- "Development of planar detectors with active edge", Oral presentation at the 8th International Conference on Radiation Effects on Semiconductor Materials and Devices (RESMDD10), October 13-15, 2010, Firenze, Italy.

- "Investigation of punch-through bias in 3D sensors", Oral presentation at the 6th Workshop on Advanced Silicon Radiation Detectors, 3D and P-type Technologies, March 2-4, 2011, Trento, Italy.

- "Slim edges in double-sided silicon 3D detectors", Oral presentation at the 13th International Workshop on Radiation Imaging Detectors (iWoRID13), July 3-7, 2011, Zürich and Villigen, Switzerland.

- "Simulation and testing of FBK detectors", Oral presentation at the first "3D student forum", November 9, 2011.

- "Impact of the layout on the electrical characteristics of double-sided silicon 3D sensors fabricated at FBK", Oral presentation at the "Hiroshima" Symposium on the Development and Application of Semiconductor Tracking Detectors (HSTD-8), December 5-8, 2011, Academia Sinica, Taipei, Taiwan.

- Functional characterization of planar sensors with active edges using laser and X-Ray beam scans, Poster at the 12th Pisa Meeting, Italy, 20-26 May 2012, La Biodola, Isola d'Elba.

- "Characterization of 3D-DDTC strip sensors with passing-through columns", Oral presentation at the 9th International Conference on Radiation Effects on Semiconductor Materials and Devices (RESMDD12), October 9-12, 2012, Firenze, Italy. Oral presentation.

- "Layout and Process Improvements to Double-Sided Silicon 3D Detectors Fabricated at FBK", Poster at the IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS-MIC'12), October 29 - November 3, 2012, Disneyland Hotel, Anaheim, California, USA.

## Contents

| 1        | Hig          | h Enei                                                                          | rgy Physics at LHC                                                                                                                                                                             | 1                                                  |

|----------|--------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|          | 1.1          | The L                                                                           | arge Hadron Collider                                                                                                                                                                           | 1                                                  |

|          | 1.2          | Brief I                                                                         | nistory of the LHC                                                                                                                                                                             | 3                                                  |

|          |              | 1.2.1                                                                           | Planned machine upgrades                                                                                                                                                                       | 4                                                  |

|          | 1.3          | The A                                                                           | TLAS Experiment                                                                                                                                                                                | 5                                                  |

|          |              | 1.3.1                                                                           | Structure of the ATLAS experiment                                                                                                                                                              | 6                                                  |

|          |              | 1.3.2                                                                           | The Pixel Detector and the FE-I3 read-out chip                                                                                                                                                 | 9                                                  |

|          |              | 1.3.3                                                                           | The Semi-Conductor Tracker                                                                                                                                                                     | 15                                                 |

|          |              | 1.3.4                                                                           | ATLAS upgrade plans                                                                                                                                                                            | 16                                                 |

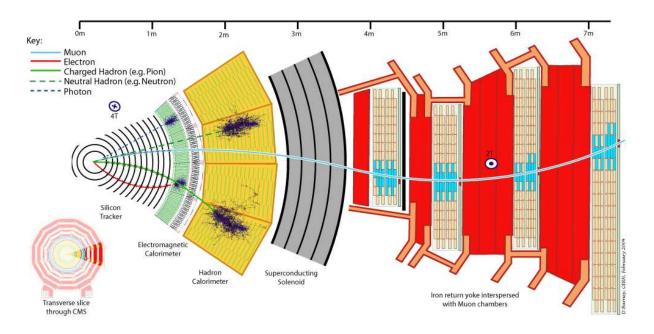

|          | 1.4          | The C                                                                           | MS Experiment                                                                                                                                                                                  | 18                                                 |

|          |              | 1.4.1                                                                           | Structure of the CMS experiment                                                                                                                                                                | 18                                                 |

|          |              | 1.4.2                                                                           | The pixel detector and the PSI46V2 read-out chip                                                                                                                                               | 22                                                 |

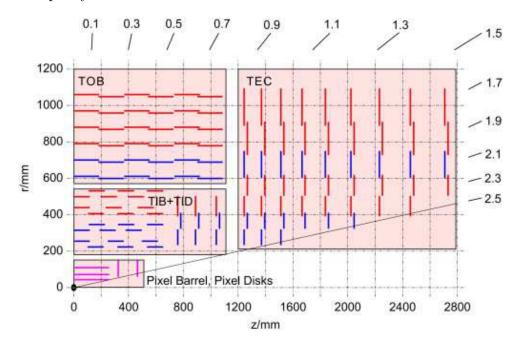

|          |              | 1.4.3                                                                           | The Silicon Strip Tracker (SST)                                                                                                                                                                | 25                                                 |

|          |              | 1.4.4                                                                           | CMS upgrade plans                                                                                                                                                                              | 27                                                 |

|          |              |                                                                                 |                                                                                                                                                                                                |                                                    |

| <b>2</b> | Silie        | con Ra                                                                          | diation Detectors                                                                                                                                                                              | 29                                                 |

| <b>2</b> | Silio<br>2.1 |                                                                                 | diation Detectors<br>concepts on semiconductor detectors                                                                                                                                       | <b>29</b><br>29                                    |

| 2        |              |                                                                                 |                                                                                                                                                                                                |                                                    |

| 2        |              | Basic                                                                           | concepts on semiconductor detectors                                                                                                                                                            | 29                                                 |

| 2        |              | Basic<br>2.1.1<br>2.1.2                                                         | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30                                           |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2                                                         | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35                                     |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor                                              | concepts on semiconductor detectors          Basic notions of semiconductor physics          P-N junction, important parameters for silicon detectors          a devices for particle tracking | 29<br>30<br>35<br>39                               |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor<br>2.2.1                                     | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35<br>39<br>39                         |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor<br>2.2.1<br>2.2.2                            | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35<br>39<br>39<br>41                   |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4          | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35<br>39<br>39<br>41<br>44             |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4          | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35<br>39<br>39<br>41<br>44<br>45<br>47 |

| 2        | 2.1          | Basic<br>2.1.1<br>2.1.2<br>Silicor<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Read- | concepts on semiconductor detectors                                                                                                                                                            | 29<br>30<br>35<br>39<br>39<br>41<br>44<br>45<br>47 |

|   |     | 2.3.4  | Equivalent Noise Charge (ENC)                                                                          | . 52  |

|---|-----|--------|--------------------------------------------------------------------------------------------------------|-------|

|   | 2.4 | The b  | ump bonding and flip-chip process                                                                      | . 57  |

|   |     | 2.4.1  | Solder based bump-bonding process                                                                      | . 57  |

|   |     | 2.4.2  | Indium based bump-bonding process                                                                      | . 58  |

|   | 2.5 | Radia  | tion damage in Silicon                                                                                 | . 60  |

|   |     | 2.5.1  | Surface damage                                                                                         | . 60  |

|   |     | 2.5.2  | Bulk damage                                                                                            | . 63  |

|   |     | 2.5.3  | Counteracting radiation damage                                                                         | . 68  |

| 3 | 3D  | detect | ors state of the art before IBL                                                                        | 71    |

|   | 3.1 | The 3  | D silicon sensor architecture                                                                          | . 74  |

|   | 3.2 | Full 3 | D detectors                                                                                            | . 76  |

|   |     | 3.2.1  | Numerical device simulations                                                                           | . 76  |

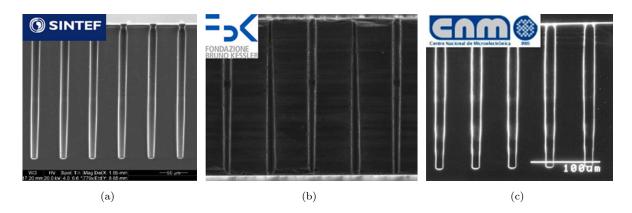

|   |     | 3.2.2  | Fabrication technology                                                                                 | . 79  |

|   |     | 3.2.3  | Experimental results                                                                                   | . 82  |

|   | 3.3 | Descri | ption of alternative approaches to 3D technology                                                       | . 85  |

|   | 3.4 | 3D-DI  | DTC at FBK                                                                                             | . 87  |

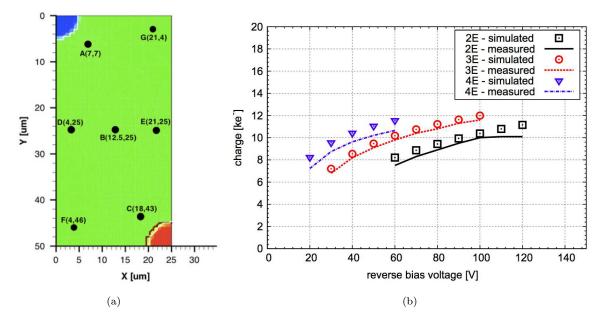

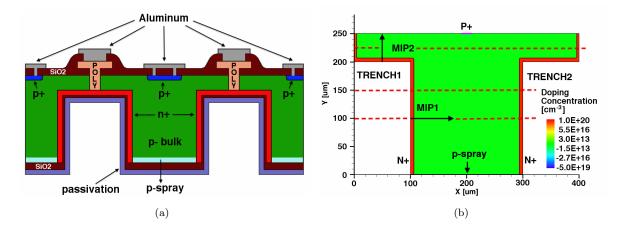

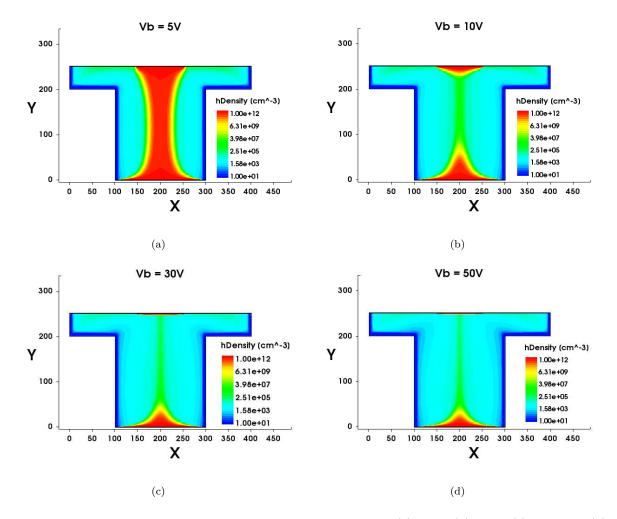

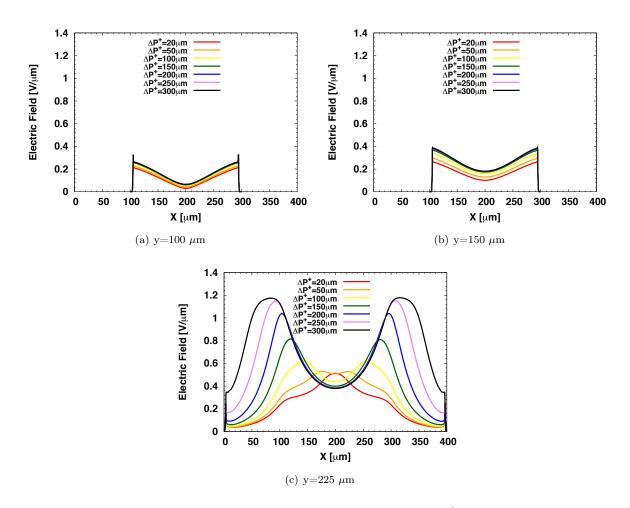

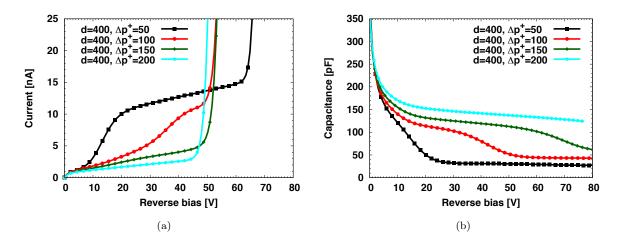

|   |     | 3.4.1  | Numerical device simulation                                                                            | . 87  |

|   |     | 3.4.2  | Fabrication technology                                                                                 | . 89  |

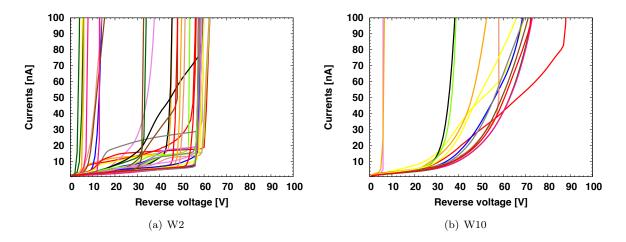

|   |     | 3.4.3  | Experimental results from the DTC-1 batch                                                              | . 91  |

|   |     | 3.4.4  | Experimental results from the DTC-2 batch                                                              | . 97  |

|   | 3.5 | 3D-DI  | DTC at CNM, most relevant results                                                                      | . 113 |

|   |     | 3.5.1  | Final consideration on the 3D-DDTC technology                                                          | . 115 |

| 4 | The | e ATLA | AS IBL and 3D detectors fabricated at FBK                                                              | 117   |

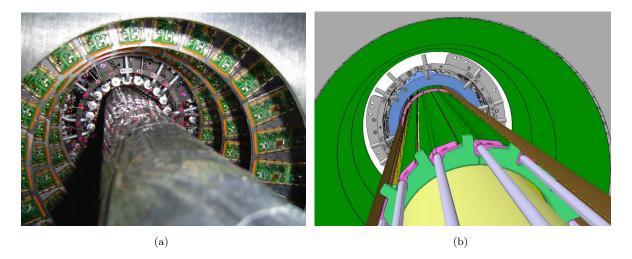

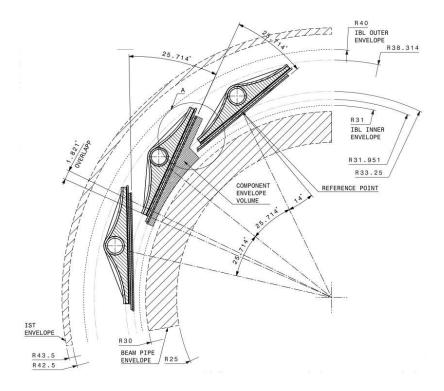

|   | 4.1 | The A  | TLAS Insertable B-Layer (IBL)                                                                          | . 117 |

|   |     | 4.1.1  | Motivations and summary of requirements                                                                | . 118 |

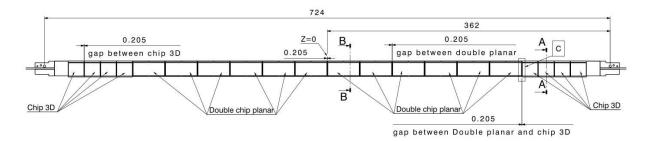

|   |     | 4.1.2  | Layout                                                                                                 | . 118 |

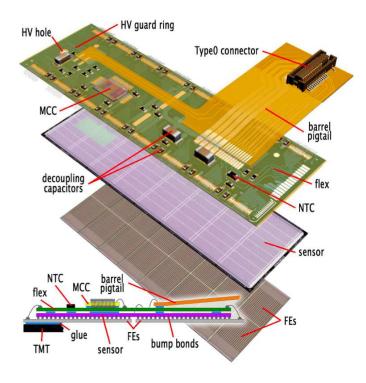

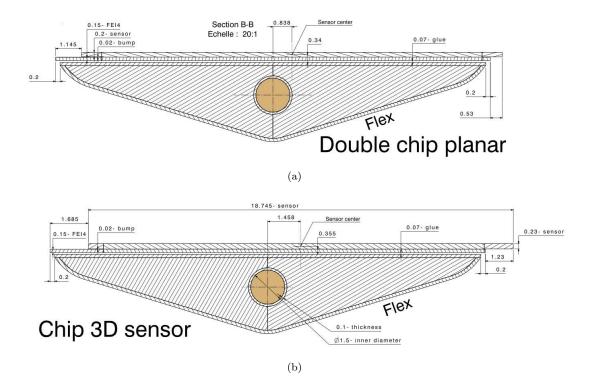

|   |     | 4.1.3  | Modules                                                                                                | . 120 |

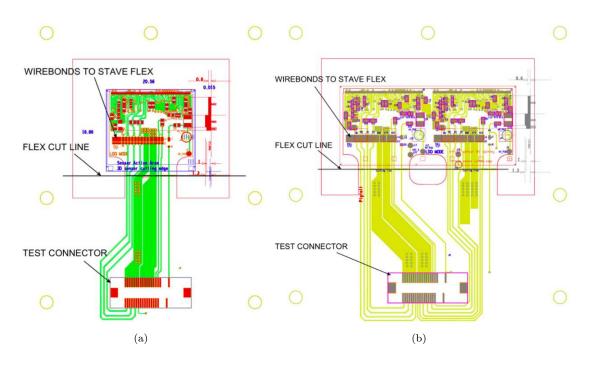

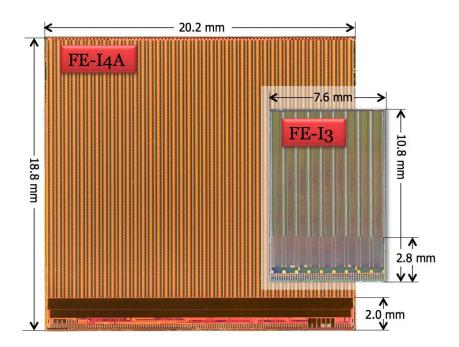

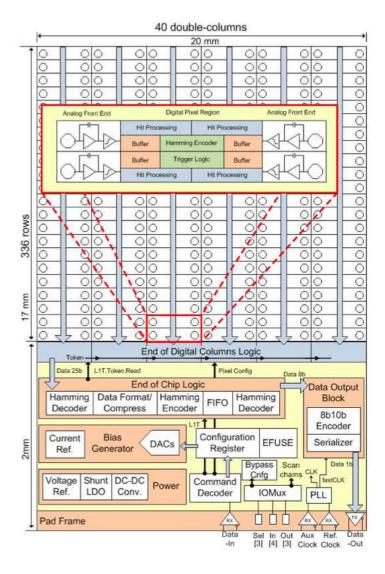

|   |     |        | Electronics, the FE-I4 readout chip                                                                    | . 121 |

|   |     |        | Chosen sensor technologies                                                                             | . 128 |

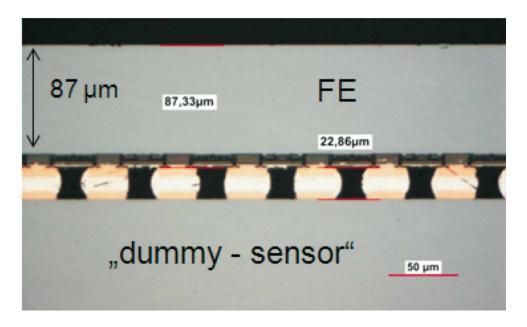

|   |     |        | The bump-bonding and flip-chip                                                                         | . 131 |

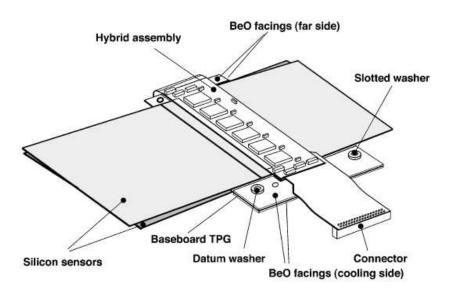

|   |     | 4.1.4  | Stave layout and assembly                                                                              | . 133 |

|   |     |        | Module loading on the stave                                                                            | . 133 |

|   | 4.2 | The A  | TLAS 3D sensor collaboration                                                                           | . 136 |

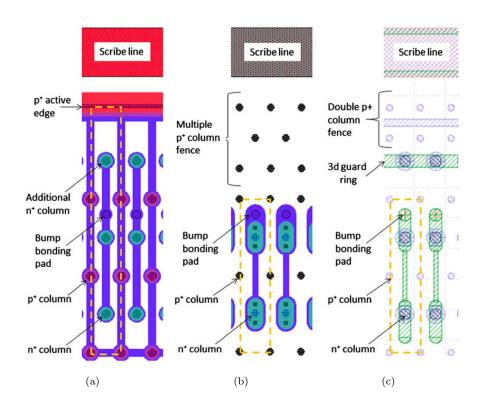

|   |     | 4.2.1  | Processing options and manufacturers                                                                   | . 136 |

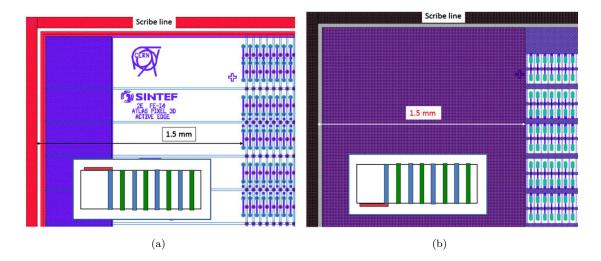

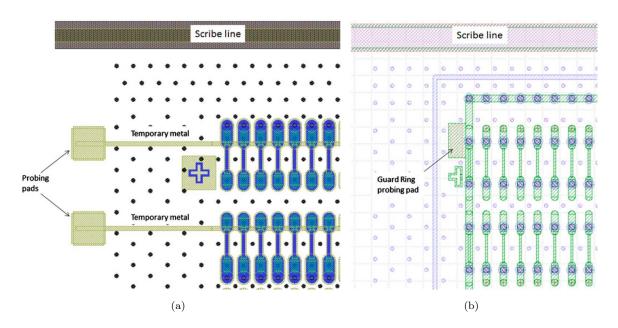

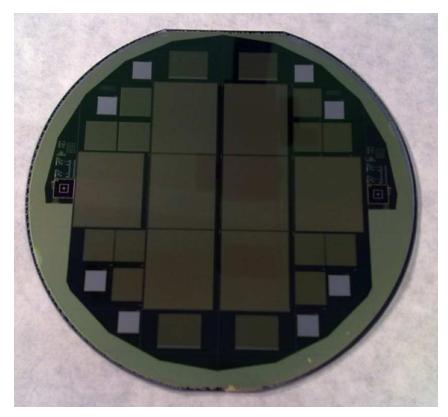

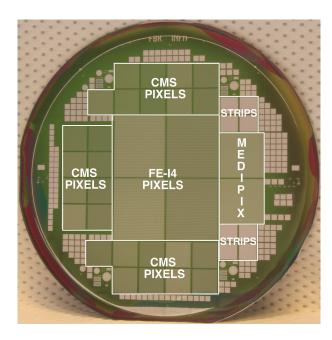

|   |     | 4.2.2  | The common wafer layout $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 137 |

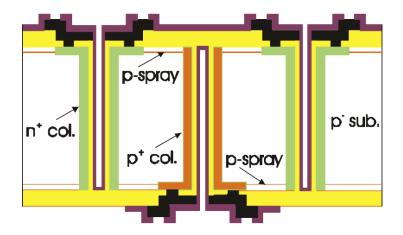

|   | 4.3 | Enhan  | nced 3D-DDTC technology at FBK                                                                         | . 142 |

|          |     | 4.3.1   | Design and technological aspects                                                                                                      |

|----------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.4 | Pre-ir  | rad. electrical characterization                                                                                                      |

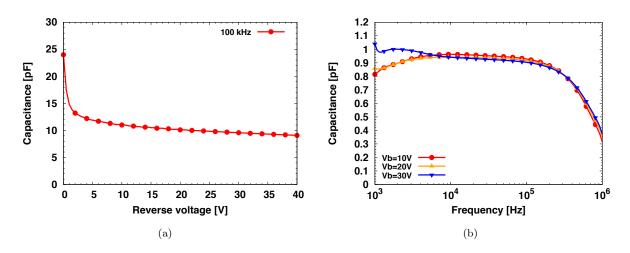

|          |     | 4.4.1   | Planar test structures                                                                                                                |

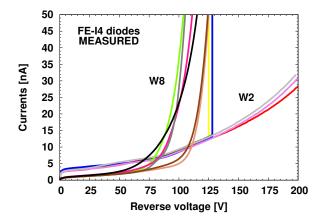

|          |     | 4.4.2   | 3D-diodes                                                                                                                             |

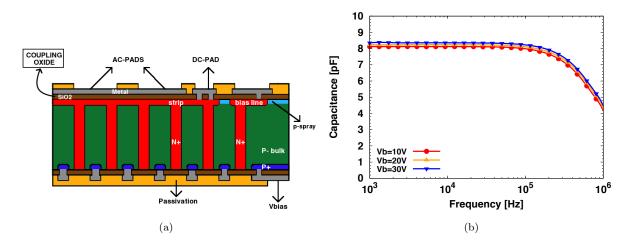

|          |     | 4.4.3   | Strip detectors                                                                                                                       |

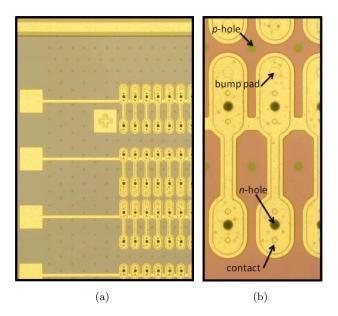

|          |     | 4.4.4   | ATLAS FE-I4 Pixel detectors                                                                                                           |

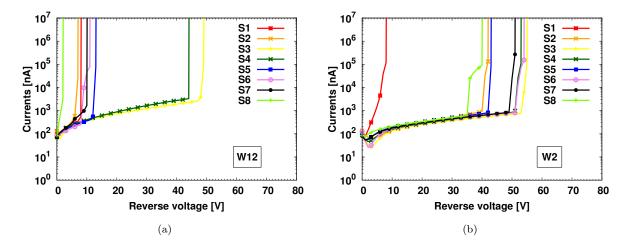

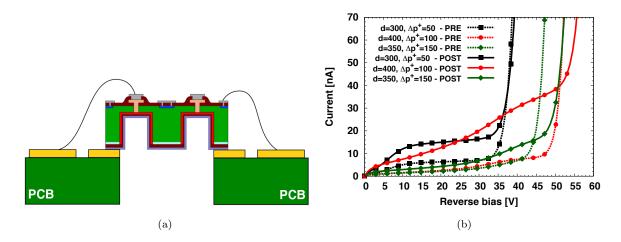

|          | 4.5 | Post-i  | rrad. electrical characterization                                                                                                     |

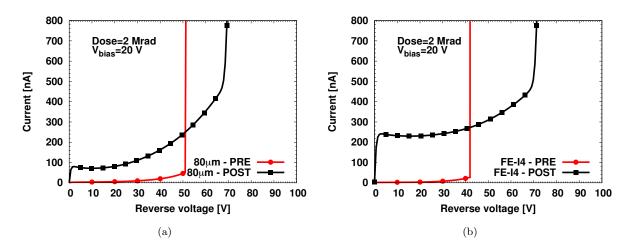

|          |     | 4.5.1   | Surface X-ray irradiation of planar test structures and 3D-diodes 177                                                                 |

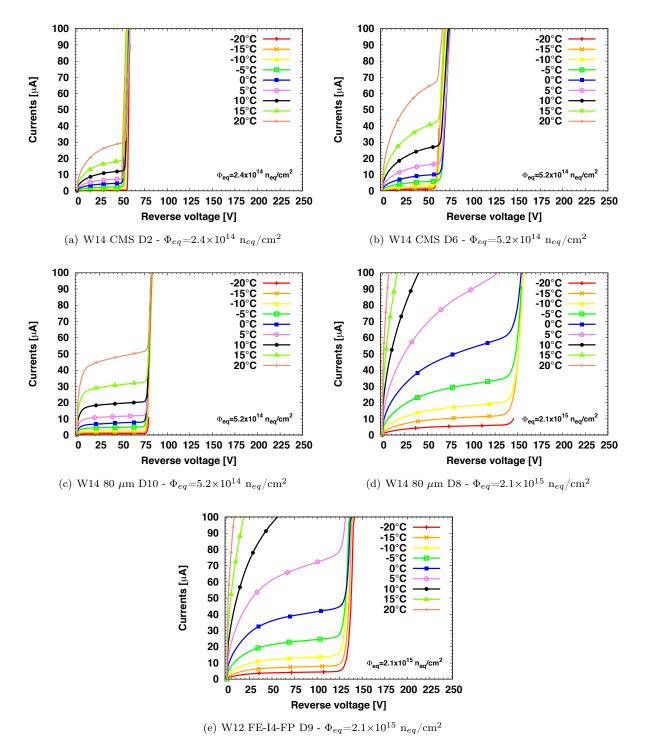

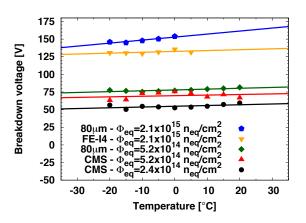

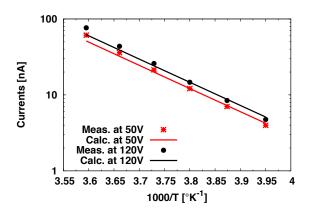

|          |     | 4.5.2   | Proton irradiated 3D-diodes                                                                                                           |

|          |     | 4.5.3   | Proton irradiated FE-I4 pixel detectors                                                                                               |

|          | 4.6 | Funct   | ional characterization                                                                                                                |

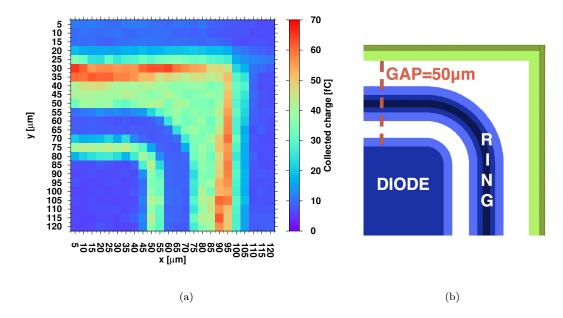

|          |     | 4.6.1   | 3D-diodes                                                                                                                             |

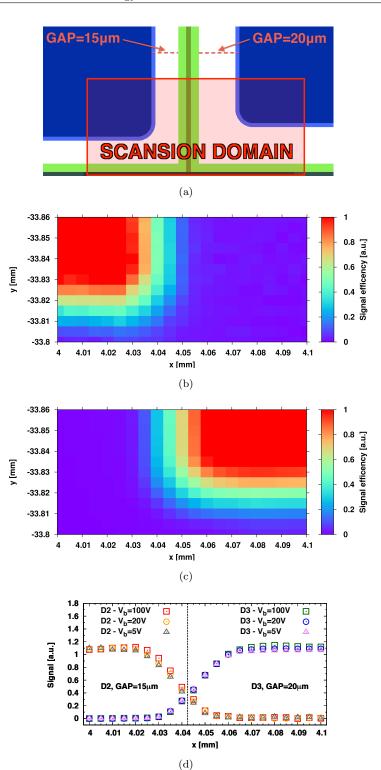

|          |     | 4.6.2   | Strip detectors                                                                                                                       |

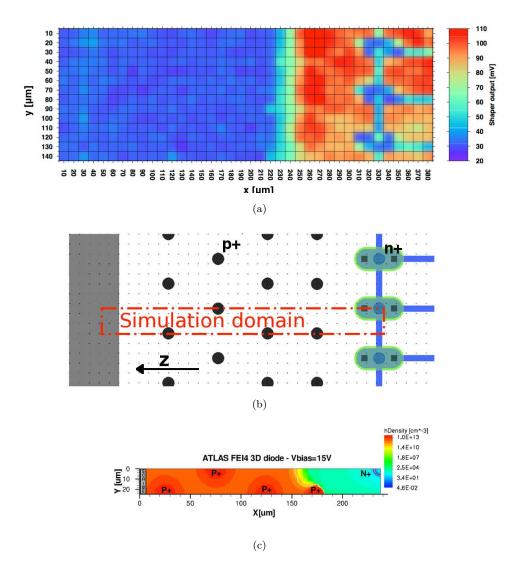

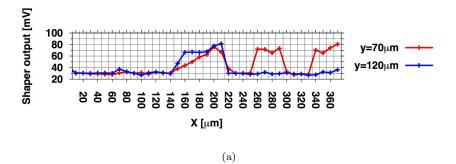

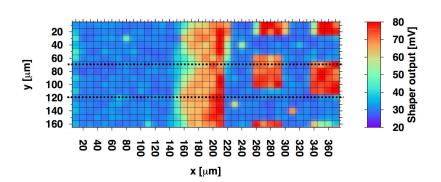

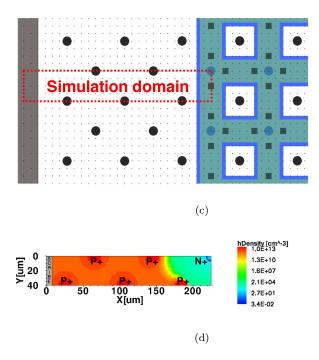

|          |     | 4.6.3   | ATLAS FE-I4 Pixel detectors                                                                                                           |

|          |     | 4.6.4   | CMS PSI46V2 Pixel detectors                                                                                                           |

| <b>5</b> | Imr | proving | g 3D technology at FBK 215                                                                                                            |

| 0        | 5.1 | -       | ble improvements to FBK technology                                                                                                    |

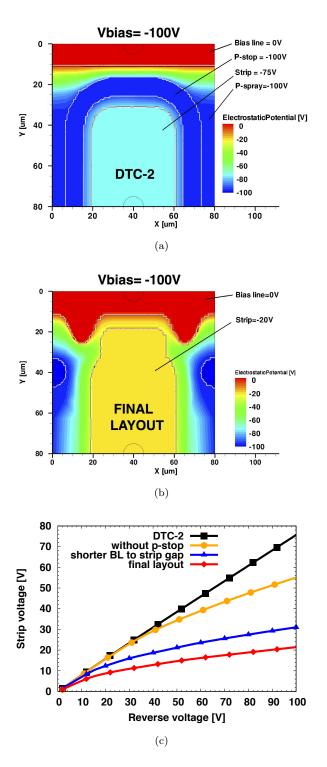

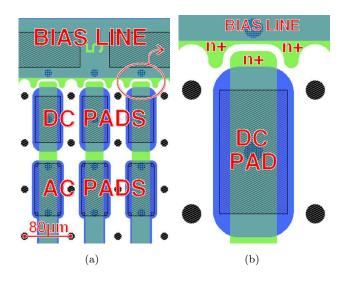

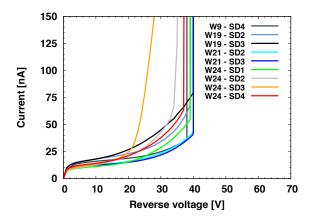

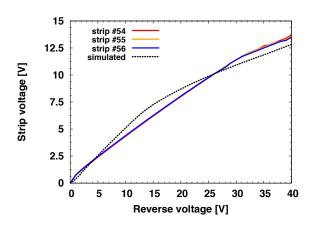

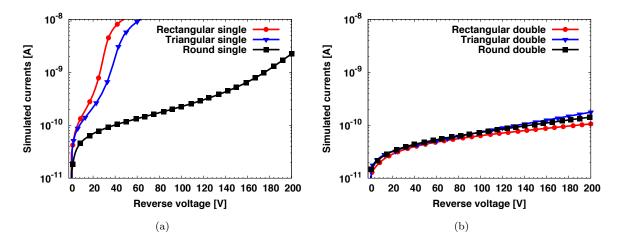

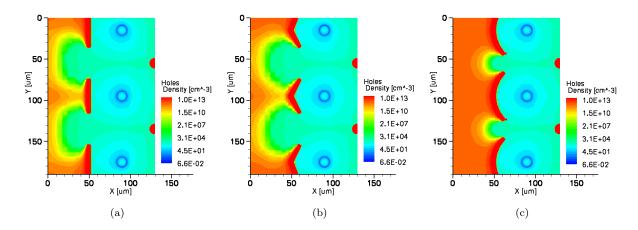

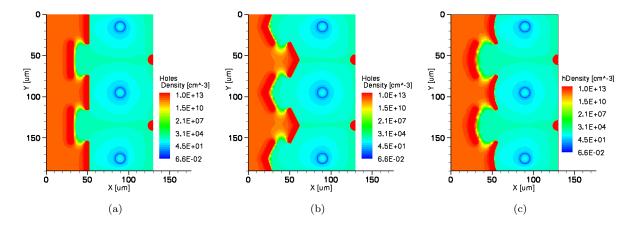

|          | 5.2 |         | $rical simulations \dots \dots$ |

|          | 5.3 |         | lim-edge implementation                                                                                                               |

|          | 5.4 |         | ss modifications and device fabrication                                                                                               |

|          | 5.5 |         | ical characterization of new devices                                                                                                  |

| 6        | Ado | litiona | l applications of 3D technology 233                                                                                                   |

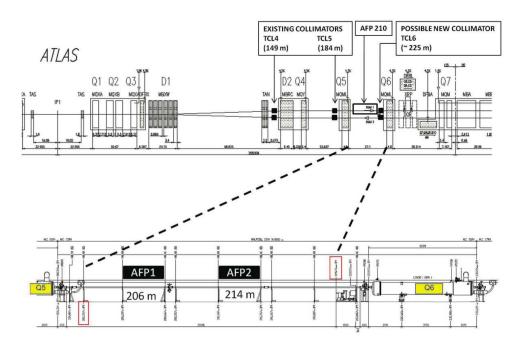

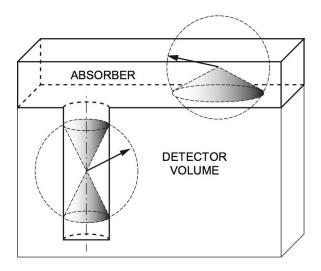

| U        | 6.1 |         | ATLAS Forward Physics                                                                                                                 |

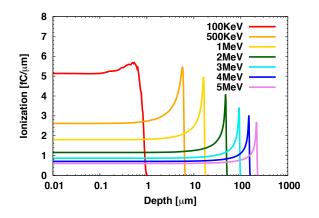

|          | 0.1 | 6.1.1   | 3D pixel detectors in un-homogenous irradiation conditions 236                                                                        |

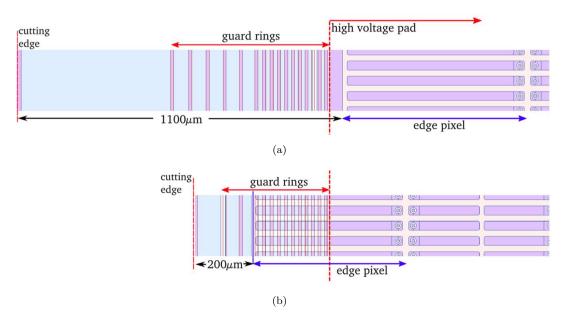

|          |     | 6.1.2   | Reduction of the edge extension in IBL 3D pixel sensors                                                                               |

|          |     | 0.1.2   | Laser scribe, cleave and Alumina sidewall passivation                                                                                 |

|          |     |         | Diamond saw cut                                                                                                                       |

|          | 6.2 | Plana   | r detectors with active-edges                                                                                                         |

|          | 0   | 6.2.1   | Computer aided design                                                                                                                 |

|          |     | 6.2.2   | Wafer layout                                                                                                                          |

|          |     | 6.2.3   | Fabrication process                                                                                                                   |

|          |     | 6.2.4   | Electrical characterization                                                                                                           |

|          |     | 6.2.5   | Functional characterization                                                                                                           |

|          | 6.3 |         | BD detectors with built-in charge multiplication                                                                                      |

|          |     | 6.3.1   | Design and technological aspects                                                                                                      |

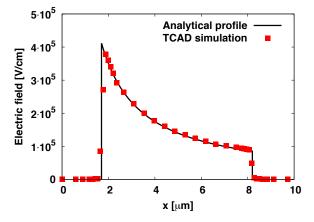

|          |     | 6.3.2   | TCAD simulation approach                                                                                                              |

|          |     |         |                                                                                                                                       |

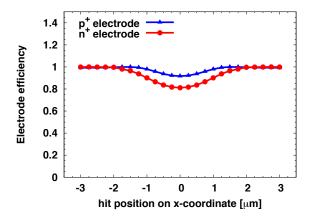

|    |                  |          | Electrode response calibration                             | . 255 |

|----|------------------|----------|------------------------------------------------------------|-------|

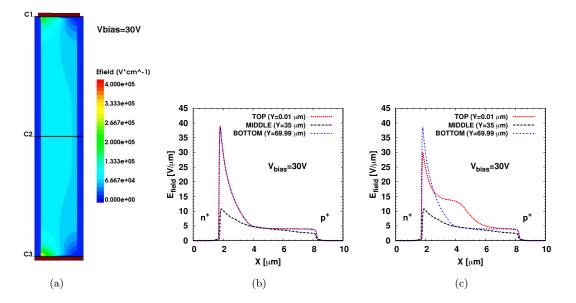

|    |                  |          | Surface isolation                                          | . 257 |

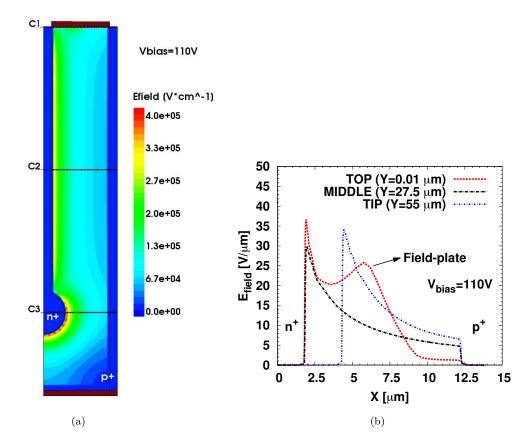

|    |                  |          | Simplified structure for charge multiplication simulations | . 258 |

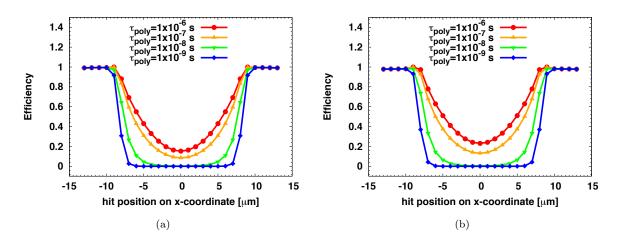

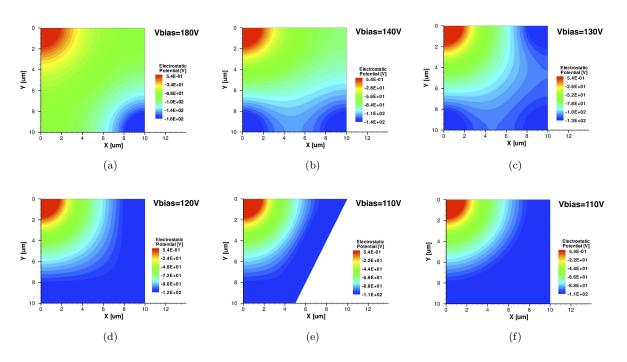

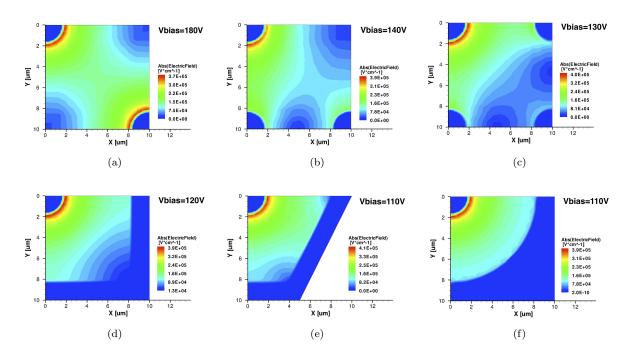

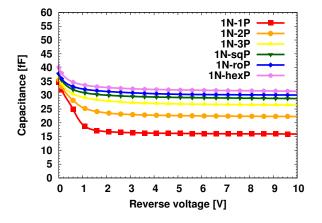

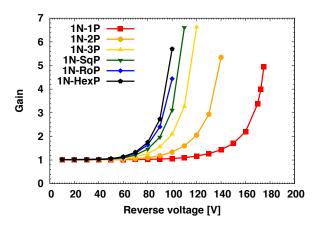

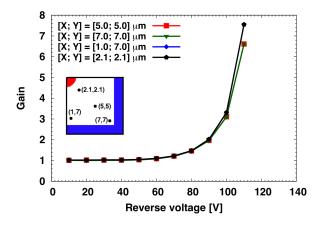

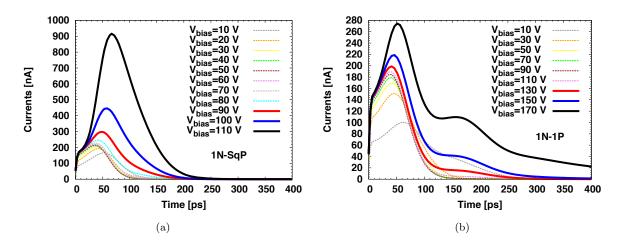

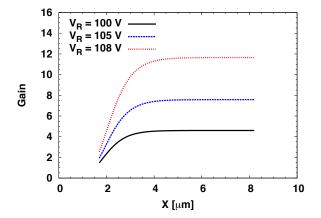

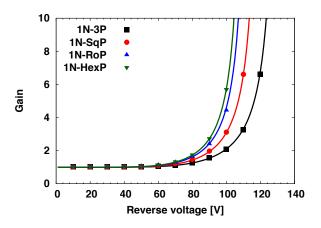

|    |                  | 6.3.3    | Charge multiplication results                              | . 260 |

|    |                  |          | Un-irradiated devices                                      | . 260 |

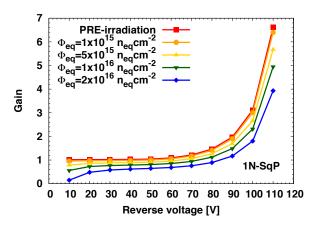

|    |                  |          | Post-irradiation                                           | . 264 |

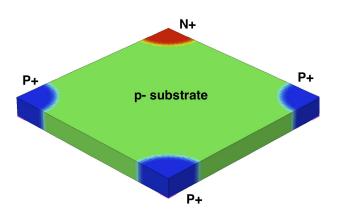

|    |                  |          | Simulation of a full 3D structure                          | . 265 |

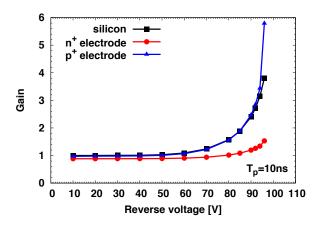

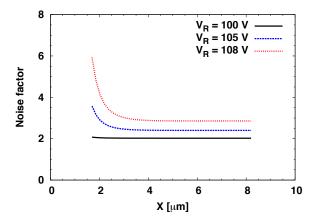

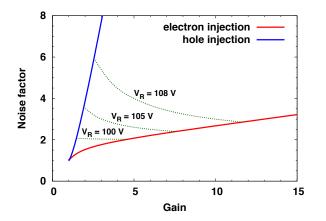

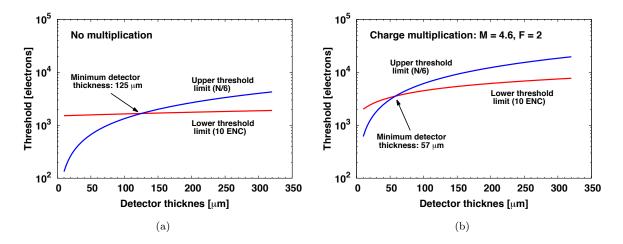

|    |                  | 6.3.4    | Noise considerations                                       | . 266 |

|    |                  |          | Noise factor calculation                                   | . 267 |

|    |                  |          | Effect of avalanche gain and noise on particle tracking    | . 271 |

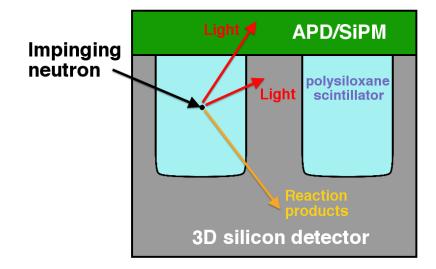

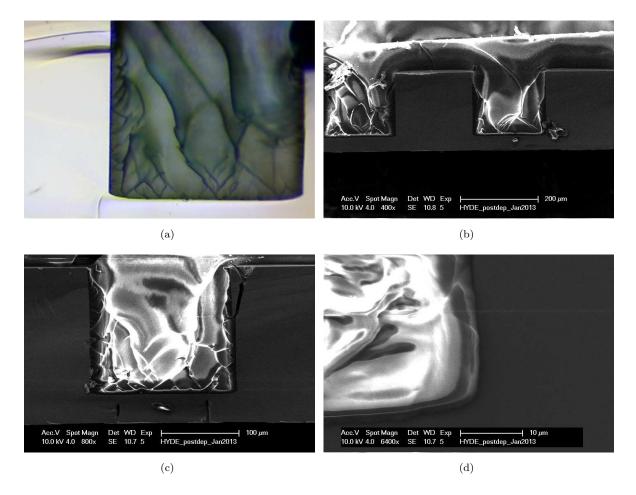

|    | 6.4              | HYbri    | d DEtectors for neutrons (HYDE)                            | . 274 |

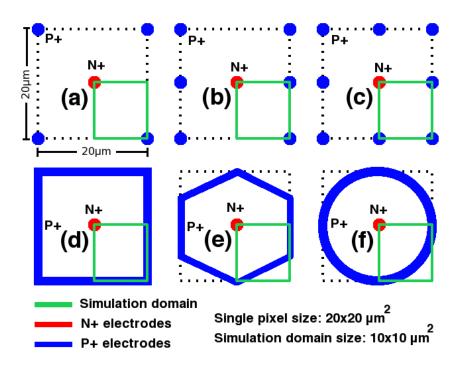

|    |                  | 6.4.1    | Computer aided design of the silicon detectors             | . 277 |

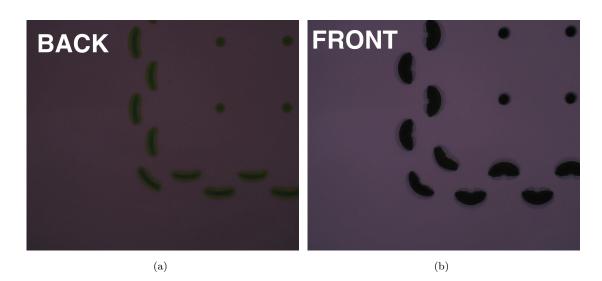

|    |                  | 6.4.2    | Wafer layout and fabrication                               | . 281 |

|    |                  | 6.4.3    | Electrical characterization                                | . 284 |

|    |                  | 6.4.4    | Sensor assembly                                            | . 287 |

|    |                  | 6.4.5    | Preliminary functional characterization                    | . 290 |

| 7  | Con              | nclusion | ns and future plans                                        | 295   |

| Bi | Bibliography 299 |          |                                                            | 299   |

## List of Tables

| 3.1 | Main features of both batches of 3D-DDTC devices fabricated at FBK [85].     | 89  |

|-----|------------------------------------------------------------------------------|-----|

| 3.2 | Summary of electrical and geometrical parameters of the first DDTC batch     |     |

|     | realized on n-type substrates extracted from test structures $[85]$          | 92  |

| 3.3 | Summary of electrical and geometrical parameters of the DTC-2 and DTC-       |     |

|     | 2B batches realized on p-type substrates extracted from test structures      |     |

|     | [85]                                                                         | 98  |

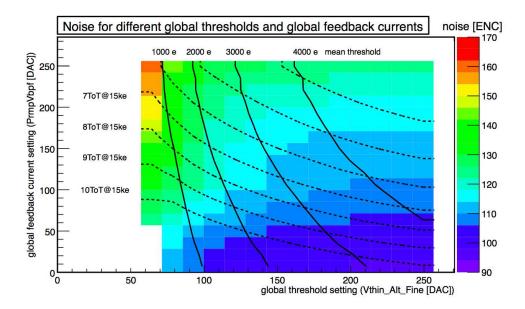

| 3.4 | Summary of threshold and noise parameters for the three available pixel      |     |

|     | configurations of sensor coming from the DTC-2 batch at a bias voltage of    |     |

|     | 35 V [96]. Values are compared with expected pixel capacitance               | 102 |

| 3.5 | Summary of irradiated DTC-2 devices. Device type, radiation fluence, type    |     |

|     | of particle used, and irradiation facility are reported. [102]               | 107 |

| 3.6 | Threshold and noise for the considered irradiated assemblies [102]           | 108 |

| 3.7 | Hit efficiency and charge sharing probability for the two irradiated sensors |     |

|     | and an un-irradiated as a function of the impinging track angle for a bias   |     |

|     | voltage of 80 V [103]. $\ldots$                                              | 111 |

| 3.8 | Mean cluster charge and mean cluster size for the two irradiated samples     |     |

|     | with respect to an un-irradiated one at 80 V of bias $[103]$                 | 113 |

| 4.1 | Most important layout parameters of the ATLAS IBL [110]                      | 120 |

| 4.2 | Basic performance requirements for the IBL modules. (*) After full dose;     |     |

|     | SEU stands for Single Event Upset [110]                                      | 121 |

| 4.3 | Main specifications of the FE-I4 readout chip [113]                          | 123 |

| 4.4 | Summary of the main IBL design specifications for 3D pixel detectors [124].  | 138 |

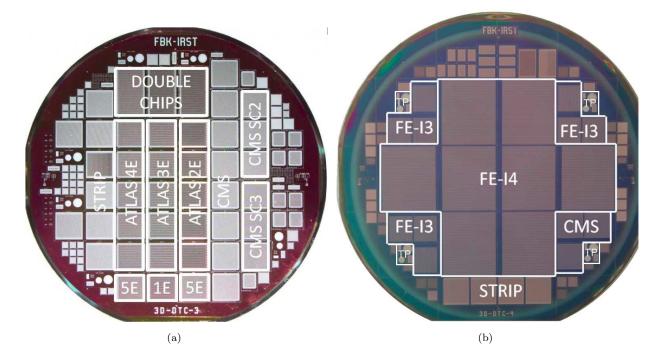

| 4.5 | Yield of all 3D batches fabricated for the IBL [126]                         | 142 |

| 4.6 | Summary of all the R&D and IBL production batches fabricated at FBK.         |     |

|     | The different edge protection are shown together with the implanted p-spray  |     |

|     | dose. The wafer layout type for each batch is also reported [129]            | 145 |

|     |                                                                              |     |

| 4.7  | Available planar test structures and their size. The parameters extracted<br>from electrical characterization are also reported: $t_{ox}$ and $Q_{ox}$ are the oxide<br>thickness and the oxide charge concentration, $R_{implant}$ and $R_{contact}$ are the<br>resistivity and the Hall coefficient of the n <sup>+</sup> implantations and the contact,<br>$C_{AC}$ is the value of the MOS capacitor realized on a highly doped substrate,<br>$s_0$ is the surface recombination velocity and $J_{bulk}$ , $V_{FD}$ and $N_{bulk}$ are the<br>bulk leakage current density, the full depletion voltage and the bulk doping<br>concentration | 151 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

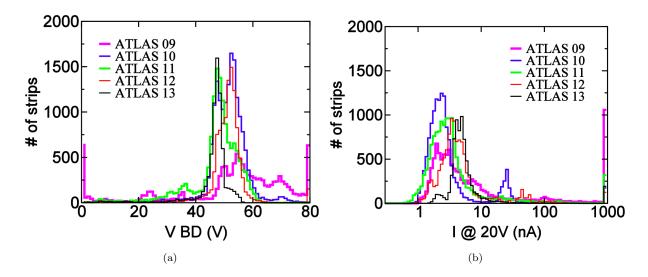

| 4.8  | Summary of the extracted process parameters measured from standard planar test structures for all the batches with passing through columns. Reported values are: the leakage current density $J_{bulk}$ , the carrier lifetimes $\tau_{n,p}$ , the breakdown voltage $V_{BD}$ , the surface recombination velocity $s_0$ and the oxide charge concentration $Q_{ox}$ [129]                                                                                                                                                                                                                                                                      | 153 |

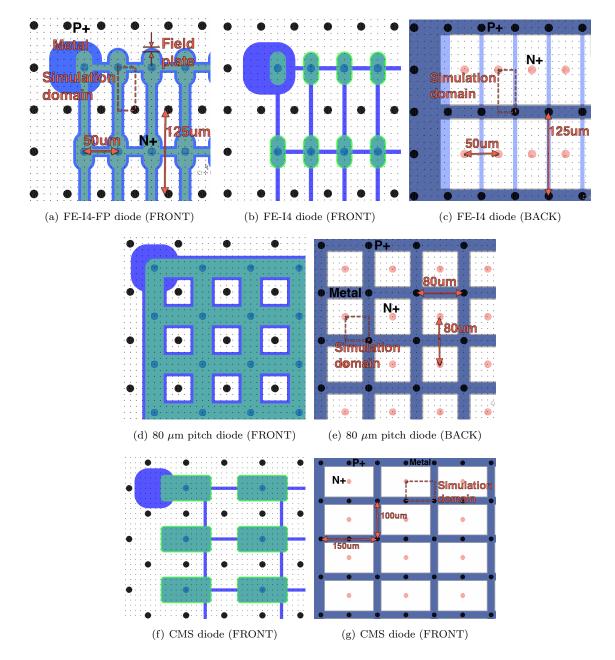

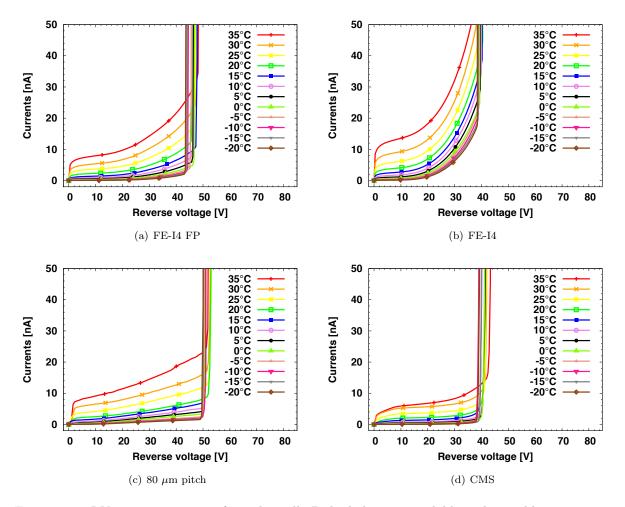

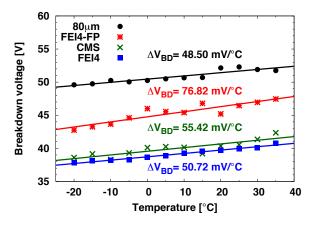

| 4.9  | Summary of the most important parameters of devices under test [130]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 155 |

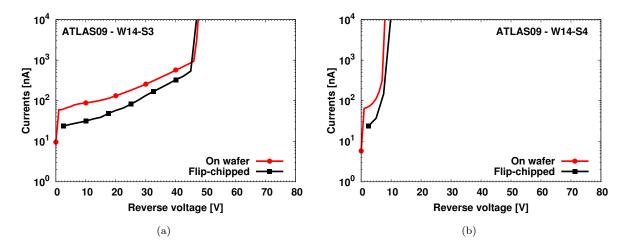

| 4.10 | Summary of measured and simulated values of breakdown voltage, leakage current/slope and capacitance [130]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 161 |

| 4.11 | Summary of the main electrical parameters of the considered 3D strip detectors [132]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 172 |

| 4.12 | Electrical specifications for the on-wafer electrical selection of the pixel sensors for the IBL [124]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 173 |

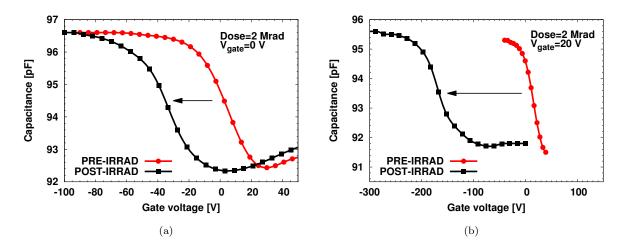

| 4.13 | Comparison between oxide charge values before and after irradiation, with-<br>out (a) and with bias (b).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178 |

| 4.14 | Summary of the devices irradiated at Los Alamos with 800 MeV protons.<br>Devices type, wafer and batch of origin are also reported together with the<br>requested and received fluences.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181 |

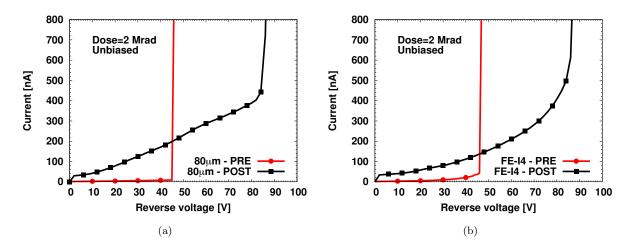

| 4.15 | Summary of the most important electrical parameters measured on irra-<br>diated devices. Device type and received fluence are report along with:<br>intrinsic breakdown voltage estimated from pre-irradiation measurements<br>and simulations ( $V_{BD-PRE}$ ), measured breakdown voltage after irradiation<br>( $V_{BD-POST}$ ) at -20 °C, reverse current density after irradiation for a com-<br>mon voltage of -55 V at a temperature of -20 °C and calculated damage                                                                                                                                                                     |     |

| 4.16 | constants ( $\alpha$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | together with received fluence and the type of performed tests $[113]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 198 |

| 1.11 | Summary of all the FBK modules characterized in beam test reporting the                                                                                                 |   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|      | most valuable results found together with tuning and irradiation parameters:                                                                                            |   |

|      | sample ID, applied bias voltage, magnetic field on/off, tilt angle in the $\phi$                                                                                        |   |

|      | direction, type of particle used for the irradiation, received dose, hit efficiency,                                                                                    |   |

|      | ToT to charge tuning and used threshold [113]                                                                                                                           | 2 |

| 4.18 | Summary of the parameters extracted from the laboratory characterization                                                                                                |   |

|      | and numerical simulation of CMS pixel detectors fabricated at FBK and                                                                                                   |   |

|      | coming front the ATLAS08 batch. Breakdown voltage $(V_{BD})$ , leakage                                                                                                  |   |

|      | current $(I_{LK})$ , signal to noise ratio and the corresponding simulated values                                                                                       |   |

|      | are here reported [138]                                                                                                                                                 | ) |

| 5.1  | Summary of the physical models used in the performed simulations 221                                                                                                    | L |

| 6.1  | Most important process parameters extracted from the the measurements                                                                                                   |   |

|      | on planar test structures: $V_{FD}$ is the full depletion voltage, $I_{LK}$ is leakage                                                                                  |   |

|      | current density, $\tau_g$ is the bulk generation lifetime, $t_{ox}$ is the oxide thickness,                                                                             |   |

|      |                                                                                                                                                                         |   |

|      | $N_{ox}$ is the oxide charge concentration and $s_0$ is surface recombination velocity.                                                                                 |   |

|      | $N_{ox}$ is the oxide charge concentration and $s_0$ is surface recombination velocity.<br>The original process is the one with non optimized trench widths while the   |   |

|      |                                                                                                                                                                         |   |

|      | The original process is the one with non optimized trench widths while the modified process is the one providing better trenches and optimized surface                  |   |

| 6.2  | The original process is the one with non optimized trench widths while the modified process is the one providing better trenches and optimized surface properties [155] | ; |

| 6.2  | The original process is the one with non optimized trench widths while the modified process is the one providing better trenches and optimized surface properties [155] | ; |

| 6.2  | The original process is the one with non optimized trench widths while the modified process is the one providing better trenches and optimized surface properties [155] |   |

# List of Figures

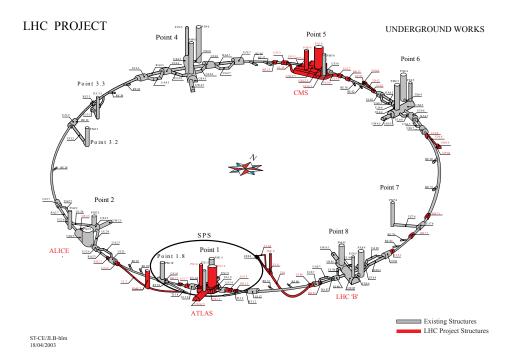

| The layout of the Large Hadron Collider. Newer structures are represented  |                                                       |

|----------------------------------------------------------------------------|-------------------------------------------------------|

| in red while older structures are represented in grey                      | 2                                                     |

| Superconducting dipole magnets of the Large Hadron Collider. (CERN-AC-     |                                                       |

| 0911188 ©CERN)                                                             | 3                                                     |

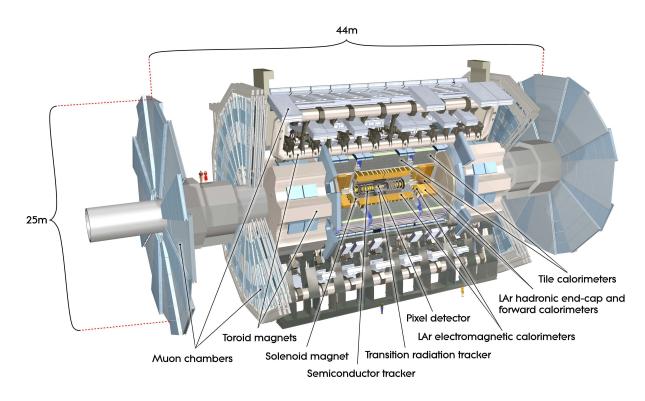

| Sketch of the ATLAS particle detector. (CERN-GE-0803012 01) $\ldots$ .     | 5                                                     |

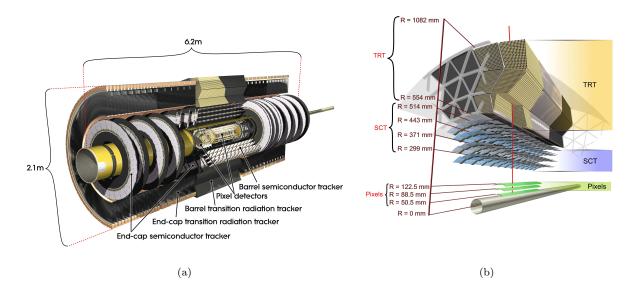

| The ATLAS Inner Detector (a) and its expanded cross-section (b). (CERN-    |                                                       |

| GE-0803014)                                                                | 7                                                     |

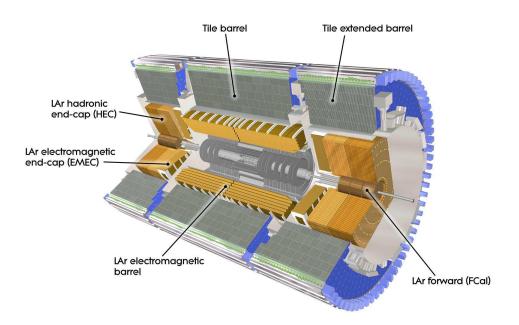

| Computer generated image of the ATLAS Calorimeters system. (CERN-          |                                                       |

| GE-0803015 01 )                                                            | 8                                                     |

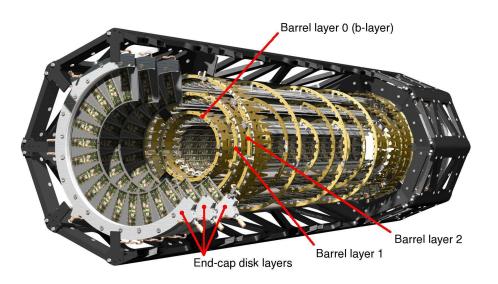

| Sketch of the active region of the ATLAS pixel detector showing the barrel |                                                       |

| and the end-cap disks. (CERN-GE-0803013 02 ) $\ldots$ $\ldots$             | 10                                                    |

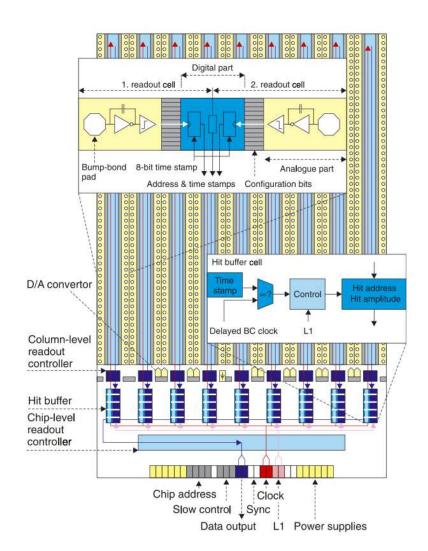

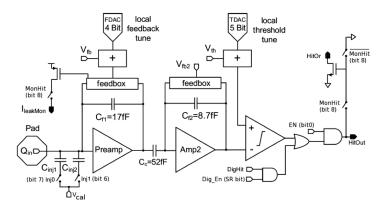

| Schematic blocks of the FE-I3 readout chip. Image from reference [9]       | 11                                                    |

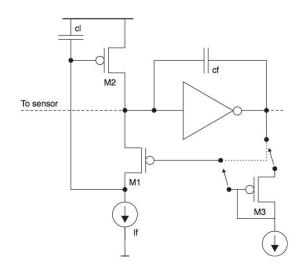

| Schematic implementation of the FE-I3 charge amplifier feedback circuit.   |                                                       |

|                                                                            | 12                                                    |

|                                                                            |                                                       |

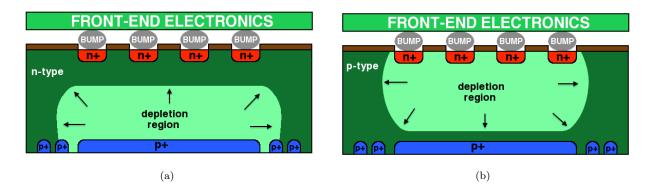

|                                                                            | 13                                                    |

|                                                                            |                                                       |

|                                                                            | 14                                                    |

|                                                                            | 16                                                    |

|                                                                            | 18                                                    |

|                                                                            |                                                       |

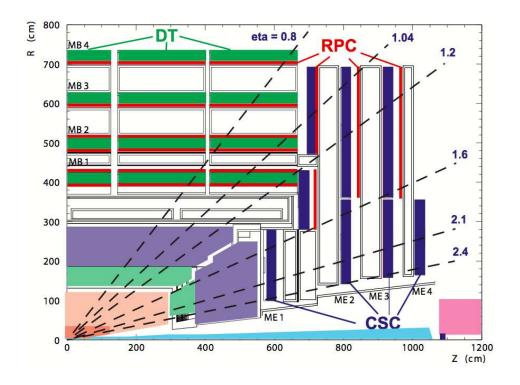

|                                                                            | 19                                                    |

|                                                                            | 21                                                    |

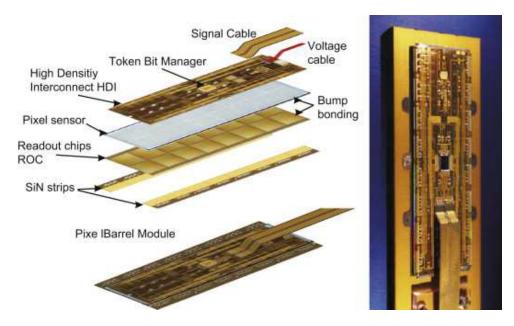

|                                                                            | 22                                                    |

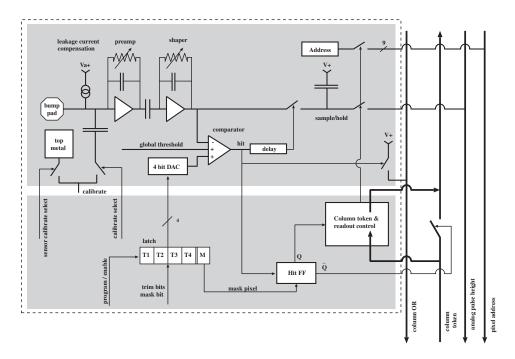

|                                                                            | 24                                                    |

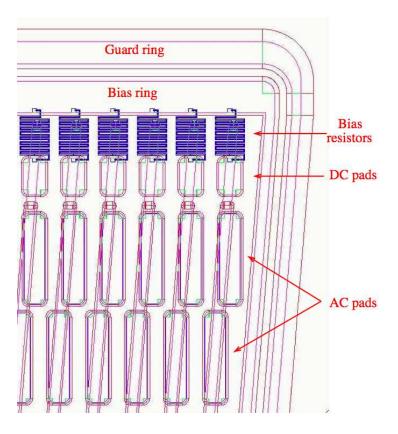

|                                                                            |                                                       |

| Figure from reference [22]                                                 | 26                                                    |

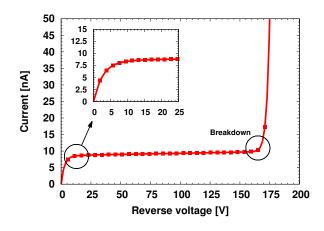

| Current of a semiconductor diode in reverse bias.                          | 37                                                    |

|                                                                            | in red while older structures are represented in grey |

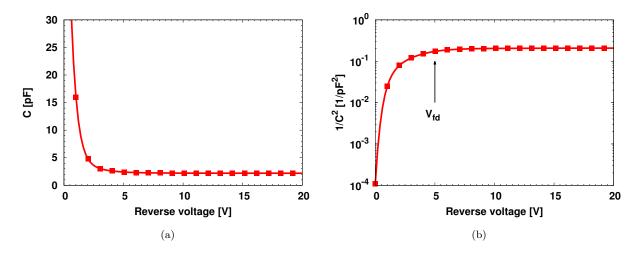

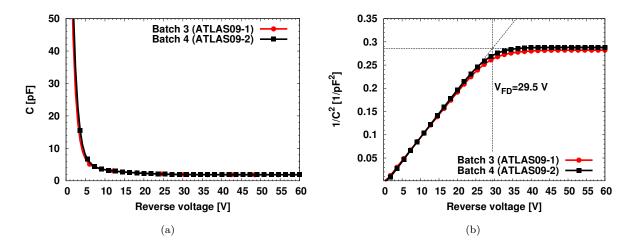

| 2.2      | Capacitance measurements on a silicon diode, capacitance versus reverse voltage (a) and $1/C^2$ versus reverse voltage (b)                                | 38  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

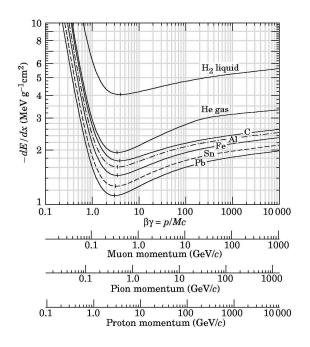

| 2.3      | Energy loss of different particles in different materials as a function of their                                                                          |     |

| 2.0      | energy.                                                                                                                                                   | 40  |

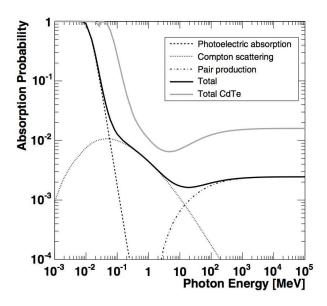

| 2.4      | Probability of photon absorption in a 300 $\mu$ m silicon layer as function of the                                                                        | 10  |

| 2.1      | photon energy. For comparison with high- $Z$ materials, the same function is                                                                              |     |

|          | plotted for CdTe [30]                                                                                                                                     | 42  |

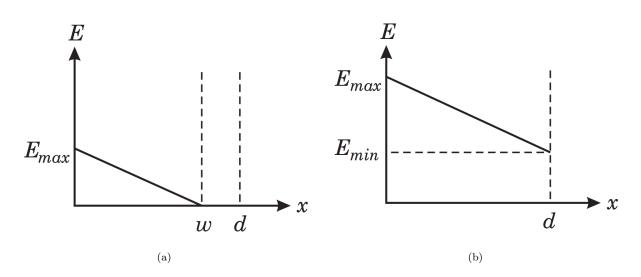

| 2.5      | Electric field distribution in a non-depleted pn-junction (a) and in an                                                                                   | 74  |

| 2.0      | over-depleted pn-junction (b) [29]                                                                                                                        | 43  |

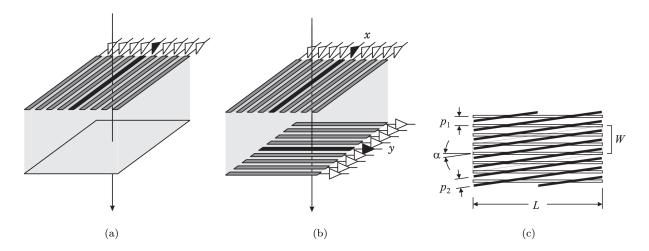

| 2.6      | Electrode segmentation in a strip detector: single sided segmentation (a),                                                                                | 10  |

| 2.0      | double sided segmentation (b) and small stereo angle between strips on                                                                                    |     |

|          | opposite sides (c) [29]                                                                                                                                   | 45  |

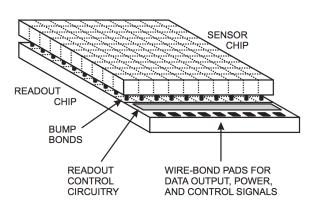

| 2.7      | Sketch of the connection of an hybrid pixel sensor to its readout chip through                                                                            | 40  |

| 2.1      | bump bonds. The wire bond pads to connect the chip to the external system                                                                                 |     |

|          | are also shown [29]                                                                                                                                       | 46  |

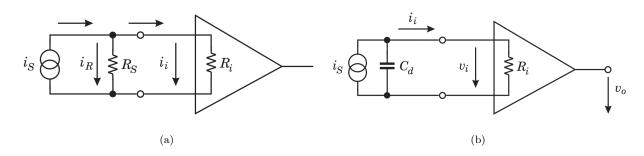

| <u> </u> |                                                                                                                                                           | 40  |

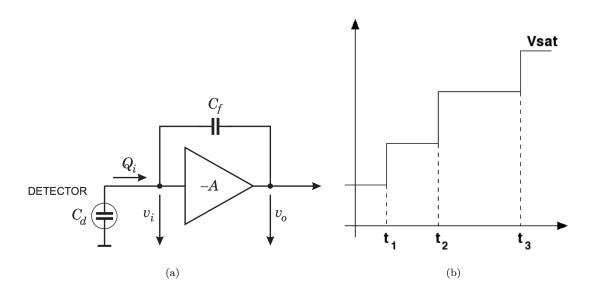

| 2.8      | Current-sensitive amplifier with input current source and parallel resistor (a) and with conscitive input $(h)$ [20]                                      | 48  |

| 2.0      | (a) and with capacitive input (b)[29]                                                                                                                     | 40  |

| 2.9      | Ideal Charge Sensitive Amplifier configuration [29] (a) and output voltage                                                                                | 40  |

| 0.10     | saturation without reset circuit (b). $\dots \dots \dots$ | 49  |

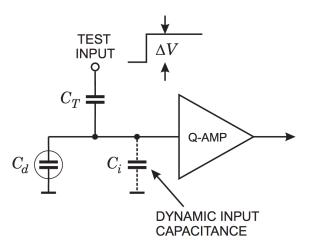

| 2.10     | Charge Sensitive Amplifier with test input $(C_t)$ for charge calibration                                                                                 | F 1 |

| 0.11     | purposes [29]                                                                                                                                             | 51  |

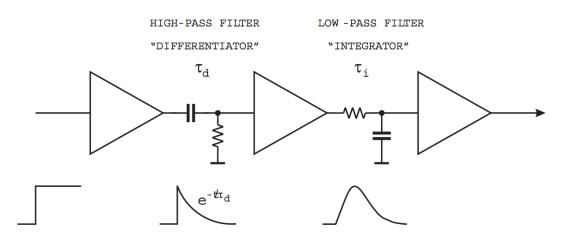

| 2.11     | Basic scheme of a CR-RC shaper. The different stages are separated by                                                                                     | ٣1  |

| 0.10     | buffers. [29]                                                                                                                                             | 51  |

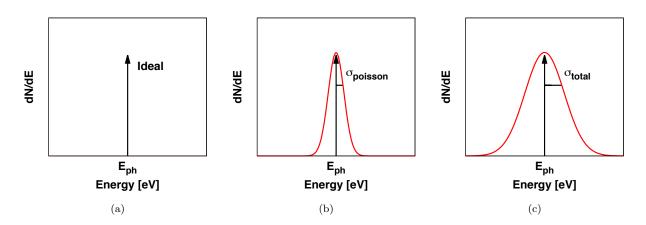

| 2.12     | Ideal spectrum measurement without fluctuations (a) with poisson (b) and                                                                                  | 50  |

| 0.10     | with both poisson and electronics fluctuation.                                                                                                            | 53  |

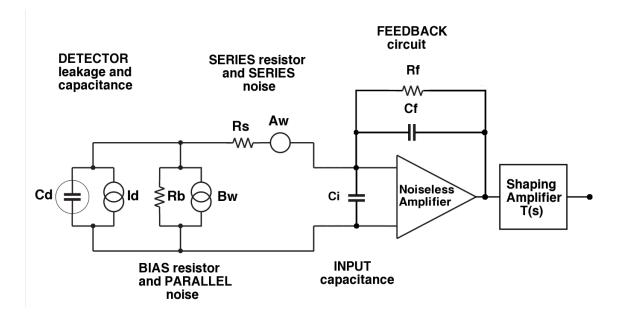

|          | Schematic model of all the noise sources in a readout system                                                                                              | 54  |

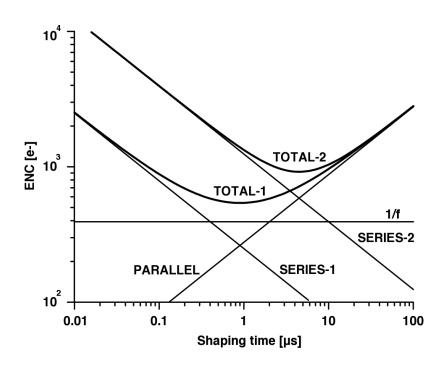

| 2.14     | Summary of the different contributions to the ENC. Parallel, series and 1/f                                                                               |     |

|          | noise are plotted with respect to the shaping time. The plot also shows                                                                                   |     |

|          | how an increase of series noise from SERIES-1 to SERIES-2, moves the                                                                                      | •   |

|          | minimum of the ENC from TOTAL-1 to TOTAL-2 [29]                                                                                                           | 56  |

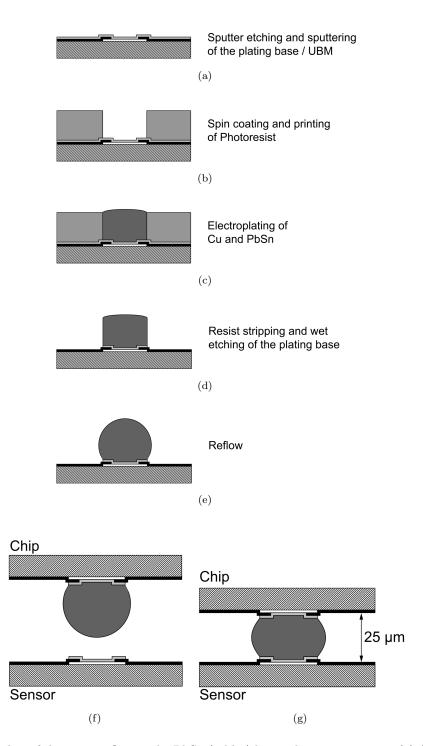

| 2.15     | Sketches of the process flow in the PbSn (solder) bump deposition process                                                                                 |     |

|          | (a)-(e) and flip-chip of the electronics die to the sensor (f)-(g) [30]                                                                                   | 59  |

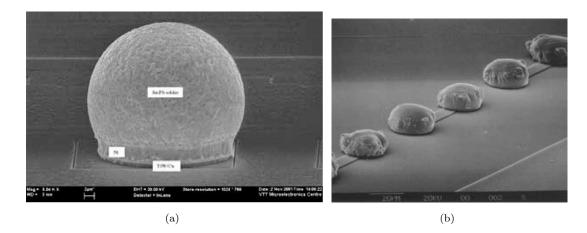

| 2.16     | Comparison between a scanning electron microscope image of a deposited                                                                                    |     |

|          | solder bump (a) with a micrograph of indium bumps deposited on silicon                                                                                    |     |

|          | (b) [30]                                                                                                                                                  | 60  |

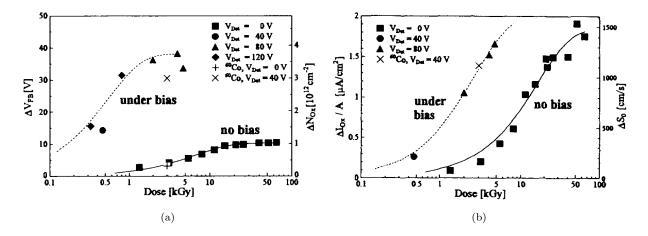

| 2.17     | Evolution of radiation induced oxide charge (a) and surface recombination                                                                                 |     |

|          | velocity (b) [48]                                                                                                                                         | 62  |

| 2.18 | Monte-Carlo simulation of a recoil atom track with primary energy equal to 50 keV [49]                                                                                                                                                                                                                                                                                 | 63 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

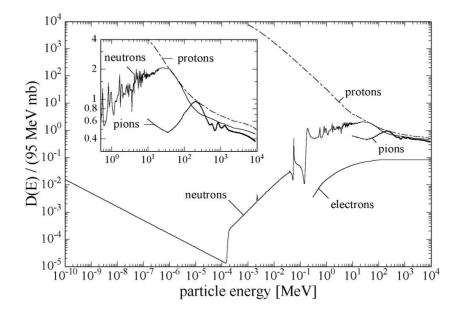

| 2.19 | Displacement damage function D(E) normalized to 95 MeV mb, for different type of particles [49]                                                                                                                                                                                                                                                                        | 64 |

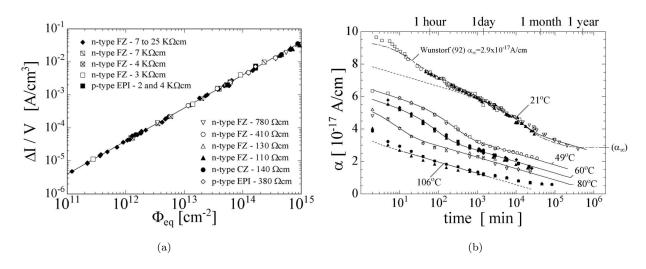

| 2.20 | Fluence dependence of the leakage current for devices produced on different materials after a thermal treatment at 60 °C for 80 min (a) and dependence of the damage constant $\alpha$ on the annealing time (b) [49]                                                                                                                                                  | 65 |

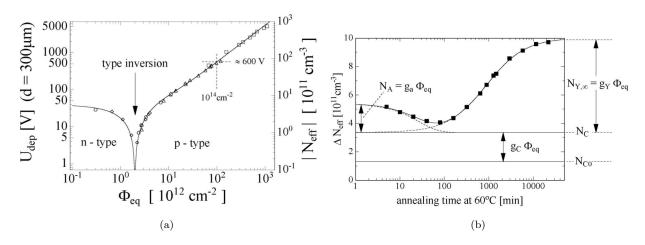

| 2.21 | Variation of the effective doping concentration of an n-type silicon material as a function of the equivalent particle fluence (a) and its annealing behavior as a function of time at 60 °C after irradiation at a fluence of $1 \times 10^{13} n_{eq}/\text{cm}^2$ [49].                                                                                             | 66 |

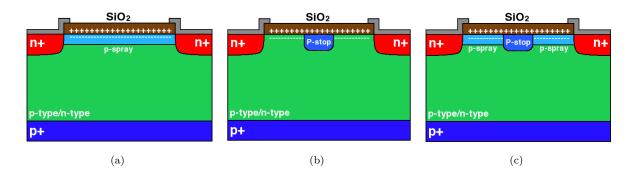

| 2.22 | Different surface isolation techniques: p-spray (a), p-stop (b) and moderated p-spray (c).                                                                                                                                                                                                                                                                             | 69 |

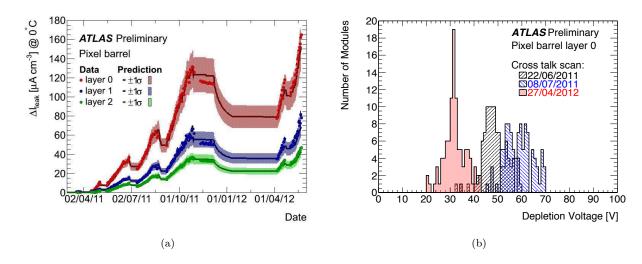

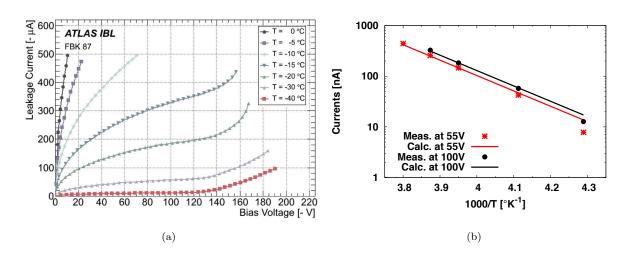

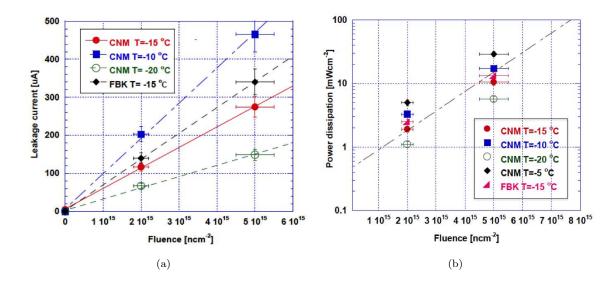

| 3.1  | Increase in leakage current (a) and change in depletion voltage (b) in the ATLAS tracker as a function of the operation date [60]                                                                                                                                                                                                                                      | 72 |

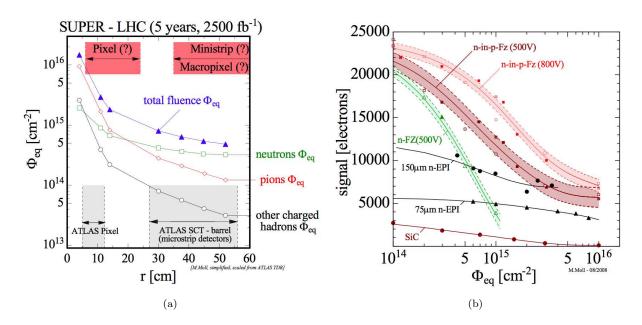

| 3.2  | Expected radiation fluence in sLHC as function of the distance from the interaction point (a) and reduction in charge collection efficiency measured on irradiated sensors in different R&D activities [61].                                                                                                                                                           | 73 |

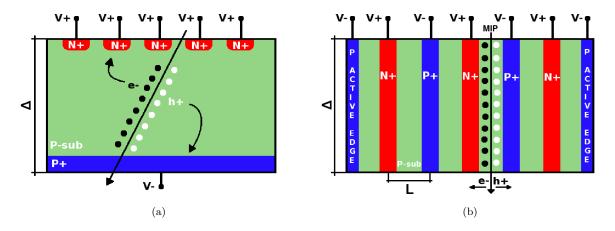

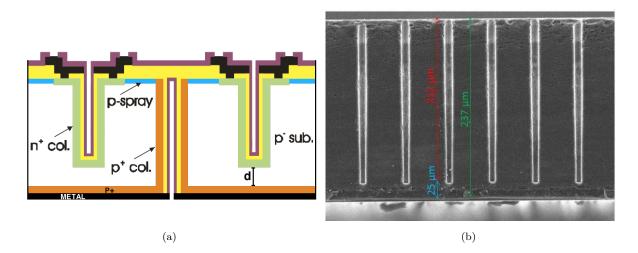

| 3.3  | Comparison between planar (a) and 3D (b) sensor architectures                                                                                                                                                                                                                                                                                                          | 74 |

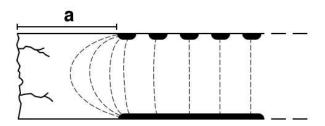

| 3.4  | Cross-section sketch of a saw cut standard device, showing the depleted region extending toward the cut region. The distance "a" indicates the space needed to insert guard-rings and to safely operate the device at high voltage.                                                                                                                                    | 76 |

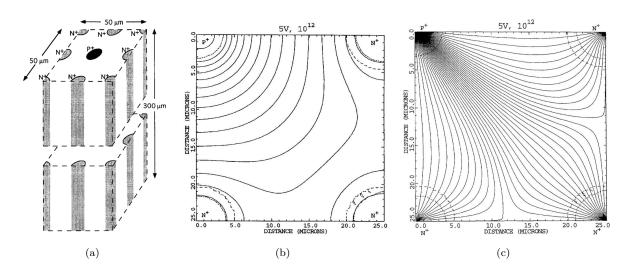

| 3.5  | Simulation results of full 3D detectors. Elementary cell of a 3D detector (a), simulated equipotential lines for a quarter of elementary cell with bulk doping equal to $10^{12}$ cm <sup>-3</sup> and bias voltage equal to 5V (b) and drift lines in the same conditions (c) [63].                                                                                   | 77 |

| 3.6  | Electric field distributions (c) [65]. Electric applied biases, extracted along the drift lines connecting a $p^+$ electrode to an $n^+$ electrode (a) and along drift lines connecting an $n^+$ to another $n^+$ electrode (b). The bulk doping concentration is equal to $10^{12}$ cm <sup>-3</sup> reverse biases are equal to 0, 5, 10, 20, 30, 40 and 50 V. [63]. | 78 |

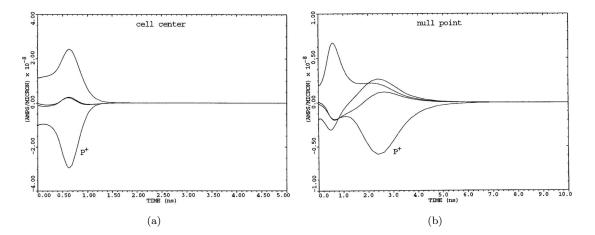

| 3.7  | Readout electrode current in response to a MIP particle crossing the device<br>in the center of a quarter of an elementary cell (a) and in the zero field<br>point of the same structure $(N_D=10^{12} \text{ cm}^{-3})$ [63].                                                                                                                                         | 78 |

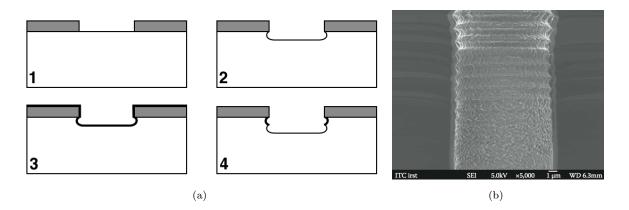

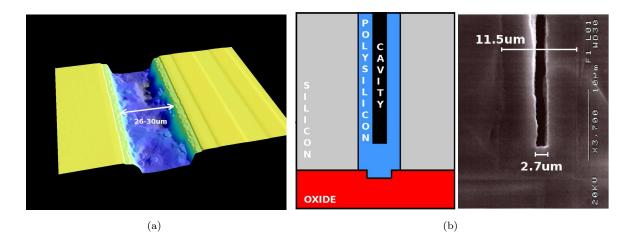

| 3.8  | Deep Reactive Ion Etching process sketch (a) showing most relevant steps:                   |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | structure definition $(a.1)$ , first etch step $(a.2)$ , hole passivation $(a.3)$ and       |    |

|      | following etch step (a.4). Example of DRIE hole also showing the resulting                  |    |

|      | scalloping effect (b) [65]. $\ldots$                                                        | 79 |

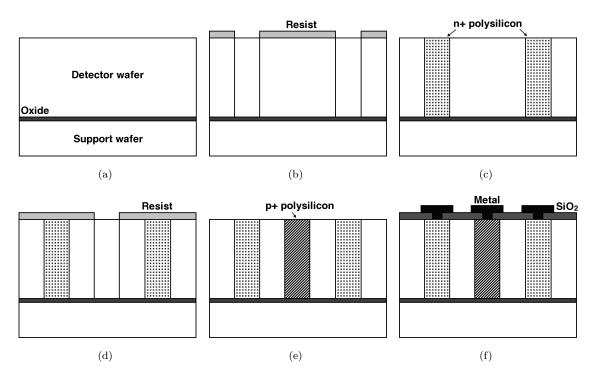

| 3.9  | Schematic representation of the most relevant fabrication steps for full 3D                 |    |

|      | detectors, the description is given in the text.                                            | 80 |

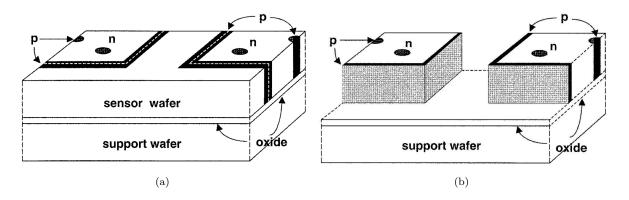

| 3.10 |                                                                                             |    |

|      | at the same time (a). After device fabrication the surplus material has to                  | 01 |

|      | be etched away (b) [71]. $\ldots$                                                           | 81 |

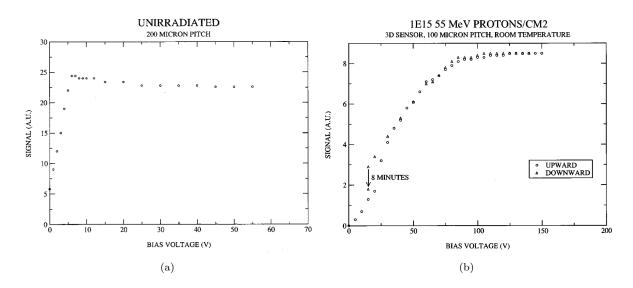

| 3.11 | Infrared laser tests showing signal amplitude versus bias voltage in pre-                   |    |

|      | irradiation condition (a) and post-irradiation with 55 MeV protons at                       |    |

|      | $1 \times 10^{15} n_{eq}/cm^{-2}$ [70]                                                      | 83 |

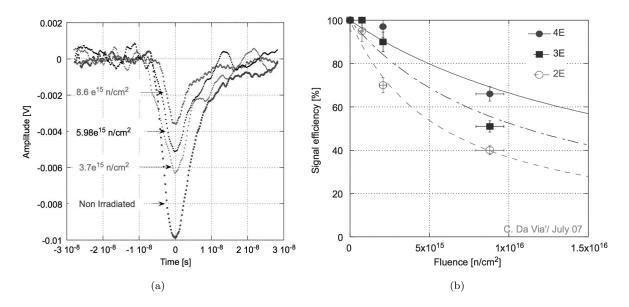

| 3.12 | Infra-red (1060 nm) pulsed laser measurements on a silicon 3D detector                      |    |

|      | (averaged 1000 times), for different radiation fluences are compared (a) [74].              |    |

|      | Signal efficiency versus fluence (b) [73]                                                   | 84 |

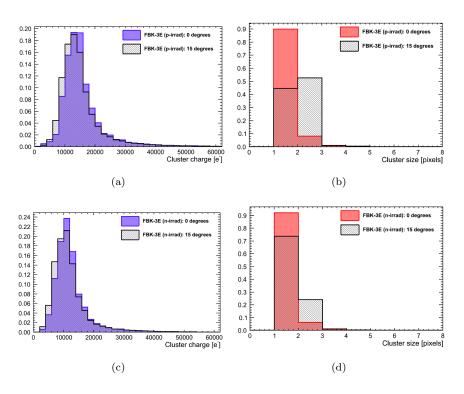

| 3.13 | Measured cluster charge distribution for a 100 GeV pion beam with different $% \mathcal{A}$ |    |

|      | incident angle: 0 $^\circ$ angle (perpendicular to the device surface) (a) and 15 $^\circ$  |    |

|      | angle (b) [75]                                                                              | 84 |

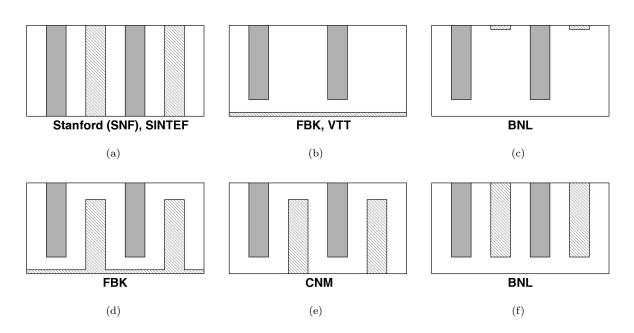

| 3.14 | Schematic representations of all the proposed approaches to the 3D technol-                 |    |

|      | ogy: the original architecture (a) is compared with: Single Type Column                     |    |

|      | implementations from FBK/VTT (b) and BNL (c), Double Sided Double                           |    |

|      | Type Columns from FBK (d) and from CNM (e) and finally the single sided                     |    |

|      | double type column from BNL (e).                                                            | 86 |

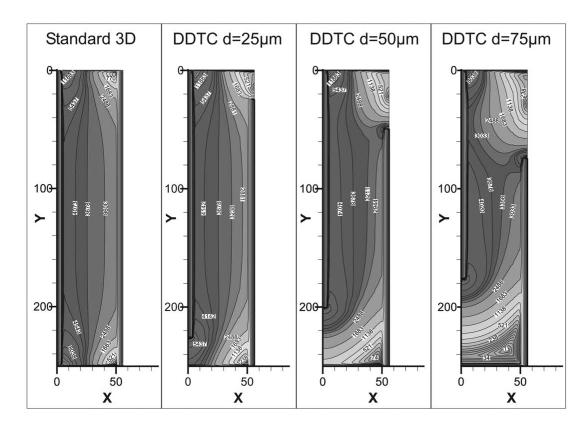

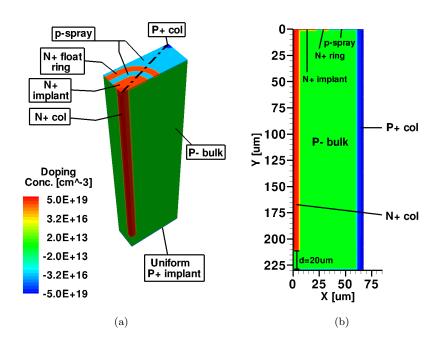

| 3.15 | Simulated electric field distribution extracted from a plane crossing the                   |    |

|      | diagonal between two electrodes of opposite doping types. The junction                      |    |

|      | column is placed at x=0 $\mu$ m and the ohmic column is placed at x=40 $\mu$ m.             |    |

|      | From left to right the distance between the electrode tip and opposite                      |    |

|      | surface is modified from 0 to 75 $\mu$ m in steps of 25 $\mu$ m [85]                        | 88 |

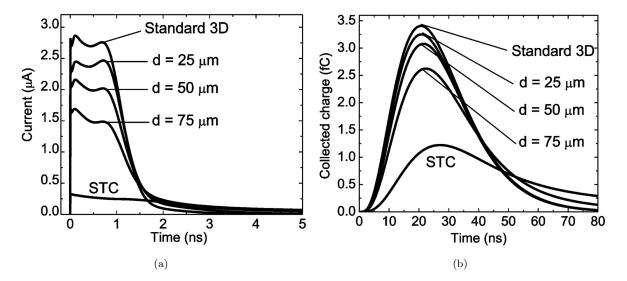

| 3.16 | Transient simulations of 3D detectors hit by a minimum ionizing particle.                   |    |

|      | Different geometries are tested differing in the tip to opposite surface                    |    |

|      | distance. Applied bias voltage is 16 V. Induced signals are reported in (a)                 |    |

|      | and equivalent shaped signals after a $CR-RC^3$ shaper are shown in (b) [85].               | 88 |

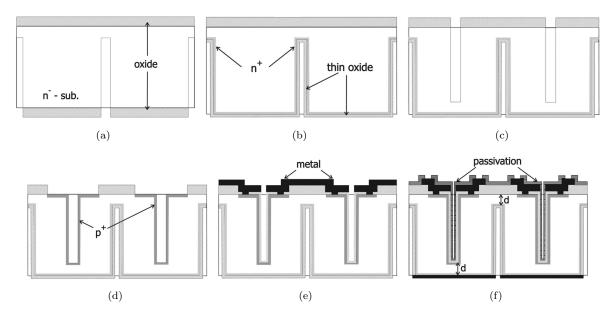

| 3.17 | Main fabrication steps of FBK 3D-DDTC detectors realized on n-type                          |    |

| 0.11 | substrate. Description in the text [85]                                                     | 90 |

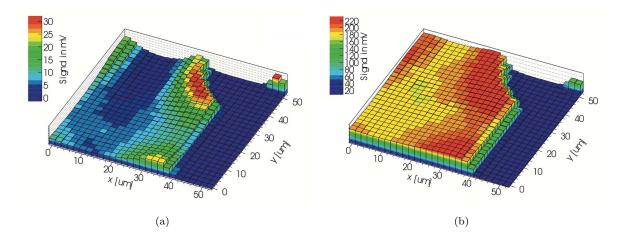

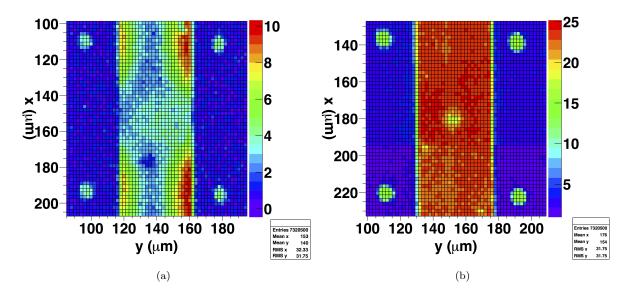

| 3 18 | Laser scans performed at 0.5 V of bias (a) and at 40 V of bias (b). The                     | 00 |

| 0.10 | scanned region corresponds to a cell of size $50 \times 50 \ \mu\text{m}^2$ and the x and y |    |

|      | step is equal to $2 \ \mu m$ [84]                                                           | 93 |

|      | stop is equal to $2 \mu \mathrm{m}$ [e.].                                                   | 50 |

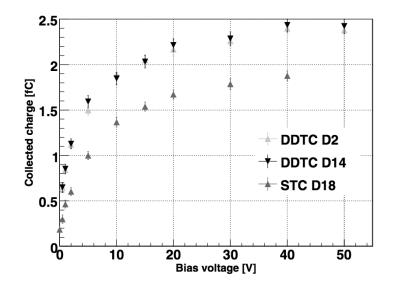

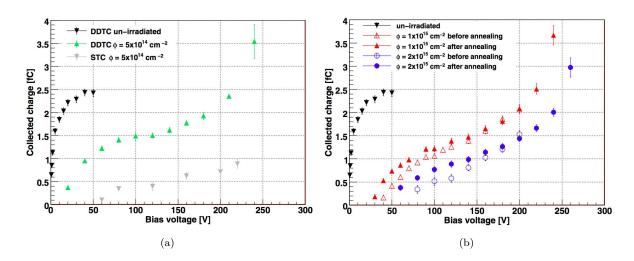

| Charge collection as a function of applied bias voltage for two 3D-DDTC<br>strip detectors in response to MIP particles. An STC device is reported for<br>comparison [84]                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

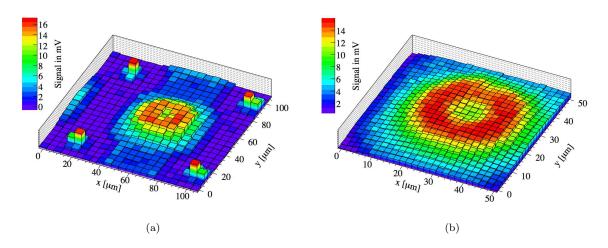

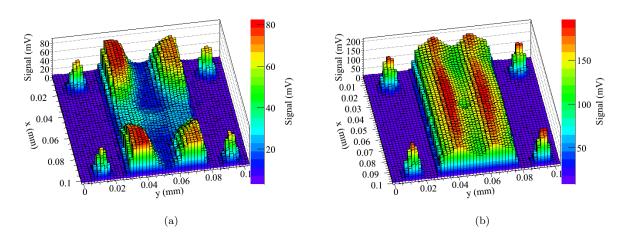

| Laser scan results for a 3D strip detector irradiated at $5 \times 10^{14} n_{eq}/\text{cm}^2$ for<br>a bias voltage of 10 V. Large area scan with 5 $\mu$ m step (a) and finer scan of<br>the inner region with 2 $\mu$ m step (b) [84] |

| Comparison between the pre-irradiation and the post-irradiation collected charge for DTC-1 strip detectors irradiated at different fluences: $5 \times 10^{14} n_{eq}/cm^2$                                                              |

| (a) and $1 \times 10^{15} n_{eq}/\text{cm}^2$ and $2 \times 10^{15} n_{eq}/\text{cm}^2$ (b) [84]                                                                                                                                         |

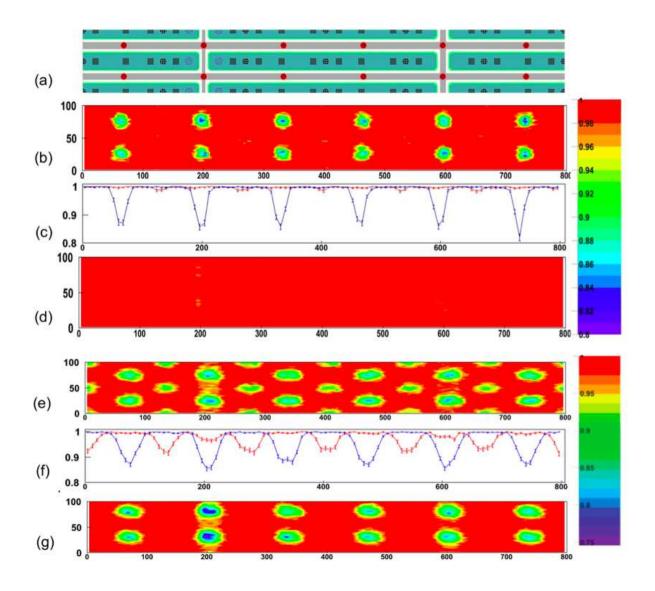

| Pre-irradiation laser scans performed on a DTC-2 strip detector for two different bias voltages: 5 V (a) and 60 V (b) [94]                                                                                                               |

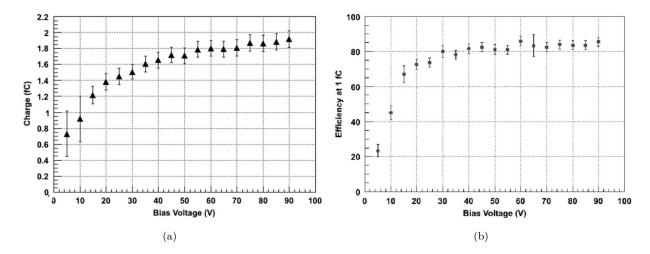

| Beta particle results for a DTC-2 strip detector in pre-irradiation conditions.<br>Collected charge (a) and sensor efficiency (b) are here shown [94] 100                                                                                |

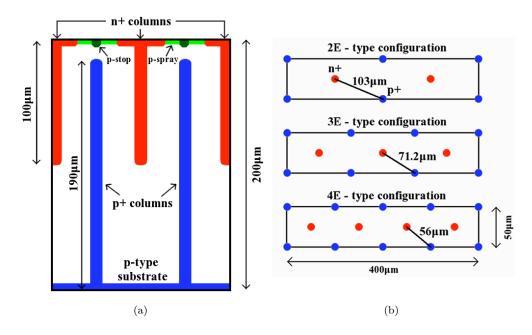

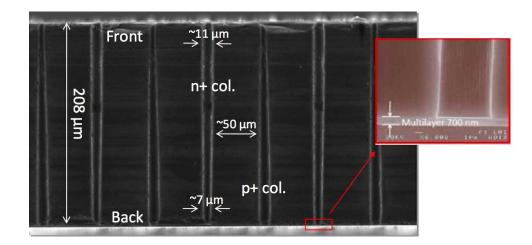

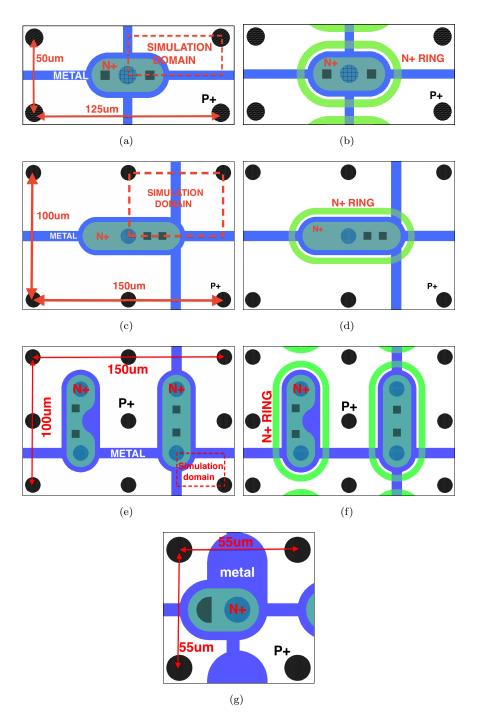

| Cross-section of a 3D-DDTC device coming from the DTC-2 batch (a) and available FE-I3 pixel configurations (b) [102]                                                                                                                     |

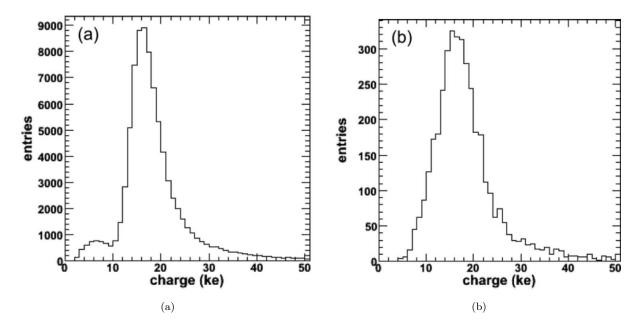

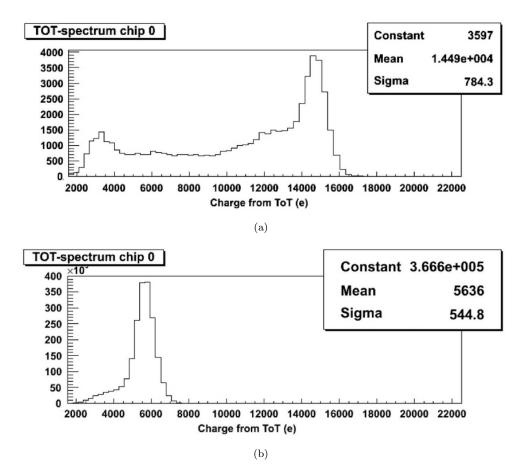

| Collected charge for a 2E pixel detector biased at 35V using <sup>241</sup> Am (a) and <sup>109</sup> Cd (b) radioactive sources [96]                                                                                                    |

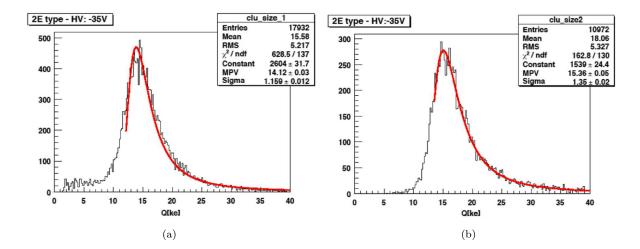

| Landau distributions as a response of a 2E pixel detector to a $^{90}$ Sr beta particle source. The device was biased at 35 V and both cluster size 1 (a)                                                                                |

| and cluster size 2 (b) distributions are shown [96]                                                                                                                                                                                      |

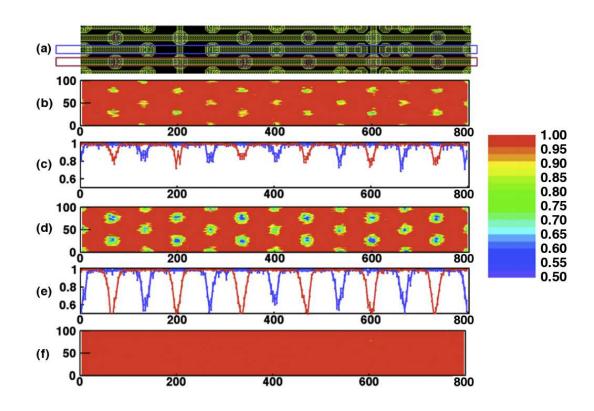

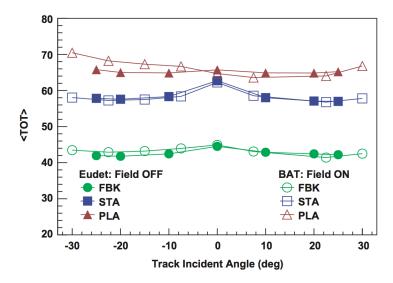

| Average ToT distribution as a function of the incident angle for an FBK, a<br>Stanford and reference planar device [98]                                                                                                                  |

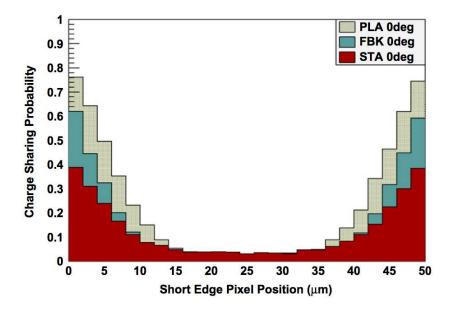

| Charge sharing probability as a function of the track position along the short edge of the pixel for an FBK, a Stanford and reference planar device [98]106                                                                              |

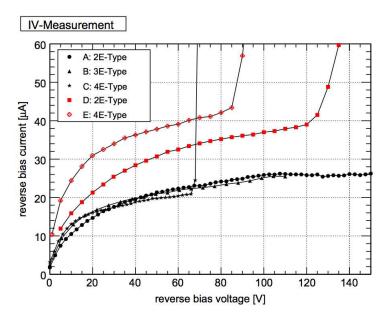

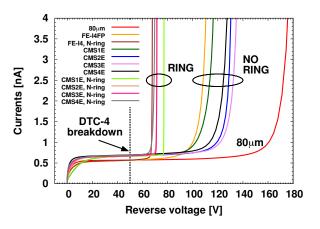

| Leakage currents for the FBK pixel devices irradiated at two different fluences, $1 \times 10^{15}$ (black) and $2 \times 10^{15} n_{eq}/\text{cm}^2$ (red) [102]                                                                        |

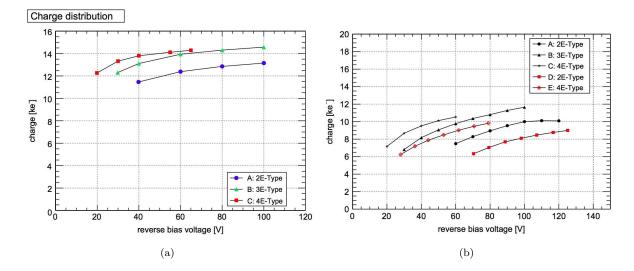

|                                                                                                                                                                                                                                          |

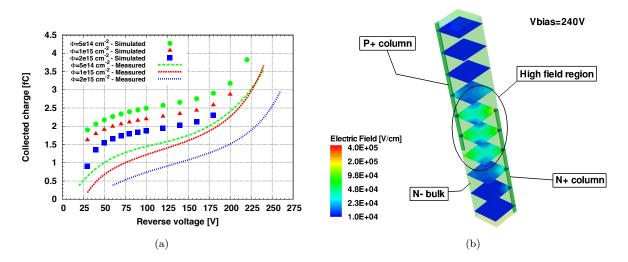

| 3.32 | Collected charge as a function of bias voltage in response to an <sup>241</sup> Am source                                                    |