CERN/EF/MPPC 89–1 28 July 1989

### PROPOSAL - THE MPPC PROJECT

Massively Parallel Processing Collaboration

ASPEX Microsystems-Brunel University-CEA-CEN Saclay-CERN-EPFLGeneva University-GSI-Thomson TMS

J.-C. Brisson<sup>3</sup>, E. Bonomi<sup>5</sup>, P. Borgeaud<sup>3</sup>, J.-J. Dumont<sup>5</sup>, J. Feyt<sup>4</sup>, M.-N. Gaujour<sup>8</sup>, B.W. Kolb<sup>7</sup>,

A. Krikelis<sup>1</sup>, M. Kunt<sup>5</sup>, J.-P. Lamarcq<sup>8</sup>, R.M. Lea<sup>1,2</sup>, M.B. Martin<sup>6</sup>, T. Reed<sup>5</sup>, F. Rohrbach<sup>4</sup>,

A. Sandoval<sup>7</sup> and M. Tomassini<sup>5</sup>

- 1 ASPEX-Microsystems Ltd, United-Kingdom

- 2 University of Brunel, United-Kingdom

- 3 CEA-CEN Saclay, DPHPE/SEIPE, France

- 4 CERN, European Organization for Nuclear Research, Geneva, Switzerland

- 5 EPFL, Ecole Polytechnique de Lausanne, Switzerland

- 6 Geneva University, Faculté des Sciences, Geneva, Switzerland

- 7 GSI Darmstadt, Germany

- 8 Thomson-TMS, France

#### **ABSTRACT**

The need for a dramatic increase in computing power is already being felt in several fields of research. It is expected to become a major issue in the near future. In high-energy hadron collider physics, many experiments being planned for the next decade will require a large increase in their data taking and analysis capabilities. In relativistic heavy-ions physics, the computing-power bottleneck has already occurred. The amount of data acquired per event, the event complexity, and the event rate are at present increasing by orders of magnitude. In many other fields, such as image-processing, cellular automata, neural networks, plasma physics, high-definition TV, autonomous guiding vehicles, artificial intelligence, etc., the computational power required is larger than that available from supercomputers. This new need in computational power will require the implementation of massively parallel processing architectures as the only possible solution at present in order to make the required breakthrough. The Massively Parallel Processing Collaboration (MPPC) intends to develop and exploit, in a two-year project, the new concept of associative parallel processing by combining all the efforts, know-how, and competence of the participating Universities, Research Institutes, and Industry to establish two powerful development 'platforms' in massively parallel processing and computing, one for the hardware and one for the software. As a 'Pilot Project' the Collaboration has selected the development of a fast, intelligent, image-intensified Charge Coupled Device (CCD) camera interfaced to an Associative String Processor (ASP) with 65,536 Associative Processing Elements (APEs). With this system, we want to demonstrate, in an experiment at CERN, the real-time data acquisition and on-line data analysis of images with 1 Mbyte of information per event. Associative parallel processing algorithms will be developed for track reconstruction of very complicated events and for large Ring-Imaging Cherenkov area (RICH) detector pattern reconstruction. The experience and knowledge gained in the realization of the Pilot Project will be applied to further problems in high-energy physics and in other fields.

Spokesman: F. Rohrbach

5002G/FR/ed

CERN LIBRARIES, GENEVA

CM-P00062754

| OVI | ERVIE | old W                                                                                                                                                                                                                  | iii                        |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| PRC | )JECT | PROPOSAL                                                                                                                                                                                                               | V                          |

| 1.  | PER   | SPECTIVE                                                                                                                                                                                                               | 1                          |

|     | 1.1   | Real-time Massively Parallel Processors (MPPs)                                                                                                                                                                         | 1                          |

|     | 1.2   | Need for massively parallel processing applied to high-energy physics                                                                                                                                                  | 3                          |

|     | 1.3   | Need for massively parallel processing applied to other sciences 1.3.1 Numerical simulation of physical phenomena 1.3.2 Cellular automata 1.3.3 Neural networks 1.3.4 Artificial Intelligence 1.3.5 Other applications | 6<br>6<br>7<br>7<br>8<br>8 |

|     | 1.4   | Second-generation massively parallel processing requirements 1.4.1 Architectural requirements 1.4.2 Engineering requirements                                                                                           | 8<br>8<br>11               |

|     | 1.5   | Dedicated pipeline architectures                                                                                                                                                                                       | 15                         |

|     | 1.6   | MIMD/SIMD array processing architectures                                                                                                                                                                               | 17                         |

| 2.  | OPP   | ORTUNITY                                                                                                                                                                                                               | 18                         |

|     | 2.1   | The Associative String Processor (ASP) 2.1.1 ASP software 2.1.2 TRAX-1                                                                                                                                                 | 19<br>21<br>22             |

|     | 2.2   | ASP potential 2.2.1 ASP module performance 2.2.2 Performance benchmark results                                                                                                                                         | 23<br>25<br>27             |

| 3.  | ОВЛ   | ECTIVES                                                                                                                                                                                                                | 27                         |

|     | 3.1   | The Pilot Project: an intelligent on-line camera                                                                                                                                                                       | 27                         |

|     | 3.2   | The contribution of massively parallel processing to high-energy physics                                                                                                                                               | 30                         |

|     | 3.3   | The contribution of massively parallel processing to other sciences                                                                                                                                                    | 30                         |

| 4.  | STR   | ATEGY                                                                                                                                                                                                                  | 31                         |

|     | 4.1   | The MPPC project                                                                                                                                                                                                       | 31                         |

|     | 4.2   | The MPP software platform at EPFL                                                                                                                                                                                      | 32                         |

|     | 4.3   | The MPP hardware platform at Saclay 4.3.1 List of activities 4.3.2 Responsibilities 4.3.3 Construction subcontractors                                                                                                  | 33<br>33<br>34<br>34       |

|     | 4.4   | CERN involvement 4.4.1 General support 4.4.2 CCD hardware and software platform                                                                                                                                        | 35<br>35<br>36             |

|     | 4.5   | 4.5.2<br>4.5.3<br>4.5.4 | ivations, applications, and involvement of the other collaborators  ASPEX-Microsystems  Brunel University  Geneva University  GSI  Thomson | 37<br>37<br>38<br>38<br>39<br>42 |

|-----|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.  | PRO   | GRAI                    | MME OF THE WORK                                                                                                                            | 43                               |

|     | 5.1   | Acti                    | vities                                                                                                                                     | 43                               |

|     | 5.2   | Time                    | e scale                                                                                                                                    | 45                               |

| 6.  | RES   | OUR                     | CES                                                                                                                                        | 47                               |

|     | 6.1   | MPF                     | PC personnel                                                                                                                               | 47                               |

|     | 6.2   | MPF                     | PC budget                                                                                                                                  | 48                               |

| REF | EREN  | NCES                    |                                                                                                                                            | 49                               |

| ANI | VEX I | (*):                    | ASP modules: cost-effective building-blocks for real-time DSP sy of VLSI Signal Processing, vol. 1 (1989) 61-76.                           | stems, Journal                   |

| ANI | VEX I | I(*):                   | ASP: a cost-effective parallel microcomputer, IEEE Micro, (October                                                                         | er 1988) 10–29                   |

| ANI | VEX I | П(*):                   | DARPA image understanding benchmark I.                                                                                                     |                                  |

| AN  | νεχ Γ | V(*):                   | DARPA image understanding benchmark II.                                                                                                    |                                  |

| AN  | VEX V | /(*) <sub>:</sub>       | Performance of the ASP on the LAA benchmark.                                                                                               |                                  |

<sup>(\*)</sup> The five Annexes are available upon request at the CERN/EF typing pool.

#### OVERVIEW

The MPPC project started in March 1989 when it was realized that the latest technological novelties in various fields were arriving at the same time to offer the possibility of developing a new fast processing system for massive amounts of data.

The future need for detectors in order to cope with the severe and stringent working conditions expected for the next generation of hadron accelerators at CERN has triggered, over the last few years, a large amount of Research and Development (R & D) for studying new ideas and new detectors with the help and support of many interested Universities, Research Institutes, and Industry (the Lepton Asymmetry Analyser (LAA) project [1,2]: a large CERN R & D programme for experimental physics with multiTeV hadron accelerators).

It so happened that, at the same time as CERN, EPFL in Lausanne and CEA-CEN Saclay in France had similar motivations to enter the new field of massively parallel computing as a possible way of providing the answer to unsolved difficulties: the demand from the physicists and engineers for increasing – by orders of magnitude – the amount of data to be analysed and, simultaneously, the requirement of speeding up the data processing above the limits of all conventional Von Neuman existing computers. This need was due to the entering of a new era of research and technology: future multi—TeV hadron colliders and very heavy ions beams in High-Energy Physics, Image Processing, and data compaction at video rates for robotics and high-definition television (HDTV), very large sampling simulation for modelling, huge data base treatment and communication, etc.

By then, at the University of Brunel (UK), the ASPEX-Microsystems company was developing a revolutionary parallel architecture for making a breakthrough in computing power. This company is developing a new device: a string of Associative Parallel Processors (ASPs) [3]. It offers a potential breakthrough towards Tera Operations Per Second (TOPS) performance at a reasonable price (target price 1 MOPS/\$) with flexibility, scalability, and efficiency. A machine based on ASP, called TRAX-1, is under construction for the NA35 experiment at CERN [4]. This machine will have 16 kASP elements. This project is supported by the NA35 Collaboration and the LAA project. Dedicated parallel software is also being presently developed and an important effort is being devoted by CERN and NA35 to the application of TRAX-1 in view of speeding up, by orders of magnitude, an existing conventional image workstation installed in Frankfurt for processing streamer chamber pictures of events coming from the NA35 heavy ion experiment at CERN.

At the same time, the development of large-area CCD detectors with high gain and granularity is also in progress in Industry [5]. Thomson-CMS can now offer a one million pixel CCD sensor with low noise, fast clear, antiblooming protection, and equipped with a 25 ms parallel read-out. Development work is going on towards higher reading frequencies, better light response, a larger number of pixels, etc.

The MPPC project proposes the development (hardware and software) of a massively parallel processing system, based on the ASP, for on-line analysis of the high-energy physics experiments at CERN. In addition, the project will demonstrate and evaluate the system's capabilities for other applications of high performance processing requirements (e.g. numerical simulation of physical phenomena, Cellular Automata, Neural Networks, Aritificial Intelligence (AI), etc.).

A software platform will be organized at the Ecole Polytechnique Fédérale, Lausanne (EPFL) with the help of ASPEX for the highly specialized ASP software. In order to develop intelligent ASP algorithms, a totally new approach is necessary for programming, which implies an important effort to change the way of thinking: there is no more addressing and the massively parallel processing is done inside the memory depending on the contents of the data and activity registers, with a minimum interaction with the outside world, and the operations are mostly conducted at the bit level. This large support in software will be essential for the proposed Collaboration.

A strong and complementary hardware platform will be launched by Saclay together with ASPEX to develop and construct the new modules.

Demonstration and evaluation of the new techniques will be performed at CERN in real applications. For this purpose, a Pilot Project will be established by the Collaboration: it consists in defining, designing, constructing and demonstrating a fast, intelligent 1 megapixel CCD camera, interfaced to an ASP with 65,536 APEs and equipped with an image intensifier. Based on these results wider applications employing 10<sup>4</sup> to 10<sup>6</sup> associative parallel processors can be planned.

### PROJECT PROPOSAL

## Synoptic presentation

Submitted to:

**CERN**

Title:

The Massively Parallel Processing Collaboration

Project Leader:

Dr. F. Rohrbach **EF** Division

**CERN**

1211 Genève 23

Telephone: Telefax:

(022) 767 4149 (022) 783 0600

Collaborators:

**Institution**

Responsible

**ASPEX**

Brunel University

Prof. R. M. Lea Dr. F. Rohrbach/EF Prof. M. Kunt /LTS

Prof. R. M. Lea

**CERN EPFL** GSI

Dr. A. Sandoval/NA35 Prof. M.B. Martin/DPNC

Geneva University Saclay

Dr. P. Borgeaud/DPHPE-SEIPE

Thomson-CMS

Mr. J.-P. Lamarcq

Platforms

SOFTWARE

**EPFL**

Dr. J.-J. Dumont /SIC

**HARDWARE**

CEA-CEN Saclay

Mr. J.-C.Brisson/DPHPE-SEIPE

CCD

CERN

Mr. J. Feyt / EF

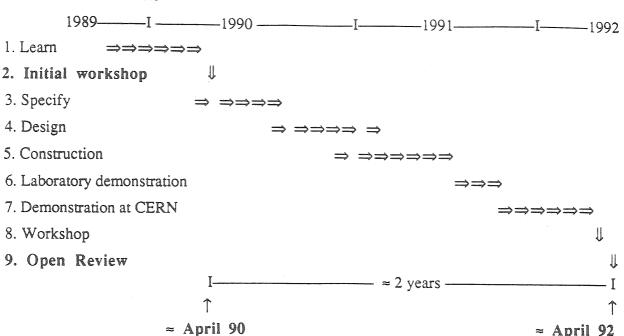

Time scale:

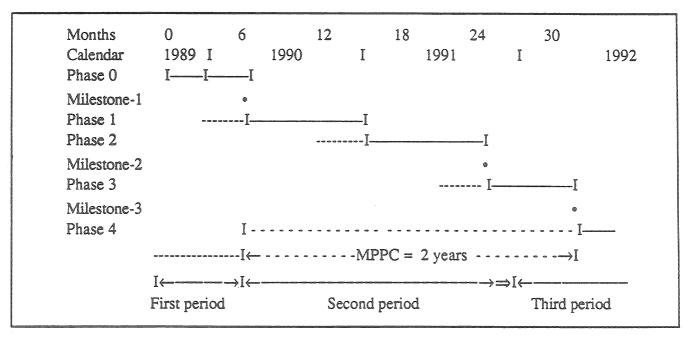

Phase 0:

1989 Oct.

1990 Apr. Foundation

Phase 1: Phase 2:

Apr. 1990 -Dec. 1990 -

Nov. 1990 Definition

Phase 3:

Sep. 1991 Construction Oct. 1991 - Apr. 1992 Demonstration

Funding requirements:

Phase 0:

110 kSF

Phase 1: Phase 2:

400 kSF

Phase 3:

925 kSF 200 kSF

Date:

27 July 1989

#### 1. PERSPECTIVE

For nearly three decades, the elusive target of an extremely powerful super-computer has stimulated the development and evaluation of parallel computer architectures. In the 1960s and 1970s, pioneer machines (e.g. Solomon, Illiac IV, Staran, CLIP, DAP) demonstrated the evolving parallel processing concepts and in the 1980s first-generation multiprocessors (e.g. Alliant FX8, Sequent Balance, Butterfly and Transporter systems), array processors (e.g. MPP, DAP and GAPP) and hypercube architectures (e.g. NCube and Connections Machine) have become commercially available; each claims impressive performance for mainly ad hoc benchmarks. Indeed, many authorities are now proclaiming the age of very powerful computer—, graphics-, and database-servers, based on Massively Parallel Processors (MPPs), for networked CAD/CAM, military, scientific, medical, and office applications.

However, although first-generation MPPs have achieved significant increases in processing performance, they have not yet demonstrated a sufficiently significant breakthrough in application flexibility and cost-effectiveness to be commercially successful.

First-generation MPPs are highly machine-oriented, each being dominated (in cost and performance) by the particular inter-processor communication network (e.g. pipeline, mesh, hypercube, tree, pyramid, Omega, Banyan, etc.) favoured value, but may have born little relation to real (problem-solving) application requirements.

### 1.1 Real-time Massively Parallel Processors (MPPs)

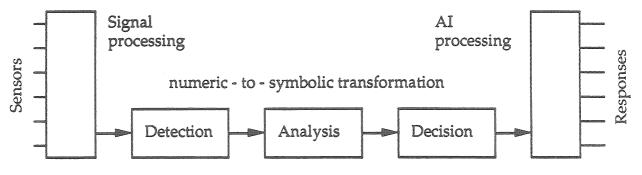

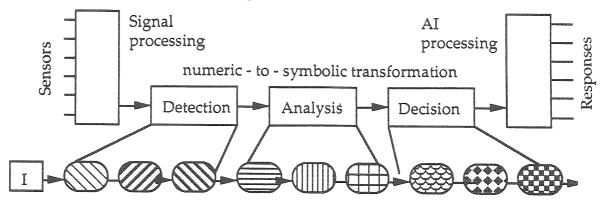

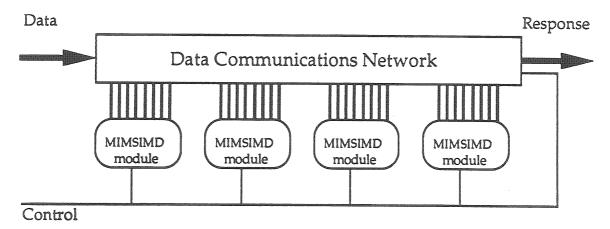

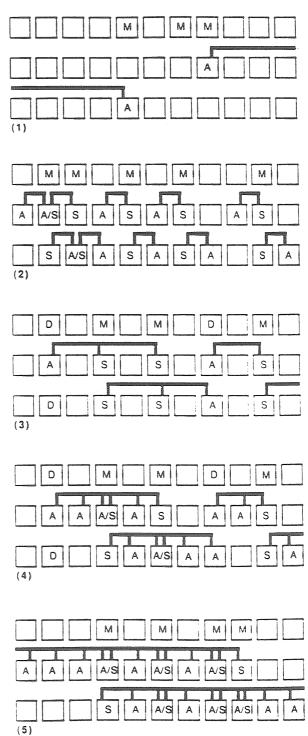

In contrast to the first-generation parallel computer experience, an important application class for second-generation MPPs will include real-time signal and data-processing systems operating in real-world locations. Achieving performance levels up to 1 TOPS and supporting continuous data input, such general-purpose (problem-solving) computing systems will attempt the rapid detection, analysis, and decision-making (based on recognition or understanding) of object-related information and the determination of some appropriate response, as indicated in Fig. 1.

Fig. 1 Real-time signal and data-processing system

Sensors may include any form of acoustic, visual, thermal, mechanical, electromagnetic, or nuclear-radiation energy, and applications include detector readout, remote sensing, surveillance, and tracking in high-energy physics, aerospace, seismological, and in biomedical environments. In particular, real-time computer vision systems suggest ideal massively parallel processing application examples, with a processor allocated to each pixel of the image to be processed.

Typical detection tasks range from signal reconstruction of restoration (to compensate for sensor non-uniformities, ageing, and eventual failure), through filtering (to improve signal-to-noise ratios and enhance particular signal features) to correlation (to discriminate relevant signal information from background clutter).

Typical analysis tasks range from grouping data associated with meaningful objects, through specific transforms for feature extraction and edge or track following (to establish feature connectivity) to object quantification (for length or area measurement or centre-of-mass coordination) and listing of relevant object properties.

Typical decision tasks range from pattern matching (correlation of invariant object descriptors with model descriptions) and navigation of semantic networks through hypothesis analysis to interpretation of object-related information to facilitate decision-making and response determination.

Real-time signal and data processing applications are characterized by the need to provide a rapid response to information derived from a high-speed continuous data stream. For example, real-time computer vision with non-interlaced (60 Hz) raster-scanned image frames requires the completion of all processing tasks (including data input and output) within a frame-time of 16.7 ms, suggesting processing rates of 10–1000 GOPS (GigaOPS) and input data rates approaching 1 Gbytes/s. Clearly, such high performance can only be achieved with massively parallel processing.

However, such end-to-end processing (namely problem-solving) systems encompass a sequence of tasks, from signal processing through some form of numeric-to-symbolic date conversion (usually achieving considerable data reduction) to AI (Artificial Intelligence) processing. Indeed, processing tasks are not solely confined to the low-level arithmetic operations on 1D or 2D arrays typical of first-generation parallel computing, but the wide variety of tasks also includes higher-level operations on more complex data structures (e.g. sets, tables, trees, or graphs). Moreover, the nature of these application environments ensures dynamically changing functionality requirements as sensor technology and application understanding improve.

Consequently, second-generation MPPs must satisfy significantly different application/design requirements from their first-generation predecessors.

## 1.2 Need for massively parallel processing applied to high-energy physics

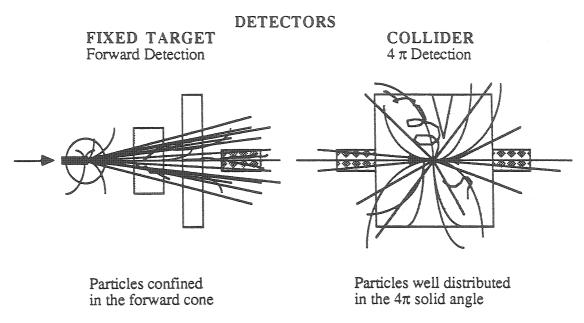

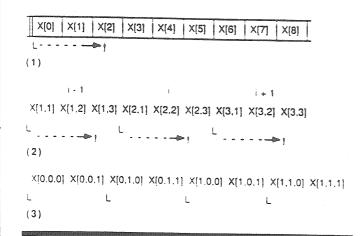

There are essentially two kinds of experiment at CERN: Fixed-target physics and Collider physics. The topology for the detectors is different in the two cases (Fig. 2).

Fig. 2 Topology of high-energy experiments at CERN

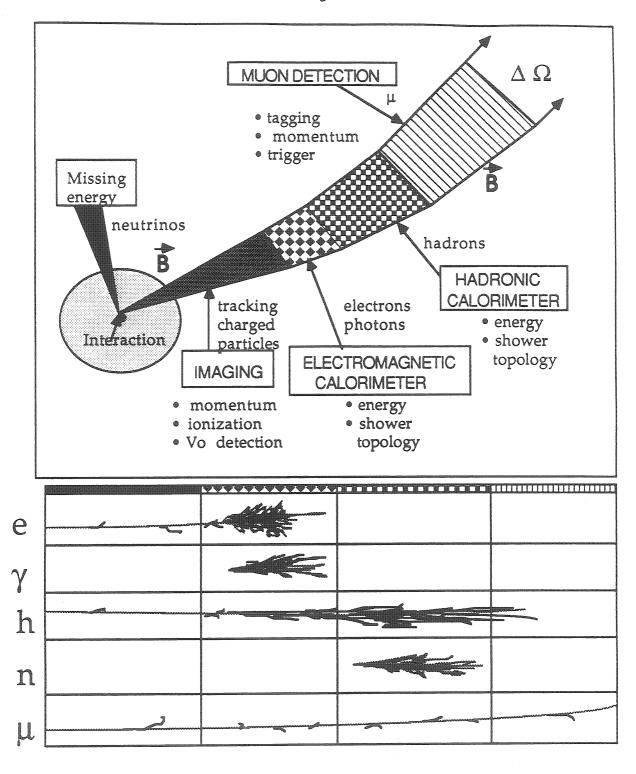

However, the detecting principle remains the same: starting from the vertex of the interaction a succession of tracking and ionization detectors, calorimeters and velocity counters, muon tagging and tracking devices are disposed in an efficient way in order to extract all the possible information from the interaction products. The simultaneous knowledge of the totality of the information coming from all the detectors surrounding the collision point is necessary for the evaluation of the event and, consequently, there exists a natural need for processing all the data in a parallel way and not sequentially (Fig. 3).

Except for imaging detectors, the number of pixels of information coming from all the detectors has up to now been limited to 10 to 100 kbytes and the event rate was not greater than 100 kHz, the interesting events being stored at a rate of a few Hz. A conventional approach using sequential machines was able to cope with these requirements by a logical implementation of some parallel treatment of the information for triggering the data acquisition out of a pipelining pre-storage system. However, the data analysis itself, which is done off-line, is taking a very long time compared to the running time of the experiment, giving rise to an imbalance between the duration of the experiment and the physics outcome. Typically years of analysis can be generated by weeks of data taking. Moreover the feedback from the experimental results which could be used to control and improve the data taking is

coming by far too late and often the experiment must face a cruel issue: the data are not usable for the analysis as expected.

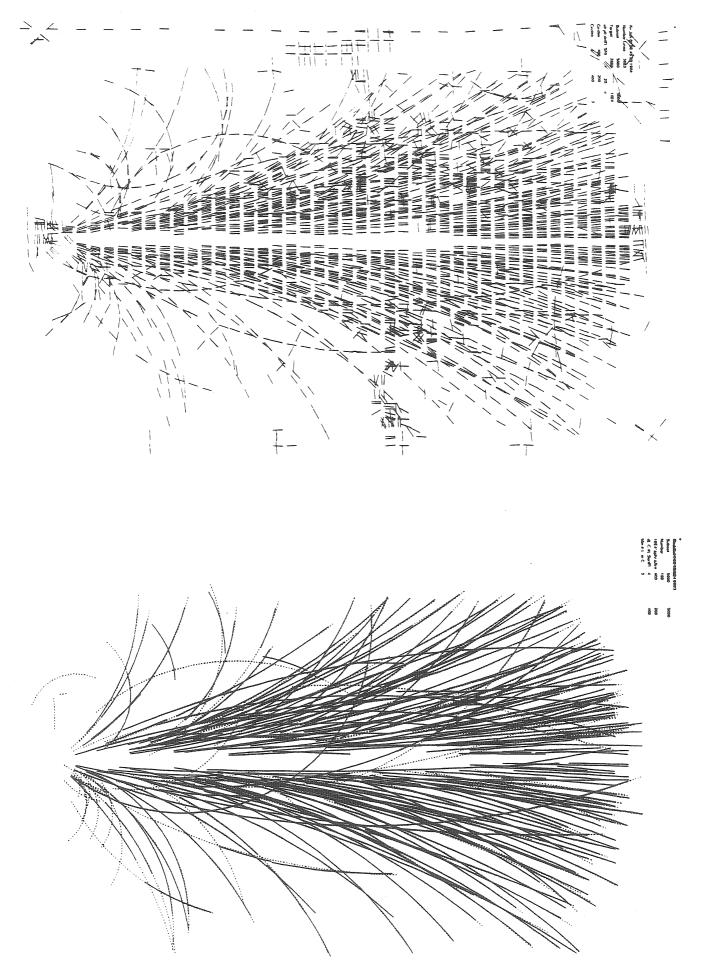

For the case of imaging detectors, the number of pixels of information per event is so high (many Mbytes) that, up to now, film has had to be used as storage support and a very long off-line analysis has had to be done (for example, 10 h on an image workstation are necessary for the analysis of every event in the NA35 heavy—ion physics experiment).

In order to improve the redundancy in particle detection - higher and higher numbers of tracks per event - and the quality of the physics analysis - mass, momentum and energy resolution - it is necessary to increase the number of pixels of information per track for tracking detectors, to reach a higher granularity for calorimeters and to provide more pads for RICH counters. This means that the total number of pixels per event is going to increase.

At the same time there is a deep physics interest to search for rarer phenomena and higher mass particles. In order to proceed along these lines, there is a need to increase both the luminosity of the accelerators and their energy. The main parameters of existing and future hadron accelerators show the huge step which is expected to take place in the rate of events and charged multiplicities for hadron colliders (Table 1).

TABLE 1

Hadron accelerators: main parameters for detector

| Machine             | Particles | √s   | L                                      | Δt      | R             | <n></n> |

|---------------------|-----------|------|----------------------------------------|---------|---------------|---------|

| SPS pp (CERN)       | pp        | 0.63 | 3 x 10 <sup>30</sup>                   | 3.8 µs  | ~ 200 kHz     | 30      |

| Tevatron (Fermilab) | p₽        | 1    | 10 <sup>30</sup>                       | 3.5 µs  | ~ 100 kHz     | 35      |

| UNK (URSS)          | pp        | 6    | 10 <sup>32</sup>                       | 6 ns    | ~ 10 MHz      | 60      |

| LHC (CERN)          | pp        | 16   | 10 <sup>33</sup> -5 x 10 <sup>34</sup> | 25-5 ns | up to ~ 5 GHz | 80      |

| SSC (Texas)         | pp        | 40   | 10 <sup>33</sup>                       | 18 ns   | ≈ 100 MHz     | 104     |

| ELOISATRON (Italy)  | pp        | 100  | ≈ 10 <sup>33</sup>                     | 25 ns   | ≈ 100 MHz     | 134     |

with:  $R = \langle r \rangle / \Delta t = L \sigma$

where R Rate of interaction (s<sup>-1</sup>)

Number of interactions in each crossing

$\Delta t$  Time between crossings (s)

L Luminosity (cm<sup>-2</sup>s<sup>-1</sup>)

σ Cross section for interaction [cm<sup>2</sup>]

√s cms energy (TeV)

and:  $\langle n \rangle = -6.55 + 6.89 \text{ s}^{0.131}$  (power fit)

<n> Average charged multiplicity for non single diffractive events [6]

s c.m.s. energy squared (GeV<sup>2</sup>)

Different kinds of particles  $\Rightarrow$  Different kinds of detectors :

ImagingElectromagneticHadronicMuonVertex DetectorCalorimeterCalorimeterTracking

Classical approach:

TPC, Streamer Chamber Scintillators & dense High Z materials LST, Drift Chambers

Fig. 3 Detection principle in high-energy experiments

There is another difficult challenge for detectors in ultra-relativistic heavy—ion experiments: going from light to very heavy ions, one has to face a continuous increase in the total charged particle multiplicity per event. The increase in average multiplicity for central collisions, observed or to be expected for future beams, is as follows:

| 1986    | O16               | <n>central</n> | <b>≅</b> 250 |

|---------|-------------------|----------------|--------------|

| 1987-91 | S32               | <n>central</n> | <b>≅</b> 400 |

| ≈1993   | Pb <sup>208</sup> | <n>central</n> | ≅ 2500!      |

In most of the present fixed-target experiments, the data-acquisition rate is only limited by the detector and the electronics but not by the beam and target from which very high luminosities could be obtained.

Consequently, for colliders as for fixed-target experiments, one expects not only a drastic increase in the rate of the events but also an increase in the number of particles filling the detectors for every interaction. Rates are increased by ~ 3 orders of magnitude, the time between successive events is decreasing down to a few ns and the number of bytes per event has to increase to many Mbytes in order to disentangle the interaction products.

At present, there are no solutions to these difficulties. However, there is a clear line of research and development which could offer the necessary breakthrough: the use of massively parallel processing in order to gate the data flow and to analyse on-line the events (tracking, clustering, event checking, etc.).

# 1.3 Need for massively parallel processing applied to other sciences

It is not only in high—energy physics that there exists a need and motivation in the direction of massively parallel processing. In many fields of science and technology, existing algorithms require huge computational resources to yield useful results. Most of them are in fact rather simple, but imply repeating the same set of operations on large amounts of data. This motivated the development of the vector processors of the so-called 'supercomputers', which are now dominating the market, but mostly by their price. It is now clear that this very expensive approach is still extremely limited and does not satisfy the present users of the 'supermachines'. It seems that the only way out of the computing crisis is to be found in massively parallel processing.

Let us summarize what are the main kinds of applications that would benefit from parallel machines, and what are their problems with the existing ones.

## 1.3.1 Numerical simulation of physical phenomena

Traditionally, such simulations use a mathematical model consisting of differential equations defined on a continuum. An algorithm, or numerical model, is used to discretize

and numerically solve the equations. Classical applications of this approach are, for instance, structural and mechanical engineering, fluid dynamics, and other physical and chemical processes such as combustion or solidification.

For this kind of problem, parallel architectures belonging to the MIMD (Multiple Instructions Multiple Data) class can be of interest: relatively cheap but powerful processors are assembled, each one executing a different stream of instructions on data stored in a local memory. Physical connections between processing elements can be with nearest neighbours, as for the Inmos transputers, or following a hypercube scheme, as for the Intel machines. However, in both cases the Minsky conjecture, which states that the effective power of a machine goes like log N if N is the number of processors, turns out to be a good approximation in most practical cases. This disappointing limitation stems from the overhead implied by the communication protocols between processors, and also from the control operations, which are sequential by nature.

This somewhat reduces the interest of transputers, which were once thought to be ideal solutions in the realm of numerical simulation and floating-point data processing. Indeed, the user must create his own communication protocols, tailored to his special application, which excludes any kind of efficient FORTRAN programming for instance. Specialized operating systems (Helios) or FORTRAN compilers (Meiko) can help, but in any case the situation remains unsatisfactory.

The Intel hypercubes are supposed to be in a better situation as far as the communication problems are concerned, as they can rely on much better software tools and on a theoretically more sophisticated connection scheme. However, good efficiencies can still only be reached for very few real life applications, and load balancing of the various processors, as for any MIMD architecture, remains a critical and largely unsolved problem.

### 1.3.2 Cellular automata

It is an alternative way of modelling and simulating physical phenomena: space is discretized by a lattice whose grid points (site) are allowed a finite number of values (states). The state of each site evolves step by step in the model, following local microscopic laws (rules) which, if chosen properly, produce the macroscopic behaviour to be simulated. The intrinsic granularity of cellular automata algorithms leads naturally to their implementation on massively parallel machines. They are very inefficient on classical number crunchers, as they need only a few bits per operation.

### 1.3.3 Neural networks

The brain is the most massively parallel processor existing today. It seems like a good idea to try to exploit its basic features for the design of electronic processors, if they are to

solve by analogy he same kind of problems as the brain does, namely associative memory storage, learning, pattern recognition, control or optimization. The bulk of neural algorithms consists in summing weighted quantities.

The main problem of these specialized processors is that they can only run one hard-coded algorithm, and can therefore be only used for one type of application. It also implies that the behaviour of the chosen algorithm in various situations must first be checked using simulators, before building the processor. This can only be done efficiently on other parallel machines. If the simulation is fast enough, the specialized processor may become unnecessary.

### 1.3.4 Artificial Intelligence

Today, it seems unlikely that large neural networks could really work like an intelligent brain and solve efficiently any AI problem. However, there are many other techniques of AI which also involve parallel processing. For instance, the 'assumption-based truth maintenance' algorithm was implemented in a parallel fashion by Xerox, with the aim of applying it to robots. In that case, it would need compact and cheap MPPs. Another example is the 'case-based reasoning', in which a huge amount of cases are to be considered, preferably in a parallel way. There is a large variety of expert systems which would benefit from such algorithms, or from other ones using various kinds of active objects, structures, sets, and graphs. No existing machine can easily and efficiently allow for the variety of data structures appearing in this kind of application.

## 1.3.5 Other applications

Without going into details, let us also mention briefly the need for parallelism in operational research (mostly for ordering problems), graphics rendering (for instance, ray—tracing algorithm for the generation of realistic pictures), and particularly image or signal processing in astronomy, geophysics, medicine, etc.

## 1.4 Second-generation massively parallel processing requirements

To be cost-effective as second-generation MPPs, parallel computer architectures will need to satisfy both architectural and engineering requirements, as discussed in the following sub-sections.

### 1.4.1 Architectural requirements

## (i) Application flexibility

In order to recover high development costs, second-generation MPPs must serve a variety of applications and users; 50 users will need to amortize high procurement costs

through a wide range of both numerical and non-numerical information processing applications.

Moreover, real (i.e. problem-solving) computer applications, as opposed to first-generation MPP benchmarks, usually involve a range of different data stuctures and different operational requirements across quite a wide span of computational tasks. For example, computer vision comprises a wide range of data structures (e.g. sets, arrays, tables, trees, and graphs) encountered in iconic-to-symbolic image processing and subsequent image understanding.

By allocating a processor to each node of a data structure and by linking the processors in order to emulate the relationship existing between such nodes, application parallelism can be exploited with the architectural parallelism of multi-node processing and multi-link navigation.

However, most first-generation MPPs are dedicated to particular data structures and optimized for particular computational tasks. Continuing with the computer vision example, mesh architectures have been applied, with reasonable success at the pixel (iconic) level, but this solution may only serve to transfer the computational bottleneck to a higher level of processing. Similarly, tree architectures perform better for (tree-structured) symbolic data processing, but are not well-suited to lower level processing.

In summary, application flexibility (maintaining efficient support of different data structures) will be an important requirement for second-generation MPPs.

### (ii) Architectural scalability

The number of processors in first-generation MPPs tends to be fixed or is severely restricted (e.g. 1 k, 4 k, 16 k or 64 k), whereas problems are not so conveniently sized. Moreover, users will wish to extend existing MPPs to achieve more processing power. Consequently, architectural extensibility (i.e. scaling of parallel processing power) will be a key issue for second-generation MPP design.

## (iii) Computational efficiency

First-generation MPPs claim up to order N (i.e. O[N]) improvement in performance for O[N] parallelism. However, although this may be possible for certain specific (highly parallel) processing tasks, other tasks may not benefit from such high degrees of parallelism. In fact, for real (i.e. multitask) applications, the overall performance of such MPPs is more likely to be worse than O[logN] (namely Minsky's conjecture). Indeed, the somewhat reluctant realization that emerges from the analysis of first-generation programs is that their performance is not affected so much by the potential processing power of the processor ensemble, but more by the loss of efficiency due to poor processor utilisation and the hidden

processing overheads associated with the strategies adopted for parallel program control, as discussed below.

- (a) sequential processing overheads, associated with the input and output of (vector) data values;

- (b) sequential processing allocation, resulting in redundant sequential processing and low concurrency within the processor ensemble and inter-processor communication network, due to a mismatch between the applied parallelism of the computer and the natural (data-level) parallelism of the data structure being processed;

- (c) sequential processing overheads, associated with the initialization and scheduling of the concurrent execution of mutually exclusive processes/operations, resulting in inefficient exploitation of natural (control-level) parallelism in the algorithmic requirement;

- (d) sequential processing due to requirements for the storage and processing of scalar (as opposed to vector), data (e.g. during the calculation of intermediate results);

- (e) parallel processing overheads, due to the initialization and synchronization of interprocessor communication (which would not be suffered by a sequential processor: for example, navigating irregular tree-structured data on an orthogonal array processor could entail much routing through redundant processors with significant control and communication overheads.

Requirements for maximal computational efficiency are outlined below in (iv) through (ix).

### (iv) Pipelining data input

In order to support on-the-fly processing of continuous input data streams, at rates up to 1 Gbytes/s, and avoid associated sequential processing overheads, real-time MPP architectures must adopt an efficient pipelining policy for data input.

# (v) Inter-processor communication network configurability

Optimal processor utilization is achieved when the MPP's network topology exactly matches the particular data structure being processed and, inevitably, the MPP would suffer loss of computational efficiency for non-matching data structures. Thus, for flexible matching of the applied parallelism of a general-purpose MPP with the natural (data-level) parallelism of different applications and for minimization of the parallel processing overheads mentioned, a reconfigurable processor interconnection strategy is required.

Consequently, the degree of network configurability (to exploit data-level paralllelism) will be a most important parameter for the computational efficiency for second-generation MPPs.

## (vi) Overlapping sequential and parallel processing

In order to avoid loss of computational efficiency due to the sequential processing overheads discussed above, it is essential that all sequential processing is overlapped with parallel processing.

### (vii) Programmability

Apart from systolic arrays, most first-generation MPPs are programmable. Similarly, second-generation MPPs will require programmability in order to gain application flexibility and achieve task-oriented specialization cost-effectively. Indeed, for flexible control over pipelining data input, inter-processor communication network configurability, process scheduling, and overlapping sequential processing as discussed above, programmability is an essential requirement for the optimization of computational efficiency.

# 1.4.2 Engineering requirements

Second-generation MPP applications are likely to dictate an engineering approach (as opposed to a computer-science approach) to parallel computer design. For example, real-time parallel computer systems must operate reliably within environmental restrictions, taking into account maintenance schedules and cost limitations. Such engineering issues are discussed below.

### (i) Environmental restrictions

Certain MPP application environments (e.g. high—energy physics detector front ends, space, avionics, underwater and automotive) present the most formidable design challenge by severely restricting size and weight, assembly and packaging techniques, and power supply and dissipation, as discussed below.

### (a) Size and weight

Typical cavities for the above application environments measure significantly less than 1 cubic foot and weight reduction can be a key issue. Rather less demanding, but nonetheless important, are the size and weight requirements for workstations, which must fit acceptable (e.g. under desk) locations of, say, less than 5 cubic feet.

In contrast, the 65,536-processor Connection Machine, representing the state-of-theart in first-generation MPP compaction, occupies 75.4 cubic feet. Clearly, second-generation MPP applications will require a step-function increase in the density of microelectronics assembly and packaging to achieve the required reduction in the size and weight of first-generation MPPs.

Consequently, the trend towards High-Density Multi-layer Interconnect (HDMI) technologies [i.e. highly-compact multi-chip modules, constructed by mounting unpackaged VLSI chips on alumina or co-fired ceramic substrates or even silicon wafers (i.e. hybrid wafer-scale integration)] is of significant interest for size and weight reduction.

### (b) Assembly and packaging

The application environments mentioned above often present a most formidable assembly and packaging challenge, owing to harsh operational conditions (e.g. extreme temperature range, radiation, electrical noise, mechanical vibration, humidity or even a corrosive atmosphere), which further stimulates interest in HDMI-VLSI multi-chip modules.

### (c) Power supply and dissipation

The application environments mentioned above typically restrict supply and thermal design with power limits of less than 1 kW.

In contrast, the CM-1 and CM-2 versions of the 65,536-processor Connection Machine, dissipate 12 kW and 28 kW respectively. Thus, even in an office environment, the power dissipation of such an MPP workstation would be unacceptable. Clearly, second-generation MPP applications will also require a step-function reduction in the power consumption of first-generation MPPs.

## (ii) Reliability and maintenance

The reliability and ease of maintenance of relatively expensive machines, such as MPPs, will always be important issues. In particular, for the reasons given below, highly-compact fault-tolerant replaceable multi-chip hybrid modules, are recommended for MPP implementation.

### (a) Fault-tolerance

Second-generation MPPs would offer improved system reliability and ease of maintenance, by adding redundancy to the processor ensemble and achieving in-service fault-tolerance with self-testing and electronic reconfiguration to isolate faulty processors. Moreover, fault-tolerant second-generation MPPs could support graceful degradation or even fail-safe systems.

## (b) Modular systems

With service lifetimes extending beyond 10 years, ease of maintenance will be a key issue for second-generation MPPs, which will stimulate a trend towards modular parallel

computing systems. Indeed, ease of maintenance would be greatly improved by the use of line replaceable modules, since simple plug-in module replacement would provide the opportunity of minimizing down-time and maximizing availability.

# (c) Microelectronics and packaging technologies

Increasing micro-miniaturization offers improvements in reliability and ease of maintenance, owing to the integration of chip-to-board-to-chip interconnections, the consequent reduction of failure-prone board connectors, and the increasing effectiveness of plug-in module replacement. Consequently, the trend towards the implementation of second-generation MPPs with HDMI-VLSI multi-chip modules, recommended above for size and weight reduction, is reinforced by these advantages.

## (iii) Cost-lifetime

The history of maxicomputer, minicomputer and microcomputer development suggests that first-generation MPPs will rapidly become obsolete as inevitable advances in microelectronics technology (e.g. increasing chip size and reducing feature size) allow more exciting products to enter the market place. Thus, second-generation MPP customers are likely to be wary of technological change. Indeed, wise customers will be looking for security and growth potential in 'future-proof' investments in MPP technology.

With service lifetimes extending beyond 10 years, architectural and software durability under functional upgrade (as application requirements change) and technological upgrade (without modification of existing software) will be very important requirements for second-generation MPPs. Indeed, the trend towards modular systems (see above) could provide some degree of system (design) stability and technology independence, with simple replacement of MPP modules.

### (iv) Cost-performance

Emerging from the first-generation MPP experience is the realization that the cost-performance of second-generation MPPs will not be dominated by the exciting increase in processing power, but by the much more mundane details of the implementation cost of the processor ensemble and, especially, the inter-processor communication network, plus the peripheral costs of the global memory, control unit, and data interfaces.

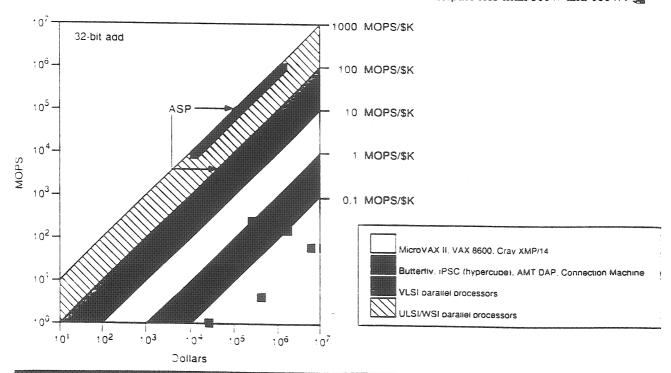

Indeed, significant increases in processing performance have enabled first-generation MPPs to stimulate commercial interest in parallel computing; applications exist, parallel algorithms are being developed, and architectural principles have been established. However, first-generation MPPs are unlikely to break through the cost barrier currently impeding commercial exploitation. For example, first-generation MPPs claim up to

1MOPS/\$1K, which represents only O[1] improvement in cost-performance for O[N] parallelism.

In contrast, second-generation MPPs must aim at O[2]–O[3] improvement, in order to provide an adequate return on the high capital investment required to install new hardware, for programmer retraining and, especially, for new software development. Hence, 1 MOPS/\$ represents a realistic cost–performance target.

In view of the dominating influence of implementation cost and the inevitability of processor redundancy (see below), it follows that second-generation MPPs should be specifically designed to exploit the economic opportunities of microelectronics technology.

## (v) Silicon-efficient chip architecture

Implementing MPP architectures in silicon introduces a different set of cost-performance trade-offs from those previously encountered by first generation MPP designers; these being rather more cost-reduction than performance-enhancement oriented. In contrast to first-generation MPP developments, top-down design of MPP architectures (designed without detailed regard to microelectronic opportunities and constraints) is likely to be less cost-effective than bottom-up design of MPP chips (without regard to architectural requirements).

An important lesson can be learned from the history of computer memory technology. Random-access memories (RAMs) incorporate massive redundancy; since, except for the addressed storage location, all other locations are inactive. Consequently, early computer memories, based on expensive implementation technologies, were kept small to maintain cost-efficiency. However, as technology improved, minimizing memory implementation cost, memory is now so cheap that even modest computers can boast a large main store. Clearly, advances in microelectronics technology have reduced the memory redundancy problem to insignificance. Thus, the challenge is to apply a similar technological trend to improve the cost-effectiveness of the processor ensemble.

With this challenge in mind, it is significant that although memory locations have been greatly reduced in size, memory redundancy remains constantly close to maximum. In contrast, the much lower level of processor redundancy tends to compensate for higher processor complexity.

A concerted attempt to render second-generation MPPs as cost-effective as RAMs would be impelled by the following design attempts to achieve silicon-efficient MPP chip architectures.

# (a) Maximize the packing density of the processor ensemble

In order to reduce the cost of inevitable processor redundancy to a negligible level, this objective requires a maximum number of processors which can be packed on an economical silicon die; this entails minimization of processor layout area to benefit from a high intrinsic chip yield.

### (b) Incorporate the inter-processor communicating network on chip

This objective entails the minimization of the geometrical layout of the inter-processor communication network and supporting global routing for the processor array. As layout feature sizes continue to reduce and VLSI chip sizes increase, the inter-processor communication network progressively dominates the device architecture, such that placement of individual processors is becoming a secondary consideration. Thus, integrating the network within the processor ensemble is of major importance for the reduction of MPP implementation cost.

### (c) Minimize input-output pinning overheads

This objective recognizes that the cost of microelectronic assembly is dominated by interconnection technology.

In summary, engineering barriers concerning size, weight, reliability, power consumption and cost are currently impeding progress towards the commercial exploitation of second-generation MPPs for real-time parallel computing. Indeed, it is clear that, in order to achieve a breakthrough, it is not just TOPS performance that is required, but second-generation MPPs must also achieve step-function improvements in TOPS/ft<sup>3</sup>, TOPS/lb, TOPS/failure, GOPS/W, and MOPS/\$. For example, assuming that weight and power problems can be resolved, it is generally recognized that a low-cost highly-compact fault-tolerant real-time computer vision system could launch high-volume products in the robotics market.

Current trends in microelectronics and packaging technologies toward highly-compact plug-in replaceable HDMI-VLSI multi-chip (hydrid) modules augur the desired breakthrough and, at the same time, simplify problems of tolerating harsh environmental conditions. Moreover, simple module replacement satisfies the need for ease of maintenance and provides a convenient means for both functional and technological upgrade during operational lifetime.

### 1.5 Dedicated pipeline architectures

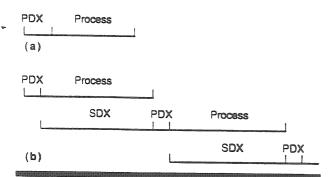

An ideal real-time parallel computing system would instantaneously process each data sample on input and, consequently, the traditional approach to the implementation of such systems is a pipeline of different processors, as shown in Fig. 4, with each stage being dedicated to a specific task which is executed on-the-fly as data flush through its processor. Clearly, in order to process a continuous stream of data samples, the task—processing rate of the first stage of the pipeline must match the maximum input data rate. However, the performance of each subsequent processor in the pipeline, can be optimized to reduce the overall latency delay of the output response.

Fig. 4 Dedicated pipeline processor

Such spatial partitioning of task parallelism implies that the scaling of overall parallel processing power, to match the ever-changing (input-to-output) complexities and performance requirements of different parallel computing applications, entails adjusting the length of the pipeline with the insertion or removal of high-performance hardware stages. Indeed, although the rate of data transfer between stages reduces rapidly as computation proceeds along the pipeline, particular tasks may, nevertheless, be based on quite complex algorithms, requiring the high-speed execution of very many low-level operations.

This ad hoc optimization of different processors and the emphasis on high-speed data flow between processors restricts opportunities for microelectronics and packaging technologies to reduce the number of expensive and error-prone interconnections and, thereby, overcome the engineering problems discussed above. Indeed, development, manufacture, and maintenance costs for a range of such unique (i.e. low volume) modules will inevitably remain high (compared with large volume standard parts) and system durability will be difficult to maintain. Moreover, the expense of a redundant processor in irregular parallel computing pipelines is likely to render attempts at fault-tolerance cost-ineffective. Consequently, such machines are unlikely to achieve the desired engineering breakthrough.

The traditional approach to overcoming these problems would be with a regular parallel computing pipeline of identical stages (e.g. the linear systolic array). Real-time on-the-fly processing can still be achieved, but the output response now suffers a latency delay which depends on the length of the pipeline (i.e. the number of stages).

By balancing processing rate with input data rate, the uniform pipeline processor gains an undoubted advantage in speed for signal processing. However, lack of architectural and programming flexibility would severely reduce the efficiency of the numeric-to-symbolic data conversion process and AI processing for which the common processing stages are not so well suited.

Lastly, it is interesting to note that such homogeneous pipeline architectures derive little benefit from the experimental observations, that for most real-time parallel computing applications the numeric-to-symbolic data conversion process may reduce the output data volume by several orders of magnitude (with respect to a given input data volume), and that application requirements for processing and input data rates are normally significantly different.

## 1.6 MIMD/SIMD array processing architectures

Architectural alternatives to dedicated pipelines, which attempt to take advantage of the above criticisms and observations, are based on homogeneous MIMD/SIMD (Multiple/Single Instruction control of Multiple Data Streams) array processing, as indicated in Fig. 5. In this case, the numeric-to-symbolic data conversation process is achieved by first distributing data elements over the identical processors of the MIMD/SIMD architecture and then executing successive tasks on the stored data. Hence, such temporal partitioning of task parallelism must be supported by data buffering to ensure that task processing rates are independent of input and output data rates.

Since application requirements for processing and input data rates are normally significantly different, such (buffered) MIMD/SIMD architectures provide a more natural medium for application flexibility than dedicated pipelines. Moreover, it should be noted that the temporal parallelism of homogeneous MIMD/SIMD array processing architectures, in contrast to the spatial parallelism of dedicated pipeline architectures, offers much greater application flexibility with a much simpler and cheaper medium for programmability and scaling of processing power.

In addition, in order to maintain high computational efficiency with MIMD/SIMD architectures, an effective balance between input data pipelining and parallel processing power must be ensured. Moreover, all sequential (scalar) processing should be overlapped (in the MIMD/SIMD array controllers) with parallel (vector) processing in the MIMD/SIMD arrays and, whenever possible, data transfer should be achieved with external data routing networks.

# 2. OPPORTUNITY

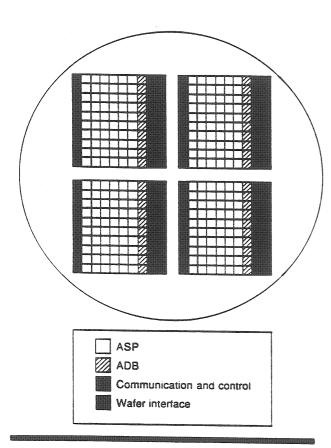

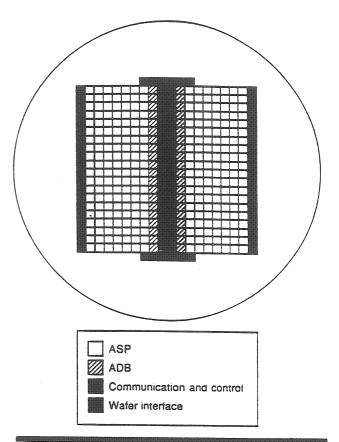

In terms of application flexibility, architectural scalability and all the engineering issues discussed above, the development of computer storage has been a great success. Indeed, as the ultimately cost-effective computer component, RAM storage represents an ideal model for the development of second-generation MPPs.

Consequently, since traditional computer storage is organized with a string topology [i.e. all application data structures are mapped to a string of (groups of) words in RAM or bytes on disk], it seems a logical prospect for second-generation MPPs to be organized as a string of processors.

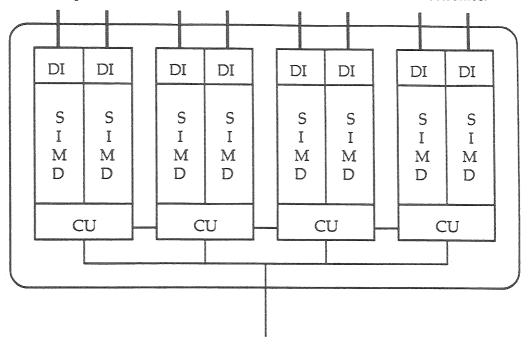

Thus, further consideration of the perspective presented above has led to the conclusion that a simply scalable and fault-tolerant homogeneous parallel computing hierarchy, based on MIMSIMD (Multiple-Instruction control of Multiple SIMD) processors, would offer the best opportunity for cost-effective second-generation MPPs.

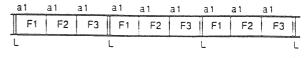

According to application requirements, a string of identical MIMSIMD processors would be plugged into the control bus and Data Communications Network of an appropriate modular MPP racking system, as indicated in Fig. 5.

Fig. 5 Modular second-generation MPP

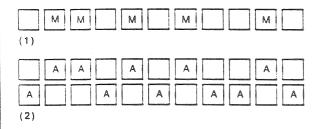

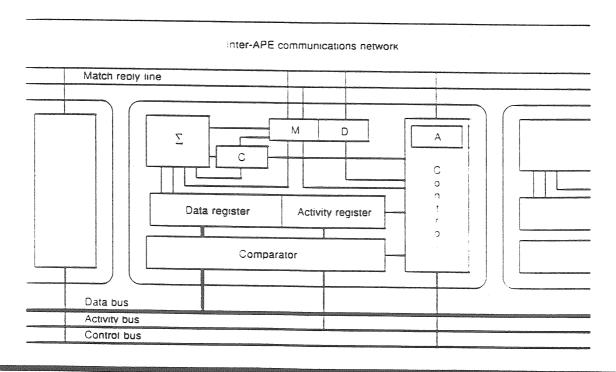

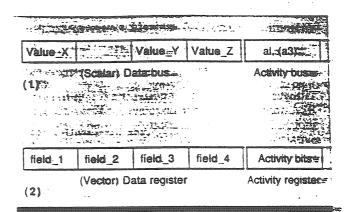

Each MIMSIMD processor comprises a simply scalable and fault-tolerant string of inter-communicating SIMD processors and shared Control Units (CUs), as shown in Fig. 6. The MIMSIMD processor would also incorporate a Data Interface (DI) for each SIMD processor and a common control interface, to connect to the MPP system rack.

Similarly, at the next level down in this homogeneous parallel computing hierarchy, each SIMD processor would comprise a simply scalable and fault-tolerant string of a large number of identical fine-grain processors and a reconfigurable inter-processor

communication network. As with RAM storage, the SIMD processors would be internally organized to exploit the most recent advances in state-of-the-art microelectronics.

Fig. 6 MIMSIMD processor

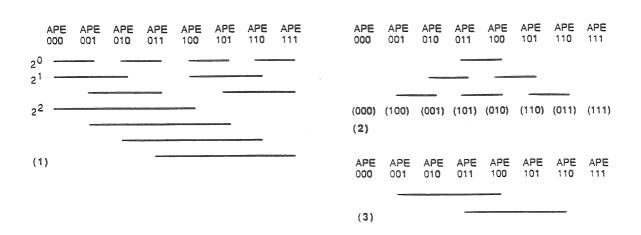

### 2.1 The Associative String Processor (ASP)

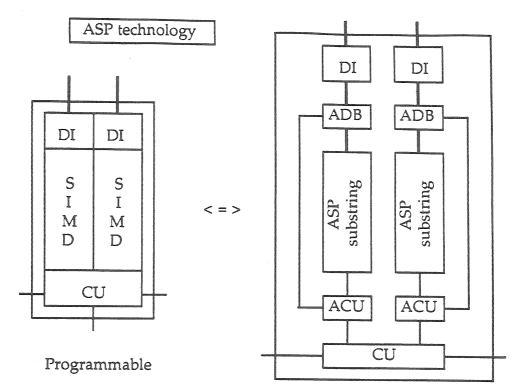

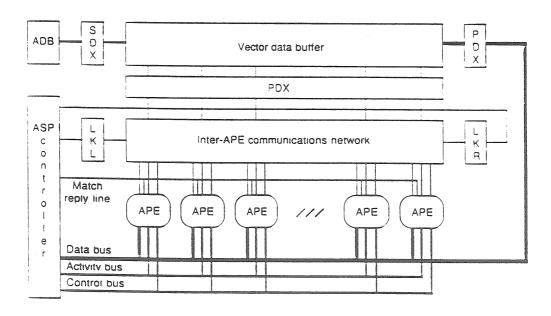

Associative String Processor architecture and support software provide the basic technology for the development of versatile parallel processing building-blocks (i.e. ASP modules of the form shown in Fig. 6) for the simple construction of modular real-time MPP systems.

An ASP module comprises a MIMSIMD parallel processing structure of intercommunicating ASP substrings, each supported with an ASP Data Buffer (ADB) and an ASP Control Unit (ACU), as shown in Figs 6 and 7. The ASP module also incorporates a single Control Interface (CI) and a multiple DI, to connect to the system rack.

Based on the encouraging results emerging from research into parallel computing architecture at Brunel University and being developed by ASPEX-Microsystems Ltd., ASP technology comprises highly versatile hardware and software modules for the construction of second-generation MPPs capable of TOPS performance.

The ASP system architecture has been specifically designed to satisfy both the second-generation MPP computational requirements and the engineering constraints discussed in the perspective above. Indeed, it is claimed that the ASP is the first parallel computing architecture to achieve this design goal.

Fig. 7 ASP substrings

Based on a fully-programmable, reconfigurable and fault-tolerant homogeneous parallel processing architecture, ASP modules offer considerable application flexibility, maintaining high computational efficiency over a particularly wide range of signal and data processing applications, due to:

- (i) simple configuration of ASP modules to simplify the development of MPP systems which are well matched to functional application requirements;

- (ii) pipelining and overlapping input—output data transfers (via the Data Communications Network) with parallel processing (within ASP sub-strings), by separating input—output from processing with the ADBs;

- (iii) overlapping of sequential processing in the ACUs with parallel processing (in ASP substrings);

- (iv) mapping different application data structures to a common string representation within ASP substrings (supporting content-addressing, parallel processing, and a reconfigurable inter-processor communication network).

The numeric-to-symbolic data conversion process (sect. 1) is achieved by first distributing data elements over the identical processors of the ASP substrings and then executing successive tasks on the stored data. Such temporal partitioning of task parallelism ensures that task processing rates are independent of input data rate, owing to data buffering

with ADBs; and scaling of overall parallel processing power simply entails adjusting the number and length of ASP substrings. Indeed, ADB storage and the uniformity of ASP substrings provide much cheaper media for scaling than the expensive processors of a dedicated pipeline.

In summary, the ASP chip architecture offers a highly compact implementation of the SIMD processor discussed above, which exploits the following benefits of associative processing:

- (i) Elimination of processor (location) addressing, for the purpose of :

- (a) achieving unlimited architectural scalability,

- (b) implementing cost-effective fault-tolerance with simple (hierarchical) bypassing of faulty processor substrings, which, until failure occurs, are available for parallel processing,

- (c) further minimization of sequential processing overheads.

- (ii) Minimization of inter-processor data movement, with high-speed activity transfer between processor subsets and in situ processing.

In particular, the ASP architecture provides an unprecedented opportunity for second-generation MPPs which require dynamic allocation of processors for the flexible and progressive trade-off of parallel processing power for increasing fault-tolerance.

Further descriptions of the ASP architecture can be found in the attached supporting documents (Annexes I and II).

By exploiting the inevitable VLSI-to-ULSI-to-WSI technological trend and state-of-the-art packaging technologies, cost-effective and highly-compact ASP modules can be implemented, which achieve processor packing-densities which are more usually associated with memory components.

In practice, ASP module form factors will depend on the packaging standards adopted for the modular construction systems of particular application environments. Indeed, the availability of such packages is intended to simplify MPP hardware development to the electrical/thermal design of appropriate bus—cooling racks, into which replaceable ASP modules can be plugged, in order to construct a MPP crate compatible with its operational environment.

### 2.1.1 ASP software

ASP application programs can be written entirely in a familiar block-structured high-level language (e.g. PASCAL, Modula-2, C, or ADA) under a familiar operating system (e.g. Unix, VMS or MS-DOS). Such programs include calls to external precompiled ASP

algorithms and procedures, written and progressively refined (in the same language) by experts, with an intimate knowledge of the ASP architecture, using a set of built-in function and procedure primitives to implement basic ASP operations. Thus, the average ASP application programmer/user does not face the full complexity of parallel algorithm development, but the much less demanding task of selecting and interfacing appropriate code from the hierarchically-organized ASP algorithm and procedure library, and only occasionally resorts to the creation of such code.

Examples of ASP procedures are given in Annexes I and II.

Parallel constructs for ASP programming are being actively investigated in experimental research programmes, but this activity is beyond the scope of this proposal.

The ASP software development system incorporates an ASP simulator, supporting multi-window ASP state and timing displays, to provide a flexible environment for the development of ASP programs.

### 2.1.2 TRAX-1

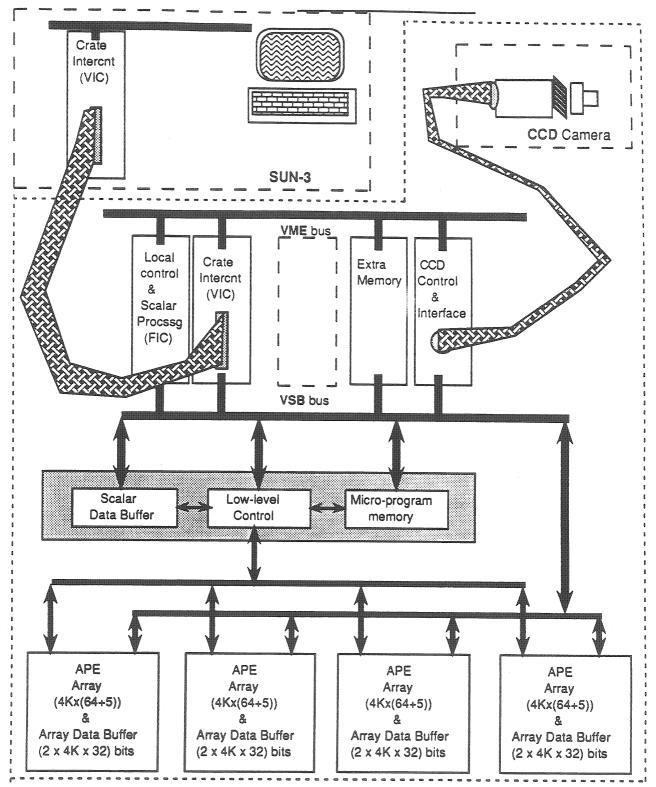

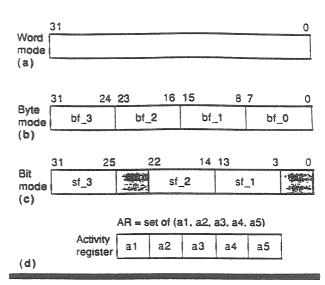

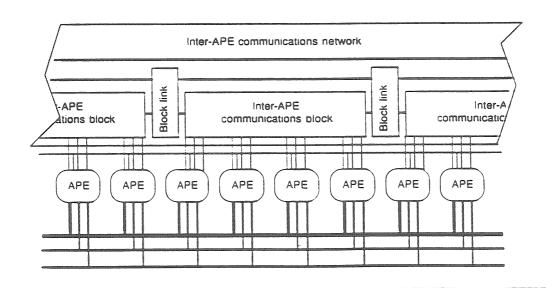

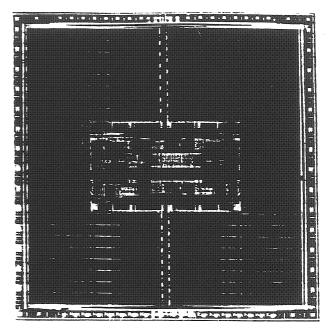

Developed by ASPEX-Microsystems, LAA, and the NA35 Collaboration, Trax-I consists of an ASP, with 16,384 Associative Processing Elements (APEs) which has been targeted for the off-line analysis of streamer chamber pictures of very complicated events. As shown in Fig. 8, TRAX-I consists of:

#### Hardware

- Host and host environment:

- SUN 3/160

- Unix and SUN tools

- Intermediate-level control

- 68020

- 256 kbytes of program storage

- 512 kbytes of ASP data storage (RAM)

- Provision for storage extension

- VME/VSB interface to host, ASP modules and data capture devices (CCDs)

- DMA data transfer between host, intermediate-level controller, and ASP modules

### • ASP module control

- Custom built based on a high performance sequencer

- 256 kbytes of micro-program memory

- Input scalar buffer with 8 kbytes cache

- Output scaler buffer with 8 kbytes cache

- 16 kbytes scratch pad buffer

- Scalar-vector operations hardware support

### ASP modules

- 4 ASP modules, each comprising 4096 APEs and (2 x 4 k x 32-bits) Array Data Buffer (ADB)

- 64-bit Data Register per APE, supporting bit-serial, byte and 32-bit word data formats

- 5-bit Activity Register per APE

- String connectivity between all ASP modules.

#### Software

- Host and host environment

- Programming in standard Modula-2, use of Libraries

- Debugging standard SUN-based tools

- Intermediate-level control

- Programming in Modula

- 2, use of Libraries

- Debugging 68020 EPROM monitor

- ASP module control and ASP modules

- Programming Modula-2 based custom language, use of Libraries

- Debugging ASP display windows, performance statistics window, source code trace.

### 2.2 ASP potential

The progress of ASP hardware and software research heralds the development of a highly-versatile and fault-tolerant line replaceable module (SEM-E) for the construction of modular MPP systems; with significant benefits in reliability, ease of maintenance, and service lifetime achieved with optimal exploitation of WSI microelectronics and packaging technologies.

**TRAX 1:** Particle Physics Workstation System Architecture-Schematic Diagram

Fig. 8 The TRAX 1 machine. Schematic diagram of the system architecture

In terms of cost-effectiveness, application studies and benchmark evaluations are demonstrating that ASP modules could match and often improve on the performance figures of contemporary MPP implementations; consequently, the competitive edge becomes that of size, weight, power requirement and, especially, cost-performance. Hence, the design targets shown in Table 2 summarize the potential of ASP modules in these terms.

**TABLE 2 –** ASP module design targets

| Configuration          | 1, 2 or 4 MIMSIMD blocks         |

|------------------------|----------------------------------|

| Performance            | 100 GOPS (12-bit adds at 40 MHz) |

| Input-output bandwidth | 320 Mbytes (at 20 MHz)           |

| Number of processors   | 65,536                           |

| Package size           | 6.4" x 5.88" x 0.6" (SEM-E)      |

| Power dissipation      | < 100 W (i.e. > 1 GOPS/W)        |

| Market cost            | < \$100,000 (i.e. > 1 MOPS/\$)   |

Since they are based on the extrapolation of results gained from experimental VLSI and WSI ASP test chips, the first four ASP module design targets of Table 2 are fairly conservative. Moreover, the cost target includes ample provision for marketing overheads, software support and profit, thereby indicating potential for significant cost reduction for higher volume marketing. In fact, the most speculative target is that of power dissipation, this being a compromise between the 50 W quoted for SEM-Es and the desire to maximize performance. Hence, current research is addressing this issue not only in terms of minimizing power dissipation in WSI circuit design, but also in improvement of the thermal characteristics of appropriate assembly and packaging materials.

Comparison with the 65,536-processor Connection Machine [CM-1: achieving 2.7 GOPS (for 12-bit adds) with a 62.5 Mbytes/s input-output bandwidth, housed in a 50" x 50" cabinet and dissipating 12 kW, for a market cost of \$3M] suggests that ASP modules offer some three orders-of-magnitude improvement in cost-performance and size. More significantly, ASP modules offer simple scalability; for example, a peak performance of 1 TOPS (i.e. 1000 GOPS) could be achieved with only 10 modules, within less than a cubic foot, and dissipating 1 kW.

### 2.2.1 ASP module performance

Extrapolation (from the results of evaluation experiments with  $2 \mu m$  CMOS VLSI ASP test chips and a 20 MHz clock-rate) enables the forecast of timings for addition and

multiplication (1.2  $\mu m$  CMOS chip fabrication technology and a 40 MHz clock-rate) presented in Tables 3 and 4.

TABLE 3

Bit-serial arithmetic timings and equivalent performance (in GOPS, i.e. 109 operations per second) assuming a 65,536-APE ASP

|                        | 8-bit          | 16-bit         | 32-bit          |

|------------------------|----------------|----------------|-----------------|

| Add/subtract           | 0.45 μs (146)  | 0.85 μs (77.1) | 1.65 μs (39.7)  |

| Scalar-vector multiply | 2.90 μs (22.6) | 10.0 μs (6.55) | 37.0 μs (1.77)  |

| Vector-vector multiply | 5.15 μs (12.7) | 18.8 µs (3.49) | 71.9 µs (0.911) |

TABLE 4

Bit-parallel arithmetic timings and equivalent performance (in GOPS, i.e. 10<sup>9</sup> operations per second) assuming a 65,536-APE ASP

|                        | 8-bit          | 16-bit          | 32-bit          |

|------------------------|----------------|-----------------|-----------------|

| Add/subtract           | 0.15 μs (54.6) | 0.15 μs (27.3)  | 0.15 μs (13.7)  |

| Scalar-vector multiply | 0.55 μs (14.9) | 1.10 μs (3.73)  | 3.20 µs (0.640) |

| Vector-vector multiply | 1.80 µs (4.55) | 4.95 μs (0.827) | 12.4 μs (0.165) |

To indicate typical DSP application performance, Tables 5 and 6 forecast digital filtering and fast Fourier Transform (FFT) timings.

TABLE 5

Digital filter timings (bit-serial mode) and equivalent performance (in GOPS, i.e. 109 operations per second) assuming a 65,536-APE ASP and equal bit-precision for samples and weights and full-precision results

|        | 8-bit          | 16-bit         | 32-bit          |

|--------|----------------|----------------|-----------------|

| 4-tap  | 0.15 μs (54.6) | 0.15 μs (27.3) | 0.15 μs (13.7)  |

| 8-tap  | 0.55 μs (14.9) | 1.10 μs (3.73) | 3.20 µs (0.640) |

| 12-tap | 1.80 μs (14.9) | 4.95 μs (0.827 | 12.4 μs (0.165) |

#### TABLE 6

FFT timings (bit-serial mode) and equivalent performance (in MOPS, i.e. 10<sup>6</sup> operations per second) assuming a 65,536-APE ASP and 8-bit samples and full-precision results

| 256-points  | 752 µs (0.340) |

|-------------|----------------|

| 512-points  | 874 μs (0.146) |

| 1024-points | 977 μs (0.065) |

For higher performance levels, the results could simply be scaled by module replication.

It should be noted that the performance forecasts presented in Tables 3 to 6, are representative of those expected for the long-term target ASP module (see above) and not interim ASP prototypes such as TRAX-1.

### 2.2.2 Performance benchmark results

Of course, such performance forecasts refer only to the low-level arithmetic operations of the numeric-to-symbolic data conversion process of real-time signal and data processing. Indeed, more realistic performance indication can be gained from application benchmarks, which include all processing from data input to the output of the required response. To this end, the ASP architecture has been evaluated in terms of the 2 US DARPA Image Understanding benchmarks set in 1986 and 1988 and the CERN LAA benchmark (which includes TRAX-1) in 1989. Although beyond the scope of this proposal, the results (see supporting documents: Annexes III, IV, and V) nevertheless indicate major costperformance advantages for ASP modules compared with contemporary parallel computers.

### 3. OBJECTIVES

## 3.1 The Pilot Project: an intelligent on-line camera

Parallel processing and in particular associative parallel processing can solve the computational bottleneck of a large variety of problems in very different fields, some of which are of great interest to this Collaboration. But in order to focus our efforts on the development of the necessary hardware and software platforms a leading project was selected which will demonstrate in an experiment at CERN the high rate on—line data acquisition and analysis of events with at least 1 Mbyte of information each.

The most straightforward detector that can produce the required data rate and which is useful in several detectors for high-energy physics experiments is an image intensified CCD camera with 1 k x 1 k pixels readout at close to video rates. This is the choice of the collaboration as a Pilot Project for MPPC. A sketch of the proposed camera is shown in Fig. 9. Such a system can be used to read out avalanche chamber events in relativistic heavy ion collisions [7] in which hundreds of particles are produced in the final state, or for large-area RICH counters being developed or for the readout of scintillating fibre detectors for future hadron collider experiments [2].

The CCD sensor selected for the camera is the Thomson THX 31156 [8] with  $1024 \times 1024$  square pixels of  $19 \, \mu m^2$  area. It has been chosen because of its 100% sensitive area, its large dynamic range, and good signal-to-noise ratio and quantum efficiency. It will be coupled with fibre optics to a four-stage EMI image intensifier for the detection of events at very low light levels.

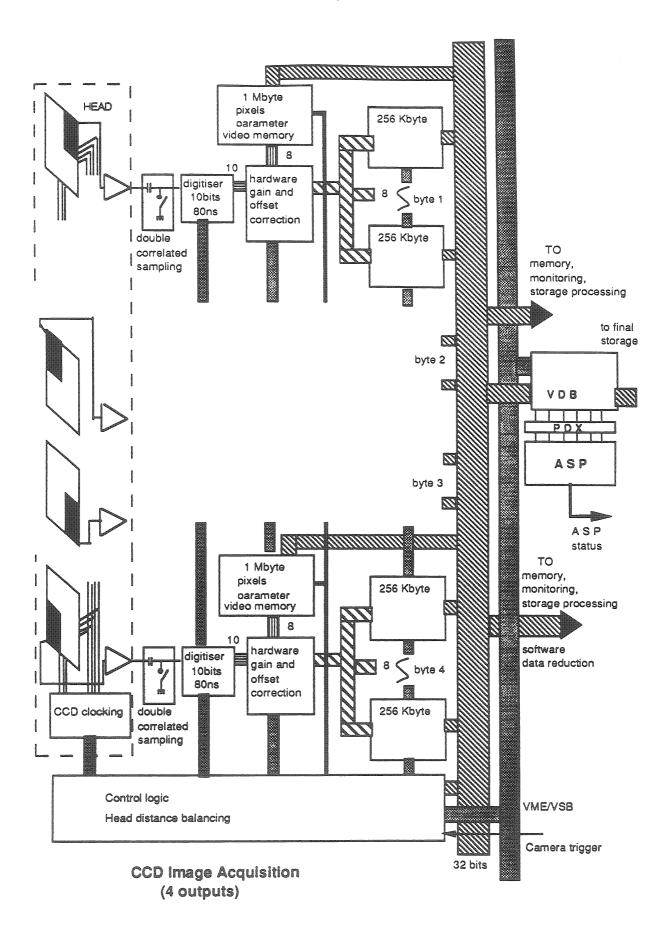

The camera head should have two functional modes; one being the TV mode in which the image can be displayed directly on a TV monitor and a digitizing mode in which the image of the triggered event is sent digitized to the ASP modules. The first mode is necessary for the focusing of the camera and the debugging of the detector being imaged. The digitalization of the 1 k x 1 k CCD chip will be done using the four outputs each at 10 MHz on 10 bits, using double correlate sampling for a good signal—to—noise value.

In the acquisition mode a pedestal image of the inherent noise of each pixel has to be subtracted. For this reason a blank picture will be stored in a buffer on command. For real images after pedestal subtraction the 10 bits will be reduced to 8 by using a look—up table. The stream of 8 bit data will be sent to the ASP; the detailed bus and the manner in which it will be done still has to be determined. It will be a great advantage to use this architecture because it allows processing of the image on-line with the data taking, using all the features of the 65,536 ASP including fast data exchange, fault tolerant capability, and reconfigurability for fast intercommunications between APEs.

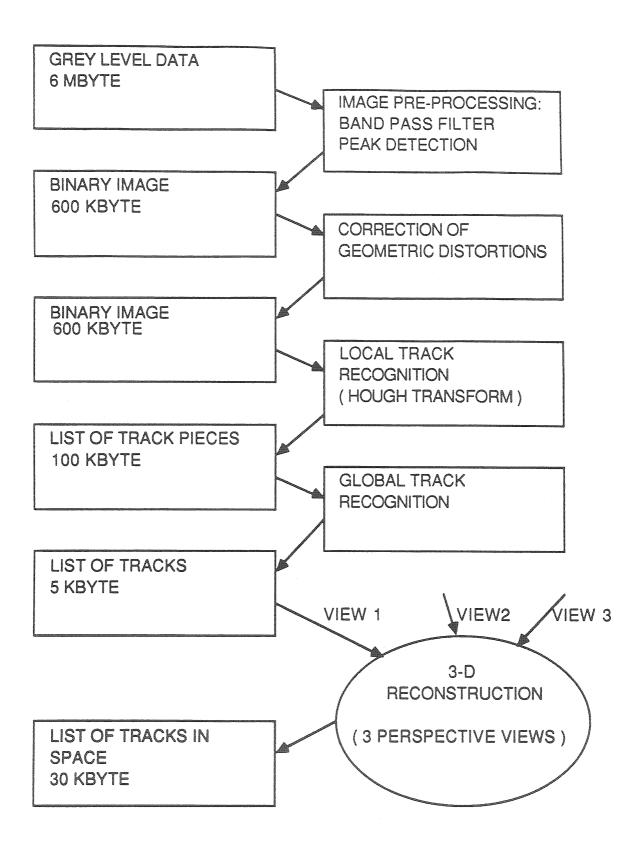

On the acquired images iconic and symbolic image processing will be done to reconstruct tracks and RICH patterns over the whole image. The full image will be analysed by mapping and processing patches. In order to get the highest efficiency possible, algorithms will be developed taking full advantage of the parallelism and of the ASP architecture.

Fig. 9 The Pilot Project: a CCD 1 megapixel on-line camera

## 3.2 The contribution of massively parallel processing to high-energy physics

There are many ways in which MPPs can have an impact at CERN and on its environment. Among these only the main class of applications will be indicated.