## Università degli studi di Napoli "Federico II"

Dottorato di ricerca in Fisica fondamentale ed applicata XXIII Ciclo

Luciano Capasso

# The Monitoring system of the ATLAS Muon Spectrometer Read Out Driver

A thesis submitted for the degree in Doctor of Philosophy in Physics

Supervisor:

Prof. A. Aloisio

Advisors:

Prof. I. Ortosecco Dott. G. Saracino

All truths are easy to understand once they are discovered. The point is to discover them.

Galileo Galilei

## Contents

| CONTENTS                                                          | <u>l</u>   |

|-------------------------------------------------------------------|------------|

| INTRODUCTION                                                      |            |

| CHAPTER ONE – THE ATLAS EXPERIMENT AND ITS DETECTOR               | 1          |

| 1.1 The Large Hadron Collider (LHC) main goals                    | 1          |

| 1.2 THE LHC ARCHITECTURE.                                         |            |

| 1.3 THE ATLAS DETECTOR                                            |            |

| 1.3.1 The magnetic system.                                        |            |

| 1.3.2 The inner detector                                          |            |

| 1.3.3 The calorimeters.                                           |            |

| 1.3.4 The Muon Spectrometer.                                      |            |

| 1.3.5 The trigger and the Data acquisition (DAQ) systems          |            |

| CHAPTER TWO – THE LEVEL 1 TRIGGER AND THE DATA ACQUISITION SYSTEM |            |

| THE ATLAS MUON SPECTROMETER.                                      | <u></u> 27 |

| 2.1 Overview of the Level 1 trigger system                        |            |

| 2.2 The trigger and DAQ system architecture                       |            |

| 2.3 THE LVL1 TRIGGER ALGORITHM FOR MUON DETECTION.                |            |

| 2.4 The segmentation of the muon spectrometer.                    |            |

| 2.5 The Resistive Plate Chambers.                                 |            |

| 2.6 The synchronization of the apparatus                          |            |

| 2.6.1 The Timing, Trigger and Control system                      |            |

| 2.7 THE RPC TRIGGER AND DAQ ELECTRONICS.                          |            |

| 2.7.1 The Coincidence matrix                                      |            |

| 2.7.2 The PAD board                                               |            |

| 2.7.3 The data path architecture                                  | 43         |

| CHAPTER THREE - THE READ OUT DRIVER OF THE ATLAS MUON SPECTROME   | TER_       |

| RPCS                                                              | 45         |

| 3.1 The ROD board in the DAQ system.                              | 45         |

| 3.1.1 The RX section of the RX/Sector Logic board                 | 46         |

| 3.1.2 The RODbus                                                  |            |

| 3.1.3 The Read Out Driver                                         |            |

| 3.1.4 The VME FPGA                                                | <u>52</u>  |

| 3.1.5 The serial custom protocol between the FPGAs                | <u>53</u>  |

| 3.1.6 The ROD FPGA                                                | 54         |

| 3.1.7 The Data and Control paths                                  | <u>55</u>  |

| 3.1.8 The serializers (SerDes)                                    |            |

| 3.1.9 The TTCrq                                                   | <u>57</u>  |

| 3.1.10 S-Link                                                     | <u>61</u>  |

| 3.1.11 The FIFO memories                                          | <u>65</u>  |

| 3.1.12 Clock domains and clock muxes                              | <u>66</u>  |

| 3.1.13 The ARM7 microcontroller                                   |            |

| 3.2 The Event building algorithm                                  |            |

| 3.2.1 The Event Builder Engine                                    | <u>71</u>  |

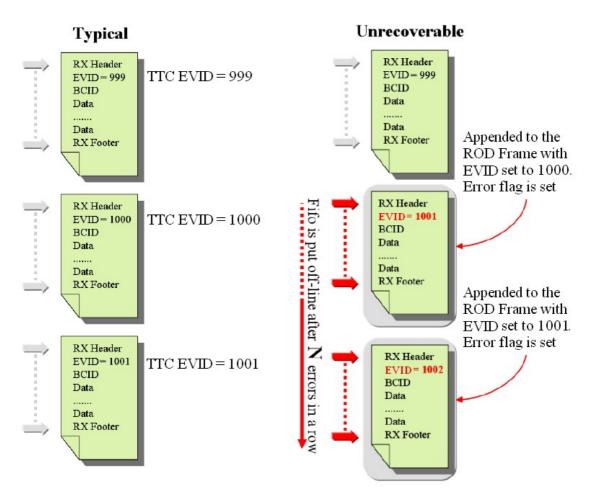

| 3.2.2 EVID errors handling                                        |            |

| 3.2.2 Frame syntax errors handling                                | <u>77</u>  |

| CHAPTER FOUR - THE MONITORING SYSTEM OF THE ROD EVENT BUILDER    | <u>79</u>  |

|------------------------------------------------------------------|------------|

| 4.1 The monitoring environment                                   | 79         |

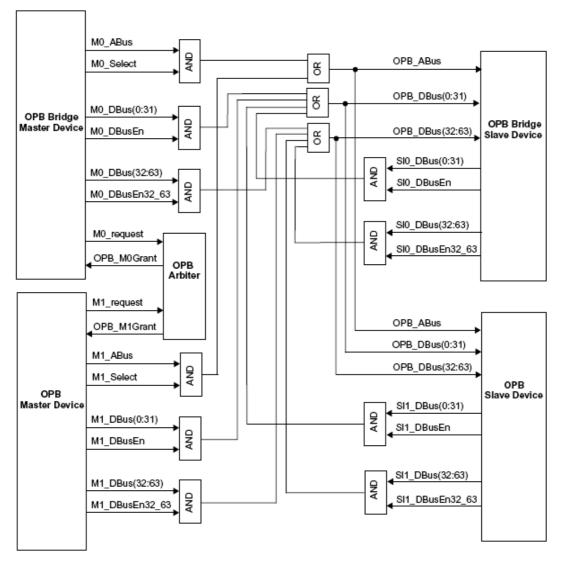

| 4.2 The MicroBlaze processor                                     | 81         |

| 4.3 MICROBLAZE ENVIRONMENT OVERVIEW.                             | 84         |

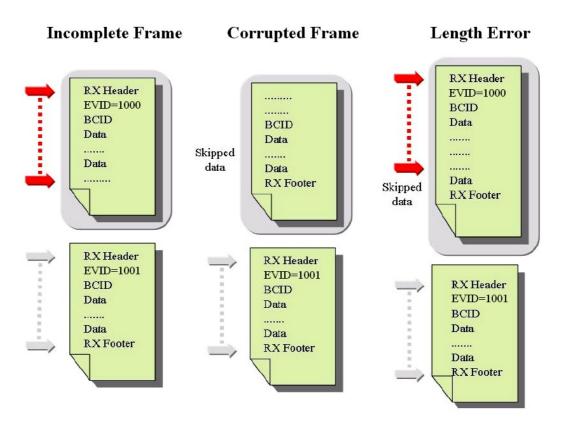

|                                                                  | 85         |

| 4.3.1 The custom protocol with the Communication Interface block | 86         |

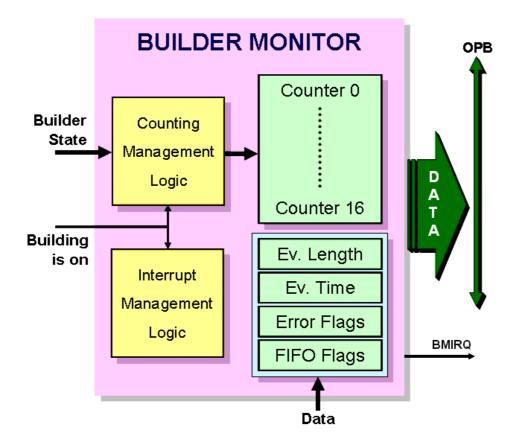

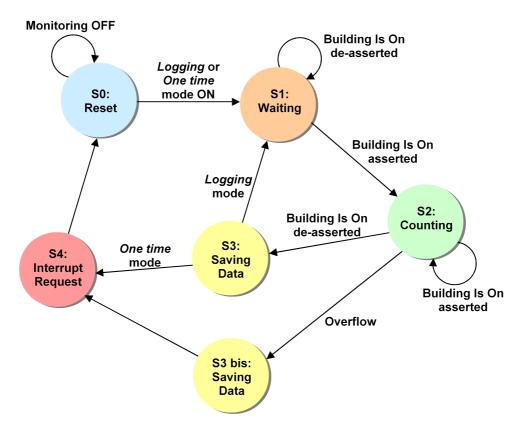

| 4.3.2 The Builder Monitor                                        | <u>90</u>  |

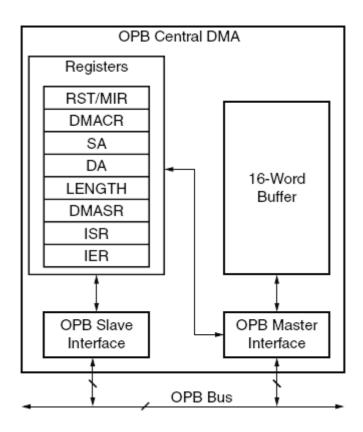

| 4.3.3 The DMA Controller device                                  |            |

| 4.3.4 The Interrupt Controller device                            | 95         |

| 4.4 The software architecture                                    |            |

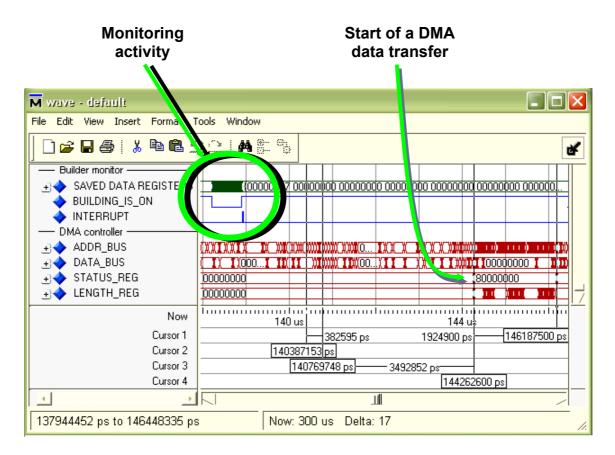

| 4.5 Simulations and tests                                        | <u>97</u>  |

| 4.5.1 Commissioning at CERN                                      | 101        |

| CONCLUSIONS                                                      |            |

| APPENDIX A                                                       | 107        |

| A.1 THE VME FPGA REGISTERS                                       |            |

| A.2 THE ROD FPGA INTERNAL REGISTERS                              | 110        |

| REFERENCES                                                       | <u>117</u> |

## Introduction

This thesis describes the design and test of the monitoring system of the Muon Spectrometer Read Out Driver (ROD) of the ATLAS experiment.

The Large Hadron Collider (LHC) is a particle accelerator and collider located at CERN in Geneva (Switzerland). It has been designed in order to provide proton-proton collisions with an energy of 14 TeV in the center-of-mass and a luminosity of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. The first beam in the Large Hadron Collider was successfully steered in the morning of 2008,  $10_{th}$  September. From that day until now, there have been measurements and calibration operations, in order to increase the beams' energy and luminosity to reach the foreseen values written above. Actually it reached energies of 7 TeV and luminosities of  $10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>.

The LHC has four interaction points around its circumference. Around one of these points, the ATLAS detector has been built.

The general purpose detector ATLAS (A Toroidal LHC ApparatuS) has been designed primarily to search for the Higgs boson in a wide mass range and in its main decay channels. The Higgs boson is theoretically responsible for the electroweak symmetry breaking and for the particle mass generation.

ATLAS will also allow measurements within B meson and top quarks physics, the study of CP violation and the search for SUSY particles.

The ATLAS muon spectrometer is located in the outer region of the detector and it is fundamental for many of the program items of the ATLAS experiment. The production of high mass particles generates muons with high transverse momentum ( $p_T$ ), so the selection and the precision measurement on muons with high  $p_T$  is of the outmost importance for the physics program.

In the barrel region of the muon spectrometer, Resistive Plate Chambers (RPC) are used as trigger detectors. Data from RPCs are collected by on-detector electronics and sent via optical fibres to the USA15 counting room, where they are received by RX boards and then transferred to the Read Out Driver (ROD) boards.

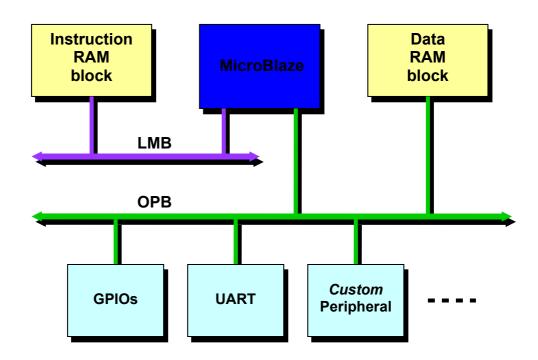

The ROD is a VME electronic board and it is part of the Data Acquisition (DAQ) environment of the ATLAS detector. It performs the event building, checks the correct data formatting and transmits the data to further data analysis levels. In the ATLAS DAQ system, each RPC ROD handles data coming from one of the 32 half-sectors of the ATLAS muon spectrometer. The ROD also controls some of the critical elements of the data acquisition system, such as the synchronization with the LHC collider, using some LHC signals and distributing them to the RX boards. The ROD event building algorithm is executed by Finite State Machines (FSMs).

My original contribution during the PhD school to the ATLAS experiment was to develop a monitoring system of the ROD Event Builder. Such system performs real time and statistical analysis of the ROD state machines dynamics. It is designed around a microprocessor interfaced with several custom peripherals. The system allows to profile the ROD activity by filling histograms, plots and transferring the ROD monitored data via SSH to a remote terminal. The monitoring environment also measures the elapsed time for each event, its length and keeps track of status and error words produced during the event building operation.

The first chapter of this thesis briefly describes the ATLAS experiment, the LHC collider and the main items of its physics program. The muon spectrometer and the its trigger system based on RPC detectors are described more deeply, while a general description of the ATLAS trigger and DAQ systems is also provided.

The second chapter is about the level 1 trigger system of the muon spectrometer. The trigger system segmentation, the algorithms for the detection of muons and the synchronization of the DAQ systems are presented. It is provided also a description of the trigger electronics

The third chapter describes the ROD board: in particular the chapter presents the hardware architecture of the ROD environment, the devices hosted on board and the electronics developed inside the FPGAs. Details on the Event Builder finite state machine and on its Engine are provided.

Chapter four presents the monitoring system of the ROD Event Builder Engine, which is the original contribution I gave to this PhD thesis work. Such system is based upon a soft-core microprocessor, connected to several peripherals and embedded inside the same FPGA hosting the ROD Event Builder Engine. The hardware environment and the processor's software architecture are deeply described. Finally the results of the performed tests are presented.

## CHAPTER ONE – THE ATLAS EXPERIMENT AND ITS DETECTOR

This chapter describes the architectures of the Large Hadron Collider, the ATLAS detector and its main physics goals. More in detail, a short description of the LHC with its main features is provided and the different sub-detectors of ATLAS together with the magnetic system are analyzed deeply. A particular attention is focused on the Muon spectrometer and its detectors, in both the Barrel and the End-cap sections. Finally an overview of the ATLAS trigger system is presented.

### 1.1 The Large Hadron Collider (LHC) main goals

LHC is the new proton-proton collider built at CERN. It has been designed primarily to search for the Higgs boson, the last piece of the *Standard Model*, a theory describing the interactions of point-like fermions with spin ½ (quarks and leptons) as mediated by bosons of spin 1 (gluons, W, Z and  $\gamma$ ): the gluons mediate the strong interaction between the quarks, another boson (a photon) mediates the electromagnetic interaction between charged particles and three other bosons (W<sup>+</sup>, W<sup>-</sup> and Z<sup>0</sup>) mediate the weak interaction. The Lagrangian of the Standard Model theory has a global gauge invariance under the symmetry group SU(3)<sub>C</sub>  $\otimes$  SU(2)<sub>I</sub>  $\otimes$  U(1)<sub>Hy</sub> where C stands for Colour, I for Isospin and Hy for Hypercharge. The interaction is the manifestation of a local gauge invariance, that implies moreover that all the masses of the fermions and bosons are equal to zero.

The existence of massive particles is justified through the *Spontaneous Symmetry Breaking* mechanism: the local gauge symmetry  $SU(2) \otimes U(1)$  is broken by the existence of a *Higgs field* that implies the existence of a neutral scalar boson H<sup>0</sup>, called *Higgs boson*. This last is thought to be responsible of the masses of all the particles. Until now the experimental data are in agreement with the Standard Model: the discovery of the neutral weak current in the '70s, the discovery of the gluons in 1979 and the discovery of W<sup>±</sup> and Z<sup>0</sup> bosons in 1983. The mass predictions for some of these particles strongly agree with the measured ones [1] [2], as shown in Table 1.

| Quantity        | Measured (GeV/c <sup>2</sup> ) | SM prediction (GeV/c <sup>2</sup> ) |

|-----------------|--------------------------------|-------------------------------------|

| Mass of W boson | 80.399 ± 0.023                 | 80.390 ± 0.018                      |

| Mass of Z boson | 91.1876 ± 0.0021               | 91.1874 ± 0.0021                    |

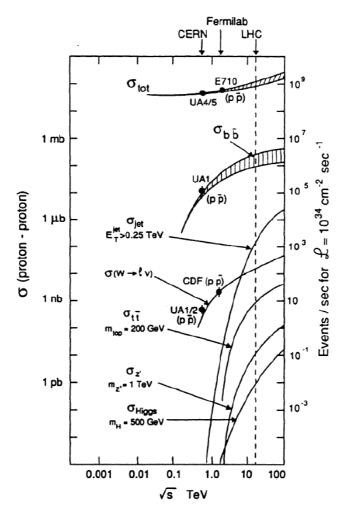

Figure 1 – Cross section for different processes with respect to the center-of-mass energy.

One of the physics goal of the LHC is to discover evidence of the existence of the Higgs boson. In Figure 1 are shown the cross sections of different processes with respect to the center-of-mass energy. The dotted line is the working line foreseen for the LHC when it will be fully operative (it should reach energies of 14 TeV and luminosities of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>). Actually the LHC reached center-of-mass energies of 7 TeV and luminosities of  $10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>. It is possible to see the cross section of the Higgs boson, whose mass is hypothesized to be 500 GeV.

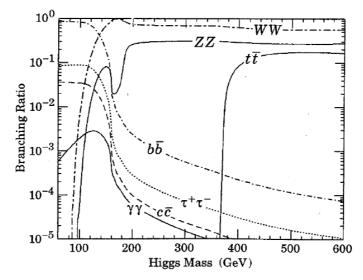

Figure 2 – Branching ratios for the Higgs, with respect to its mass.

Figure 2 shows the branching ratios of several decay channels for the Higgs boson, with respect to its mass. Some processes are difficult to be detected: for example, processes involving neutrinos in the final state require missing energy measurements, or processes with a background of hadronic jets have a difficult reconstruction procedure. The most easily detectable decays are:

$$H \rightarrow ZZ \rightarrow 4$$

leptons

$H \rightarrow ZW^* \rightarrow 2$  leptons + 2 v

$H \rightarrow ZZ^* \rightarrow 4$  leptons

Until now, particle accelerators have never reached the high energy levels of the LHC. This fact implies that every detector of the ATLAS apparatus must be built to give the better performances the actual technology allows, in order to investigate as better as possible eventual physics phenomena beyond the Standard Model.

For example, one of the new studies that will be performed at the LHC is the determination of the quark top mass with a resolution less than 0.05 GeV/c2. The most interesting decay to reach such purpose is:

$t t \rightarrow b b W (jj) W (lv)$

so the ATLAS apparatus will have to be able to detect leptons in the final state and reconstruct secondary decay vertexes. These characteristics will be also used to investigate the B<sup>0</sup> meson physics, e.g. the rare decay study:

$$B^{0}_{d} \rightarrow \mu^{+} \mu^{-} (X)$$

or the decay:

$$B^0_d \rightarrow J/\psi K^0_s$$

useful in CP violation studies.

In summary, LHC has been designed to investigate new physics in a energy range never reached before. In particular, the main goals of the LHC are:

- Searching for the Higgs boson;

- The investigation of the heavy quark physics (as the B and T quarks);

- Studying the CP violation;

- The study of an eventual composite quarks' structure;

- Searching for SUSY particles;

- The investigation of eventual new phenomena beyond the modern physics.

### 1.2 The LHC architecture

The LHC is a collider designed to accelerate two proton beams in opposite directions, in order to let them to collide with an energy of 14 TeV in the center-of-mass. The foreseen luminosity is  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. As said before, the

actual reached values for the energy and the luminosity are respectively 7 TeV and  $10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>.

The beams are a succession of proton bunches, each one containing 10<sup>11</sup> particles, spaced by 25 ns (corresponding to a frequency of 40 MHz) [3] [4].

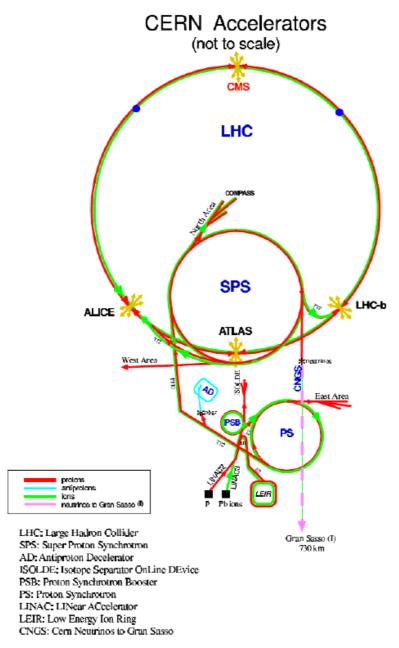

Figure 3 – Injection scheme for the LHC.

The luminosity of the LHC is defined as:

$$\mathcal{L} = f \frac{N^2}{4 \pi \sigma_x \sigma_y}$$

where N is the number of proton per bunch (10<sup>11</sup>), f is the collision frequency (40 MHz) and  $\sigma_x$  and  $\sigma_y$  characterize the Gaussian transverse profile in the horizontal and vertical directions.

The LHC has been built in the LEP tunnel where it is fed by particle sources and different pre-accelerators. The protons are produced and accelerated to 50 MeV by the proton Linac, before being injected into the Proton Synchrotron Booster (PSB), that accelerates them to 1.4 GeV. From the PSB, the protons reach the Proton Synchrotron (PS), that accelerates them as far as 26 GeV. Finally, the Super Proton Synchrotron (SPS) injects the proton beams into the LHC with an energy of 450 GeV. This last accelerates every beam up to 7 TeV. In Figure 3 you see the injection scheme just described for the Large Hadron Collider. In Table 2 are shown some foreseen parameters of the LHC for proton-proton operation [5].

| Parameter                                      | Value            |

|------------------------------------------------|------------------|

| Energy (TeV)                                   | 7.0              |

| Dipole field (T)                               | 8.4              |

| Coil aperture (mm)                             | 56               |

| Distance between apertures (mm)                | 180              |

| Luminosity (cm <sup>-2</sup> s <sup>-1</sup> ) | 10 <sup>34</sup> |

| Beam-beam parameter                            | 0.0032           |

| Injection energy (GeV)                         | 450              |

| Circulating current/beam (A)                   | 0.53             |

| Bunch spacing (ns)                             | 25               |

| Particles per bunch                            | 10 <sup>11</sup> |

| Stored beam energy (MJ)                        | 332              |

| Normalized transverse emittance (mm)           | 3.75             |

| R.m.s. bunch length (m)                        | 0.075            |

| Beta values at I.P. (m)                        | 0.5              |

| Full crossing angle (mrad)                     | 200              |

| Beam lifetime (h)                              | 22               |

| Luminosity lifetime (h)                        | 10               |

| Energy loss per turn (keV)                     | 6.9              |

| Critical photon energy (eV)                    | 45.6             |

| Total radiated power per beam (kW)             | 3.7              |

|                                                | 1                |

Table 2 – Parameters of the LHC for the proton-proton operation.

The two proton beams channels lie side by side, 194 mm apart, in order to let them use the same magnets' system. This arrangement enabled a cost saving of 30%, compared to a system with two separate magnets.

In order to accelerate the proton beams to the required energy and to bend them properly around the LEP tunnel, the magnetic fields need to be about 9 T. To reach such a high field, superconductive magnets are used. These lasts, in order to reach superconductive temperatures, are immersed in a pressurised bath of superfluid helium at about 0.13 MPa (1.3 bar) and a maximum temperature of 1.9 K [6].

### 1.3 The ATLAS detector

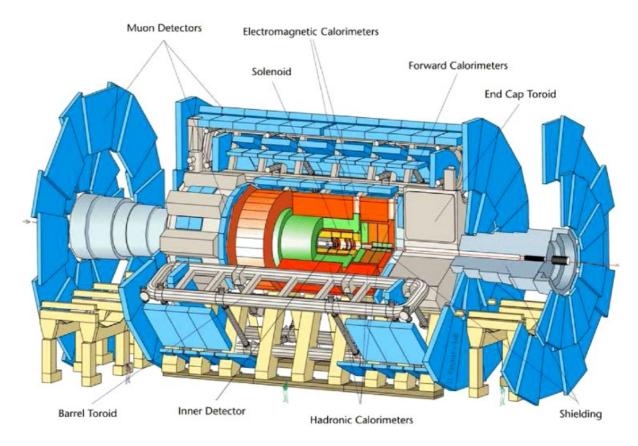

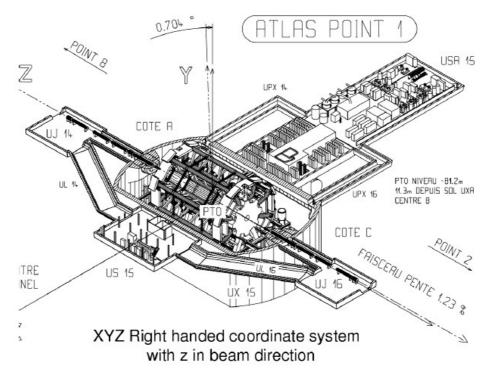

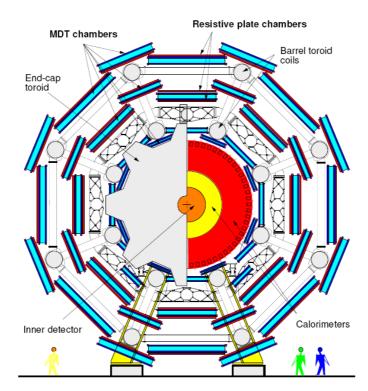

ATLAS is a detector built at one of the four LHC beam interaction point. It has a cylindrical symmetry along the beam axis and the cylinder has a 46 m length m and a 22 m diameter. Figure 4 shows the ATLAS architecture. Closest to the interaction point there is a tracking detector (called inner detector) and, from inner to outer radius, there are an electromagnetic calorimeter, an hadronic calorimeter and a muon spectrometer. All these sub-detectors are immersed in a magnetic field in order to bend the charged particle trajectories and measure their momentum.

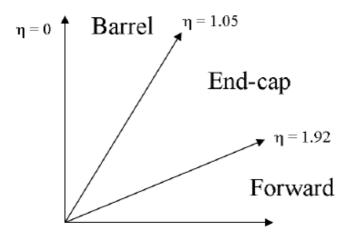

In Figure 5 the ATLAS coordinate system in shown. The system is right-handed with the z-axis along the beam direction and the x-axis pointing toward the center of the LHC circumference; the y-axis points from the interaction point upward. Because of the detector's symmetry, a cylindrical  $(z, \phi, \theta)$  coordinate system is used. The azimuthal angle  $\phi$  is referred to the x-axis, in the x-y plane; the polar angle  $\theta$  is referred to the z-axis, in the r-z plane. Instead of the polar angle  $\theta$ , the pseudorapidity variable is used. This last is defined as:

$$\eta \approx$$

- ln ( tan(  $\theta/2$  ) )

and allows to identify three regions in the detector, *Barrel*, *End-cap* and *Forward*, as show in Figure 6.

Figure 4 – The ATLAS detector architecture.

Figure 5 – The ATLAS coordinate system.

Figure 6 – The three detector's regions, defined by the pseudorapidity variable.

In order to give the highest performances, the ATLAS detector has been designed to satisfy the following requirements:

- A tracking system with a very high resolution, allowing the reconstruction of secondary decay vertexes of heavy quarks;

- A very good energy and direction resolution of the electromagnetic calorimeter, to identify correctly electrons and photons;

- A good hadronic calorimeter to achieve accurate energy measurements in order to perform jets identification and missing energy measurements;

- A muon spectrometer able to perform momentum measurements with a very high precision;

- Large acceptance in pseudorapidity and almost total coverage in azimuthal angle;

- High trigger efficiency for all interesting processes.

#### 1.3.1 The magnetic system

Magnetic fields are essential in the ATLAS detector, in order to bend the trajectories of charged particles. There are two different structures that generate such fields [7]:

- a superconducting solenoid, producing a 2 Tesla magnetic field for the inner detector;

- an external toroidal superconducting magnet, producing a variable magnetic field from 3 to 6 Tesla (depending from the pseudorapidity) for the muon spectrometer.

The external magnet is made of three toroids, one in the barrel region and two in the end-cap regions, and each one is made of eight independent coils, arranged with an octagonal symmetry. It has on open structure to minimize the contribution of multiple scattering to the momentum resolution; most of the coils is cooled by liquid Helium at 4.5 Kelvin.

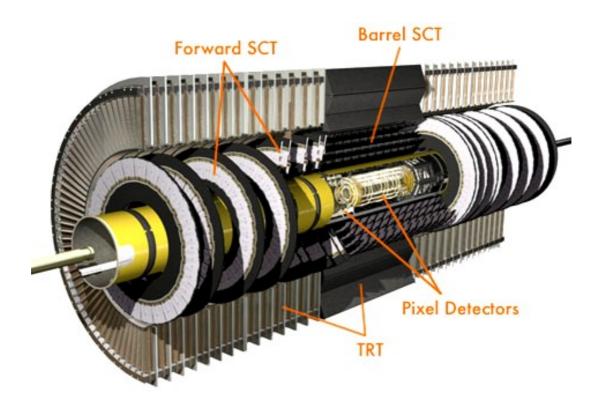

#### 1.3.2 The inner detector

The Inner detector (shown in Figure 7) is located around the beam's interaction zone and has a cylindrical symmetry, with a length of 7 m and an external diameter of 2.3 m. A superconducting solenoid surrounds entirely the inner detector and it generates a magnetic field of 2 Tesla parallel to the beam axis. This field wraps up entirely the detector.

The main task of the inner detector is to reconstruct particles' tracks and to perform measurements of momenta of charged particles in the apparatus. Moreover, the inner detector gives the position of primary and secondary vertexes of decays of some short-lifetime particles, such as B-Hadrons:

$$B^0_d \rightarrow J/\psi K^0_s$$

,

allowing to identify the produced K particles.

The core of the inner detector has a very high spatial resolution and it is made up of two concentric structures: one made by pixel detectors with fine granularity, in order to grant a high resolution; the other is made by SemiConductor Trackers (SCT), that contributes to measurements of vertex position and momenta. The outer region of the detector is made up of Transition Radiation Trackers (TRT), that are tube detectors arranged along the beam's axis in the barrel region and radially in the end-cap regions. These sub-detectors have electron identification capability, by employing Xenon gas to detect transition radiation photons. The resolutions of the three sub-detectors making the inner detector are reported in Table 3.

| Resolutions    | σ <sub>Rφ</sub> (μm) | σ <sub>z</sub> (μm) |

|----------------|----------------------|---------------------|

| Pixel detector | 12                   | 66                  |

| SCT            | 16                   | 580                 |

| TRT            | 170                  | -                   |

Table 3 – Spatial resolutions of the inner detector.

Figure 7 – Architecture of the inner detector.

#### 1.3.3 The calorimeters

The energy resolution of calorimeters improves with increasing energy, making them suitable for use at high energy colliders. Physics requirements on calorimeters on LHC include:

- Accurate measurements of energies and positions of both electrons and photons;

- Measurements of energies and directions of jets;

- Measurements of missing transverse energy of events;

- Particle identification, including separation of electrons, photons and hadronic τ decays from jets;

- Event selection already at the first level of trigger.

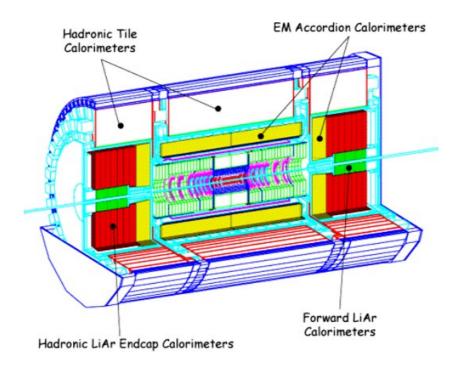

The system is divided into an electromagnetic (EM) calorimeter with high resolution close to the interaction point and a large hadronic calorimeter behind with a coarser resolution. The first of them uses Liquid Argon (LiAr) as active medium while in the hadronic calorimeter different technologies are used depending on the environmental constraints like radiation dose. The calorimetric system is shown in Figure 8.

**Figure 8 –** The ATLAS calorimetric system.

The electromagnetic calorimeter is required to reconstruct electron and photons in the energy range from 2 GeV to 5 TeV.

The principal channels for this calorimeter are:

$$H \rightarrow Z Z^* \rightarrow 4e$$

$H \rightarrow \gamma\gamma$

These channels place the most stringent requirements on the electromagnetic calorimeter in terms of energy resolution, energy range and particle identification.

The EM calorimeter is a lead-Liquid Argon (LiAr) detector [8]. The barrel of the electromagnetic calorimeter covers  $|\eta| < 1.475$  and the two identical end-caps cover  $1.375 < |\eta| < 3.2$ .

The Liquid Argon technology is radiation resistant and provides long-term stability of the detector response, excellent hermeticity, good energy resolutions and relatively easy detector calibration.

The ATLAS hadronic calorimeters cover the range of  $|\eta| < 4.9$  using different techniques best suited for the widely varying requirements and radiation environment over the large  $\eta$  range. The calorimeter provides good resolution for high energy jets. The large  $\eta$  coverage will also guarantee a good  $E_{Tmiss}$  measurement, which is important for many physics signatures and in particular for SUper SYmmetry (SUSY) particle searches.

The hadronic barrel calorimeter is a cylinder divided in three sections: a central barrel and two identical extended barrels. They are sampling calorimeters with iron as absorber material and scintillating tiles as active material, called Tile Calorimeter [9].

At larger pseudo-rapidities, where higher radiation resistance is needed, the intrinsically radiation-hard LiAr technology was chosen: the hadronic end-cap calorimeters (EHCal) and the forward calorimeter (FHCal) with the front face 4.7 m far from the interaction point.

#### 1.3.4 The Muon Spectrometer

One of the most important proof of interesting physics at the LHC is the creation of high-momentum muons during the interactions. The ATLAS muon spectrometer [10] has been designed to provide a high precision measurement of muon momentum and spatial position without the need of any other information from other detector data. Moreover, a homogeneous coverage up to large rapidity ( $|\eta| = 3$ ) and high efficiency for identifying muons is required in order to achieve the physics goals of the experiment.

The muon spectrometer requirements are:

- A momentum resolution lower than 10%, up to values of transverse momentum pT ~ 1 TeV/c.

- A spatial resolution of ~  $\mu$ m in the measurement of the particles' position in the direction and lower than 10 mm in the \_ direction.

- A good performance in reconstructing events whose final states are characterized by the presence of 2 or 4 muons, that are events that can be related to a Higgs boson decay.

- A trigger system selectivity up to pT > 20 GeV/c.

Figure 9 – A section of the ATLAS Muon Spectrometer.

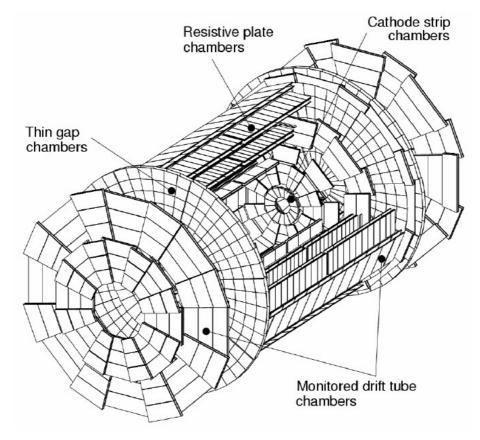

The muon spectrometer is built in the outer region of the ATLAS apparatus. It is a tracking system in a toroidal magnetic field and it is made up of precision chambers and trigger detectors. The spectrometer has a barrel shape. It is 46 m long and 22 m wide.

The spectrometer has an octant symmetry in the R- $\phi$  plane and it is subdivided in barrel and end-cap spectrometers. In Figure 9 you can see a section of the detector.

The operation principle is based on the magnetic deflection of muon tracks in the magnetic field generated by three large toroidal magnets (one for the barrel and two in the end-caps). The magnetic field lines in the spectrometer are parallel to the  $\varphi$  direction: hence, the component of the particles' momenta in the  $\varphi$  direction is parallel to the magnetic field lines. If we define a cylindrical coordinates system, particles' trajectories are arcs of circumference in the r-z plane. The radius and the direction of the curvature of the trajectory in the r-z plane are depending, given the magnetic field value, by the momentum and by the charge of the particle. By reconstructing the trajectory, the charge and the momentum of the particle can be calculated.

Figure 10 – Detectors compounding the Muon Spectrometer.

Four different kinds of gaseous detectors have been designed, both for precision measurements and for trigger chambers (Figure 10). In the barrel region, both precision chambers and trigger detectors are arranged in three cylindrical concentric surfaces, mounted at a distance of about 5 m, 7.5 m and 11 m from the beam axis, as shown in Figure 9; in the two end-cap regions the detectors are located on four vertical stations, at a distance of ~ 7 m, 10 m, 14 m and 22 m from the interaction point.

For position measurements, *Monitored Drift Tubes* (MDT) are used in the barrel region and *Cathode Strip Chambers* (CSC) are used in the region with high pseudorapidity ( $|\eta|$  up to 2.7). For trigger measurements, stations of *Resistive Plate Chambers* (RPC) are used in the region with  $|\eta| < 1.05$ , and *Thin Gap Chambers* (TGC), multiwire proportional chambers, are used in the end-cap regions.

#### Monitored Drift Tubes (MDT)

MDT detectors [11] are cylindrical drift tubes with a 30 mm diameter and with a 50  $\mu$ m W-Rn wire; the gas is a mixture of Ar(91%)-CH<sub>4</sub>(4%)-N<sub>2</sub>(5%). The drift time is lower than 480 ns and the average spatial resolution for a single tube is 80  $\mu$ m.

In order to enhance the spatial resolution, each MDT chamber is made of two tracking planes, each made by a superposition of 3 or 4 layers of drift tubes.

The geometry and the position of the detectors is granted by an optical system called RASNIK [12] with a precision better than 30  $\mu$ m. According to the azimuthal symmetry of the magnet, the spectrometer is divided in 16 sectors in the  $\phi$  projection and every sector is completely covered by a chamber. The drift tubes are installed perpendicularly to the beam axis: so the chambers can measure muons' position in the  $\eta$  projection, reconstucting the track in the r-z plane. There is a superposition of 200 mm between two chambers of adjacent sectors, to avoid dead regions in the apparatus due to the presence of reinforcement structures and cables.

#### Cathode Strip Chambers (CSC)

Cathode Strip Chambers [13] are proportional multiwire chambers with cathode strips readout, used to achieve a better spatial resolution: they have to

reconstruct tracks of particles with higher transverse momentum. A precision measure is obtained by evaluating the charge on the cathode (made by several strips), induced by the avalanche formed on the anode wire. The gas contained into the chamber is a mixture of Ar(30%)-CO<sub>2</sub>(50%)-CF<sub>4</sub>(20%), the wires are supplied by 2.6 kV and the gas gain is about  $10^4$ . The spatial resolution obtained is lower than 60 µm. As the MDT chambers, a CSC chamber is made of two planes, each made of four layers of detector.

CSC detectors are used at about ~ 7 m from the interaction point, in regions with high pseudorapidity, where a high flux of particles is expected. The main characteristic of the CSC detectors are a small drift time of the electrons (30 ns), a good timing resolution (7 ns) and a low sensitivity to the neutrons. Moreover, using strips orthogonal to the cathode strips, a measure of the second coordinate can be also performed.

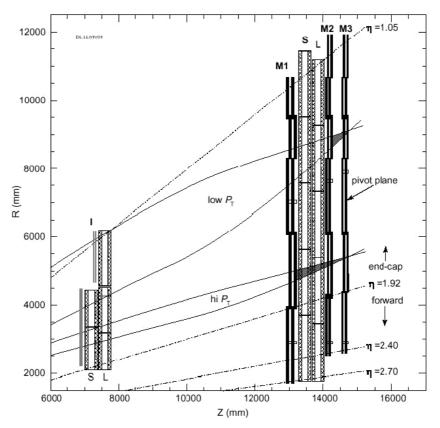

#### Thin Gap Chambers (TGC)

Thin Gap Chambers [14] [15] are used for trigger purposes in the end-cap regions because of their very good rate capability and their long ageing characteristics. TGC are, like CSC detectors, multiwire proportional chambers. The gas mixture is made of 55%  $CO_2$  and of 45% n-pentane (n-C<sub>5</sub>H<sub>12</sub>) and the chambers operate at an high voltage of about 3 kV. The small distance between wires and the electric field configuration ensure a short drift time and a good timing resolution of about 4 ns.

The anode wires, with a 50  $\mu$ m diameter, are arranged parallel to the MDT wires and produce the trigger signal; read-out strips are orthogonal to the wires and are used to measure the second coordinate. TGC chambers have both a trigger purpose, in the end-cap region, and a precision chambers purpose (for the measure of the second coordinate) in the forward region, in the inner and middle stations of the spectrometer.

In particular, in the end-cap region, the detectors are installed at a distance of bout 14 m from the interaction point and placed on three different planes to form a triplet (M1) and two doublets (M2 and M3) of chambers. In Figure 11 is shown the TGC disposition in the end-cap regions.

Figure 11 – Disposition of the Thin Gap Chambers in the end-cap region.

#### **Resistive Plate Chambers (RPC)**

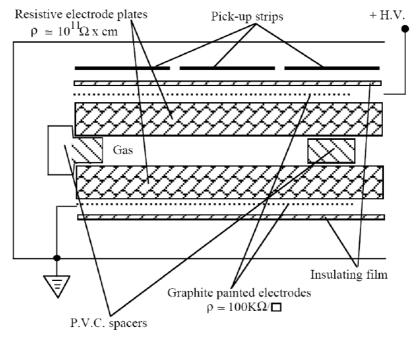

Resistive Plate Chambers (RPC) detectors [16] [17] [18] are installed in the barrel region of the apparatus, for trigger purposes. RPCs are detectors that guarantee good timing performances at a moderate cost. Their typical timing and spatial resolution are respectively 1 ns ed 1 cm with an intrinsic detection efficiency greater than 98%.

RPCs are ionization detectors whose working principle is based on the discharge inside the gas. Figure 12 shows the section of an RPC detector. Two Bakelite planes delimit a gas gap in which a uniform electric field is applied, whose intensity is about 4.5 kV/mm. The bakelite planes, also called resistive plates because of their high resistivity ( $\rho = 1010 \ \Omega \ cm$ ), are externally coated with two thin graphite layers, connected respectively to high voltage and to ground.

A thin layer (few hundred microns) of PET is glued on the graphite electrodes in order to insulate the high voltage electrodes from the read-out strips, oriented in the X and Y directions.

Figure 12 – Section of an RPC.

The graphite electrodes, because of their high resistance, are transparent to the electrical pulse created inside the gas gap, when a charged particle crosses the gap itself. For this reason, the signal can be read by induction on the readout metallic plates, made up of copper strips.

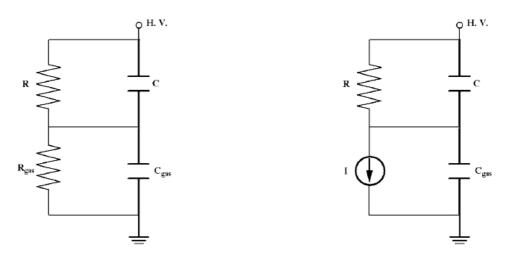

The RPC just described has the structure of a two dielectric planar capacitor. The working model of the chamber is shown in Figure 13. The capacitors C and  $C_{gas}$  and the resistors R and  $R_{gas}$  describe the capacitance and the resistance of the bakelite planes and of the gas gap, respectively.

(a) Before ionization

(b) After ionization

Figure 13 – Working scheme of an RPC detector.

In steady condition, when there is no ionization, the gas has infinite resistance ( $R_{gas} = \infty$ ). So the high voltage HV is entirely applied on the gas gap.

When there is an interaction with charged particles, there is the production of electrons by ionization and the gas gap behaves like an ideal current generator. This current generator discharges the "gas capacitor"  $C_{gas}$  and some of the HV is gradually transferred to the resistive plates, described by the C capacitance. The system goes back to the initial conditions following an exponential law with a time constant:

$$\tau = R (C + C_{gas}) = \rho \epsilon_0 (\epsilon_r + 2 d / g)$$

where  $\varepsilon_r$  is the dielectric relative constant of the bakelite, d is the thickness of the bakelite plates and g is the thickness of the gas gap. For  $\rho = 10^{10} \Omega$  cm, the previous relationship gives  $\tau = 10$  ms. This value has to be compared with the time of production of the discharge, that is only ~ 10 ns. In this time interval, the electrode plates behave like insulators and the voltage on the gas gap is too low to feed the discharge. This quenching mechanism is at the basis of the working principle of the detector.

A chamber with resistive electrode plates can be divided in a large number of small "discharge cells" [19], each one independent from the others. An estimation of the extension of the area where the discharge is located is given by the formula S = Q g /  $\varepsilon_0$  V, where Q is the charge delivered in the gas.

Therefore, the detector is "blind" only in a region of extension S, for a time  $\tau$ . By this, the total charge produced inside the detector, and so the intensity of the electric field, has a direct influence on the rate capability of an RPC. A small value of Q has two important effects: it allows to have small currents in the detector (a crucial point to prevent detector ageing) and to have a high detecting efficiency, also when there is a high flux of ionizing particles.

The current produced by the discharge in the gas induces a signal on the pick-up electrode. The pick-up electrodes can be shaped as strips or square pads. The strip has the advantage to behave as signal transmission line of well defined impedance, allowing the transmission at large distances with a small loss of amplitude and timing information. Two orthogonal sets of strips are used; the pitch of every strip is 2-3 cm. Two contiguous strips are separated by a

0.3 mm wire, connected to ground to reduce the capacitive coupling of two adjacent strips.

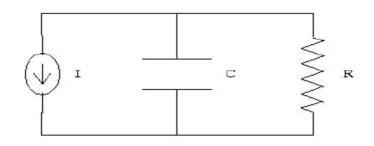

The equivalent circuit of the read-out electrode (shown in Figure 14) can be described as a current generator, charging a capacitor C in parallel to a resistor R, where C is the electrode's capacitance and R is the resistance between the electrode and the ground.

Typical values for C and R are: C ~ 1 pF and R ~ 25  $\Omega$ ; the time constant of the circuit results to be  $\tau$ ' = 25 ps, much smaller than the rising time of the signal. So the read-out signal is not integrated, but the current circulating in the read-out electrode is every instant proportional to the current produced by the discharge inside the gas.

Figure 14 – Equivalent circuit of the read-out electrode of an RPC strip.

#### 1.3.5 The trigger and the Data acquisition (DAQ) systems

Because of the enormous expected background, the design of an extremely selective trigger is needed. The interesting physics processes must be selected and accepted with high efficiency. For example, at the nominal luminosity of LHC, searching for a Higgs boson with a mass of ~ 80 - 100 GeV, one interesting event is expected every  $10^{13}$  produced.

This is achieved by defining three different trigger levels (LVL1 [20], LVL2 and LVL3 [21], also called Event Filter). The first level receives data only from the detector, whilst each of the two following levels elaborates data from the detector and also the information collected at the previous level.

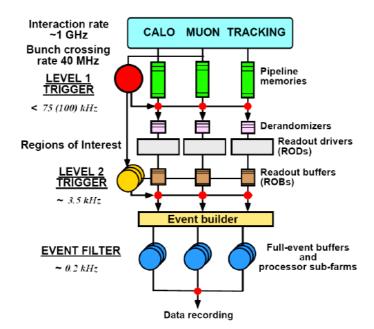

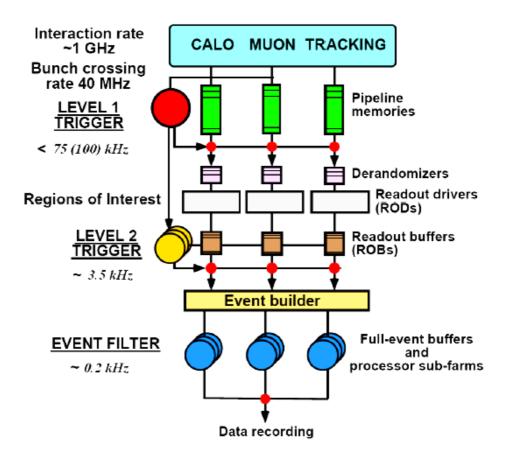

The architecture of the trigger system [22] and the three levels of the trigger are shown in Figure 15.

Figure 15 – The three levels of the trigger system.

The first level trigger must identify, without ambiguity, the bunch crossing of the interesting event, using only data coming from the calorimeters and from the spectrometer, and uses synchronous parallel processors working at the bunch crossing frequency 40 MHz. Programmable logic devices (FPGA e CPLD) and ASIC (Application Specific Integrated Circuit ) are massively used.

Data produced by the detector are elaborated by the level-1 trigger, with a latency lower than 2.5  $\mu$ s; during this time, information are stored in FIFO memories (First-In First-Out). The output frequency of data is 75 KHz, increasable up to 100 Khz.

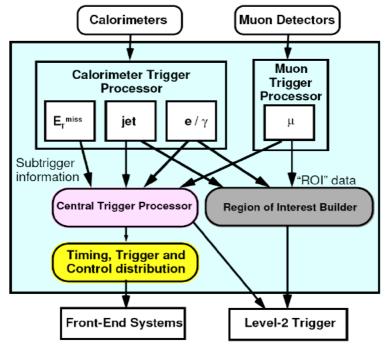

In particular, the level-1 trigger structure (Figure 16), is composed by four subsystems:

- the Muon Trigger Processor receives data from TGC and RPC, respectively from the end-cap and the barrel regions; it detects events that have in the final states muons with a transverse momentum greater than a programmable threshold and identifies the spatial region the muon comes from;

- the Calorimeter Trigger Processor identifies electrons, photons, hadrons and jets, and measures the possible missing energy;

- the Central Trigger Processor collects and elaborates information from the trigger processors;

22

the TTC distribution system (Timing, Trigger and Control) generates and distributes the control signals to the whole apparatus.

Figure 16 – The level-1 trigger.

When an event is accepted by the LVL1, a level-1 trigger signal is generated by the trigger processor: in this case, data stored in the L1FIFO buffer are transferred to the next elaboration levels. Data are read out from the front-end electronics systems of the detectors into Read Out Drivers (RODs) and then forwarded to Read Out Buffers (ROBs). Figure 17 shows the path of data from the detector to the elaborators, for the RPC detectors.

Figure 17 – The path of data from the detector to the elaborators.

All the existing electronics present in the trigger and DAQ data path from the on-detector ones up to the Read Out Drivers are developed specifically for the detector on which they are installed. The other electronics of the DAQ environment are the same for all the detectors. For example, the Read Out Drivers of the Muon Spectrometer can't be switched with the ones developed for the Calorimetric system, while the Read Out Buffers can.

The trigger system is divided into Regions of Interest (*ROI*), with a granularity ~  $\Delta\eta \times \Delta\phi$ = 0.1 x 0.1. For example, in the barrel region, the trigger system is divided into 1664 ROI. The level-1 trigger generates and transmits to the level-2 trigger processors the coordinates of the ROIs where an interesting event occurred. In this way, the level-2 trigger accesses only to that ROIs, reducing the amount of data to be elaborated. At this stage, full granularity and full precision data from most of the sub-detectors are available and are used by the LVL2 to select interesting physics events. Moreover, even if it is possible to access all the data of the event, only the information needed to decide whether accept or reject that event are acquired.

Data for the bunch crossing selected by the LVL1 trigger are stored in the ROBs during the LVL2 trigger latency (expected in the range of 1-10 ms). Then, if data are related to an interesting event, the LVL2 trigger promotes them to the following trigger level (otherwise data are deleted). The data elaboration, formatting and storing operations are called *event building*.

Whilst the level-1 trigger is based on an hardware designed for the specific application, both level-2 and Event Filter use commercial processors; moreover, the structures of computing and communication are quite similar. The differences between the level-2 and Event Filter are that level-2 trigger needs simple and fast algorithms, and the Event Filter uses elaboration algorithms similar to the ones used for the off-line analysis.

The level-2 trigger system is made of a sub-farm of commercial processors and the expected trigger frequency is ~ 3.5 KHz. An event accepted by the level-2 trigger is built by the Event Filter. The Event Filter uses offline algorithms, based on up to date calibration and alignment information, such as the magnetic field map. Most of the rejection power of the Event Filter comes from the use of complex algorithms and criteria that cannot be performed by the LVL2 trigger, because of processing time limits. The Event Filter sends data to the mass memories with a bandwidth of ~ 10 - 200 Mbyte/s; a single event size should be ~ 1 Mbyte, so the output frequency of the Event Filter should be of ~ 200 Hz.

# CHAPTER TWO – THE LEVEL 1 TRIGGER AND THE DATA ACQUISITION SYSTEM OF THE ATLAS MUON SPECTROMETER

This chapter describes the architectures of the first level trigger and of the Data Acquisition system (DAQ) of the ATLAS muon spectrometer.

The signals generated by the RPCs of the spectrometer when muons are detected undergo several elaborations before being sent via optical fibres to the counting room USA15. The algorithms of the coincidence matrix, for the generation of the trigger, and the structures of the other acquisition boards are described.

In this chapter, the transmission system on optical fibre will be presented. The receivers of such system produce data input to the Read Out Driver (ROD), a VME board whose main tasks are to receive and process trigger and data signals, to format them into frames in order to send them to the next electronics.

The ROD will be deeply described in the next chapter.

## 2.1 Overview of the Level 1 trigger system

The ATLAS trigger and data-acquisition system is based on three levels of online event selection. Each trigger level refines the decisions made at the previous level and, where necessary, applies additional selection criteria. Starting from an initial bunch-crossing rate of 40 MHz, the rate of selected events must be reduced to ~100 Hz for permanent storage. While this requires an overall rejection factor of 10<sup>7</sup> against 'minimum-bias' processes, excellent

efficiency must be retained for the rare new physics, such as Higgs boson decays, that is sought in ATLAS [23].

High transverse-momentum muons are identified using only Resistive Plate Chambers (RPCs) in the barrel and Thin Gap Chambers (TGCs) in the endcaps.

An essential requirement on the LVL1 trigger is that it should uniquely identify the bunch crossing of interest. Given the short (25 ns) bunch crossing interval, this is a non-trivial consideration. In the case of the muon trigger, the physical size of the muon spectrometer implies times-of-flight comparable to the bunch crossing period. In order to select about 75000 events per second from the 10<sup>9</sup> expected, the ATLAS level one trigger system has to be extremely selective and efficient. The requirements are:

- reconstruction of the track and discrimination of the event within the highest allowed LVL1 trigger latency of the experiment (2.5 µs);

- identification of the bunch-crossing of interesting events;

- identification of the Region Of Interest (ROI) of interesting events;

- high acceptance in pseudo-rapidity (  $|\eta| < 2.4$  ).

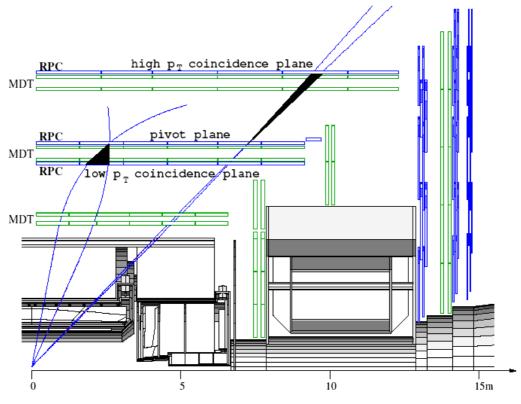

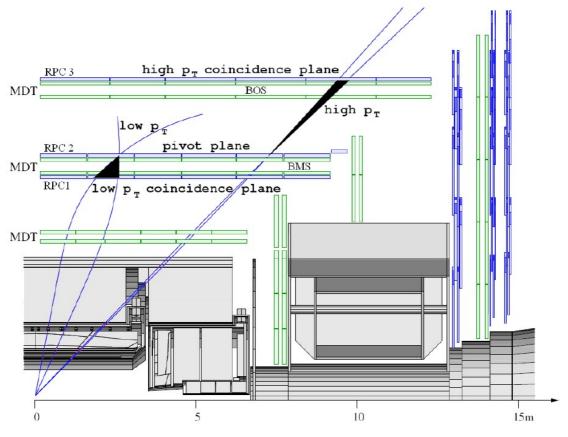

For the physics researches at the LHC, two kinds of interesting events should be taken into account in the design of the trigger system of the spectrometer: the production of muons with transverse momentum  $p_T$  greater than 6 GeV/c in low luminosity regime, that will be indicated as *low*  $p_T$  events; the production of muons with values of transverse momentum  $p_T$  greater than 20 GeV/c, in high luminosity regime, that will be labelled as *high*  $p_T$  events. The spectrometer's RPCs are designed for identifying both low and high  $p_T$  events. In the Figure 18 a section of the barrel spectrometer is shown. In such figure, both the high  $p_T$ and the low  $p_T$  coincidence RPC planes are schematized. The first one is made up of a single layer of RPCs sub-detectors, while to reveal low pT muons two close RPCs layers are needed. The trigger algorithm will be described in section 2.3.

Figure 18 – Section of the barrel muon spectrometer.

Figure 19 – The three levels of the trigger and the DAQ system.

## 2.2 The trigger and DAQ system architecture

In Figure 19 you can see the block diagram of the trigger and the Data Acquisition (DAQ) system architecture. Data produced by the detector are elaborated by the level-1 trigger, with a latency lower than 2.5  $\mu$ s. During this time, information are stored in pipelines memories. The output frequency of data goes from 75 KHz up to 100 Khz.

In particular, the level-1 trigger structure is composed by four subsystems:

- the Muon Trigger Processor receives data from TGC and RPC; it detects events that have in the final states muons with high p<sub>T</sub>.

- the Calorimeter Trigger Processor identifies electrons, photons, hadrons and jets, and measures the missing energy.

- the Central Trigger Processor collects and elaborates information from the trigger processors.

- the *Timing Trigger Control* (TTC) system generates and distributes the control signals to the whole apparatus.

When an event is accepted by the LVL1, the trigger processor generates a LVL1 accept signal: in this case, data stored in the L1FIFO buffer are transferred to the next elaboration levels. Data are read out from the front-end electronics of the detectors and sent to Read Out Drivers (RODs). Then they are forwarded to Read Out Buffers (ROBs).

In order to reduce the amount of data to be elaborated by the LVL2 trigger processors, the trigger system is divided into ROIs (Region of Interest), small detector areas with a granularity of  $\Delta \phi \Delta \eta = 0.1 \times 0.1$ . The level-1 trigger generates and transmits to the second level only the coordinates of the ROIs where an interesting event occurred. This strategy allows to transmit only the information needed to decide whether accept or reject the occurred event.

Data for the bunch crossing selected by the LVL1 trigger are stored in the ROBs during the LVL2 trigger latency. Then the LVL2 trigger promotes such data (if considered interesting) to the following trigger level, called *Event Filter*.

The level-2 trigger frequency is ~ 3.5 KHz. An event accepted by the level-2 trigger is built by the *Event Filter*. The *Event Filter* uses offline algorithms, based

on calibration and alignment information, such as the magnetic field map. After its work, the Event Filter sends data to the mass memories with a rate between 10 and 200 Mbyte/s. As a single event size is around 1 Mbyte, the output frequency of the Event Filter is ~ 200 Hz.

# 2.3 The LVL1 trigger algorithm for muon detection

The aim of the trigger system of the muons spectrometer of the ATLAS apparatus is the detection of particles coming from the interaction vertex having a transverse momentum greater than a certain programmable threshold.

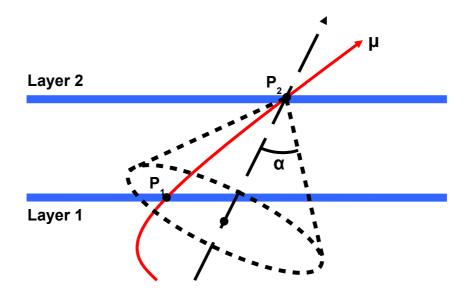

The muon trajectories are deflected into the apparatus by the toroidal magnetic field. The curvature will depend firstly by the momentum of the particle. In Figure 20 it's shown the functioning principle of the trigger system.

Let's suppose that our will is to detect a muon using two different stations of the spectrometer, called Layer 1 and 2.

$P_1$  and  $P_2$  are the impact points respectively in the first and in the second Layer. Let the dotted line crossing  $P_2$  and the interaction vertex be the axis of a cone with the vertex in  $P_2$  (such axis could be seen as the trajectory of a particle in the limit  $p = \infty$ ).

Figure 20 – Schematization of the trigger system functioning principle.

All the particles detected by the first station inside the cone volume have a momentum greater than a certain threshold  $p_t$ , related to the cone opening angle  $\alpha$ . The greater is the threshold, the lower is the angle. In the spectrometer, the position of the particle in the station is given by the position of the read-out electrodes on which the signal is induced by the muon.

The trigger algorithm is based upon the signals of the two layers, taken with opportune timing coincidences: for example if the hit on the layer 2 is detected *before* the one on the layer 1, the trigger doesn't give the accept signal, because the only allowed muon trajectories go from the interaction point toward the extern of the spectrometer.

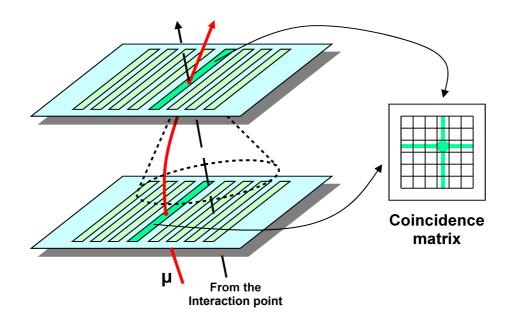

The coincidence conditions are written into a programmable memory that acts as a matrix whose raw and column indexes represent the positions of the strips on the detectors (Figure 21). The matrix, programmed according to the chosen trigger condition, indicates the validity (or not) of the coincidence between the signals corresponding to the matrix elements.

Figure 21 – The muon trajectories are reconstructed with a coincidence matrix between the detectors read-out strips' positions.

## 2.4 The segmentation of the muon spectrometer

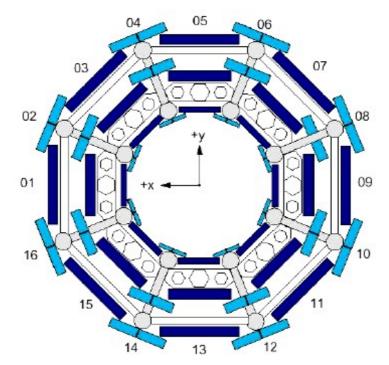

The barrel muon spectrometer has been physically segmented in 16 different sectors, as shown in Figure 22. The chamber towers labelled with even numbers are built "around" the coils of the octagon-shaped magnetic system. These sectors are called *Small Sectors*, while the ones labelled with odd numbers are called *Large Sectors*.

The trigger and data acquisition system is segmented into 64 logic sectors: each of the 16 physical sectors (*Large* or S*mall*) of the spectrometer is divided in two, and a further division is done for  $\eta > 0$  and for  $\eta < 0$ .

Figure 22 – The spectrometer segmentation in the barrel region.

# 2.5 The Resistive Plate Chambers

The RPC detectors are assembled in three different stations in each of the 16 sectors of the spectrometer, as you can see in Figure 23. The RPC1 and RPC2 stations are installed on the top and the bottom of the middle MDT precision chamber, labelled as BMS (Barrel Middle Small); the RPC3 station is at a greater distance from the beam axis, upon the MDT BOS (Barrel Outer Small) chamber.

Figure 23 – Section of the muon spectrometer.

A *low*  $p_T$  event ( $p_T$  < 6 GeV/c) is detected if a signal is seen in the RPC1 station and one is detected in the RPC2 station, in the programmed trigger window. An *high*  $p_T$  event is detected if a *low*  $p_T$  coincidence is found and also a signal in the RPC3 station is detected. Both for *high*  $p_T$  and *low*  $p_T$  events, the time coincidence between signals must to be in a 20 ns interval.

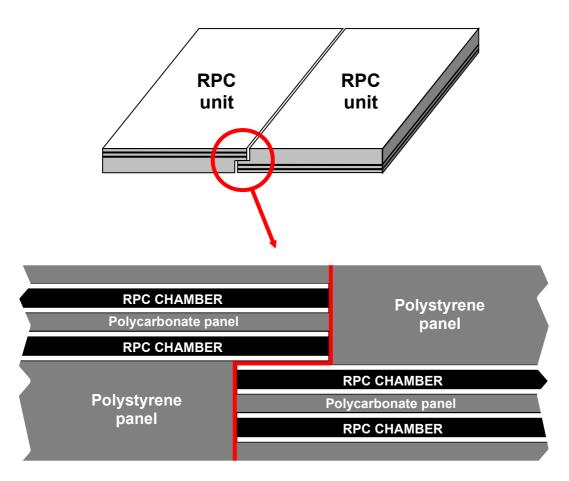

Each RPC detector is made of two *RPC units* glued together. The junction point is shown in the upper side of Figure 24. The longest dimensions of the various units are limited by the propagation delay of the signals on the read-out strips of the chambers. In order to allow the correct identification of the bunch-crossing of the event, this delay must be lower than 11 ns.

Each RPC unit is made of two *RPC chamber* separated by insulating polycarbonate spacers. This structure is glued to a thick polystyrene panel that supports it (Figure 24).

Each RPC chamber is realized with two bakelite planes containing a gas mixture (95%  $C_2H_2F_4$ , 4%  $C_4H_{10}$ , 1%  $SF_6$ ). The RPC is read-out by parallel electrode strips, glued to the surface of the bakelite plane.

Figure 24 – RPC detector panel, made up of two units.

The RPC chambers are installed upon the RPC unit so that their read-out strips are mutually orthogonal. The strips oriented in the azimuthal direction, parallel to the magnetic field lines, measure the coordinates in the  $\eta$  projection, in the r-z plane. Such strips will be indicated as  $\eta$  strips. The strips oriented in the longitudinal direction, and so parallel to the beam axis, measure the azimuthal coordinates in the  $\phi$  projection, in the x-y plane. Such strips will be indicated as  $\phi$  strips.

The RPC detectors just described allow to locate the muon hit point with a resolution of  $\sim$  10 mm.

# 2.6 The synchronization of the apparatus

In the beams of the LHC collider [24], protons are grouped in "bunches" of 10<sup>11</sup> particles that interact every 25 ns. Such interaction is called *bunch crossing*. As said before, the ATLAS detector is made up of several sub

detectors. In order to correctly reconstruct and correlate data generated by all these sources, a very precise synchronization system have been developed. The entire ATLAS apparatus is a system working at the *bunch crossing* frequency of the LHC (40 MHz).

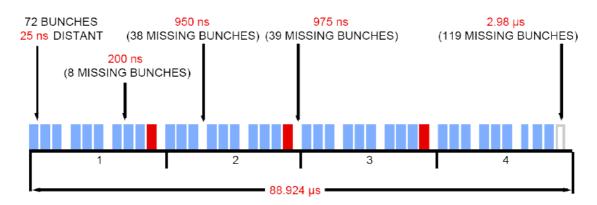

The DAQ and trigger systems are driven by a common clock signal, synchronous to the *bunch crossing* frequency of the collider. A periodic signal, called *orbit*, is associated to the revolution of the proton bunches in the LHC (Figure 25). This signal, generated by the control system of the LHC collider, has a period of 88924 ns and is made of 3564 elements (called *trains*), which are bursts of 72 bunches. Some "holes" (called *missing trains*), due to PS injector dead time, are visible inside the orbit. Such holes of different amplitude are crucial in order to establish the correct synchronization between the LHC orbit and the experiments' data acquisition systems.

Figure 25 – The bunches' distribution in the LHC orbit signal.

In order to achieve the synchronization between the elaboration systems and the machine clock it has been built a transmission system, able to distribute the clock signal and all the other control signals to all the elements of the ATLAS apparatus. Because of the large dimensions of the detector, the reference clock signal must be transmitted over distances up to hundreds meters, in order to reach all the parts of the apparatus. This is one of the problems that have been faced to make the entire apparatus working at 40 MHz. The clock phase is controlled at a sub-nanosecond level, to avoid phase discrepancy between all the sub-systems of the ATLAS apparatus. So there is the essential need to use a system that allows a resynchronization procedure and that guarantees a clock recovery in the event of a loss of synchronization.

### 2.6.1 The Timing, Trigger and Control system

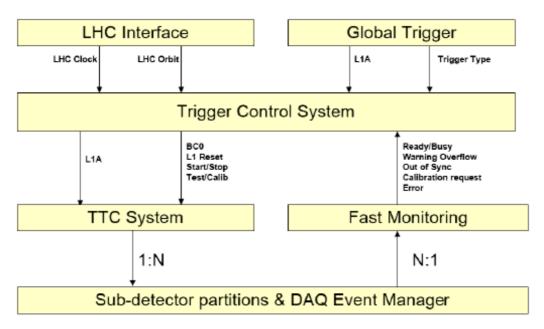

In Figure 26 it is shown the control architecture [25] designed for the LHC collider, in particular the Trigger Control System (TCS) and the system Timing, Trigger and Control (TTC). The Trigger Control System generates the timing and trigger signals. It receives from the LHC machine the clock and the orbit signals and receives from the Central Trigger Processor (CTP) of the ATLAS experiment the signal of validation of the Level 1 trigger (L1A, that means Level 1 Accept).

The TCS also manages the Reset signals, used to recovery the synchronization in case of a loss of information, and some service signals. A further task of the TCS is the control and the management of the calibration, synchronization and test signals for the apparatus subsystems.

Figure 26 – The control architecture of the LHC.

The Trigger Timing and Control [26] system is responsible of the distribution of the timing and trigger signals to the entire detector and to the different entities of data elaboration. Moreover, in order to make a correct identification of interesting events, the on-detector electronics associate to data in each event a unique progressive number (Event Identifier, or EVID) and a number identifying the bunch crossing that generated the collision (Bunch Crossing Identifier, or BCID). Such signals, together with the 40 MHz clock signal, the orbit signal, the L1A and other service signals, are sent from the TCS to the TTC. All these signals are coded and optically transmitted to the elaboration systems and toward different destinations in the ATLAS apparatus (Figure 27). Signals are reconstructed at the destination and are adapted to the protocols of every sub-detector.

The TTC incorporates facilities to compensate for particle flight times and detector electronics propagation delays. In addition it provides simultaneous transmission of synchronized broadcast commands and individually-addressed controls and parameters, such as channel masks and calibration data.

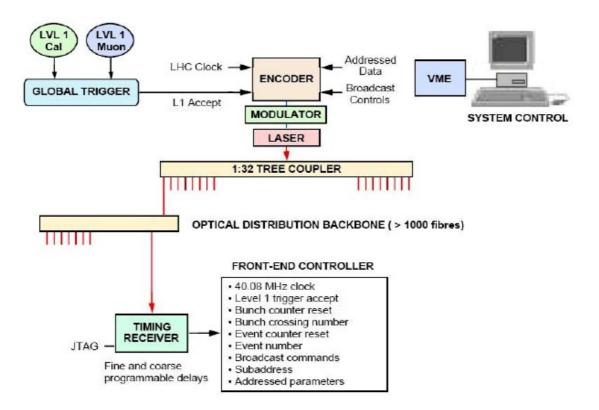

Figure 27 – The TTC system.

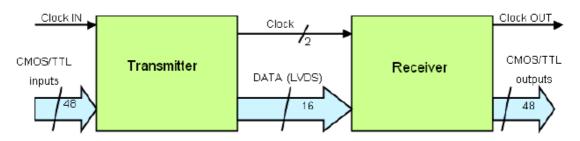

At each destination, a special timing receiver (TTCrx) delivers all the signals required by the electronics controllers.

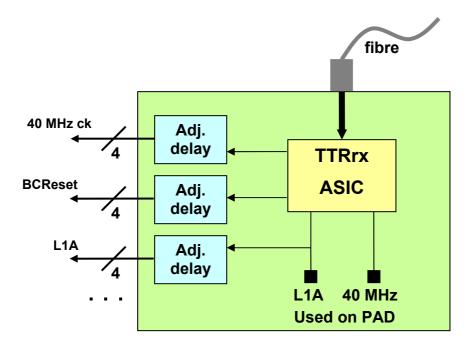

The distribution to the different units of the apparatus is made by the TTCrq board (that hosts the TTCrx ASIC), shown in Figure 28, that reconstructs the signals Clock, L1A, Event Counter Reset and Bunch Counter Reset and makes them available on four different channels, so they can be used by the different elaboration structures.

Figure 28 – The TTCrq board.

Starting from the TTCrx signals, the data acquisition boards (on-detector electronics) can generate the Event Identifier and the Bunch Counter Identifier. The EVID, incremented every time that a L1A signal occurs, is coded by 24 bit and is counted starting from the last EVID Reset. The BCID, incremented at every bunch of the orbit, is coded by 12 bit and is counted starting from the last BCID Reset.

## 2.7 The RPC trigger and DAQ electronics

The electronics of the RPC detectors are made of Amplifier Shaper Discriminator (ASD) boards, of Coincidence Matrixes (CM) and of PAD boards. The signals induced by muons on the RPC electrode strips are received by the ASD boards that amplify, discriminate by using a programmable threshold and shape them in width. Each ASD board houses eight acquisition channels (so eight RPC electrode strips).

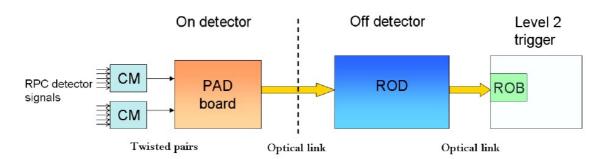

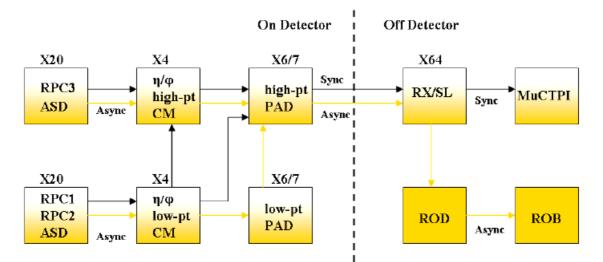

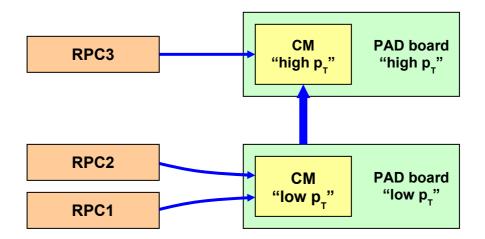

The Coincidence Matrixes use the information produced by the ASD boards to execute the two trigger algorithms (*low*  $p_T$  and *high*  $p_T$ ). Data produced by the CMs are elaborated by the PAD boards, that manage also the transmission to the processors of the next trigger and DAQ levels: a simplified path of the readout data and of trigger information is depicted in Figure 29.

Figure 29 – Scheme of the on-detector and the off-detector electronics.

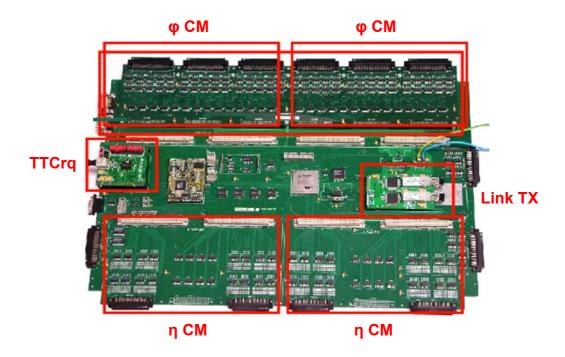

## 2.7.1 The Coincidence matrix

The ASD boards, installed on the RPCs, are connected to the Coincidence Matrixes [27]. These lasts are distant few meters and are hosted by the PAD logic boards. Every PAD board hosts four CMs, relative to a region of granularity  $\Delta \eta \times \Delta \phi \approx 0.2 \times 0.2$ . It also hosts the modular board TTCrq and the modular board Link Tx, that transmits on optical fibre trigger and readout data to the next DAQ levels. In Figure 30 a picture of a PAD board is shown.

Figure 30 – A PAD board.

As said before, each RPC detector is made up of two RPC chambers glued together, so a "low  $p_T$ " event is detected resolving the coincidences defined between the signals of the four RPC chambers of the two inner detector planes. The coincidence is verified in a programmable matrix, depending on the fixed transverse momentum threshold. Every CM board allows to program up to three different trigger conditions. The coincidence can be also programmed with a majority 2/4, 3/4 or 4/4 check between the four detector planes.

As example, with a 3/4 majority, the trigger condition is valid only if at least 3 up to 4 signals received from the two trigger stations are detected, within the trigger window and in a timing coincidence of 20 ns. This majority algorithm partly allows reducing the background noise of the apparatus.

To analyze the "high  $p_T$ " events, information from "low  $p_T$ " CMs and from the two detector planes of the RPC3 station are transferred to the corresponding "high  $p_T$ " CMs, installed on the RPC3 chambers. The coincidence algorithm is the same as before: as for a "low  $p_T$ " event, the matrix searches a time coincidence between the signals, within a time interval of 20 ns, with a 2/4, 3/4, 4/4 majority check and in spatial programmable windows (called *roads*) depending on the threshold of the imposed transverse momentum.

Trigger data are elaborated inside the CM board and formatted into a frame. The *header* contains the code that identifies the board (CM) and two identifiers, FEL1ID and FEBCID, produced by the two counters of EVID and of BCID on the board. The data frame is then transmitted to the trigger processors. Read Out data are stored in FIFO (First In First Out) memories and wait to be transmitted (or not) to the next DAQ levels, depending on the decision of the level 1 trigger.

### 2.7.2 The PAD board

The information of two adjacent "low  $p_T$ " CMs in  $\eta$  direction and the corresponding information of the two CMs in  $\varphi$  direction are elaborated by the "low  $p_T$ " PAD Logic board. For the "high  $p_T$ " trigger algorithm, data arriving to the "high  $p_T$ " PAD logic board come from both the CM "low" and from the CM "high" (Figure 31). The PAD Logic "low  $p_T$ " board and the four CM "low  $p_T$ " are installed

on the RPC2 station, while the PAD Logic "high  $p_T$ " board and the four CM "high  $p_T$ " are installed on the RPC3 station.

**Figure 31 –** Data path for the "high  $p_T$ " events.

One PAD Logic board covers a granularity region of  $\Delta \eta \times \Delta \phi \approx 0.2 \times 0.2$ , whereas the dimension of a Region Of Interest is  $\Delta \eta \times \Delta \phi \approx 0.1 \times 0.1$ : so each PAD Logic contains information on 4 ROIs. A *Small* sector of the spectrometer is managed by 7 PADs, while a *Large* one is managed by 6 PADs.

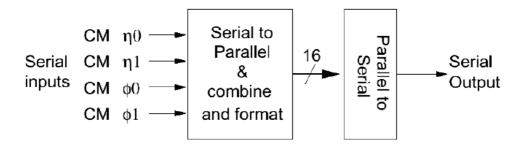

The main task of the PAD board is to perform a further elaboration of read-out and trigger data produced by the CMs. These data are combined and two different frames with different information (for read out and for trigger) are produced and sent via optical fibre to the counting room *USA15*. The other tasks of a PAD board are: the identification of the Region Of Interest for the event validated by the trigger system that combines information both in  $\eta$  and in  $\phi$  direction; the transmission of trigger information, of the BCID and of other signals. Furthermore, using a TTCrq modular board, each PAD receives the trigger signals from the TTC and distributes them to the four coincidence matrixes and to the PAD logic. In Figure 32 a data flow diagram of the PAD board is shown.

Figure 32 – The PAD board data flow diagram.

### 2.7.3 The data path architecture

Read-out data and Trigger data from a PAD are transmitted via optical fibre to a RX/SectorLogic (RX/SL) board. The trigger data path must be rigorously synchronous, at the 40 MHz of the LHC machine, but the read out data path is asynchronous, because interesting data (and so the L1A signal that validates them) are not produced in the detector at every bunch crossing. The RX/SL board is therefore made up of two main parts, one asynchronous (the read-out section, named RX) and one synchronous (the trigger section, named SL) with the machine clock. The first one is dedicated to the reception, the elaboration and the transmission of read-out data to the Read Out Driver (ROD) board, while the second one is responsible of the reception of trigger data and of the transmission of them to the Muon Trigger Central Processor Interface (µTCPI).

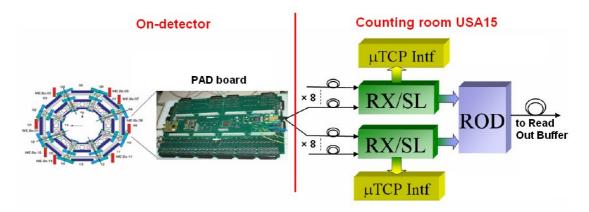

The ROD is a VME electronic board and it is responsible of the management and the elaboration of the read-out data coming from the PAD boards of a whole sector (*Large* or *Small*) and of the transmission of data to the next TDAQ levels (Figure 33).

The ROD crate is located in the counting room USA15, at about 80 meters from the beam interaction point. Such crate hosts two independent structures, each one made up of two RXSector Logic boards (slaves) and one ROD board (master). Every crate is controlled by a VME central unit CPU. Every ROD is connected, through a custom bus (RODbus), both to the trigger section (SL) and to the read-out section (RX) of every RX/SL board. The trigger section (SL) of the RX/SL board receives trigger data over optical fibre from the PAD boards, transmits its data to the interface to the trigger processor  $\mu$ TCPI (muon Trigger Central Processing Interface) and transfers diagnostic information to the ROD.

Figure 33 – Data path from the PAD to the ROD.

The read-out section (RX) receives read-out data over optical fibre from up to eight PAD boards and, after elaboration, transmits them to the ROD.

The task of the ROD board is to parse the received data frames, to check their coherence and to build a data structure for all the RPCs of one of the 32 sectors of the spectrometer. Each ROD sends the event fragments to the next DAQ levels for further event building and analysis. The ROD hardware environment and its architecture will be deeply described in the next chapter.

As just said, every ROD manages the information coming from one of the 32 sectors into which the spectrometer is divided (16 towers, each one divided in two sectors, for  $\eta > 0$  and  $\eta < 0$ ). To each one of these sectors correspond two logic sectors into which the trigger system is divided (so 64 trigger logic sectors, in total). These lasts are managed by 7 PADs, if it is a *Small* sector, or by 6 PADs, if it is a *Large* sector. Each RX/SL manages the data produced by one of the 64 trigger logic sectors of the spectrometer, receiving information from 6 or 7 PADs. The number of the PAD boards connected to a ROD, through the RX/SL boards, will therefore be given by 6 × 2 = 12 (for a *Large* sector) or by 7 × 2 = 14 (for a *Small* sector). A total of 32 structures, similar to the one shown in the right side of Figure 33, are needed to manage the flux of trigger and read out data of the whole spectrometer.

The ROD will be described in detail in the next chapter.

# CHAPTER THREE – THE READ OUT DRIVER OF THE ATLAS MUON SPECTROMETER RPCs

The ROD is part of the DAQ system of the ATLAS muon spectrometer. in this chapter I describe the hardware environment and the architecture of the board, together with the block diagram of the Event Builder, responsible of the event building process. The different devices present on the board are presented too.

# 3.1 The ROD board in the DAQ system

The Read Out Driver [28] is a VME board located in one of the off-detector data acquisition subsystem shown in Figure 34. These structures are installed in the USA15 counting room, at about 80 meters from the beam interaction point. In this structure the ROD manages readout data of one of the 32 half-sectors into which the spectrometer is divided (considering the  $\eta > 0$  and  $\eta < 0$  regions).

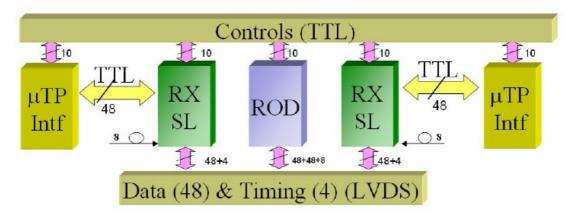

Each sector managed by the ROD corresponds to two of the 64 logic sectors into which the trigger system is divided. Each ROD is linked, via a custom bus (RODbus), with two RX-SL boards, that have the task to receive and elaborate trigger and read-out data from the on-detector electronics.

The RODbus is a bus that allows the boards to exchange data, control and timing signals.

Figure 34 – The Read Out Driver in the DAQ system.

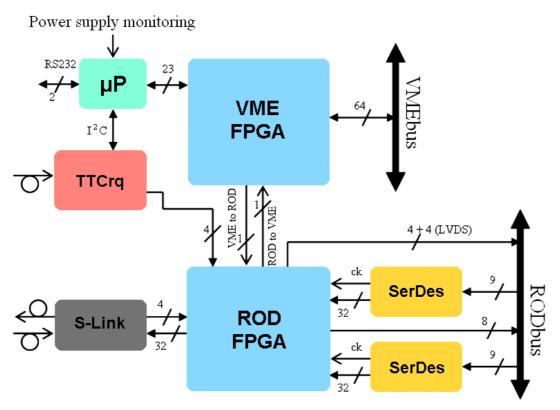

In particular, data and timing signals are transmitted in LVDS standard in order to have high frequency, low skew and low jitter, while control signals (as busy, reset, offline), run at lower rate and are transmitted in TTL standard. In the next paragraphs a detailed description of the RODbus will be given.

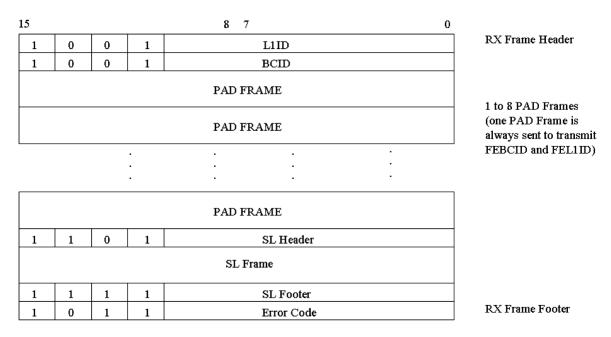

### 3.1.1 The RX section of the RX/Sector Logic board

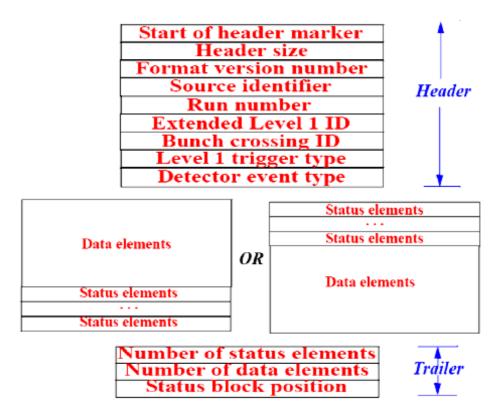

The RX section of the RX/Sector Logic board receives read-out data from PAD boards, via up to eight optical fibre. Such data are then elaborated and transmitted to the ROD, over the RODbus backplane. The main task of the RX/Sector Logic board is to format in a single frame the readout data coming from different PAD boards. Data are sorted according to the same event number and bunch-crossing parameters and some control bits are added. Events with the same bunch-crossing identifiers, even if arrived to the RX/SL board at different times, are grouped in the same RX Frame. The format of the RX Frame is shown in Figure 35.

The RX section logic also checks the correctness of data frames, analysing header and footer in input from the PAD. The RX/SL board has a VME interface that can be used both for the board configuration and for the test of data transmission to the ROD.

Figure 35 - Format of the RX Frame.

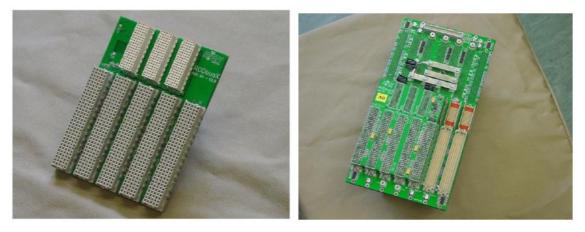

### 3.1.2 The RODbus

In the subsystem that hosts the ROD board there are two RX/SL boards and two Muon Central Trigger Processor Interfaces, whose task is to interface the trigger section of the nearest RX/SL board to the Muon Central Trigger Processor.

The custom backplane RODbus has been designed to handle all the functionalities needed for this section of the trigger and data acquisition system of the ATLAS spectrometer. Front and rear view of the RODbus are shown in Figure 36. It is a 10 layer PCB (Printed Circuit Board) and it fits into the VME64x rear side: connectors on the bottom are assigned to control signals (i.e. busy, reset, diagnostics) driven in TTL standard; the three upper connectors (that match the J0 connector of the VME64X) host high frequency data and timing signals, that are transmitted in LVDS standard.

Figure 36 - The RODbus backplane.

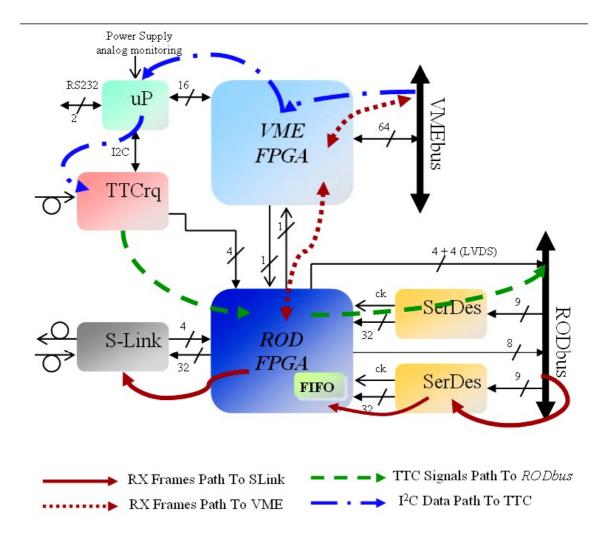

As said before, trigger and read-out information arrive on the RX/SL boards, via optical fibre, and read-out data are sent to the ROD via the RODbus: each RX/SL sends 48 bit at 40 MHz. The signals received by the ROD from the LHC (via TTC) are sent on the RODbus too. Such signals are forwarded to RX/SL boards and to the  $\mu$ TCPIs. For each RX/SL there is a 18 bit TTL shared bus for control signals. The RODbus also allows transmission of data from each RX/SL to the nearest  $\mu$ TCPI over a 48bit TTL private bus. On the LVDS domain, the backplane is made of differential pairs, routed as edge-coupled microstrips. The noisy TTL lines are routed on separate planes and connectors and are terminated as VME lines.

### 3.1.3 The Read Out Driver

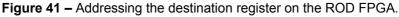

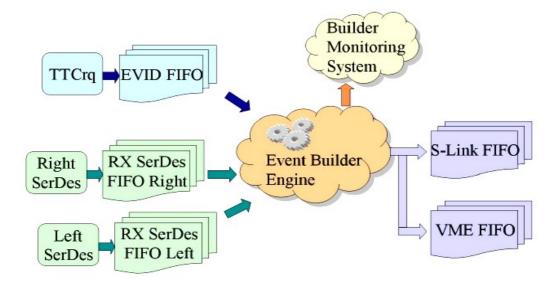

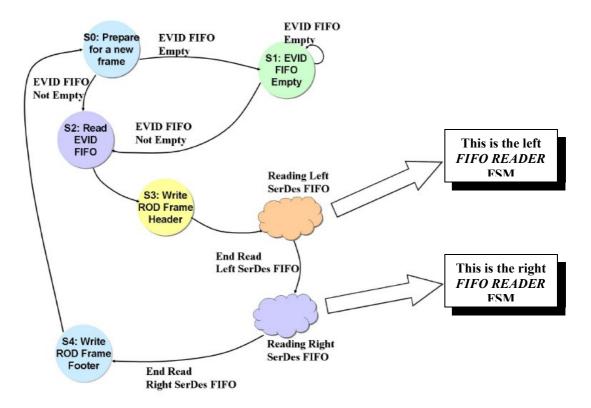

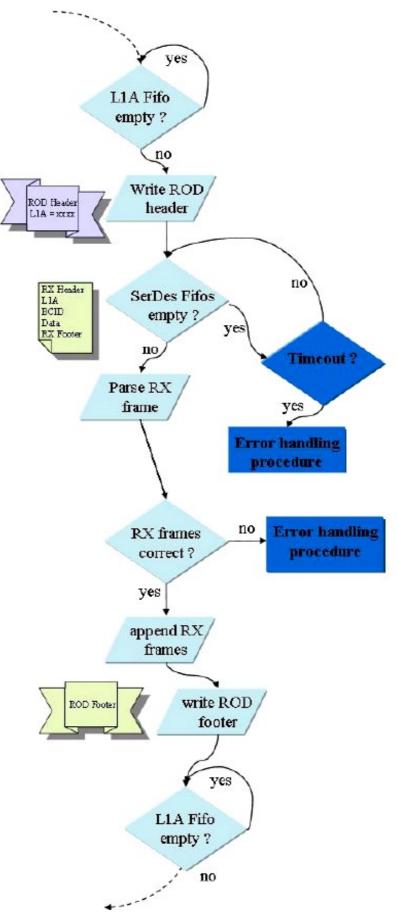

The main task of the ROD is to receive information from each of the two RX/SL boards connected to the ROD via RODbus and to perform a further framing, before transmitting data to the next DAQ levels: the Read Out Buffers (ROB). The scheme of the ROD event builder is shown in Figure 37.

The frames coming from each RX/SL have an RX Header, a certain number of data words (payload) and a footer. The two 16-bit Header words contain information on L1A and BCID of the event and are checked by the ROD Event Builder Engine; the payload of each frame is not inspected by ROD.

Figure 37 – Scheme of the ROD event builder.

The ROD produces a new frame, the MUON ROD FRAME, that has a ROD Header (pertaining to a specific L1A value), a payload made up of the data coming from the selected RX/SL boards, and a ROD Footer.

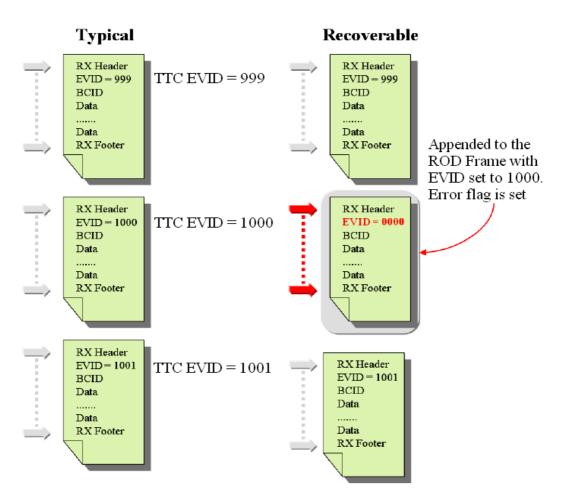

In the event building procedure, the ROD performs also a control of syntactic and logical coherence upon the information coming from the RX/SL boards. In particular, the ROD detects errors in data transmission or mismatch between the L1ID and BCID codes (generated by the On-detector boards and embedded in the RX/SL boards frames) and the corresponding codes transmitted by the TTC to the ROD. Data coming from the RX/SL pertaining to the same event number and Bunch Crossing parameters (L1ID and BCID) are selected and written in the payload of the Muon ROD frame. If there is a discrepancy between L1 and/or BCID identifiers, data are transmitted but flagged with one or more error bits.

Figure 38 – The output data format of the ROD board.

The output data format of the ROD board [29] is shown in Figure 38: the frame starts with a ROD Header (pertaining to a specific EVID value), includes as a payload the frames coming from the RX/SL boards and ends with a Footer containing status and error flags. Output data are 32 bit words and both "Header" and "Trailer" (or "Footer") are made of more words.

Some ROD features have been specifically designed to manage the operations of flow control and error handling. These features allow a user to obtain information about events and errors occurred and to retrieve information about the internal working status of the board.

As already mentioned, the ROD also manages the timing signals of the trigger and data acquisition system. For this purpose, the ROD hosts a TTC receiver module (the TTCrq board) from which it receives control signals to be forwarded to the RX/SL boards. The main timing signals are the LVL1Accept, generated by the first level trigger processor to validate data related to a specific bunch-crossing, and the reset signals BCR and ECR, needed to clear respectively the Bunch Counter and the Event Counter registers. The ROD also provides the RX/SL boards with a clock signal synchronous to LHC.

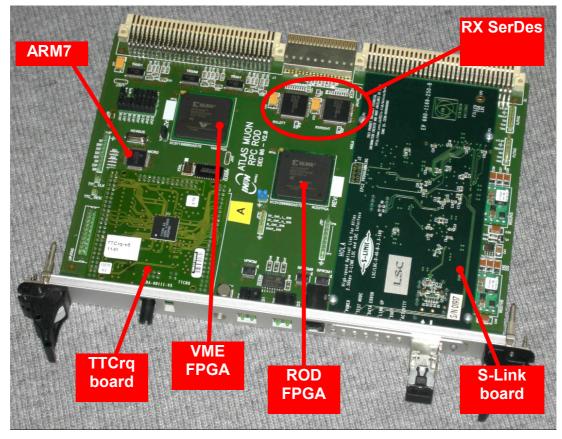

Figure 39 – The Read Out Driver VME board.

The ROD (Figure 39) has a VME interface that allows the user to access the Event Builder function via a VME CPU, on which a specifically designed software runs.

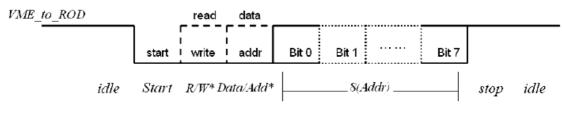

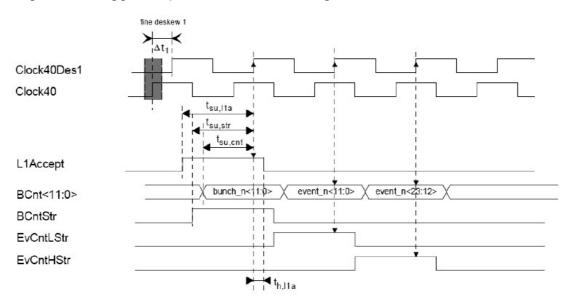

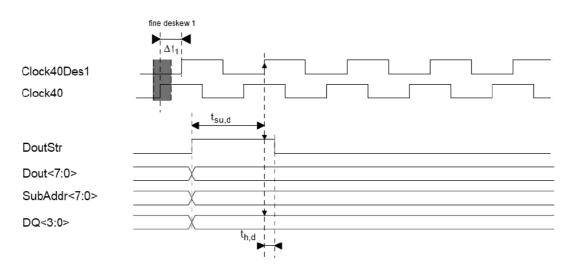

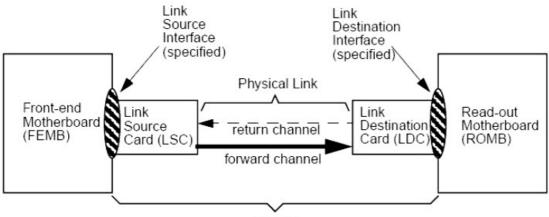

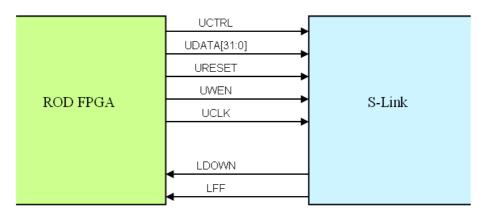

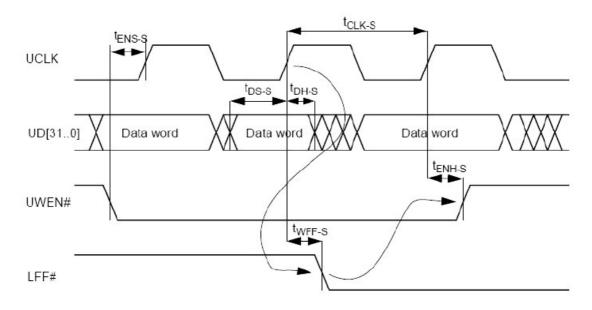

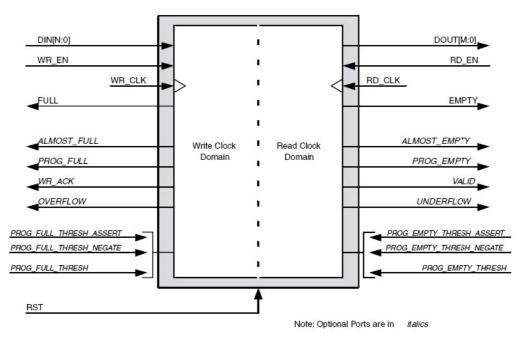

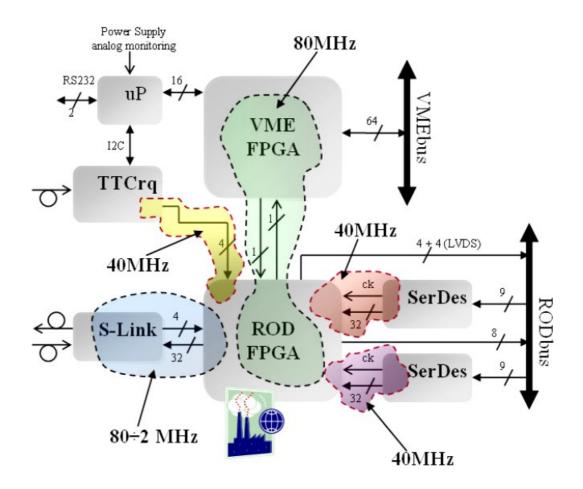

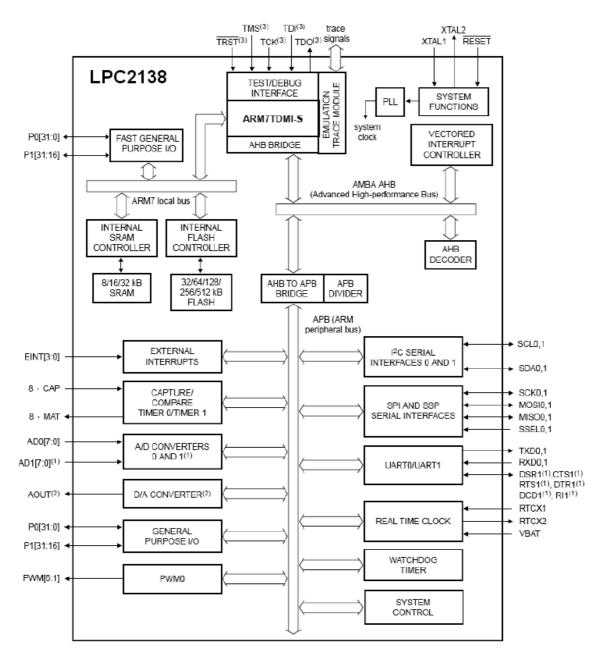

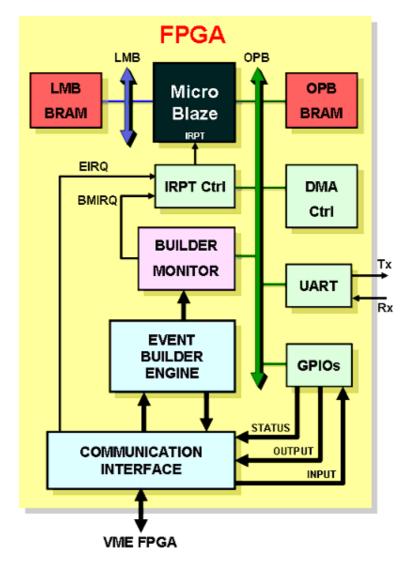

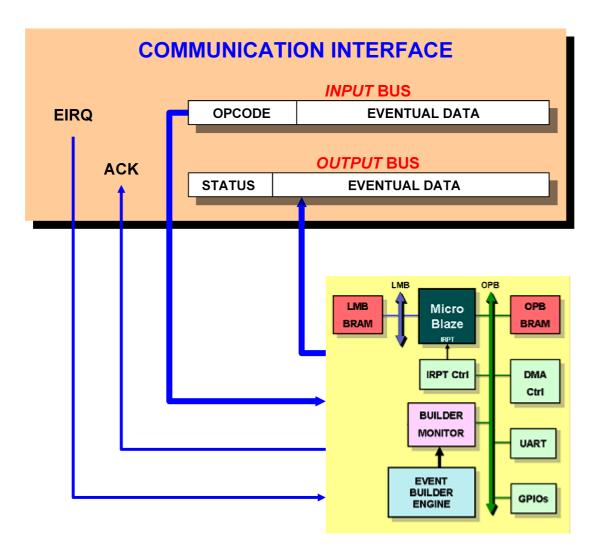

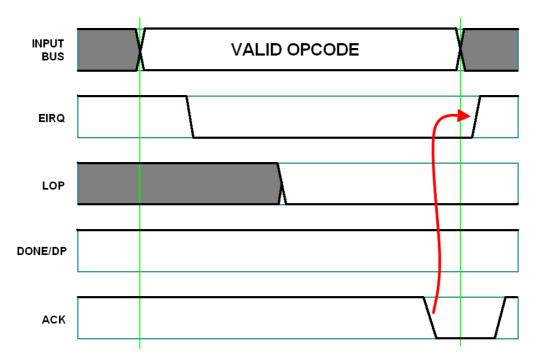

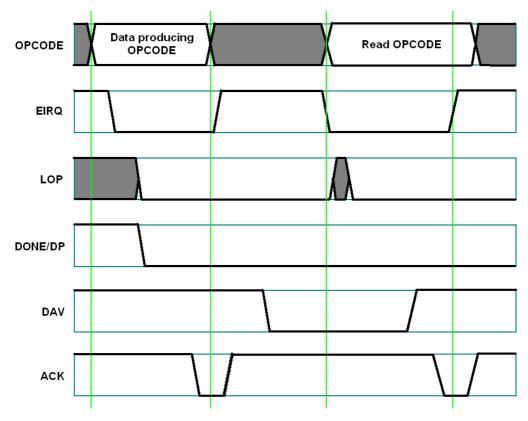

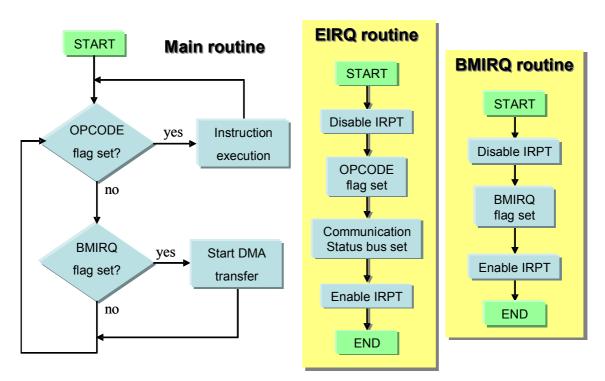

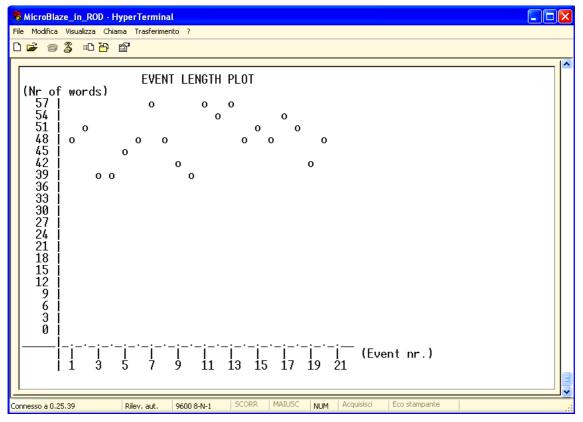

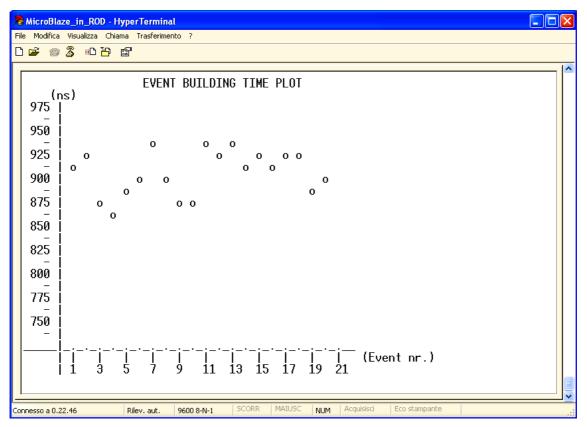

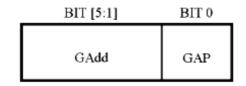

Other monitoring features of the ROD include the control of power supply, of the RODbus backplane's temperature and the of the TTC timing setting. This is achieved by an ARM7 microcontroller, via an I<sup>2</sup>C communication protocol [30].In Figure 39 a photo of the ROD board is shown. The board has the form factor of the VME 64X 6U and is equipped with two VIRTEX II [31] XILINX FPGAs, labelled in Figure 39 as *VME FPGA* and *ROD FPGA*. The board also hosts a microcontroller (labelled as *ARM7*) and the deserializers (*RX SerDes*) that receive data via the RODbus backplane from the RX/SL boards. In Figure 39 are also shown the *TTCrq* modular board, receiver of the TTC optical system, and the transmitter modular board *S-Link*, responsible of the data transmission to the next acquisition levels. Each of these elements will be discussed on later.