# ELECTRONIC SYSTEMS FOR RADIATION DETECTION IN SPACE AND HIGH ENERGY PHYSICS APPLICATIONS

PIERPAOLO VALERIO

Ph.D. Thesis

SUPERVISORS Prof. Augusto Nascetti Dr. Rafael Ballabriga

October 2013

Pierpaolo Valerio: *Electronic systems for radiation detection in space and high energy physics applications,* Ph.D. Thesis, © October 2013

This was a triumph I'm making a note here: HUGE SUCCESS. — GLaDOS from *Portal*

Ohana means family. Family means nobody gets left behind, or forgotten. — Lilo from Lilo & Stitch

This Ph.D. thesis focuses on the analysis and development of novel solution for electronics system for radiation detector, especially suited for space and high energy physics applications. The many blocks of a readout system were studied to develop complete systems, investigating where the performances can be improved over state of the art technologies.

Two different architectures, suitable for different applications, were studied: Fractional Packet Counting, for High Dynamic Range (HDR) integrating imagers and CLICpix, an example of high-accuracy hybrid photon counting detector. The main specifications of the two systems were anayzed and solutions were proposed and implemented to meet them.

A CLICpix prototype has been designed, fabricated and tested (characterization is still ongoing) using a commercial 65 nm CMOS technology. The technology used for the prototype has also been characterized and validated for High Energy Physics (HEP) use and radiation hard design.

## ABSTRACT (ITALIANO)

Questa tesi di dottorato riguarda l'analisi e lo sviluppo di nuove soluzioni per sistemi elettronici per il rilevamento di radiazioni, in particolare per utilizzo in ambito spaziale o per la fisica delle alte energie. I principali blocchi di un sistema di acquisizione sono stati studiati, sviluppando sistemi completi, ricercando soluzioni che permettessero di superare le tecnologie disponibili allo stato dell'arte.

Due diverse architetture sono state studiate, ognuna adatta a una applicazione specifica: Fractional Packet Counting, per sensori ad integrazione ad alto range dinamico, e CLICpix, un esempio di un detector ibrido basato su photon counting. Le principali specifiche sono state analizzate e sono state proposte soluzioni in grado di rispettarle.

Un prototipo di CLICpix e' stato progettato, realizzato e testato (la caratterizzazione e' ancora in corso) utilizzando una tecnologia commerciale CMOS a 65 nm. Questa tecnologia e' stata anche caratterizzata e validata per l'utilizzo nel disegno di strutture rad-hard nella fisica delle alte energie.

Some ideas and figures have appeared previously in the following publications:

- Valerio, P., Alozy, J. A., Arfaoui, S., Ballabriga, R., Benoit, M., Bonacini, S., Campbell, M., Dannheim, D., De Gaspari, M., Felici, D., Kulis, S., Llopart, X., Nascetti, A., Poikela, T., Wong, W. S. (2013). A prototype hybrid pixel detector ASIC for the CLIC experiment. *Accepted as Oral presentation at TWEPP 2013*

- De Gaspari, M., Alozy, J. A., Ballabriga, R., Campbell, M., Llopart, X., Poikela, T., Valerio, P., Wong, W. S. (2013). Design of the analog front-end for the Timepix3 and Smallpix hybrid pixel detectors in 130nm CMOS technology. *Accepted as Oral presentation at TWEPP 2013*

- Bonacini, S., Valerio, P., Avramidou, R., Ballabriga, R., Faccio, F., Kloukinas, K., Marchioro, A. (2012). Characterization of a commercial 65 nm CMOS technology for SLHC applications. *Journal* of *Instrumentation*

- Wong, W. S., Anton, G., Ballabriga, R., Blaj, G., Böhnel, M., Campbell, M., Gabor, T., Heijne, E., Llopart, X., Michel, T., Ritter, I., Poikela, T., Sievers, P., Tlustos, L., Valerio, P. (2012). Electrical measurements of a multi-mode hybrid pixel detector ASIC for radiation detection. *Journal of Instrumentation*

- Wong, W. S., Anton, G., Ballabriga, R., Böhnel, M., Campbell, M., Heijne, E., Llopart, X., Michel, T., Münster, I., Plackett, R., Sievers, P., Takoukam, P., Tlustos, L., Valerio, P. (2011). A pixel detector asic for dosimetry using time-over-threshold energy measurements. *Radiation Measurements*

- Nascetti, A., Valerio, P. (2011). Use of fractional packet counting for high dynamic range imaging applications. *Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment*

- Nascetti, A., Valerio, P. (2011). Design of pixel electronics based on asynchronous self-reset approach with floating-point output representation for high dynamic range imagers. *Journal of Instrumentation*

- Nascetti, A., Valerio, P., Caputo, D., De Cesare, G. (2010). Detection system based on a novel large area hybrid detector. *Microelectronics Journal*

With engineering, I view this year's failure as next year's opportunity to try it again. Failures are not something to be avoided.

You want to have them happen as quickly as you can so you can make progress rapidly.

— Gordon Moore

## ACKNOWLEDGMENTS

So, where to begin... I'm about to be a PhD! Looking back at my studies, it seems that some of what happened has been slightly *random*. I've studied mostly digital stuff at the university, but I worked characterizing a pixel detector for my thesis only because it was my opportunity to go abroad for a while. It turned out my work on pixel detectors helped me to come to CERN, which was something I'd never even thought about before.

Sure, I have plenty of people to thank for being here. Augusto, my university supervisor, for helping me when I was in Rome and supporting me when I went to Geneva, along with all the jolly good fellows who worked with me at the university. My parents who always supported me and especially Enrica, who still loves me despite my choice of pursuing a career abroad (or maybe because of it...). At CERN I've found plenty of awesome colleagues, starting from Rafa, my supervisor, who helped me a lot, not only at work. I have to thank all my "bosses": Lucie, Michael, Alessandro, who, contrary to how a boss is usually depicted, were in fact always kind and supportive. I'd like to mention the other colleagues who helped me and who put up with my stupid emails from time to time: Xavi, Winnie, Massimiliano, Tuomas, Sandro, Szymon, Jérôme, Davide, Lorenzo, Thanu, Daniele (who shared the apartment with me, by the way) and many others.

I also need to thank all the fantastic people I've met here in the *CERN Games Club* (they are too many to list, thank you all!) and our *Random Trip Club* (Hugo, Angela, Herta and Lena, who helped me go through some rough times: tack!). I still miss all my friends I've left in Italy, but I can say people here are awesome too. Speaking of friends in Italy, I need to list at least some: my three "DB pals", Nunzia, Simona and Silvia, and everyone who shared silly passions with me even while hundreds of kilometers away (fantasy football, videogames, *sillier things*).

Finally, I would like to thank all people I've met *once*, whose name I can't remember who gave me a laugh or shared a few minutes of their time with me. Traveling around I've found out that the world is full of diverse people who are wonderful, each in their own way.

Life is good, even as a PhD student. Hell, *especially* as a PhD student. Just enjoy the ride.

## I INTRODUCTION

1 INTRODUCTION TO RADIATION DETECTION 3

1

3

- 1.1 Motivation

- 1.2 Main challenges 4

- 1.3 An engineering approach 4

- II HIGH DYNAMIC RANGE DETECTORS

- 2 THE FRACTIONAL PACKET COUNTING ARCHITECTURE 11

9

11

- 2.1 Motivations and applications

- 2.2 Architectures for HDR detectors 11

- 2.3 Main building blocks 13

- 2.4 Quantitative analysis 15

## III ELECTRONICS FOR HIGH ENERGY PHYSICS 19

- 3 THE CLIC EXPERIMENT 21

- 3.1 A new particle accelerator 21

- 3.1.1 Physics of the CLIC linear accelerator 21

- 3.1.2 Comparison with the LHC 21

- 3.1.3 Some specifications 22

- 3.2 Requirements for the vertex detectors 24

- 3.2.1 General requirements for the vertex detector 24

27

- 3.2.2 Specifications for the pixel detector 25

- 3.3 Technology and design choices

- 3.3.1 State-of-the-art 27

- 3.3.2 Choosing a CMOS technology 29

- 4 TECHNOLOGY CHARACTERIZATION 31

- 4.1 Radiation induced effects on electronics 31

- 4.1.1 Total dose effects 31

- 4.1.2 Single event effects 33

- 4.1.3 Radiation hard electronics by design 34

- 4.2 Design of a test chip for radiation measurements 36

- 4.2.1 TID test structures 37

- 4.2.2 Digital test structures 37

- 4.3 TID and SEU measurements results 38

- 4.3.1 TID testing setup 38

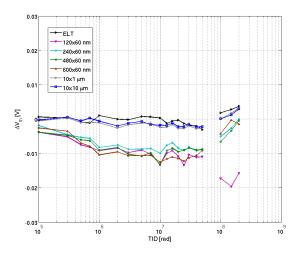

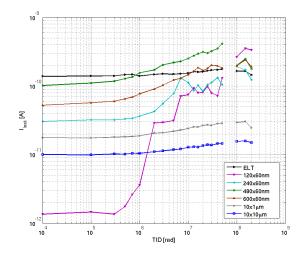

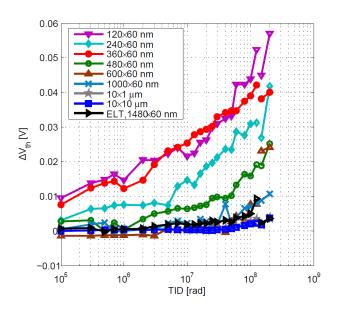

- 4.3.2 TID test results 39

- 4.3.3 SEU testing setup 45

- 4.3.4 SEU test results 46

- 4.4 Tests on analog front-end blocks 48

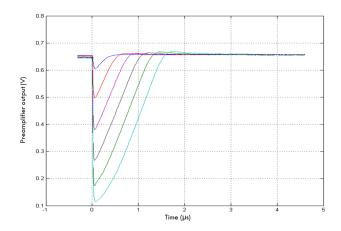

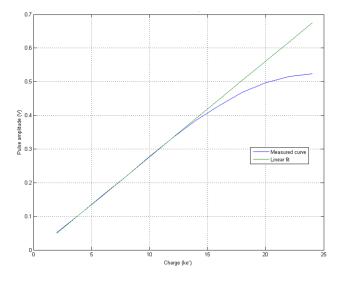

- 4.4.1 Preamplifier block 49

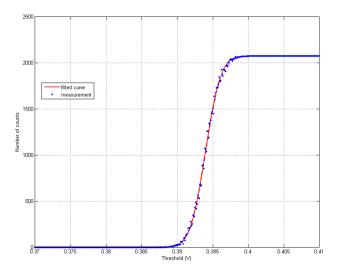

- 4.4.2 Discriminator block 52

- 4.4.3 Calibration DACs 53

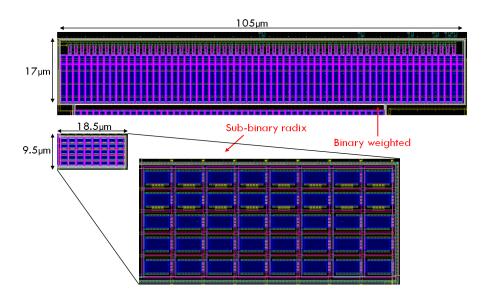

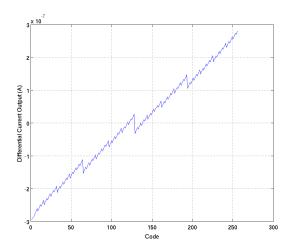

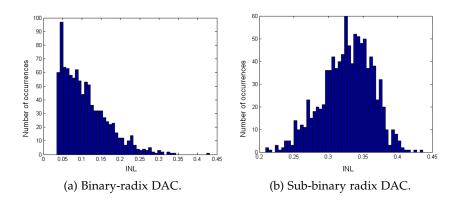

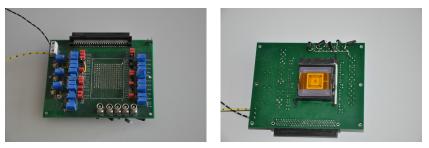

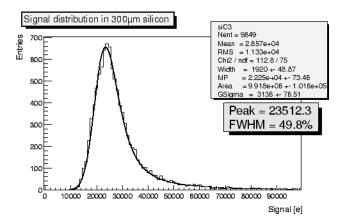

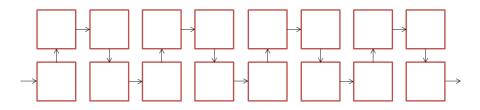

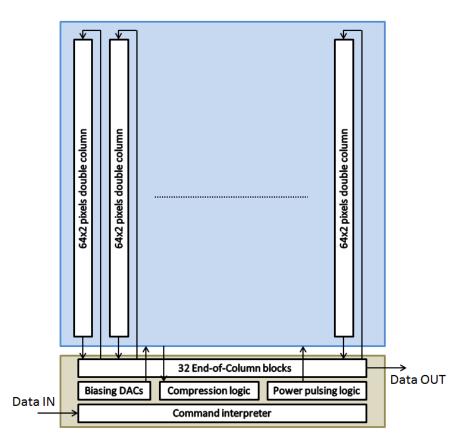

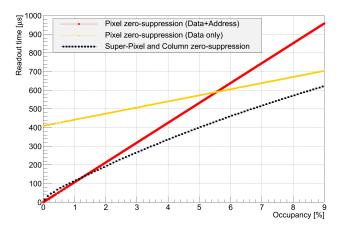

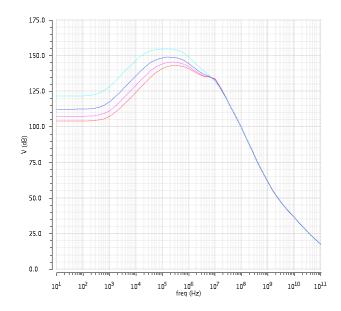

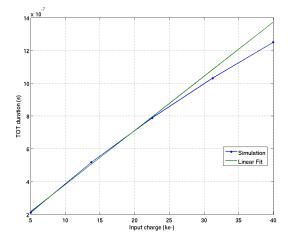

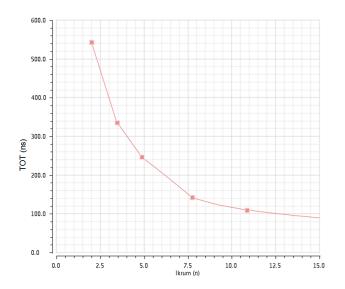

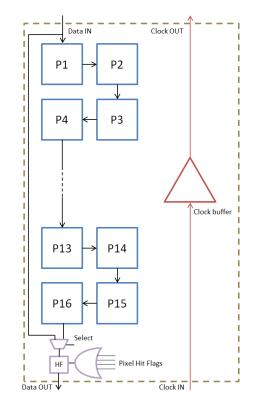

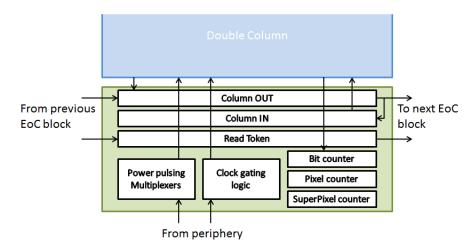

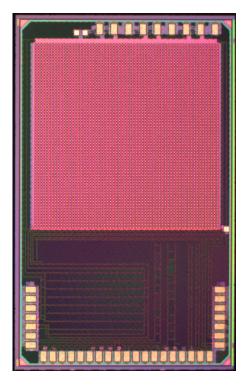

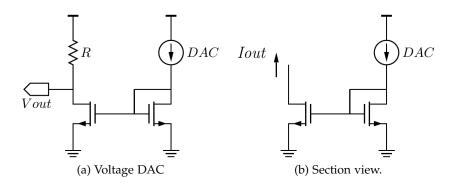

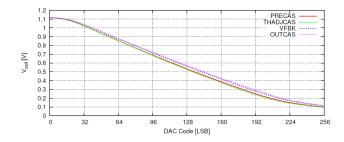

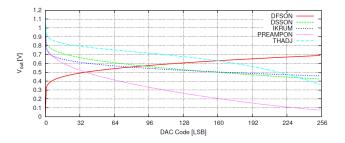

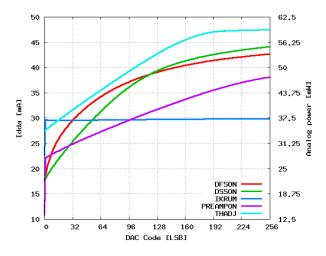

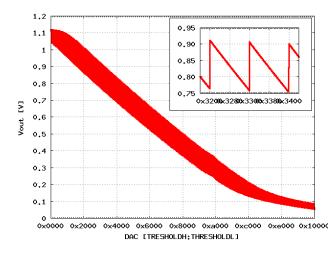

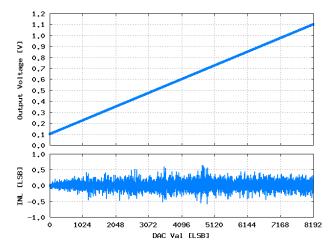

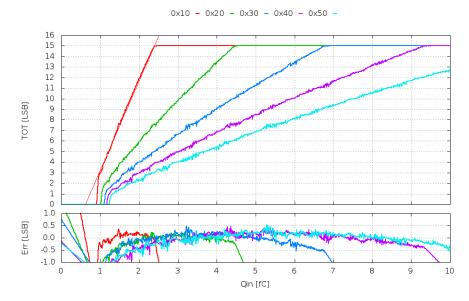

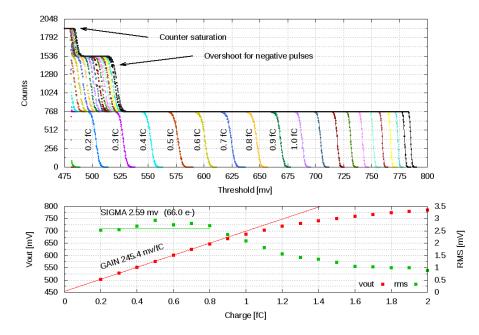

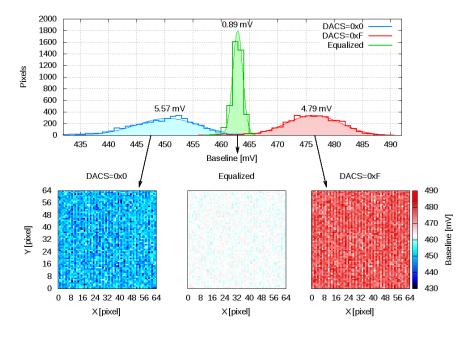

Testing setup 4.4.4 57 Measurement results 58 4.4.5 THE CLICPIX DESIGN 61 5 5.1 The CLIC vertex detector specifications 61 Final specifications of the analog front-end 5.1.1Timing and other global specifications 5.1.2 5.2 CLICpix architecture 64 Pixel architecture 5.2.1 64 Global chip architecture 5.2.2 66 5.2.3 Configuration and operation 67 5.3 Novel features 68 Power pulsing 68 5.3.1 A data compression scheme 5.3.2 69 The analog front-end 5.4 70 Preamplifier and feedback network 5.4.1 71 Discriminator 78 5.4.2 Calibration DAC 80 5.4.3 5.5 Pixel logic 82 5.5.1 Digital pixel blocks 82 Superpixel architecture 5.5.2 83 Asynchronous state machines 84 5.5.3 Periphery and other blocks 85 5.6 5.6.1 End-of-column block 85 State machines and control logic 5.6.2 86 Global configuration and biasing 5.6.3 87 5.6.4 Power distribution 88 I/O interfaces 5.6.5 89 CLICPIX ELECTRICAL CHARACTERIZATION 6 93 6.1 Measurement setup 93 6.2 Test results 94 Periphery measurements 6.2.1 94 6.2.2 Pixel characterization 98

61

63

IV CONCLUSIONS 101

BIBLIOGRAPHY 103

## LIST OF FIGURES

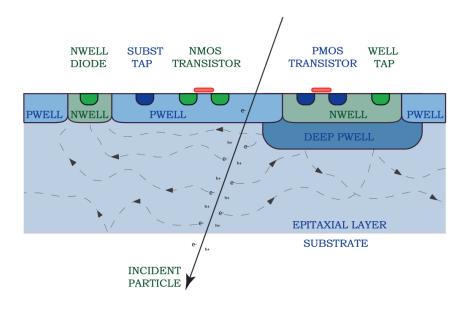

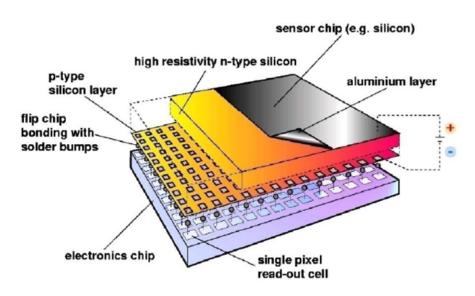

| Figure 1  | MAPS pixel detector 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2  | The state of the second s |

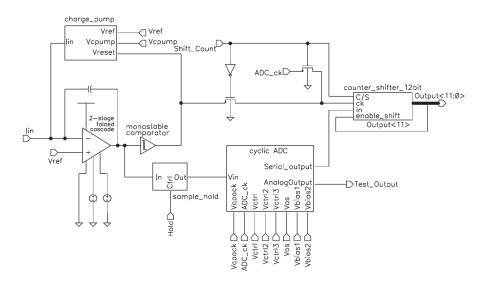

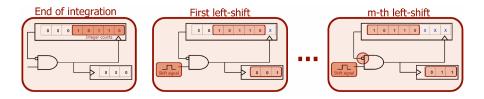

| Figure 3  | FPC block diagram 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

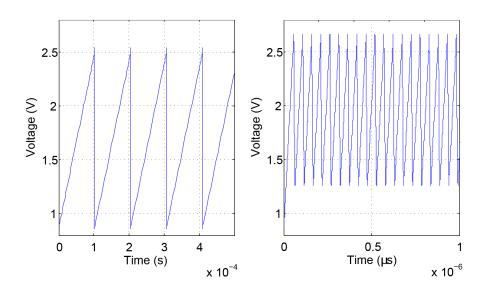

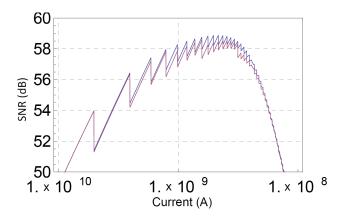

| Figure 7  | SNR of FPC architecture. 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

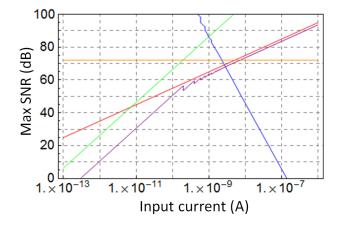

| Figure 8  | SNR contributions in the FPC architecture. 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

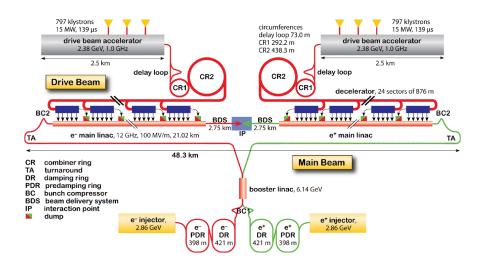

| Figure 9  | CLIC accelerator scheme 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

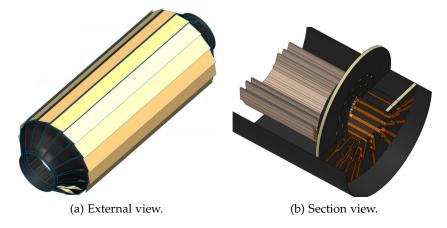

| Figure 10 | The CLIC barrel detector 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

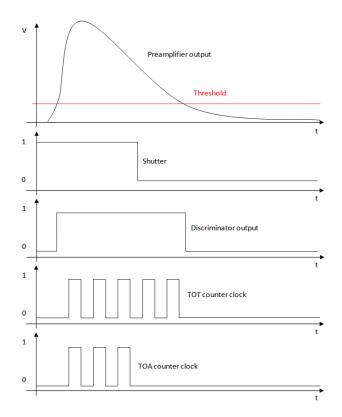

| Figure 11 | Counting clocks timings. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

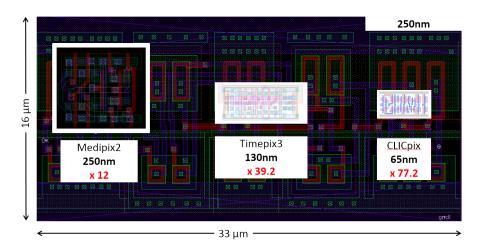

| Figure 12 | Standard cells comparison 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

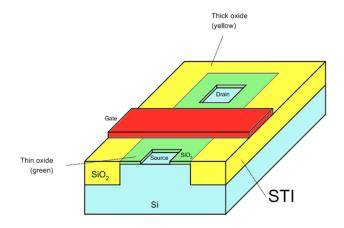

| Figure 13 | STI insulation. 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

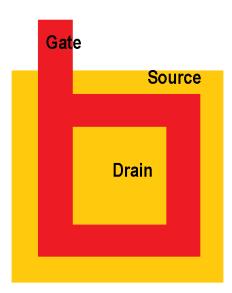

| Figure 14 | ELT transistor 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

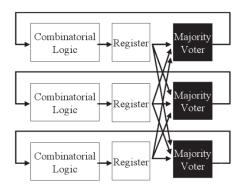

| Figure 15 | TMR architecture 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

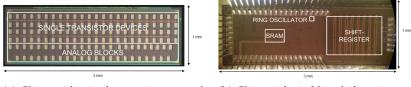

| Figure 16 | Test chips 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

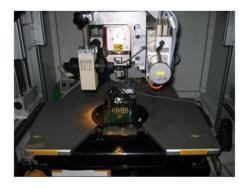

| Figure 17 | X-ray test setup 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

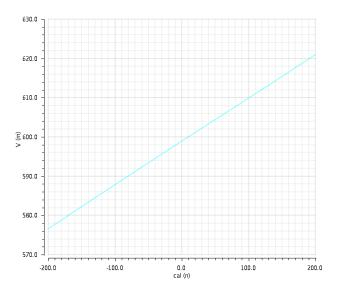

| Figure 18 | Threshold shift of core NMOS devices 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

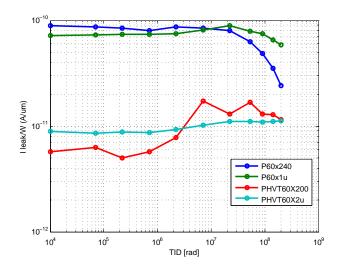

| Figure 19 | Leakage of core NMOS devices 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 20 | Threshold shift of core PMOS devices 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

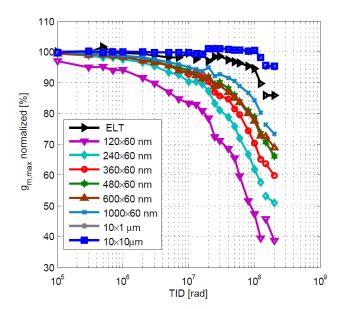

| Figure 21 | Maximum $g_m$ for core PMOS devices 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

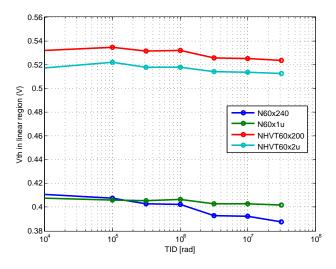

| Figure 22 | Threshold shift of high-Vt NMOS devices 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

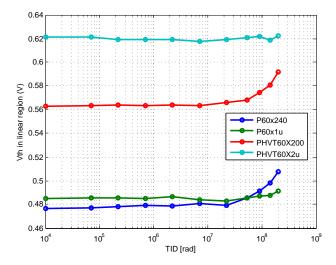

| Figure 23 | Threshold shift of high-Vt PMOS devices 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

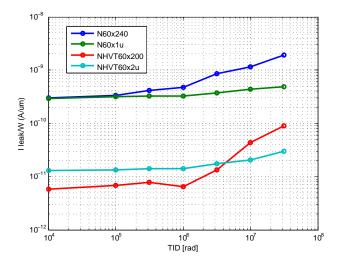

| Figure 24 | Leakage of high-Vt NMOS devices 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 25 | Leakage of high-Vt PMOS devices 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

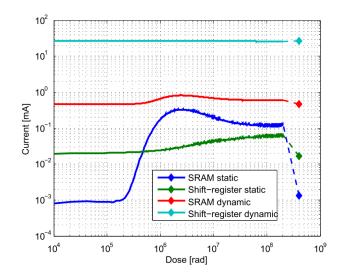

| Figure 26 | Power consumption variation of memory blocks 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

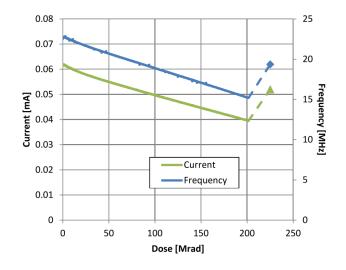

| Figure 27 | Ring oscillator frequency and supply current 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

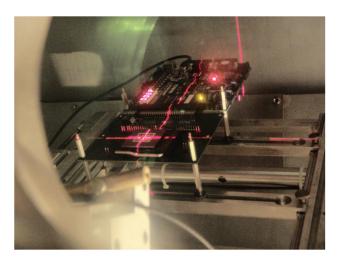

| Figure 28 | SEU test setup 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

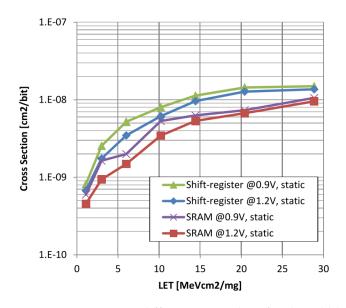

| Figure 29 | Cross-section vs LET 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

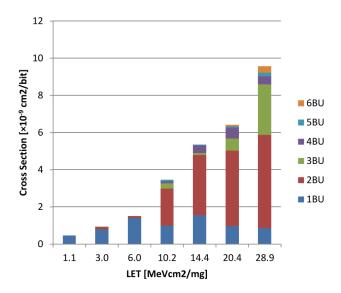

| Figure 30 | Multiple Bit Upsets 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

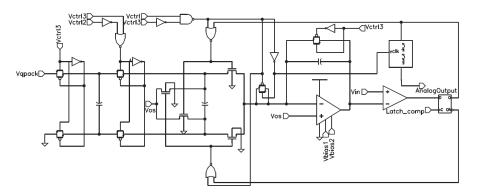

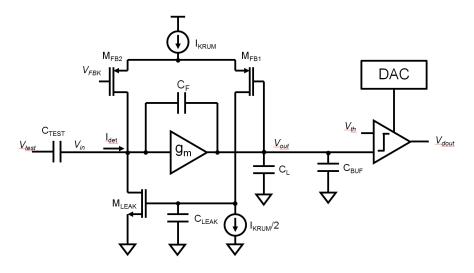

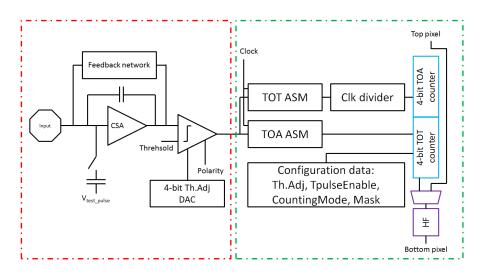

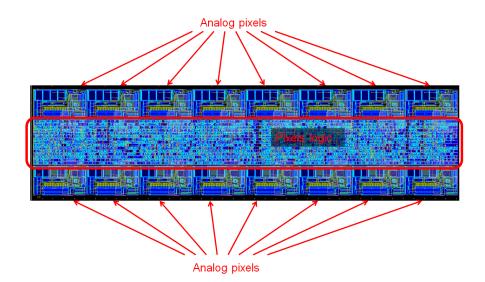

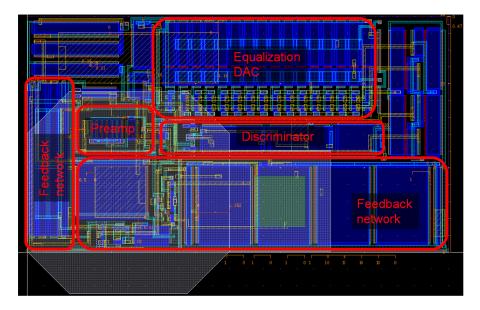

| Figure 31 | Analog Front-End schematic 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

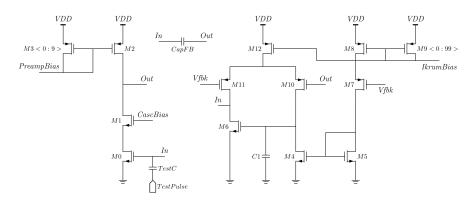

| Figure 32 | Preamplifier with Krummenacher feedback net-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | work 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

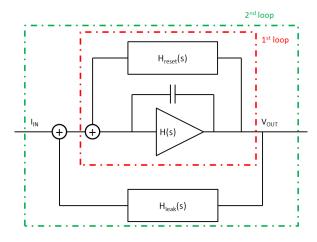

| Figure 33 | Krummenacher double loop network 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

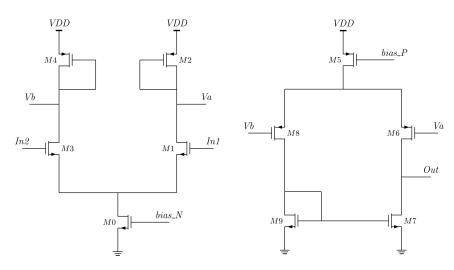

| Figure 34 | Discriminator schematic 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 35 | Ideal DAC characteristics 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

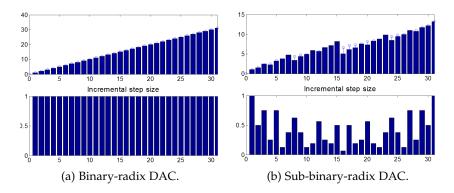

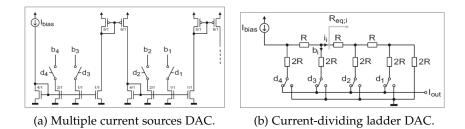

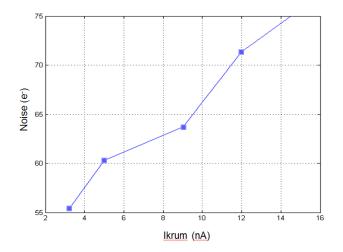

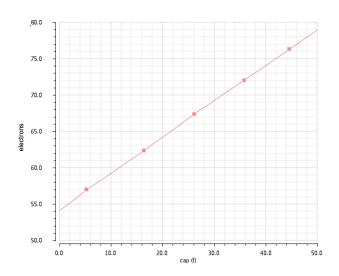

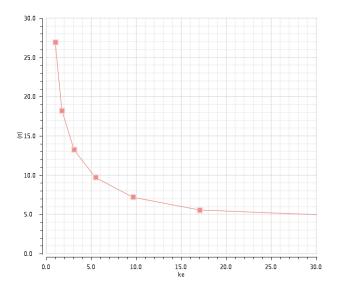

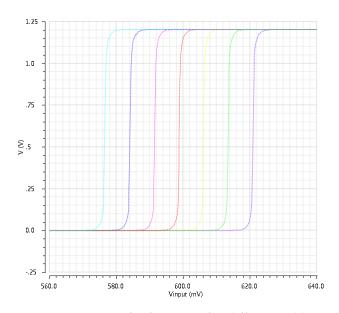

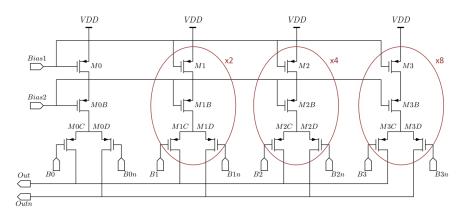

| Figure 36 | Different DAC implementations 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |