# Technical Design Report for the Phase-I Upgrade of the ATLAS TDAQ System

The ATLAS Collaboration

Issue: 1 Reference: CERN-LHCC-2013-018 ATLAS-TDR-023 Created: 21 September 2013 Last modified: 30 November 2013 Prepared by: ATLAS Collaboration

# **Executive Summary**

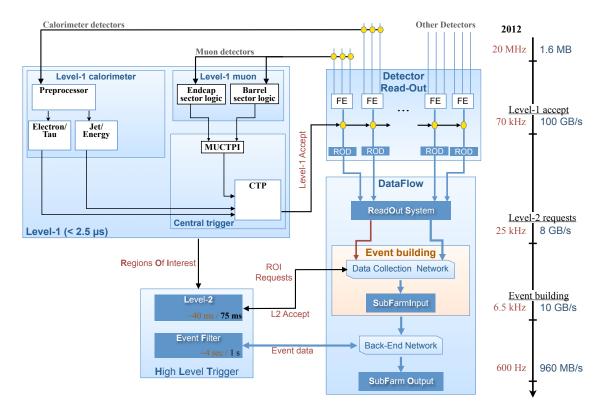

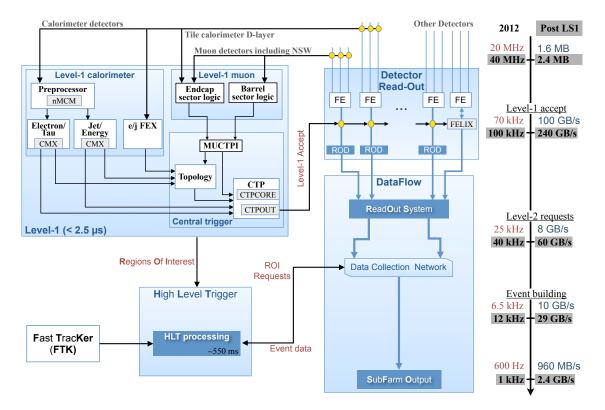

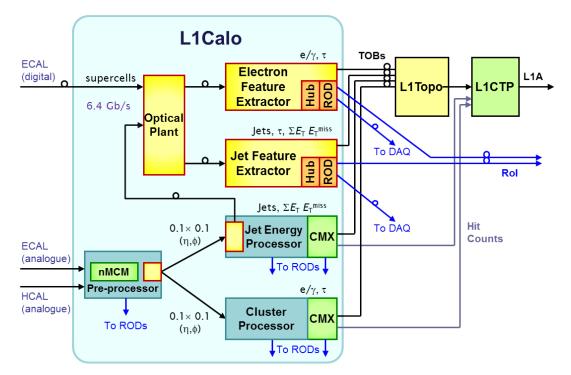

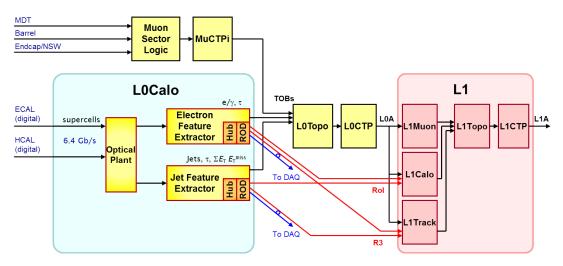

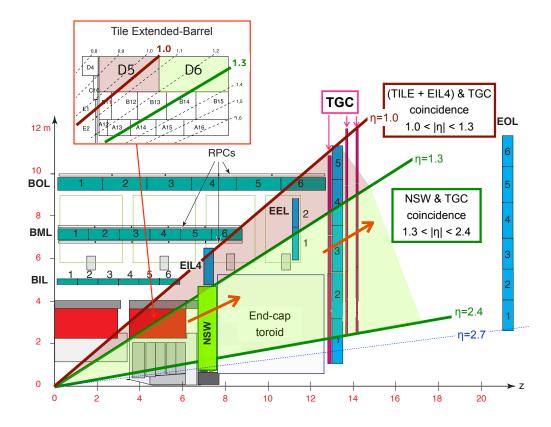

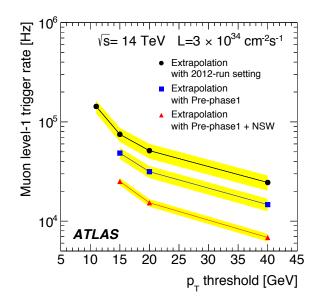

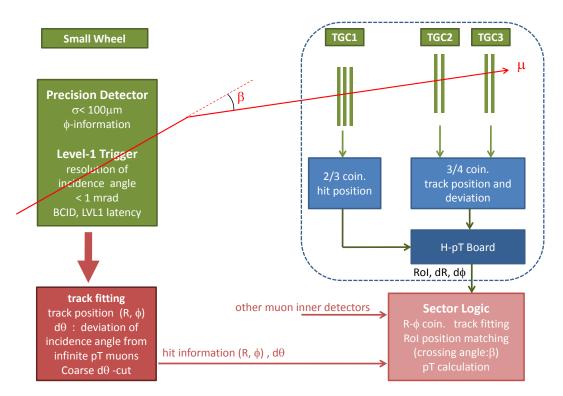

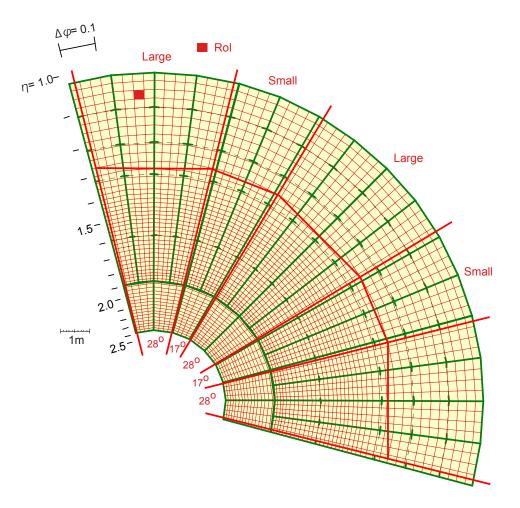

The Phase-I upgrade of the ATLAS Trigger and Data Acquisition (TDAQ) system will allow the ATLAS experiment to efficiently trigger and record data at instantaneous luminosities that are up to three times that of the original LHC design while maintaining trigger thresholds close to those used in the initial run of the LHC. New Level-1 calorimeter feature extraction processors will be incorporated to allow finer granularity data from the Liquid Argon (LAr) Calorimeter to be used to improve electron, photon, and tau selection; more sophisticated and larger-area algorithms to be used to improve jet selection; and improved pile-up corrections to be used for missing momentum reconstruction. The finer granularity data will be optically transmitted from new dedicated LAr Calorimeter hardware which is described in a separate technical design report. The Phase-I TDAQ upgrade will also benefit from the construction of the New Small Wheel (NSW), described in a separate technical design report. The new signals from the NSW will be included in the Level-1 muon endcap trigger, significantly reducing the overall rate by rejecting a large fraction of fake triggers. In addition, signals from the outer layer of the extended barrel of the Tile Calorimeter will be made available to the Level-1 muon endcap trigger for reducing the fake trigger rate in the overlap region between barrel and endcap in the Muon Spectrometer. The upgraded Level-1 muon trigger electronics will provide input to the new Muon-to-Central-Trigger-Processor Interface (MUCTPI). The new calorimeter feature extraction processors and the new MUCTPI will produce object quantities (e.g.  $\eta$ ,  $\phi$  and momentum) that can be combined with each other as well as with signals from the existing calorimeter trigger in a new topological processor. The Central Trigger Processor will be expanded to allow up to 512 distinct triggers. The Data Acquisition and the High-Level Trigger (HLT) processing farm will be upgraded to allow full calorimetry information on a large fraction of the 100 kHz of accepted Level-1 events to be read out and processed. The processing of the HLT will be complemented by the new Fast Tracker (FTK), described in a separate technical design report, that provides full track reconstruction at the start of the HLT selection process at the full Level-1 accept rate. Improved dataflow software, and improved and refined HLT selection algorithms will allow the 100 kHz Level-1 accept rate to be reduced to less than 1 kHz for recording.

# The ATLAS Collaboration

# Argentina

Universidad de Buenos Aires, Buenos Aires Universidad Nacional de La Plata, La Plata

**Armenia** Yerevan Physics Institute, Yerevan

Australia

University of Adelaide, Adelaide Research Centre for High Energy Physics, Melbourne University, Melbourne University of Sydney, School of Physics, Sydney

### Austria

Institut für Astro- und Teilchenphysik, University of Innsbruck, Innsbruck Fachhochschule Wiener Neustadt (FHWN), Wiener Neustadt

Azerbaijan Republic Institute of Physics, Azerbaijan Academy of Sciences, Baku

# **Republic of Belarus**

Institute of Physics, National Academy of Sciences of Belarus, Minsk

National Centre for Particle & High Energy Physics, Minsk

#### Brazil

*Universidade Federal de Juiz de Fora, Universidade Federal do Rio De Janeiro, COPPE/EE/IF, Rio de Janeiro, Universidade Federal de Sao Joao del Rei and Universidade de Sao Paulo*

#### Canada

University of Alberta, Edmonton University of Carleton, Carleton University of Montreal, Group of Particle Physics, Montreal, Quebec Department of Physics, McGill University, Montreal Simon Fraser University, Burnaby, BC Department of Physics, University of Toronto, Toronto TRIUMF, Vancouver and York University, Toronto Department of Physics, University of British Columbia, Vancouver University of Victoria, Victoria

# CERN

European Laboratory for Particle Physics (CERN), Geneva

# Chile

Joint team from Pontificia Universidad Católica de Chile, Santiago and Universidad Técnica Federico Santa María, Valparaíso

#### China

Chinese cluster formed by IHEP Beijing, Nanjing, Shandong, Shanghai Jiao Tong and Hefei

#### Colombia

Universidad Antonio Narino (UAN), Bogotá

#### **Czech Republic**

Palacký University, Olomouc

Academy of Sciences of the Czech Republic, Institute of Physics and Institute of Computer Science, Prague

Charles University in Prague, Faculty of Mathematics and Physics, Prague

*Czech Technical University in Prague, Faculty of Nuclear Sciences and Physical Engineering, Faculty of Mechanical Engineering, Prague*

#### Denmark

Niels Bohr Institute, University of Copenhagen, Copenhagen

#### France

Laboratoire d'Annecy-le-Vieux de Physique de Particules (LAPP), CNRS-IN2P3, Annecy-le-Vieux

Laboratoire de Physique Corpusculaire, Université Blaise Pascal, CNRS-IN2P3, Clermont-Ferrand

Laboratoire de Physique Subatomique et de Cosmologie de Grenoble (LPSC), CNRS-IN2P3, Université Joseph Fourier, Grenoble

Centre de Physique de Particules de Marseille (CPPM), CNRS-IN2P3, Marseille

Laboratoire de l'Accélérateur Linéaire (LAL), CNRS-IN2P3, Orsay

Laboratoire de Physique Nucléaire et de Hautes Energies (LPNHE), Universités de Paris VI et VII, CNRS-IN2P3, Paris

Commisariat a l'Energie Atomique (CEA), DSM/DAPNIA, Centre d'Etudes de Saclay, Gif-sur-Yvette

#### Georgia

Institute of Physics of the Georgian Academy of Sciences and Tbilisi State University, Tbilisi

#### Germany

Physikalisches Institut, University of Bonn, Bonn Deutsches Elektronen-Synchrotron (DESY), Hamburg and Zeuthen TU Dortmund, Experimentelle Physik IV, Dortmund Technical University Dresden, Dresden Fakultät für Mathematik und Physik, Albert-Ludwigs-Universität, Freiburg Justus-Liebig-Universität, Giessen Fakultät für Physik, II. Physikalisches Institut, Georg-August-Universität, Göttingen

Ruprecht-Karls-Universität Heidelberg, Kirchhoff-Institut für Physik and Zentrales Institut für Technische Informatik (ZITI), Heidelberg

Institut für Physik, Humboldt Universität, Berlin

Institut für Physik, Universität Mainz, Mainz

Sektion Physik, Ludwig-Maximilians-Universität München, München

Max-Planck-Institut für Physik, München

Fachbereich Physik, Universität Siegen, Siegen

Fachbereich Physik, Bergische Universität, Wuppertal

Julius-Maximilians-University, Würzburg

### Greece

National Technical University of Athens, Athens

University of Athens, Athens

University of Thessaloniki, High Energy Physics Department and Department of Mechanical Engineering, Thessaloniki

# Israel

Department of Physics, Technion, Haifa School of Physics, Tel Aviv University, Tel Aviv Department of Particle Physics, The Weizmann Institute of Science, Rehovot

# Italy

Dipartimento di Fisica dell' Università di Bologna e I.N.F.N., Bologna Dipartimento di Fisica dell' Università della Calabria e I.N.F.N., Cosenza Laboratori Nazionali di Frascati dell' I.N.F.N., Frascati Dipartimento di Fisica dell' Università di Genova e I.N.F.N., Genova Dipartimento di Fisica dell' Università di Lecce e I.N.F.N., Lecce Dipartimento di Fisica dell' Università di Milano e I.N.F.N., Milano Dipartimento di Scienze Fisiche, Università di Napoli 'Federico II' e I.N.F.N., Napoli Dipartimento di Fisica dell' Università di Pisa e I.N.F.N., Pisa Dipartimento di Fisica dell' Università di Pisa e I.N.F.N., Pisa Dipartimento di Fisica dell' Università di Roma I 'La Sapienza' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma II 'Tor Vergata' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma III 'Roma Tre' e I.N.F.N., Roma

# Japan

Hiroshima Institute of Technology, Hiroshima

KEK, High Energy Accelerator Research Organization, Tsukuba

Kobe University, Kobe

Department of Physics, Kyoto University, Kyoto

Kyoto University of Education, Kyoto

Kyushu University, Kyushu

Nagasaki Institute of Applied Science, Nagasaki

Nagoya University, Nagoya

Faculty of Science, Okayama University, Okayama

Osaka University, Osaka

Faculty of Science, Shinshu University, Matsumoto

International Center for Elementary Particle Physics and Department of Physics, The University of Tokyo

Tokyo Institute of Technology, Tokyo

Physics Department, Tokyo Metropolitan University, Tokyo

Institute of Physics, University of Tsukuba, Tsukuba

Waseda University, Tokyo

#### Morocco

Faculté des Sciences Ain Chock, Université Hassan II, Casablanca, Université Mohamed Premier et LPTM, Oujda, Université Cadi Ayyat et LPHEA, Marrakech, CNESTEN et Université Mohamed V, Rabat

# Netherlands

FOM - Institute SAF NIKHEF and University of Amsterdam/NIKHEF, Amsterdam

Radboud University Nijmegen and NIKHEF, Nijmegen

#### Norway

University of Bergen, Bergen

University of Oslo, Oslo

#### Poland

Institute of Nuclear Physics (IFJ PAN), Polish Academy of Sciences, Cracow

*Faculty of Physics and Applied Computer Science, AGH University of Science and Technology and Marian Smoluchowski Institute of Physics, Jagiellonian University, Cracow*

# Portugal

Laboratório de Instrumentação e Física Experimental de Partículas (LIP), Faculdade de Ciências, Universidade de Lisboa, Centro de Física Nuclear da Universidade de Lisboa, Department of Physics, University of Coimbra, Departamento de Física, Universidade do Minho, Dep Física and CEFITEC of Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa, University of Granada

# Romania

Horia Hulubei National Institute of Physics and Nuclear Engineering (IFIN-HH), Institute of Atomic Physics, Bucharest, ITIM, Cluj Napoca, West University, Timisoara and University Politehnica Bucharest

#### Russia

Institute for Theoretical and Experimental Physics (ITEP), Moscow P.N. Lebedev Institute of Physics, Moscow Moscow Engineering & Physics Institute (MEPhI), Moscow Moscow State University, Moscow Budker Institute of Nuclear Physics (BINP), Novosibirsk State Research Center of the Russian Federation - Institute for High Energy Physics (IHEP), Protvino Petersburg Nuclear Physics Institute (PNPI), St. Petersburg

#### JINR

Joint Institute for Nuclear Research, Dubna

#### Serbia

Institute of Physics, University of Belgrade and Vinca Institute of Nuclear Sciences, Belgrade

#### **Slovak Republic**

Bratislava University, Bratislava, and Institute of Experimental Physics of the Slovak Academy of Sciences, Kosice

#### Slovenia

Jožef Stefan Institute and Department of Physics, University of Ljubljana, Ljubljana

#### South Africa

*University of Cape Town, University of Johannesburg (UJ) and University of the Witwatersrand (WITS), Johannesburg*

#### Spain

Institut de Física d'Altes Energies (IFAE), Universitat Autònoma de Barcelona, Bellaterra (Barcelona)

Physics Department, Universidad Autónoma de Madrid, Madrid

*Instituto de Física Corpuscular (IFIC), Centro Mixto UVEG-CSIC, Valencia and Instituto de Microelectrónica de Barcelona, Bellaterra (Barcelona)*

#### Sweden

Fysiska institutionen, Lunds universitet, Lund Royal Institute of Technology (KTH), Stockholm Stockholm University, Stockholm University of Uppsala, Department of Physics and Astronomy, Uppsala

#### Switzerland

University of Bern, Albert Einstein Center for Fundamental Physics, Laboratory for High Energy Physics, Bern

Section de Physique, Université de Genève, Geneva

#### Taiwan

Academia Sinica, Taipei

#### Turkey

Department of Physics, Ankara University, Gazi University and TOBB ETU, Ankara Department of Physics, Bogazici University, Dogus University and Gaziantep University, Istanbul

#### **United Kingdom**

School of Physics and Astronomy, The University of Birmingham, Birmingham University of Sussex, Brighton Cavendish Laboratory, University of Cambridge, Cambridge University of Warwick, Coventry School of Physics & Astronomy, University of Edinburgh, Edinburgh Department of Physics and Astronomy, University of Glasgow, Glasgow Physics Department, Lancaster University, Lancaster University of Liverpool, Liverpool Department of Physics, Queen Mary and Westfield College, University of London, London Department of Physics, Royal Holloway, University of London, Egham Department of Physics and Astronomy, University College London, London Department of Physics and Astronomy, University of Manchester, Manchester Department of Physics, Oxford University, Oxford Rutherford Appleton Laboratory, Science and Technology Facilities Council, Didcot Department of Physics, University of Sheffield, Sheffield

#### United States of America

State University of New York at Albany, New York Argonne National Laboratory, Argonne, Illinois University of Arizona, Tucson, Arizona Department of Physics, The University of Texas at Arlington, Arlington, Texas Lawrence Berkeley National Laboratory and University of California, Berkeley, California Physics Department of the University of Boston, Boston, Massachusetts Brandeis University, Department of Physics, Waltham, Massachusetts Brookhaven National Laboratory (BNL), Upton, New York University of Chicago, Enrico Fermi Institute, Chicago, Illinois Nevis Laboratory, Columbia University, Irvington, New York University of Texas at Dallas, Dallas, Texas

Department of Physics, Duke University, Durham, North Carolina Department of Physics, Hampton University, Virginia Department of Physics, Harvard University, Cambridge, Massachusetts Indiana University, Bloomington, Indiana Iowa State University, Ames, Iowa University of Iowa, Iowa City, Iowa University of California, Irvine, California Louisiana Tech University, Louisiana University of Massachusetts, Amherst, Massachusetts Massachusetts Institute of Technology, Department of Physics, Cambridge, Massachusetts Michigan State University, Department of Physics and Astronomy, East Lansing, Michigan University of Michigan, Department of Physics, Ann Arbor, Michigan Department of Physics, New Mexico University, Albuquerque, New Mexico Department of Physics, New York University, New York Northern Illinois University, DeKalb, Illinois Ohio State University, Columbus, Ohio Department of Physics and Astronomy, University of Oklahoma Oklahoma State University, Oklahoma University of Oregon, Eugene, Oregon Department of Physics, University of Pennsylvania, Philadelphia, Pennsylvania University of Pittsburgh, Pittsburgh, Pennsylvania Institute for Particle Physics, University of California, Santa Cruz, California SLAC National Accelerator Laboratory, Stanford, California Physics Department, Southern Methodist University, Dallas, Texas State University of New York at Stony Brook, New York Tufts University, Medford, Massachusetts High Energy Physics, University of Illinois, Urbana, Illinois Department of Physics, Department of Mechanical Engineering, University of Washington, Seattle, Washington Department of Physics, University of Wisconsin, Madison, Wisconsin

Yale University, New Haven, Connecticut

# Contents

| Ех | ecuti      | ve Summary                                                                      | iii      |

|----|------------|---------------------------------------------------------------------------------|----------|

| 1  | Intr       | oduction                                                                        | 1        |

|    | 1.1        | Changes for Detectors, Trigger and Data Acquisition                             | 1        |

|    | 1.2        | Upgrade Strategies                                                              | 2        |

|    | 1.3        | Present System and Planned Upgrades                                             | 3        |

|    | 1.4        | Outline of this Report                                                          | 4        |

| 2  | Phv        | sics Motivation                                                                 | 7        |

| -  | 2.1        | Introduction                                                                    | 7        |

|    | 2.2        | Rates and Performance                                                           | 8        |

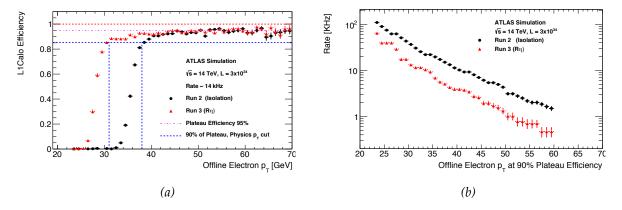

|    |            | 2.2.1 Electron and photon rates                                                 | 8        |

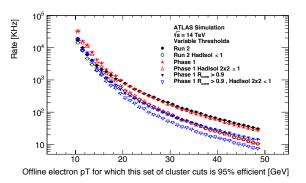

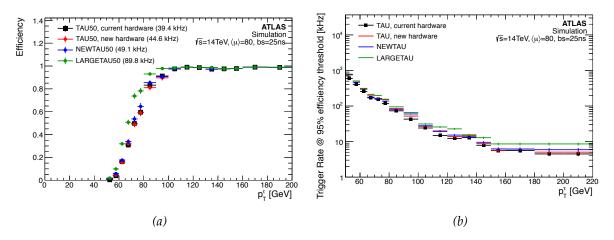

|    |            | 2.2.2       Hadronic tau rate                                                   | 9        |

|    |            | 2.2.3         Muon rate                                                         | 9        |

|    |            | 2.2.4 Missing transverse momentum rate at high pile-up                          | 11       |

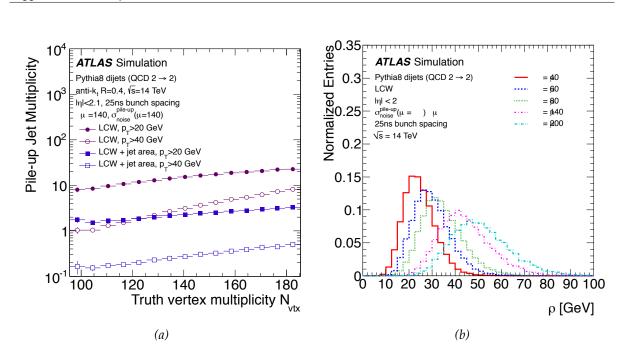

|    |            | 2.2.5 Jet rate at high pile-up                                                  | 11       |

|    |            | 2.2.6       Topological triggering                                              | 12       |

|    | 2.3        | Level-1 Trigger Menus                                                           | 13       |

|    | 2.4        | HLT at Phase-I.                                                                 | 16       |

|    | 2.1        | 2.4.1 HLT selections based on single electron and muon triggers                 | 17       |

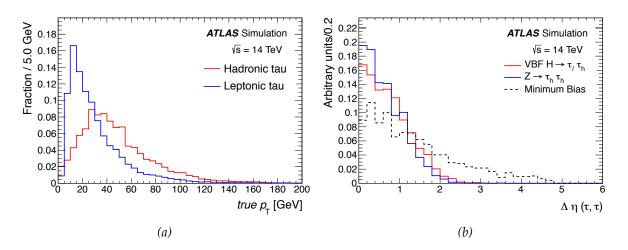

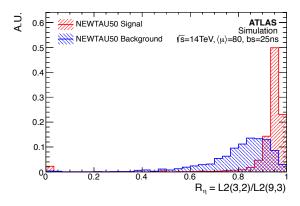

|    |            | 2.4.2 HLT selections based on hadronically decaying tau leptons                 | 17       |

|    |            | 2.4.3 HLT selections based on hadronic triggers                                 | 18       |

|    | 2.5        | Physics Studies                                                                 | 19       |

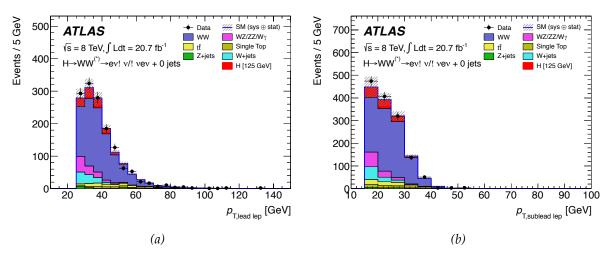

|    | 2.0        | 2.5.1 Higgs couplings and properties                                            | 19       |

|    |            | 2.5.1       Finggs couplings and properties         2.5.2       Boosted objects | 23       |

| 3  | Larr       | el-1 Calorimeter Trigger                                                        | 26       |

| 3  | <b>Lev</b> | Introduction                                                                    | 26<br>26 |

|    | 3.1<br>3.2 |                                                                                 | 26<br>27 |

|    | 5.2        | Algorithms & Performance                                                        | 27       |

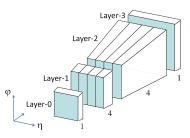

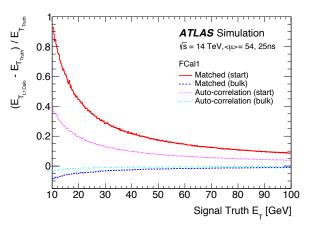

|    |            | 3.2.1 Input data                                                                |          |

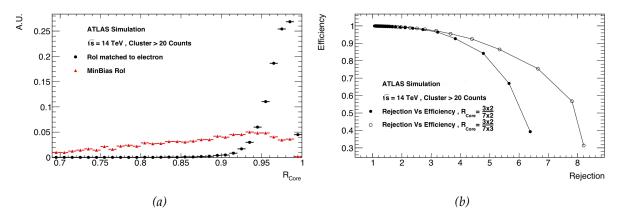

|    |            | 3.2.2 Electron/photon trigger                                                   | 27       |

|    |            | 3.2.3 Tau trigger                                                               | 30       |

|    | 2.2        | 3.2.4 Jet trigger                                                               | 31       |

|    | 3.3        | System Evolution                                                                | 34       |

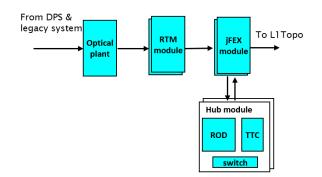

|    |            | 3.3.1 Architecture                                                              | 34       |

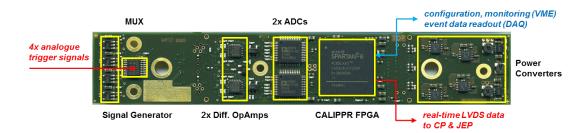

|    |            | 3.3.2 nMCM                                                                      | 37       |

|    | 0.4        | 3.3.3 CMX modules                                                               | 39       |

|    | 3.4        | Phase-I Architecture                                                            | 41       |

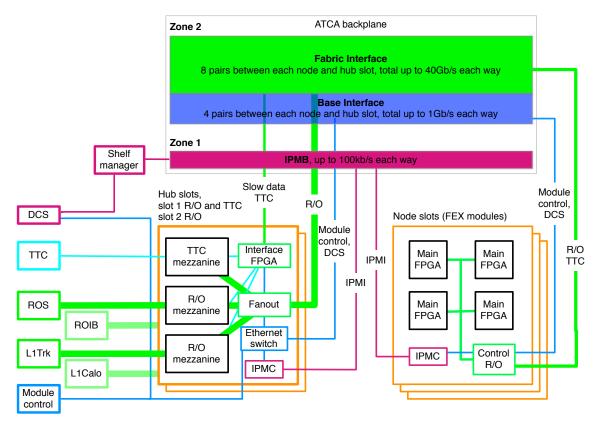

|    |            | 3.4.1 Input interfaces                                                          | 41       |

|    |            | 3.4.2 The Electron Feature Extractor (eFEX) module                              | 43       |

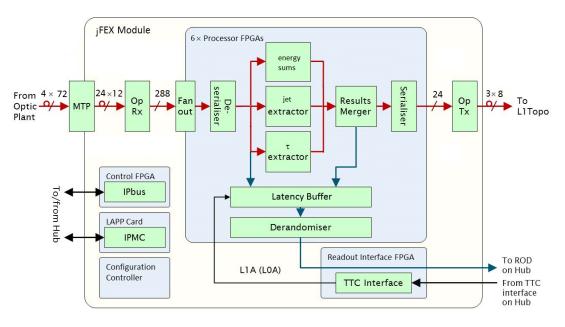

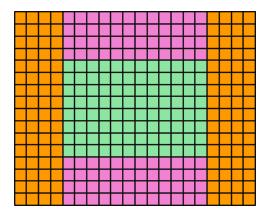

|    |            | 3.4.3 The Jet Feature Extractor (jFEX) module                                   | 46       |

|    |            | 3.4.4 Output interfaces                                                         | 49       |

|    | a =        | 3.4.5 Common modules                                                            | 51       |

|    | 3.5        | Latency Considerations                                                          | 56       |

|    | 3.6        | Firmware                                                                        | 56       |

|   | 3.7  | Software                                          | 57       |

|---|------|---------------------------------------------------|----------|

|   |      |                                                   | 57       |

|   |      | 3.7.2 Offline software                            | 57       |

|   | 3.8  | Testing, Installation & Commissioning             | 58       |

|   |      | 3.8.1 Testing                                     | 58       |

|   |      | 3.8.2 Installation                                | 59       |

|   |      | 3.8.3 Commissioning                               | 59       |

|   | 3.9  | System Performance                                | 59       |

|   |      | 3.9.1 Validation                                  | 59       |

|   |      | 3.9.2 Calibration and monitoring                  | 60       |

|   | 3.10 | Optional Additions                                | 61       |

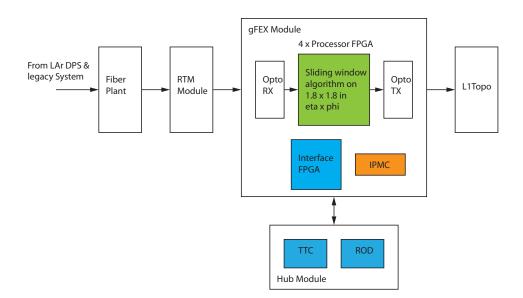

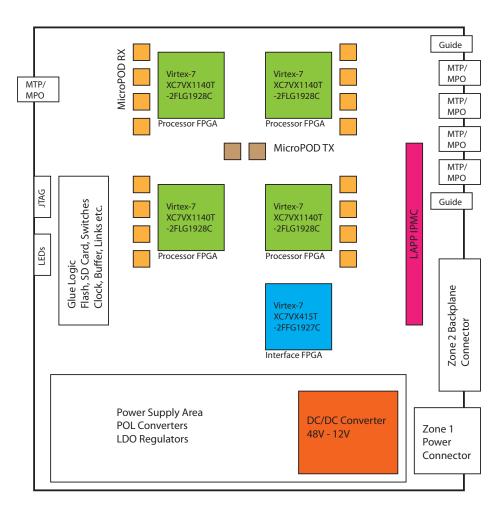

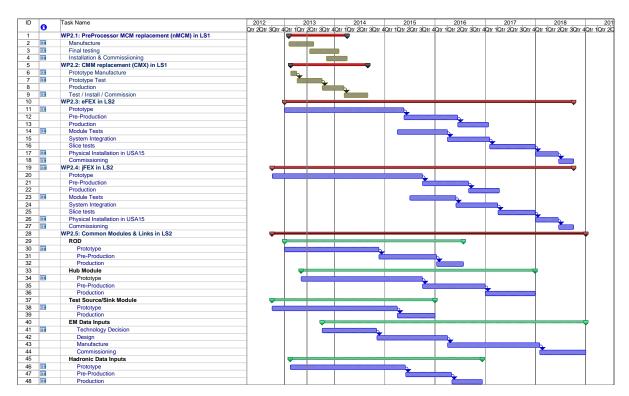

|   |      | 3.10.1 The Global Feature Extractor (gFEX) module | 61       |

|   | 3.11 | Relation to the Phase-II Upgrade                  | 64       |

|   | 3.12 | Project Organisation                              | 65       |

| 4 | Leve | el-1 Muon Trigger                                 | 67       |

| • |      |                                                   | 67       |

|   |      |                                                   | 67       |

|   |      |                                                   | 67       |

|   |      |                                                   | 69       |

|   |      | 0                                                 | 71       |

|   |      | 0                                                 | 72       |

|   |      | 5                                                 | 72       |

|   | 4.2  |                                                   | 73       |

|   |      |                                                   | 73       |

|   |      |                                                   | 73       |

|   |      |                                                   | 77       |

|   | 4.3  |                                                   | 77       |

|   |      |                                                   | 78       |

|   |      | 4.3.2 Muon efficiency and fake rate reduction     | 78       |

|   |      |                                                   | 80       |

|   |      |                                                   | 81       |

| 5 | Low  | el-1 Central Trigger System                       | 83       |

| 5 | 5.1  |                                                   | 83       |

|   | 0.1  |                                                   | 84       |

|   |      |                                                   | 85       |

|   |      |                                                   | 86       |

|   |      | 00                                                | 87       |

|   |      | 1 1                                               | 87       |

|   |      | 8                                                 | 88       |

|   | 5.2  | 5                                                 | 88       |

|   | 0.2  |                                                   | 89       |

|   |      |                                                   | 89       |

|   |      |                                                   | 90       |

|   |      | 1                                                 | 90<br>91 |

|   |      |                                                   | 91<br>92 |

|   |      | 5.2.5 Latency                                     | ッム       |

|   |                                                                                                              | 5.2.6 Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                                                        |

|---|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                              | 5.2.7 Project planning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93                                                                                                                                                        |

|   | 5.3                                                                                                          | Level-1 Topological Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                                                                        |

|   | 5.4                                                                                                          | Level-1 Trigger Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                                                                                                                                                        |

|   | ~ .                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

| 6 |                                                                                                              | line and High-Level Trigger Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>99</b>                                                                                                                                                 |

|   | 6.1                                                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99                                                                                                                                                        |

|   | 6.2                                                                                                          | Description of the Run 1 and Run 2 Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 99                                                                                                                                                        |

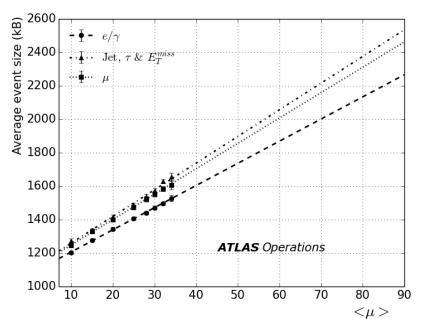

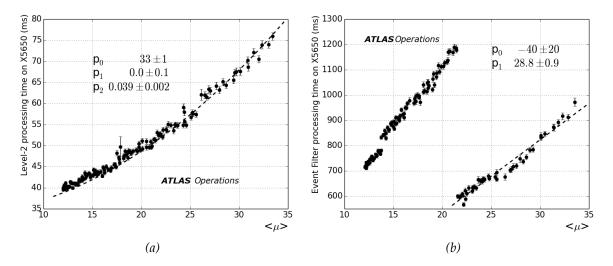

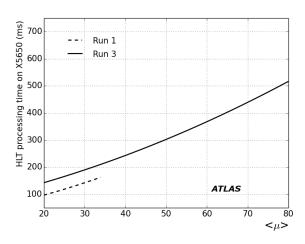

|   | 6.3                                                                                                          | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                           |

|   | 6.4                                                                                                          | Baseline System, Assumptions and Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |

|   | 6.5                                                                                                          | Work Breakdown and Effort Estimates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                           |

|   |                                                                                                              | 6.5.1 High-Level Trigger selection software tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                           |

|   |                                                                                                              | 6.5.2 Data acquisition and control online software tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |

|   |                                                                                                              | 6.5.3 Effort estimates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                           |

|   |                                                                                                              | 6.5.4 Milestones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |

|   | 6.6                                                                                                          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108                                                                                                                                                       |

| 7 | Dat                                                                                                          | a Acquisition and High-Level Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110                                                                                                                                                       |

| 1 | <b>7</b> .1                                                                                                  | 1 0 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 110                                                                                                                                                       |

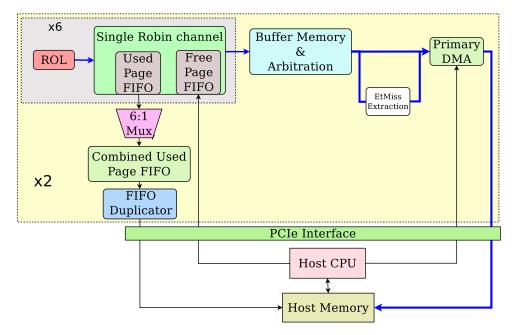

|   | 7.1                                                                                                          | 7.1.1 Read-out system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           |

|   |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

|   |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

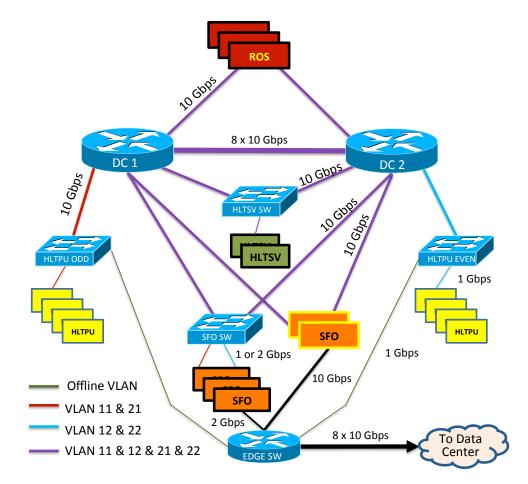

|   |                                                                                                              | 7.1.2 DAQ networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113                                                                                                                                                       |

|   | 72                                                                                                           | <ul><li>7.1.2 DAQ networks</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113<br>115                                                                                                                                                |

|   | 7.2                                                                                                          | 7.1.2DAQ networks7.1.3Output to mass storageUpgrades in LS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113<br>115<br>117                                                                                                                                         |

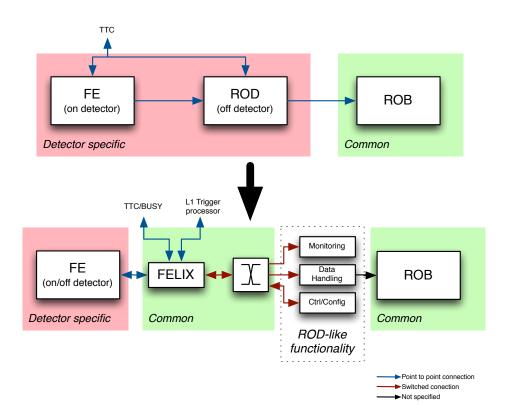

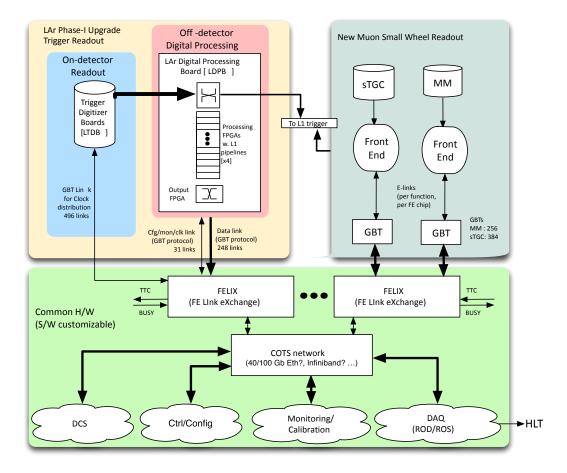

|   |                                                                                                              | 7.1.2DAQ networks7.1.3Output to mass storageUpgrades in LS27.2.1Detector read-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113<br>115<br>117<br>117                                                                                                                                  |

|   | 7.2<br>7.3                                                                                                   | 7.1.2DAQ networks7.1.3Output to mass storageUpgrades in LS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113<br>115<br>117<br>117                                                                                                                                  |

| 8 | 7.3                                                                                                          | 7.1.2 DAQ networks7.1.3 Output to mass storageUpgrades in LS27.2.1 Detector read-outEvolution of HLT Compute Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113<br>115<br>117<br>117                                                                                                                                  |

| 8 | 7.3                                                                                                          | 7.1.2 DAQ networks7.1.3 Output to mass storageUpgrades in LS27.2.1 Detector read-outEvolution of HLT Compute Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>113</li> <li>115</li> <li>117</li> <li>117</li> <li>120</li> <li>124</li> </ol>                                                                  |

| 8 | 7.3<br><b>Res</b> e                                                                                          | 7.1.2 DAQ networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113<br>115<br>117<br>117<br>120<br><b>124</b>                                                                                                             |

| 8 | 7.3<br><b>Res</b><br>8.1                                                                                     | 7.1.2 DAQ networks       7.1.3 Output to mass storage         7.1.3 Output to mass storage       7.1.3 Output to mass storage         Upgrades in LS2       7.2.1 Detector read-out         7.2.1 Detector read-out       7.2.1 Detector read-out         Evolution of HLT Compute Power       7.2.1 Output Power         ources, Organisation, and Workplan         Participating Institute Responsibilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol> <li>113</li> <li>115</li> <li>117</li> <li>120</li> <li>124</li> <li>124</li> <li>127</li> </ol>                                                     |

| 8 | 7.3<br><b>Res</b><br>8.1<br>8.2                                                                              | 7.1.2 DAQ networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>113</li> <li>115</li> <li>117</li> <li>120</li> <li>124</li> <li>124</li> <li>127</li> <li>128</li> </ol>                                        |

| 8 | 7.3<br><b>Res</b><br>8.1<br>8.2<br>8.3                                                                       | 7.1.2 DAQ networks       7.1.3 Output to mass storage         9.1.3 Output to mass storage       9.1.3 Output to mass storage         9.1.3 Output to mass storage       9.1.3 Output to mass storage         9.1.3 Output to mass storage       9.1.3 Output to mass storage         9.1.3 Output to mass storage       9.1.3 Output to mass storage         9.1.3 Output to mass storage       9.1.3 Output to mass storage         9.1.4 Detector read-out       9.1.4 Output to mass storage         9.1.5 Output to read-out       9.1.4 Output to mass storage         9.1.6 Output to read-out       9.1.4 Output to mass storage         9.1.7 Output to read-out       9.1.4 Output to mass storage         9.1.8 Output to read-out       9.1.4 Output to mass storage         9.1.1 Detector read-out       9.1.4 Output to mass storage         9.1.1 Output to mass storage       9.1.4 Output to mass storage         9.1.1 Output to mass storage       9.1.4 Output to mass storage         9.1.1 Output to mass storage       9.1.4 Output to mass storage         9.1.1 Output to mass storage | <ul> <li>113</li> <li>115</li> <li>117</li> <li>120</li> <li>124</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>128</li> </ul>              |

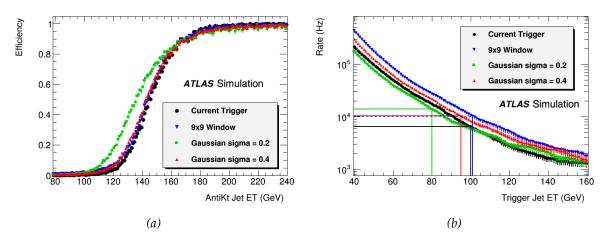

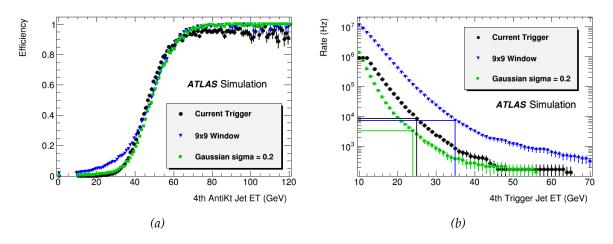

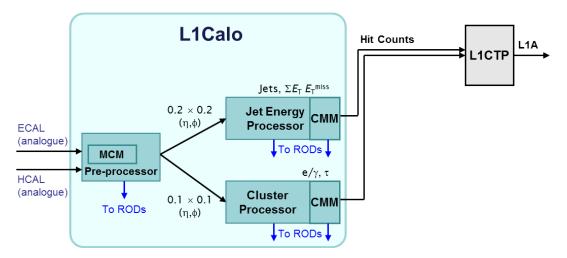

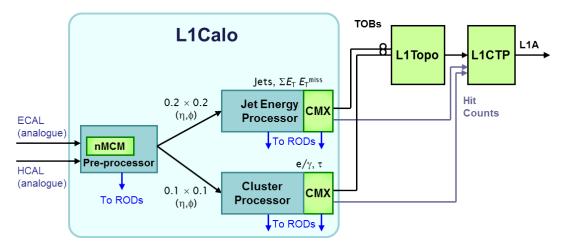

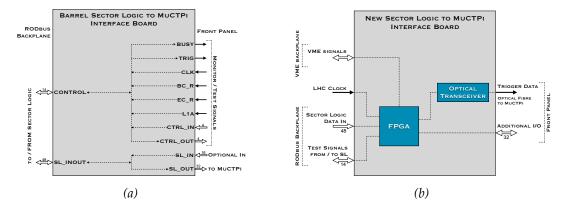

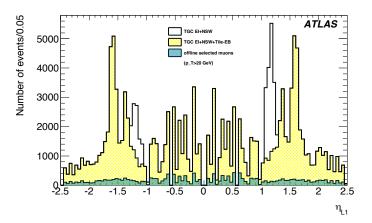

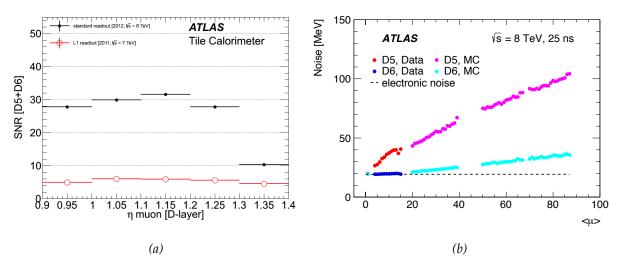

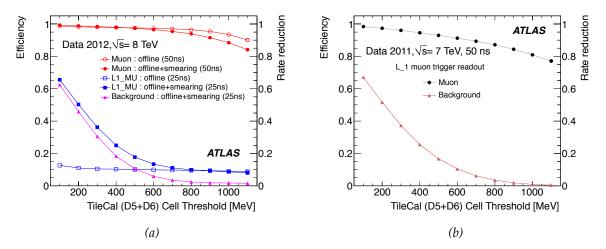

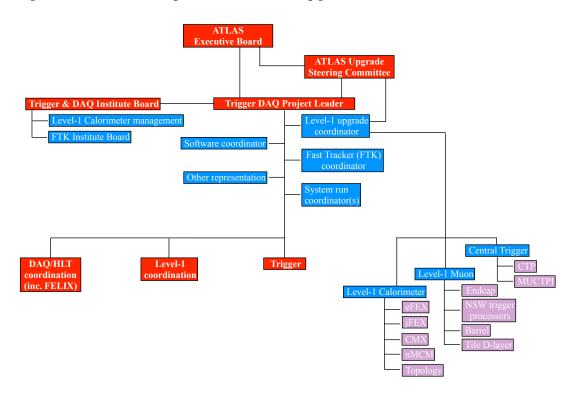

| _ | <ul> <li>7.3</li> <li><b>Res</b></li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> </ul> | 7.1.2 DAQ networks         7.1.3 Output to mass storage         Upgrades in LS2         7.2.1 Detector read-out         Fources, Organisation, and Workplan         Participating Institute Responsibilities         Management Organisation         Construction and Software Effort         Schedule and Milestones         Cost and Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>113</li> <li>115</li> <li>117</li> <li>120</li> <li>124</li> <li>124</li> <li>127</li> <li>128</li> <li>128</li> <li>128</li> <li>128</li> </ul> |