## UNIVERSITY OF PADOVA

Department of Electronics and Computer Engineering (DEI)

Ph.D in: Electronics and Communication Engineering

years 1996-1999

Dissertation

# Development of the digital read-out system for the CERN Alice pixel detector

Coordinator: Full Prof. Silvano Pupolin

Supervisor: Full Prof. Enrico Zanoni

Ph.D student: Tullio Grassi

December, the 31<sup>st</sup> 1999

## UNIVERSITÀ DEGLI STUDI DI PADOVA

Sede Amministrativa: Università degli Studi di Padova

Dipartimento di Elettronica e Informatica della Facoltà di Ingegneria

#### DOTTORATO DI RICERCA IN: INGEGNERIA ELETTRONICA E DELLE TELECOMUNICAZIONI

#### XII CICLO

Tesi:

# Sviluppo del sistema digitale di lettura del rivelatore a pixel di Alice (CERN)

(titolo originale: Development of the digital read-out system for the CERN Alice pixel detector)

Coordinatore: Ch.mo Prof. Silvano Pupolin

Supervisore: Ch.mo Prof. Enrico Zanoni

Dottorando: Tullio Grassi

31 dicembre 1999

## Acknowledgement

Over the three years in which the work presented in this thesis was done I had the chance to work in three different groups. My original team is the Microelectronic group of the University of Padova. Here I thank very much my Ph.D. supervisor Prof. Enrico Zanoni, but also the professors Sandro Paccagnella and Andrea Neviani for the interest showed in my activity. I do not forget the help and friendship received by Andrea Candelori, Marco Ceschia and the other students of the group. Thanks also to the group III of the Padova section of INFN, leaded by Prof. Morando, as they first introduced me to the field of the electronics for high energy physics. From this group I mention Nicola Carrer as he was able to explain to an engineer the mysteries of the quark nature! But also Gianfranco Segato for the time spent in the laboratory and Sandro Martini for the time spent outside the lab! For what I learned in term of circuit and system level design, I owe a special thank to Fabio Formenti and the components of the ED/EP group of CERN: Luciano Musa for the precious advice that he often gave me, Michel Morel and Mike Burns for helping me when I felt lost facing a mountain of cables and instrumentations, Prof. Jose Toledo "Curro" for our useful battles and for teaching me electronics in Spanish, Alex Kluge for the review of my thesis, Ken Wyllie and the members of the CERN/MIC group for our fruitful "interface". Finally I would like to thank my family for their affectionate and unselfish support and

my girlfriend Ludmila who could not care less about my work, showing that one can live (very good) also without electronics and physics.

Development of the digital read-out system for the Cern Alice pixel detector

# **Table of Contents**

|                                                                                                                                                                     | et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1. Intro                                                                                                                                                            | duction: Alice at Cern                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                                                                                     |

|                                                                                                                                                                     | Cern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                        |

| 1.2. 7                                                                                                                                                              | he Large Hadron Collider (LHC)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                     |

|                                                                                                                                                                     | Physics at LHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| 1.3. <i>A</i>                                                                                                                                                       | ALICE - A Large Ion Collider Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                     |

| 1.3.1.                                                                                                                                                              | Purpose of the experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                     |

| 1.3.2.                                                                                                                                                              | The ultra-relativistic heavy-ion collisions                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                     |

| 1.3.3.                                                                                                                                                              | The Design of the ALICE detector                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

| 1.3.4.                                                                                                                                                              | 66 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                        |

| 1.3.5.                                                                                                                                                              | Tracking in ALICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                                                                                                     | Design considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

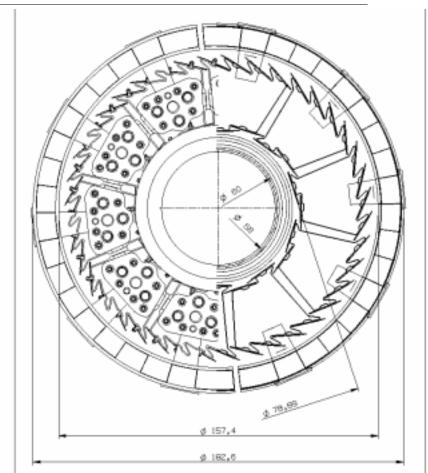

|                                                                                                                                                                     | Layout of the ITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                                                                                                     | Design of the pixel layers                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

|                                                                                                                                                                     | Detector overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                                                                                                     | Front-end electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| 1.4.3.                                                                                                                                                              | Readout and control                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                     |

| 2. The                                                                                                                                                              | Silicon Pixel Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

|                                                                                                                                                                     | Front-end chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

| 2.1.1.                                                                                                                                                              | The Omega2 front-end chip                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                     |

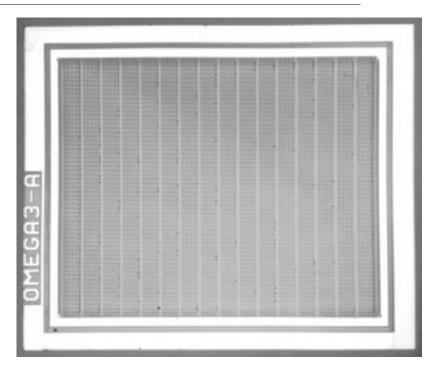

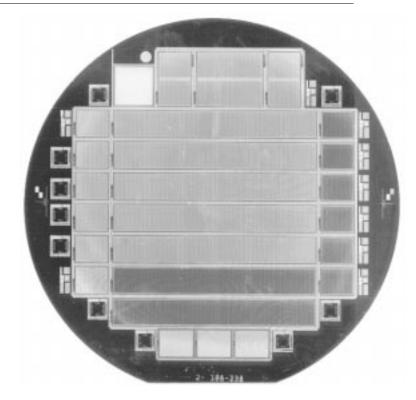

| 2.1.1.<br>2.1.2.                                                                                                                                                    | The Omega2 front-end chip<br>The Omega3 front-end chip                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

|                                                                                                                                                                     | The Omega3 front-end chip                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                                     |

| 2.1.2.<br>2.1.3.                                                                                                                                                    | The Omega3 front-end chip                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                                     |

| 2.1.2.<br>2.1.3.                                                                                                                                                    | The Omega3 front-end chip<br>Gate-all-around CMOS design                                                                                                                                                                                                                                                                                                                                                                                                                              | 34<br>38<br>42                                                                         |

| 2.1.2.<br>2.1.3.<br>2.1.4.                                                                                                                                          | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip                                                                                                                                                                                                                                                                                                                                                                                | 34<br>38<br>42<br>51                                                                   |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.                                                                                                                      | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip                                                                                                                                                                                                                                                                                                                                                                                | 34<br>38<br>42<br>51<br>57                                                             |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2.                                                                                                              | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip                                                                                                                                                                                                                                                                                                                                                   | 34<br>38<br>42<br>51<br>57<br>61                                                       |

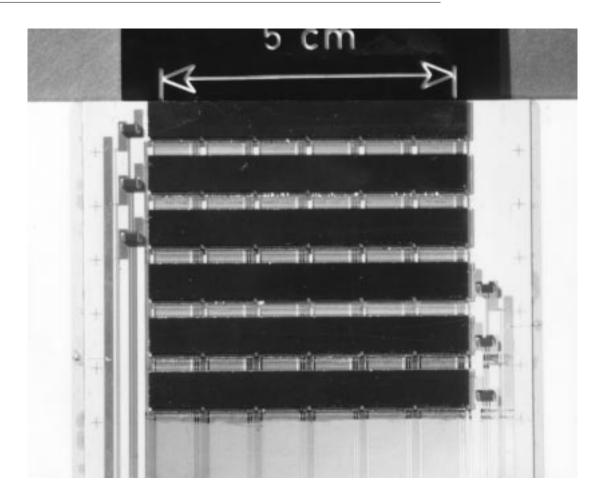

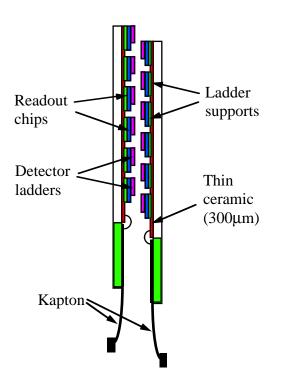

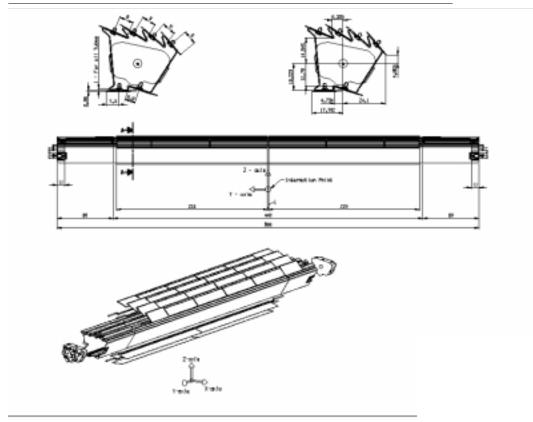

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.                                                                                        | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders                                                                                                                                                                                                                                                               | 34<br>38<br>42<br>51<br>61<br>61<br>65                                                 |

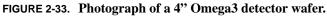

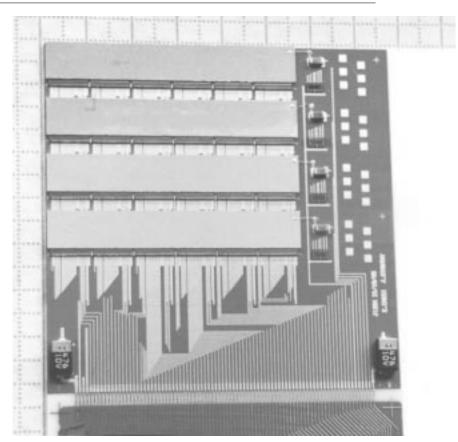

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.                                                                              | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly                                                                                                                                                                                                                                         | 34<br>38<br>42<br>51<br>61<br>61<br>65<br>66                                           |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.                                                                              | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control                                                                                                                                                                                                         | 34<br>42<br>51<br>61<br>61<br>65<br>66<br>69                                           |

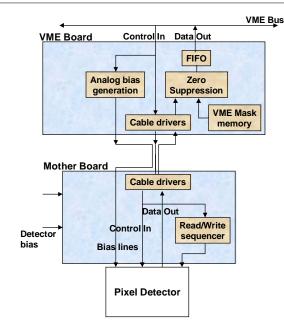

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.                                                                              | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems                                                                                                                                      | 34<br>42<br>51<br>61<br>65<br>66<br>69<br>69                                           |

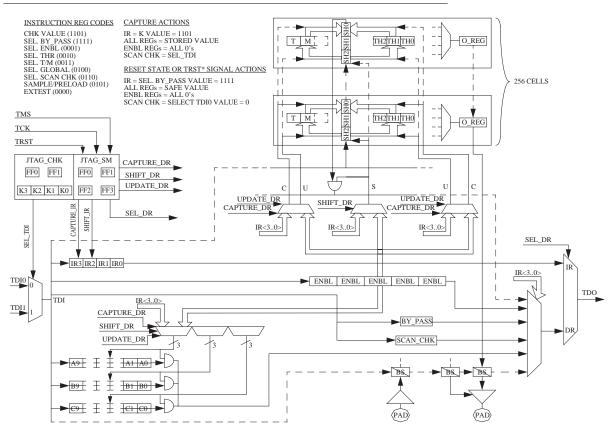

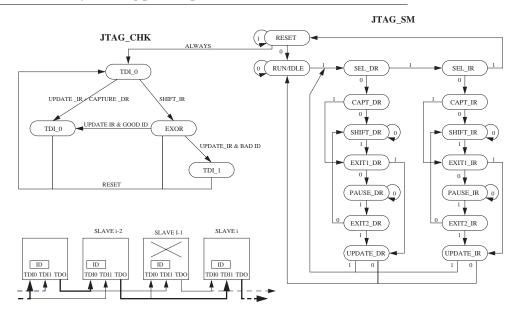

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.                                                          | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control                                                                                                                      | 34<br>38<br>42<br>51<br>61<br>61<br>65<br>66<br>69<br>69<br>74                         |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.<br>2.3.3.                                                | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control<br>Readout logic                                                                                                     | 34<br>38<br>42<br>51<br>61<br>61<br>65<br>66<br>69<br>69<br>69<br>64<br>64             |

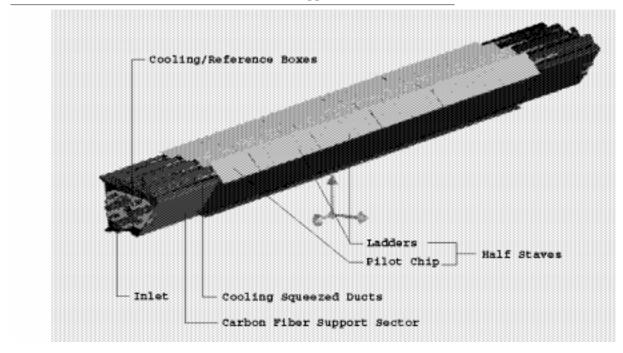

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.<br>2.3.3.<br>2.3.4.                                      | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control<br>Readout logic<br>Assembly, mechanics and cooling                                                                  | 34<br>38<br>42<br>51<br>61<br>65<br>66<br>69<br>69<br>74<br>84<br>90                   |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.<br>2.3.3.<br>2.4. <i>P</i><br>2.4.1.                     | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control<br>Readout logic<br>Assembly, mechanics and cooling<br>Introduction                                                  | 34<br>38<br>42<br>51<br>61<br>61<br>65<br>66<br>69<br>74<br>74<br>84<br>90<br>90       |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.<br>2.3.3.<br>2.3.3.<br>2.4. <i>A</i><br>2.4.1.<br>2.4.2. | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control<br>Readout logic<br>Assembly, mechanics and cooling<br>Introduction<br>Stave assembly                                | 34<br>38<br>42<br>51<br>61<br>65<br>66<br>69<br>69<br>69<br>74<br>84<br>90<br>91       |

| 2.1.2.<br>2.1.3.<br>2.1.4.<br>2.1.5.<br>2.1.6.<br>2.2. [<br>2.2.1.<br>2.2.2.<br>2.2.3.<br>2.3.1.<br>2.3.2.<br>2.3.3.<br>2.4. <i>P</i><br>2.4.1.                     | The Omega3 front-end chip<br>Gate-all-around CMOS design<br>The Alice1Test chip<br>The Alice2Test chip<br>The Alice1 front-end chip<br>Detector modules<br>Omega2 and Omega3 detector ladders<br>ALICE detector ladders<br>Flip-chip assembly<br>Bussing, readout and control<br>Bussing, readout, and control for the Omega2 and Omega3 systems<br>JTAG control<br>Readout logic<br>Assembly, mechanics and cooling<br>Introduction<br>Stave assembly<br>Carbon-Fibre Support Sector | 34<br>38<br>42<br>51<br>61<br>65<br>66<br>69<br>69<br>69<br>74<br>84<br>90<br>91<br>93 |

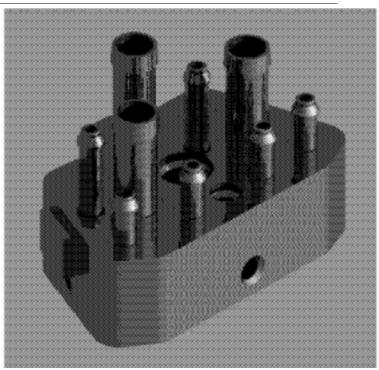

| 2.4.5. Cooling system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

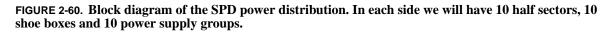

| 2.5. Power distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

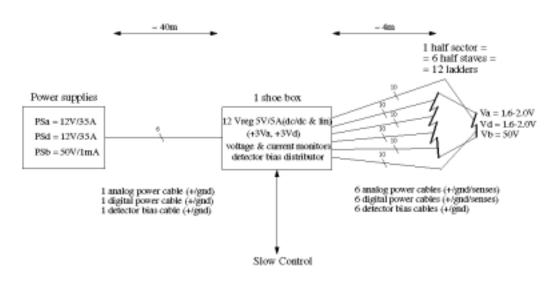

| 3. The Pilot System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                 |

| 3.1. Problem description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                 |

| 3.1.1. Detailed Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                 |

| 3.2. Design of the Pilot System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 3.2.1. Description of the module of Fast Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                 |

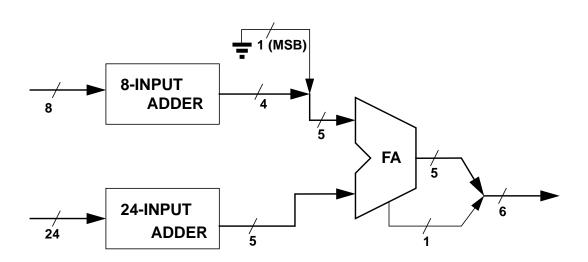

| 3.2.2. Description of the module Adders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                 |

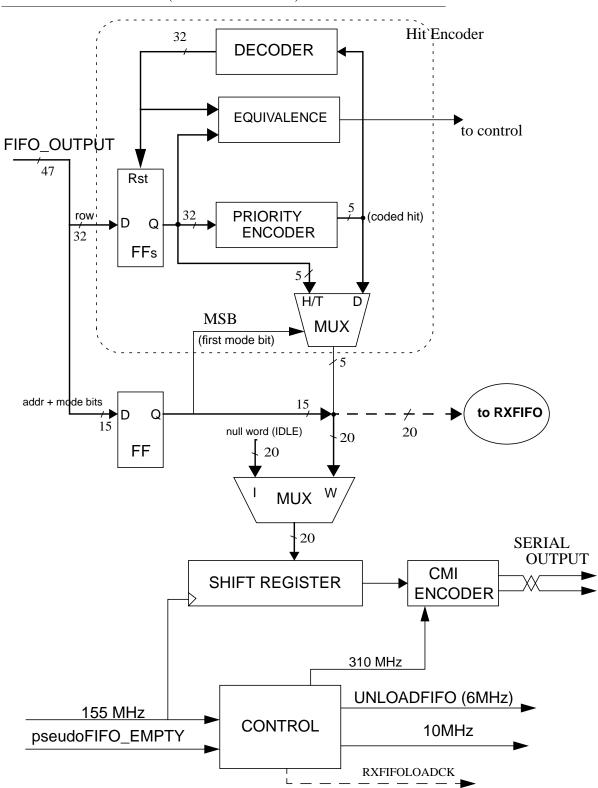

| 3.2.3. Description of the piso device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |

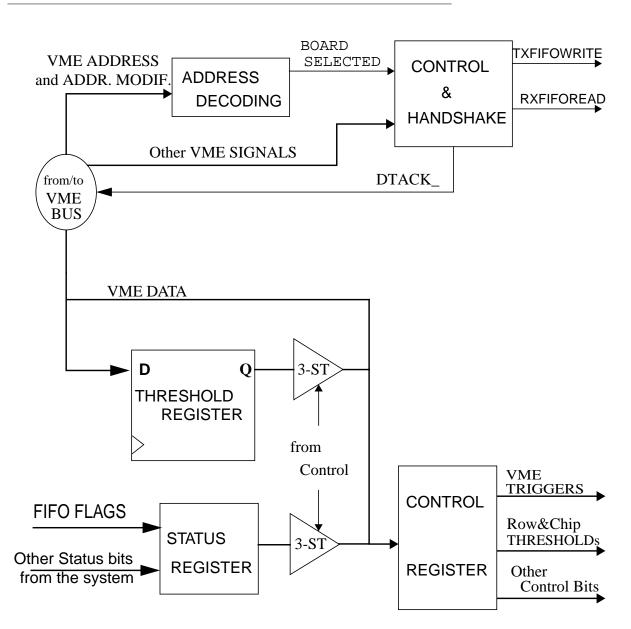

| 3.2.4. The VME Interface Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                 |

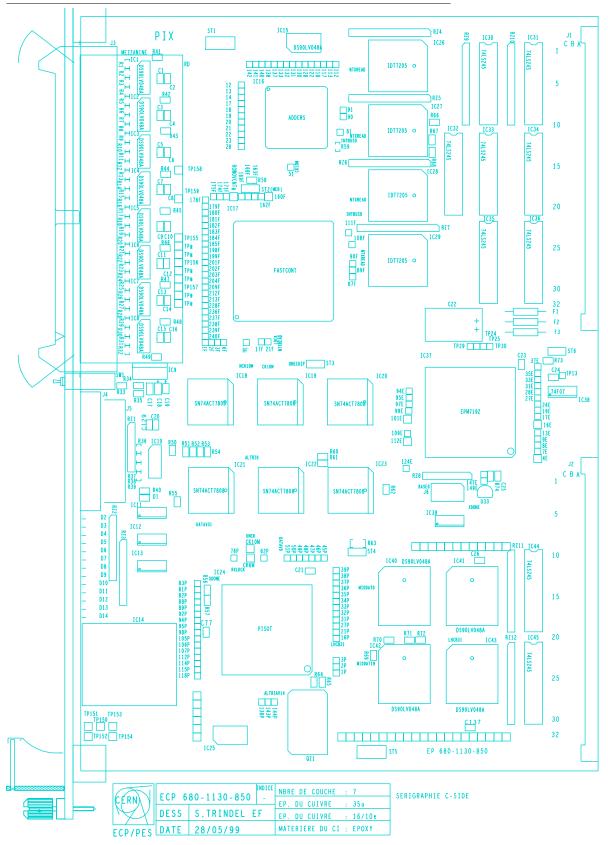

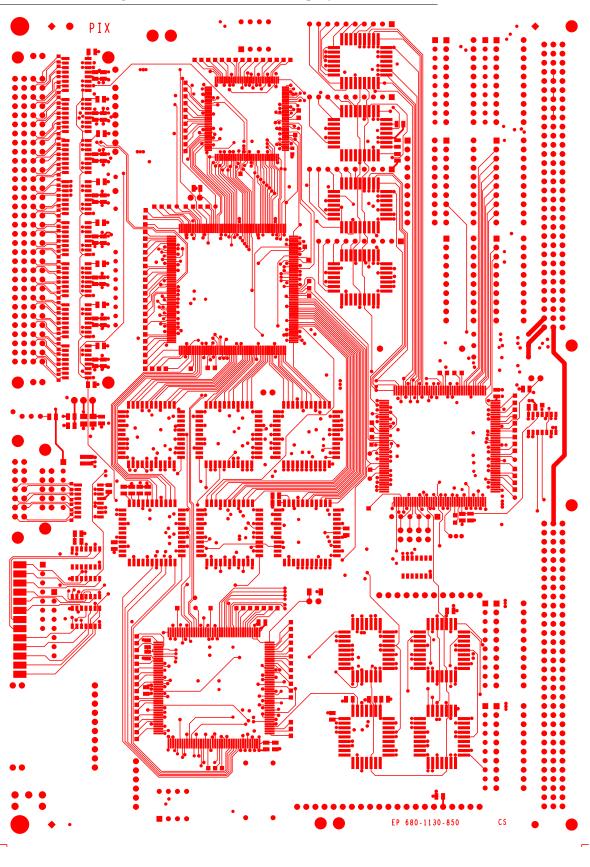

| 3.2.5. Board Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                 |

| 3.3. Design evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 4. Testing of the Pilot System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                 |

| 4.1. Introduction to testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                 |

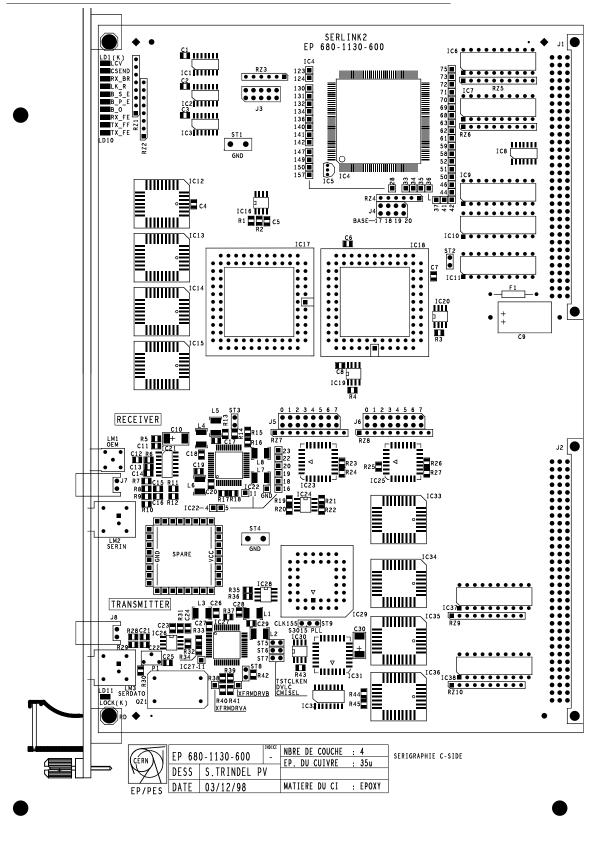

| 4.2. Short Link Test Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                 |

| 4.3. Testing with the VMEbus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                 |

| 4.3.1. PCI-MXI2-VME bridge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                 |

| 4.3.2. VISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 |

| 4.3.3. Software description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                 |

| 4.3.4. Execution of the testing with VME access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 4.4. Testing with Pattern Generator and Logic Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                 |

| 4.5. Conclusions of the testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1/2                                                                                                                                                                                                             |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 5. Design with Programmable Logic Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                 |

| 5. Design with Programmable Logic Devices<br>5.1. User-programmable switch technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>144</b><br>145                                                                                                                                                                                               |

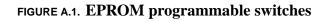

| <b>5. Design with Programmable Logic Devices</b><br>5.1. User-programmable switch technologies<br>5.1.1. EPROM and EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>144</b><br>145<br>146                                                                                                                                                                                        |

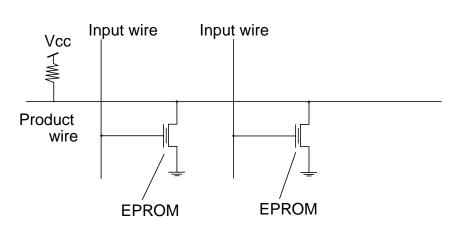

| <ul> <li>5. Design with Programmable Logic Devices</li> <li>5.1. User-programmable switch technologies</li> <li>5.1.1. EPROM and EEPROM</li> <li>5.1.2. Static Memory Technology (SRAM)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>144</b><br>145<br>146<br>147                                                                                                                                                                                 |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148                                                                                                                                                                          |

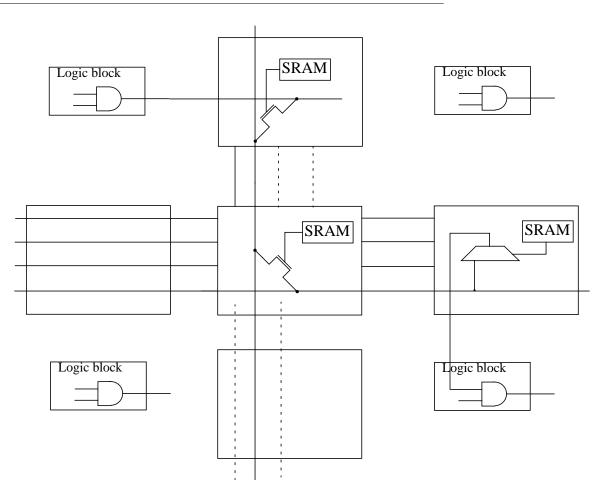

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>148<br>149                                                                                                                                                            |

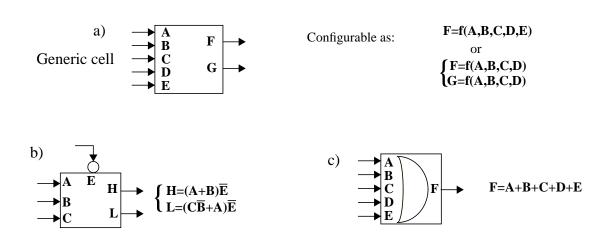

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>147<br>148<br>149<br>149                                                                                                                                                     |

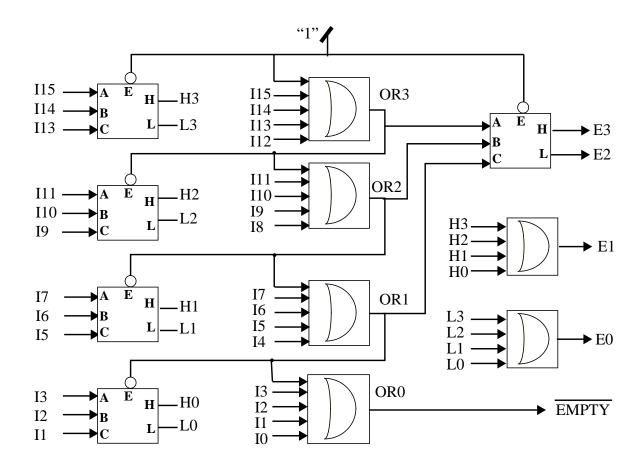

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>148<br>149<br>149<br>149                                                                                                                                              |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>149<br>149<br>149<br>149<br>151                                                                                                                                       |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>149<br>149<br>149<br>149<br>151<br>151                                                                                                                                |

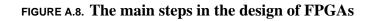

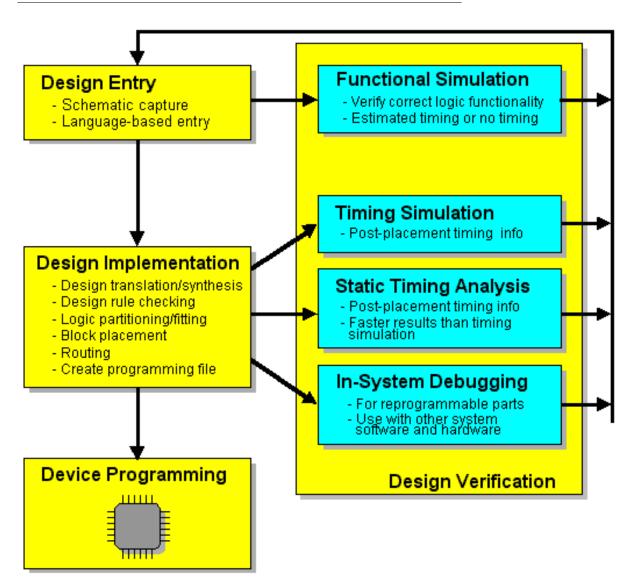

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>149<br>149<br>149<br>149<br>151<br>152<br>156                                                                                                                         |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>148<br>149<br>149<br>149<br>149<br>151<br>151<br>152<br>156                                                                                                                  |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b><br>145<br>146<br>147<br>147<br>148<br>149<br>149<br>149<br>149<br>151<br>152<br>156<br>156<br>156<br>157                                                                                             |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b> 145 146 147 148 149 149 149 149 151 152 156 156 157 158                                                                                                                                              |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b> 145 146 147 148 149 149 149 149 149 151 152 156 156 156 157 158 158                                                                                                                                  |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>144</b> 145 146 147 147 148 149 149 149 151 152 156 156 156 157 158 158 158                                                                                                                                  |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 144         145         146         147         148         149         149         149         151         152         156         157         158         158         160                                     |

| <ul> <li>5. Design with Programmable Logic Devices.</li> <li>5.1. User-programmable switch technologies</li> <li>5.1.1. EPROM and EEPROM.</li> <li>5.1.2. Static Memory Technology (SRAM)</li> <li>5.1.3. Anti-fuse</li> <li>5.1.4. FLASH technology</li> <li>5.2. Families of PLDs</li> <li>5.2.1. SPLD - Simple Programmable Logic Device</li> <li>5.2.2. CPLD - Complex Programmable Logic Device</li> <li>5.2.3. FPGA - Field Programmable Gate Array</li> <li>5.3.1. Design With programmable logic</li> <li>5.3.2. Design Implementation</li> <li>5.3.3. Verification</li> <li>5.3.4. Device Programming</li> <li>5.4. High-speed design techniques</li> <li>5.5. Market overview</li> </ul> | 144         145         146         147         148         149         149         149         149         151         152         156         157         158         158         158         160         164 |

| <ul> <li>5. Design with Programmable Logic Devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 144         145         146         147         148         149         149         149         151         152         156         156         157         158         158         160         164         164 |

## **Abstract**

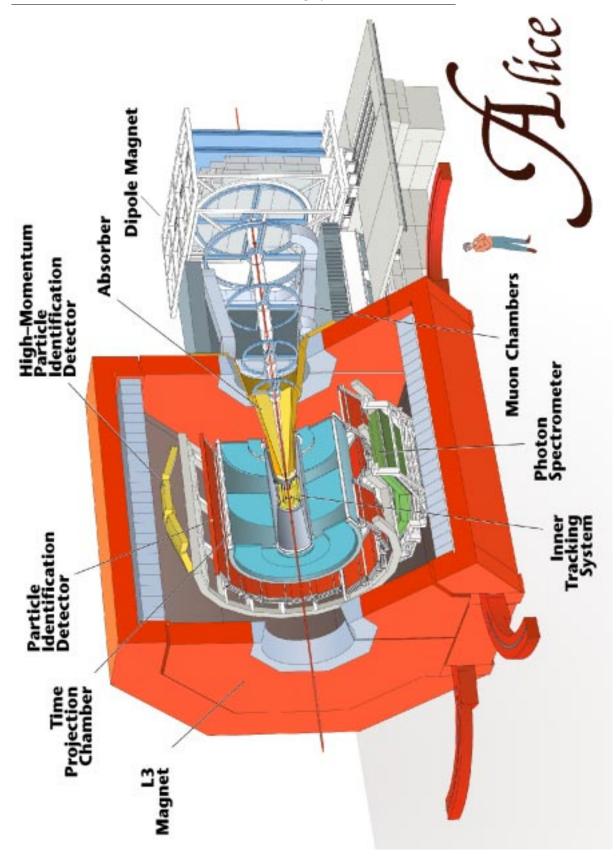

In order to gain new experimental insight at the TeV energy scale, CERN (Geneva) will build the Large Hadron Collider (LHC), a new collider machine operating at a maximum center-of-mass energy of 14 TeV (in the p+/p+ interactions). The accelerator can operate in a heavy ion collision mode achieving a center-of-mass energy of ~5.5 TeV. The experimental environment at LHC is characterized by a high crossing rate of the particle bunches (one every 25 ns for p+/p+) and high levels of radiation. Therefore stringent requirements are imposed on the performance of detectors at LHC. Such a particle physics environment calls for dedicated hardware/software solutions with specific constraints, such as radiation tolerance, limited amount of material and limited power dissipation.

One of the particle physics experiments carried out in LHC is ALICE (A Large Ion Collider Experiment). The ALICE detector will face a very high density of tracks of particles (a multiplicity of 8000 charged particles per unit of rapidity, that implies a maximum density of ~90 tracks/cm<sup>2</sup>) and it comprises an enormous number of electronic channels (~  $2x10^7$ ). Most of these channels (~ $15x10^6$ ) come from the two layers of pixel detector, that produce a data rate of 75 Gbyte/s.

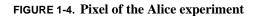

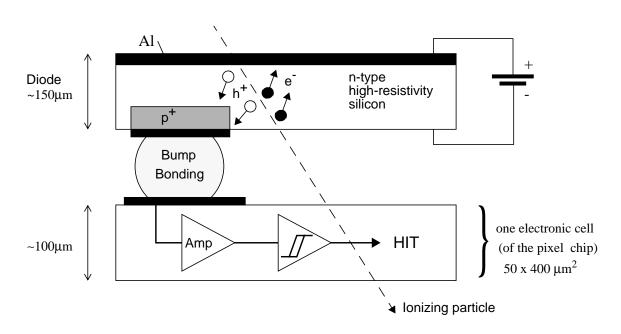

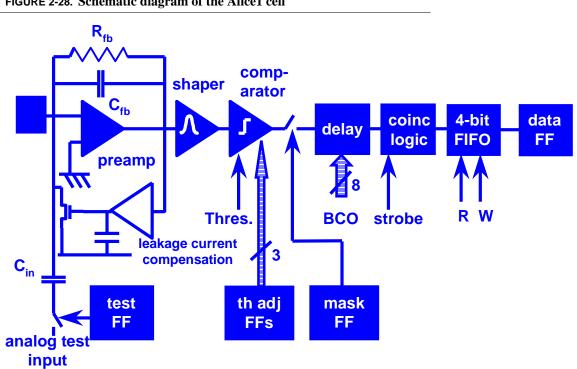

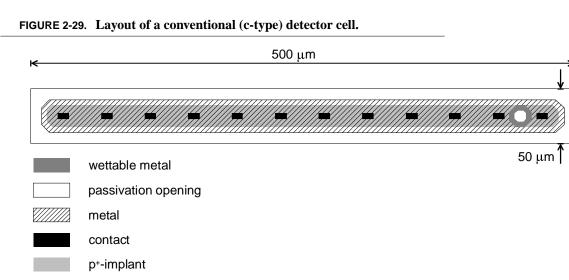

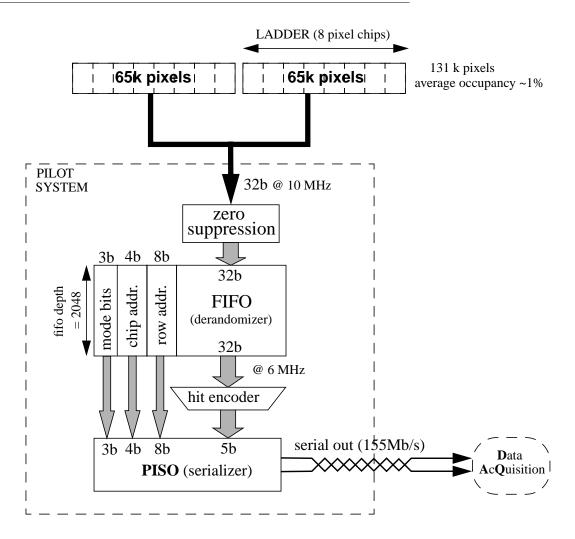

The pixel detector system performs the bi-dimensional high-speed detection of the position of the tracks of ionizing particles, with a spatial resolution of ~ 12 μm. It comprises the silicon detector cells, the mixed front-end electronics (Pixel chip) and a digital module (Pilot system) located in the detector front-end, that accomplishes high level functions, typical of an external Data Acquisition stage.

My main responsibilities were to contribute to the definition of the interfaces between the sub-systems and the design of the Pilot system.

For such a complicated project like the ALICE detector, the definition of the design specifications and of the interfaces between the sub-systems is an important part of the study, in order to guarantee the feasibility of the project. Hence a closed collaboration between designers is often required, including the involvement of a designer in some design issues of the neighboring systems. This is why the pixel chip is extensively presented in chapter 2 (besides several contributions in the measurements discussed in the same chapter).

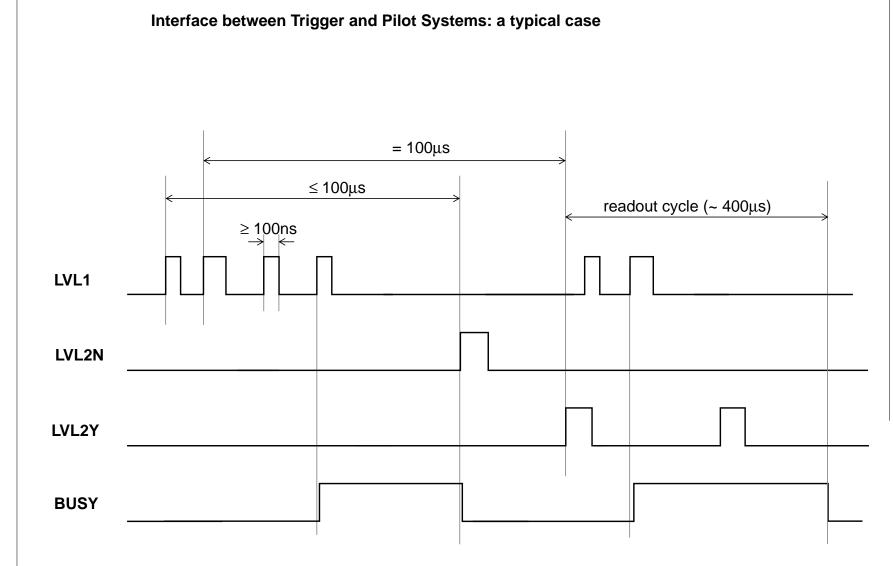

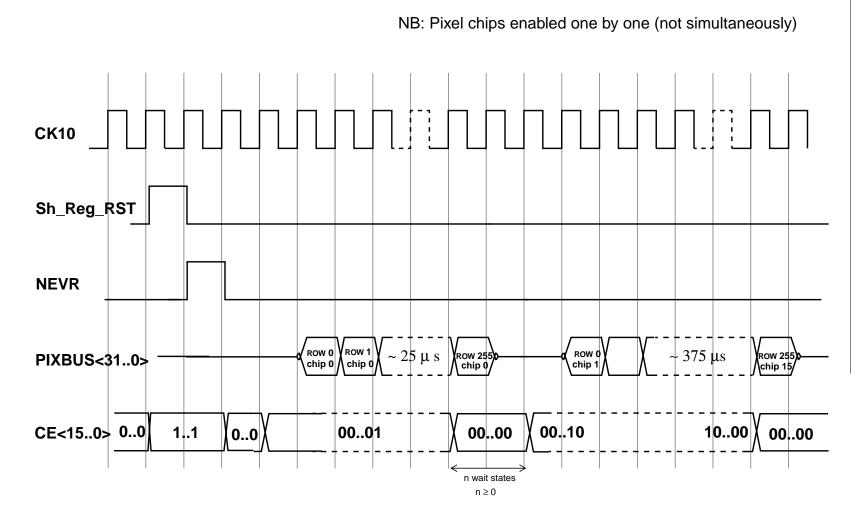

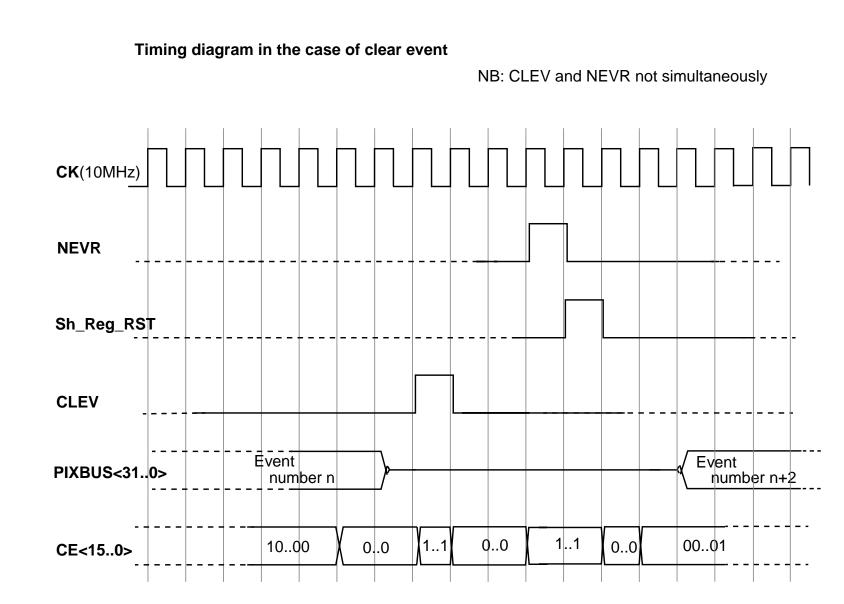

The design of the Pilot system (described in chapter 3) challenges the processing of the huge amount of pixel data (in the experiment there will be 15 million pixels, managed by no more than 240 Pilot modules); moreover, the system plays the role of the master in the pixel fast-control protocol.

The key idea to handle the pixel data is based on the low probability of a pixel cell being hit by a particle, due to the high granularity of the detector. A hit is repre-

sented by a logic value one in the pixel matrix received by the Pilot system: an on-line zero-suppression operation allows the full address encoding of every hit. This guarantees the required data compression rate, keeping a simple and reliable hardware implementation of the algorithm. After the encoding, an output stage running a CMI-encoded serial stream on a 40 meters copper cable transmits the data to the following stage (the router, that will be located outside the detector) at a bit rate of 155 MHz, thus minimizing the number of output links. The proposed architecture allows to reduce the clock frequency in the rest of the system. This avoids the risks and side-effects of the high-frequencies in such a harsh environment. This goal is reached also using state-of-the-art technologies, like the recent LVDS standard, for low-voltage differential binary transmission.

As mentioned above, the interfaces between the detector sub-systems were an important part of the investigations, that are still in progress. As a consequence the design specifications of the single sub-systems are subject to several modifications in order to test and optimize the detector protocols. That is why, during the present stage of the preparation, a flexible implementation of the Pilot logic is required. Hence the system is prototyped on a board, based on programmable logic devices. In spite of the technology used, a 310 MHz clock has been successfully routed inside a programmable logic device.

A dedicated set-up (based on LabView) for the testing of the board has been built, including two new custom boards (a receiver card for the test of the 155 MHz serial link, and a second one to interface the Pilot board with a system for logic testing).

*This set-up (described in chapter 4) allowed to check the correct behavior of the logic, in agreement with the Verilog simulations carried out during the design of the system.*

Once the specifications will be fixed, the final version of the Pilot system for the Alice experiment (supposed to begin in 2005) is foreseen to be on a single chip (ASIC). For the design migration to the ASIC technology, the use of automatic translation tools is under investigation.

In addition, the board implementation already satisfies the requirements of other experiments (so far, the NA6i experiment at CERN-SPS).

## Sommario

Allo scopo di ottenere nuove conoscenze sperimentali a energie dell'ordine dei TeV, il CERN (Ginevra) costruirá LHC (Large Hadron Collider, Grande collisore di adroni), una nuova macchina acceleratrice operante a una energia del centro di massa di 14 TeV (per interazioni  $p^+/p^+$ ). Il collisore potrá funzionare in modalitá ioni pesanti, rag-

giungendo un'energia del centro di massa di ~5.5 TeV. L'ambiente sperimentale di LHC é caratterizzato da un'alta frequenza di transito dei pacchetti di particelle (uno ogni 25 ns per p<sup>+</sup>/p<sup>+</sup>) e da alti livelli di radiazione. Quindi sono imposte caratteristiche stringenti sulle prestazioni dei rivelatori di LHC. Un tale ambiente di fisica delle particelle richiede soluzioni hardware/software dedicate e con vincoli specifici, quali tolleranza alle radiazioni, e con limiti sulla quantitá di materia e sulla potenza dissipata. Uno degli esperimenti realizzati in LHC é ALICE (A Large Ion Collider Experiment). Il relativo rivelatore affronterá un'altissima densitá di traiettorie di particelle (una molte-

plicitá di 8000 particelle cariche per unitá di rapiditá, che implica una densitá massima di ~90 traiettorie/cm<sup>2</sup>) e comprende un enorme numero di canali elettronici (~2x10<sup>7</sup>). La maggior parte di questi canali (~15x10<sup>6</sup>) viene dai due livelli di rivelatore a pixel, che producono un data rate di 75 Gbyte/s.

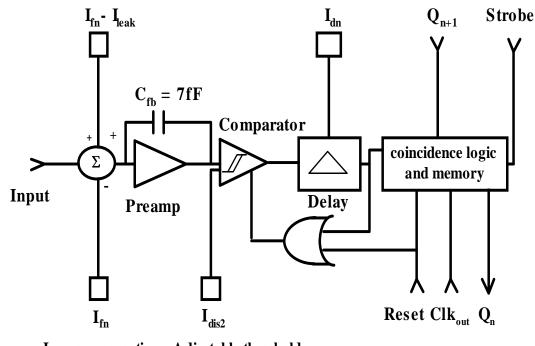

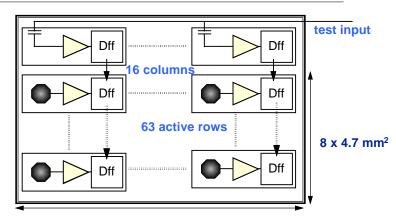

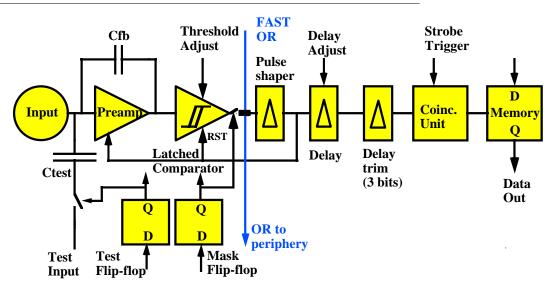

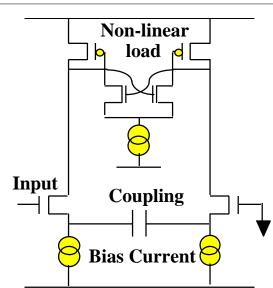

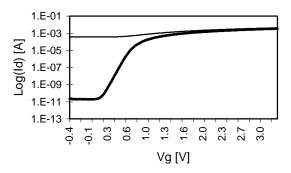

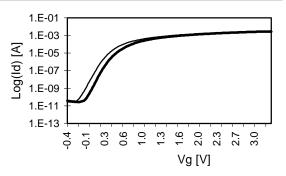

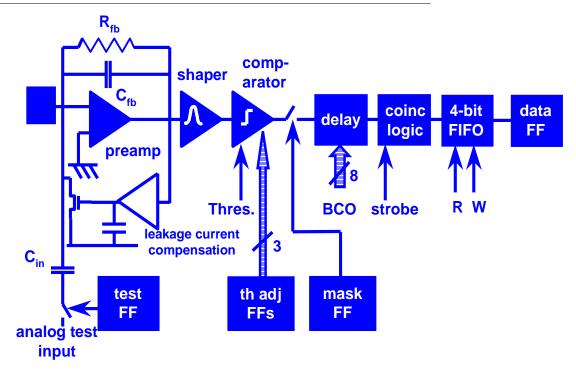

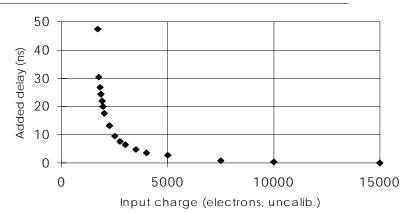

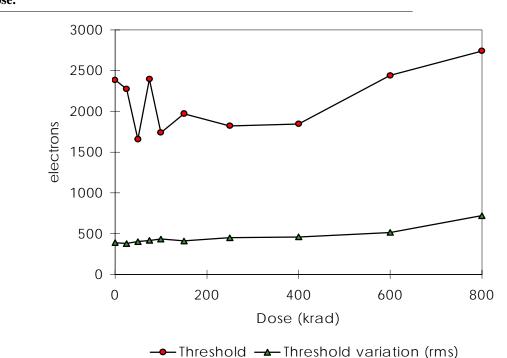

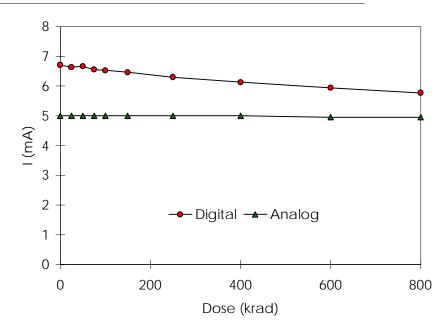

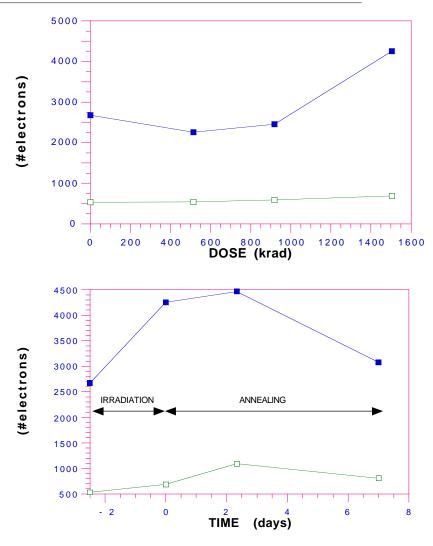

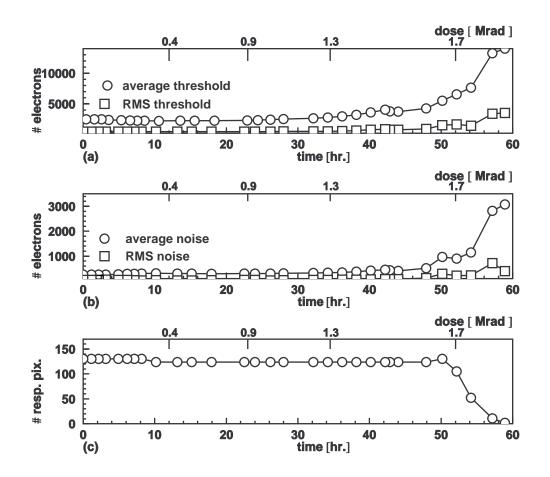

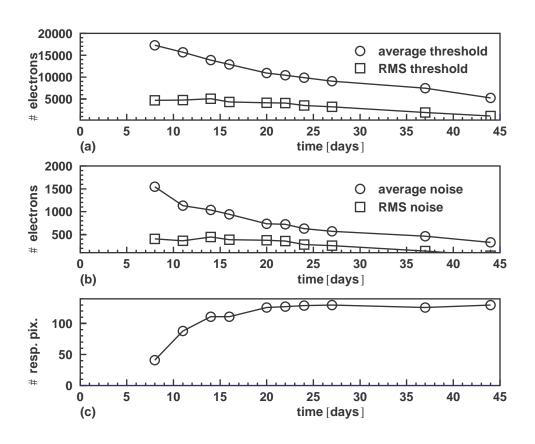

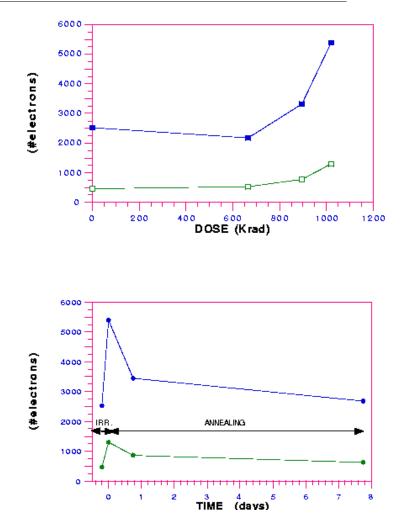

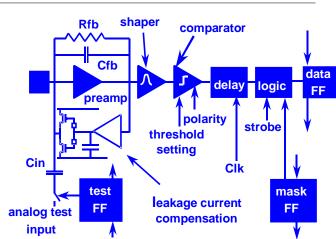

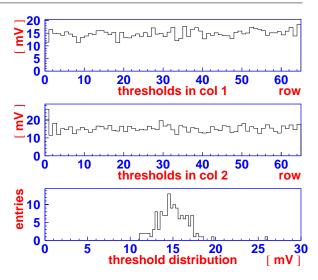

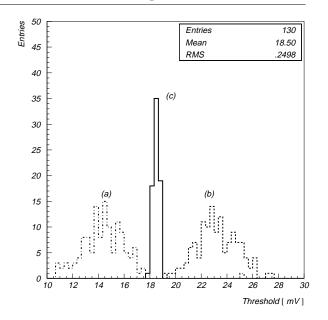

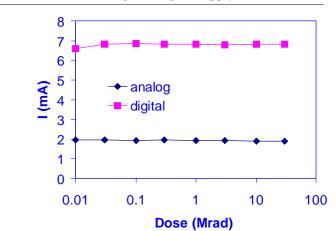

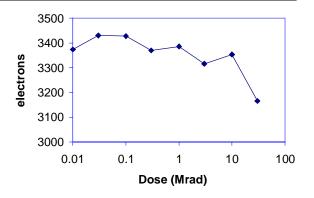

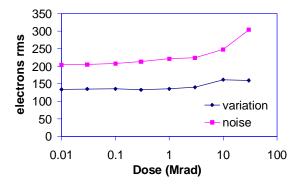

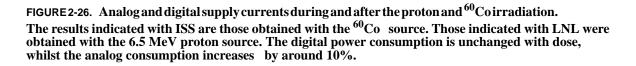

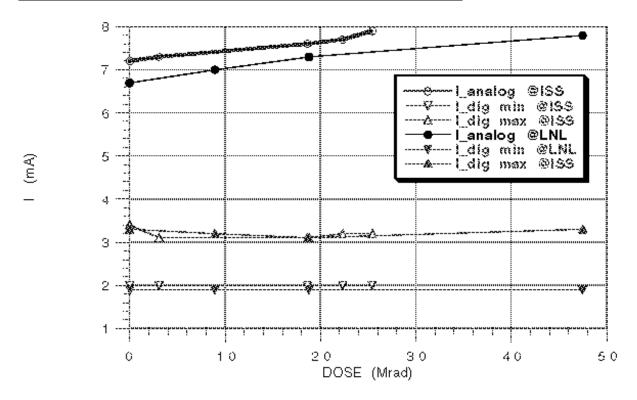

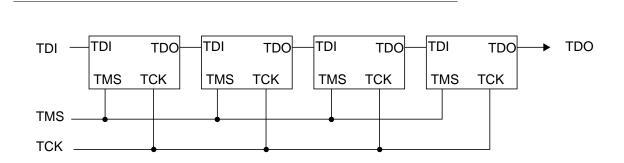

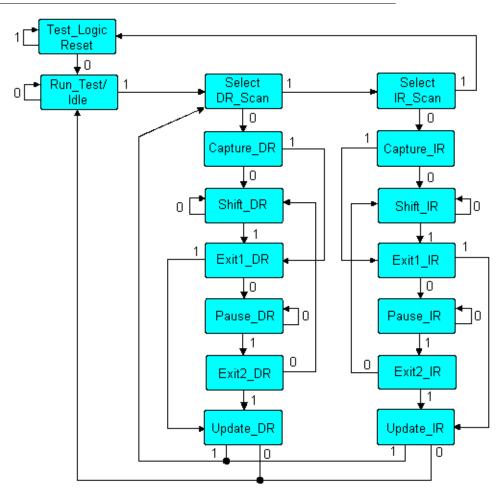

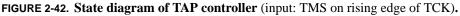

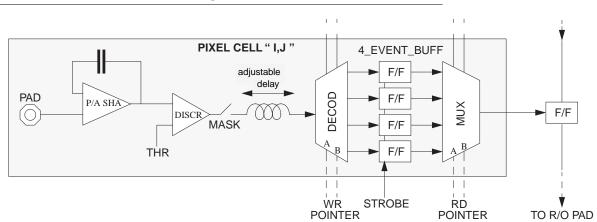

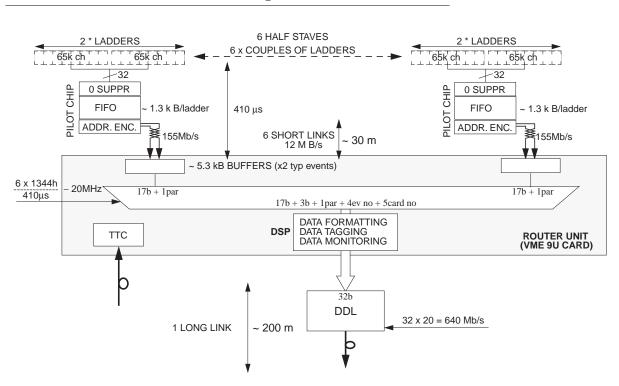

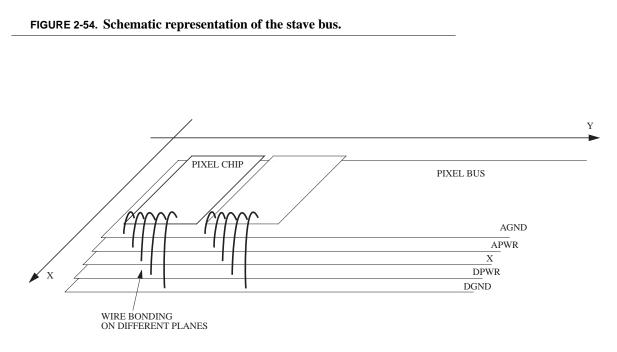

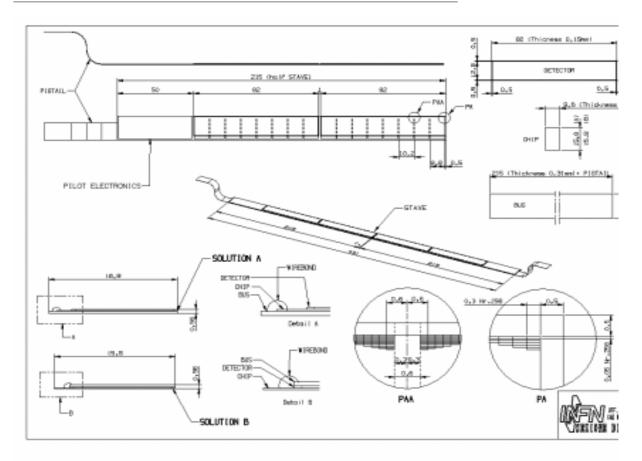

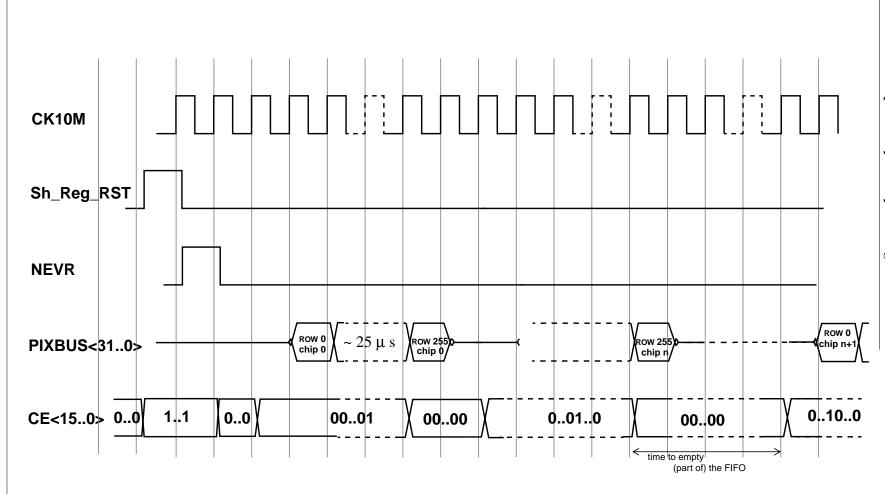

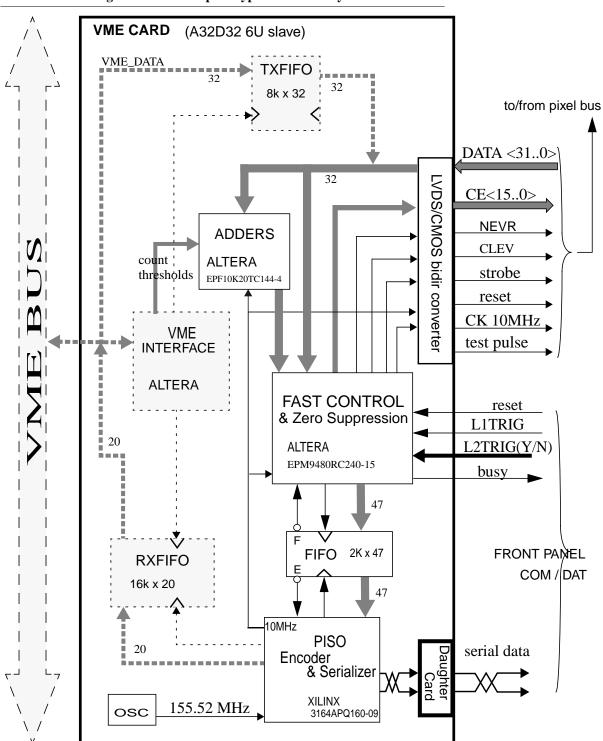

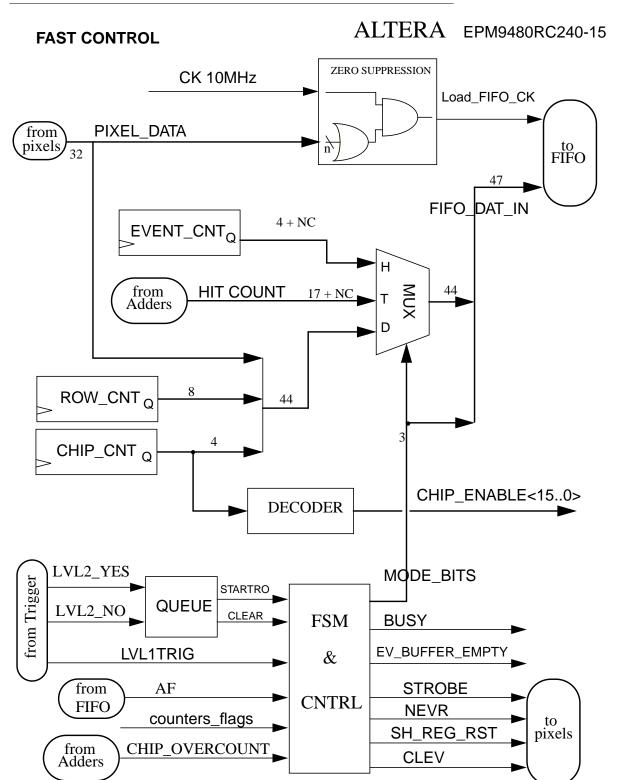

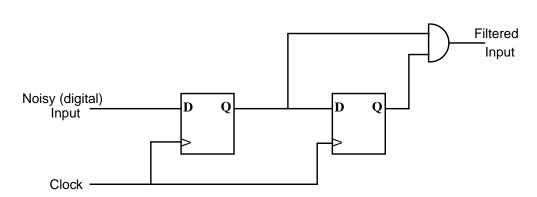

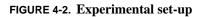

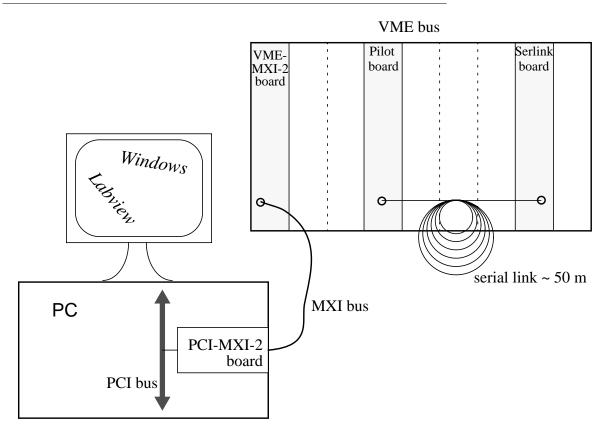

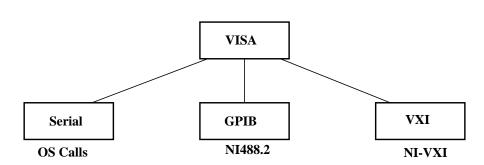

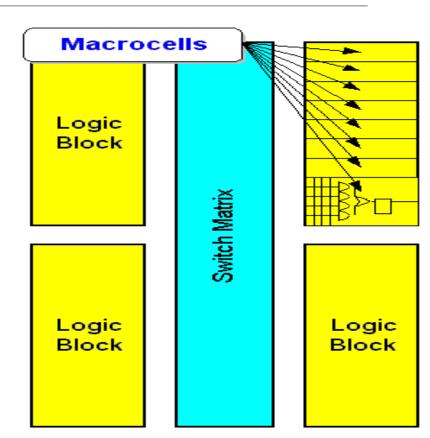

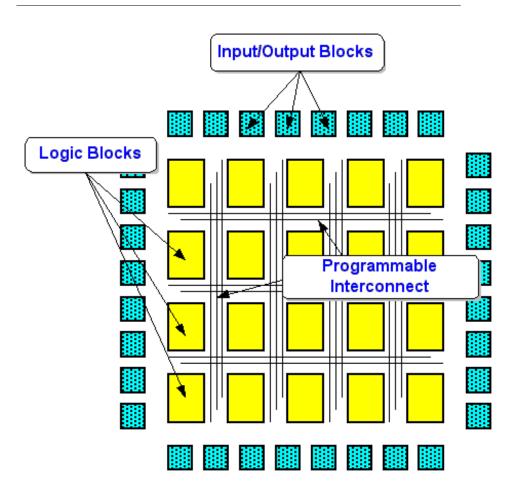

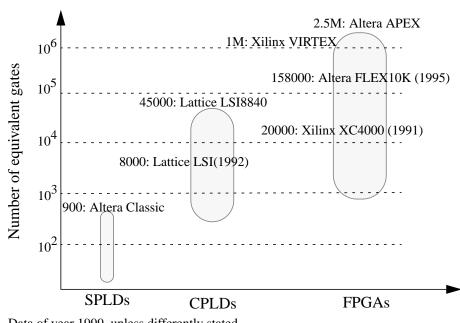

Il rivelatore a pixel rivela i punti di transito delle particelle ionizzanti, in maniera bidimensionale, ad alta velocitá e con una precisione di ~12µm. Esso comprende le celle di rivelatore al silicio, l'elettronica di front-end analogico-digitale (Pixel chip) e un modulo digitale (Pilot system) posto nel front-end del rivelatore, che realizza funzioni di alto livello, tipiche di uno stadio esterno di acquisizione dati. Le mie responsabilitá principali sono state un contributo alla definizione delle interfacce tra sottosistemi e il disegno del Pilot system.