# Characterization of new hybrid pixel module concepts for the **ATLAS Insertable B-Layer upgrade**

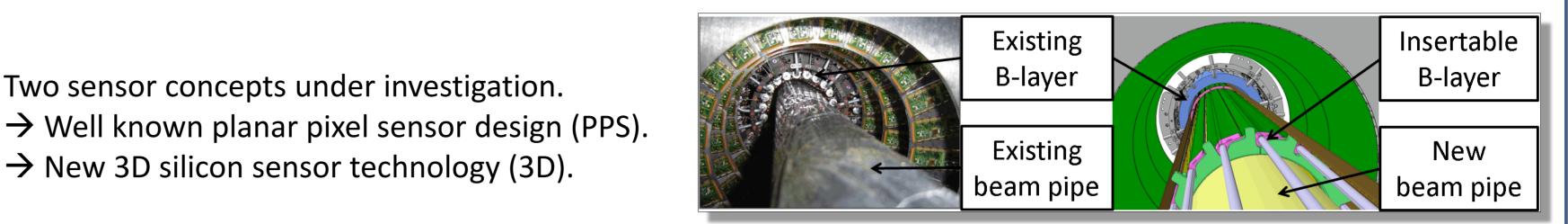

Two sensor concepts under investigation.

$\rightarrow$  New 3D silicon sensor technology (3D).

## **ATLAS IBL Upgrade**

New Insertable B-Layer Upgrade installation planned for 2013 LHC shutdown.

$\rightarrow$  Recover from eventual failures in present pixel system, esp. B-Layer.

$\rightarrow$  Ensure excellent tracking, vertexing and b-tagging performance during LHC phase I.

$\rightarrow$  Add to robustness of tracking with high luminosity pile-up.

IBL design values: Peak luminosity 2-3x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, integrated luminosity 700 fb<sup>-1</sup>, fluence 5x10<sup>15</sup> neq cm<sup>-2</sup>, dose 250 MRad.

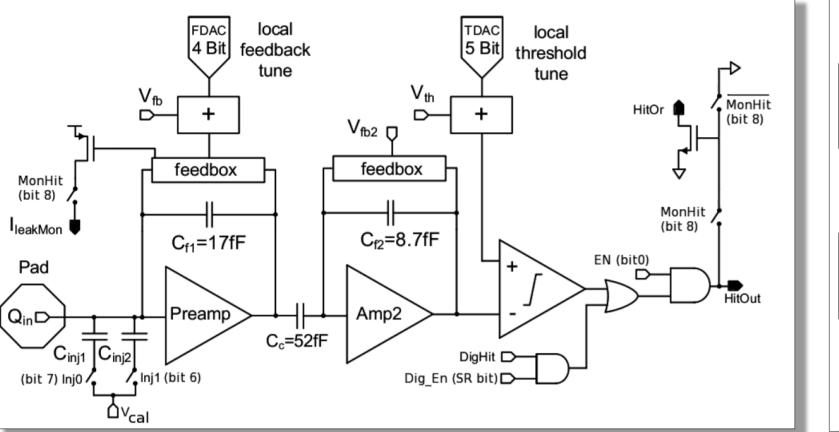

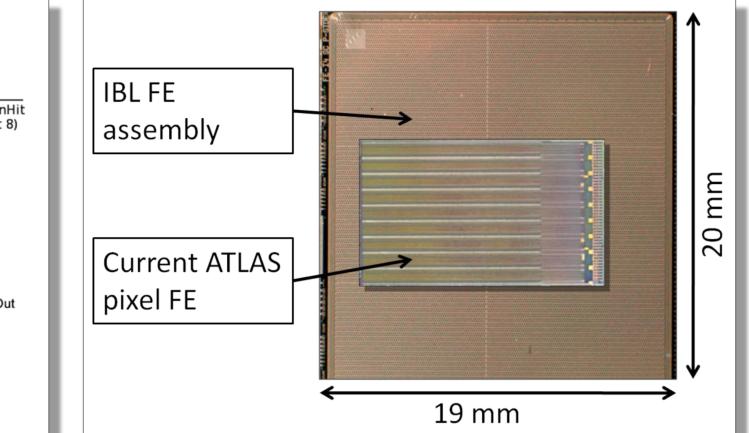

### **FE-I4 IC Architecture** Technology:

CMOS 130 nm feature size process and thin gate oxide transistors for radiation hardness. **Geographical Design:**

Large IC (20.2x18.8 mm<sup>2</sup>) enables simplified module concept.

• Active area holding 80x336 pixels Periphery with ~2mm height  $\rightarrow$  Active / Inactive area fraction is 90%. Analog Front End:

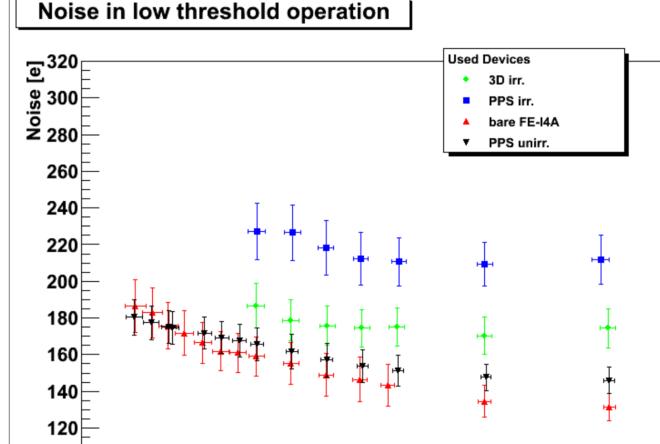

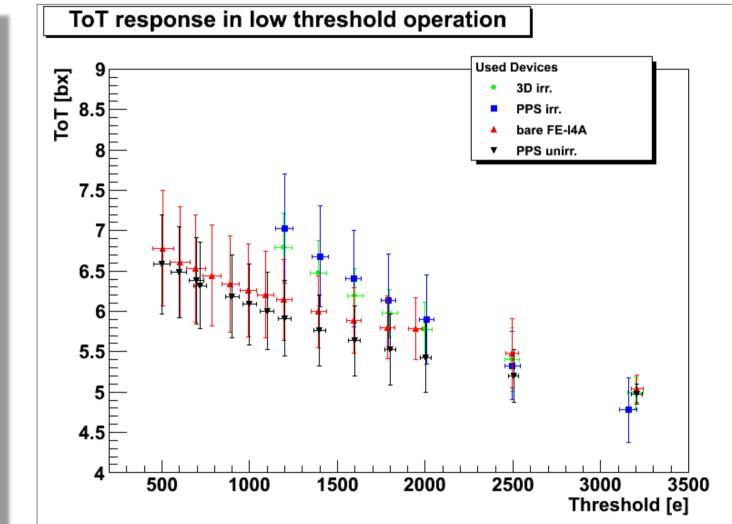

## **Low Threshold Operation**

#### 4-pixel digital region:

Transport of hits to periphery is the limiting factor for high hit occupancies in FE-I3. New digital hit processing architecture developed for FE-I4:

• Hits stored on pixel level. • Single LV1 counter for 4 analog pixels mirrors clustered nature of real hits.

#### **Pixel flavours:**

Different flavours of the pixel cell has been implemented:

Another feedback capacitor in 19 out of 80 columns, low power discriminator in 2 columns and 15 columns with SEU hard pixel memory cells.

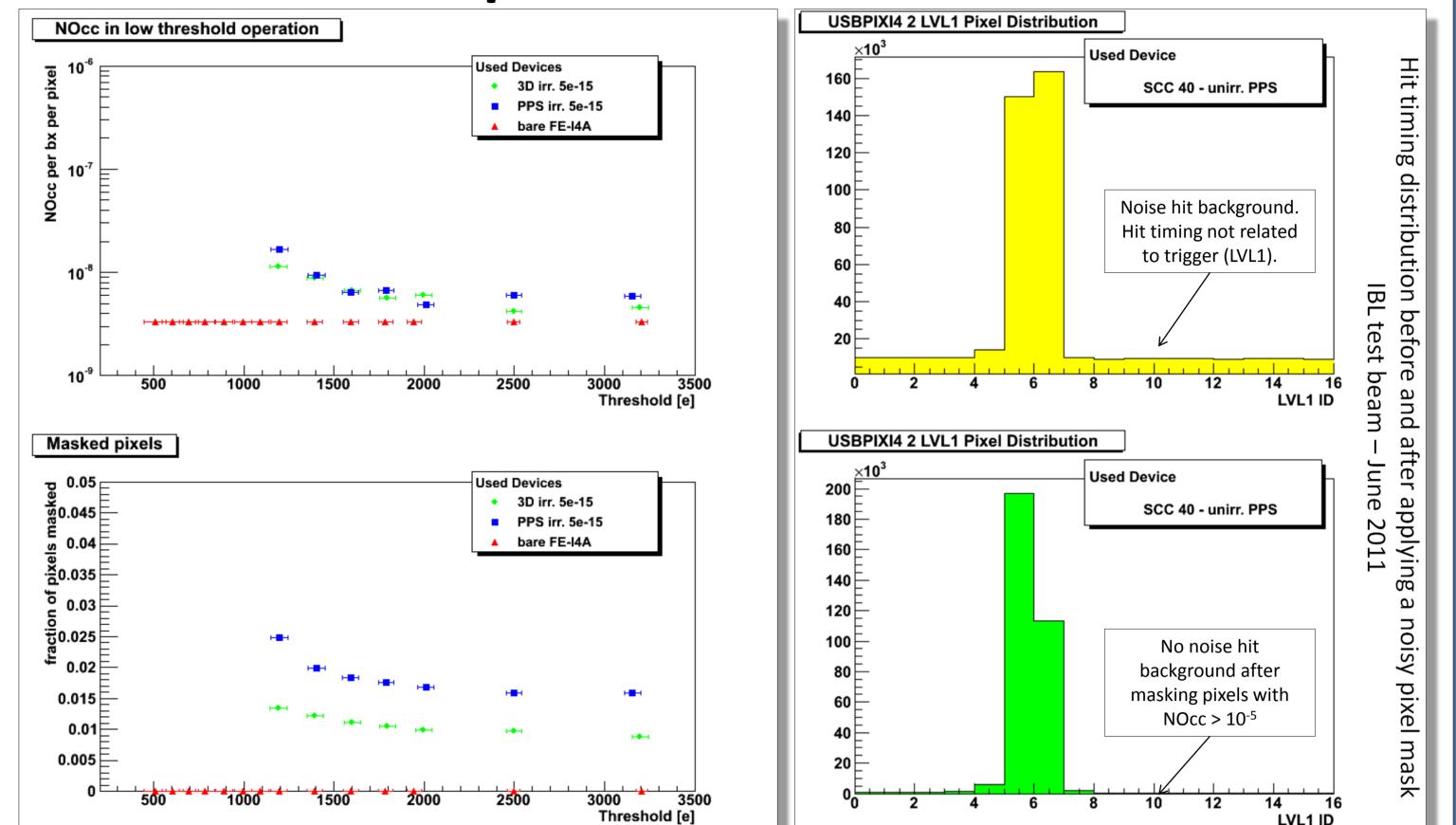

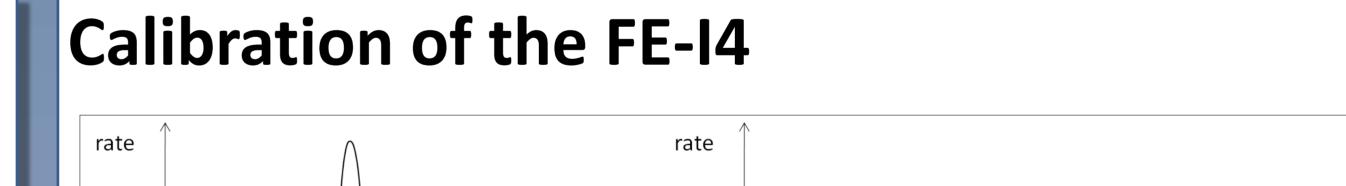

NOcc: Noise hit probability per pixel within 25ns; NOcc rises below threshold of 1200e. 1-2% dead pixel fraction independent from sensor technology seen in electronic devices irradiated to fluence: 5x10<sup>15</sup>neq. & FE dose >> 800 Mrad (300 Mrad design TID)

**FE-I4A:** First full scale prototype chip with this architecture.  $\rightarrow$  FE-I4B will be the experiment chip for IBL.

## IC and Module Performance

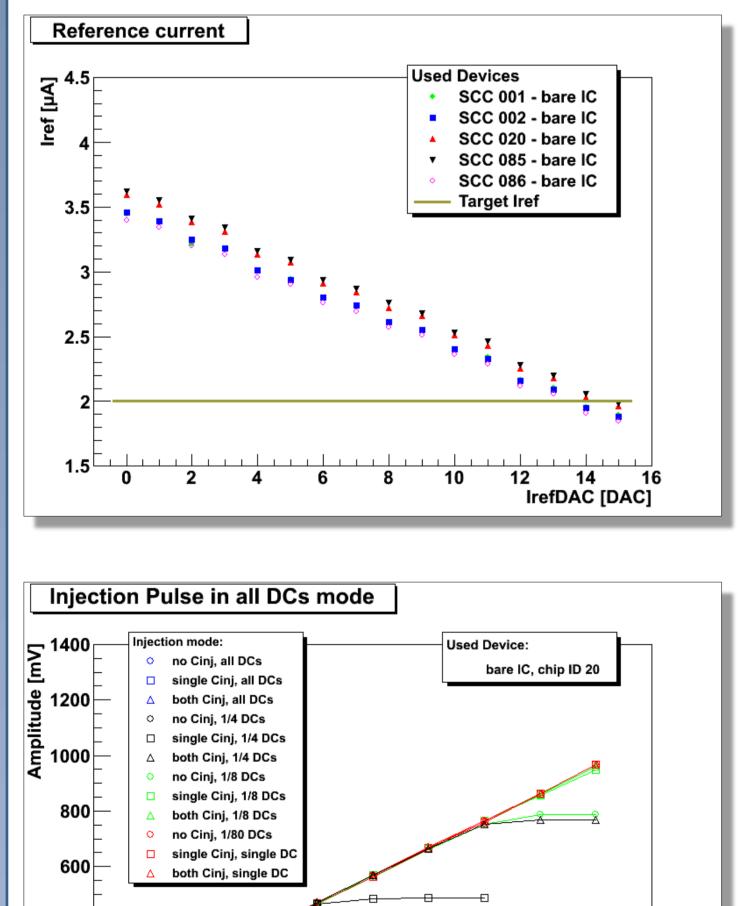

• Reference current DAC needs to be adjusted on every chip to design value of Iref = 2  $\mu$ A.

• DAC setting can be burned to EFUSE register.

Read and Memory Managmen

ency counter & Trigger Managme

ToT Counter and ToT Memory managment

• 2µA Iref on edge of dynamic DAC range.

$\rightarrow$  Dynamic DAC range will centered in FE-I4B.

Threshold Distribution

$\rightarrow$

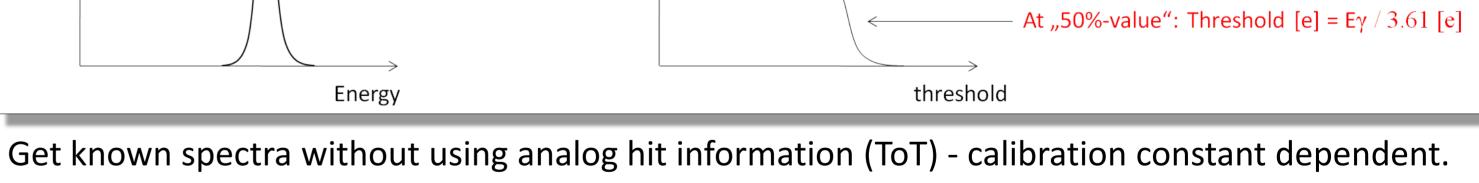

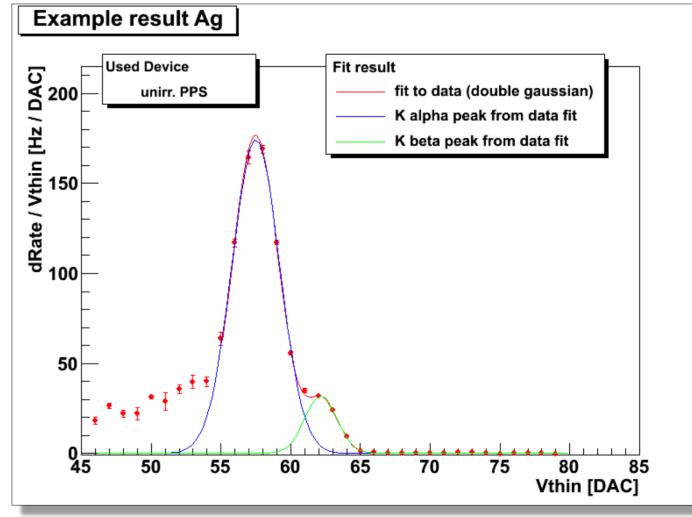

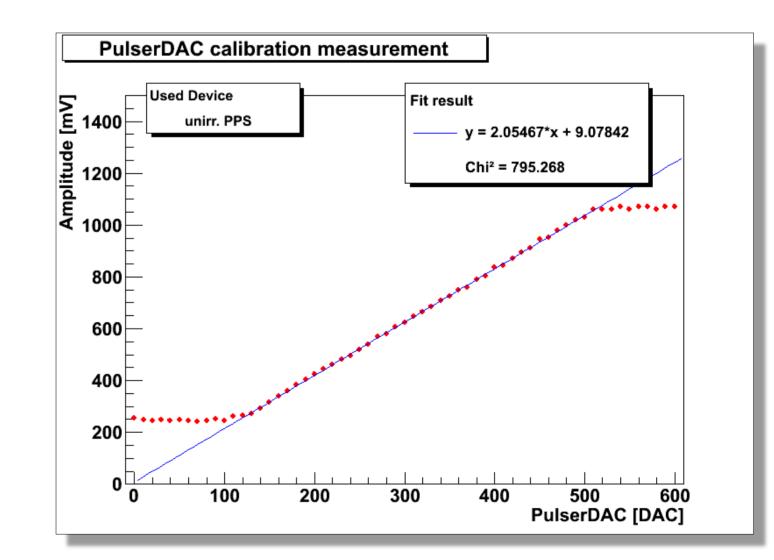

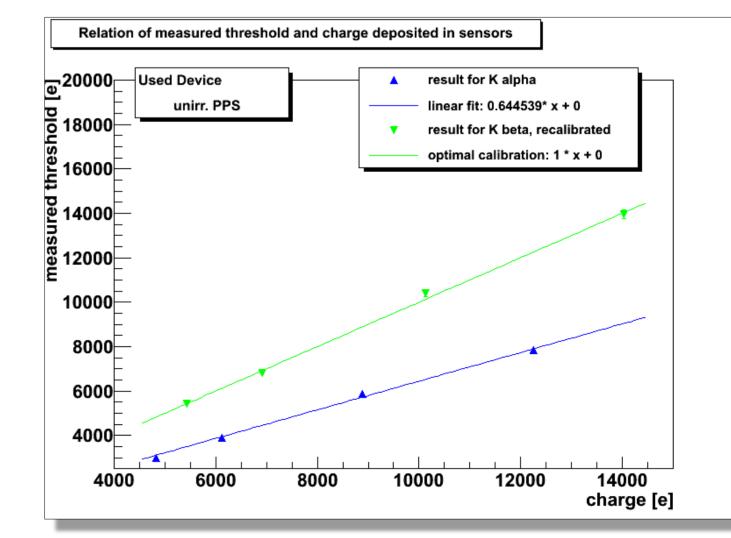

$\rightarrow$  Measure rate and change threshold DAC, measure threshold at peak DAC position.

$\rightarrow$  Calculate injection capacitance.

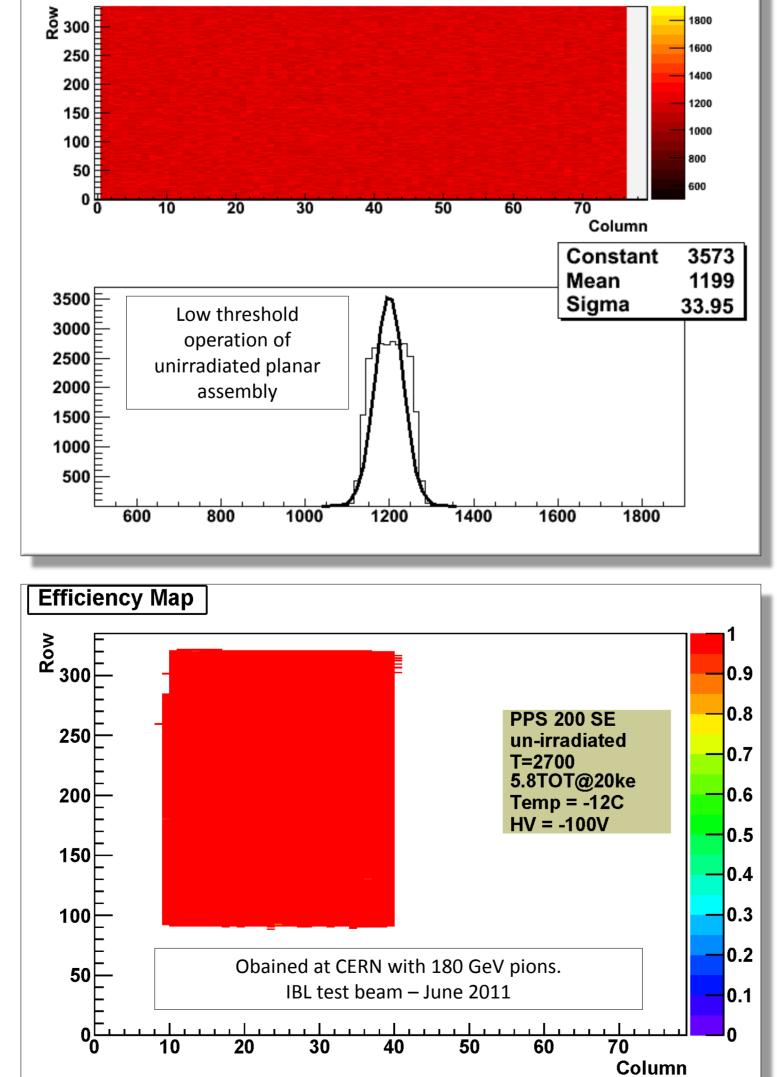

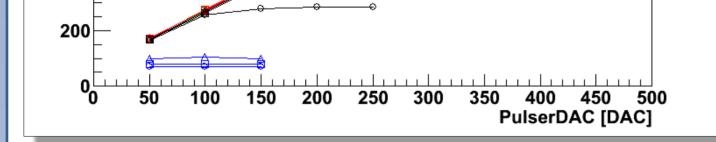

Saturation of pulse amplitude. Reason known and will be fixed in FE-I4B. Pulse injection possible in 1/8 and single DC mode.

IBL test beam conditions (IBL test beam – June 2011)

FE-I4A based prototype modules successfully operated at thresholds ~1600 electrons in

$\rightarrow$  decreases scan

speed.

400

- **Result:**

- C<sub>ini</sub> = 6.7 fF, 1.13 times larger then simulated (5.7 fF)

- Expected uncertainty of order 10%. • Independent measurement confirmed this result.

- $\rightarrow$  Absolut discriminator threshold is known with 10% accuracy.

Malte Backhaus on behalf of the ATLAS IBL collaboration, University of Bonn

9th International Conference on POSITION SENSITIVE DETECTORS, September 11 – 16, 2011 in Aberystwyth, UK

Großgeräte der physikalischen Grundlagenforschung