# Development of Digital Readout Electronics for the CMS Tracker

**Emlyn Peter Corrin**

High Energy Physics Imperial College London Prince Consort Road London SW7 2BW

Thesis submitted to the University of London for the degree of Doctor of Philosophy

November 2002

## Abstract

The Compact Muon Solenoid (CMS) is a general-purpose detector, based at CERN in Switzerland, designed to look for new physics in high-energy protonproton collisions provided by the Large Hadron Collider. The CMS tracker has 10 million readout channels being sampled at a rate of 40 MHz, then read out at up to 100 kHz, generating huge volumes of data; it is essential that the system can handle these rates without any of the data being lost or corrupted. The CMS tracker FED processes the data, removing pedestal and common mode-noise, and then performing hit and cluster finding. Strips below threshold are discarded, resulting in a significant reduction in data size. These zero suppressed data are stored in a buffer before being sent to the DAQ. The processing on the FEDs is done using FPGAs. Programmable logic was chosen over custom ASICs because of the lower cost, faster design and verification process, and the ability to easily upgrade the firmware at a later date.

This thesis is concerned with the digital readout electronics for the CMS tracker, working on the development of the FED, and verifying that it will meet the requirements of the detector. Firmware was developed for the back-end FPGA of the FED, implementing the CMS-wide common data format. Each event is wrapped in a header/trailer containing information such as the trigger number, bunch-crossing number and error-detection information. The firmware was developed in VHDL, and will be incorporated into the back-end FPGA of the FED, both in the tracker, and in the other subdetectors.

A study was performed, looking into the flow of data and buffer levels in the FED. A program was written in C++ that models the behaviour of the FED buffers. It was shown that during normal operation the FED can handle occupancies of up to 4 % with 100 kHz random triggers, assuming a sustainable output rate of 200 Mbyte/s. Even when the trigger rate was increased to its maximum of 140 kHz, the FED buffers did not overflow as long as the occupancy remained below 2.5 %. These results confirmed that the FED buffers should never overflow in normal operating conditions.

## Acknowledgements

I would like to thank everyone in the High Energy Physics group for their help and support during my three years there. In particular Geoff Hall for his supervision and guidance, Costas Foudas for his help and for spending so much time proofreading my thesis, and Peter Dornan for letting me work with the group. Thanks also to John Coughlan, Rob Halsall, Bill Haynes, Peter Sharp, and Mike Johnson at RAL. I would also like to thank the Particle Physics and Astronomy Research Council (PPARC) and the Rutherford Appleton Laboratory (RAL) for funding my project.

I would especially like to thank Greg, Mark, Barry, Jonni, Etam, Rob, and Matt for the great atmosphere both in the lab and also over a coffee or a pint. Above all I would like to thank my girlfriend Sandra for her help and moral support while writing my thesis. Thanks also to my grandmother Win, my sister Naomi, my mum Marie-Pierre, Laurent, and all the rest of my family.

I dedicate this thesis to my dad, Ian, and my grandfather, George, for inspiring me towards an inquisitive mind.

## Contents

| Abstract   |                                   | 2  |

|------------|-----------------------------------|----|

|            | lgements                          |    |

|            |                                   |    |

|            | ires                              |    |

| e          | les                               |    |

|            |                                   |    |

| -          | Introduction                      |    |

| 1.1 T      | The Large Hadron Collider (LHC)   | 15 |

|            | hysics at the LHC                 |    |

| 1.2.1      | The Higgs                         | 16 |

| 1.2.2      | CP Violation                      |    |

| 1.2.3      | Supersymmetry                     |    |

| 1.3 T      | The Compact Muon Solenoid (CMS)   | 19 |

| 1.3.1      | The Magnet                        | 20 |

| 1.3.2      | The Tracker                       |    |

| 1.3.3      | The Electronic Calorimeter (ECAL) | 24 |

| 1.3.4      | The Hadronic Calorimeter (HCAL)   | 25 |

| 1.3.5      | The Muon Detectors                |    |

| 1.3.6      | The Trigger                       |    |

| 1.4 S      | ummary                            | 29 |

| Chapter 2: | Field Programmable Devices        |    |

| 2.1 D      | Digital Logic                     |    |

| 2.1.1      | Combinatorial Logic               |    |

| 2.1.2      | Sequential Logic                  |    |

| 2.2 P      | rogrammable Logic                 |    |

| 2.3 H      | listory of Programmable Logic     |    |

| 2.3.1      | The PROM                          |    |

| 2.3.2      | The PLA and PAL                   |    |

| 2.3.3      | The CPLD                          |    |

| 2.3.4      | The FPGA                          |    |

### Contents

| 2.4     | Memory Technolog    | y44                   | 0 |

|---------|---------------------|-----------------------|---|

| 2.4     | 1 Fuses and Anti    | fuses40               | 0 |

| 2.4     | 2 The EPROM a       | nd EEPROM4            | 1 |

| 2.4     | 3 SRAM              |                       | 2 |

| 2.5     | The Xilinx Virtex-I | I Range of FPGAs4     | 3 |

| 2.5     | 1 Logic Blocks      | 4                     | 5 |

| 2.5     | 2 I/O Blocks        | 4'                    | 7 |

| 2.5     | 3 Routing Resou     | rces                  | 9 |

| 2.6     | The Design Process  |                       | 0 |

| 2.6     | 1 Design Entry      |                       | 0 |

| 2.6     | 2 Verilog           |                       | 2 |

| 2.6     | 3 VHDL              |                       | 2 |

| 2.6     | 4 Simulation and    | Synthesis             | 4 |

| 2.6     | 5 Device Program    | nming54               | 4 |

| 2.7     | Summary             |                       | 6 |

| Chapter | 3: The CMS Trac     | ker Readout System    | 7 |

| 3.1     | Overview            |                       | 7 |

| 3.2     | The Silicon Detecto | rs5                   | 8 |

| 3.3     | The APV Readout (   | Chip59                | 9 |

| 3.3     | 1 Preamplifier      |                       | 1 |

| 3.3     | 2 Shaping Filter.   |                       | 1 |

| 3.3     | 3 Pipeline and Fl   | IFO6                  | 1 |

| 3.3     | 4 APSP              |                       | 1 |

| 3.3     | 5 Analogue Mult     | tiplexer6             | 3 |

| 3.3     | 6 Slow Control      |                       | 4 |

| 3.4     | The APVMUX          |                       | 5 |

| 3.5     | The Optical Link    |                       | 5 |

| 3.6     | The Front-End Driv  | er60                  | 6 |

| 3.7     | The S-LINK64        |                       | 7 |

| 3.8     | The DAQ             |                       | 7 |

| 3.9     | Control and Monito  | ring6                 | 8 |

| 3.9     | 1 Timing, Trigge    | er and Control (TTC)6 | 8 |

### Contents

| 3.9.    | .2  | The Tracker Control System (TCS)               | 69  |

|---------|-----|------------------------------------------------|-----|

| 3.10    | Sun | nmary                                          | 69  |

| Chapter | 4:  | The Front-End Driver                           | 70  |

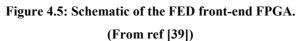

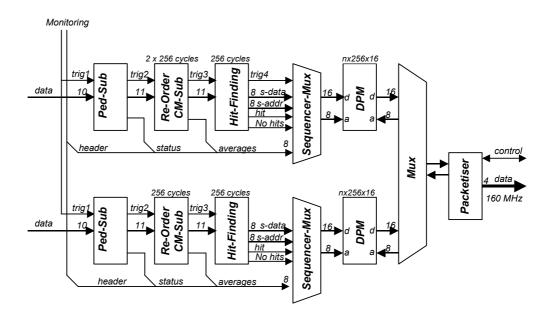

| 4.1     | The | FED Front-End Modules                          | 71  |

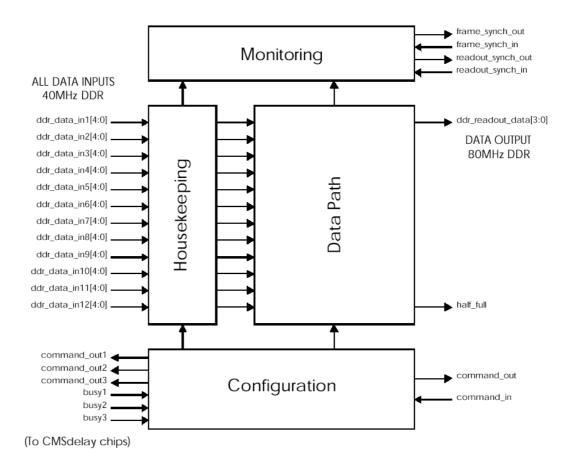

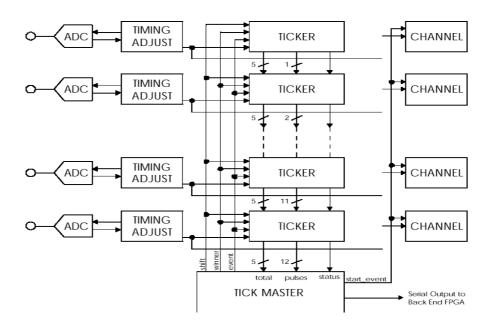

| 4.2     | The | Front-End FPGA                                 | 75  |

| 4.2.    | .1  | Housekeeping                                   | 76  |

| 4.2.    | .2  | Monitoring                                     | 77  |

| 4.2.    | .3  | Configuration                                  | 77  |

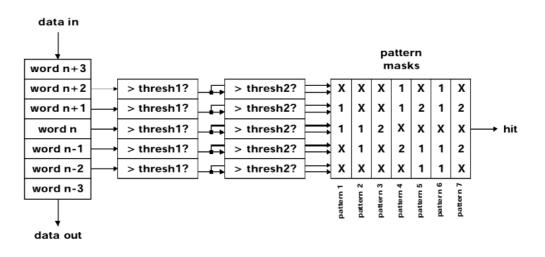

| 4.2.    | .4  | Data Path                                      | 78  |

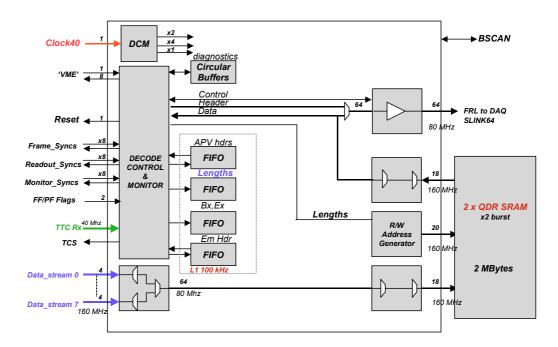

| 4.3     | The | Back-End FPGA                                  | 82  |

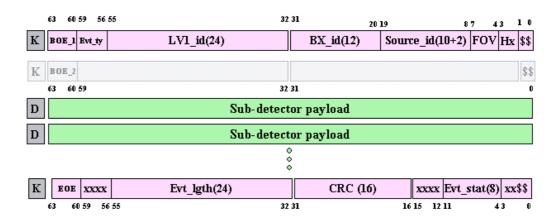

| 4.3.    | .1  | Common Data Format                             | 83  |

| 4.3.    | .2  | CRC                                            | 84  |

| 4.4     | Imp | lementation of Common Data Format              | 86  |

| 4.5     | Sun | nmary                                          | 92  |

| Chapter | 5:  | Analysis of Data Flow and Buffering in the FED | 93  |

| 5.1     | The | APV Buffers                                    | 94  |

| 5.1.    | .1  | The APV Emulator                               | 94  |

| 5.2     | Mo  | delling the FED                                | 95  |

| 5.2.    | .1  | Source Data                                    | 97  |

| 5.3     | Sim | ulation Results                                | 99  |

| 5.3.    | .1  | Zero-Suppression Mode                          | 99  |

| 5.3.    | .2  | Raw-Data Mode                                  | 108 |

| 5.4     | Sun | nmary                                          | 110 |

| Chapter | 6:  | Perspectives                                   | 111 |

| 6.1     | FEI | O Schedule                                     | 111 |

| 6.2     | FEI | D Testing                                      | 111 |

| 6.2.    | .1  | JTAG and Boundary Scan Testing                 | 112 |

| 6.2.    | .2  | Basic Analogue Tests                           | 112 |

| 6.2.    | .3  | Basic Digital Tests                            | 112 |

| 6.2.    | .4  | More Advanced Tests                            | 113 |

| 6.3     | Con | iclusions                                      | 113 |

|         |     |                                                |     |

| Appendix  | A: Common Data Format Implementation    | .115  |

|-----------|-----------------------------------------|-------|

| A.1       | fed_data_format.vhd                     | .115  |

| A.2       | builder.vhd                             |       |

| A.3       | fifo.vhd                                | . 122 |

| A.4       | mem64_general.vhd                       | . 124 |

| A.5       | mux.vhd                                 | . 125 |

| A.6       | pck_crc16_d64_ccitt.vhd                 | . 126 |

| A.7       | pck_crc16_d64_x25.vhd                   | .128  |

| Appendix  | B: Common Data Format Verification Code | .132  |

| B.1       | testbench.vhd                           | . 132 |

| B.2       | tester.vhd                              | . 135 |

| B.3       | main.c                                  | .139  |

| B.4       | crcmodel.h                              | . 141 |

| B.5       | crcmodel.c                              | .144  |

| Reference | es                                      | . 147 |

## List of Figures

| Figure 1.1: The LHC site, (a) map, (b) aerial view.                        | .15  |

|----------------------------------------------------------------------------|------|

| Figure 1.2: Higgs production at the LHC.                                   | .16  |

| Figure 1.3: Principle decay modes of the Higgs at CMS.                     | .17  |

| Figure 1.4: The CMS detector.                                              | . 19 |

| Figure 1.5: Transverse view of the CMS detector.                           | .20  |

| Figure 1.6: Diagram of the CMS superconducting magnet system               | .21  |

| Figure 1.7: The CMS tracker                                                | .22  |

| Figure 1.8: A prototype microstrip detector module from the tracker        | .23  |

| Figure 1.9: An ECAL crystal                                                | .24  |

| Figure 1.10: An assembled half-barrel of the HCAL.                         | .25  |

| Figure 1.11: A Muon drift tube                                             | .26  |

| Figure 1.12: A Muon cathode strip chamber                                  | .27  |

| Figure 1.13: A Muon resistive plate chamber.                               | .28  |

| Figure 1.14: The CMS level-1 global trigger.                               | .29  |

| Figure 2.1: Bipolar transistors (npn and pnp) and their symbols            | .30  |

| Figure 2.2: JFET transistors (n-channel and p-channel) and their symbols   | .31  |

| Figure 2.3: MOSFET transistors (n-channel and p-channel) and their symbols | .32  |

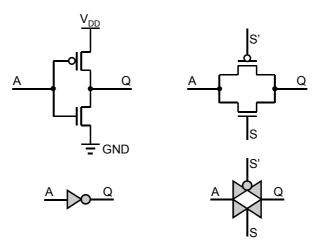

| Figure 2.4: A CMOS inverter and transmission gate, and their symbols       | .32  |

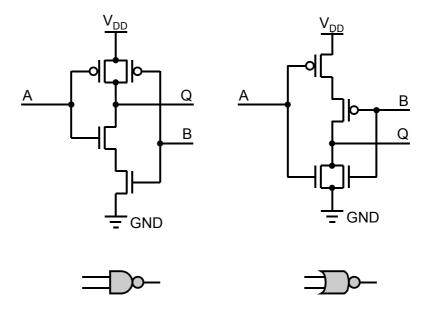

| Figure 2.5: CMOS NAND and NOR gates and their symbols                      | .33  |

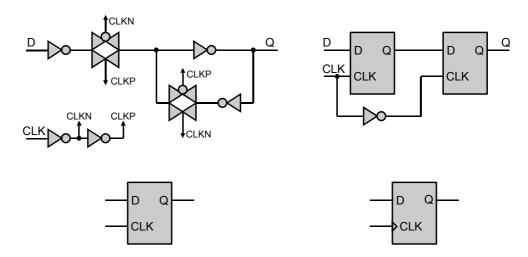

| Figure 2.6: CMOS transparent latch and flip-flop and their symbols         | .34  |

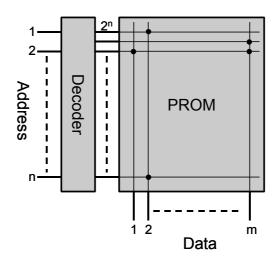

| Figure 2.7: Memory used as programmable logic.                             | .36  |

| Figure 2.8: A very small PLA                                               | .37  |

| Figure 2.9: Architecture of a CPLD.                                        | .38  |

| Figure 2.10: Architecture of an FPGA.                                      | . 39 |

| Figure 2.11: Example of a fine-grained logic cell.                         | .40  |

| Figure 2.12: Antifuses: (a) ONO, (b) amorphous silicon.                    | .40  |

| Figure 2.13: An EPROM memory cell: a) schematic, b) use in wired-AND       | .41  |

| Figure 2.14: An SRAM memory cell.                                          | .42  |

| Figure 2.15: Xilinx Virtex-II Architecture.                                | .44  |

| Figure 2.16: Virtex-II logic blocks: (a) CLB, (b) slice                    | .45  |

| Figure 2.17: (a) I/O banks in Virtex-II flip-chip packages, (b) an I/O block      | .48  |

|-----------------------------------------------------------------------------------|------|

| Figure 2.18: Virtex-II routing resources.                                         | .49  |

| Figure 2.19: The FPGA Design Process                                              | .50  |

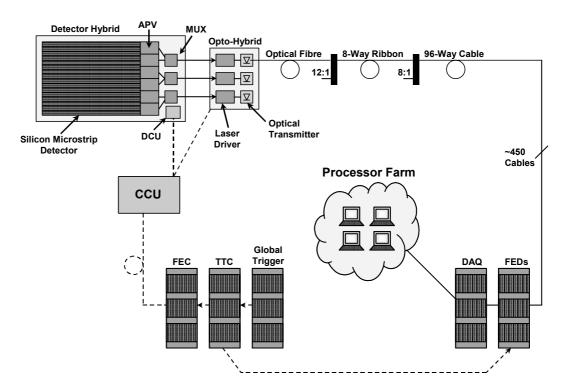

| Figure 3.1: An overview of the tracker readout system                             | .57  |

| Figure 3.2: A silicon microstrip detector.                                        | .58  |

| Figure 3.3: The APV25-S1                                                          | .60  |

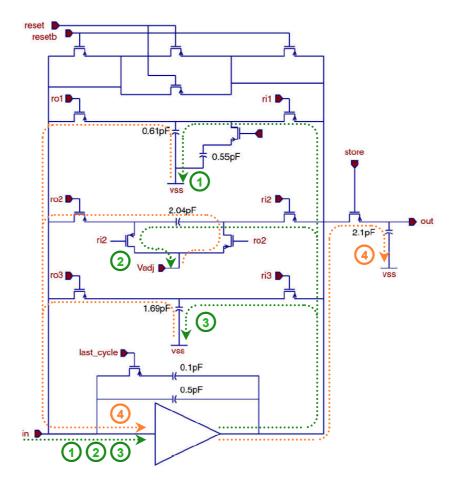

| Figure 3.4: The APV25 APSP circuit                                                | .63  |

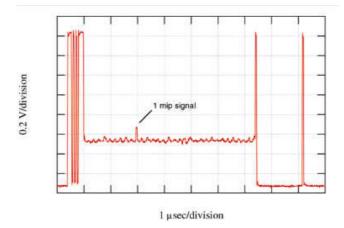

| Figure 3.5: A typical APV output frame                                            | .64  |

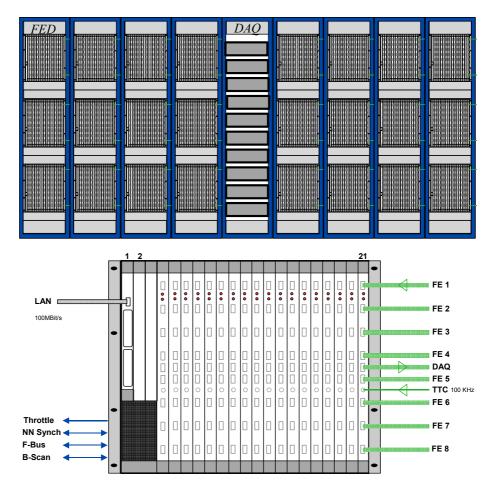

| Figure 3.6: The FED and DAQ racks (top) and a FED crate (bottom)                  | .66  |

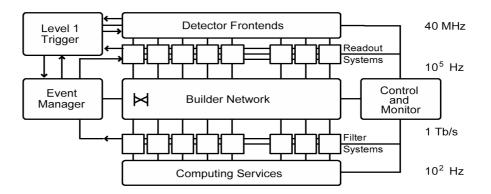

| Figure 3.7: Overview of the CMS DAQ system                                        | .67  |

| Figure 3.8: Schematic of the tracker control system.                              | . 69 |

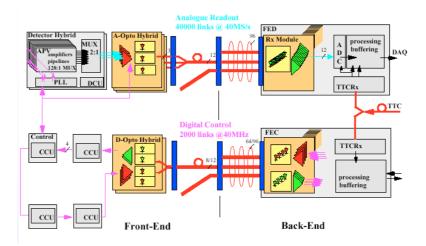

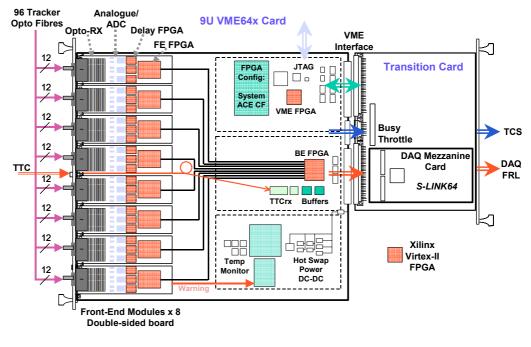

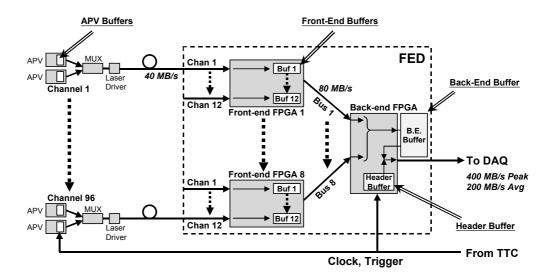

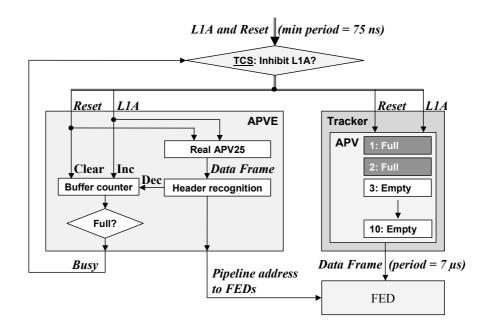

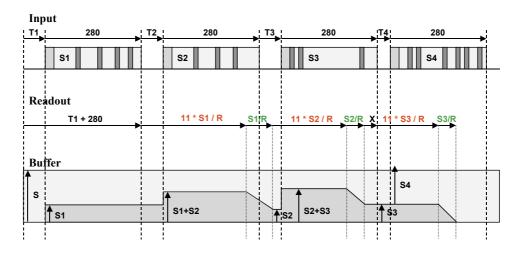

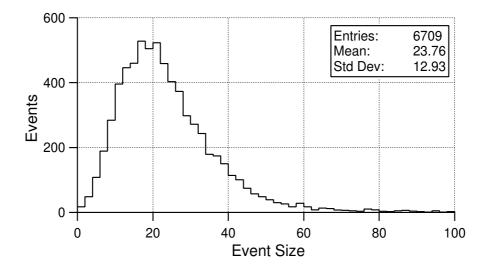

| Figure 4.1: Schematic of the Front-end driver                                     | .70  |

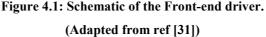

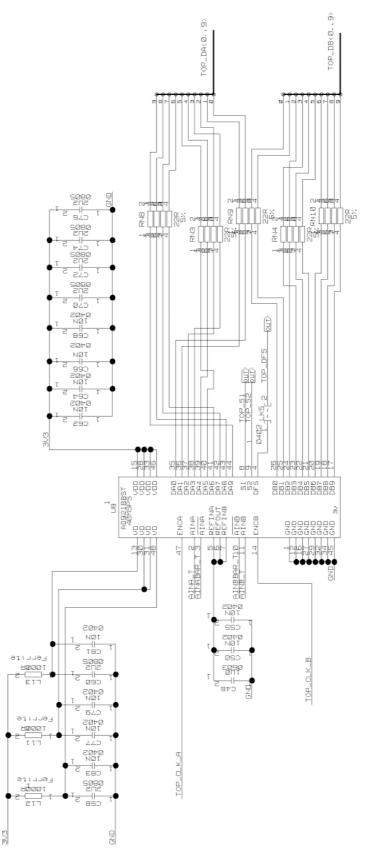

| Figure 4.2: Schematic of a FED front-end module                                   | .71  |

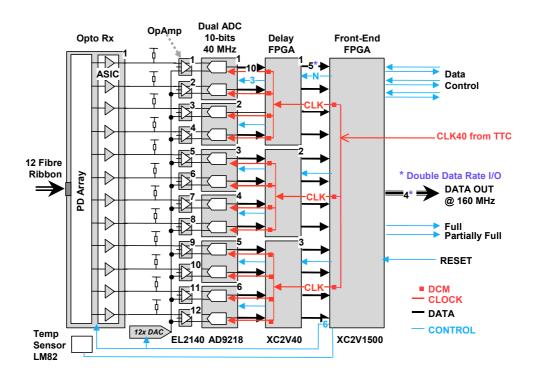

| Figure 4.3: Schematic of a FED front-end module analogue section                  | .72  |

| Figure 4.4: Schematic of a FED front-end module two channel ADC                   | .73  |

| Figure 4.5: Schematic of the FED front-end FPGA.                                  | .75  |

| Figure 4.6: Basic schematic of the housekeeping block                             | .76  |

| Figure 4.7: A pair of channels from the datapath block.                           | .78  |

| Figure 4.8: Graphical representation of the clustering algorithm                  | .80  |

| Figure 4.9: Diagram of the back-end FPGA                                          | .82  |

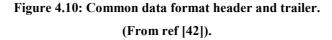

| Figure 4.10: Common data format header and trailer                                | .83  |

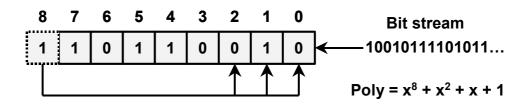

| Figure 4.11: Graphical representation of the CRC algorithm (for CRC-8)            | .85  |

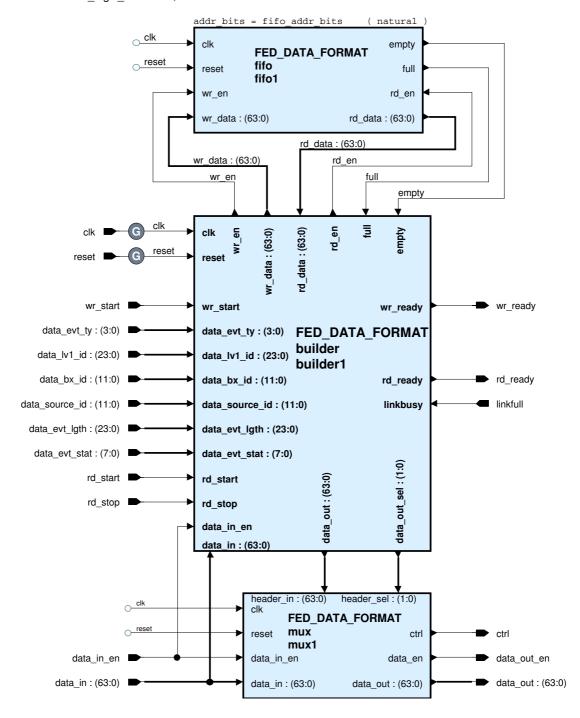

| Figure 4.12: Block diagram of the header formatting block.                        | .88  |

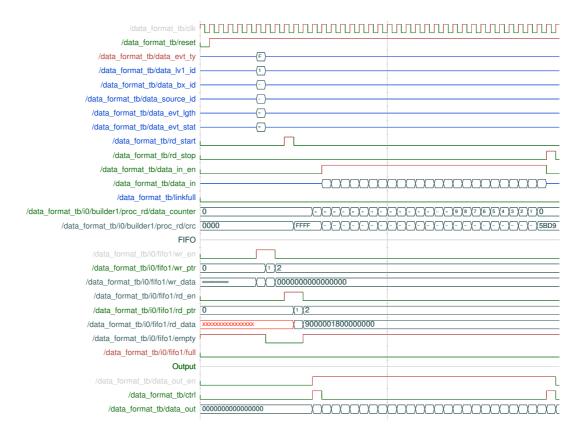

| Figure 4.13: A short period of the simulation                                     | .90  |

| Figure 5.1: Data flow and buffers in the tracker readout system                   | .93  |

| Figure 5.2: The APV Emulator System.                                              | .94  |

| Figure 5.3: Graphical representation of the FED buffer model                      | .96  |

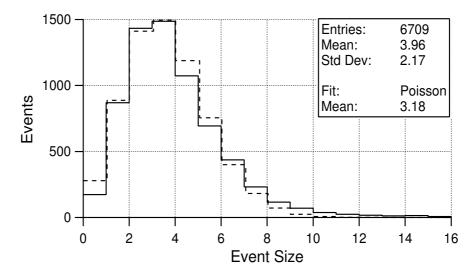

| Figure 5.4: Distribution of event sizes in strips per detector, from Monte-Carlo. | 97   |

| Figure 5.5: Estimated distribution of event sizes in strips per APV               | .98  |

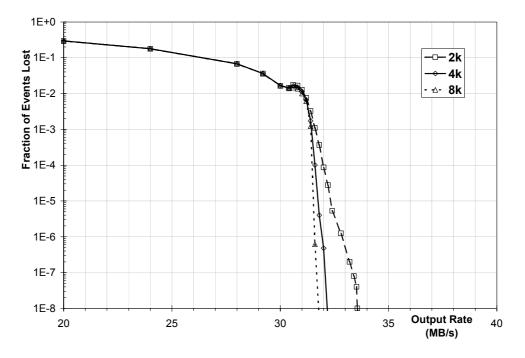

| Figure 5.6: Zero-suppression, front-end: events lost vs. output rate              | 100  |

| Figure 5.7: Zero-suppression, front-end: events lost vs. occupancy.               | 101  |

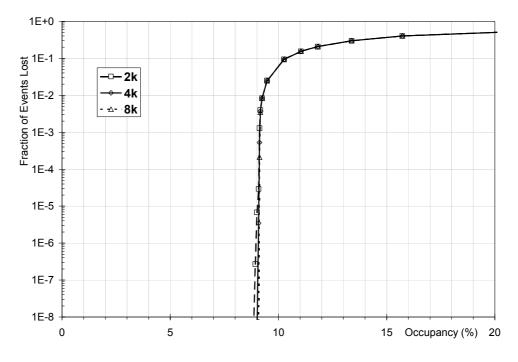

| Figure 5.8: Zero-suppression, back-end: events lost vs. output rate.              | 102  |

| Figure 5.9: Zero-suppression, back-end: events lost vs. occupancy        | 103     |

|--------------------------------------------------------------------------|---------|

| Figure 5.10: Zero-suppression, back-end: maximum occupancy vs. output ra | ate.104 |

| Figure 5.11: Zero-suppression: peak level of data buffer vs. occupancy   | 105     |

| Figure 5.12: Zero suppression: peak level of header buffer vs. occupancy | 106     |

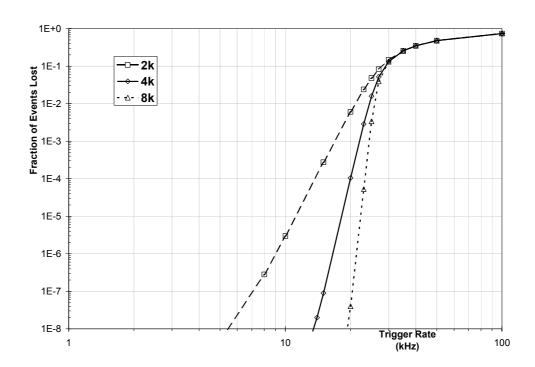

| Figure 5.13: Raw data, front-end: events lost vs. trigger rate           | 108     |

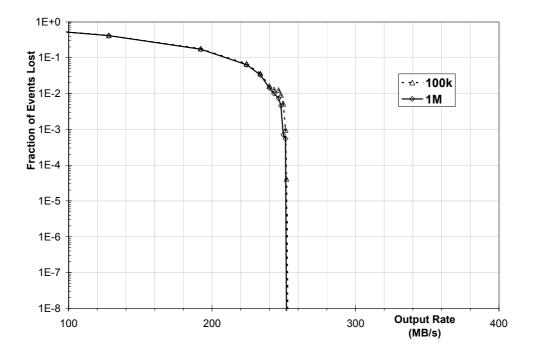

| Figure 5.14: Raw data, back-end: events lost vs. trigger rate            | 109     |

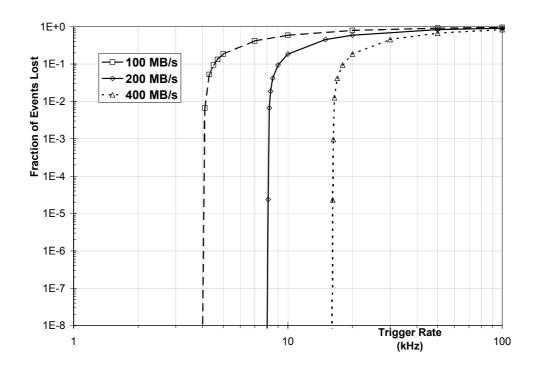

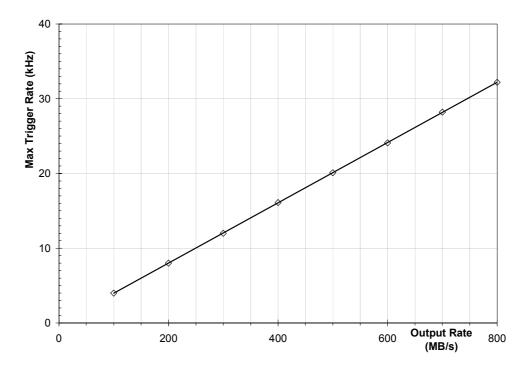

| Figure 5.15: Raw data: maximum trigger rate vs. output rate              | 110     |

## List of Tables

| Table 2.1: Truth tables for NAND and NOR gates.            | 33   |

|------------------------------------------------------------|------|

| Table 2.2: Summary of Programming Technologies             | 43   |

| Table 2.3: Virtex-II family members.                       | 45   |

| Table 2.4: Virtex-II block-RAM configurations.             | 47   |

| Table 4.1: Rules for data size reduction in the FED        | 81   |

| Table 4.2: Common data format header and trailer fields    | 84   |

| Table 4.3: Parameters for the reference CRC.               | 91   |

| Table 4.4: Synthesis results for the header building code. | 91   |

| Table 5.1: Peak header buffer levels                       | .107 |

## Glossary

- ADC Analogue-to-Digital Converter.

- APSP Analogue Pulse Shape Processor: Processing stage in the APV readout chip.

- APV Analogue Pipeline (Voltage Mode): Front-end readout chip.

- APV25 APV built on 0.25 µm process.

- APV6 Early version of the APV built on 1.2 µm process.

- APVE APV Emulator.

- APVM Early version of the APV built on 1.2 µm process, for MSGCs.

- APVMUX APV Multiplexer: Combines the outputs from pairs of APVs to send to laser driver.

- ASIC Application Specific Integrated Circuit.

- BPM BiPhase Mark: Encoding scheme used by the TTC system.

- BRAM Block-RAM: One of several logic blocks in an FPGA.

- CCITT Comité Consultatif International de Télégraphique et Téléphonique: International consultative committee on telecommunications and telegraphy.

- CCU Communications and Control Unit: Distributes clock, trigger, control and monitoring data within the tracker.

- CERN The European Laboratory for Particle Physics Research, in Geneva, Switzerland.

- CLB Configurable Logic Block: Basic unit of logic functionality in FPGAs.

- CMOS Complementary Metal Oxide Semiconductor: A semiconductor technology consisting of both p-type and n-type devices, and having low power dissipation.

- CMS Compact Muon Solenoid.

- CPLD Complex Programmable Logic device.

- CRC Cyclic Redundancy Check: An error detection code.

- CSC Cathode Strip Chamber: A type of muon detector used at CMS.

- DAC Digital-to-Analogue Converter.

- DAQ Data Acquisition system.

- DCM Digital Clock Manager: One of several logic blocks in an FPGA.

- DCU Detector Control Unit: Interface to monitor slowly varying parameters in the tracker.

- DDR Double Data Rate: Port in which data is latched on both clock edges, resulting in a doubling of the data rate.

- DPM Dual Port Memory.

- DT Drift Tube: A type of muon detector used at CMS.

- DUT Device Under Test.

- ECAL Electromagnetic Calorimeter.

- EEPROM Electrically Erasable Programmable Read Only Memory.

- EPROM Erasable Programmable Read Only Memory.

- FEC Front End Controller: Distributes clock, trigger and control data to, and receives monitoring data from, the tracker readout system via digital optical links.

FED Front End Driver. FET Field Effect Transistor. FIFO First In First Out: Type of buffer in which the data are read out in the same order in which they were written. FIR Finite Impulse Response: Type of signal-processing filter. Type of EEPROM in which large areas of memory can be erased at FLASH once. **FPD** Field Programmable device: A general term for all types of userprogrammable integrated circuits. FPGA Field Programmable Gate Array: an FPD with a structure allowing very high logic capacity. HCAL Hadronic Calorimeter. HDL Hardware Description Language.  $I^2C$ Inter-IC: Two-wire serial communications protocol developed by Philips. IC Integrated Circuit. Institute of Electrical and Electronic Engineers: Standards IEEE committee. IIR Infinite Impulse Response: Type of signal-processing filter. ILA Integrated Logic Analyzer: Part of the Chipscope debugging tool for FPGAs from Xilinx. IOB Input/Output Block. ISP In System Programmable. JFET Junction Field Effect Transistor. **JTAG** Joint Test Action Group: Standard for controlling and monitoring pins and internal registers of electronic devices such as FPGAs. L1A Level-1 Accept: First-level trigger decision signal (up to 100 kHz). LEP Large Electron Positron Collider. Large Hadron Collider. LHC LSP Lightest Supersymmetric Particle. LVDS Low Voltage Differential Signalling: High performance, low power, and low noise signalling standard. MIP Minimum Ionising Particle: Corresponds to roughly 25 000 electrons in a 300 µm thick silicon detector. Metal-Oxide-Semiconductor Field Effect Transistor. MOSFET MPGA Mask Programmable Gate Array: ASIC technology consisting of standard logic cells (as in an FPGA) but programmed by a custom metal layer during the manufacturing process. MSGC Microstrip Gas Chamber. MSSM Minimal Supersymmetric Standard Model. Negative-channel Metal Oxide Semiconductor. NMOS OVI Open Verilog International: Non-profit organisation that maintains Verilog HDL. PAL Programmable Array Logic: Simple FPD with programmable AND-plane and fixed OR-plane (registered trademark of Advanced Micro Devices Inc.). PAR Place-and-Route. Printed Circuit Board. PCB

- PCI Peripheral Component Interconnect: Widely used bus designed by Intel.

- PLA Programmable Logic Array: Simple FPD with a programmable AND-plane and OR-plane.

- PLD Programmable Logic Device: See FPD, often used to refer to relatively simple types of devices.

- PMC PCI Mezzanine Card.

- PMOS Positive-channel Metal Oxide Semiconductor.

- PPARC Particle Physics and Astronomy Research Council.

- PROM Programmable Read Only Memory.

- QDR Quad Data Rate.

- RAL Rutherford Appleton Laboratory, in Didcot, Oxfordshire.

- RAM Random Access Memory.

- ROM Read Only Memory.

- RPC Resistive Plate Chamber: A type of muon detector used at CMS.

- SDF Standard Delay Format.

S-LINK Protocol for transmission of data in 8-32-bit words at up to 40 MHz

- S-LINK64 Extension of S-LINK allowing 64-bit data at a rate of 100 MHz.

- SM Standard Model.

- SOP Sum of Products.

- SPLD Simple Programmable Logic Device.

- SRAM Static RAM.

- SUSY Supersymmetry.

- TCS Tracker Control System.

- TTC Timing, Trigger and Control System.

- TTCrx TTC Receiver: Custom IC

- TTL Transistor-Transistor Logic: A semiconductor technology using bipolar transistors.

- VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language.

- VME Versa Module Europa: A flexible backplane interconnection bus system, using the Eurocard standard circuit board sizes and defined by IEEE standard 1014-1987.

## **Chapter 1: Introduction**

## 1.1 The Large Hadron Collider (LHC)

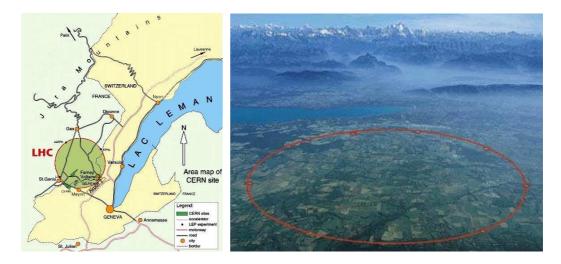

The LHC is a particle accelerator being built at CERN, the European Laboratory for Particle Physics Research near Geneva in Switzerland. It is located in the 27 km circumference circular tunnel previously used for the Large Electron-Positron (LEP) collider (see figure 1.1).

Figure 1.1: The LHC site, (a) map, (b) aerial view.

When operational, it will provide proton-proton collisions with a centre-ofmass energy of 14 TeV and a luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. This is orders-ofmagnitude higher than any previous accelerator, leading to an extremely demanding radiation environment. In order to sustain such a high luminosity, bunches of particles are separated by only 25 ns, and the readout electronics must be capable of determining from exactly which bunch crossing each signal originated, leading to very strict timing requirements.

In addition to proton-proton collisions, heavy ions, such as lead, will be collided at energies in excess of 1000 TeV/ion and luminosity over  $10^{27}$  cm<sup>-2</sup>s<sup>-1</sup>.

Introduction

## 1.2 Physics at the LHC

The LHC will open up new, previously unexplored, areas of physics. The energies available will allow many predictions to be either confirmed by experiment, or rejected. In addition it will allow much more accurate measurement of many fundamental parameters of physics.

#### 1.2.1 The Higgs

The Standard Model (SM) of particle physics requires the existence of a new particle, the Higgs. Particles acquire mass through their interaction with the Higgs field. There is a theoretical upper limit on the mass of the Higgs, of about 1 TeV, and masses up to 114 GeV have been ruled out by direct searches at LEP [1] and other experiments, although there were hints of a possible Higgs at a mass of 115.6 GeV [2]. Depending on its mass, there are a number of ways in

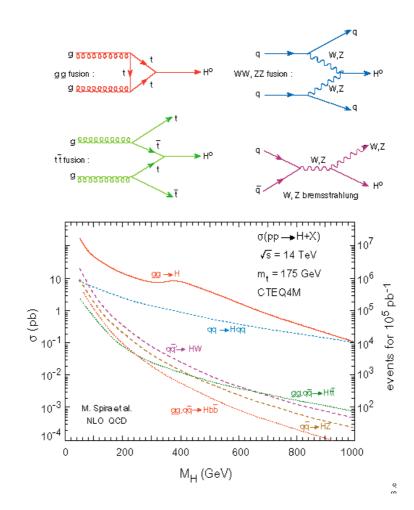

Figure 1.2: Higgs production at the LHC.

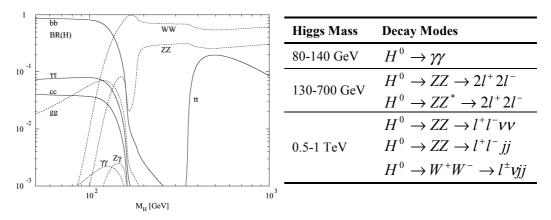

which Higgs particles may be produced at the LHC (see figure 1.2), but the dominant production channel is by gluon fusion. Once produced, there are a number of different ways the Higgs may decay, also depending on its mass. The branching ratios for the various modes are depicted in figure 1.3, along with a table of the decay modes best suited for a search at CMS.

Figure 1.3: Principle decay modes of the Higgs at CMS.

For a light Higgs, up to around 140 GeV, the dominant decay channel is  $H^0 \rightarrow b\overline{b}$ , but this channel will be difficult to observe due to a large background of QCD jets. A better channel will be the much rarer  $H^0 \rightarrow \gamma\gamma$  channel, with a branching ratio of around 10<sup>-3</sup>. There will also be a large irreducible photon-photon background, but over the relevant mass range this will be smoothly varying, and the Higgs particle would therefore produce a slight hump superimposed on top of a well-calibrated background. For this to be possible, very accurate energy resolution is needed for the photons, and the ECAL has been optimised with this in mind.

For a slightly heavier Higgs, up to about 700 GeV, the most promising decay channels are  $H^0 \rightarrow ZZ, ZZ^* \rightarrow 2l^+ 2l^-$ . In this case, detection relies on the excellent performance of the muon chambers along with the crystal ECAL and the tracker.

For the highest Higgs mass, there are a number of promising decay modes, with detection relying on leptons, jets, and missing transverse energy in the case of neutrinos. For this the performance of the HCAL is very important. If the Higgs boson exists, it is expected that it will be produced and detected once in about every  $10^{13}$  collisions, which, with 800 million collisions per second, corresponds to about once a day.

#### 1.2.2 CP Violation

The known universe is dominated by matter, as opposed to antimatter, and yet the four known forces seem to act equally on matter and antimatter. This introduces the question of how the universe evolved into its current asymmetric state. A clue may be provided by the phenomenon of charge-parity (CP) violation, discovered in 1964 in the decays of the neutral kaon ( $K^0$ ), an s-quark containing meson. There is a small difference in the decay rates of  $K^0$  and  $\overline{K}^0$  mesons. This implies that either there exists another, as yet unknown, force of nature, which is matter-antimatter asymmetric, or that the weak interaction, through which kaons decay, can actually distinguish between matter and antimatter. If this is the case, then mesons made of quarks heavier than the s quark should display an even larger asymmetry in their decay rates. The best candidate is the b quark, which forms B mesons. Although the LHCb experiment at the LHC is dedicated to B physics, CMS will also play a role in the study of CP violation especially during the initial low luminosity phase of the LHC [3].

#### 1.2.3 Supersymmetry

Supersymmetry (SUSY) introduces a new symmetry, not present in the standard model, between fermions and bosons. It proposes that each fermion  $(\text{spin-}^{1}/_{2})$  has a superpartner of spin-0, while each boson (integer-spin) has a spin- $^{1}/_{2}$  superpartner. In the minimal supersymmetric standard model (MSSM) there are at least five Higgs bosons, as well as a host of new superpartners for currently known particles, called sparticles (supersymmetric particles). The heavier sparticles will rapidly decay, while the lightest supersymmetric particle (LSP) will be stable, and can be detected from missing transverse energy.

#### **1.3 The Compact Muon Solenoid (CMS)**

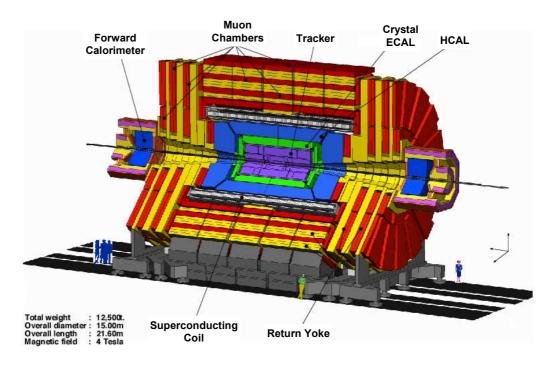

The Compact Muon Solenoid is one of the several experiments based at the LHC. It is a general-purpose detector designed to detect cleanly a diverse range of signatures of possible new physics, and is optimised to search for the standard model Higgs boson in the mass range from 90 GeV to 1 TeV.

Figure 1.4: The CMS detector.

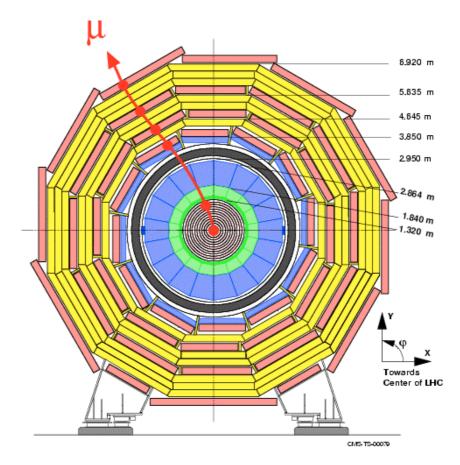

CMS is built around a large toroidal superconducting electromagnet of length 13 m and inner diameter 5.9 m, which generates a magnetic field of 4 Tesla [4] (see figure 1.4 and figure 1.5). It consists of several sub-detectors each optimised to detect certain types of particles. The tracker is made of layers of silicon pixel and microstrip detectors, and is designed to track all ionising particles without significantly affecting their energy or momentum. Surrounding the tracker is the electronic calorimeter, made of lead tungstate (PbWO<sub>4</sub>) crystals. This is designed to absorb all electrons and photons and measure their energy from the scintillation produced by the deposited energy, while other particles such as hadrons, muons and neutrinos, pass through. Outside this is the hadronic calorimeter, which measures the energy and position of the hadrons.

Figure 1.5: Transverse view of the CMS detector.

The only particles that escape through all these layers of detectors and the magnet are muons and neutrinos. Muons lose energy almost solely through ionisation along their path, and even in dense materials like steel or copper, this amounts to a loss of only 1 MeV per millimetre. The muons are detected by the muon chambers surrounding the detector, and the neutrinos have to be inferred from missing energy.

#### 1.3.1 The Magnet

The CMS magnet system consists of a large superconducting coil capable of generating a magnetic field of 4 Tesla, and a return yoke to contain the generated magnetic field. With a length of 13 m and an inner diameter of 5.9 m, it will be the largest superconducting magnet in the world; the stored energy (2.5 GJ) is

enough to melt 18 tonnes of gold. The use of such a high magnetic field allows a much more efficient first-level trigger [5] by improving the momentum resolution of the muon detectors. It also improves the momentum resolution of the tracker, and allows the electromagnetic calorimeter to be accurately calibrated by comparing the energies of electrons with their momentum in the tracker. A reduction of the magnetic field strength to 3 Tesla, would require the running time to increase by one third to achieve the same level of significance for a mass measurement from multi-charged particle states [5].

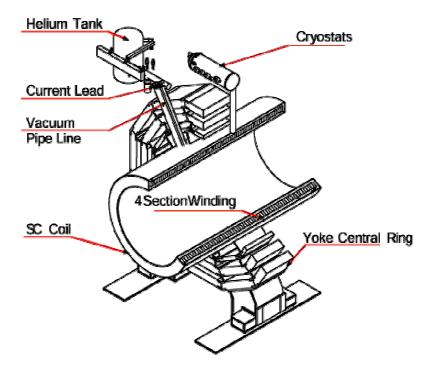

Figure 1.6: Diagram of the CMS superconducting magnet system.

A diagram of the magnet system, excluding most of the yoke, is shown in figure 1.6. The coil itself is built in four sections, each with four layers of winding, giving a total of 43 km of superconducting cable. The coil is contained within a vacuum tank, a 240 tonne stainless steel vessel, which also acts as a support structure for the barrel HCAL, ECAL, and tracker.

A cryogenic system, using liquid helium, keeps the coil at a working temperature of 4.5 K, with a maximum temperature difference of 0.1 K within the coil.

Introduction

#### 1.3.2 The Tracker

The tracker is designed to reconstruct tracks efficiently, giving accurate measurements of the vertex, the impact parameter, and any secondary vertices, whilst being as thin as possible to minimise multiple scattering and energy loss, which would have adverse effects on the calorimetry. It must have a high enough spatial resolution to isolate and identify isolated leptons and photons, in order to reduce backgrounds sufficiently for Higgs and SUSY searches. For a typical particle energy of 100 GeV, the tracker can measure the transverse momentum with a resolution of about 2 % up to  $|\eta| < 1.6$  and about 6.5 % up to  $|\eta| < 2.5$  [6].

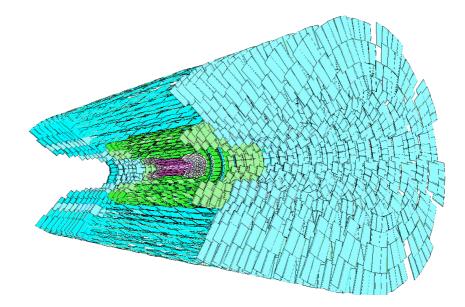

Figure 1.7: The CMS tracker.

The layout of the tracker is shown in figure 1.7. The central three layers are based on silicon pixel detectors. Surrounding this is the inner barrel, consisting of four layers of microstrip detectors, and the outer barrel, consisting of six layers. At each end of the cylinder are the pixel forward detector (2 layers, pixel), the inner disk (3 layers, microstrip) and the endcaps (9 layers). The original proposal had been to use microstrip gas chambers (MSGCs) for the outer layers of the tracker, but a review in December 1999 decided to move to an all-silicon design as this was just as viable and allowed more effort to be concentrated onto a smaller set of problems [7].

Introduction

#### **Pixel Detectors**

The pixel detectors are located close to the interaction point, where the occupancies are highest, in three barrel-layers and two end-layers. Each pixel measures  $150 \times 150 \mu m$ , and by using charge sharing between pixels to interpolate the track positions, will provide a spatial resolution of about 10  $\mu m$  in the r- $\phi$  direction and about 20  $\mu m$  in the z direction [6]. The pixel detector will confirm or reject track segments proposed by the surrounding tracker layers.

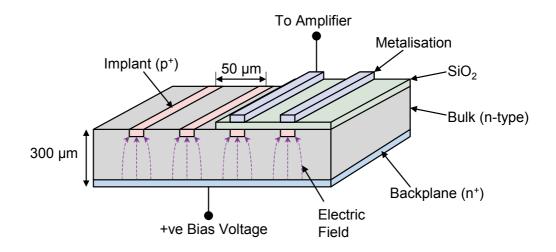

#### **Microstrip Detectors**

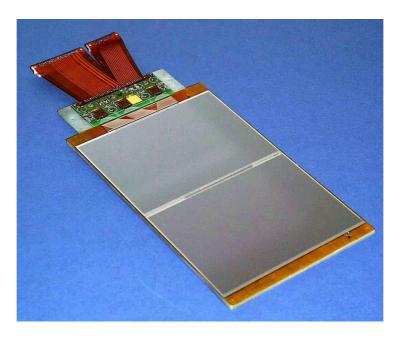

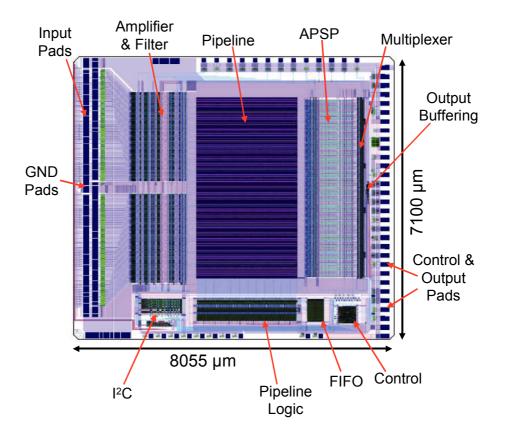

The microstrip detectors are arranged in 10 layers around the pixel detectors. Their pitch varies from 80  $\mu$ m in the inner layer to 205  $\mu$ m in the outer layer. Typical spatial resolutions (for a 100  $\mu$ m pitch detector) are 34  $\mu$ m in r- $\phi$  and 320  $\mu$ m in the z direction [6]. One of the prototype detector hybrid modules from the microstrip tracker is shown in figure 1.8. It consists of two microstrip detectors, bonded together at the centre. A pitch adaptor connects one end of the detector to the APV readout chips. There is space for six APV chips; each reading out 128 of the 768 detector strips, although in the prototype only three are mounted, and only half of the detector is read out. A kapton cable connects the outputs of the APVs to the opto-hybrid, where the signals are driven via optical fibres to the counting room.

Figure 1.8: A prototype microstrip detector module from the tracker.

#### **1.3.3 The Electronic Calorimeter (ECAL)**

The electromagnetic calorimeter (ECAL) will consist of more than 80 000 lead tungstate (PbWO<sub>4</sub>) crystals (see figure 1.9). Lead tungstate is extremely dense (more than eight times denser than water), and the whole collection of crystals will weigh more than 90 tonnes [8]. Lead tungstate has a very short radiation length of 0.89 cm, allowing a very compact detector, and a small Moliere radius of 2.19 cm, allowing a fine granularity. It has an interaction length of 22.4 cm, and each crystal has a length of 22 cm [8], so hadrons will on average only interact once in the ECAL.

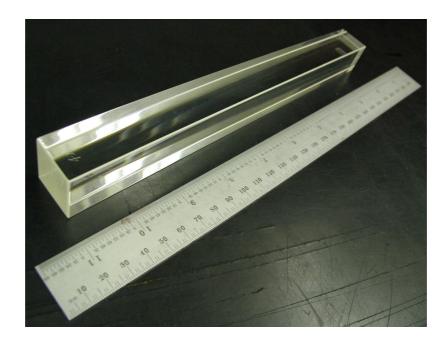

Figure 1.9: An ECAL crystal.

Particles are detected in the ECAL by the scintillation light they produce in the crystals. This is measured by avalanche photodiodes in the barrel section, and by vacuum phototriodes in the endcap regions, where the neutron flux is higher, and the photodiodes would suffer unacceptably high radiation damage. Vacuum phototriodes cannot be used in the barrel region due to the orientation of the magnetic field.

#### **1.3.4 The Hadronic Calorimeter (HCAL)**

The combined calorimeter system of CMS will measure the directions and energies of quarks, gluons, and neutrinos indirectly by measuring the direction and energy of particle jets and of the missing transverse energy [9]. Both the barrel and the endcap of the HCAL (see figure 1.10) will experience the 4 Tesla magnetic field of the CMS solenoid, and are therefore constructed from brass and stainless steel, which are non-magnetic. The central hadronic calorimeter consists of 4 mm thick plastic scintillator tiles inserted between copper absorber plates (5 cm thick in the barrel and 8 cm thick in the endcaps). The scintillator tiles are read out using wavelength-shifting plastic fibres. An additional layer of scintillator tiles is located outside of the solenoid to ensure adequate sampling depth for the whole  $|\eta| < 3$  region. This is known as the outer hadronic calorimeter. The thickness of the HCAL system varies from 5.15 interaction lengths at  $\eta = 0$  up to 5.82 interaction lengths [9].

Figure 1.10: An assembled half-barrel of the HCAL.

The HCAL also includes the forward calorimeter, located 6 m downstream from the HCAL endcaps, and extending the hermeticity of the hadronic calorimeter up to  $|\eta| < 5$ . It is constructed from quartz fibres embedded in a copper absorber matrix, and is necessary for an accurate measurement of missing transverse energy, and for forward jet detection.

#### 1.3.5 The Muon Detectors

There are three different types of detector used for muons: Resistive Parallel Plate Chambers (RPCs), Drift Tubes (DTs), and Cathode Strip Chambers (CSCs). Together they measure the transverse momentum of the muons with an accuracy of better than 4 % up to  $|\eta| < 2$ , for muons with a typical energy of 100 GeV [10].

#### **Drift Tubes**

The drift tubes are located in the central barrel region of the detector, where the magnetic field is guided and almost fully trapped by the iron plates of the magnet yoke. They are located in four layers, or stations; two on the inner and outer face of the iron yoke, and two in slots inside it. The redundancy provided by four stations of twelve planes each means it is possible to cope with inefficiencies from dead zones caused by supporting ribs and longitudinal space caused by the joins between the rings of the CMS detector.

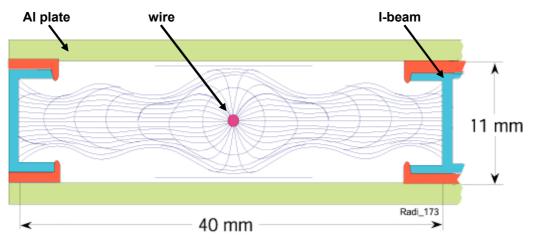

Figure 1.11: A Muon drift tube.

A diagram of a drift tube is shown in figure 1.11. It consists of parallel aluminium plates separated by aluminium I-beams, with a wire stretched along the centre. When an ionising particle passes through the tube, it liberates electrons, which then drift along the electric field lines towards the positively charged wire. The time taken for the ionisation electrons to drift to the wire is measured to within an accuracy of 1 ns, and as the drift velocity of the electrons is known, this gives a good measure of the distance of the original particle from the wire.

#### **Cathode Strip Chambers**

The cathode strip chambers (CSCs) are located in the endcap regions of the detector, where the magnetic field is vertical and contained within the iron yoke disks. There are four layers of CSCs sandwiched between the iron disks of the return yoke.

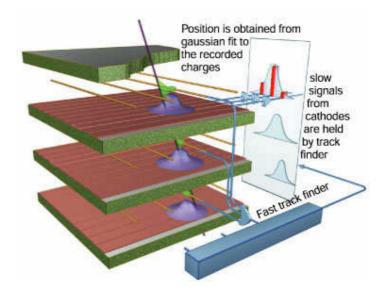

Figure 1.12: A Muon cathode strip chamber.

A CSC (see figure 1.12) consists of cathode planes segmented into strips, and interleaved with wires running perpendicular to the strips. A passing particle ionises atoms, and the freed electrons are collected by the wires, while the positive ions drift to the strips. This gives two coordinates, the wires measuring the radial coordinate, while the strips measure  $\phi$ . The close spacing of the wires make the CSC a fast detector, particularly suitable for triggering.

#### **Resistive Parallel Plate Chambers**

The Resistive Plate Chambers (RPCs) are used in both the barrel and the endcap regions of the detector, and are used to provide an additional complementary trigger. They will cover approximately the same area as the DTs and CSCs, but will provide a faster timing signal and have a different sensitivity to background.

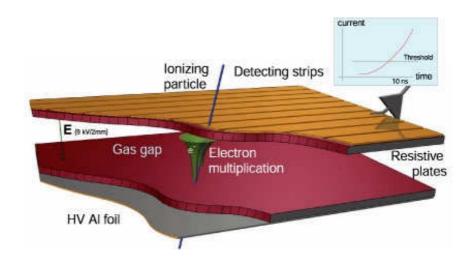

Figure 1.13: A Muon resistive plate chamber.

An RPC is shown in figure 1.13. It consists of two parallel plates of highresistivity plastic material, separating a thin gap filled with gas. A passing ionising particle releases electrons, which accelerate towards the positively charged side of the chamber in an avalanche. The plastic is transparent to these electrical signals, which are then picked up by external metallic strips.

The signals from each of the three types of muon detectors proceed in parallel to the trigger logic. Every muon with enough energy to penetrate the detector material should traverse at least three of the muon stations.

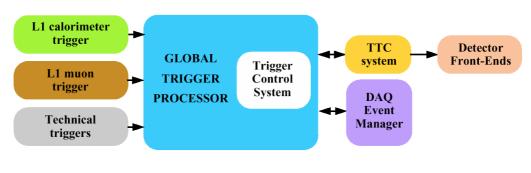

#### 1.3.6 The Trigger

In normal operation, the global trigger processor receives data from the calorimeters and the muon chambers. It can also use special signals for set-up, synchronisation, calibration and testing purposes. It contains logic for processing up to 128 different trigger algorithms in parallel, the results being delivered as a

128-bit word, with one bit per algorithm. This can be compared with a predefined input word that selects which particular triggers are of interest for the run.

Figure 1.14: The CMS level-1 global trigger. (Adapted from ref [11])

The level-1 accept trigger decision (L1A), along with the 40.08 MHz LHC machine clock, and other signals, such as bunch-crossing reset are distributed to the detector by the TTC system. The data for each 25 ns bunch-crossing period are stored in the detector front-end until the trigger decision is known. This period, known as the trigger latency, will be about 3  $\mu$ s.

#### 1.4 Summary

The CMS detector and its readout system need to process huge volumes of data, and reduce it to a manageable amount before it can be stored and properly analysed. The LHC, at its full luminosity, will generate 20 interactions with a significant transverse energy for every bunch crossing, at a rate of 40.08 MHz. The first level trigger will reduce this to a rate of up to 100 kHz, with the raw data for each event being about 1 Mbyte. This means that the readout system still needs to process about 100 Gbyte of data every second. The tracker consists of about 10 million detector channels, and is expected to generate up to 70 % of the final data volume at CMS. These data rates are orders of magnitude higher than in any previous experiment and demand state-of-the-art technology as well as massively parallel processing if the experiment is to be successful.

## **Chapter 2: Field Programmable Devices**

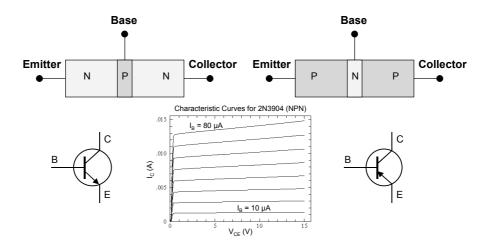

All digital logic circuits are made up of simple building blocks known as logic gates, which are in turn made of transistors. Two main technologies exist, known as transistor-transistor logic (TTL) and complementary metal oxide semiconductor (CMOS).

#### 2.1 Digital Logic

The older of the two, TTL is made of bipolar transistors, which are sandwiches of n- and p-type semiconductor material in either npn or pnp configurations (see figure 2.1). The transistor consists of two p-n junctions, with the thin central section connected to the base terminal, and the two ends connected

Figure 2.1: Bipolar transistors (npn and pnp) and their symbols.

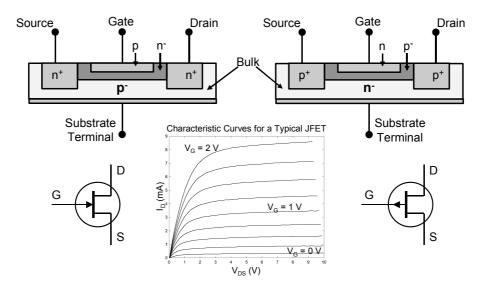

to the collector and the emitter. An npn transistor conducts current when its base is pulled high, and a pnp transistor conducts when its base is low. Bipolar transistors are current-amplifying devices: the amount of current flowing into the base controls the amount of current flowing in the collector circuit, but they can also be used in voltage amplification circuits. Bipolar transistors can operate at speeds in excess of a gigahertz, and can be designed to handle large currents up to several amps, but they have a relatively low input impedance of up to about 1 k $\Omega$ , and so are not suitable for applications requiring high circuit impedance. Field effect transistors exist in two main types, Junction Field Effect Transistor (JFET) and Metal Oxide Semiconductor FET (MOSFET). In both types, current flows along a semiconductor channel (n-type or p-type) between the source at one end and the drain at the other. In a JFET, the gate is of the opposite type of semiconductor to the channel, creating a p-n junction (see figure 2.2). A DC voltage is connected to the gate so that the junction is normally reverse-biased, although under certain conditions a small current can flow during part of the signal cycle.

Figure 2.2: JFET transistors (n-channel and p-channel) and their symbols.

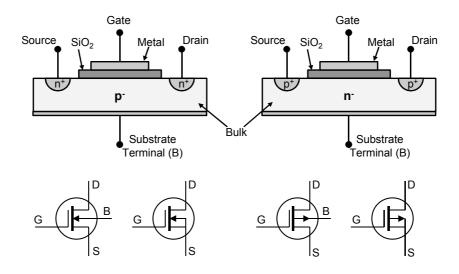

In MOSFETs the gate electrode is a piece of metal, separated from the semiconductor by a layer of oxidised silicon (see figure 2.3). This gate oxide acts as a dielectric and electrically insulates the gate from the junction. Because of this, the MOSFET has a very high input impedance of several megohms, and virtually no current flows during any part of the input cycle. However, the oxide layer is very thin, and is susceptible to damage from electrostatic discharge, so special precautions are necessary when handling MOS devices. A p-channel FET conducts when the gate voltage is low, and an n-channel FET conducts when the gate voltage is high.

Figure 2.3: MOSFET transistors (n-channel and p-channel) and their symbols.

The dominant semiconductor technology is CMOS, which uses a combination of both n-channel and p-channel MOSFETS. The main advantage is its very low static power consumption; power is only dissipated when the circuit switches, allowing many gates to be integrated into each IC, resulting in higher performance than is possible with bipolar technology.

#### 2.1.1 Combinatorial Logic

A CMOS inverter can be built with only two complementary MOSFET transistors (see figure 2.4). When the input voltage is high, the output is connected

Figure 2.4: A CMOS inverter and transmission gate, and their symbols.

to ground, and when it is low, the output is connected to the drain voltage,  $V_{DD}$  (typically 1.8, 2.5, 3.3 or 5V). A transmission gate is used like a switch; when the input *S* is high (and *S'* is low), the input *A* appears at the output *Q*, and when *S* is low (and *S'* is high), the output is in a high impedance state, effectively disconnected.

Figure 2.5: CMOS NAND and NOR gates and their symbols.

Two other combinatorial logic gates, the NAND and the NOR, are shown in figure 2.5, along with their truth tables in table 2.1. Other logic gates, such as AND and OR gates can be easily constructed by following the output of a NAND or NOR gate with an inverter.

| A | B | Q | A | В | ( |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |   |

| 0 | 1 | 1 | 0 | 1 | ( |

| 1 | 0 | 1 | 1 | 0 | ( |

| 1 | 1 | 0 | 1 | 1 | ( |

Table 2.1: Truth tables for NAND and NOR gates.

#### 2.1.2 Sequential Logic

In combinatorial logic circuits, the output is a function of only the current inputs. More complex circuits use sequential logic, with memory that is generated by feeding the output of a logic-block back in to the inputs. The output of a sequential logic circuit is a function not only of the current inputs, but also of past inputs. The simplest sequential logic block is the latch (see figure 2.6). When the clock input is high, the output follows the data input, but when the clock input is low, the output retains its current level no matter what appears on the data input. This is known as a level-triggered, or transparent, latch because it is triggered by the level of the clock input. However, most sequential logic is edge-triggered, meaning that the output only takes on the value at the input at the rising edge of the clock. This is achieved using two transparent latches in series, the second triggered by the inverse of the clock, producing what is known as a D-type flip-flop (see figure 2.6).

Figure 2.6: CMOS transparent latch and flip-flop and their symbols.

#### 2.2 Programmable Logic

When custom logic devices are needed in a system, there are a number of different options available. Simple circuits can often be built out of discrete logic components, but many systems are more complex, consisting of the equivalent of tens of millions of logic gates, and this quickly becomes unfeasible. Another option is to use a microprocessor, which offers great flexibility and is functionally very versatile, but due to its inherently serialised processing, for many tasks it is just too slow, when compared to the hugely parallel processing available in a dedicated logic circuit.

Application-specific integrated circuits (ASICs) are made up of successive layers, etched directly onto a silicon wafer using a photographic mask, and offer the highest level of complexity and speed. In full-custom ASICs, all mask layers are customised, and designing a new IC takes a huge amount of time and effort, as each individual transistor needs to be specified. In a standard-cell-based ASIC all layers are also customised, but a library of standard cells are available for higherlevel functions, reducing the design effort to some extent. Another type of ASIC technology is the mask-programmable gate array (MPGA), which consists of an array of standard blocks, with only the interconnect layers being customised [12]. This reduces the manufacturing lead-time, but any design changes still require a complete new manufacturing run.

Field programmable logic devices have no custom mask layers or custom logic cells; they are programmed by the user. They have the advantage over custom-designed ASICs that the design and verification process is much faster, and (in technologies which are not one-time programmable) the configuration can be updated at a later time to fix errors, or simply to upgrade the firmware. For small to medium volumes they are also much cheaper. The disadvantage is that all the programming logic takes up space in the chip, leaving less space for the actual design. In a 0.18μm process an FPGA typically holds 1500 gates/mm<sup>2</sup> compared to 60 000 gates/mm<sup>2</sup> for an ASIC, and runs at a maximum clock speed of 100 MHz, compared to 600 MHz in an ASIC. However, the density of these devices is increasing rapidly, and in many situations it is the speed of the input/output logic that limits the amount of processing that can be done, so FPGAs are becoming powerful enough to replace ASICs in more and more situations.

### 2.3 History of Programmable Logic

#### 2.3.1 The PROM

The first type of user-programmable chip that could implement logic circuits was the PROM [13] (see figure 2.7). The *n* address lines represent the input to the logic function, the decoder translates each of the  $2^n$  possible combinations to a logic signal on one of  $2^n$  lines, and the *m* data lines are different functions of the inputs. Filling the memory appropriately allows any arbitrary logic function to be generated [12]. The  $2^n$  lines generated by the decoder are known as product terms, and are logical ANDs of the input lines (or their inverses). If each product term is a function of all of the input lines (or their inverses), as is the case here, then they are known more specifically as minterms, and each will be active for only one possible input combination. Each function is simply a logical OR of all the minterms for which the corresponding bit in the memory is high. This method of representing a logic function is known as a sum of products (SOP).

Figure 2.7: Memory used as programmable logic. (Adapted from ref [13])

#### 2.3.2 The PLA and PAL

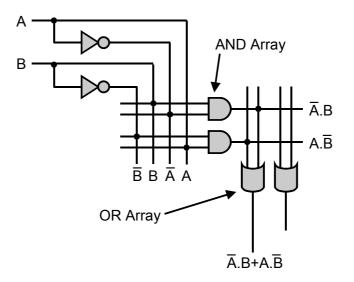

Most logic functions require relatively few product terms, while a PROM contains a full decoder for its address inputs (generating all  $2^n$  possible minterms for the *n* inputs). This makes it an inefficient architecture for implementing logic circuits, as a lot of the logic is never used. A Programmable Logic Array (PLA) is based on the same principle as the PROM device, but without the full decoding of the input variables (see figure 2.8). An array of programmable AND gates provide the product terms, and an array of programmable OR gates provide the sum of products. The number of product terms available is less than the total number of minterms (in this case 2 instead of 4), but most logic functions can be rewritten to use fewer product terms (e.g. using Karnaugh maps) and made to fit.

Figure 2.8: A very small PLA. (Adapted from ref [13])

The two levels of configurable logic in a PLA make it relatively expensive to manufacture, and also affect the speed performance [12]. To overcome this, Programmable Array Logic (PAL<sup>®</sup>) devices were developed. They are similar to PLAs; with the OR array being fixed instead of programmable, and a number of improvements. The outputs of the OR gates are fed back to the inputs of the AND array, allowing a reduction in the number of terms in some functions at the expense of speed. At the outputs of the OR gates there are flip-flops, also with

their outputs fed back to the inputs of the AND array, allowing more complex systems to be built, such as state machines. The I/O pins are programmable, with tri-state outputs, allowing them to be used for input, output, or bi-directional signals.

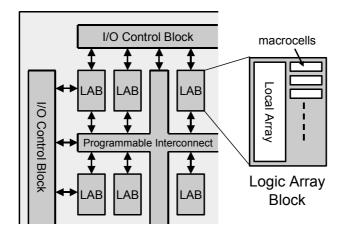

### 2.3.3 The CPLD

Small programmable devices, including PLAs and PALs, are known collectively as Simple Programmable Logic Devices (SPLDs). As technology advanced, the capacity of SPLDs grew; but with these architectures, the structure of the logic planes grows very quickly as the number of inputs is increased, so the logic becomes less efficiently used. To get around this, Complex Programmable Logic Devices (CPLDs) were developed. These are effectively arrays of PAL-like blocks (known as macrocells) connected together with a programmable interconnect (see figure 2.9).

Figure 2.9: Architecture of a CPLD. (Adapted from ref [13])

Blocks of 8 to 16 macrocells are grouped together with other logic into function blocks, or Logic Array Blocks (LABs), with the macrocells within each function block usually being fully interconnected [13]. Often the function blocks themselves will only be partially interconnected, as it makes the manufacturing process cheaper, but it means that complex designs will be harder to route, and design changes may force the pin layout to be changed. It also has the effect that the delays between the function blocks are not fixed, whereas with full interconnect the delays are fixed and predictable.

CPLDs are generally CMOS devices, and use non-volatile memory cells (usually EEPROM or FLASH) to define their functionality. Typically, they are insystem programmable (ISP), meaning they can be programmed in-circuit, as opposed to needing to be plugged into a special CPLD-programming unit.

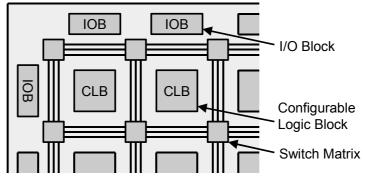

### 2.3.4 The FPGA

The architecture of CPLDs makes it difficult to increase the capacity beyond the equivalent of about 50 SPLD devices. The highest capacity devices, Field Programmable Gate Arrays (FPGAs), are based on a different architecture, similar to MPGAs. They are made up of an array of up to about 100 000 configurable logic blocks (CLBs), surrounded by programmable I/O blocks, and connected by a programmable interconnect network (see figure 2.10). The blocks are not fully interconnected, but sophisticated software is used to route the logic.

Figure 2.10: Architecture of an FPGA. (Adapted from ref [13])

FPGAs can be either coarse-grained or fine-grained. Coarse-grained FPGAs contain large logic blocks containing two or more look-up tables, two or more flip-flops, and other logic such as multiplexers and fast-carry logic. Fine-grained FPGAs, on the other hand, contain a large number of simple logic blocks containing either a 2-input logic function or 4-to-1 multiplexer, and a flip-flop. They make more efficient use of the active components, but require greater

routing resources, and are generally slower and less dense. An example (from a Plessey device) is shown in figure 2.11.

Figure 2.11: Example of a fine-grained logic cell. (Adapted from ref [13])

# 2.4 Memory Technology

### 2.4.1 Fuses and Antifuses

Field programmable devices are programmed after the manufacturing process, and the configuration has to be stored in some form of memory. There are several technologies available for this, each with its own advantages and disadvantages. The original technology used was fuse technology. A metal link creates a normally closed connection, and the device is programmed by passing a relatively large current through the fuse, melting it and opening the connection.

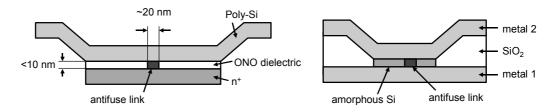

Figure 2.12: Antifuses: (a) ONO, (b) amorphous silicon. (Adapted from ref [13])

A variation of this is antifuse technology; it is now much more widely employed as it uses a modified CMOS technology. An oxide-nitride-oxide (ONO) antifuse (see figure 2.12a) consists of an insulating ONO layer sandwiched between conductive polysilicon and  $n^+$  diffusion layers [13, 14]. The device is programmed by applying a current of 5-15 mA, causing the thin dielectric to melt, and form a small antifuse link with a typical resistance of about 500  $\Omega$ , and allowing current to flow through the device. The amorphous silicon (or metalmetal) antifuse (see figure 2.12b) is similar to the ONO variety, with the advantages that the connections are made directly to metal; they have a lower programmed resistance (typically about 80  $\Omega$ ), and have less parasitic capacitance. Antifuses are small and radiation hard, but they are slow to program, cannot be reprogrammed, and their properties can vary over time, creating reliability issues.

#### 2.4.2 The EPROM and EEPROM

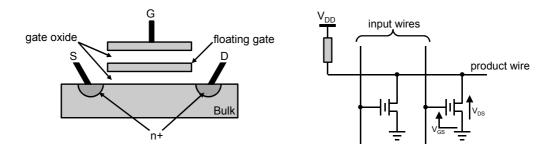

Another technology used is the EPROM, which is only slightly larger than an antifuse. It is similar to a standard n-channel MOSFET, with an extra *floating gate* (see figure 2.13a). In normal operation, the floating gate has no charge and the field effect transistor can be switched on or off by the gate voltage. To

Figure 2.13: An EPROM memory cell: a) schematic, b) use in wired-AND. (Adapted from ref [13] (a) and ref [12] (b))

program the device,  $V_{DS}$  is set to a large voltage (~12 V) creating energetic, or hot, electrons in the bulk. The gate voltage  $V_{GS}$  is set to a positive voltage, attracting some of the electrons, which tunnel through the gate oxide and are trapped in the floating gate, producing a negative charge. This increases the threshold voltage enough so that the transistor is then permanently switched off, even with a positive gate voltage up to  $V_{DD}$ . An EPROM cell can be used in a programmable AND-plane (see figure 2.13b) where each input wire is connected to a separate EPROM cell and can be disabled by programming the relevant cell. If the device is built with a UV-transparent window, it can be erased by being exposed to UV light. This gives the trapped electrons enough energy to return to the substrate, therefore erasing the program; although it requires about an hour of exposure before the device is completely erased, and cannot be done in-circuit.

An EEPROM (or E<sup>2</sup>PROM) is similar to an EPROM, but uses an electric field to remove the trapped electrons, allowing this to be done in-circuit. Because of this, the cells are generally about twice as large as those in an EPROM. Some newer devices use FLASH memory, which is a type of EEPROM, but the electric field is applied to large areas of the memory at once so the erase time is much shorter, and the cells are smaller, being only slightly larger than in an EPROM.

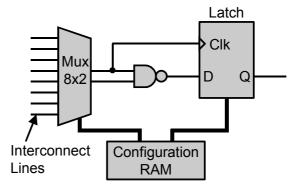

#### 2.4.3 SRAM

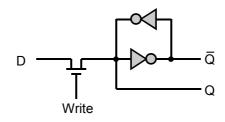

Many devices use static RAM (SRAM) technology (see figure 2.14). SRAM cells are relatively large, and are volatile, so any program will be lost when the power is removed. However, most SRAM devices are in-system programmable, and are designed to automatically boot at power-up from a PROM, which typically takes no more than a few hundred milliseconds. SRAM is widely used in FPGAs, where the function generators are often implemented as look-up tables. In this way, the tables can be made writeable and therefore used as memory blocks as well as function generators.

Figure 2.14: An SRAM memory cell. (Adapted from refs [13, 15])

Static RAM is relatively expensive to produce, and a cheaper alternative, often used in computers, is dynamic RAM (DRAM). In DRAM, memory bits are stored on capacitors, and accessed through a transistor. However, the charge on the individual capacitors has a tendency to leak away, so DRAM has to be regularly refreshed every 50 ms or so. Because of this, DRAM is not suitable for use in programmable logic devices, since all the configuration data must be constantly available.

A summary of the different memory technologies and their main properties is given in table 2.2.

| Name            | Re-programmable      | Volatile | Resistance<br>(Ω) | Capacitance<br>(fF) | Technology |

|-----------------|----------------------|----------|-------------------|---------------------|------------|

| Fuse            | No                   | No       | (Data not av      | ailable)            | Bipolar    |

| Antifuse (ONO)  | No                   | No       | 300-600           | 5                   | CMOS+      |

| Antifuse (a-Si) | No                   | No       | 50-100            | 1.2                 | CMOS+      |

| EPROM           | Yes (out of circuit) | No       | 2k-4k             | 10-20               | UVCMOS     |

| EEPROM          | Yes (in-circuit)     | No       | 2k-4k             | 10-20               | EECMOS     |

| SRAM            | Yes (in-circuit)     | Yes      | 500-2k            | 10-20               | CMOS       |

Table 2.2: Summary of Programming Technologies.(Adapted from refs [12, 13])

# 2.5 The Xilinx Virtex-II Range of FPGAs

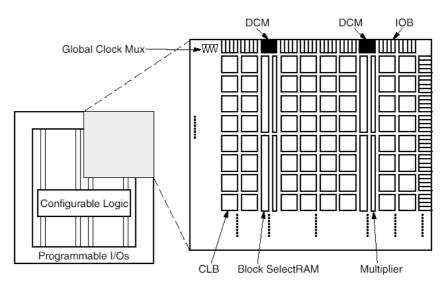

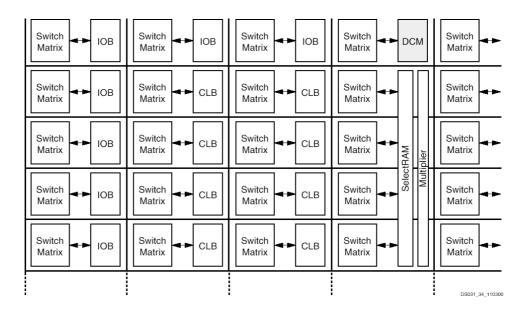

The Virtex-II range of FPGAs from Xilinx<sup>®</sup> is based on the previous Virtex and Virtex-E families, with sizes ranging from 40 K to 8 M system gates. It is SRAM based, and built on 0.15 µm technology, allowing clock speeds in excess of 300 MHz. The general layout consists of an array of configurable logic surrounded by programmable I/O (see figure 2.15). The configurable logic consists mainly of configurable logic blocks (CLBs, described in section 2.5.1), with some of the columns (from 2 to 6 depending on the size of the device) containing 18-kbit block RAMs and 18-by-18-bit multipliers in place of the CLBs, and a digital clock manager at the top and bottom of the column [16].

<sup>&</sup>lt;sup>®</sup> The Xilinx name is a registered trademark. Virtex, Virtex-E and Virtex-II are trademarks of Xilinx Inc.

Figure 2.15: Xilinx Virtex-II Architecture. (From ref [16])

The differences between the members of the Xilinx Virtex-II family are shown in table 2.3. The devices are named by their size, expressed in thousands of system gates (the number of NAND-gates needed to build an equivalent design in discrete logic), preceded by XC2V (Xilinx Virtex II). The table gives the width and height of the array of CLBs, and the number of slices (4 times the number of CLBs). Then the number of multipliers and block-RAMs are given (the same since they are paired together) and the total size of the block-RAMs (18 kbits times the number of BRAMs) followed by the number of Digital Clock Manager blocks, the number of tri-state buffers, and the maximum number of I/O blocks (which may be less, depending on the type of package). Finally the table gives the number of bits needed to configure the device.

| Device    | CLB<br>Array | Slices  | Multipliers/<br>BRAMs | BRAM<br>(kbits) | DCMs | 3-State<br>Buffers | Max.<br>IOBs | Config.<br>Bits |

|-----------|--------------|---------|-----------------------|-----------------|------|--------------------|--------------|-----------------|

| XC2V40    | 8 x 8        | 256     | 4                     | 72              | 4    | 128                | 88           | 338 208         |

| XC2V80    | 16 x 8       | 512     | 8                     | 144             | 4    | 256                | 120          | 597 408         |

| XC2V250   | 24 x 16      | 1 536   | 24                    | 432             | 8    | 768                | 200          | 1 591 584       |

| XC2V500   | 32 x 24      | 3 072   | 32                    | 576             | 8    | 1 536              | 264          | 2 557 856       |

| XC2V1000  | 40 x 32      | 5 1 2 0 | 40                    | 720             | 8    | 2 560              | 432          | 3 749 408       |

| XC2V1500  | 48 x 40      | 7 680   | 48                    | 864             | 8    | 3 840              | 528          | 5 166 240       |

| XC2V2000  | 56 x 48      | 10 752  | 56                    | 1 008           | 8    | 5 376              | 624          | 6 808 352       |

| XC2V3000  | 64 x 56      | 14 336  | 96                    | 1 728           | 12   | 7 168              | 720          | 9 589 408       |

| XC2V4000  | 80 x 72      | 23 040  | 120                   | 2 160           | 12   | 11 520             | 912          | 14 220 192      |

| XC2V6000  | 96 x 88      | 33 792  | 144                   | 2 592           | 12   | 16 896             | 1 104        | 19 752 096      |

| XC2V8000  | 112 x 104    | 46 592  | 168                   | 3 024           | 12   | 23 296             | 1 108        | 26 185 120      |

| XC2V10000 | 128 x 120    | 61 440  | 192                   | 3 456           | 12   | 30 720             | 1 108        | 33 519 264      |

Table 2.3: Virtex-II family members.

(Adapted from ref [17])

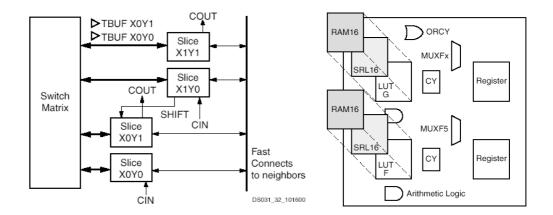

## 2.5.1 Logic Blocks

In the Xilinx Virtex-II FPGA family, each CLB contains four similar slices (see figure 2.16a) arranged in two columns with separate carry chains (used for implementing arithmetic functions and sum of products logic) and a single shift chain (used for implementing shift registers). There are also two tristate buffers

Figure 2.16: Virtex-II logic blocks: (a) CLB, (b) slice. (From ref [17])

45

which are accessible to any of the slices via the switch matrix [17]. Each slice (see figure 2.16b) contains:

- Two independent function generators, implemented as 4-input look-up tables (LUT F and G), which can be reconfigured as 16x1-bit RAMs (RAM16) or 16-bit variable-tap shift registers (SRL16). If used as RAM, the look-up tables in a CLB can be combined into a larger memory blocks, from 16x8-bit to 128x1-bit. When used as shift-registers, the slices can be combined into one long 128-bit shift-register with dynamic access to any bit in the chain.

- Multiplexers (MUXF5 and MUXFx) to combine the outputs of the function generators and produce functions with larger numbers of inputs. Along with the function generators, MUXF5 can generate functions of five inputs, and MUXFx can generate functions of 6, 7 or 8 inputs, depending on the slice in the CLB.

- Logic for building fast carry chains (CY), used to build efficient addition and subtraction logic.

- A dedicated OR gate (ORCY) connecting carry logic with the output of the corresponding ORCY in the adjacent slice, allowing easy production of large sum of products chains.

- Logic for other arithmetic functions, such as efficient multiplier implementations.

- Two registers, configurable as either edge-triggered D-type flip-flops, or as level-sensitive latches.

Depending on its size, each Virtex-II FPGA can have between 64 and 11 648 CLBs. On top of that, it can have up to 168 18-kbit dual-port block RAMs. Each port of each block RAM can be individually configured for various widths (see table 2.4). In the 9, 18 and 36-bit widths the full 18 kbits are accessible with one bit per byte available for parity or for any other use. In the narrower configurations, the parity bits are not available and only 16 kbits are accessible.

| Width (bits) | Depth (bits) | Addressable bits |

|--------------|--------------|------------------|

| 36           | 512          | 18 k             |

| 18           | 1 k          | 18 k             |

| 9            | 2 k          | 18 k             |

| 4            | 4 k          | 16 k             |

| 2            | 8 k          | 16 k             |

| 1            | 16 k         | 16 k             |

Table 2.4: Virtex-II block-RAM configurations.(Adapted from ref [17])

Associated with each block-RAM is an 18-bit twos-complement signed multiplier. The switch matrix is optimised to feed one input from an 18-bit wide block RAM, although they can be used separately. This is because many digital signal-processing applications use a multiplier-accumulator function for finite and infinite impulse response (FIR and IIR) digital filters.

Each FPGA has 16 clock inputs, and a number of global clock buffers used to distribute the clocks to the synchronous logic elements. There are also up to 12 Digital Clock Managers (DCMs), which are based on delay-locked loops (DLLs). Unlike phase-locked loops (PLLs) they are completely digital, meaning they are less affected by temperature and supply voltage variations. However, PLLs generally have lower jitter, as they tend to filter out higher frequency components. The DCMs are used to de-skew the clock signals, ensuring that they remain in phase over the whole device, and perform clock multiplication and division, generating a wide range of clock frequencies from a single clock source.

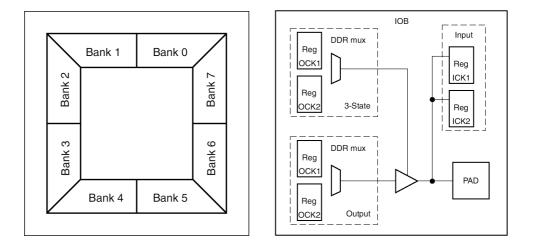

### 2.5.2 I/O Blocks

Connections to the outside world are made through programmable input/output blocks (IOBs). Each pin can be an input, an output, or bi-directional, and neighbouring pairs of IOBs can be combined to provide differential signalling [17]. Groups of IOBs are organised into eight banks (see figure 2.17a), each of which can operate at a range of voltages from 1.2 to 3.3 Volts, independently of the core voltage of 1.5 V; this allows a number of I/O signalling standards to be supported while maintaining a low core voltage. The increasing

density of FPGAs means that there is little space for termination resistors, especially with ball grid array packages. To help with this, each bank contains a digitally controlled impedance system, where a single pair of resistors provides a reference to set the series and/or parallel termination resistance of the entire bank.

Figure 2.17: (a) I/O banks in Virtex-II flip-chip packages, (b) an I/O block. (From ref [17])

Each IOB (see figure 2.17b) contains six registers, each of which can be configured as an edge-triggered D-type flip-flop or as a level-sensitive latch. Each path (input, output, and 3-state) contains two of these registers, allowing double data rate (DDR) input/output signals by clocking each register 180° out of phase with respect to the other.

#### 2.5.3 Routing Resources

On top of the blocks mentioned, there are a number of local and global routing resources used to connect the blocks together and distribute signals across the device. Unlike previous architectures, the Virtex-II uses Active Interconnect technology, where the signals are fully buffered at each routing interconnect point. This means that signal delays are more precisely controlled and reasonably

Figure 2.18: Virtex-II routing resources. (From ref [17])

independent of signal fan-out, making it easier to route complex designs [17]. Each CLB, DCM and IOB is connected to a switch matrix, and each block RAM and multiplier share four switch matrices between them (see figure 2.18). Each switch matrix provides eight fast connections from the outputs of the associated block back to the inputs, and 16 direct connections to the eight neighbouring blocks. There are 40 horizontal and 40 vertical *double lines* providing connections to every first or second block away in all four directions, and 120 horizontal and 120 vertical *hex lines* providing connections to every third or sixth block. Finally there are 24 horizontal and 24 vertical *long lines* which are bi-directional wires spanning the width and height of the device. In addition to these routing resources

there are a number of dedicated signals such as the global clock nets, and the shift and carry chains.

The routing resources are segmented, allowing designs to be compiled hierarchically, i.e. small modules of the design can be compiled independently, and then moved around the device without affecting their internal timing characteristics. This allows faster compile times, and also permits the portable use of IP cores, which are precompiled modules that can be incorporated into designs and are available from both the device manufacturer and from other companies.

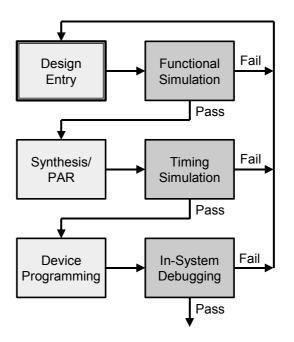

## 2.6 The Design Process

There are several steps to programming an FPGA (see figure 2.19) and a number of tools available for this.

Figure 2.19: The FPGA Design Process.

#### 2.6.1 Design Entry

The first step is the design entry. This can be done in either schematic form, using a hardware description language (HDL) such as VHDL or Verilog, or more often, using a combination of schematics and HDL. Schematics allow more control over the specific blocks used in the device, and their physical placement, although for complex designs this is also more time-consuming. Language-based tools, on the other hand, allow quick design entry, especially for more sophisticated designs. In the past, this was often at the expense of lower performance or density; but logic synthesis tools have significantly improved over recent years, and are becoming better at inferring the correct blocks to use for different language constructs. Language-based tools also permit a higher level of abstraction, making designs easier to port to different devices, but they also pose dangers. For example, if a conditional statement (e.g. *if* or *case*) does not take into account all possible input states, it will be assumed that the output should remain unchanged in these cases. This implies memory (the signal must remember its previous value) and therefore a latch is needed. This is useful if a latch is actually required, but can often be unintentional, leading to code bloat (redundant logic that increases the size of a design without adding any functionality).

Libraries are available from the hardware vendors for blocks that cannot easily be inferred from an HDL. For example, in the Virtex-II, RAM is available in several block-RAMS, as well as distributed-RAM made from combining groups of look-up tables to generate larger RAM structures. By using an array of signals, the synthesis tools are able to infer that RAM is needed, but it is not obvious whether block-RAM or distributed-RAM should be used. If a block-RAM is needed (in order to conserve logic blocks for other functions), it is often better to use a block from the Xilinx-specific library and force the synthesis tools to use the correct type of RAM. This means that the design will not synthesise into devices which do not have the same block-RAMs, and for this reason it is nearly always necessary to decide on which family of FPGAs to use, before starting a design.

Many chip vendors also supply *cores*, which are common design building blocks, from distributed-RAM to PCI-bus interfaces and even microprocessors, implemented in programmable-logic elements. Some simpler cores are available free, whereas cores that are more complex generally have to be bought. They help to speed the development of logic systems, and are becoming an increasingly important design entry tool as FPGAs become denser and can implement evermore complex designs.

51

There are two industry standard hardware description languages available: VHDL and Verilog HDL (usually referred to simply as Verilog). Both were originally designed for describing (and hence simulating) hardware, as opposed to design entry, and because of this, they allow certain constructs that it is not possible to synthesise. However, this is not considered a problem, as in any case different types of hardware have different capabilities, and there will always be constructs that cannot be synthesised in certain types of hardware. There are two main aspects to modelling hardware that HDLs facilitate: true abstract behaviour, and hardware structure. The hardware structure aspect (known as register transfer level, or RTL) is used to describe hardware in terms of registers and the logic joining them together, and is the most easily synthesizable. The true abstract behaviour is useful for higher-level descriptions of hardware systems, and for testing designs, where the test-bench will not be synthesised, and is therefore not described in terms of hardware. These aspects are harder to synthesise, and allow some constructs which are impossible to synthesise, although synthesis tools are getting better at understanding and synthesizing these higher-level descriptions.

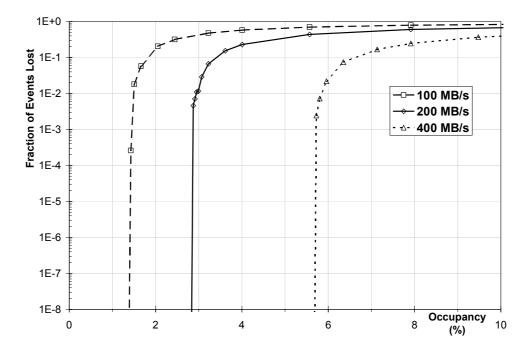

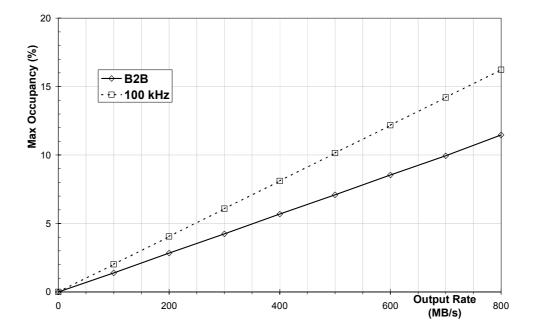

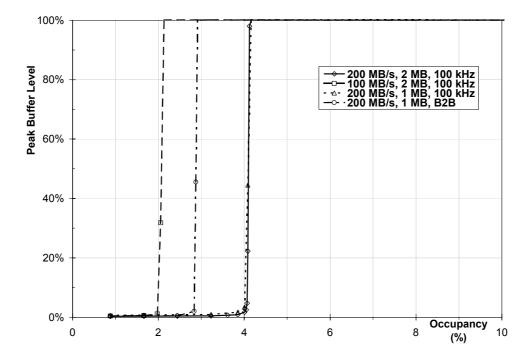

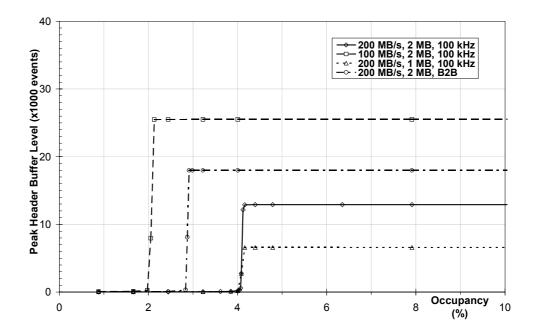

### 2.6.2 Verilog