## INAUGURAL-DISSERTATION

zur Erlangung der Doktorwürde der Naturwissenschaftlich-Mathematischen Gesamtfakultät der Ruprecht-Karls-Universität Heidelberg

vorgelegt von Diplom-Physiker Marcus Gutfleisch aus Heidelberg

Tag der mündlichen Prüfung: 28.03.2006

# Local Signal Processing of the ALICE Transition Radiation Detector at LHC (CERN)

Gutachter: Prof. Dr. Volker Lindenstruth

Prof. Dr. Bernd Jähne

### Lokale Signalverarbeitung des ALICE Übergangsstrahlungsdetektors am LHC (CERN)

Beim Schwerionenexperiment ALICE am LHC (CERN) werden innerhalb des Übergangsstrahlungsdetektors bereits Teile des Datennahme- und Triggersystems integriert. Hierfür wurde ein aus zwei Mikrochips bestehendes Modul entwickelt. Die Detektorsignale werden vorverstärkt und geformt (Preamplifier and Shaper Chip, PASA). Danach werden sie analog-digital-gewandelt und weiterverarbeitet (Tracklet Processor Chip, TRAP).

Diese Arbeit beschreibt die digitale Signalverarbeitung im TRAP-Chip. Die Eingangssignale werden digital gefiltert und durch einen Preprozessor sowie vier CPUs hinsichtlich Teilchenspurabschnitten untersucht. In der Arbeit wird der Bogen gespannt vom Hardware-Entwurf von Filter und Preprozessor über deren Kalibration, die Programmierung der CPUs bis hin zu ersten Anwendungsstudien an einem Prototypensystem.

## Local Signal Processing of the ALICE Transition Radiation Detector at LHC (CERN)

The transition radiation detector of the heavy ion experiment ALICE at LHC (CERN) integrates parts of the data acquisition and trigger system. Therefore, a multi chip module has been developped which incorporates two microchips. Detector signals are preamplified and shaped (Preamplifier and Shaper Chip, PASA). Thereafter they are converted from analog to digital and are processed (Tracklet Processing Chip, TRAP).

This thesis describes the digital signal processing of the TRAP chip. The input signals are filtered digitally. Then, they are analyzed by a preprocessor and four CPUs with respect to segments of tracks. The thesis covers the complete development from hardware design of filter and preprocessor, their calibration, programming of the CPUs, up to first application studies on a prototype system.

# Contents

| 1        | Intr | oduction                                | 1  |

|----------|------|-----------------------------------------|----|

| <b>2</b> | The  | Target Application                      | 3  |

|          | 2.1  | The Large Hadron Collider (LHC)         | 3  |

|          | 2.2  | A Large Ion Collider Experiment (ALICE) | 6  |

|          | 2.3  | The Transition Radiation Detector (TRD) | 8  |

|          | 2.4  | The ALICE Trigger System                | 10 |

|          | 2.5  | The TRD Trigger                         | 12 |

|          | 2.6  | The Global Tracking Unit (GTU)          | 14 |

|          | 2.7  | ALICE TRD Front-end Electronics         | 15 |

| 3        | The  | Tracklet Processing Chip (TRAP)         | 19 |

|          | 3.1  | General Structure                       | 19 |

|          | 3.2  | Chip Development and Design Flow        | 21 |

|          | 3.3  | Global State Machine                    | 23 |

|          | 3.4  | Configuration                           | 24 |

|          | 3.5  | Analog Digital Converters               | 25 |

|          | 3.6  | Digital Filter                          | 26 |

|          | 3.7  | Event Buffer                            | 27 |

|          | 3.8  | Preprocessor                            | 28 |

|          | 3.9  | CPUs                                    | 29 |

|          | 3.10 | Readout Network Interface               | 31 |

| 4        | Eve  | nt Acquisition and Readout              | 33 |

|          | 4.1  | Functional Overview                     | 33 |

|          | 4.2  | Data Transmission                       | 35 |

|          | 4.3  | Zero Suppression                        | 36 |

| <b>5</b> | Digi | ital Filter                             | 39 |

|          | 5.1  | Functional Overview                     | 39 |

|          | 5.2  | Nonlinearity Correction                 | 41 |

|          | 5.3  | Pedestal Correction                     | 42 |

|          | 5.4  | Gain Correction                         | 45 |

#### CONTENTS

|              | $5.5 \\ 5.6$                                                 | Tail Cancellation                                                                                                                                                                                                                                                                                                         | 46<br>49                                     |

|--------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 6            | Loca<br>6.1<br>6.2<br>6.3                                    | al Tracking<br>Overview                                                                                                                                                                                                                                                                                                   | <b>55</b><br>55<br>57<br>61                  |

| 7            | Para<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8 | ameter Calibration         Nonlinearity Correction Filter         Pedestal Correction Filter         Gain Correction Filter         Tail Cancellation Filter         Crosstalk Suppression Filter         Position Correction Look-up Table         Cluster Quality Measure Threshold         Tracklet Program Parameters | 67<br>68<br>69<br>73<br>76<br>79<br>79<br>81 |

| 8            | Fune<br>8.1<br>8.2<br>8.3                                    | ctional Tests         Setup          Overall Method          Test Modules                                                                                                                                                                                                                                                 | <b>85</b><br>85<br>86<br>87                  |

| 9            | Pow<br>9.1<br>9.2<br>9.3<br>9.4                              | ver Consumption         Overview       .         Variation of the Crucial Parameters       .         Dynamic Power Increment       .         Conclusions       .                                                                                                                                                          | <b>89</b><br>89<br>91<br>97<br>99            |

| 10           | 10.1<br>10.2                                                 | Dication<br>Overview                                                                                                                                                                                                                                                                                                      | <b>101</b><br>101<br>103<br>106              |

| 11           | Sum                                                          | nmary and Outlook                                                                                                                                                                                                                                                                                                         | 115                                          |

| $\mathbf{A}$ | Abb                                                          | previations                                                                                                                                                                                                                                                                                                               | 120                                          |

# List of Figures

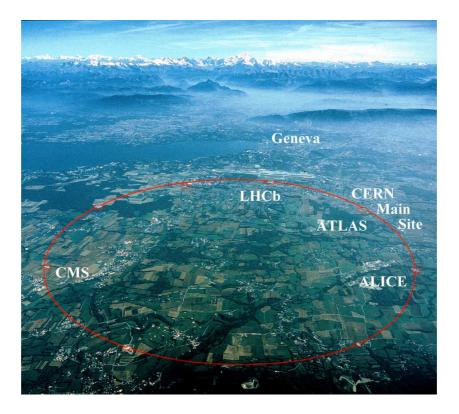

| 2.1  | overview of the LHC ring (CERN Photo)                                                   | 4  |

|------|-----------------------------------------------------------------------------------------|----|

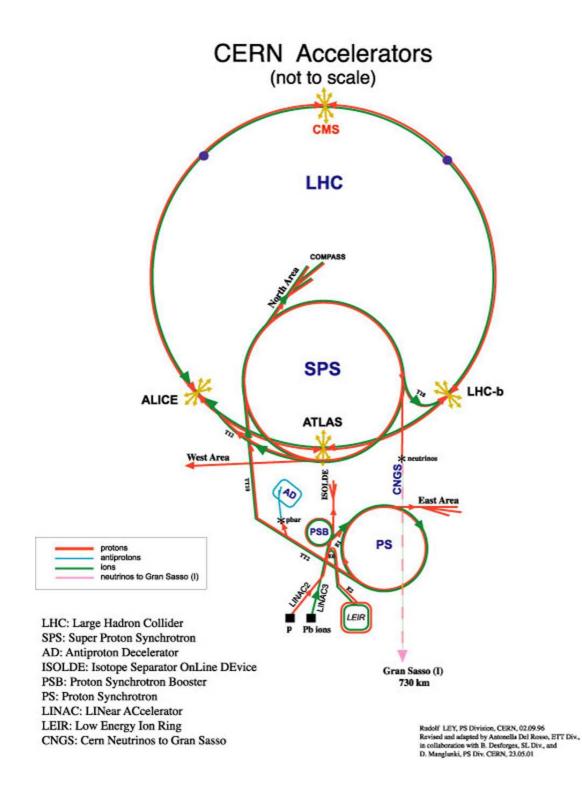

| 2.2  | the CERN accelerator system (CERN Photo)                                                | 5  |

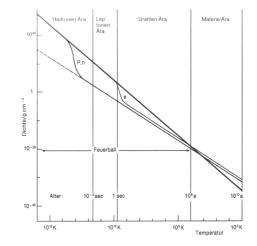

| 2.3  | phase diagram of the Quark-Gluon Plasma (ALICE Colaboration)                            | 6  |

| 2.4  | development of the universe after the electro-weak transition (from                     |    |

|      | [mhw], p. 523)                                                                          | 6  |

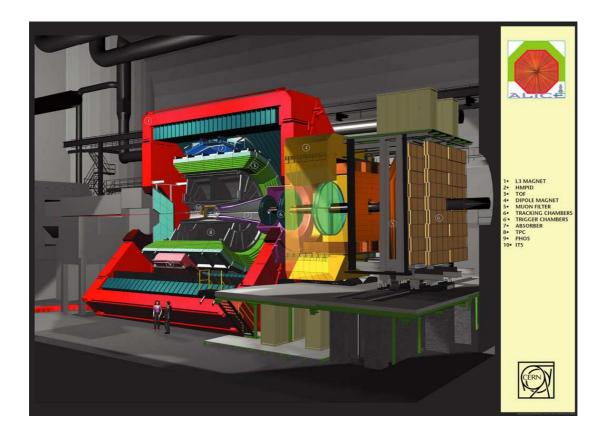

| 2.5  | the ALICE detectors (CERN Photo)                                                        | 7  |

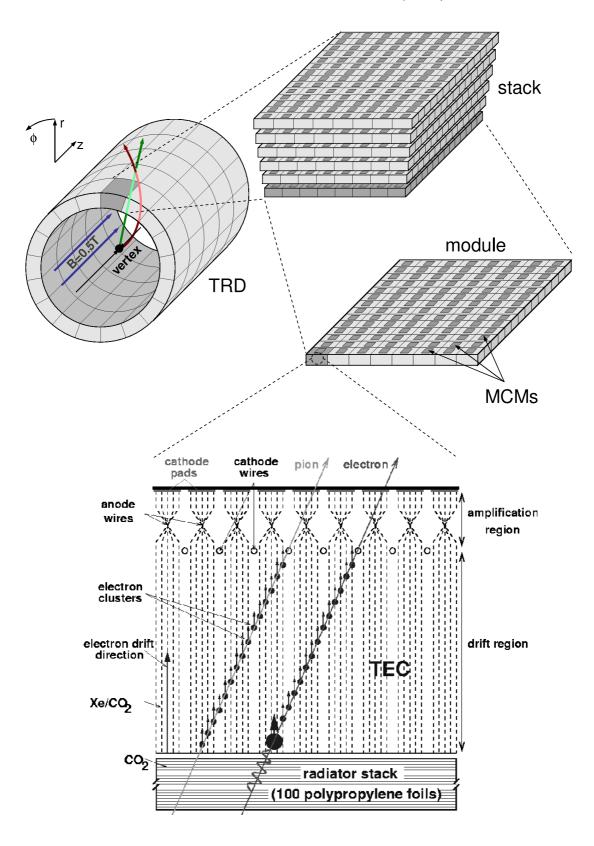

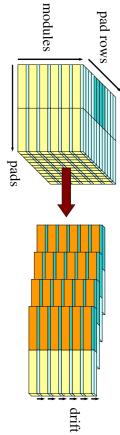

| 2.6  | structure of the ALICE TRD                                                              | 9  |

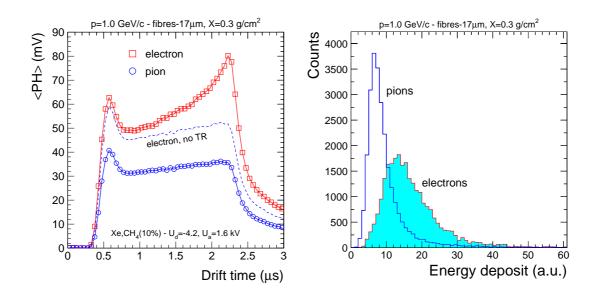

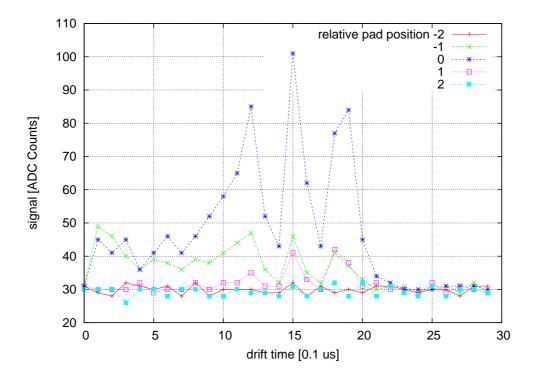

| 2.7  | mean ionization of one detector chamber along a particle track                          | 10 |

| 2.8  | energy deposit of one particle track at a momentum of 1 ${\rm GeV/c}~$ .                | 10 |

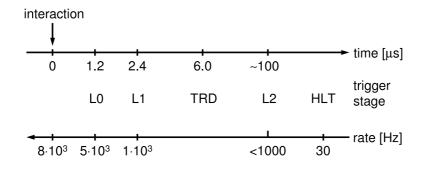

| 2.9  | latencies and rates of the several trigger levels                                       | 11 |

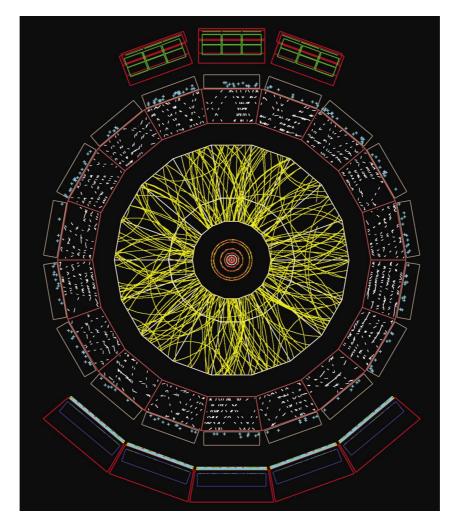

| 2.10 | display of a simulated ALICE event with cut in $60^{\circ} \leq \theta \leq 62^{\circ}$ |    |

|      | (CERN Photo)                                                                            | 12 |

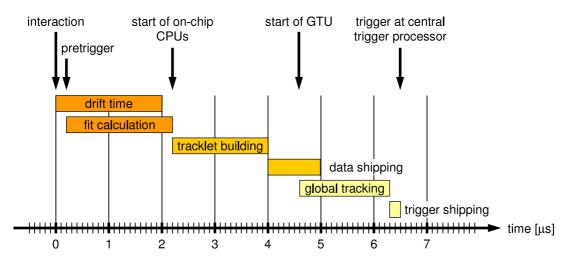

| 2.11 | timing of the TRD trigger                                                               | 13 |

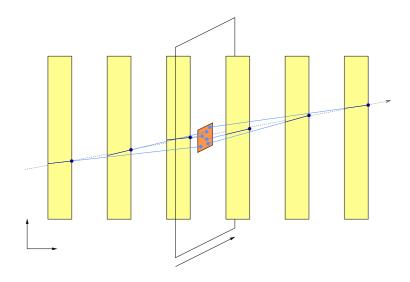

| 2.12 | tracklets matching within the GTU [jc0, p. 29]                                          | 14 |

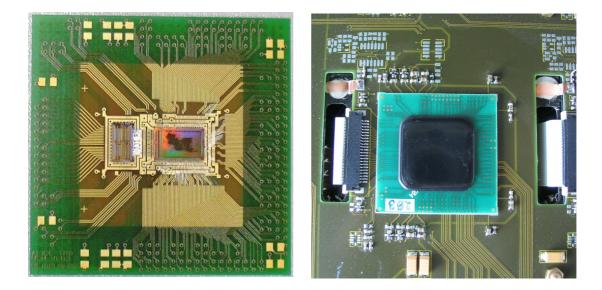

| 2.13 | one Multi Chip Module (MCM) incorporating one PASA on the                               |    |

|      | left hand side and one TRAP on the right hand side                                      | 15 |

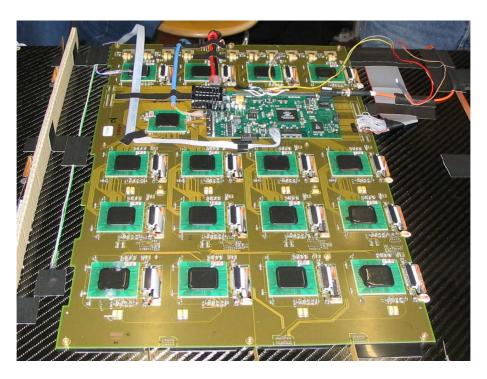

| 2.14 | one MCM coated with glob top, integrated on a readout board and                         |    |

|      | connected to a detector chamber via a ribbon cable on the left $\ .$ .                  | 15 |

| 2.15 | one readout board mounted on a detector chamber carrying 17                             |    |

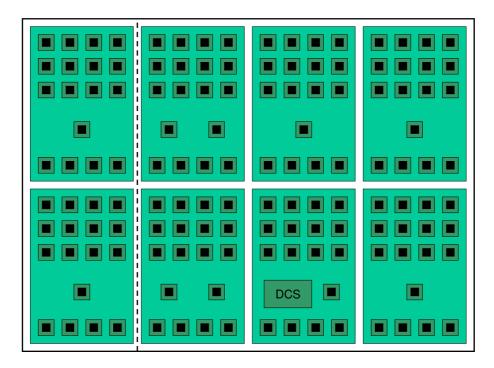

|      | MCMs and one DCS board                                                                  | 16 |

| 2.16 | coverage of the detector chambers by various readout boards. There                      |    |

|      | are half chamber mergers on two of the boards and one DCs board.                        | 16 |

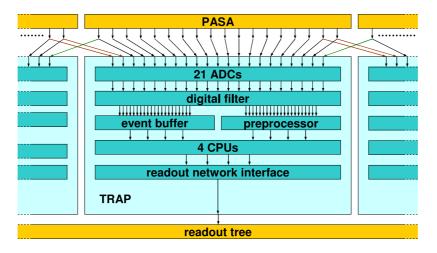

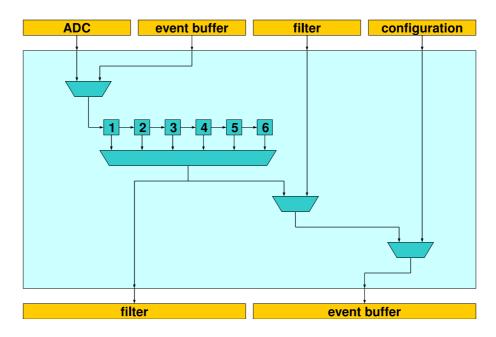

| 3.1  | main signal path of the TRAP chip                                                       | 19 |

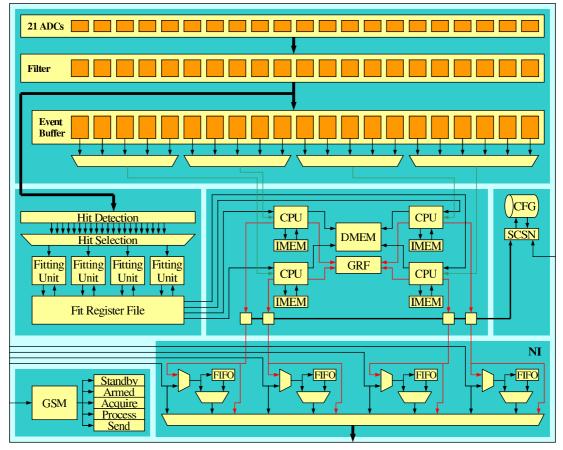

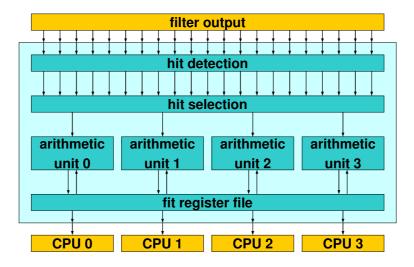

| 3.2  | structure of the TRAP chip                                                              | 20 |

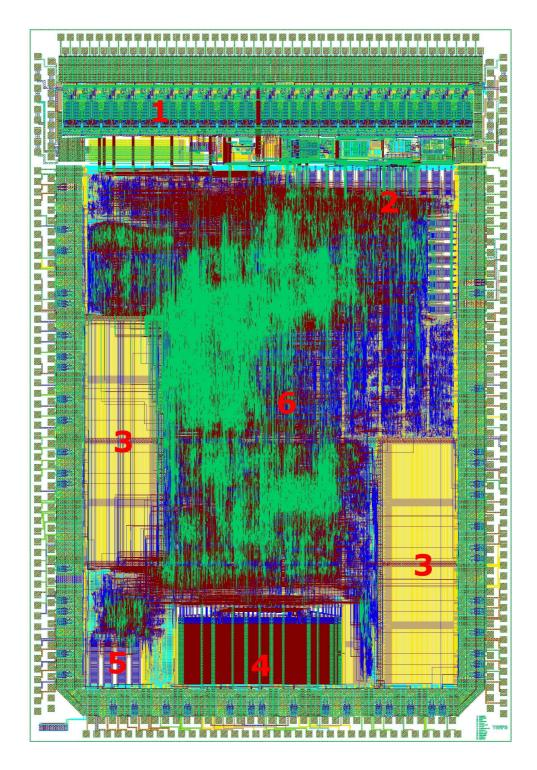

| 3.3  | layout of the TRAP chip: analog digital converters 1, event buffer                      |    |

|      | 2, instruction memory 3, data memory 4, readout network interface                       |    |

|      | 5, standard cell area ('sea of gates') 6                                                | 22 |

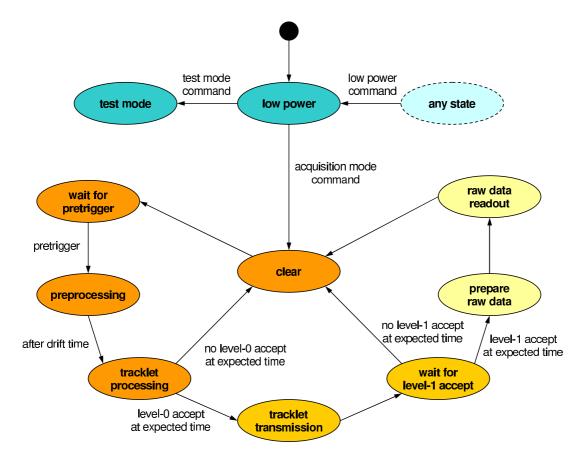

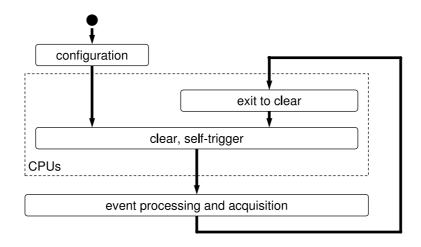

| 3.4  | state diagram of the global state machine                                               | 23 |

| 3.5  | configuration path of the TRAP chip via SCSN network and global                         |    |

|      | input/output bus                                                                        | 25 |

| 3.6  | overall structure of the digital filter                                                 | 26 |

| 3.7  | acquisition control of event buffer and preprocessor                                    | 27 |

#### LIST OF FIGURES

| 3.8<br>3.9<br>3.10<br>3.11                                                                                | data path to filter and event bufferpreprocessor control and data flowCPUs' data and control flowstructure of the Readout Network Interface                                                           | 28<br>29<br>30<br>31             |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

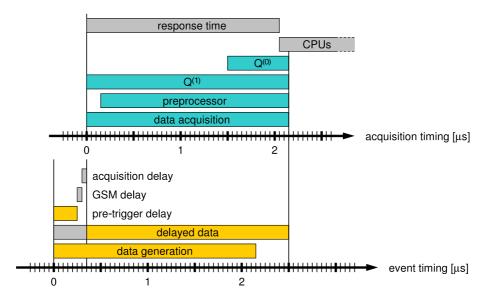

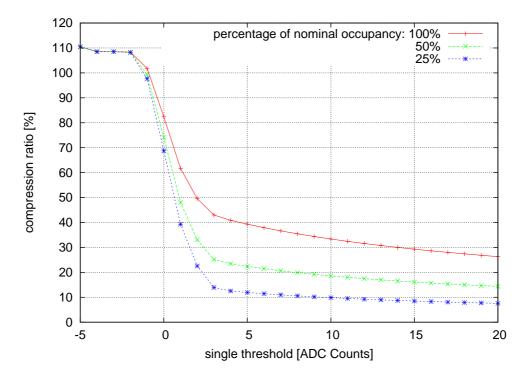

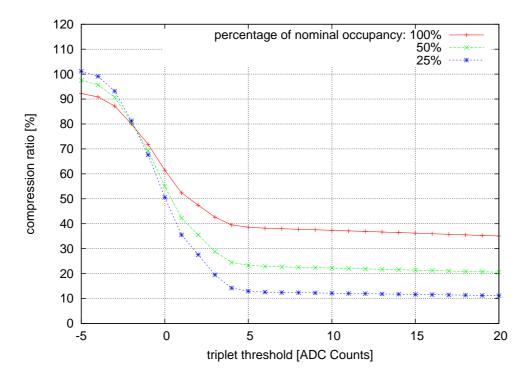

| 4.1<br>4.2<br>4.3                                                                                         | timing of the data acquisition                                                                                                                                                                        | 33<br>38<br>38                   |

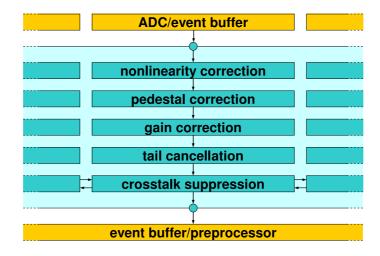

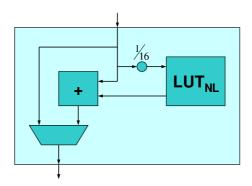

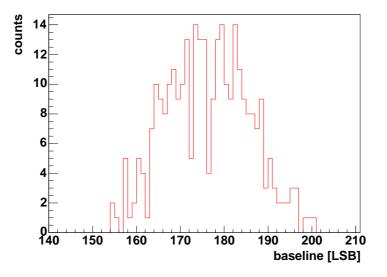

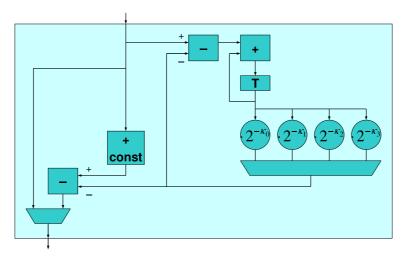

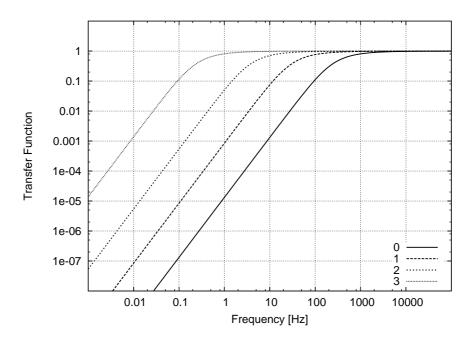

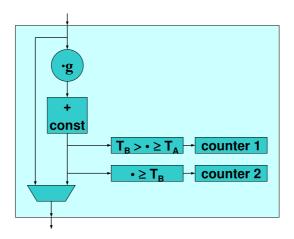

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                           | data flow through the five stages of the TRAP's digital filter structure of the nonlinearity correction filter baseline distribution of one readout board structure of the pedestal correction filter | 39<br>41<br>42<br>43             |

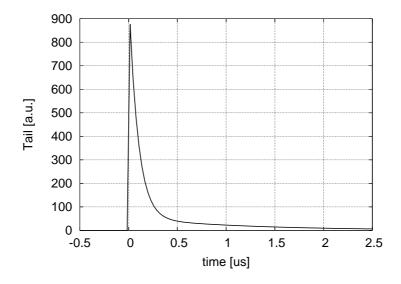

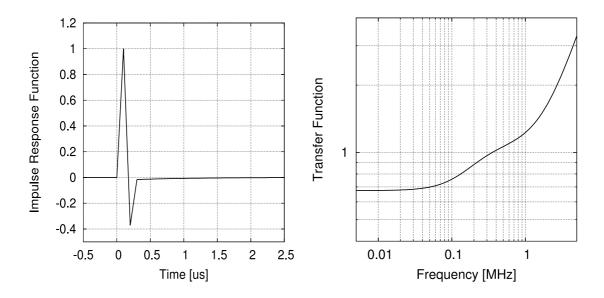

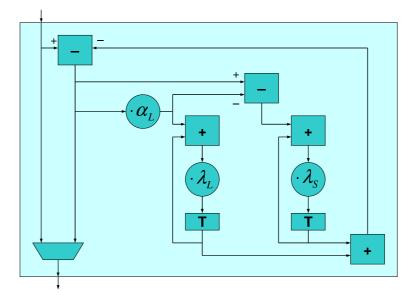

| 5.6<br>5.7<br>5.8<br>5.9                                                                                  | filter at the four available settings                                                                                                                                                                 | 44<br>45<br>46<br>47<br>47       |

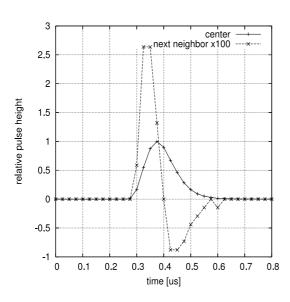

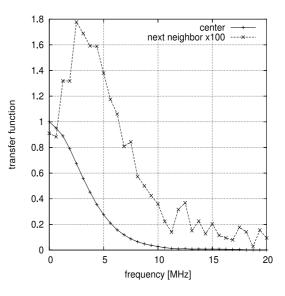

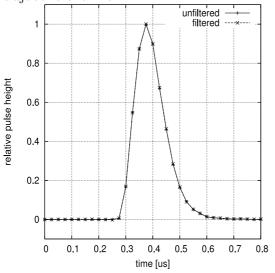

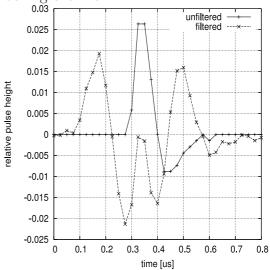

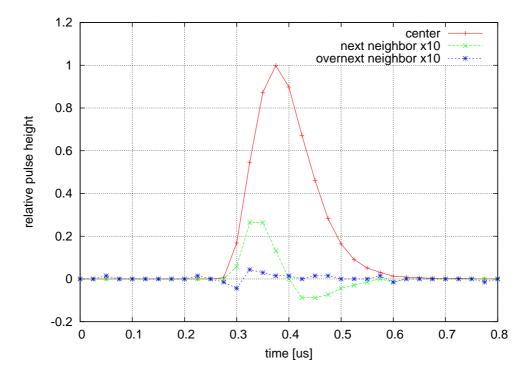

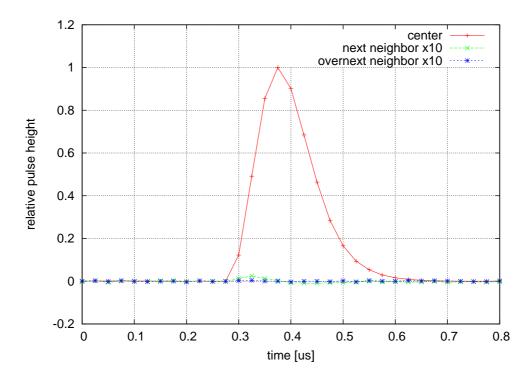

| 5.10<br>5.11                                                                                              | signal shape in a pulsed channel and induced signal shape in an adjacent channel                                                                                                                      | 48<br>50                         |

|                                                                                                           | frequency spectrum of the signal induced by a pulse to a neighbor-<br>ing channel                                                                                                                     | 50                               |

| 5.14                                                                                                      | the crosstalk suppression filter                                                                                                                                                                      | 50<br>50                         |

| 5.15                                                                                                      | structure of the crosstalk suppression filter                                                                                                                                                         | 52                               |

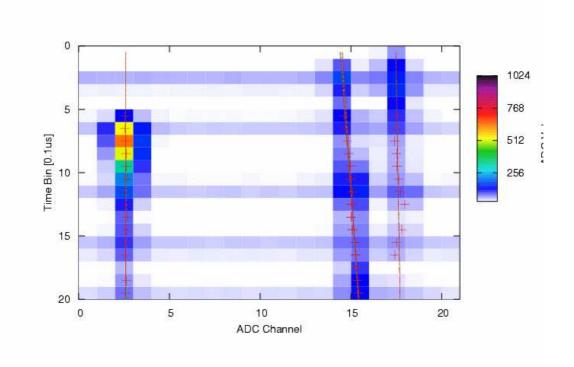

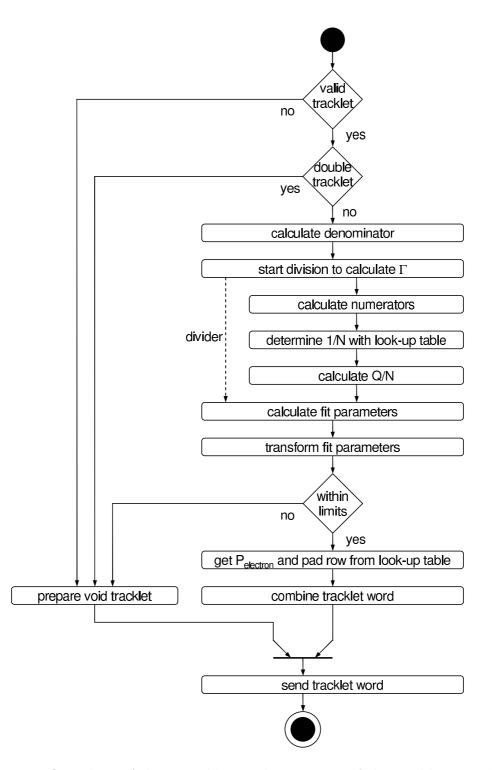

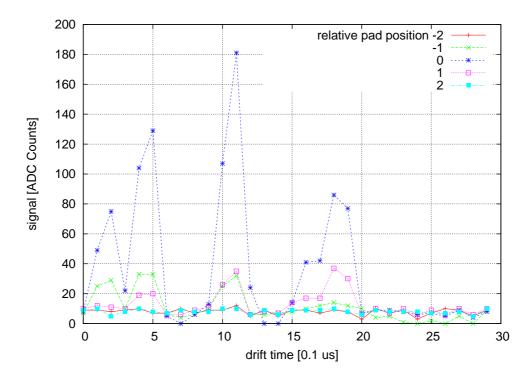

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4 \\       6.5 \\     \end{array} $ | example event                                                                                                                                                                                         | 56<br>58<br>59<br>62<br>66       |

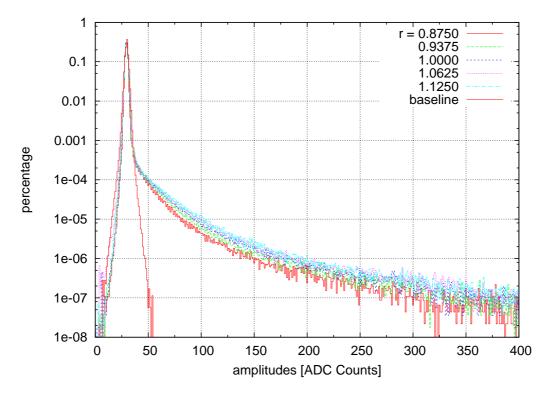

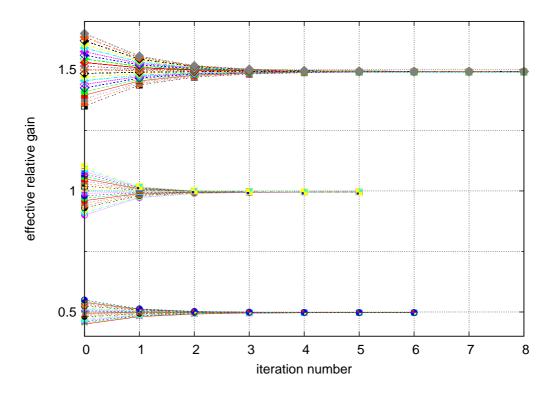

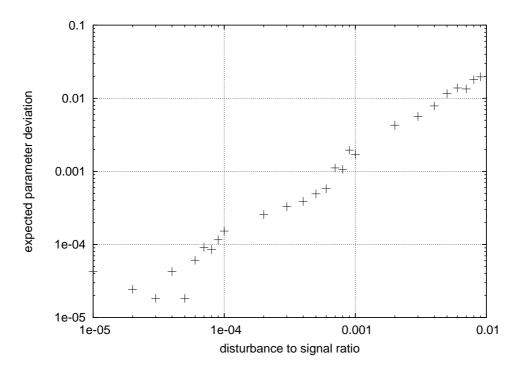

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6$                                                                  | amplitude spectra with various gain settings examples of convergence of local gain balancing                                                                                                          | 70<br>72<br>74<br>75<br>77<br>77 |

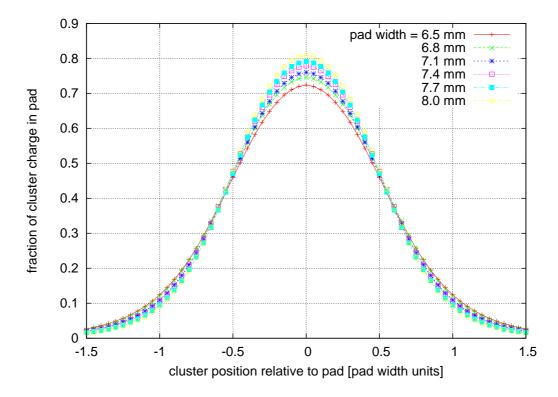

| 7.7                                                                                                       | Pad Response Function of the six pad geometries of the TRD [ac0]                                                                                                                                      | 78                               |

IV

#### LIST OF FIGURES

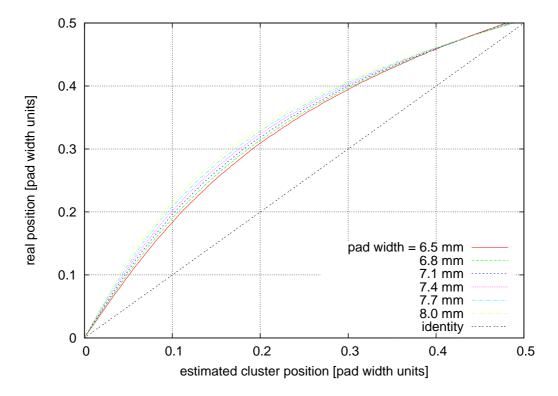

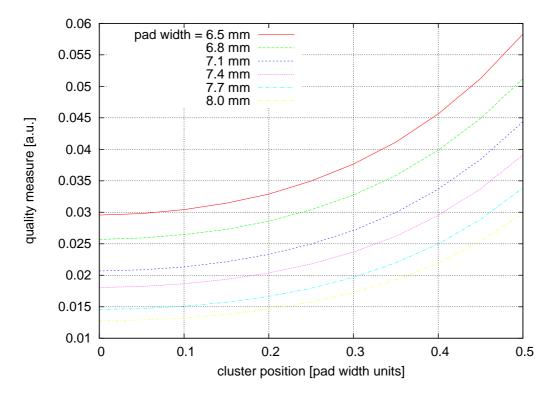

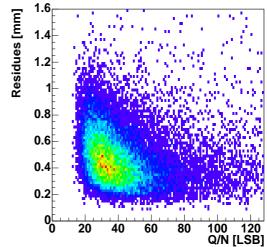

| $7.8 \\ 7.9$ | real cluster position as a function of the estimation                                                                                                           | 78<br>80 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.5          | quality measure for ideal clusters as a function of position                                                                                                    | 00       |

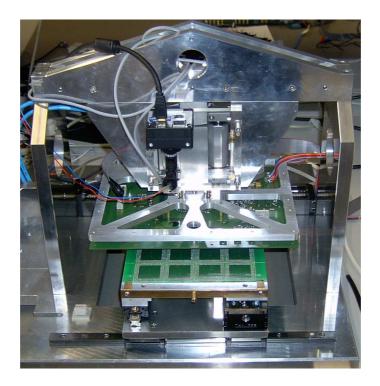

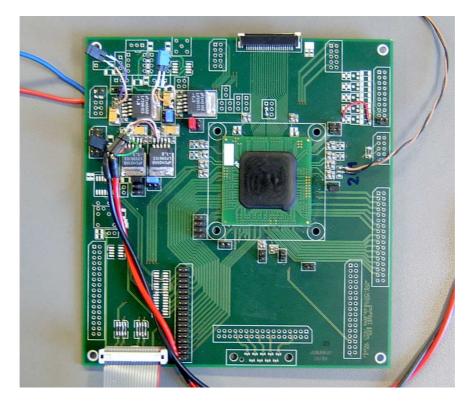

| 8.1          | MCM tester                                                                                                                                                      | 85       |

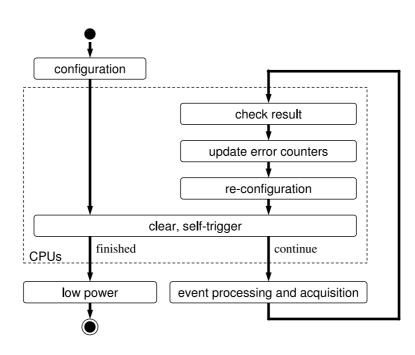

| 8.2          | test procedure of the internal filter tests                                                                                                                     | 86       |

| 9.1          | setup for parameter optimization                                                                                                                                | 91       |

| 9.2          | event loop for filter and preprocessor stimulation                                                                                                              | 92       |

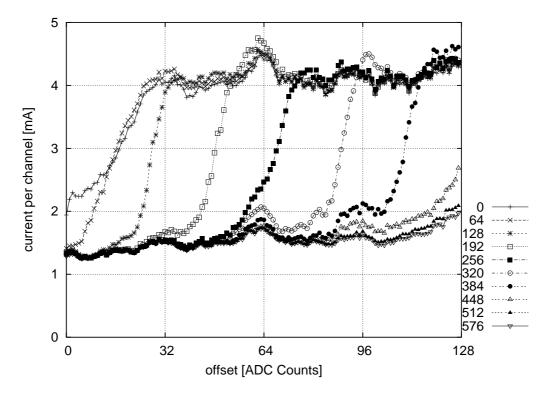

| 9.3          | dependence of the power consumption of filter and preprocessor<br>from different offset settings at various choices of the hit threshold<br>of the preprocessor | 93       |

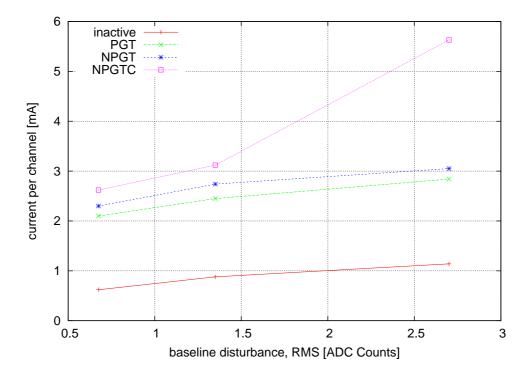

| 9.4          | variation of the baseline disturbance of the input data at four dif-                                                                                            | 90       |

| 0.1          | ferent sets of used filter components                                                                                                                           | 94       |

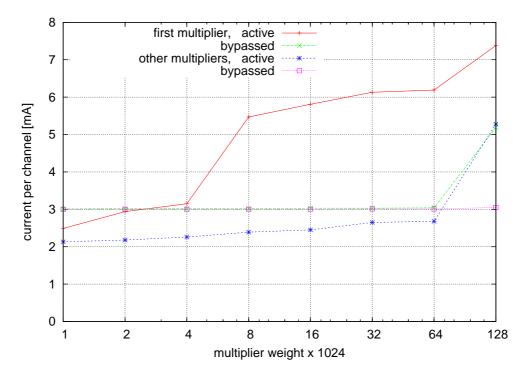

| 9.5          | variation of single bits of the crosstalk multipliers                                                                                                           | 94       |

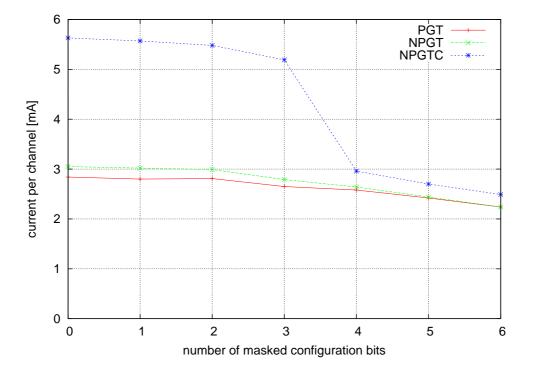

| 9.6          | series of masked lower configuration bits with three different sets                                                                                             |          |

| o <b>T</b>   | of used filter components                                                                                                                                       | 95       |

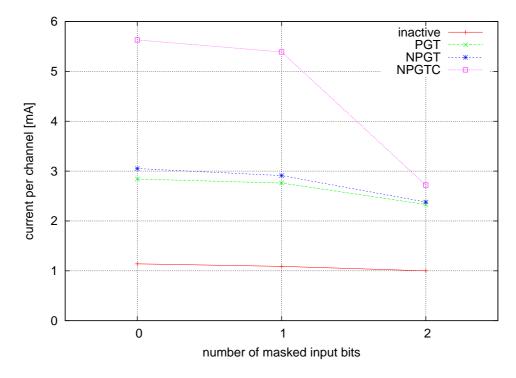

| 9.7          | power consumption as a function of masked input bits                                                                                                            | 96       |

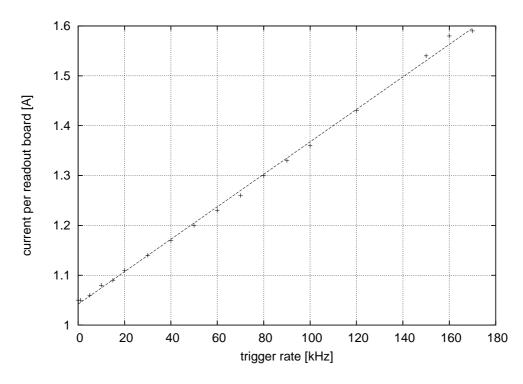

| 9.8          | power consumption increment caused by the processing and trans-<br>mission of tracklets                                                                         | 97       |

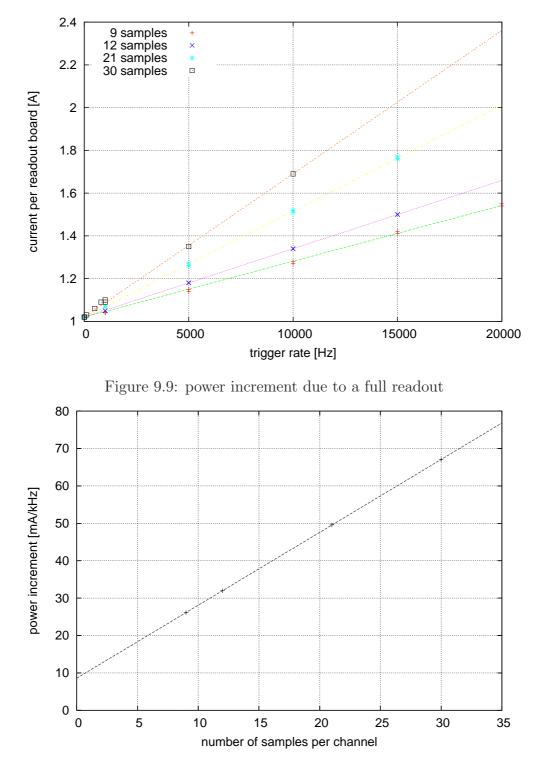

| 9.9          | power increment due to a full readout                                                                                                                           | 98       |

| 9.10         | power increment as a function of transmitted samples                                                                                                            | 98       |

| 0.10         |                                                                                                                                                                 | 00       |

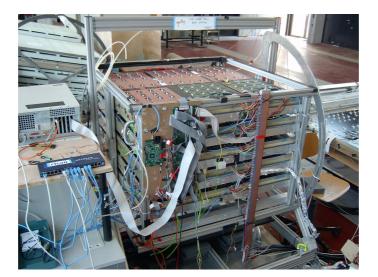

| 10.1         | TRD prototype stack at KIP                                                                                                                                      | 101      |

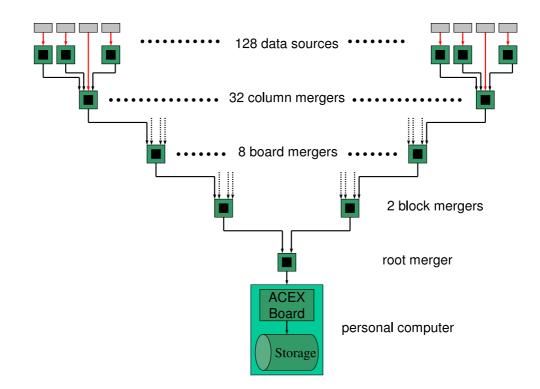

|              | topology of the prototype readout tree                                                                                                                          | 102      |

| 10.3         | the TRD prototype stack at CERN PS (T9) $\ldots \ldots \ldots$                                                                                                  | 103      |

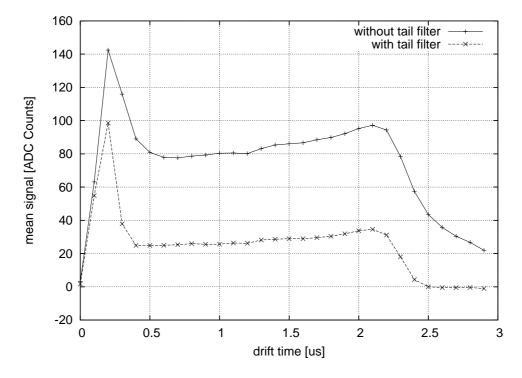

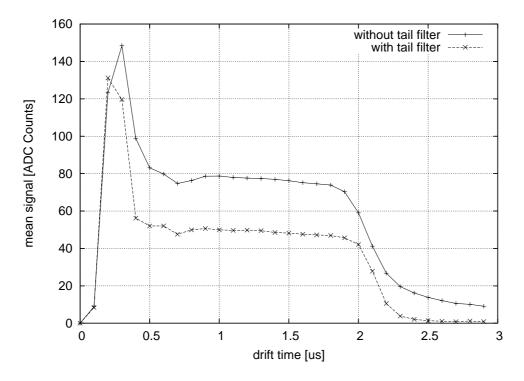

|              | mean signal along the tracks with different filter settings $\ldots$ .                                                                                          | 104      |

| 10.5         | example event with tail cancellation filter                                                                                                                     | 104      |

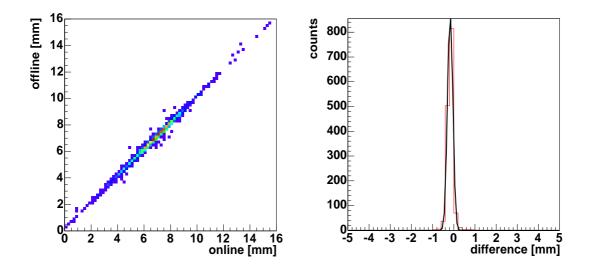

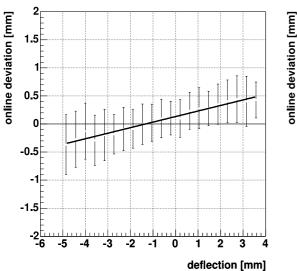

| 10.6         | correlation of deflection lengths, which are based on online and offline analysis                                                                               | 105      |

| 10.7         | distribution of the difference of online and offline deflection lengths                                                                                         | 105      |

| 10.7         | (red) and a Gaussian fit (black)                                                                                                                                | 105      |

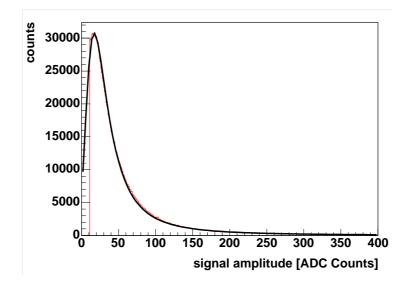

| 10.8         | signal amplitude distribution (red) and a Landau fit (black)                                                                                                    | 107      |

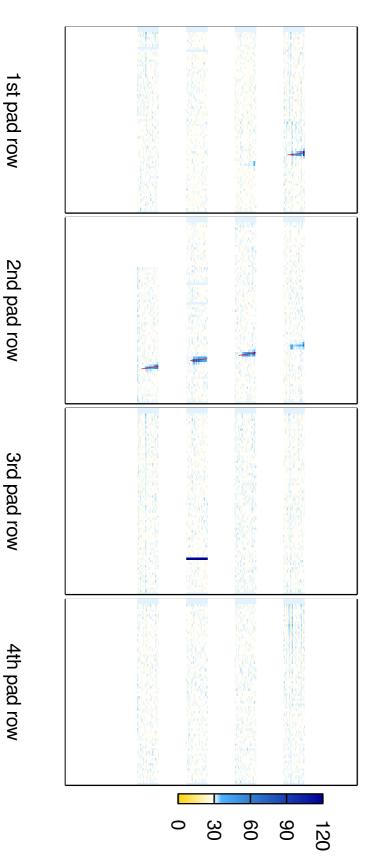

|              | example event with a common track in 1st and 2nd pad row, the                                                                                                   |          |

|              | active part of the stack is marked with orange and dark blue color                                                                                              |          |

|              | in the upper drawing                                                                                                                                            | 108      |

| 10.10        | Dexample tracklet with tail cancellation, taken from third layer,                                                                                               |          |

|              | second pad row of the same event as in fig. 10.9 $\ldots$                                                                                                       | 109      |

| 10.11        | Imean signals along the tracklets                                                                                                                               | 109      |

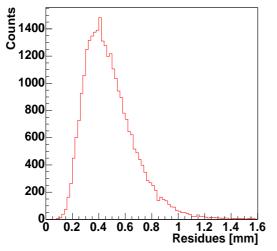

| 10.12        | 2 mean deviation of the hits of a tracklet from the corresponding fit                                                                                           | 110      |

| 10.13        | Bhistogram to show the relation between mean hit charge of a track-                                                                                             |          |

|              | let and mean hit deviation                                                                                                                                      | 110      |

$\mathbf{V}$

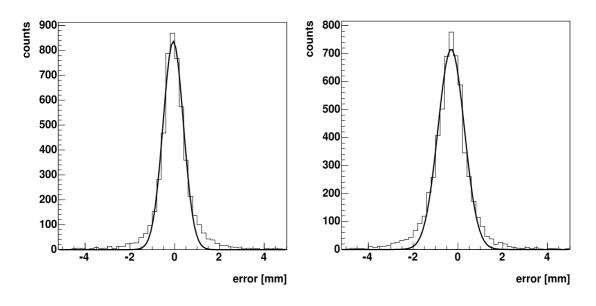

| 10.14 error distribution of the online calculated deflection length in a run   |     |

|--------------------------------------------------------------------------------|-----|

| with active tail cancellation filter and a Gaussian fit ( $\sigma$ =0.45 mm,   |     |

| RMS=1.05 mm)                                                                   | 111 |

| 10.15 error distribution of the online calculated deflection length in a run   |     |

| with inactive tail cancellation filter and a Gaussian fit ( $\sigma$ =0.59 mm, |     |

| RMS=1.09 mm)                                                                   | 111 |

| 10.16 deviation of the online deflection as a function of the deflection       |     |

| with active tail cancellation filter                                           | 113 |

| 10.17 deviation of the online deflection as a function of the deflection       |     |

| with inactive tail cancellation filter                                         | 113 |

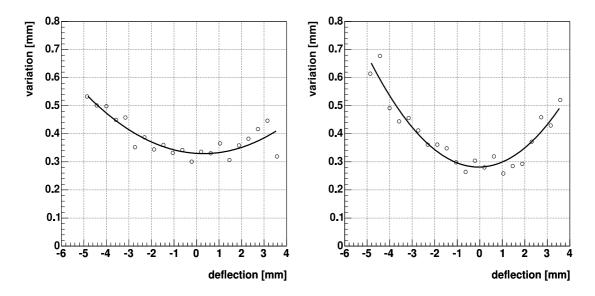

| 10.18 resolution of the online deflection as a function of the deflection      |     |

| with active tail cancellation filter                                           | 113 |

| 10.19 resolution of the online deflection as a function of the deflection      |     |

| with inactive tail cancellation filter                                         | 113 |

|                                                                                |     |

# List of Tables

| 2.1                                                     | some LHC parameters in Lead-Lead mode                                                                                                                                                                                                                                                                  | 4                                       |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 3.1                                                     | operating parameters of the TRAP ADCs                                                                                                                                                                                                                                                                  | 26                                      |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array}$ | data delay contributions                                                                                                                                                                                                                                                                               | 34<br>34<br>35<br>36                    |

| $5.1 \\ 5.2$                                            | pedestal correction filter characteristics                                                                                                                                                                                                                                                             | 45<br>51                                |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$               | Fit Register File access of the CPUs                                                                                                                                                                                                                                                                   | $\begin{array}{c} 63 \\ 65 \end{array}$ |

| 7.1                                                     | ideal quality measure maxima and thresholds                                                                                                                                                                                                                                                            | 80                                      |

| 9.1<br>9.2                                              | average power consumption of an un-triggered MCM<br>power consumption of the digital filter at the core voltage depend-<br>ing on the usage of different filter components (nonlinearity correc-<br>tion N, pedestal correction P, gain correction G, tail cancellation T,<br>crosstalk suppression C) | 90<br>90                                |

# 1 Introduction

In collision experiments, the structure of matter is analyzed to gain a better understanding of nature's fundamental forces and particles. The apparatus for such experiments consists of an accelerator machine and a detector which traces and identifies particles resulting from the collision reaction.

The technology of both accelerators and detectors has developed rapidly during the last decades. By increasing collision energy and improving spatial resolution it has been possible to resolve several levels of the structure of matter. While the demand of higher energies leads to larger accelerator machines with several kilometers circumference, the need of higher accuracy at last causes a huge increment of the amount of raw sensor information, which has to be processed per collision event.

To achieve an optimum utilization of bandwidth to mass storage, a selection of events with interesting reactions has to be performed. The so-called trigger systems take these decisions by the analysis of quickly available sensor information from the detector. While in classical detector architectures there is a spacial separation of readout electronics and sensors from trigger and data acquisition system, parts of the trigger functionality migrate on the detector in experiments of the next generation.

A Large Ion Collider Experiment (ALICE) is one of the four new experiments on the Large Hadron Collider (LHC) which will be built at CERN, Geneva, until 2008. It is the goal to analyze the Quark-Gluon Plasma which will be created by the collision of two lead ions. An indication for an interesting reaction is the observation of electron pairs leaving reaction area with high transverse momentum. To identify those particles the Transition Radiation Detector (TRD) is integrated into the experiment. It makes possible separation of electrons from pion background by transition radiation photons and determination of transverse momentum by calculation of the curvature of the particle tracks.

The readout time of the TRD is about two microseconds. This is fast enough to use it as a primary part of the ALICE trigger system. Therefore particle identification and tracking has to be performed within a time budget of six microseconds. The processing of the TRD's 1.2 million channels within this time corresponds to a data rate of up to five terabytes per second. That challenge is handled by a hierarchical approach. Piecewise tracking and first estimate of particle identity are realized locally within the front-end electronics. On a global stage, track segments have to be combined to common tracks. Here, final particle classification and transverse momentum determination are accomplished. Thus the data flow from the detector to the Global Tracking Unit (GTU) is reduced to the percent level during the trigger phase.

To satisfy the requirements given above, front-end electronics with specialized components has been developed. The detector chambers are covered by readout boards which are carriers of the major building blocks. These are Multi Chip Modules (MCM) which incorporate one analog and one mixed signal chip. The analog Preamplifier and Shaper Chip (PASA) is connected to the detector chamber output channels and drives the analog inputs of the mixed signal chip. This Tracklet Processing Chip (TRAP) performs analog-to-digital conversion, digital filtering, event buffering and local tracking. Due to the well-defined task and tight boundary conditions like timing, analog noise generation and power consumption, the chip was realized as an Application Specific Integrated Circuit (ASIC).

This thesis describes the digital signal path of the TRAP chip which consists of a filter and a preprocessor preparing data for four on-chip CPUs. It is divided into a structural presentation, the elaboration of its functionality and the description of application aspects.

Chapter 2 gives an overview on the target application, the ALICE experiment. It describes how the TRAP chips are interated in the detector design. The general structure and the mayor components of the chip are presented in chapter 3. With the knowledge of the available devices it is possible to realize the mayor functionality of the chip. The data acquisition and readout is described in chapter 4, while the data processing is separated in digital filtering (chapter 5) and local tracking (chapter 6). The signal processing system has to be adapted to the actual boundary conditions. Therefore the system is tuned by a couple of parameters, their calibration is presented in chapter 7. To guarantee the functionality of the chip, a test environment has been developed, it is described in chapter 8. The power consumption of the chip is analyzed in chapter 9. The final proof of concept of the signal processing is given by the application in a prototype environment (chapter 10). The results of the thesis are discussed in chapter 11.

## 2

## The Target Application

#### 2.1 The Large Hadron Collider (LHC)

The Large Hadron Collider (LHC) is an accelerator ring, which will be built for the European Organization for Nuclear Research (CERN) until the end of 2007 (see fig. 2.1). It will be located in the tunnel of the former Large Electron Positron Collider (LEP) and will be operated in two modes. Proton-proton collisions will take place at energies of 14 TeV while collisions of two lead ions reach energies of 1150 TeV.

Particles are injected into the 27 kilometers long LHC ring from a system of accelerators consisting of the Proton Synchrotron (PS) and the Super Proton Synchrotron (SPS) (see fig. 2.2). They are accelerated in two beams in opposite direction and meet at four interaction points. Around these collision points the four experiments of LHC are built.

The experiments ATLAS (A Toroidal LHC Apparatus) and CMS (Compact Muon Solenoid) are based on proton-proton collisions and are intended to analyze nature of mass, especially to proof existence of Higgs Bosons. Furthermore theoretical models beyond the Standard Model are planned to be checked there. LHCb (LHC Beauty Experiment) is supposed to measure CP violation in b-meson systems. Thus it contributes to the understanding of imbalance of matter and antimatter. ALICE (A Large Ion Collider Experiment, see section 2.2) analyzes the Quark-Gluon Plasma which will be created by the collision of two lead ions.

With LHC a new generation of accelerator machines will be put into operation. Collision energies will be about 30 times higher than those of the Relativistic Heavy Ion Collider (RHIC) at the Brookhaven National Laboratory (BNL). Luminosity, a measure for the rate of events of a specific process, will be more than two times larger. In proton-proton mode it will exceed existing accelerators even by two orders of magnitude. Thereby its constituent energy will be seven times larger than that of the Tevatron at the Fermilab. Table 2.1 shows some parameters of LHC in Lead-Lead mode.

Figure 2.1: overview of the LHC ring (CERN Photo)

| Maximum Beam Energy          | 2.76  TeV/u                                |

|------------------------------|--------------------------------------------|

| Luminosity                   | $1 \cdot 10^{27} \mathrm{~cm^{-2}~s^{-1}}$ |

| Time between Collisions      | 0.1 µs                                     |

| Bunch Length                 | $7.94~\mathrm{cm}$                         |

| Beam Radius                  | $15.9 \ \mu m$                             |

| Luminosity Lifetime          | 7.3 h                                      |

| Filling Time (both beams)    | $20 \min$                                  |

| Acceleration Period          | 1200 min                                   |

| Injection Energy             | $0.1774 { m ~TeV/u}$                       |

| Particles per Bunch          | $7\cdot 10^7$                              |

| Bunches per Ring per Species | 592                                        |

| Circumference                | $26.659~\mathrm{km}$                       |

| Dipoles in Ring              | 1232 Main Dipoles                          |

| Quadrupoles in Ring          | 482 2-in-1, 24 1-in-1                      |

| Peak Magnetic Field          | 8.3 T                                      |

Table 2.1: some LHC parameters in Lead-Lead mode  $[\mathrm{pdg0}]$

Figure 2.2: the CERN accelerator system (CERN Photo)

# the second state of the s

Figure 2.3: phase diagram of the Quark-Gluon Plasma (ALICE Colaboration)

Figure 2.4: development of the universe after the electro-weak transition (from [mhw], p. 523)

In ALICE lead ions collide at a total center of mass energy of 1148.0 TeV. Thereby a Quark-Gluon Plasma is expected to be created. A plasma is a system incorporating a large number of particles which are excited by high temperature or pressure (see fig. 2.3). Thus, particles loose their individuality, the whole system corresponds to a sea of the constituents of the former particles. In case of an electromagnetic plasma ions and electrons move independently, only the system as a whole is neutral with respect to electric charge. A Quark-Gluon Plasma consists of the constituents of the nucleons and their interaction particles, the gluons. In this case strong interaction is dominant and only the system as a whole is neutral with respect to its charge, the color charge or flavor.

A Large Ion Collider Experiment (ALICE)

The universe passed through this state about 1 µs after the big bang. It is common belief that all particles, anti-particles and interaction particles were in thermodynamic equilibrium at the beginning of the universe. Because of the high energy density all particles could convert into each other and all forces had equal strength. About  $10^{-35}$  seconds after the big bang strong force decoupled from electro-weak force. After this phase transition, almost all quarks were able to convert to quarks only and leptons to leptons respectively. Another  $10^{-11}$ seconds later the temperature of the universe fell below 100 GeV (kT = 1 eVis equivalent to T = 11604 K) and weak force decoupled from electromagnetic force.

This Quark-Gluon Plasma existed until universe had expanded such that temperature had reached 100 MeV. About  $10^{-6}$  seconds after the big bang quarks combined into hadrons. Figure 2.4 shows the further development of the universe.

2.2

Figure 2.5: the ALICE detectors (CERN Photo)

Due to its expansion, temperature and density decreased continously. Thermal excitation was no longer sufficient for creation of new hadrons (hadron era) and of new leptons (lepton era) afterwards. Down to a temperature of about 3000 K radiation density exceeded density of matter (radiation era). At the current temperature of the universe (cosmic background radiation: 2.7 K) matter dominates radiation (matter era).

The Quark-Gluon Plasma created in ALICE is observed indirectly. Up to 20,000 particles which are leaving the collision area are traced and identified. This allows a reconstruction of reactions within the plasma. ALICE setup incorporates a variety of detectors focusing on different particle properties (see fig. 2.5).

There are three tracking detectors in ALICE. The Inner Tracking System (ITS) is located closest to the beam. It has a length of about one meter and an inner radius of about three centimeters. It consists of multiple layers of silicon pixel, silicon strip and silicon drift detectors. Next, the cylindrical Time Projection Chamber (TPC) covers space from about 57 cm to 278 cm in radial dimension. The within the chambers is ionized locally by charged particles. Due

to an electric field, charges drift to the end caps where they are detected. This takes less than 100 µs on an axial length of the TPC of about 5.1 m. The Transition Radiation Detector (TRD, see section 2.3) is about 295 cm apart from the beam pipe, has a thickness of  $\approx 75$  cm and an axial length of seven meters. It is structured in six layers. Each of them contains a radiator volume and a drift chamber. Charged particles traversing the gas volume can be detected as well as transition radiation photons, which are generated by them.

All other detectors provide particle properties only. Next, there is a Time of Flight Detector (TOF). Its 160,000 parallel pad counters measure the time it takes for the particles to move away from the interaction point. The Photon Spectrometer (PHOS) is an electromagnetic calorimeter made of lead-tungsten crystals. The High Momentum Particle Identification Detector (HMPID) operates by measuring Cherenkov radiation rings.

All detectors above are part of the central area which is enclosed by a magnet generating a field of about 0.5 Tesla. It allows the determination of particle momentum by calculation of its track curvature. In addition there are a couple of forward detectors and a Muon Spectrometer (Forward Multiplicity Detector, FMD; Photon Multiplicity Detector, PMD; Centauro and Strange Object Research, CASTOR; Zero Degree Calorimeter, ZDC).

#### 2.3 The Transition Radiation Detector (TRD)

The TRD is structured in a cylindric geometry (see fig. 2.6). In the angular direction ( $\phi$ ) it is separated into 18 super-modules. Each of them contains five stacks which are arranged in z direction. The TRD stacks are located at a radius position between 2.9 and 3.7 meters. Each of them incorporates six detector modules. These modules consist of detector chambers and front-end electronics. The chambers can be divided into radiator, drift region and amplification region which are about 4.5 cm, 3.0 cm and 0.7 cm thick, respectively. Front-end electronics is mounted on top of these modules.

The radiator consists of polypropylene fiber mats, embedded in Rohacell foam sheets. Both components are extraordinary inhomogeneous in terms of optical density. If a charged particle crosses the transition of media of different optical density, the so-called transition radiation will be emitted. It is concentrated in a forward cone of  $\theta \leq \gamma^{-1}$  where  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$  is the relativistic factor ( $\beta = \frac{v}{c}$ ). Thus transition radiation is a direct measure of particle velocity. At given momentum it can be used to determine the particle mass. In case of the ALICE TRD this radiation is in the range of soft X-rays. It is used to discriminate pions from electrons. Because pions are up to  $\approx 273$  times heavier, their production of transition radiation can be neglected.

Figure 2.6: structure of the ALICE TRD

Figure 2.7: mean ionization of one detector chamber along a particle track

Figure 2.8: energy deposit of one particle track at a momentum of 1 GeV/c

The drift region is filled with a mixture of xenon and carbon dioxide. As both electrons and pions are charged particles, they induce ionization clusters along the track within the gas. Figure 2.7 shows the mean charge along the track. On average, ionization caused by electrons is larger than that of pions. Furthermore the electron's transition radiation photons convert into additional charge clusters of relatively high amplitudes. The exponential probability distribution of this conversion can also be seen here. The first peak of the signal is due to the transition of the particles through the amplification region. The overall ionization caused by one particle is shown in figure 2.8.

Ionization within the gas volume is detected by net charges which are induced on the cathode pads next to the amplification region (see fig. 2.6). Due to an electric field gas electrons within the drift region move into the amplification region within 2  $\mu$ s. There they initiate cascades of ionization which are caused by the cylindrical electric field around the anode wire. While the electrons are caught by the anode wire, the ions slowly drift out of the amplification region.

#### 2.4 The ALICE Trigger System

The event rate is about  $10^4$  collisions per second in lead-lead mode. Only about 100 events per second are considered to contain interesting physics. They are characterized by a couple of criteria like small impact parameters. To optimize

Figure 2.9: latencies and rates of the several trigger levels

the usage of detector data bandwidth a selection of events has to be performed by the so-called trigger system [vl0].

The ALICE trigger system is separated into several levels. They differ by the amount of data on which the decision is based and by the complexity of the data analysis. Trigger levels of longer latency process data of detectors with longer readout time (see fig. 2.9).

The Level-0 Trigger (L0) uses the data of the Forward Multiplicity Detector (FMD). It will accept an event after 1.2  $\mu$ s, if its multiplicity is above some threshold, the interaction point is close to the nominal position and the forward-backward distribution is that of a beam-beam interaction.

In parallel to the generation of the Level-0 Trigger, the TRD Trigger searches for electron positron pairs with high transverse momenta (see section 2.5). For this purpose, the time budget is  $6.5 \ \mu s$ .

The Level-1 Trigger (L1) uses information of the Zero Degree Calorimeter (ZDC) and of the Muon Spectrometer to perform further analysis of centrality and multiplicity of an event. Furthermore, it is looking for muon pairs with high momenta. This decision is taken 6.5 µs after the event. The acceptance of an event by this trigger initiates readout of the TPC.

The Level-2 Trigger (L2) uses TPC readout time for a more detailed analysis like cuts on the mass of muon pairs, search for  $J/\Psi$  particles or inspection of clusters of the FMD. In addition, data from more detectors like the Photon Spectrometer is available.

Finally, the High-Level Trigger (HLT) processes the tracking information of the TRD Trigger in combination with the TPC data. Is performs more sophisticated particle tracking for particle identification and momentum determination. The input event rate of this trigger level is about 200 Hz, while the event rate of the succeeding data acquisition system is about 30 Hz.

#### 2.5 The TRD Trigger

Figure 2.10: display of a simulated ALICE event with cut in  $60^{\circ} \le \theta \le 62^{\circ}$  (CERN Photo)

It is the main task of the TRD trigger to select events with a high probability of the production of so-called heavy vector mesons like  $J/\Psi$  or  $\Upsilon$ . They can be detected via their decay channel into an electron-positron pair. Due to the energy released by the decay they have a high total momentum and a high transverse momentum, consequently. Accordingly, the TRD Trigger is supposed to search for electron-positron pairs with transverse momenta of typically more than 3 GeV/c. The TRD provides the data for the described trigger decision, because it allows to sufficiently estimate transverse momenta by particle tracking, is capable of identifying electrons and its readout time is short enough due to the multiple flat chamber design.

Figure 2.11: timing of the TRD trigger

Electron identification is performed by the separation from pions which are the dominant particles (see section 2.3). Particle tracks have to be reconstructed through the six layers of the TRD. Since there are 20 samples per event of ten bit each within about 1.2 million analog channels this leads to 29 MB of raw data. This has to be processed within a time budget of 6.5 µs. To handle such an amount of data a hierarchical design has been implemented. Because the segments of the tracks (the so-called *tracklets*) in several layers can be detected within a few adjacent channels, their parameterization is performed locally and in parallel. As the bandwidth of the detector is limited by cabling, which is determined by geometrical boundary conditions, it is inefficient to ship the raw data for any processing out of the detector in the given time. Hence, this computation has to be done by the front-end electronics on the detector. To meet these functional requirements as well as tight power and electric noise restrictions, an Application Specific Integrated Circuit (ASIC) has been developed, the Tracklet Processing Chip (TRAP, see chapter 3). On a global stage, only information of detected tracklets is necessary to combine them to common tracks and thus to estimate their transverse momentum (Global Tracking Unit, GTU, see section 2.6). The timing of the TRD trigger is shown in figure 2.11. Detector data is acquired during drift time, which is 2 µs long and starts immediately after the interaction. Meanwhile, data is buffered, digitally filtered and furthermore preprocessed to parameterize the tracklet content. Thereafter, tracking information for the GTU is built locally by four CPUs on each of the TRAP chips. About 4 µs after the interaction TRAP chips are starting to send tracklet data to the GTU. The GTU is starting in parallel and has to make a trigger decision until 6.5 µs after the interaction. About 0.1 µs later the trigger decision will arrive at the Central Trigger Processor (CTP).

#### 2.6 The Global Tracking Unit (GTU)

The Global Tracking Unit (GTU) matches tracklets to tracks within the full TRD. This makes it possible to calculate certain track parameters, especially transverse momentum and particle identity.

Figure 2.12: tracklets matching within the GTU [jc0, p. 29]

Because the detector stacks are arranged in a nearly projective geometry, especially the stiff tracks are located in one of them exclusively. Hence, the problem of global track reconstruction can be reduced to matching in each of the detector stacks. This is performed by 90 Track Matching Units (TMU), corresponding to the number of detector stacks. Each of them receives data from one stack by 12 optical lines. They provide the data which is collected by readout networks in the detector modules.

Inside the GTU, all tracklets of a detector stack are projected to a central plane. If a minimum of four tracklets out of six detector chambers with similar slope can be found in a local neighborhood within this plane, these tracklets will be combined to a global track (see fig. 2.12). This criterion is implemented as a moving window algorithm.

Subsequently, the track parameters can be estimated by using the position and slope information of the incorporated tracklets. A final decision on particle identity is performed by combination of the estimates which were calculated locally and are contained in the tracklet data as well. Structured like this, only little information has to be processed by a common trigger unit within the GTU. It receives all relevant results of the TMUs. At present, a prototype of the GTU is developed, its design is proposed and analyzed in [jc0].

#### 2.7 ALICE TRD Front-end Electronics

Figure 2.13: one Multi Chip Module (MCM) incorporating one PASA on the left hand side and one TRAP on the right hand side

Figure 2.14: one MCM coated with glob top, integrated on a readout board and connected to a detector chamber via a ribbon cable on the left

There are two main tasks, front-end electronics has to accomplish. First, it has to acquire and to buffer detector data. In addition, it has to perform local online tracking. All the functionality is implemented on two chips, which are combined to a Multi Chip Module (MCM, fig. 2.13). Each of them is connected to 18 cathode pads of the detector (fig. 2.14).

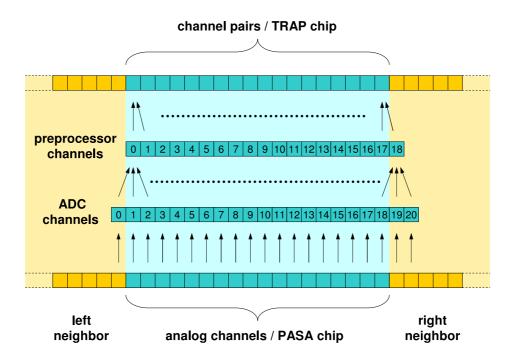

On the MCMs, pads inputs are connected to the Preamplifier and Shaper Chip (PASA). It amplifies the charge fluctuations on its input ports by a factor of 12 mV/fC. Furthermore, it removes long signal components by a first order pole/zero circuit. Finally the signals are shaped by a fourth order filter. This leads to a Gaussian-like point spread function with a peaking time of 70 ns and a FWHM of 120 ns. To prevent artifacts in data processing due to tracklets crossing pads, which are associated to two adjacent TRAPs, three output channels are distributed to the TRAP chips of neighboring MCMs. At last PASA drives 18+3 differential voltage output ports.

The TRAP chip receives signals by 21 differential voltage input ports. Being a mixed mode chip it contains the Analog-to-Digital Converters (ADCs) as well as digital circuits for event buffering and processing (see section 3.1).

The MCMs are integrated on the so-called readout boards (fig. 2.15). Six up to eight of them are used to cover one detector chamber. They provide the

Figure 2.15: one readout board mounted on a detector chamber carrying 17 MCMs and one DCS board  $\,$

Figure 2.16: coverage of the detector chambers by various readout boards. There are half chamber mergers on two of the boards and one DCs board.

configuration network of the chips (Slow Control Serial Network, SCSN, see [rg0]), the fast readout network for tracklet and raw data transmission (see [rs0]), power supply and the clock and pre-trigger distribution.

Each readout board incorporates 16 MCMs which are connected to the chamber to acquire data. In addition there is one MCM which is used for merging of the boards readout stream only (Board Merger). On two of the readout boards another MCM is mounted to merge the data of one half of the chamber (Half Chamber Merger). Here, the final data stream is built. It is sent via an optical transmitter, which is mounted on a mezzanine board, which is next to each of the Half Chamber Mergers.

One readout board per chamber carries a board of the Detector Control System (DCS). It controls the power of a chamber, checks runtime parameters like supply voltage, humidity or temperature, distributes clock and pre-trigger signals and provides the configuration interface for all TRAP chips of one chamber (SCSN). A detailed discussion of readout board components, structure and routing is given in [ir0].

#### 2. THE TARGET APPLICATION

## 3

# The Tracklet Processing Chip (TRAP)

#### 3.1 General Structure

Figure 3.1: main signal path of the TRAP chip

The Tracklet Processing Chip (TRAP) is the core component of the ALICE TRD front-end electronics. It is a mixed mode chip receiving analog signals from the PASA chip (see section 2.7) and providing digital signal processing capabilities. Figure 3.1 shows the main signal path of the TRAP chip.

First, analog signals are converted to digital signals (see section 3.5). Then, they are filtered and stored in the event buffer (see section 3.7). There they are accessible for the on-chip CPUs (see section 3.9) to be read, compressed and sent to the readout network interface. That device collects data of all CPUs and feeds it into the readout network which is organized in a tree structure (see section 3.10).

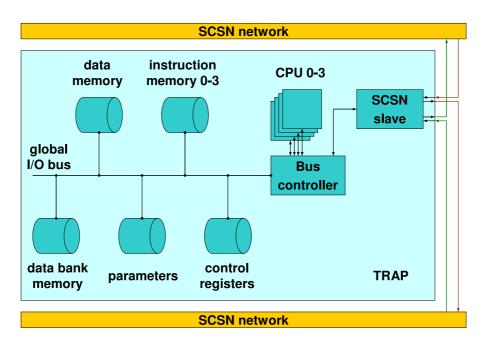

Figure 3.2: structure of the TRAP chip

The signal processing devices of the chip are specialized for local track finding (see chapter 6). It is the first step to detect and fit sub-tracklets within each of the covered signal channels. This is performed by a preprocessor which is working on the basis of the filtered signals (see section 3.8). The CPUs are started to finally process the fit information of the preprocessor. Tracklets with signal in more than one channel are combined and the tracking information for the GTU is built. It is transmitted by the same network as the raw data.

Figure 3.2 shows the detailed architecture of the TRAP chip. It includes the inner structure of the major components, which are discussed in the following sections. There are two additional components of the chip which are not a part of the actual data path. The global state machine controls all actions on the chip and especially synchronizes it to external trigger commands (see section 3.3). The configuration interface is discussed in section 3.4.

#### 3.2 Chip Development and Design Flow

The TRAP chip is produced in the UMC 0.18 µm mixed mode process. A first chip incorporating prototypes of all major components was designed and submitted in May 2002 (TRAP1). A chip prototype providing full functionality has been developed until May 2003 (TRAP2). The final chip was submitted in March 2004 (TRAP3) and is available for testing since July 2004. This chip is used for integration tests, beam measurements at CERN in fall 2004 and continuous measurements of cosmic radiation at the Kirchhoff-Institute of Physics (KIP) at the University of Heidelberg (see chapter 10).

The analog components of the TRAP chip have been developed at the Chair of Microelectronics, Prof. Dr. Tielert, University of Kaiserslautern. The digital components are designed in the VHDL hardware description language and are mapped on a standard cell library provided by Virtual Silicon Technology Inc. The design synthesis has been performed by Synopsis Design Analyzer. All major building blocks like filter channels, preprocessor, network interface, CPUs, etc. were synthesized separately and merged only on higher design levels. The result of the synthesis was exported in a Verilog net-list file.

On the basis of the result of the synthesis and geometrical information of the analog components and standard cells (Library Exchange Format, LEF) the layout of the chip can be designed. For this purpose Cadence First Encounter has been used. It provides all necessary design steps such as floor planning, placement, power planning, clock tree routing and optimization, signal routing and optimization and finally the timing analysis. The latter can be used for back annotation of simulation timing models. Thus, the target speed of 120 MHz for the CPUs, and the readout network interface as well as 10 MHz for digital filter, preprocessor and event buffer was verified. The layout is exported to another intermediate file (Gridded Data Set Format 2, GDS2).

Finally, the chip layout and the layout of the analog components are combined using Calibre by Mentor Graphics Corp. A last consistency check is included by comparing chip layout and schematic net-list (Layout versus Schematic Check, LVS). To ensure producibility the design has to satisfy various process dependent design rules like minimum distance of adjacent signal traces or minimum width of design structures. Thus a Design Rule Check (DRC) has to be performed. Figure 3.3 shows the final layout of the TRAP chip. It is bordered by various input/output pads providing signal connectivity and power supply. Some easily recognizable structures are labeled next to the figure.

A priori, functionality has been verified by simulation on functional level and on gate level using ModelSim by Mentor Graphics Corp. On gate level, timing of each used standard cell and timing of signal propagation between those cells (back annotation) is included into the model.

Figure 3.3: layout of the TRAP chip: analog digital converters 1, event buffer 2, instruction memory 3, data memory 4, readout network interface 5, standard cell area ('sea of gates') 6

# 3.3 Global State Machine

Figure 3.4: state diagram of the global state machine

All functionality of the chip is controlled by a central device, the Global State Machine (GSM). The transitions between its ten states can be initiated by external trigger signals, by internal timers or by commands in the command register which is accessible for configuration and the CPUs via a global input/output bus (see section 3.4). The resulting state diagram is shown in figure 3.4.

After a reset the chip starts up in low power state. All but the configuration interface is disabled and not clocked. The chip can always return to this state by a low power command. It can be left for test mode or clear state by the test mode or acquisition mode command. Leaving the low power state the analog digital converters are enabled and the digital filter is clocked.

The clear state is the entry point to typical operation. The preprocessor is reset and the CPUs are started and clocked to prepare for potential tracklet processing later on. This state is left after the CPUs have finished their clearing procedure. The GSM stays in the following state until a pre-trigger signal occurs. Subsequently, the GSM timers are started and the chip changes to preprocessing state. The event data is acquired and the fit parameters of the preprocessor are calculated. The preprocessor is clocked only in this state. After the drift time of the detector chamber, the acquisition control machine signalizes to the GSM to have finished. This causes the GSM to change to tracklet processing state.

In this state the CPUs are clocked to process the tracklet candidates presented by the preprocessor. This is completed by building of tracklet words which are sent to the network interface. The external level-0 accept signal is expected at a given time after the pre-trigger, which is checked by one of the timers, which has been started at the transition to preprocessing state. The present acquisition sequence will be ended by changing to clear state if no level-0 accept has occurred. If so, the GSM will change to tracklet transmission state during which the network interface transmits the tracklet information. Leaving the tracklet processing state the CPUs are switched off.

The state after tracklet transmission is a wait state for level-1 accept. The accept signal is expected at a time, which is defined by another timer, which has also been started at the transition to preprocessing state. If the signal does not occur, the acquisition sequence is ended by the transition to clear state. If it does, the GSM changes to the raw data preparation state. The CPUs are enabled again to read data from the event buffer and prepare data for transmission. After changing to the raw data readout state, the CPUs fill all data, which is to be sent, into the network interface. It handles the handshaking and communication with the network. After completion the chip returns to clear state and is prepared for another acquisition sequence.

# 3.4 Configuration

To put a TRAP chip into operation, internal parameters have to be set, the CPUs' data and instruction memory have to be initialized, some commands have to be stated via control registers and the data bank memory has to be filled eventually. All those resources are accessible by a chip-global input/output bus (see fig. 3.5). There is one bus controller which drives the write enable signal, the 16 bits wide address bus and the 32 bits wide input data bus. The addressed device is multiplexed to the output data bus.

Both write and read statements on the global input/output bus can be initiated by any of the four on-chip CPUs or by commands received via the external configuration network. To handle concurrent bus accesses a priority driven arbitration is performed by the bus controller [tm, section 8.1].

The configuration network (Slow Control Serial Network, SCSN) is organized in two serial rings of opposite direction. If a TRAP chip within the SCSN network fails, the neighboring chips can close one remaining ring by the assignment of the input of one ring to the output of the other one and vice versa [rg0]. The SCSN

#### 3.5. ANALOG DIGITAL CONVERTERS

Figure 3.5: configuration path of the TRAP chip via SCSN network and global input/output bus

communication is organized in packets, which are generated by the SCSN master of the corresponding ring, and modified or passed over by each of the SCSN slaves in the ring. Thus, a configuration of a TRAP chip corresponds to a series of write packets, which are received by its SCSN slave. It translates them to accesses on the global input/output bus.

The global input/output bus operates with parallel busses and a strobe signal with a 120 MHz timing. The asynchronous and serial SCSN network incorporates one signal only. The packet has a net width of 86 bits including a 16-bit check sum to ensure data integrity. It is enlarged by a variable number of padding bits to guarantee a minimum frequency of signal changes for synchronization.

# 3.5 Analog Digital Converters

The Analog Digital Converter (ADC) used in the TRAP chip has been developed for the special purposes of the target experiment [dm0]. It performs a cyclic successive approximation of its differential analog input signal. Some typical parameters are give in table 3.1. As the internal reference voltage can be adjusted by about 40 % the conversion gain and dynamic range are variable by the same order of magnitude. The phase of the sampling time of the ADC relative to the internal 10 MHz clock is adjustable in order to minimize disturbances of the analog measurements due to digital activity.

| Conversion Gain           | 2.0-2.8  mV/ADC Count |

|---------------------------|-----------------------|

| Dynamic Range             | 2.0-2.8 V             |

| Sampling Rate             | 10.0 MHz              |

| Number of Bits            | 10                    |

| Effective Number of Bits  | 9.3                   |

| Differential Nonlinearity | <0.5 ADC Counts       |

| Integral Nonlinearity     | <0.5 ADC Counts       |

| Power Consumption/Channel | $12,0 \mathrm{~mW}$   |

Table 3.1: operating parameters of the TRAP ADCs

One of the major demands on the ADCs was to combine high quality signal sampling with extraordinary low power consumption. The ADC is designed such that the power consumption can be adjusted downward but this leads to a corruption of faster signals since the dynamics of the circuits is reduced. The ADC is instantiated 21 times for all analog inputs of the TRAP chip plus another one for internal run time parameter checks like temperature and voltages [tm, section 5.2].

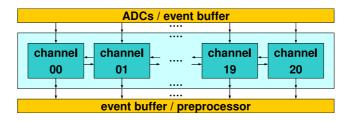

### 3.6 Digital Filter

The digital filter of the TRAP chip receives data of 21 ADCs and distributes it to the event buffer and the preprocessor. For test purposes it is possible to change filter input to the event buffer (see fig. 3.8). The filter is structured channel-wise because the signals are processed almost independently. Only Data of adjacent channels has to be exchanged (see fig. 3.6).

The internal structure of each of the filter channels corresponds to its functionality and is discussed in chapter 5. The filter is operated at the sampling frequency of the ADCs (10 MHz).

Figure 3.6: overall structure of the digital filter

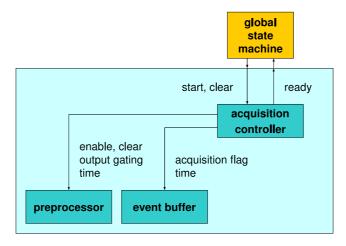

Figure 3.7: acquisition control of event buffer and preprocessor

### **3.7** Event Buffer

The event buffer stores the data of the events. It is steered by a common control module for event acquisition and event preprocessing (see fig. 3.7). It is cleared and started by the GSM and provides a time reference relative to the pre-trigger signal. After a programmable time it indicates readiness to the GSM which proceeds to its next state subsequently (see section 3.3).

The event buffer is organized in 21 independent memory blocks of  $64 \times 11$  bits each. The memory blocks offer two independent ports for reading and for writing. The write port is operated at the ADC's sampling frequency of 10 MHz. The write address is given by the acquisition controller's time tag plus a given offset in acquisition mode. In the other states, it is connected to the global input/output bus. The write data is determined by the selection logic shown in fig. 3.8. If the acquisition controller indicates no acquisition the data can be taken from the configuration interface. For acquisition phase it can be selected whether filtered data or data from the input delay chain is stored. The delay can be set to one up to six samples. The input delay chain is filled by the ADCs or by data taken from the event buffer itself (see below).

The read port is operated at the CPUs' operation frequency of 120 MHz. Typically the read address is set by the CPUs while they are accessing the event buffer via their local input/output bus. Five event buffer channels are assigned to CPU 0 to 2 while CPU 3 is assigned to the uppermost six channels. For test purposes the chip can be set in simulation mode to provide data out of the event buffer as input for the input delay chain (fig. 3.8). Therefore the read address is given by the acquisition controller's time tag plus a given offset. The read data bus is connected to the input multiplexer of the data delay chain and to the data multiplexer of the CPUs' local input/output bus.

Figure 3.8: data path to filter and event buffer

In order to handle write access to event buffer memory an interface between those two clock domains is provided. Thus, address and data of an event buffer write access are buffered and a synchronization logic controls the data flow from the 120 MHz strobe domain into the 10 MHz clock domain. This reduces data bandwidth down to half a word per 10 MHz clock cycle. As the event buffer access during configuration is much slower and write access of the CPUs are for test purposes only the core functionality of the chip is not affected.

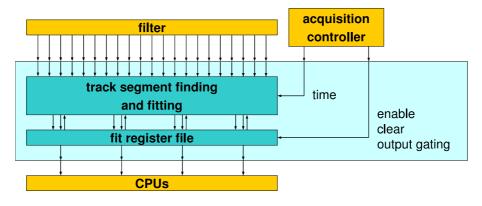

### 3.8 Preprocessor

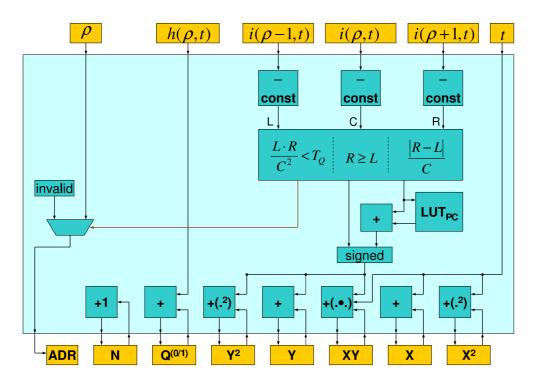

The preprocessor parameterizes track segments in 19 channels by processing triplets of the 21 filter channels. It is steered by and gets timing information for segment fitting from the acquisition controller (see fig. 3.9).

The concept of track segment finding and fitting as well as the corresponding hardware design are discussed in chapter 6. Up to four track segments can be processed in parallel. The fit parameters are stored for each channel. Therefore a memory instance has been implemented, which provides four independent read-modify-write ports with a size of  $19 \times 111$  bits, the Fit Register File (FRF). The memory entries are cleared by the acquisition controller during the GSM's clear state (see section 3.3). They are enabled for writing during a given period of time after the pre-trigger while the GSM is in preprocessing state and the acquisition controller takes care of the precise timing. The time information is

also distributed to the segment finding and fitting unit.

Figure 3.9: preprocessor control and data flow

For further processing by the CPUs up to four tracklet candidates are selected. A tracklet candidate is a pair of adjacent channels with a given minimum number of hits in both channels and another minimum number of hits in its lower channel. It is indicated by its lower channel number. If there are more than four potential candidates, those with the maximum number of hits in both channels are selected.

The sorting is performed in parallel to the fitting arithmetics. The corresponding hardware design is optimized for cell area and not for timing because the cell area increases rapidly with respect to tighter timing constraints and timing is not critical here. After a given time the sorting logic provides a stable result which is signaled by the acquisition controller's output gating flag.

After the fitting period, the addressing of the FRF is switched from the segment finding and fitting unit to the sorting unit in order to distribute the tracklet candidate parameters to the CPUs. Thus, fit parameters of the lower channels of the tracklet candidates are read from the FRF. They are stored in four latches which are gated by the acquisition controller's output gating flag. Subsequently, the address to the FRF is incremented. So the parameters of the upper channels of the tracklet candidates are available in parallel to those stored in the latches. Each CPU incorporates a multiplexer to select the parameters out of its tracklet candidate. For test purposes the sorting unit can be bypassed and an arbitrary address can be defined to read the FRF entry.

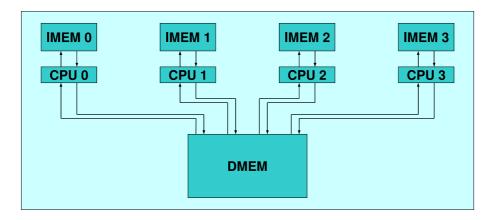

## **3.9** CPUs

The four TRAP CPUs are designed in a Harvard architecture with separated data and instruction memory. There is an individual instruction memory block for each CPU while the data memory is implemented as a common device with four independent ports (see fig. 3.10).

Figure 3.10: CPUs' data and control flow

Since both the data and the instruction flows of the CPUs are independent, the four CPUs represent a Multiple Instruction Multiple Data (MIMD) processor [fl0]. For the instruction memories (IMEM) a single ported  $4096 \times 30$  bits design by Virtual Silicon Technology Inc. has been chosen. Each instruction word contains 24 functional bits plus six redundancy bits. The quad-ported data memory (DMEM) has been developed as a microelectronic full custom design of the size of  $1024 \times 39$  bits. Each data word contains 32 functional bits plus seven redundancy bits. Therefore the hamming distance of the instruction and the data code set is four. Because this allows to correct one bit errors and to detect up to two bit errors, the radiation hardness of the CPUs is improved.

The CPUs are designed with a RISC instruction set, which affords to use a two stage pipeline at an operation frequency of 120 MHz. The small pipeline depth avoids data dependencies in the instruction code, which is useful as the programs, which have to be executed, are quite short.

Each CPU can read the fit parameter registers of the tracklet candidate it has been assigned to. It possesses 16 private registers and accesses 16 additional global registers, which can be used for a fast data exchange in between the CPUs. For communication with other devices on the chip the CPUs are connected to a private input/output bus (e.g. event buffer read access or transactions to readout network interface) and the global input/output bus (see section 3.4). In order to start the CPUs with instruction code which is suitable for a given state of the chip (e.g. tracklet processing, raw data readout) there is an interrupt handler which sets the program counter of the CPUs to an appropriate start address which is defined in the interrupt vector table.

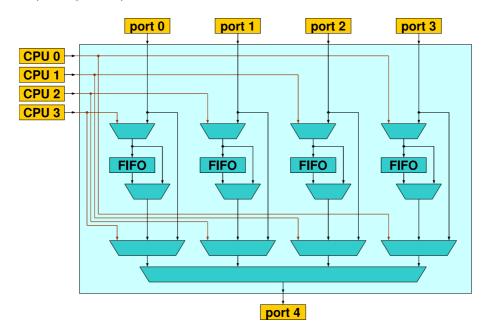

### **3.10** Readout Network Interface

The readout network interface of the TRAP chip is designed to merge data streams of up to four external input sources and those from the four internal CPUs [rs0]. The resulting data stream is forwarded to one external output destination (see fig. 3.11).

Figure 3.11: structure of the Readout Network Interface

The network interface operates in two modi. For tracklet transmission it is important to ship data as fast as possible. Thus, the tracklet words are sent directly to the output multiplexers of the interface module. All incoming data is buffered in the First-In First-Out Memories (FIFOs). In order to speed up data forwarding a FIFO is bypassed if it is empty and no data is contributed from the CPUs (Merger Functionality). The buffering is necessary because there is no handshaking procedure between the ports of two chips in tracklet mode.

In raw data readout mode the amount of data is larger and timing is not that tight. Consequently, some handshaking protocol is performed between the ports of connected chips. In this mode the FIFOs are used to buffer the data coming from the on-chip CPUs. In order to save power, this makes it possible to switch off the CPUs during major parts of the readout while the FIFOs of the network interfaces of all TRAP chips in readout tree are flushed (see section 2.7).

While the CPUs' data word width is 32 bits, the network interface works with words of the width of 16 bits only. Therefore buffers are placed at the input ports of the CPUs to the interface module. This makes it possible to split each incoming word in two successive half words. To improve utilization of the TRAP's input/output pins the internal 16-bit words of the interface module are split again in two 8-bit words which are transmitted on each of the clock edges. At last, the external communication between two network interfaces is performed on a data bus of the width of 8 bits plus a parity bit and a spare bit, one control and one clock/strobe signal at a frequency of 120 MHz Double Data Rate (DDR).

# 4

# **Event Acquisition and Readout**

# 4.1 Functional Overview

Figure 4.1: timing of the data acquisition

While analog-to-digital conversion and signal filtering within the TRAP chip are continuously active, data acquisition and readout are event oriented. The event data is stored in the event buffer, which incorporates one  $11 \times 64$  bits memory for each of the 21 input channels. One data word contains 10-bit ADC data and one parity bit. It can be accessed by the CPUs for test purposes. In addition it is checked continuously in parallel to each read access. The results are monitored in parity violation counters.

For the purpose of zero suppression, the event buffer has been amended by a set of indicator bits. They are used to mark those data words, which are supposed to be transmitted in case of a raw data readout (see section 4.3). The indicators as well as the event buffer memories are accessible for reading by the CPU's private input/output bus. The CPUs compile the data to the actual readout stream, which is transmitted via the network interface (see section 4.2). For test purposes it is copied to the local data memory, where it is visible for the SCSN slave as well.

The timing of the data acquisition is controlled by various configuration settings. In Figure 4.1, there are two time axes. Event timing refers to the primary physical reaction, acquisition timing to the corresponding activity of the TRAP chip. The shift between event and acquisition timing is caused by the delay of the pre-trigger signal and some delay of the GSM which is due to the decoding of the pre-trigger signal and the synchronization of the acquisition to the sampling clock of the chip. The additional acquisition delay parameter is typically set to zero. In order not to loose data, the data is delayed by the front-end electronics to balance the delay of the acquisition machinery (see table 4.1).

| PASA signal rise time             | 70 ns           |

|-----------------------------------|-----------------|

| ADC pipeline delay                | 130 to $140$ ns |

| programmable input shift register | 100 to $600$ ns |

| crosstalk filter shift register   | 0 or 200 ns     |

Table 4.1: data delay contributions

| sample content              | start [ns] | duration [ns] |

|-----------------------------|------------|---------------|

| baseline (pre-sample)       | 0          | 100           |

| amplification region peak   | 100        | 200           |

| drift time                  | 300        | 2000          |

| signal decay (post-samples) | 2300       | 0 to 700      |

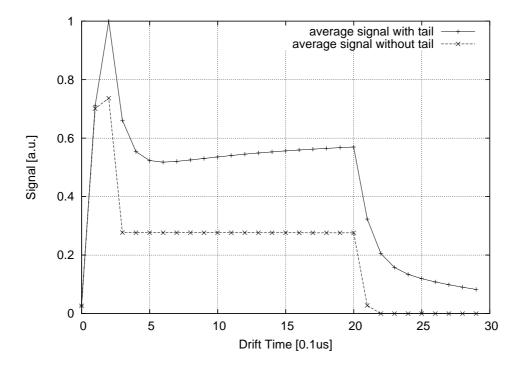

Table 4.2: typical data content