## ETHZ-IPP Internal Report 98-2 April 1998

# Übersprechverhalten einer totzeitfreien Pixelauslese

Beat Meier

Diplomarbeit Institut für Teilchenphysik ETH Zürich

April 1998

## CERN LIBRARIES, GENEVA

# Übersprechverhalten einer totzeitfreien Pixelauslese

Beat Meier

Diplomarbeit Institut für Teilchenphysik ETH Zürich

April 1998

CERN LIBRARIES GENEVA

CM-P00080992

#### Zusammenfassung

Das Institut für Teilchenphysik der ETH Zürich und das Paul Scherrer Institut bauen zusammen einen Silizium-Vertex-Detektor für das CMS Experiment am neu entstehenden LHC beim CERN. Dafür werden auch die Pixeldetektoren und die dafür notwendigen Elektronikchips entwickelt.

Da die Bunch Crossing Rate bei LHC 40MHz beträgt und ca.  $50 \cdot 10^6$  Pixel vorhanden sind, ist die anfallende Datenmenge gewaltig gross. Diese muss daher schon von der Elektronik, die sich unmittelbar an Detektor befindet, stark reduziert werden. Ein solches Verfahren ergibt sich daraus, dass die Anzahl der Detektorpixel mit einem Treffer vergleichsweise gering ist. Daher wird ein Ausleseverfahren benötigt, das getroffene Pixel sehr schnell finden kann.

Zur Realisierung eines solchen Verfahrens wurden Testschaltungen auf Chips hergestellt. Diese erlauben sogar eine totzeitfreie Pixelauslese. Das heisst, dass die Elektronik während der Auslese schon wieder bereit ist, um neue Treffer zu registrieren.

Das Problem das dabei auftritt sind die Störungen, die bei der Auslese produziert werden. Da die Pixel während der Auslese aktiv sind, besteht die Wahrscheinlichkeit, dass die Störungen als Treffer registriert werden.

In der vorliegenden Arbeit wurde die Grösse dieser Störungen ermittelt. Daneben wurde auch das Zeitverhalten des Auslesemechanismus gemessen. Für die Durchführung wurde eine Messaparatur gebaut, mit der diese Testschaltungen in Betrieb genommen werden konnten. Dabei musste sehr darauf geachtet werden, dass die Messaparatur nicht selbst zur Quelle von Störungen wurde.

Es hat sich gezeigt, dass die Störungen einem äquivalenten Detektorsignal von weniger als 820 Elektronen entsprechen. Da bei CMS eine untere Grenze von 2500 Elektronen gefordert wird, erfüllt der getestete Auslesemechanismus die Erwartungen voll.

.

## Inhaltsverzeichnis

| 1 | 1.1 Das CMS Experiment am LHC                                                                                                                                                                                                                              | 1<br>1<br>1                                 |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| 2 | ixeldetektoren  1 Halbleiter-Detektoren                                                                                                                                                                                                                    |                                             |  |

| 3 | 3.2 Technologie                                                                                                                                                                                                                                            | 1<br>1<br>1<br>2                            |  |

| 4 | 4.1 Aufbau       1         4.2 Totzeitfreier Auslesemechanismus       1         4.2.1 Funktionsweise       1         4.2.2 Ausbreitung des /ENCD-Signals       2         4.2.3 Beschleunigungsmechanismus       2         4.3 Die Struktur "WELLE"       2 | 6<br>16<br>17<br>17<br>20<br>22<br>25<br>28 |  |

| 5 | 5.1 Anforderungen                                                                                                                                                                                                                                          | 30<br>30<br>35                              |  |

| 6 | 6.1 Inbetriebnahme                                                                                                                                                                                                                                         | 36<br>38<br>40<br>43                        |  |

| 7 | 7.1 Inbetriebnahme                                                                                                                                                                                                                                         | 45<br>45<br>47<br>48<br>50                  |  |

|                  |                                        | 7.5.2  | Verstärkerkennlinien                       | . 51 |  |

|------------------|----------------------------------------|--------|--------------------------------------------|------|--|

|                  |                                        | 7.5.3  | Frequenzverhalten                          | . 53 |  |

|                  |                                        | 7.5.4  | Wahl der Eichung für die Crosstalk-Messung | . 53 |  |

|                  | 7.6                                    | Cross  | stalk Messung                              | . 56 |  |

|                  | 7.7                                    | Schlus | ssfolgerungen                              | . 58 |  |

| A Schemas PSI-32 |                                        |        |                                            |      |  |

| В                | B Daten für die Simulationen mit SPICE |        |                                            |      |  |

| $\mathbf{C}$     | C Elektronikboard                      |        |                                            |      |  |

À

## 1 Einleitung

## 1.1 Das CMS Experiment am LHC

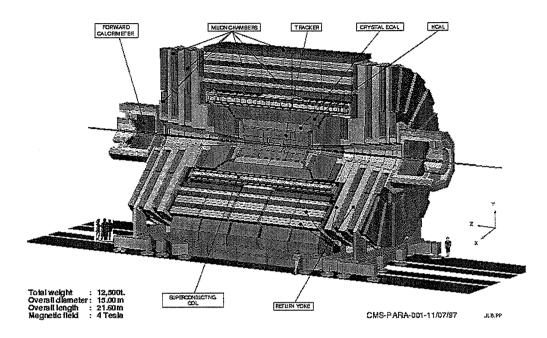

Abbildung 1: CMS Detektor

Beim CERN ist der Bau des LHC (Large Hadron Collider) geplant. Die Maschine soll Proton-Proton-Kollisionen mit einer Ruheenergie von 14TeV bei einer Luminosität von bis zu  $10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1}$  liefern. Daneben sollen auch Kollisionen mit schweren Ionen produziert werden.

Abbildung 1 zeigt den Aufbau des CMS Detektors der am LHC betrieben werden soll. Seine Hauptaufgabe ist die Suche nach Higgs- oder SUSY-Teilchen. Die Erkennung von b-Jets ist dabei von grosser Bedeutung. Der Detektor eignet sich auch um B-Physik zu betreiben, wo die CP-Verletzung und seltene Zerfälle untersucht werden.

Zur Vermessung der sekundären Vertices ist eine möglichst genaue Rekonstruktion der Teilchenspuren nötig. Dazu wird ein Vertex-Detektor mit guter Ortsauflösung benötigt. Dieser muss sich so nahe wie möglich am Kollisionspunkt befinden. Da dort grosse Teilchenflüsse vorhanden sind, stellt die eindeutige Ortszuordnung ein grosses Problem dar. Aus diesem Grund hat man sich für den Einsatz von Pixeldetektoren entschieden.

#### 1.2 Vertex-Detektor

Für den Vertex-Detektor werden Module von Pixeldetektoren zu der in Abb. 2 gezeigten Anordnung zusammengebaut. Diese besteht aus zwei ineinanderliegenden Zylindern und

2 1 EINLEITUNG

Abbildung 2: Anordnung der Pixelmodule beim Vertex-Detektor. Zwei konzentrische Zylinder und je zwei Scheiben auf jeder Seite bewirken, dass jede Teilchenspur zwei Signale erzeugt. Die Montagevorrichtung ist nicht gezeigt

je zwei Scheiben auf beiden Seiten. So erzeugt jede Spur zwei Signale, mit denen dann ihre Lage im Raum festgelegt ist.

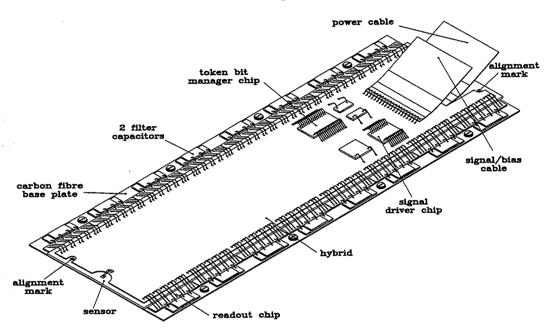

Der Aufbau der Module, wie sie für den Zylinder gebraucht werden, zeigt Abb. 3. Ein Modul besteht aus einer Siliziumplatte (Sensor), die die einzelnen Pixeldetektoren enthält. Auf diese Platte sind 16 Pixel-Auslesechips durch Bump Bonding mit den Pixeldetektoren kontaktiert (in Abb. 3 von der Unterseite). Über dem Detektor befindet sich eine Hybrid-Schaltung mit der die Pixel-Auslesechips durch Bond-Drähte verbunden sind. Auf der Hybrid-Schaltung befindet sich der Token Manager Chip und der Signal Driver Chip. Diese liefern die nötigen Steuer- und Taktsignale für die Auslesechips und sind für die Datenübermittlung zuständig. Am Hybrid sind die beiden Kapton Flachbandkabel angebracht, die für die Speisung des Moduls und für die Signalzu- und abführung benötigt werden. Das ganze Modul ist auf einer Trägerplatte aus Kohlefasermaterial montiert. Diese wird auf die Kühlrohre des Vertex-Detektors geschraubt.

Abbildung 3: modulare Detektoreinheit

## 2 Pixeldetektoren

#### 2.1 Halbleiter-Detektoren

Die Funktionsweise eines Halbleiterdetektors basiert auf einem pn-Übergang an dem eine elektrische Spannung anliegt. Als Ausgangsmaterial bei der Herstellung von Halbleiterdetektoren werden Silizium oder Germanium und neuerdings auch GaAs oder Diamant verwendet.

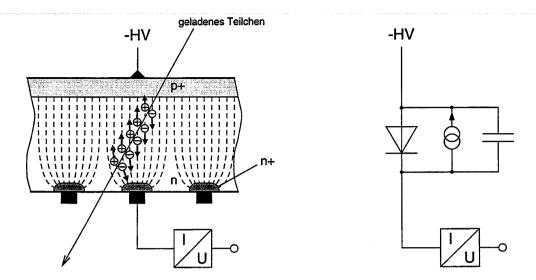

Abbildung 4: Vereinfachte Darstellung des Querschnitts durch einen Halbleiterdetektor (links) und Ersatzschaltbild (rechts)

Abbildung 4 zeigt schematisch den Querschnitt durch einen Si-Detektor wie er in der Hochenergiephysik gebraucht wird. Das Substrat (Si) ist schwach n-leitend. Die p+ dotierte Schicht auf der oberen Seite bildet den anderen Pol der Diode. Auf der unteren Seite gewährleistet die n+ Dotierung eine gut leitenden Verbindung zum aufgebrachten Metallkontakt. Indem man die Metallkontakte als einzelne Inseln ausbildet, lassen sich mehrere Detektoren auf einem Chip realisieren.

Legt man eine Spannung in Sperrrichtung an die Diode an, entsteht beim pn-Übergang eine Verarmungszone, die mit zunehmender Sperrspannung immer mehr in die n-Schicht eindringt, und schliesslich beim Erreichen der Betriebsspanung die ganze n-Schicht ausfüllt. In der Verarmungszone entsteht ein elektrische Feld, das in Abb. 4 durch gestrichelte Linien angedeutet ist.

Durchdringt ein geladenes Teilchen den Detektor, werden in der Verarmungszone freie Elektronen und Löcher erzeugt. Diese bewegen sich im Feld zu den entsprechenden Polen und bewirken einen Stromstoss von einer gewissen Ladungsmenge. Die Anzahl der erzeugten Ladungsträger hängt vom Energieverlust des Teilchens im Verhältnis zur Energie, die zur Erzeugung eines freien Ladungsträgers gebraucht wird, ab. Der Energieverlust pro Länge lässt sich nach der Bethe-Bloch-Formel berechnen. Da die Ladungen auch zu den benachbarten Pixeln abfliessen, lässt sich über die Aufteilung der Ladung der Durchgang des Teilchens sehr genau lokalisieren. Wenn sich der Detektor in einem Magnetfeld befindet, wie das bei CMS der Fall ist, ist zusätzlich noch zu beachten, dass die Ladungsträger unter dem Lorentz-Winkel abgelenkt werden. Die Ladung wird von einem Strom-/Spannungswandler in einen proportionalen Spannungsimpuls ungewandelt.

In Abb. 4 ist rechts das Ersatzschaltbild des Detektors gezeigt. Parallel zur idealen Diode befindet sich eine parasitäre Kapazität und eine Stromquelle. Die Kapazität wirkt sich

in zweierlei Hinsicht störend aus. Zum einen sammelt sie die Ladungsträger auf, die ein Teilchen erzeugt. Um das zu verhindern muss die Elektronik einen möglichst kleinen Eingangswiderstand besitzen, damit sich dieser parasitäre Kondensator nicht aufladen kann. Zum anderen können Schwankungen der Betriebspannung des Detektors (-HV) über die Kapazität in die Elektronik gelangen und dort störende Signale erzeugen.

Die Stromquelle im Ersatzschaltbild symbolisiert den Signalstrom und den Leckstrom des Detektors. Dieser Leckstrom fliesst auch dann, wenn der Detektor keine Teilchen registriert. Er nimmt mit zunehmender Temperatur und mit zunehmender Detektorfläche zu. Ein Anstieg ergibt sich auch mit zunehmender Strahlendosis, der der Detektor ausgesetzt war. Er bewirkt eine Verschiebung des Arbeitspunktes des Strom-/Spannungswandlers, der beim Überschreiten eines kritischen Wertes nicht mehr arbeitet. Bei Pixeldetektoren bekommt man dieses Problem aber leicht in den Griff, da wegen der kleinen Detektorfläche der Leckstrom klein ist.

#### 2.2 Streifen- und Pixeldetektoren

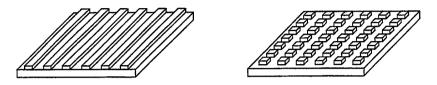

Wie im letzten Abschnitt beschrieben, lassen sich auf einem Halbleiter Chip viele einzelne Detektoren realisieren. Auf Grund der Anordnung teilt man sich in Streifen- und Pixeldetektoren ein.

Abbildung 5: Aufbau eines Streifendetektors (links) und eines Pixeldetektors (rechts)

Bei Streifendetektoren sind die einzelnen Dioden als schmale Streifen ausgebildet, die sich über den gesamten Chip ziehen. Die Elektronik kann am Ende der Streifen angebracht werden. Die gesamte Länge eines Streifens ist durch den maximal zulässigen Leckstrom begrenzt.

Mit Streifendetektoren lässt sich eine eindimensionale Ortsauflösung erreichen. Stapelt man zwei davon, um 90° verdreht, übereinander, lässt sich damit eine quasi zweidimensionale Auflösung erreichen. Diese Anordnung kann bei grossen Teilchenströmen aber keine eindeutige Zuordnung der Orte mehr liefern. Das ist der Grund, wieso man in diesen Fällen zu Pixeldetektoren übergeht.

Bei Pixeldetektoren sind die Dioden als einzelnen Punkte auf dem Chip angeordnet (Abb. 5 rechts). Damit lässt sich eine echte zweidimensionale Ortsauflösung erreichen. Die Anzahl der Datenkanäle nimmt im Vergleich zum Streifendetektor quadratisch mit den Dimensionen des Detektors zu. Daraus ergibt sich ein grosses Anschlussproblem. Daher muss ein ganz neuer Weg zur Kontaktierung der Detektoren eingeschlagen werden. Weil es nicht mehr möglich ist, die Signalleitungen jedes Pixels einzeln herauszuführen, muss sich die Elektronik direkt beim Pixel befinden. Die Daten können dann über ein Bussystem ausgelesen werden. Da die Elektronik auf die Pixelgrösse beschränkt sein muss, tritt zusätzlich noch ein Platzproblem auf. Dies muss beim Auslegen der Schaltung hinsichtlich der Anzahl der Transistoren für die Pixelelektronik und beim Design des Chips berücksichtigt werden.

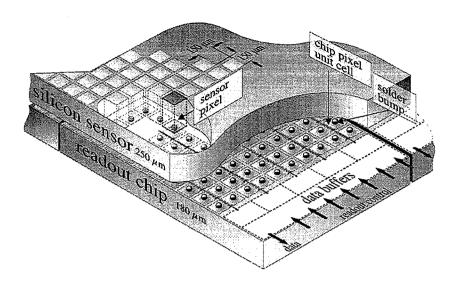

Der Weg der am PSI zur Lösung dieser Probleme gewählt wurde ist der, die Elektronik auf einem separaten VLSI-Chip zu platzieren. Die Elektronik der einzelnen Pixel wird darauf im gleichen Raster wie die Pixeldetektoren angeordnet. Für das Raster hat sich eine Länge von  $150\mu m$  als optimal herausgestellt. Durch ein Bump Bonding Verfahren wird die Detektorplatte mit den Chips in Kontakt gebracht, wie das in Abb. 6 gezeigt ist. Dabei werden 16 Chips für die ganze Detektorfläche gebraucht.

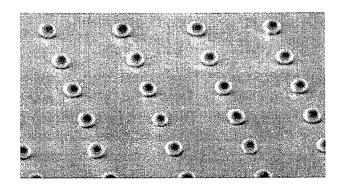

Der Kontakt wird durch kleine Kügelchen aus Indium (Bumps) hergestellt. Diese werden zuerst auf den Detektor aufgebracht (Abb. 7). Anschliessend wird der Auslesechip darauf positioniert und das Ganze miteinander verschmolzen.

Abbildung 6: Kontaktierung des Detektors (oben) mit den Pixel Readout Chips (unten)

Abbildung 7: Eine REM Aufnahme der Bumps auf einer Trägerplatte. Ihr Abstand beträgt in diesem Fall  $125\mu m$ .

#### 2.3 Die Elektronik für Pixeldetektoren

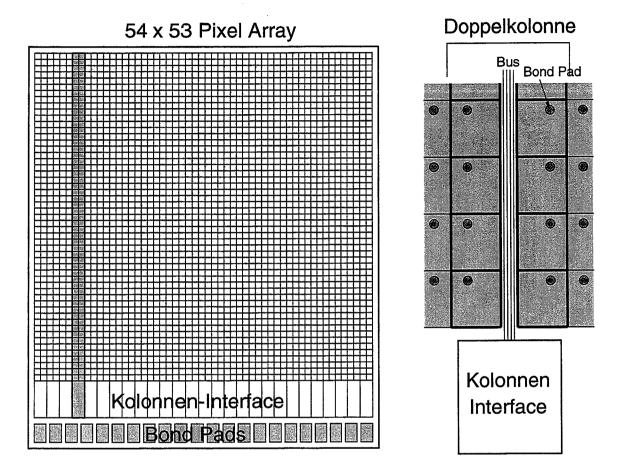

Abbildung 8: Struktur eines Pixel Auslesechips (Doppelkolonne mit Interface markiert). Rechts: vergrösserter Ausschnitt aus einer Doppelkolonne

Der Pixel Auslesechip, wie er für CMS gebraucht wird, besteht voraussichtlich aus einem Array von 53 mal 54 Pixeln (Abb. 8). Jeweils zwei benachbarte Kolonnen werden zu einer Doppelkolonne zusammengefasst und über einen gemeinsamen Bus mit dem Interface verbunden. Über die Bond Pads auf den Pixeln wird der Chip mit dem Detektor kontaktiert.

Die Elektronik der Pixel hat die Aufgabe, die Signale vom Detektor in Impulse umzuwandeln und zu verstärken. Anschliessend muss sie anhand der Signalamplitude entscheiden, ob es sich um einen Treffer handelt. Wenn das zutrifft, signalisiert sie über den Bus das Kolonnen-Interface um eine Auslese anzufordern.

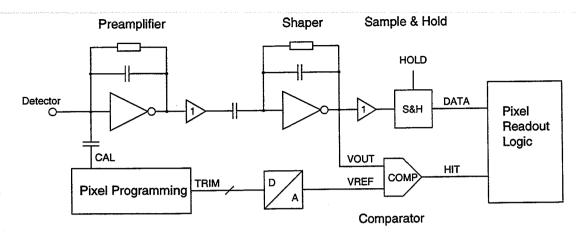

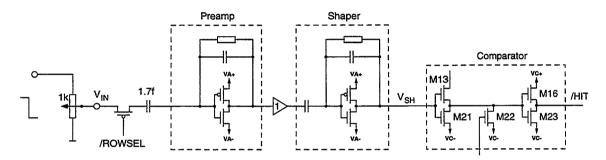

Abbildung 9 zeigt das Blockschaltbild eines Pixels. Das Signal vom Detektor gelangt zuerst auf den Vorverstärker. Dieser besitzt den geforderten niedrigen Eingangswiderstand. Darauf folgt ein Spannungsfolger, der für die Stromverstärkung sorgt, um den Shaper, der ebenfalls einen niedrigen Eingangswiderstand besitzt, anzusteuern. Dieser ist gleich aufgebaut ist wie der Vorverstärker. Wegen dem Spannungsversatz des Spannungsfolgers ist ein

Abbildung 9: Aufbau der Elektronik für einen Pixel

Kondensator nötig, um den Shaper gleichspannungsmässig abzutrennen. Ausserdem werden so Gleichspannungskomponenten vom Shaper ferngehalten, die durch den Leckstrom des Detektors auftreten.

Das Signal  $V_{OUT}$  am Shaper-Ausgang gelangt auf den Komparator. Übersteigt die Signalamplitude einen Referenzwert  $V_{REF}$ , wird ein Treffer (Hit) ausgelöst, der zur Pixel Readout Logic gelangt.  $V_{OUT}$  gelangt ausserdem über einen Spannungsfolger auf die Sample- und Hold-Schaltung. Dort wird die Impulshöhe festgehalten. Das dazu erforderliche HOLD-Signal wird z. B. vom HIT-Signal geliefert. Diese Grösse kann ebenfalls über den Bus ausgelesen werden. Mit Hilfe dieser Information lässt sich durch Ladungsinterpolation benachbarter Pixel die Ortsauflösung steigern.

Um die Pixel-Elektronik zu kalibrieren enthält sie eine Programmierlogik. Diese spricht auf die Row-/Column Signale an, mit denen ein bestimmter Pixel auf dem Chip adressiert werden kann. Auf dem selektierten Pixel kann dann ein Calibrate-Signal auf den Vorverstärker eingespiesen werden. Mit den TRIM-Bits lässt sich über einen Digital-/Analog-Wandler die Referenzspannung für den Komparator einstellen. Falls ein einzelner Pixeldetektor einen Defekt aufweist, lässt sich der Pixel auch ganz ausschalten.

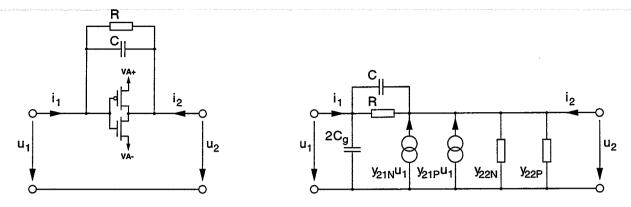

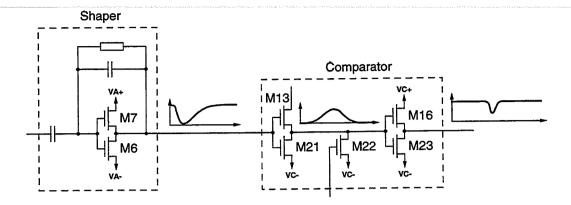

Diese Schaltung wurde am PSI auf verschiedenen Testchips in strahlungsharter BiC-MOS Technologie implementiert. Damit lassen sich neben digitalen auch analoge Schaltungen realisieren. Abb. 10 zeigt die Schaltung des invertierenden Verstärkers, wie er für den Vorverstärker und den Shaper verwenden wird. Er besteht aus einem komplementären Transistorpaar (CMOS). Durch die Gegenkopplung mit dem Widerstand R stellt sich der Gleichspannungs-Arbeitspunkt auf die halbe Betriebspannung (d. h.  $\frac{VA_+-VA_-}{2}$ ) ein. R und C zusammen sorgen für die nötige Signalformung. Der Widerstand R wird durch einen langestreckten PFET realisiert. Über dessen Gate Anschluss lässt sich der Widerstandswert einstellen.

Zur Berechnungen des Kleinsignal Übertragungsverhaltens verwendet man Vierpol-Parameter. Damit lässt sich die Schaltung durch ein lineares Gleichungssystem der fol-

Abbildung 10: Preamplifier mit CMOS Inverter (links) mit Kleinsignal Ersatzschaltbild (rechts)

genden Form beschreiben:

$$i_1 = y_{11}u_1 + y_{12}u_2 i_2 = y_{21}u_1 + y_{22}u_2$$

(1)

Die Indizes bezeichnen Eingangs- (1) und Ausgangsgrössen (2). Damit lassen sich durch Auflösen für den unbelasteten Fall  $(i_2 = 0)$  folgende Grössen bestimmen:

Leerlaufspannungsverstärkung

$$V_0 := \frac{u_2}{u_1} = -\frac{y_{21}}{y_{22}} \tag{2}$$

Eingangswiderstand

$$R_{IN} := \frac{u_1}{i_1} = \frac{1}{y_{11} - \frac{y_{12}y_{21}}{y_{22}}} \tag{3}$$

Strom-/Spannungsübertragungsverhältnis

$$A_0 := \frac{u_2}{i_1} = \frac{u_2}{u_1} \frac{u_1}{i_1} = V_0 R_{IN} = -\frac{1}{\frac{y_{22}y_{11}}{y_{21}} - y_{12}}$$

$$\tag{4}$$

Aus dem Ersatzschaltbild in Abbildung 10 rechts erhält man für die  $y_{ij}$  mit  $u_2=0$

$$y_{11} = \frac{i_1}{u_1} = \frac{1 + j\omega RC}{R} + 2j\omega C_g \tag{5}$$

$$y_{21} = \frac{i_2}{u_1} = -\frac{1 + j\omega RC}{R} + y_{21N} + y_{21P} \tag{6}$$

und mit  $u_1 = 0$

$$y_{12} = \frac{i_1}{u_2} = -\frac{1 + j\omega RC}{R} \tag{7}$$

$$y_{22} = \frac{i_2}{u_2} = \frac{1 + j\omega RC}{R} + y_{22N} + y_{22P}$$

(8)

$y_{21N}$  Vorwärtssteilheit des NFET

$y_{21P}$  Vorwärtssteilheit des PFET

$y_{22N}$  Ausgangsleitwert des NFET

$y_{22P}$  Ausgangsleitwert des PFET

$C_q$ : Gate Kapazität des NFET bzw. PFET

Durch Einsetzen in (2), (3) und (4) lassen sich dann die entsprechenden Eigenschaften bestimmen.

## 3 Der DM\_PSI30 Chip

#### 3.1 Einführung

Am PSI wurde die Elektronik der Pixeldetektoren auf verschiedenen Chips realisiert. Auf dem Chip, mit der Bezeichnung DM\_PSI30, exististiert ein 22 mal 30 Pixel Array mit zugehöriger Ausleseelektronik. Auf dem PSI31 Chip sind einzelne Pixel zu Studienzwecken vorhanden. Mit dem DM\_PSI32 Chip steht eine leicht optimierte Version des DM\_PSI30 Chips zur Verfügung. Dazu kommen, auf demselben Chip, verschiedenartige Designs von Verstärkern und Komparatoren. Ausserdem sind Teststrukturen für einen schnelleren Auslesemechanismus vorhanden.

Der Aufbau des DM\_PSI30 Chips entspricht im Wesentlichen der in Abbildung 8 gezeigten Anordnung mit der Ausnahme, dass er nur 11 Doppelkolonnen bzw. 22 Kolonnen mit je 30 Pixeln besitzt. Der Abstand zwischen den Pixeln beträgt in diesem Fall  $125\mu m$ . Die gesamte Elektronik, wie sie Abb. 9 zeigt, findet hier also auf einer Fäche von  $125\mu m$  mal  $125\mu m$  platz. Beim Auslesechip für CMS wird dafür ein Platz von  $150\mu m$  mal  $150\mu m$  zur Verfügung stehen.

## 3.2 Technologie

Der DM\_PSI30 Chip sowie der DM\_PSI32 Chip wurden in strahlungsharter CMOS Technologie hergestellt. Dafür hatte man den DMILL Prozess von Temic gewählt. Das ist ein besonders strahlungsharter BiCMOS Prozess mit dem neben CMOS auch bipolare Transistoren auf demselben Chip hergestellt werden können. Ausserdem eignet er sich sehr gut zur Realisierung von Analogschaltungen. Als Substrat dient nicht das Trägermaterial sondern eine sehr dünne Siliziumschicht. Diese ist durch eine isolierenden Oxydschicht vom Trägermaterial getrennt. Wegen dem kleinen Substratvolumen bilden sich viel weniger Strahlungsschäden. Der DMILL Prozess lässt Strahlungsdosen von 100kGy zu.

Das Si-Substrat bildet nicht eine zusammenhängende Fläche, sondern ist in Inseln aufgeteilt, auf denen sich die einzelnen Transistoren befinden. Wegen dieser galvanische Trennung besitzt diese Technologie auch hinsichtlich des Übersprechverhaltens gute Eigenschaften.

Der Prozess lässt zwei Metallschichten zu. Verwendet man die oberste Schicht für die Speisespannungen und deckt damit den gesamten Chip ab, bildet sie eine gute Abschirmung.

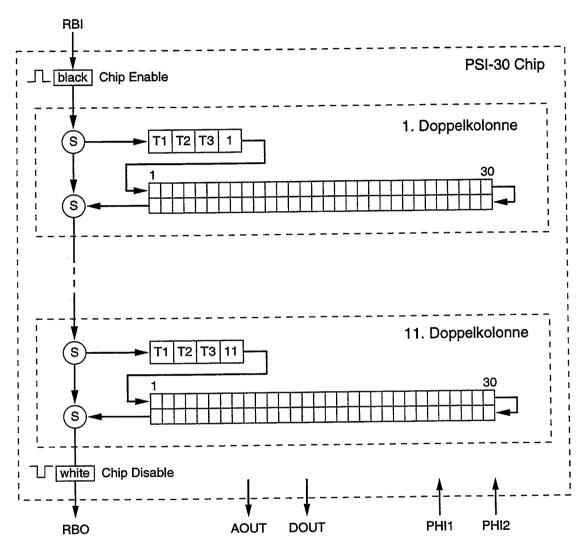

#### 3.3 Auslesemechanismus

Die Auslese des Pixel-Arrays geschieht sequentiell. Dazu enthält die Ausleselogik jedes Pixels eine Bit-Speicherzelle. Alle diese Zellen einer Doppelkolonne sind zu einem Schieberegister zusammengeschaltet wie in Abb. 11 gezeigt ist. Im Kolonnen-Interface jeder Doppelkolonne befinden sich noch vier weitere Zellen. Diese sind für das Auslesen des Zeitpunkts des Treffers und für die Identifizierung der Doppelkolonne zuständig. Die Schiebergister der einzelnen Doppelkolonnen sind alle zu einem einzigen langen Schieberegister hintereinandergeschaltet. Durch dieses lassen sich Datenbits, die am RBI-Eingang anliegen, durchschieben. Der dazu nötige Schiebetakt wird über die Anschlüsse PHI1 und PHI2 auf den Chip gegeben. Dabei handelt es sich um einen Zweiphasentakt.

Zuerst betrachtet man alle Zellen als gelöscht. Läuft nun ein gesetztes Bit in das Schieberegister einer Doppelkolonne, schaltet der Pixel, der das gesetzte Bit enthält, seine Daten auf die Leitungen AOUT und DOUT. Alle anderen Pixel lassen diese Leitungen unbeeinflusst.

Die Auslese des gesamten Chips spielt sich auf folgende Weise ab. Registriert ein Pixel einen Treffer, informiert er über die /COLOR-Leitung sein Kolonnen-Interface. Dieses hält den Zeitpunkt mittels eines Zählers fest und stellt die Schalter S so ein, dass das Schieberegister durch die Doppelkolonne führt. Im anderen Fall würde die Doppelkolonne überbrückt. Auf diese Weise werden nur die Doppelkolonnen ausgelesen, die einen Treffer registriert haben.

Die Auslese wird gestartet, indem während eines Taktzyklus der RBI- Eingang von aussen aktiviert wird. Damit befindet sich ein einzelnes gesetztes Bit im Schieberegister, das den Chip durchläuft (Token Bit). Als erstes befindet es sich in der Zelle mit der Bezeichnung "black". Damit wird der Chip selektiert, so dass er die Leitungen AOUT und DOUT aktivieren kann. Ausserden wird er ein positives Signal auf AOUT ausgegeben. Anschliessend durchläuft das Bit die Zellen T1, T2 und T3 der ersten Doppelkolonne, die einen Treffer registriert hat. Damit wird die Zeitinformation des Treffers, die im Interface gespeichert ist, auf AOUT ausgegeben. Es handelt sich um ein 12 Bit Wort. Jeweils vier Bits werden pro Schiebetakt durch einen Code von 16 Spannungsstufen ausgegeben. Anschliessend wird auf die gleiche Weise die Nummer der Doppelkolonne ausgegeben. Das ist nötig, um die Doppelkolonnen zu identifizieren, denn es werden ja nicht alle ausgelesen. Nun durchläuft das Lesebit noch die anderen Doppelkolonnen, die einen Treffer registriert haben. Am Schluss der Auslese befindet es sich in der "white"-Zelle und liefert dabei ein negatives Signal auf AOUT, das das Ende der Chip-Auslese markiert. Gleichzeitig wird er Chip wieder deaktiviert. Damit sind die Leitungen AOUT und DOUT frei für die Auslese des nächsten Chips. Das geschieht dadurch, dass der RBO-Ausgang mit dem RBI-Eingang des nächsten Chips verbunden wird.

Ein häufiger Fehler, der während der Auslese auftreten kann, ist der Verlust des Lesebits im Schieberegister. Das geschieht wenn es irgendwo in eine defekte Zelle hineinläuft.

Abbildung 11: Schematische Darstellung des Auslesemechanismus beim DM\_PSI30 Chip. Die Pfeile markieren die möglichen Wege, die die Daten durch das Schieberegister nehmen.

Die Folge davon ist, dass alle nachfolgenden Doppelkolonnen auf dem fehlerhaften Chip und alle nachfolgenden Chips nicht mehr ausgelesen werden. Es können also nur diejenigen Chips aus einer Produktion verwendet werden, auf denen alle 706 Zellen einwandfrei funktionieren. Ein Chip der Grösse, wie er für CMS vorgesehen ist, würde etwa 3000 Zellen enthalten. Dieses Problem besteht beim neuen Auslesemechanismus, der auf dem PSI32 Chip realisiert wurde, nicht mehr.

Die Überbrückung von Doppelkolonnen ohne einen Treffer bewirkt eine gewisse Steigerung der Auslesegeschwindigkeit. Die Doppelkolonnen, die Treffer registrieren, müssen aber immer noch vollsändig ausgelesen werden. Auch dieses Problem wurde beim neuen Auslesemechanismus gelöst. Dazu wurde der Mechanismus mit dem Schieberegister aufgegeben.

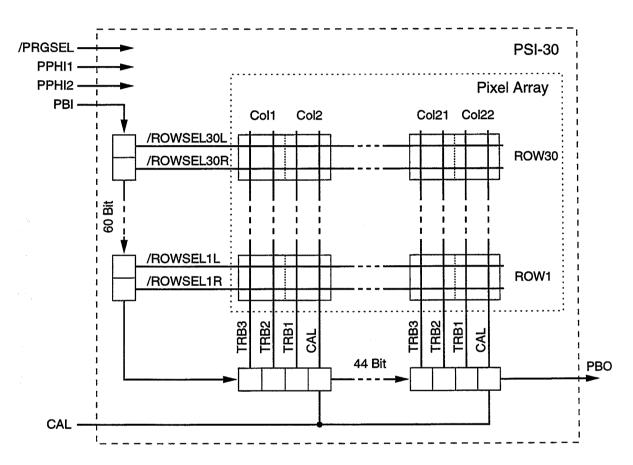

#### 3.4 Programmierung

Die Logik zur Programmierung des Chips hat die Aufgabe, einzelne Pixel zu selektieren um sie kalibrieren zu können. Die Pixelprogrammierung arbeitet völlig unabhängig vom Auslesemechanismus. Mit ihr lassen sich folgende Manipulationen an den einzelnen Pixeln vornehmen:

- Aufschalten eines Calibrate-Signals auf den Eingang des Vorverstärkers.

- Setzen der Schwelle des Komparators durch ein drei Bit Steuerwort (TRB1, TRB2 und TRB3). Damit lässt sich die Ansprechschwelle jedes einzelnen Pixels separat einstellen. Pixel können auch ganz abgeschaltet werden. So werden Pixel mit fehlerhaften Detektoren deaktiviert.

Die Selektion eines Pixels geschieht durch das Laden eines 104 Bit Schieberegisters. Zu seiner Steuerung sind folgende Eingänge vorhanden:

- PPHI1: Taktphase 1 für das Schieberegister

- PPHI2: Taktphase 2 für das Schieberegister

- PBI: Dateneingang

- /PROGSEL: Schreiben der Daten auf die Pixel

Die Bedeutung der einzelnen Zellen des Schieberegisters ist aus Abb. 12 ersichtlich. 60 Bits werden benötigt, um die Reihen zu selektionieren. Pro Reihe werden zwei Bits benötigt. Das eine steuert die jeweiligen linken Pixel der Doppelkolonnen an und das andere die rechten. Mit den restlichen 44 Bits des Schieberegisters werden die Daten an die Doppelkolonnen angelegt. An jeder Doppelkolonne liegen die drei Trimmbits TRM1, TRM2 und TRM3 an, mit denen die Komparatorschwelle eingestellt werden kann. Diese Informationen werden mit dem Anlegen eines /PROGSEL-Impulses in die Pixel geschrieben. Damit wird eine ganze Reihe von Pixeln neu programmiert.

Abbildung 12: Schematische Darstellung des Mechanismus zur Pixel Programmierung

Das vierte Bit dient dazu, das Calibrate-Signal auf die jeweilige Doppelkolonne zu schalten. Das analoge Calibrate-Signal wird von aussen in den Chip eingespiesen. Ist das CAL(n) Bit im Schieberegister gesetzt, kann das Signal auf die n. Doppelkolonne gelangen. Damit das Signal weiter auf den Pixel in der m. Reihe gelangen kann, muss das entsprechende /ROWSEL(m) Signal anliegen.

## 4 Der DM\_PSI32 Chip

#### 4.1 Aufbau

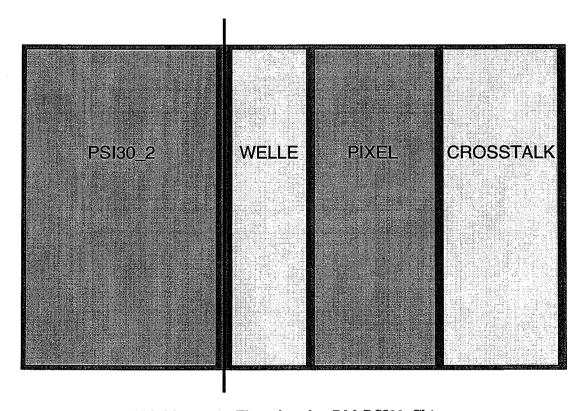

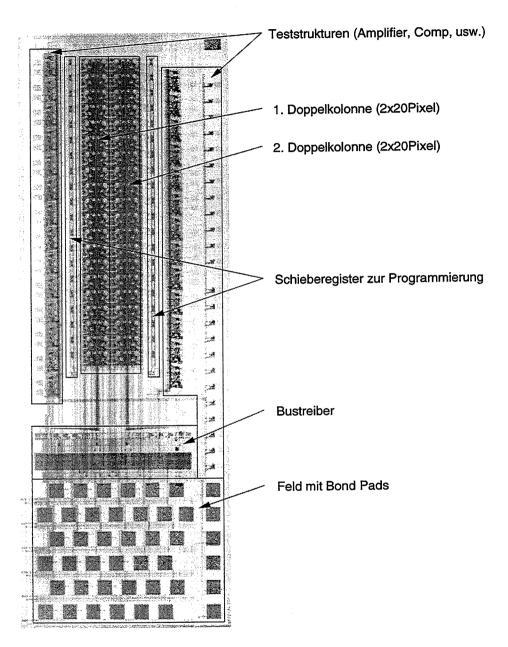

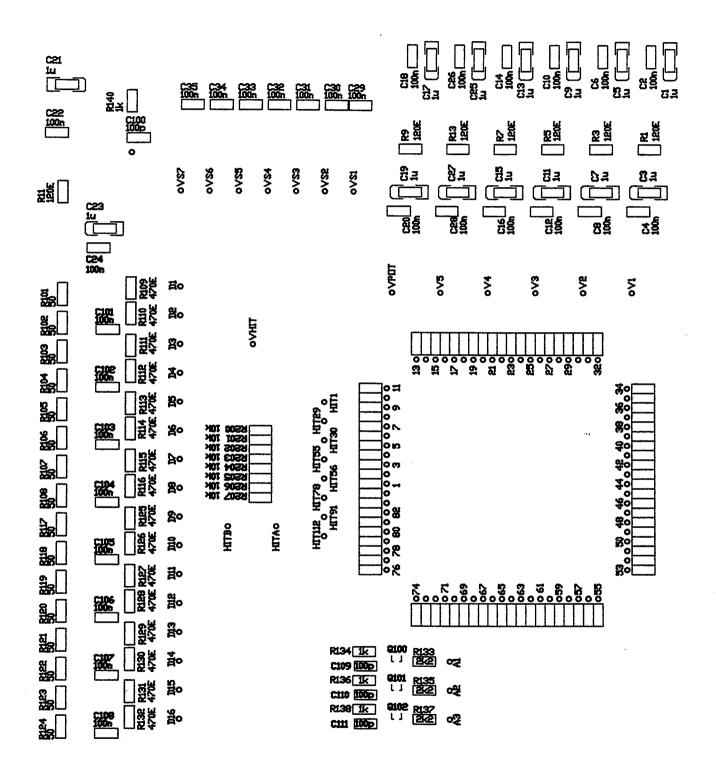

Abbildung 13: Floorplan des DM\_PSI32 Chips

Der 5 mal 8mm grosse DM\_PSI32 Chip ist ebenfalls im DMILL Prozess hergestellt worden. Auf ihm befinden sich vier unabhängige Teststrukturen, deren Anordnung Abb. 13 zeigt. Sie haben folgende Funktionen:

- PSI30\_2: Hier handelt es sich um eine neue Version des DM\_PSI30 Chips mit leicht optimiertem Design.

- WELLE: Hier befindet sich der digitale Teil des neuen totzeitfreien Auslesemechanismus. Dieser Teil wurde in der vorliegenden Arbeit benutzt um das Zeitverhalten

des Auslesemechanismus zu studieren.

- PIXEL Auf diesem Teil befinden sich verschiedene Teststrukturen wie verschiedene Einzeltransistoren, um Toleranzen bei der Chip-Herstellung zu prüfen, und verschiedenartige Verstärker und Komparatoren.

- CROSSTALK: Hier befinden sich zwei Doppelkolonnen aus vollständigen Pixeln mit Analog- und Digitalteil. Der digitale Teil ist der gleiche, wie bei der Struktur "WELLE". An dieser Teststruktur wurden die Crosstalk-Messungen für die vorliegende Arbeit durchgeführt.

Der PSI30\_2 Teil des Chips wurde mit einer Diamantsäge abgetrennt, um damit gleichzeitig andere Messungen durchzuführen.

#### 4.2 Totzeitfreier Auslesemechanismus

#### 4.2.1 Funktionsweise

Wie in Abschnitt 3.3 beschrieben wurde, besitzt der Auslesemechanismus des DM\_PSI30 Chips die beiden Nachteile der langen Auslesezeit und der Intoleranz gegenüber Fehlern beim Schieberegister. Beide Nachteile sind beim neuen Auslesemechanismus nicht mehr vorhanden. Zusätzlich ermöglicht er eine nahezu totzeitfreie Auslese. Das bedeutet, das während dem Auslesevorgang, von der Pixelelektronik weitere Treffer registriert werden können. Damit tritt aber das Problem des Übersprechens auf. Da die Pixel während der Auslese bereits wieder messbereit sind, besteht die Wahrscheinlichkeit, dass der Auslesevorgang Störungen erzeugt, die sich auf die Eingänge der Vorverstärker auswirken. Diese können sich wie Treffer auswirken.

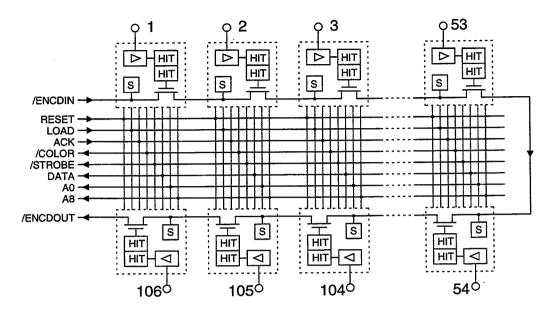

Abbildung 14 zeigt schematisch eine Doppelkolonne bestehend aus 2 mal 53 Pixeln und den Busleitungen. Der wesentliche Teil eines Pixels, der die totzeitfreie Auslese ermöglicht ist das doppelte Hit-Flip-Flop das die Treffer speichert. Während das eine den letzten Zustand für die Auslese bereithält kann das andere bereits wieder neue Treffer registrieren. Diese werden dann bei der nächsten Auslese berücksichtigt. Der Bus setzt sich aus den folgenden Signalleitungen zusammen:

| /ENCDIN | (Enable Column Drain Input) Mit diesem Eingang startet das<br>Kolonnen-Interface die Pixelsuche. Dies ist eigentlich keine<br>Busleitung, da das Signal nicht parallel an jedem Pixel anliegt. |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET   | Damit wird das erste Hit-Flip-Flop, das sich unmittelbar nach dem Analogteil befindet, gelöscht.                                                                                               |

| LOAD    | Ein 1 Pegel bewirkt, dass in jedem Pixel ein High-Signal auf die /ENCD-Leitung gegeben wird. Das dient zur Vorbereitung der Pixelsuche.                                                        |

| ACK     | (Acknowledge) Ein 1 Pegel fordert einen Pixel auf, seine Daten auf die Leitungen DATA, A0 und A8 zu geben.                                                                                     |

| /COLOR   | (Column Or) Durch Ausgabe eines Low-Signals meldet ein<br>Pixel einen Treffer. Die Leitung arbeitet als Wired Or.                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| /STROBE  | Damit meldet ein Pixel die Bereitschaft zur Auslese. Die Leitung arbeitet als Wired Or.                                              |

| DATA     | Hier gibt der Pixel den Spannungwert im Sample und Hold aus, wenn ACK anliegt.                                                       |

| A0       | Die unteren drei Bits der Pixelnummer werden, bei aktivem ACK-Signal, über diese Leitung durch 8 Spannungsstufen codiert ausgegeben. |

| A8       | Ausgabe der oberen Bits der Pixelnummer                                                                                              |

| /ENCDOUT | (Enable Column Drain Output) Dieser Ausgang zeigt dem<br>Kolonnen-Interface das Ende der Pixelsuche an.                              |

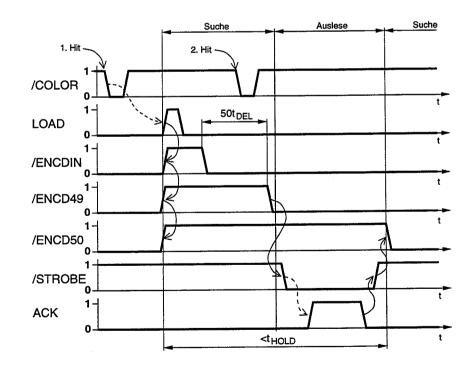

Registriert ein Pixel in der Doppelkolonne einen Treffer, dann gibt er auf die /COLOR-Leitung einen Low-Pegel (=0). Damit benachrichtigt er das Interface. Dieses startet darauf die Auslese der Kolonne. Die Auslese lässt sich in zwei Schritte unterteilen. Beim ersten Schritt, der Pixelsuche, geht es darum, den ersten Pixel in der Doppelkolonne, der einen Treffer registriert hat, zu finden. Ist dies geschehen, werden im zweiten Schritt die Informationen ausgelesen.

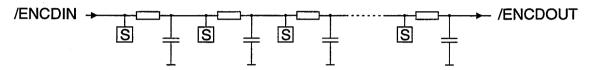

Für die Pixelsuche spielt die /ENCD-Leitung die zentrale Rolle. Sie beginnt beim /ENCDIN-Eingang und führt durch jeden Pixel und endet beim /ENCDOUT-Ausgang. Derjenige oder diejenigen Pixel mit einem Treffer unterbrechen diese Leitung durch öffnen des NFETs, der als Schalter dient. Die Vorbereitung der Suche geschieht durch das Anlegen eines /LOAD-Impulses. Dieser gelangt auf jedem Pixel auf den mit S bezeichneten Schaltungsblock, der die /ENCD-Leitung auf den High-Pegel (=1) bringt. Gleichzeitig wird auf /ENCDIN ein High-Pegel gegeben. Nach dem Wegnehmen des /LOAD-Signals befindet sich die Leitung in einem hochohmigen Zustand. Der High-Pegel bleibt wegen der Leitungskapazität erhalten. Nun wird die Suche gestartet, indem man auf /ENCDIN ein Low-Signal bringt. Die /ENCD-Leitung entlädt sich bis zum ersten Pixel mit einem Treffer (in Abb. 15 wäre es der 50. Pixel). Dieser reagiert darauf, indem er einen Low-Pegel auf die /STROBE-Leitung gibt. Damit wird das Interface informiert, dass ein Pixel zur Auslese bereit ist.

Bis jetzt weiss das Interface noch nicht, welcher Pixel angesprochen wurde. Diese Information holt es sich durch die nun folgende Auslese. Dazu setzt es das ACK-Signal. Jetzt legt der Pixel seine Identifikation auf die A0- und A8-Leitung. Gleichzeitig liegt der Inhalt des Sample & Hold auf DATA. Wenn das Interface das ACK-Signal wieder zurücknimmt, ist die Auslese beendet. Gleichzeitig schaltet der Pixel den NFET in der /ENCD-Leitung wieder ein und leitet so das Signal zu den folgenden Pixeln weiter. Damit wird die Suche nach Treffern auf den nachfolgenden Pixeln fortgesetzt. Werden weitere Treffer gefunden, beginnt eine neue Auslese. Die Suche ist beendet, wenn das Signal den /ENCDOUT- Ausgang erreicht.

Abbildung 14: Blockschaltbild des neuen Auslesemechanismus

Abbildung 15: Zeitdiagramm für die Auslese

#### 4.2.2 Ausbreitung des /ENCD-Signals

Die Laufzeit des Signals auf der /ENCD-Leitung soll möglichst klein sein. Sie wird durch die Widerstände der NFETs im leitenden Zustand und den Kapazitäten der Leitungsabschnitten dazwischen bestimmt. Abb. 16 zeigt ein vereinfachtes Modell dieser Leitung. Die Widerstände R stellen die Kanalwiderstände der FETs im leitenden Zustand dar. Dieser beträgt einige  $k\Omega$ . Dazwischen liegen die Kapazitäten der Leitungsabschnitte. Ihr Wert beträgt 30fF. Die Gleichung für die Signalausbreitung lässt sich anhand eines Kettengliedes

Abbildung 16: Modell der stark gedämpften /ENCD-Leitung

ableiten.

Daraus erhält man für die Spannungen

$$u_{k+1} - 2u_k + u_{k-1} = -RC\dot{u}_k \tag{11}$$

Näherungsweise kann man R und C als kontinuierlich auf der Leitung verteilt betrachten und erhält in diesem Grenzfall  $(dx \to 0)$ :

$$\frac{\partial^2 u}{\partial r^2} + R'C' \frac{\partial u}{\partial t} = 0 \tag{12}$$

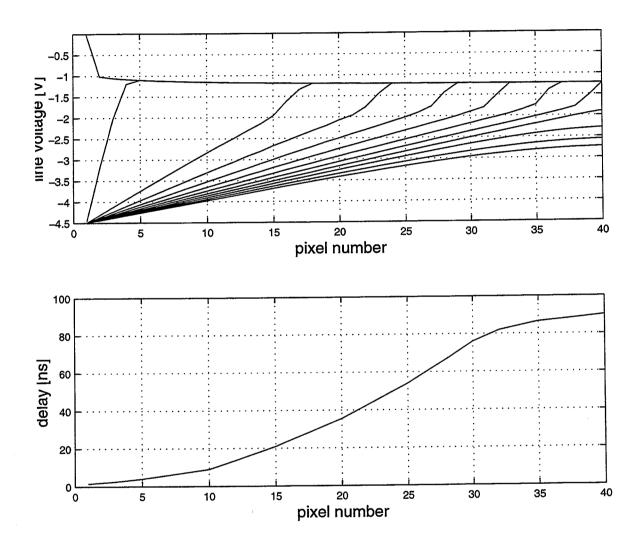

mit u=u(x,t);  $R'=\frac{R}{dx}$ ;  $C'=\frac{C}{dx}$ . Das ist die Diffusionsgleichung mit der Diffusionskonstanten  $D=\frac{1}{R'C'}$ . Diese Konstante bestimmt die Laufzeit des Signals. In Fall der /ENCD-Leitung ist die Randbedingung für die Lösung der Gleichung am /ENCDIN-Anschluss gegeben. Abbildung 17 zeigt eine Simulation der Spannungsverteilung auf der /ENCD-Leitung zu verschiedenen Zeitpunkten. Für die Simulation wurde eine Leitung über 40 Pixel verwendet und an Stelle der Widerstände reale NFETs im leitenden Zustand eingesetzt. Für die Kapazitäten wurden 30fF angenommen. Zum Zeitpunkt Null befindet sich die Leitung im High-Zustand. Danach wird /ENCDIN auf Low-Pegel (-4.5V) gebracht. Man beobachtet wie sich das Signal fortpflanzt und dabei immer mehr abflacht. Die Krümmung im oberen

Abbildung 17: oben: simulierter Spannungsverlauf auf der /ENCD-Leitung zu den Zeitpunkten T=0, T=1ns, T=10ns, T=20ns, T=30ns, T=40ns, T=50ns, T=60ns, T=70ns, T=80ns, T=90ns und T=100ns; unten: Signallaufzeit in Abhängigkeit von Abstand vom Leitungsanfang.

Teil der Kurven stammen daher, dass der Widerstand der NFETs von den Spannungen an den Anschlüssen Drain und Source abhängt und damit von der Spannung auf der Leitung. Nimmt man an, dass ein Pixel beim Unterschreiten einer Schwelle von -2.5V auf das Signal reagiert, lässt sich daraus die Laufzeit des Signals bestimmen (Abb. 17 unten). Die Laufzeit nimmt quadratisch mit der Leitungslänge zu. Das liegt daran, dass sich die Kapazitäten nur über das eine Leitungsende entladen können und dieser Weg über immer mehr Widerstände führt. Nur am Ende der Leitung ergibt sich wieder eine Abflachung. Aus dem Graphen liest man nach 30 Pixeln bereits eine Verzögerung von ca. 75ns ab. Rechnet man mit einem quadratischen Verlauf der Kurve bis zum 106. Pixel ergäbe sich eine Zeit von über  $1\mu$ s, um die ganze Leitung abzusuchen.

#### 4.2.3 Beschleunigungsmechanismus

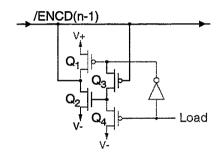

Die Lösung des Laufzeitproblems besteht darin, dass man bei jedem Pixel die in Abb. 18 gezeigte Schaltung einfügt. Diese Schaltung bietet den Leitungskapazitäten die Möglichkeit,

Abbildung 18: Beschleunigungsschaltung

sich bei jedem Pixel entladen zu können. Damit wird ein linearer Anstieg der Verzögerungszeit mit der Leitungslänge erwartet.

Die Schaltung arbeitet folgendermassen: In einem ersten Schritt wird die Leitung für die Pixelsuche vorbereitet. Dazu wird ein aktives LOAD-Signal angelegt, das die Transistoren  $Q_1$  und  $Q_4$  leitend macht. Über  $Q_1$  wird jetzt die Leitung aufgeladen.  $Q_4$  verhindert, dass sich  $Q_2$  nicht gleichzeitig im leitenden Zustand befindet. Wird jetzt das LOAD-Signal wieder weggenommen, befindet sich die Schaltung in einem Zustand mit Kippverhalten. Alle vier Transistoren sind im hochohmig. Erreicht nun das Suchsignal auf /ENCD die Schaltung, wird  $Q_3$  beim Unterschreiten seiner Schwellenspannung von 0.8V leitend. Damit wird auch  $Q_2$  leitend und die Spannung auf der /ENCD-Leitung heruntergezogen. Diese positive Rückkopplung hat zur Folge, dass die Schaltung in den leitenden Zustand kippt. So bietet sie für die nachfolgenden Leitungsabschnitte einen Weg, sich schnell zu entladen. Nun kippt nacheinander jeder Pixel. Dieser Vorgang ist zu vergleichen mit einer Kette von Dominosteinen. Mit dem LOAD-Signal werden alle Steine aufgestellt. Fällt der erste Stein um bewirkt das, das in schneller Folge alle Steine umkippen. Das Signal pflanzt sich mit gleichbleibender Geschwindigkeit durch die ganze Kette fort.

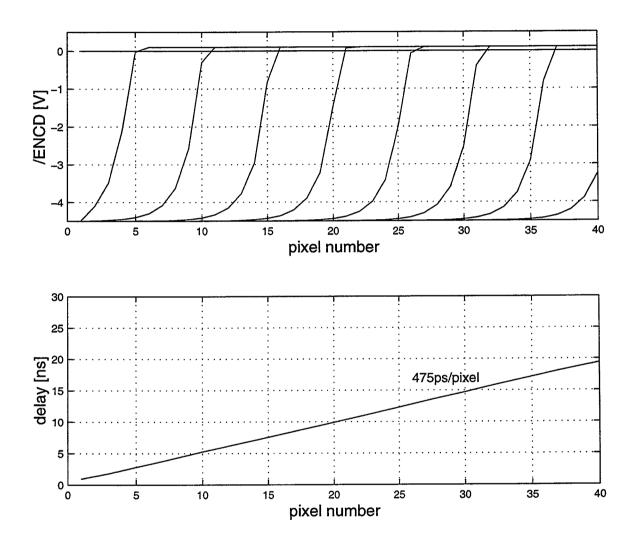

Abbildung 19: simulierter Spannungsverlauf auf der /ENCD-Leitung in Zeitabständen von 5ns mit Beschleunigungsmechanismus (oben), Signallaufzeit in Abhängigkeit von der Distanz zum Leitungsanfang (unten)

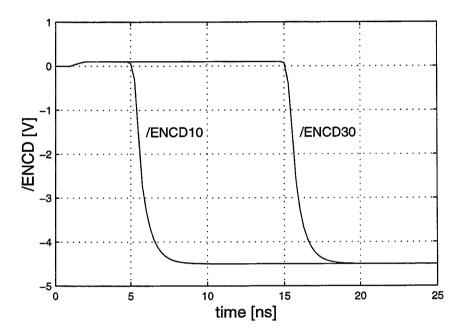

Abbildung 19 zeigt das Resultat einer Simulation des Zeitverhaltens mit der Beschleunigungsschaltung. Die Simulation wurde mit SPICE durchgeführt. Man Vergleiche dieses Ergebnis mit dem in Abbildung 17 ohne Beschleunigung. Im unteren Graphen sieht man den linearen Anstieg der Laufzeit mit zunehmendem Abstand vom Leitungsanfang. Abbildung 20 zeigt noch den zeitlichen Verlauf der Spannungen bei den Pixeln 10 und 30. Aus der Zeitdifferenz lässt sich eine Laufzeit von  $t_{DEL}$ =475ps pro Pixel ablesen. Das entspricht einer Pixel Suchfrequenz von 2.1GHz. Dieser Wert ist allerdings mit einigen Unsicherheiten behaftet, die sich aus folgenden Unzulänglichkeiten des Modells ergeben:

- Abweichung des SPICE Transistormodells vom realen Transistor

- Unberücksichtigte parasitäre Kapazitäten

Abbildung 20: zeitlicher Verlauf von /ENCD10 und /ENCD30 aus der Simulation

Neben der Frage nach der Laufzeit ist noch eine weitere Frage von Interresse: Wie lange bleibt die /ENCD-Leitung nach dem Anlegen des /LOAD-Impulses im geladenen hochohmigen Zustand? Die Spannung kann sich durch Leckströme der Transistoren im Laufe der Zeit etwas entladen. Wird dabei die Kippschwelle der Beschleunigungsschaltungen unterschritten, wird die Leitung sofort entladen. Dann ist die Auslese nicht mehr möglich. Diese Haltezeit  $t_{HOLD}$  sollte auf jeden Fall grösser sein, als die gesamte Zeit, die für die Auslese benötigt wird.

Die Messung von  $t_{DEL}$  und  $t_{HOLD}$  ist ein Gegenstand der vorliegenden Arbeit. Dazu ist auf dem DM\_PSI32 Chip die Teststruktur "WELLE" vorhanden, die im folgenden Abschnitt beschrieben wird.

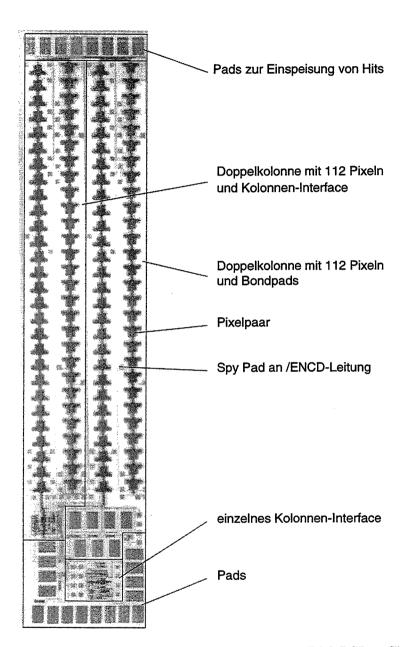

#### 4.3 Die Struktur "WELLE"

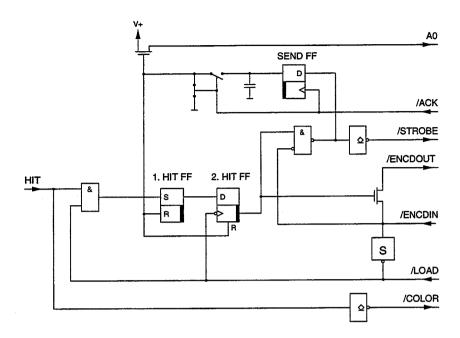

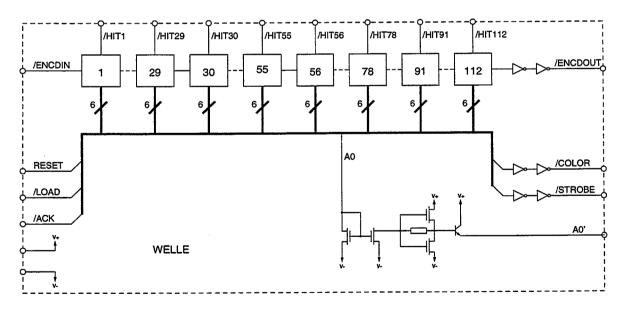

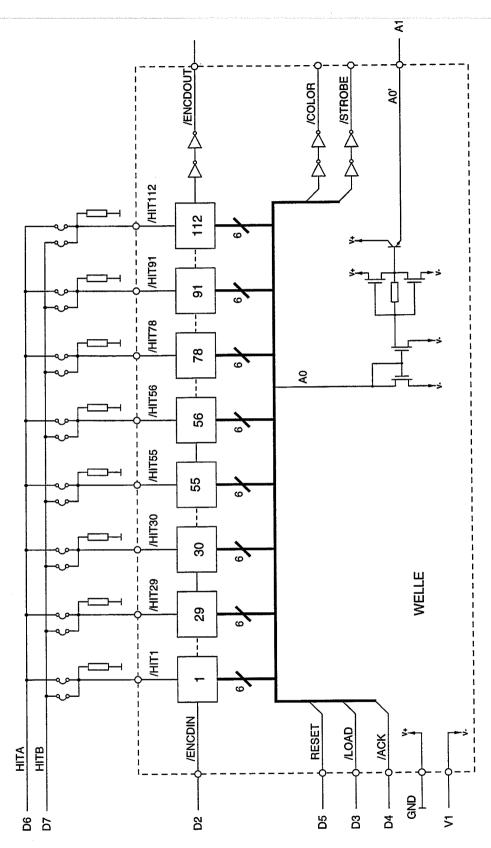

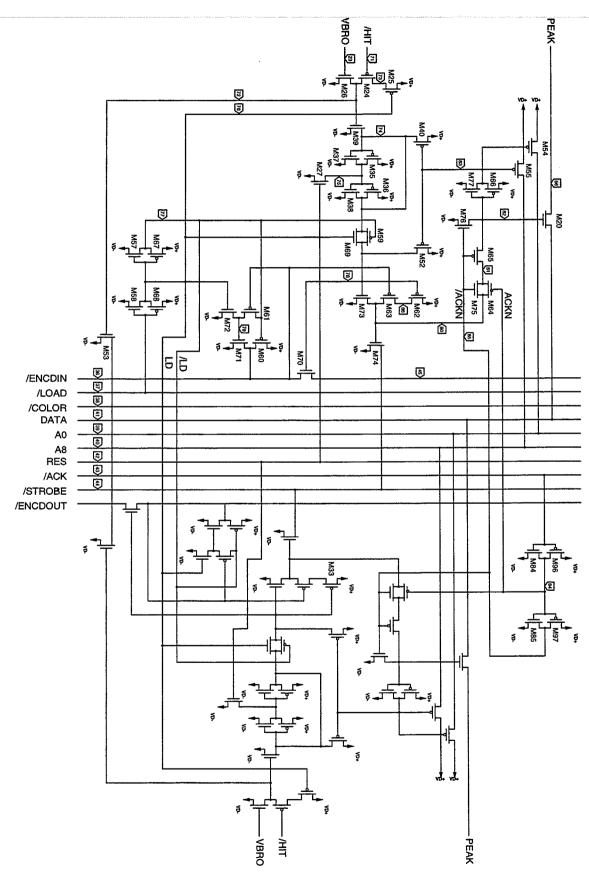

Abb. 21 zeigt die Anordnung der Komponenten auf der Struktur "WELLE". Aus Platzgründen sind die beiden Doppelkolonnen in der Mitte gefaltet. Für die Messungen von  $t_{DEL}$  und  $t_{HOLD}$  wurde nur die Doppelkolonne ohne Interface benutzt. Aus diesem Grund wird nicht näher auf die anderen Strukturen eingegangen. Abb. 22 zeigt das Blockschaltbild eines Pixels auf dieser Struktur. Es ist die Implementierung des totzeitfreien Auslesemechanismus. Der ganze Analogteil und die DATA- und A8-Leitung fehlen.

Ein HIT-Signal zieht die /COLOR-Leitung auf den Low-Pegel und setzt das erste HIT-Flip-Flop, ausser wenn gerade das LOAD-Signal anliegt. Wird jetzt von aussen ein LOAD-Impuls angelegt, übernimmt das zweite HIT-Flip-Flop den Zustand des ersten. Ist das zweite HIT-Flip-Flop gesetzt, unterbricht der FET die /ENCD-Leitung. Fällt nun die Spannung an /ENCDIN auf den Low-Pegel, Dann wird die /STROBE-Leitung auf den Low-Pegel gezogen. Ein /ACK-Impuls kann jetzt das Send-Flip-Flop setzen. Damit wird A0 ausgegeben und die HIT-Flip-Flops zurückgesetzt. Der FET schaltet die /ENCD-Leitung nun wieder durch.

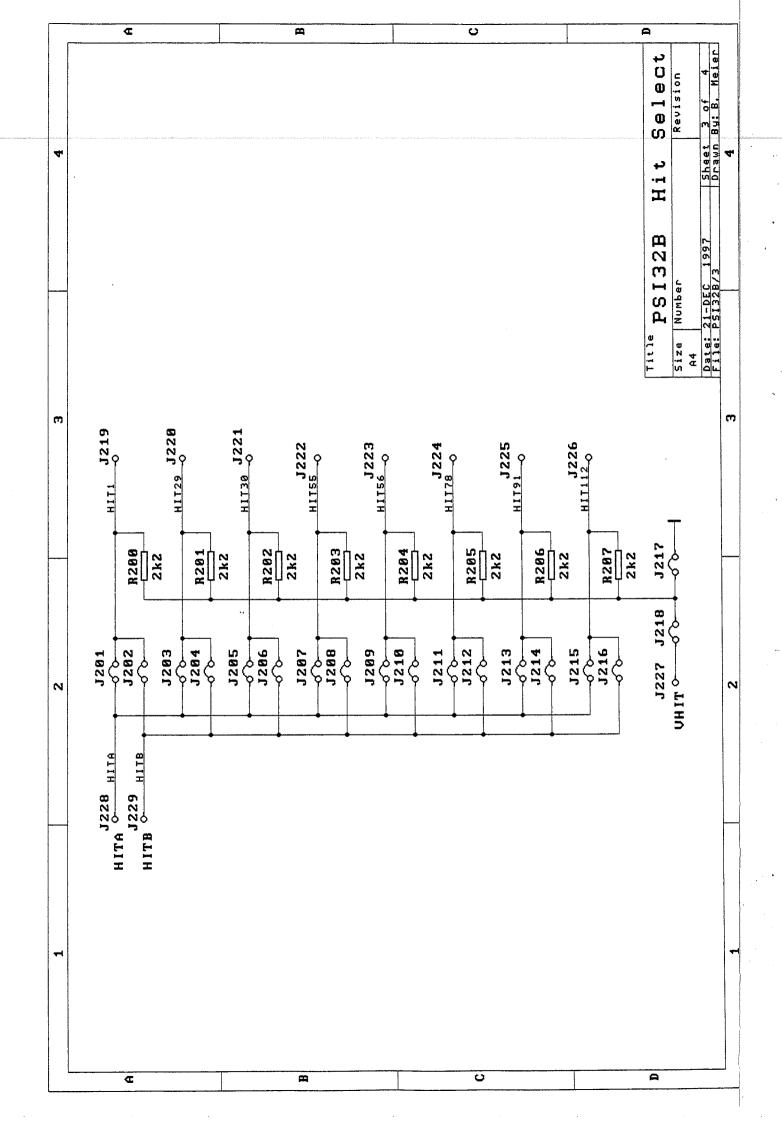

In Abb. 23 ist das Blockschema der gesamten Doppelkolonne wiedergegeben. Zur Simulation von Treffern sind die /HIT-Eingänge der Pixel 1, 29, 30, 55, 56, 78, 91 und 112 auf Bondpads geführt. Die anderen sind mit logisch 1 verbunden. An einigen Stellen sind an der /ENCD-Leitung Spy-Pads angebracht um mit einer Probe direkt auf dem Chip messen zu können. Die Leitungen für die Eingangssignale werden direkt zu den Pixeln geführt. Die Ausgangssignale /ENCDOUT, /COLOR und /STROBE laufen über Signaltreiber. Für A0 ist ein Stromspiegel mit nachgeschaltetem Spannungsfolger vorhanden.

Abbildung 21: Struktur "WELLE" auf dem DM\_PSI32 Chip

Abbildung 22: Blockschaltbild des Auslesemechanismus eines Pixels

Abbildung 23: Blockschema der Doppelkolonne ohne Interface auf der Struktur "WEL-LE". Sie enthält insgesamt 112 Pixel. Es sind aber nur diejenigen eingezeichnet, die einen angeschlossenen /HIT-Eingang besitzen.

#### 4.4 Die Struktur "CROSSTALK"

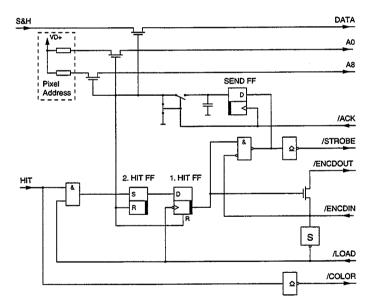

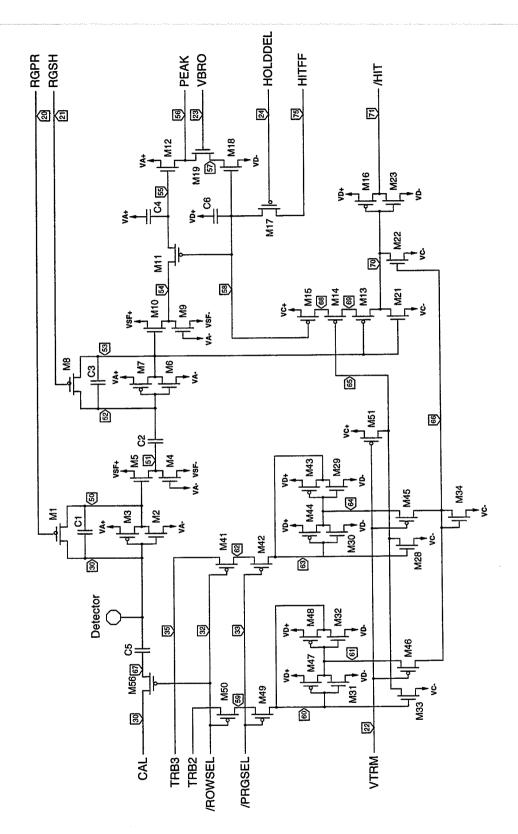

Zur Messung des Übersprechverhaltens wurde der Pixel Auslesemechanismus bei der Struktur "CROSSTALK" mit dem Analogteil ergänzt. Abb. 25 zeigt die Anordnung der Komponenten auf dieser Struktur.

Der Hauptteil besteht aus den beiden Doppelkolonnen, die unabhängig voneinander betrieben werden können. Das Interface beschränkt sich auf Treiber, die in die Signalleitungen zwischen den Bond Pads und den Doppelkolonnen eingefügt sind. Über die Bond Pads werden die diversen Spannungen angelegt, die zum Betrieb nötig sind. Die Busleitungen sowie die Programmierleitungen sind für jede Doppelkolonne separat herausgeführt. Einzig die /RESET- und CAL-Leitungen sind für beide zusammengefasst.

Zur Programmierung der Pixel dient ein vereinfachter Mechanismus, wie er schon beim DM\_PSI30 Chip verwendet wurde. Für die Selektierung der Reihen sind zwei 20 Bit-Schieberegister vorgesehen, mit denen die /ROWSEL-Signale für die beiden Doppelkolonnen festgelegt werden können. Sie sind zu einem 40 Bit-Schieberegister verkettet. Innerhalb einer Doppelkolonne können die Pixel nur paarweise angesteuert werden, da nur eine Speicherzelle pro Pixelpaar vorgesehen ist. Da nur zwei Doppelkolonnen vorhanden sind, ist für die Ansteuerung der Kolonnen kein Schieberegister vorgesehen. Die Leitungen CAL, TRB2, TRB3, sind für beide Doppelkolonnen direkt auf die Bond Pads geführt.

Abbildung 24: Blockschaltung des Auslesemechanismus eines Pixels auf der Struktur "CROSSTALK"

Abb. 24 zeigt das Blockschaltbild der Ausleselogik eines Pixels. Er unterscheidet sich von dem der Struktur "WELLE" in Abb. 22 nur darin, dass er um die Signale DATA und A8 ergänzt wurde. Der Analogteil entspricht dem aus Abb. 9. Die detailierten Schemas des Pixels befinden sich im Anhang A.

Abbildung 25: Anordnung der Komponenten auf der Struktur "CROSSTALK"

### 5 Messanordnung

### 5.1 Anforderungen

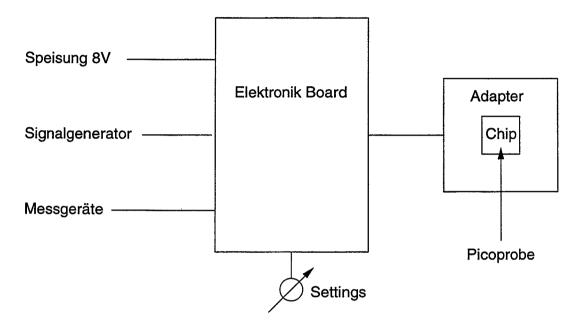

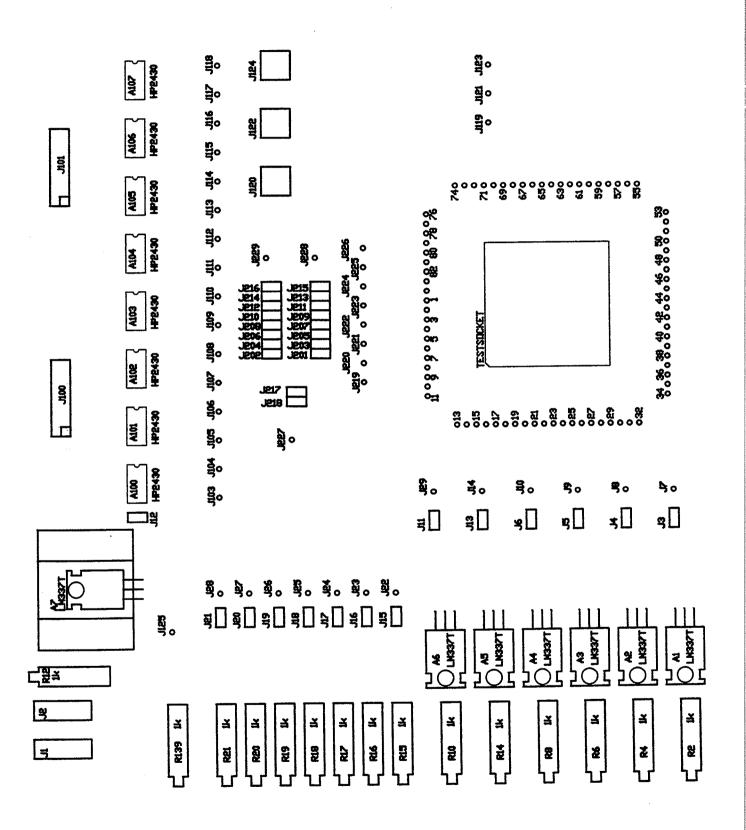

Um Messungen am DM\_PSI32 Chip durchzuführen, müssen diverse Spannungen und Signale auf den Chip geführt werden. Da mit verschiedenen Chips gearbeitet werden soll, muss ein austauschbarer Träger vorhanden sein, auf den man den Chip fest montieren kann. Abb. 26 zeigt die Hauptkomponenten, aus denen der Messaufbau besteht.

Abbildung 26: Hauptkomponenten des Messaufbaus

#### 5.2 Aufbau

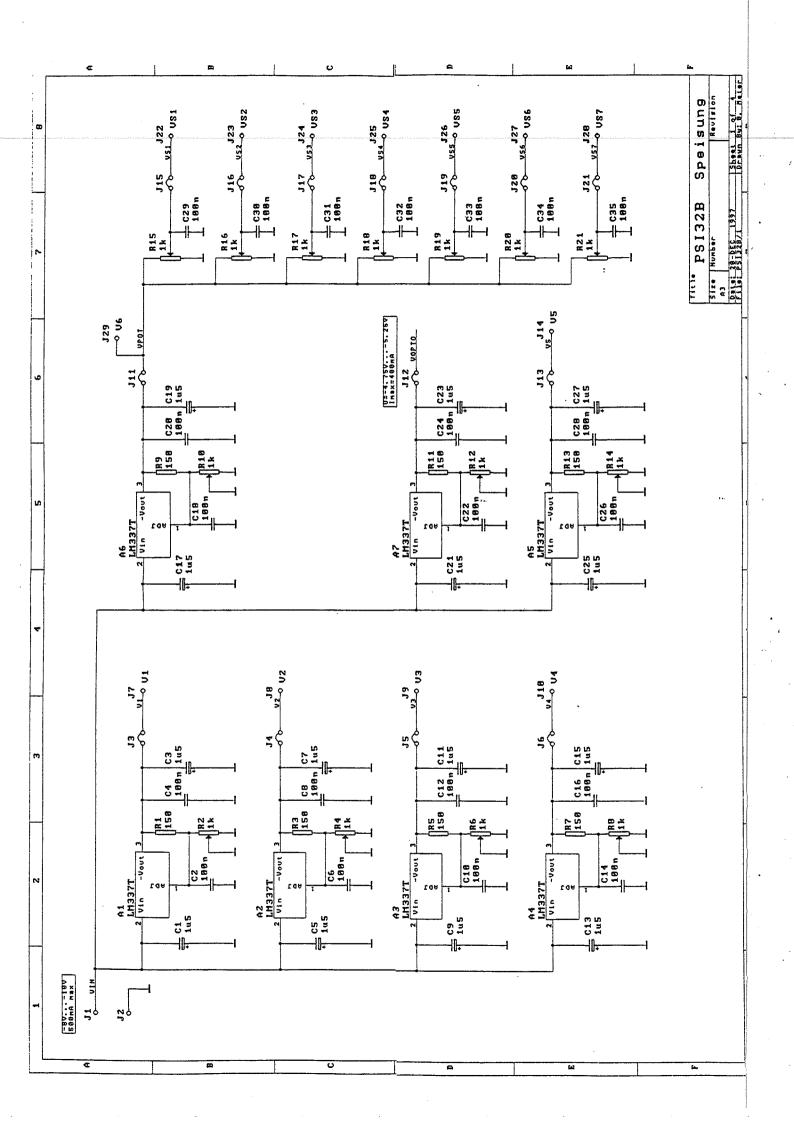

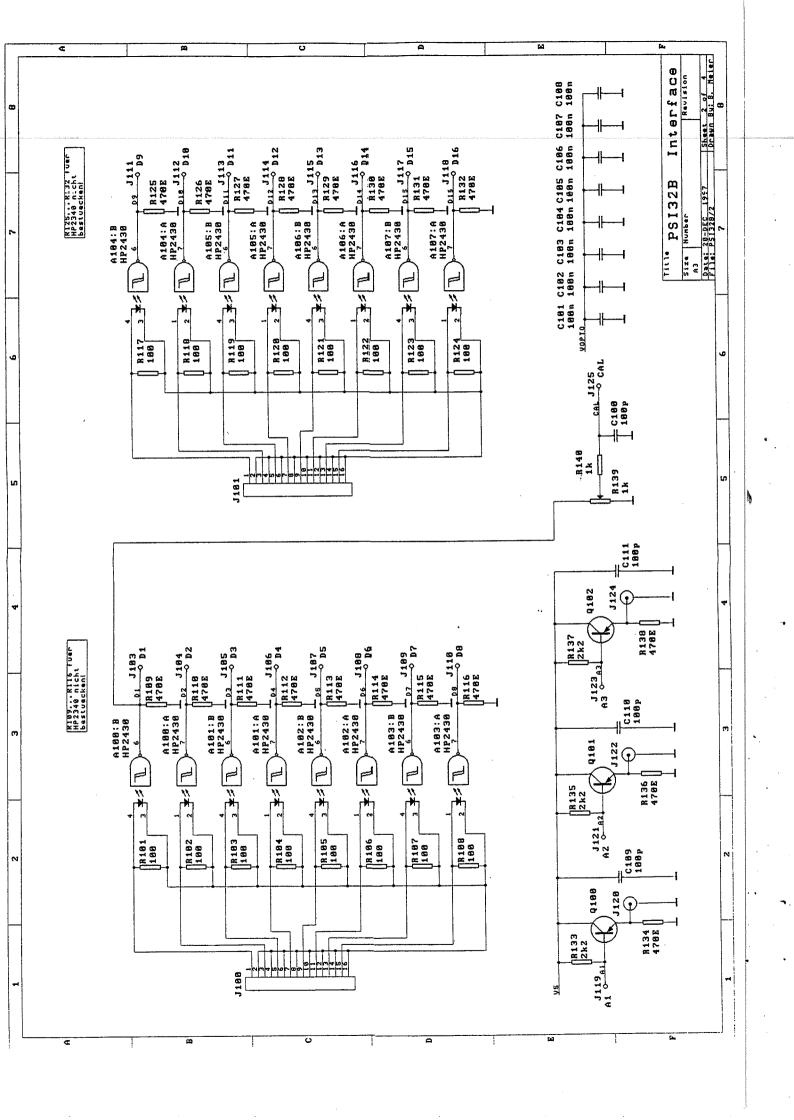

Das Elektronikboard stellt den Hauptteil des Messaufbaus dar. Es besteht aus einer bestückten Leiterplatte, an die die Messgeräte angeschlossen werden und der Chipadapter aufgesteckt werden kann. Es sind folgende Komponenten vorhanden:

- Sechs niederohmige Spannungsquellen V1 bis V6 die in einem Bereich von -1.25 bis -6V einstellbar sind. Sie dienen zur Spannungsversorgung des Chips. Drei davon werden auf dem Board selbst benötigt.

- Sieben Steuerspannungsquellen VS1 bis VS7, einstellbar im Bereich von 0 bis -6V. Sie bestehen nur aus Potentiometern und besitzen einen relativ hohen Innenwiderstand. Damit sind sie nicht zur Stromversorgung geeignet. Sie steuern Gates von FETs auf dem Chip, die die Eigenschaften der Schaltung beeinflussen.

- Galvanische Trennung der digitalen Signale. Damit keine Störungen über die Masseleitungen vom Bitmustergenerator auf den Chip gelangen können, werden die Signale über Optokoppler geführt. Die Optokoppler sind vom Typ HP2430 (Hewlett Packard) und besitzen Schaltzeiten von 8ns. Es befinden sich acht Stück auf dem Board. Über jeden von ihnen können zwei Signalleitungen geführt werden.

- Drei Spannungsfolger für die Signale DATA, A0 und A8. Diese werden gebraucht weil die Signale vom Chip zu schwach sind, um direkt die Messleitungen anzusteuern. Die Signale können auf dem Board an LEMO Buchsen abgenommen werden.

- Eine einstellbare analoge Signalquelle zur Erzeugung des Calibrate-Signals für die Crosstalk-Messung.

- Ein Verteiler zur Simulation von Treffern für die Messung an der Struktur "WELLE".

- Ein 84 poliger Stecksockel, um den Chipadapter aufzunehmen. Auf diesen Sockel passen auch normierte Chip Carrier.

Die Anschlüsse des Stecksockels für den Chipadapter sind auf dem Board noch nicht mit den Spannungs- und Signalquellen verbunden. Dies geschieht durch eine nachträgliche Verdrahtung. Damit lässt sich das gleiche Board durch entsprechendes Verdrahten für verschiedene Messungen einsetzen. Auf dem Board, unmittelbar bei den Kontakten des Stecksockels sind Plätze frei um Filterkondensatoren für die Speisespannungen oder Abschlusswiderstände zu bestücken.

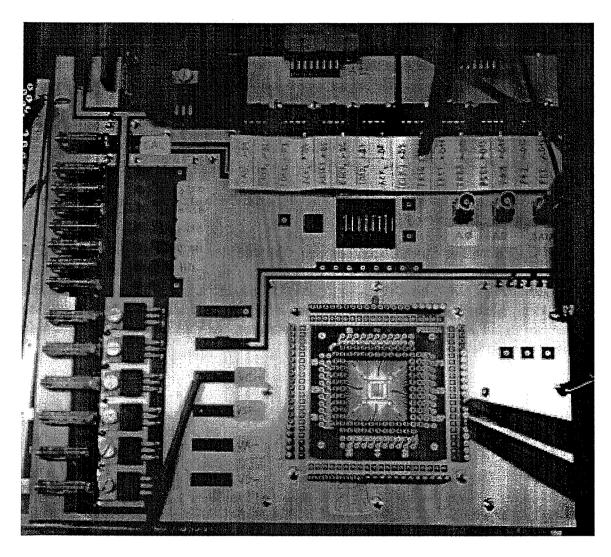

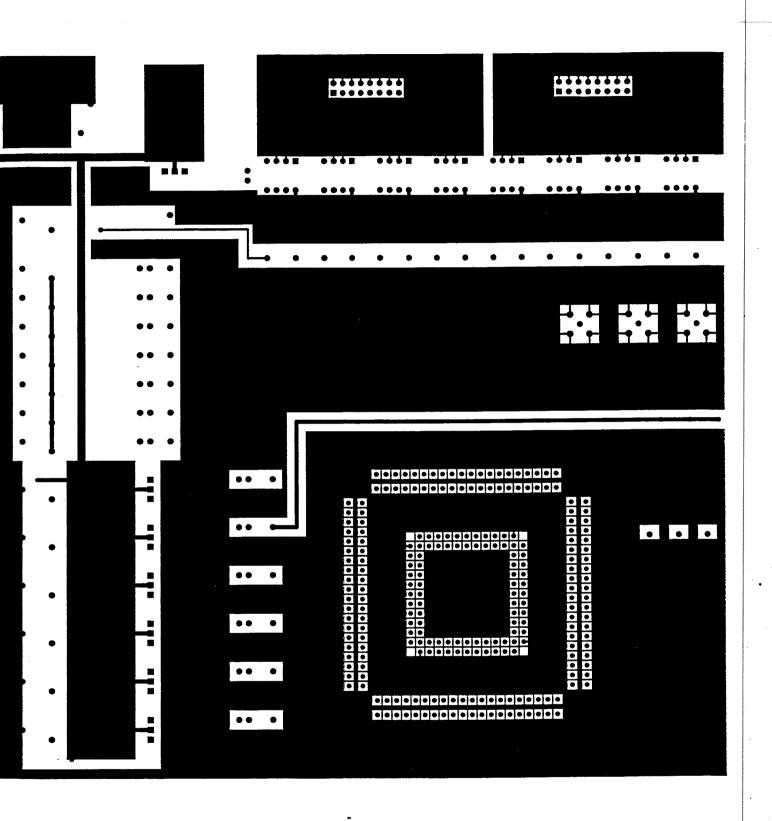

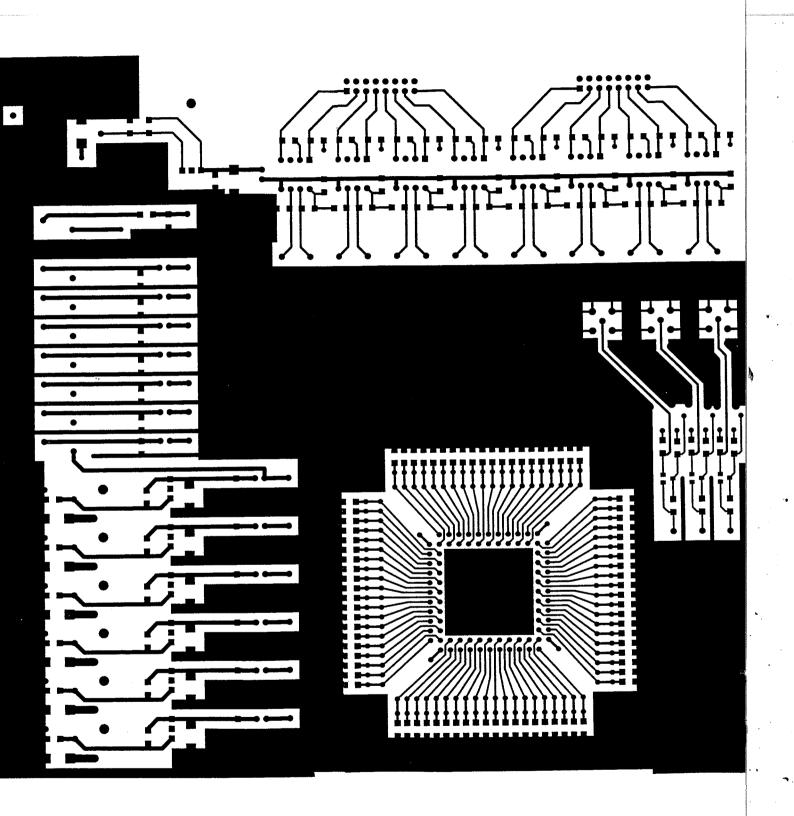

Abbildung 27: Vorderseite des Elektronikboards. am linken Rand befinden sich unten die sechs regelbaren Spannungsquellen und oben die Potentiometer für die Steuerspannungen und das Analogsignal. Oben befinden sich die Optokoppler mit der Stromversorgung links davon. Unten etwas rechts befindet sich der Chipadapter mit dem DM\_PSI32 Chip.

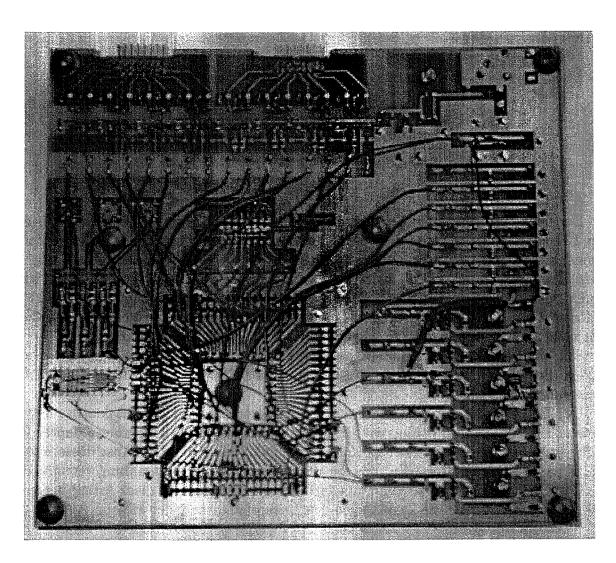

Abbildung 28: Rückseite des Elektronikboards mit der Verdrahtung für die Crosstalk-Messung.

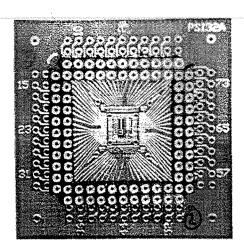

Abbildung 29: Adapter mit PSI32 Chip

Der Chipadapter besteht aus einer Glasfaser-Epoxy Leiterplatte. Er ist der Träger für den Chip und stellt die Verbindung vom Chip zum Elektronikboard her. Auf der Vorderseite befinden sich dazu die Leiterbahnen und in der Mitte eine freie Fläche, um den Chip aufzukleben (Abb. 29). Die elektrischen Verbindungen von Chip zum Adapter werden durch Bond-Drähte aus Al ( $25\mu$ m Durchmesser) hergestellt. Es ist nicht möglich, alle Pads auf dem Chip gleichzeitig zu bonden. Daher wurde für die unterschiedlichen Messungen mit mehreren Adaptern mit verschiedenen Bond-Konfigurationen gearbeitet.

Auf der Rückseite des Adapters befindet sich eine Kupferfläche die geerdet wird. So werden Streufelder vermieden und Kopplungen der Leitungen untereinander und mit der Umgebung unterdrückt.

Um den Adapter mit dem Elektronikboard zu verbinden sind Kontaktstifte bestückt. Diese besitzen auf der Vorderseite Buchsen. Damit lassen sich mehrere Adapter durch aufeinanderstecken miteinander in Kontakt bringen. So können die Anschlüsse mehrerer Chips parallelgeschaltet werden, was die Verdrahtung bei der Bestrahlung vereinfacht.

Das Elektronikboard und der Chipadapter wurden speziell für diese Arbeit hergestellt. Die Schaltschemas und die Layouts von den Leiterplatten befinden sich im Anhang C.

### 5.3 Messgeräte

Abbildung 30: Messplatz

Abb. 30 zeigt den Messplatz mit den wichtigsten Messgeräten. In der Mitte befindet sich das Elektronikboard auf einer leitenden Unterlage. Diese ist geerdet (Schutzleiter), um den Chip vor statischer Aufladung zu schützen. Aus demselben Grund sind auch alle Geräte geerdet. Das Erdungspotential ist mit der Masse der Speisespannungen für den Chip verbunden.

Folgende Mess- und Testgeräte wurden verwendet:

- 2 Kanal Oszilloskop, Tektronix Typ 2465B, 400MHz mit Sonden 10:1, 10MΩ, 10pF

- DVM, BBC Typ MA2D, 3 1/2 Stellen, zur Messung der Versorgungsspannungen und Ströme.

- $\bullet\,$  DVM, Metex Typ M-4650CR, 4 1/2 Stellen, zur Messung der Schaltschwellen für die Crosstalk-Messung

- ullet Picoprobe, Modell 12C mit 1M $\Omega$  Eingangswiderstand und 100fF Eingangskapazität, um direkt auf dem Chip zu messen.

- Binokular zur Platzierung der Picoprobe auf dem Chip.

- HP Patterngenerator zur Erzeugung der digitalen Signale für den Chip.

- Labornetzgerät zur Stromversorgung des Elektronikboards (ca. 8V)

Das zweite DVM, die Picoprobe und das Binokular sind in Abb. 30 nicht vorhanden.

### 6 Zeitmessungen an der Struktur "WELLE"

#### 6.1 Inbetriebnahme

Zur Messung des Zeitverhaltens des Auslesemechanismus musste die Struktur "WELLE" auf dem DM\_PSI32 Chip in Betrieb genommen werden. Dazu wurden einige Chips auf Adaptern montiert und die Bond-Drähte zum Betreiben der Doppelkolonne angebracht. Das Elektronikboard musste dementsprechend verdrahtet werden. Abb. 31 zeigt die dazugehörige Schaltung zusammen mit dem Blockschema der Doppelkolonne.

Die Speisung erfolgt mit der Spannungsquelle V1. Die Bussignale werden von den Signalquellen D2, D3, D4 und D5 geliefert. Mit den Signalen D6 und D7 stehen zwei unabhängige Quellen für die Treffersimulation zur Verfügung. Über die Jumper auf dem Board lassen sie sich verschiedenen Pixeln zuordnen. Mit den acht Widerstände werden nicht angeschlossene HIT-Eingänge auf Masse gelegt. Die Ausänge /ENCDOUT, /COLOR und /STROBE können auf dem Board zur Signalmessung abgegriffen werden. Der Ausgang A0 ist mit dem Eingang des Spannungsfolgers A1 verbunden. Das Signal kann dann niederohmig an der entsprechenden LEMO-Buchse abgegriffen werden.

Bei der Funktionskontrolle der Doppelkolonne stellte sich heraus, dass einige Designfehler auf dem Chip vorhanden sind. Zum einen können die Signale /COLOR und /STROBE nicht beobachtet werden, da auf dem Chip die Abschlusswiderstände vor den Ausgangstreibern nicht vorhanden sind. D. h. die beiden Leitungen befinden sich in einem undefinierten Zustand. Der andere Fehler betrifft die /ENCD-Leitung. Alle Transistoren auf der zweiten Kolonne sind kurzgeschlossen. Damit ist nur die erste Kolonne für die Messungen verwendbar. Die Messungen werden aber durch diese beiden Fehler nicht wesentlich beeinträchtigt.

Abbildung 31: Schaltung für die Messungen an der Welle

### 6.2 Messung der Laufzeit $t_{DEL}$

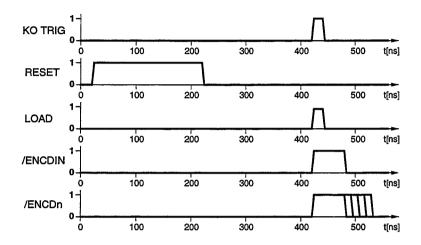

Für die Durchführung der Laufzeitmessung wurde mit dem in Abb. 32 gezeigten Signalverlauf gearbeitet. Die Generierung geschieht durch den Bitmustergenerator, der durch ein entsprechendes Programm gesteuert wird.

Abbildung 32: Zeitlicher Ablauf der Laufzeitmessung

Mit einem RESET-Signal werden zuerst alle Hit-Flip-Flops der Pixel gelöscht. Danach wird die /ENCD-Leitung mit einem LOAD-Impuls und dem Anlegen des /ENCDIN-Signals aufgeladen. Gleichzeitig wird ein Triggersignal für das Oszilloskop generiert. Die Messung beginnt mit der fallenden Flanke an /ENCDIN. Der ganze Vorgang wird alle 700ns periodisch wiederholt.

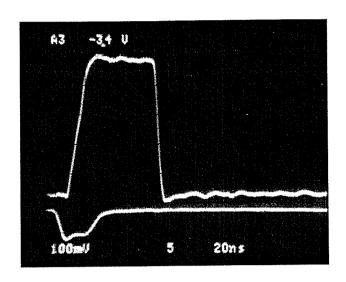

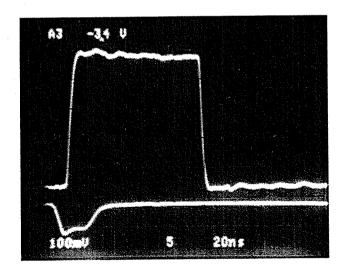

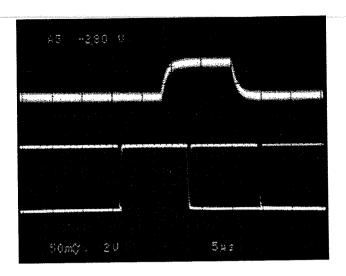

Mit einer Picoprobe wird nun an verschiedenen Stellen auf dem Chip, wo Spy-Pads angebracht sind, gemessen. Die gemessenen Signale vor den Pixeln 2 bzw. 50 sind auf Abbildung 33 bzw. 34 zu sehen.

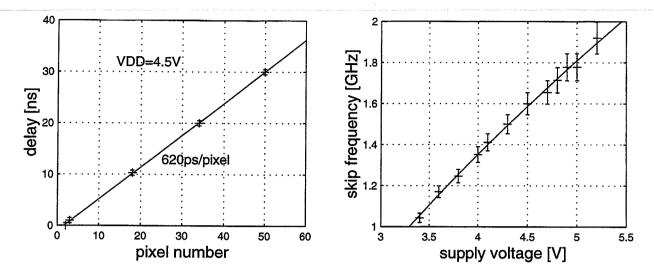

Um eine Laufzeitmessung durchzuführen wurden bei fünf Messpunkten an der ENCD-Leitung die Verzögerungszeiten gemessen. Durch lineare Interpolation wurde daraus die Laufzeit pro Pixel  $t_{DEL}$  ermittelt. Bei einer Speisespannung von -4.5V, dem typischen Wert, ergab sich ein Wert von

$$t_{DEL} = (620 \pm 5) \text{ps}$$

Da für die Messung nur zwei Chips zur Verfügung standen, lässt sich nichts genaues über die Streuung zwischen verschiedenen Chips aussagen. Der Wert des zweiten Chips lag aber nur ca. 2% darüber.

Vergleicht man das Ergebnis mit der Simulation aus Abschnitt 4.2.3, dann fällt die etwas grössere Zeit auf. Das ist auf die bei der Simulation nicht berücksichtigten parasitären Kapazitäten zurückzuführen. Der gemessene Wert liegt aber innerhalb der Erwartungen.

Die Laufzeitmessungen wurden bei verschiedenen Speisespannungen durchgeführt. In Abb. 35 rechts zeigt das Resultat. Anstelle von  $t_{DEL}$  ist die Pixel-Suchrate aufgetragen die

Abbildung 33: ENCD2 mit Picoprobe gemessen

Abbildung 34: ENCD50 mit Picoprobe gemessen

Abbildung 35: Resultate der Laufzeitmessungen. Links ist die Signalverzögerung entlang der /ENCD-Leitung gezeigt. Der rechte Graph zeigt die Pixel-Suchrate in Abhängigkeit von der Speisespannung.

man nach der Gleichung

$$f_{skip} = \frac{1}{t_{DEL}}$$

berechnet ist.

Das Ansteigen der Abfragerate bei zunehmender Spannung ist auf folgende Weise zu erklären. Da bei zunehmender Speisespannungen auch die Gate Spannungen der NFETs in der /ENCD-Leitung und im Beschleunigungsmechanismus zunehmen, sinkt ihr Drain-Source Widerstand. Das heisst dass alle RC-Zeitkonstanten kleiner werden. Als Folge davon skaliert auch  $t_{DEL}$  etwa mit dieser Zeitkonstante. Zusätzlich wirkt sich noch aus, dass die gleichbleibende Schwellenspannung von 0.8V der Beschleunigungsschaltung schneller erreicht wird, da in Vergleich dazu die anderen Spannungen grösser sind.

### 6.3 Messung der Haltezeit $t_{HOLD}$

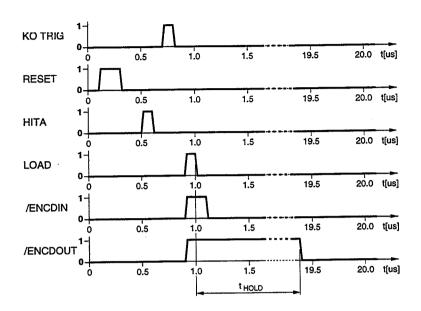

Für die Messung der Haltezeit wurde der Bitmustergenerator zur Erzeugung der in Abb. 36 gezeigten Signale programmiert. Zuerst löscht wieder ein RESET-Signal die Hit-Flip-Flops der Pixel. Danach wird das HITA-Signal erzeugt. Dieses wird durch setzen der Jumper auf den ersten Pixel gegeben. Alternativ dazu kann auch einer der anderen Pixel ausgewählt werden. Nach einer kurzen Verzögerung wird das Triggersignal für das Oszilloskop erzeugt und anschliessend die /ENCD-Leitung geladen und eine Pixelsuche gestartet. Das Signal bleibt wegen dem HIT-Signal und weil keine Auslese erfolgt beim ersten Pixel stehen. Ab jetzt wartet man so lange, bis die Spannung auf der /ENCD-Leitung von selbst kippt. Dies ist die Haltezeit  $t_{HOLD}$ . Die Messung wird ca. alle 20ms wiederholt.

Abbildung 36: Zeitdiagramm für die Messung Der Haltezeit

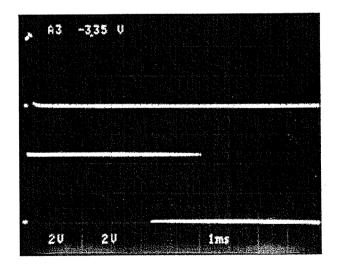

Abbildung 37: Oben: /ENCDIN; unten: /ENCDOUT. Der Chip wurde bei der Messung beleuchtet. Man erkennt den Jitter, der durch das 100Hz Flackern entstand.

Abb. 37 zeigt ein gemessenes Signal. Oben ist /ENCDIN zu sehen und unten /ENCDUT.  $t_{HOLD}$  hängt von der Stärke der Beleuchtung des Chips ab. Bei der Messung war der Chip dem Licht einer Leuchtstofflampe ausgesetzt. Wegen dem 100 Hz Flackern und weil in der Aufnahme mehrere Messung überlagert wurden, beobachtet man einen Jitter beim /ENCDOUT-Signal.

Um repräsentative Messwerte zu bekommen muss der Chip abgedunkelt werden. Dann steigt die Haltezeit auf ihren Maximalwert. Dieser Wert ist sehr konstant, besitzt also nur einen sehr kleinen Jitter. Bei 4.5V Betriebsspannung liegt dieser Wert bei

$$t_{HOLD} = (12 \pm 0.2) \text{ms}.$$

Für den zweiten Chip ergibt sich ein Wert von 11.5ms.

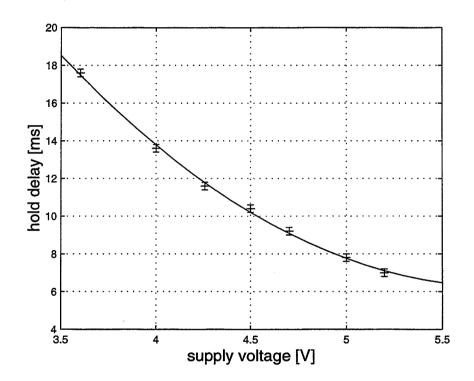

Abbildung 38:  $t_{HOLD}$  in Abhängigkeit von der Betriebsspannung

Abb. 38 zeigt  $t_{HOLD}$  in Abhängigkeit von der Betriebsspannung. Da der Wert von  $t_{HOLD}$  bei konstanten Umwelteinflüssen wie Beleuchtung und Temperatur einen konstanten Wert annimmt, liegt es nahe, die Ursache in Entladevorgängen zu suchen. Dabei sind Leckströme die Ursache. Ist die Spannung auf der /ENCD-Leitung einmal bis zur Schwellenspannung der Beschleunigungsschaltungen gefallen, setzt der Kippvorgang ein.

In Betracht kommen Leckströme der FETs der Beschleunigungsschaltung. Dafür sprechen weitere Untersuchungen mit verschieden langen Leitungsabschnitten die immer etwa das gleiche Ergebnis für  $t_{HOLD}$  liefern. Eine Auslese dauert maximal ca. 200ns.  $t_{HOLD}$  liegt

also weit über der Zeit für eine Pixelauslese und genügt daher den geforderten Ansprüchen vollkommen.

Alle diese Messungen wurden bei unbestrahlten Chips durchgeführt. Es stellt sich also noch die Frage, wie sich die gemessenen Parameter durch die Bestrahlung verändern. Diese Messungen müssen noch durchgeführt werden und werden in einem späteren Report bekanntgegeben.

#### 6.4 Test des Auslesevorgangs

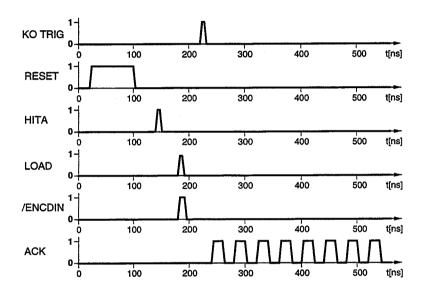

Als abschliessenden Test der Welle habe ich noch einen vollständigen Auslesevorgang untersucht. Die Signale vom Bitmustergenerator zeigt Abb. 39.

Abbildung 39: Zeitdiagramm für eine Auslese von acht Pixeln

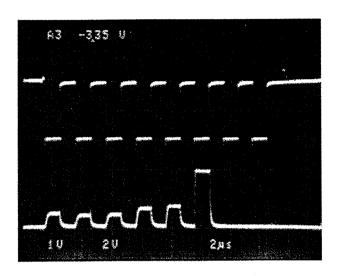

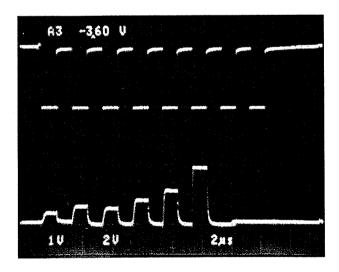

Nach dem Reset wird ein Treffer bei allen acht Pixeln ausgelöst. Dann werden in genügend grossen Zeitabständen die acht /ACK-Impulse generiert. Diese sollen die acht Pixel auslesen. Die gewählte Zeit ist so gross, dass das Suchsignal die Pixel jeweils erreichen kann. Die Abbildungen 40 und 41 zeigen die gemessen Signale für zwei verschiedene Chips. Oben befinden sich die /ACK-Impulse und unten die A0-Signale. Man beachte die Unterschiede der Impulshöhen bei A0 zwischen den verschiedenen Chips. Dass der drittletzte Impuls viel höher ist als die anderen und die letzten beiden gar nicht vorhanden sind, liegt daran, dass wegen des einen Designfehlers die Transistoren in der ENCD-Leitung kurzgeschlossen sind. Weil das Signal dort trotz der Treffer durchlaufen kann, antworten alle Pixel bei der drittletzten Abfrage gleichzeitig.

Abbildung 40: /ACK (oben) und A0 (unten) beim Auslesevorgang

Abbildung 41: Wie bei Abb. 40 aber ein anderer Chip

## 7 Messung des Übersprechens

#### 7.1 Inbetriebnahme

Die Messung des Übersprechens habe ich an der Struktur "CROSSTALK" durchgeführt. Dabei ging es darum, wie sich der Auslesevorgang auf die Pixel in Bezug auf Störungen auswirkt. Dieses Problem tritt, wie schon in Abschnitt 4.4 erwähnt, bei einer totzeitfreien Auslese auf.

Für die Inbetriebnahme der Struktur "CROSSTALK" waren zuerst die gleichen vorbereitenden Schritte nötig wie bei der Struktur "WELLE". Das Bord musste neu verdrahtet werden. Für den Betrieb der beiden Doppelkolonnen wurden jetzt alle Spannungs- und Signalquellen auf dem Elektronikboard gebraucht. Ausserdem mussten einige Modifikationen, zur Verminderungen von Störungen vorgenommen werden. Diese und weitere Massnahnen werden in den folgenden Abschnitten beschrieben.

### 7.2 Programmierung der Pixel

Durch gezieltes Einschalten einzelner Pixel lässt sich das Störverhalten von Pixeln an verschiedenen Plätzen auf dem Chip studieren. Für die Kalibrierung der Pixel war es ausserdem erforderlich, Calibrate-Signale auf die Pixel aufzuschalten.

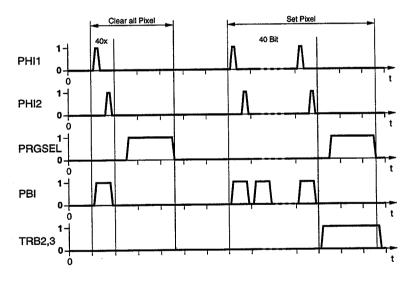

Abbildung 42: Zeitdiagramm für die Programmierung der Pixel

Abb. 42 zeigt den Signalverlauf für eine Programmierung, wie sie für die Kalibrierung der Pixel benutzt wurde. Im ersten Teil werden alle Pixel abgeschaltet. Dazu müssen zuerst alle Pixel selektiert werden indem das ganze 40 Bit-Schieberegister mit Nullen gefüllt wird. Wenn TRB2=TRB3=0 sind, löscht ein PROGSEL-Impuls alle Register in den Pixeln. Im zweiten Teil werden die einzelnen benötigten Pixel wieder eingeschaltet. Dazu

muss ein entsprechendes Steuerwort zur Pixeladressierung in das Schieberegister geladen werden. Wenn TRB2=TRB3=1 sind, aktiviert ein PROGSEL-Impuls die adressierten Pixel. Bleibt das letzte Steuerwort im Schieberegister, sind zu den aktiven Pixel auch gleich die Calibrate-Signale durchgeschaltet. Das wird zur Kalibrierung so gebraucht. Für die Crosstalk-Messung muss das Schieberegister in einem dritten Teil wieder gelöscht werden.

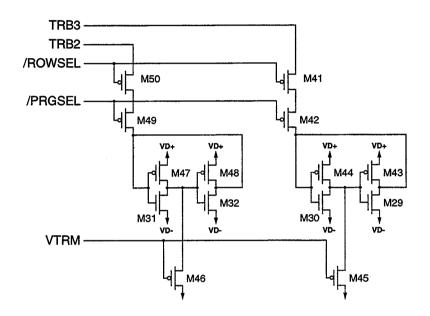

Die Programmierung der Pixel war mit gewissen Schwierigkeiten verbunden. Das liegt an Dimensionierung der Speicherzellen auf dem Chip. Abb. 43 zeigt den entsprechenden Schaltungsteil des Pixels.

Abbildung 43: Schema der Speicherzellen

Die engen Platzverhältnisse auf dem Pixel erzwingen eine Schaltung, die mit möglichst wenigen Transistoren auskommt. Als Preis dafür mussten Kompromisse eingegangen werden. Es sind zwei Speicherzellen vorhanden, eine für TRB2, bestehend aus den Transistoren M47, M48, M31 und M32, und die andere für TRB3, bestehend aus M29, M30,M43 und M44. Sie sind aus zwei verketteten Invertern aufgebaut. Um den Zustand von TRB2 bzw. TRB3 in die Speicherzellen zu schreiben müssen M50 und M49 bzw. M41 und M42 durch das Anlegen von /ROWSEL und /PRGSEL leitend gemacht werden. Nun beginnt der Kampf der Transistoren. Auf dem Testchip waren die PFETs M41, M42, M49 und M50 zu "schwach" und die NFETs M29 und M32 zu "stark". Soll z. B. TRB2=1 in die gelöschte Zelle geschrieben werden, müssen M50 und M49 gegen M32 arbeiten. Wenn sie es schaffen, die Spannung um die halbe Betriebsspannung zu erhöhen, kippt die Speicherzelle in den neuen Zustand. Durch senken der Spannung an VTRM lässt sich Vorgang etwas begünstigen. Für die Crosstalk-Messungen ist es wichtig zu wissen, ob die Zellen wirklich gesetzt wurden. Eine Möglichkeit das zu prüfen liegt im Beobachten der Span-

nungen an TRB2 bzw. TRB3. Haben alle selektierten Pixel den Zustand von TRB2 bzw. TRB3 angenommen, fliest über diese Leitungen kein Strom mehr in den Chip. Dann ist die äussere Signalquelle entlastet und die Spannung steigt etwas an. Damit erhält man die Gewissheit, dass die Speicherzellen richtig programmiert wurden. Dieser Fehler wird in den neuen Layouts korrigiert.

Das Programmieren von Nullen geht hingegen problemlos. Auf logisch Null können alle Zellen gleichzeitig programmiert werden. Auf logisch Eins hingegen nur einige wenige auf einmal. Das ist der Grund dafür, dass beim oben beschriebenen Algorithmus zuerst alle Zellen gelöscht wurden.

### 7.3 Wahl der Betriebsspannungen

Für die Durchführung mussten die Werte diverser Betriebs- und Regelspannungen festgelegt werden. Alle positiven Spannungen am Chip liegen auf Masse und die negativen sind mit den Spannungsquellen des Elektronikboards verbunden.

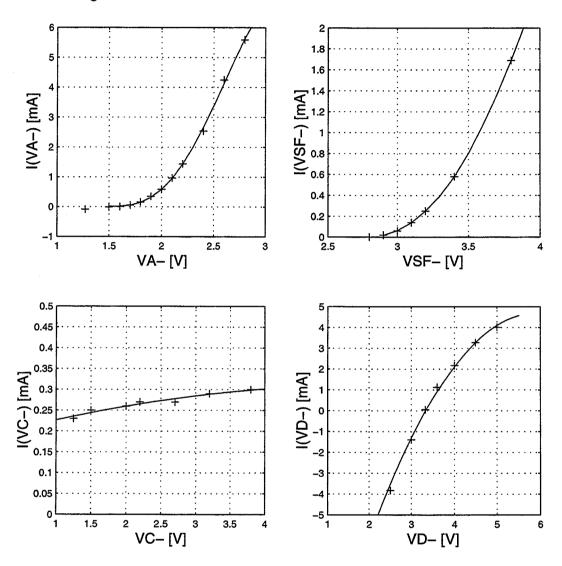

Die Spannung VD- für den digitalen Teil wurde auf -4.5V festgelegt. Dort liegt etwa das Optimum zwischen Schnelligkeit und Stromaufnahme. In Abb. 44 ist die Stromaufnahme bei VD gezeigt. Er trägt mit dem grössten Beitrag zur Gesamtstromaufnahme bei. Zu beachten ist, dass bei zu kleiner Spannung die Stromrichtung umkehrt. Das liegt möglicherweise an Rückspeisungen von den Signalleitungen.

Der Spannungswert für VA- von -2V wurde vom DM\_PSI30 Chip übernimmen. Der Strom wird durch die Querströme der Transistorpaare der invertierenden Verstärkern verursacht. Sobald die Summe der Schwellenspannung der Transistorpaare (ca. 1.5V) überschritten wird, beginnt Strom zu fliessen (Abb. 44). Damit die Verstärker arbeiten, muss die Spannung über diesem Wert liegen.

Mit der Spannung VSF wird der Strom der Spannungsfolger eingestellt. Sie liefert die Drain Spannung eines NFETs, der als regelbare Stromquelle benutzt wird (siehe Schema im Anhang A). Für den Wert des Stromes ist die Differenz zwischen VA- und VSF- entscheidend. In Abb. 44 ist der Strom bei VA-=-2V angegeben. Wählt man eine Strom von 3  $\mu$ A pro Spannungsfolger ergibt sich bei zwei Spannungsfolgern pro Pixel und total 80 Pixeln ein Gesamtstrom von 480  $\mu$ A, der über VSF fliesst. Bei VSF-=-3.4V und VA-=-2V wird dieser Strom erreicht. VA- und VSF- bewirken zusammen eine Verlustleistung von 35  $\mu$ W pro Pixel.

Die Wahl der Spannung für die Komparatoren VC- muss immer etwas unterhalb von VA- liegen. Sie wird bei den Messungen variiert, um die Schaltschwelle einzustellen.

Der Wert der Spannung an VTRM für die Trimmung des Komparators ist bei der Crosstalk-Messung nicht von grosser Bedeutung weil die Trimmung ausgeschaltet war. Sie muss einfach so gewählt werden, dass die Schaltung überhaupt arbeitet. Sie wurde mit -1.8V möglichst tief gewählt, um das Kippen der Speicherzellen bei der Programmierung etwas zu erleichtern.

VBRO ist für das funktionieren des Pegelwandlers zwischen dem Digital- und dem Analogteil zuständig und muss mit -3.5V um 1V über der Spannung an VD- liegen.

Für VHD wurde bei allen Messungen ein Spannungswert von -4V beibehalten. Die Wahl der Regelspannungen VRGPR und VRGSH für die den Verstärker und Shaper wird in Abschnitt 7.5 genauer beschrieben.

Abbildung 44: Stromaufnahme an den vier Speisungen in Abhängigkeit von der Spannung. Bei der Variation einer Spannung wurden für die anderen folgende Fixwerte eingestellt: VA-=-2V; VSF-=-3.4V; VC-=-2.2V; VD-=-4.5V

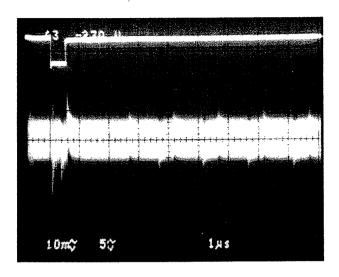

### 7.4 Entstörung

Das Ziel der Crosstalk-Messung ist die Messung des Übersprechens auf dem Chip. Um die Crosstalk-Messungen durchzuführen, ist es also wichtig, dass die Störungen, die durch das Elektronikboard verursacht oder übertragen werden, so weit gesenkt werden, dass sie

nicht mehr ins Gewicht fallen. Dazu waren verschiedene Massnahmen nötig. Abb. 45 zeigt Störungen auf VA-.

Abbildung 45: Unten sind die gemessenen Störungen auf VA- zu erkennen (10mV/div). Oben sieht man das LOAD-Signal. Deutlich sind die Auswirkungen auf VA- zu erkennen. Das breite Band setzt sich aus Rauschen und einem Störsignal von 27MHz und ca. 400MHz zusammen.

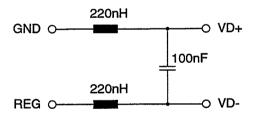

Abbildung 46: LC-Filter zur Entkopplung von VD

Als erste Massnahme musste die Speisung des Digitalteils, als Verursacher von Störungen, vom Rest getrennt werden. Dazu wurde der LC-Tiefpass in Abb. 46 in die Zuleitungen von VD+ und VD- zum Chip eingebaut. Damit war der grösste Teil der Störungen weg. Auch die Speisung der Optokoppler auf dem Board sind eine Ursache von Störungen. Durch die gleiche Massnahme konnten auch diese Störungen beseitigt werden.

Die digitalen Signale der Optokoppler bilden eine weitere Quelle von Störungen. Um diese zu unterdrücken, mussten die Anstiegs- und Abfallzeiten der Signale RESET, /ENCDIN, LOAD und /ACK durch RC-Tiefpässe ( $R=1\mathrm{k}\Omega,\,C=100\mathrm{pF}$ ) von 8ns auf 100ns erhöht werden. Diese Massnahme ist zulässig, da die Signalflanken auf dem Chip durch Dreifachinverter wieder regeneriert werden. Ausserdem kommen die Signale bei einem kompletten

Pixel-Auslesechip auch nicht von aussen sondern werden im Kolonnen-Interface erzeugt. Mit all diesen Massnahmen war eine realistische Crosstalk-Messung möglich.

#### 7.5 Kalibrieren des Verstärkers

#### 7.5.1 Prinzip der Signalmessung

Um die Messung des Übersprechens durchzuführen ist ein Verfahren zur Beurteilung der Signalamplituden nötig. Die einzige Möglichkeit bestand darin, festzustellen, ob ein Treffer aufgetreten ist. Indem man die Schwellen der Komparatoren durch verändern von VC-variiert und die Wahrscheinlichkeit für das Auftreten von Treffern beobachtet, liessen sich Aussagen über die Amplituden machen.

Diese Aussagen machen aber nur einen Sinn, wenn sie mit der äquivalenten Signalgrössen eines Detektors verglichen werden können. Dazu mussten Vorverstärker und Shaper genau kalibriert werden.

Abbildung 47: Signalweg des Calibrate-Signals

Abb. 47 zeigt den Weg des Calibrate-Signals. Generiert wird es durch eine fallende Flanke, die vom Bitmustergenerator erzeugt wird, die über die galvanische Trennung auf das Potentiometer gelangt. Mit diesem kann eine variables Signal  $V_{CAL}$  auf den CAL-Eingang des Chips gegeben werden. Über den Transistor und den Kondensator gelangt das Signal auf den Vorverstärker. Der Kondensator bestimmt die Ladungsmenge die bei einer gewissen Signalgrösse auf den Vorverstärker gelangt. Für die Anzahl der Elektronen gilt:

$$n_e = \frac{Q}{e} = \frac{CV_{CAL}}{e} \tag{13}$$

Die Kapazität wurde in [7] an einem Chip gemessen. Ihr Wert beträgt  $C=1.75 \mathrm{fF}$  mit einem Fehler von 5%. Dazu kommen noch die Toleranzen bei der Chipfertigung die laut DMILL Spezifikationen 10% betragen. Der Gesamtfehler für C beträgt dann 11%. Damit ergibt sich ein Wert von

$$(1090 \pm 120)e^{-}$$

pro 100mV. (14)

Dieser Wert dient als Basis für die Umrechnung von Volt in Anzahl Elektronen.

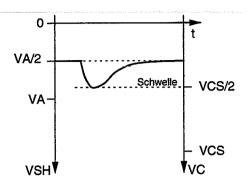

Abbildung 48: Beziehung zwischen VC- und Signalamplitude

Die Impulshöhe am Ausgang von  $V_{SH}$  lässt sich durch Verändern der Komparatorschwelle bestimmen. Der Arbeitspunkt des Shapers liegt etwa bei der halben Betriebsspannung VA-. Darauf liegt das Signal als negativer Impuls (siehe Abb. 48). Die Schaltschwelle des Komparators liegt bei der halben Betriesspannung VC-. Es ist nun sinnvoll folgende Spannung zu definieren.

$$V_{OUT} := \frac{V_{CS} - V_{CS0}}{2} \tag{15}$$

$V_{CS}$ :

$V_C$ -Wert bei dem der Komparator anspricht

$V_{CS0}$ :

$V_{CS}$ -Wert ohne Eingangssignal

Die Annahme ist, dass  $V_{OUT}$  bis auf eine additive Konstante  $V_{SH}$  entspricht. Die genaue Kenntnis von  $V_{SH}$  ist nicht wichtig, weil bei allen Messungen immer über das ganze System aus Verstärker und Shaper gemessen wird.

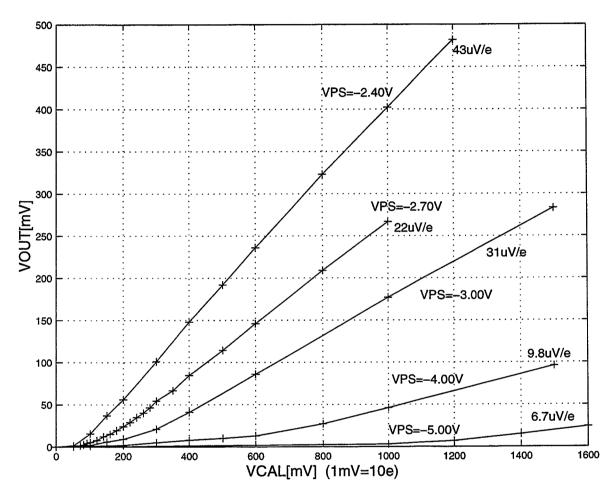

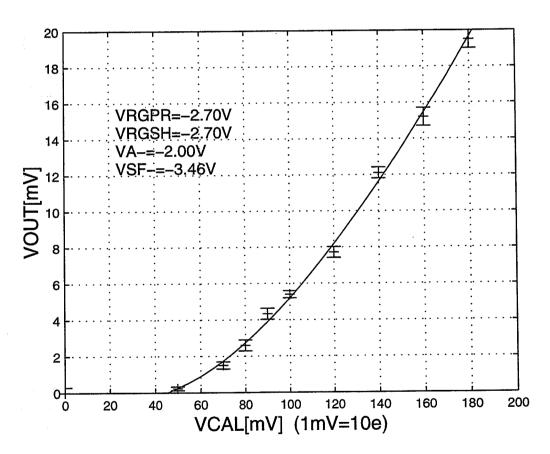

#### 7.5.2 Verstärkerkennlinien

Mit den im letzten Abschnitt beschriebenen Verfahren habe ich die Verstärkerkennlinien bestimmt. Abb. 49 zeigt die Resultate der Messung. Es ist  $V_{OUT}$  in Abhängigkeit von  $V_{CAL}$  für verschiedene Verstärkungseinstellungen aufgetragen. Die Verstärkung wurden durch verändern von VRGPR und VRGSH eingestellt. Die beiden Spannungen wurden dabei immer zueinander gleich gehalten. Aus den Steigungen der Kurven lässt sich die jeweilige Verstärkung ablesen.

Besondere Beachtung verdient die Abflachung im unteren Bereich der Messkurven. Dieser Teil ist für die Crosstalk-Messung besonders wichtig, da die Störsignale in diesem Bereich liegen. Es wurden drei Ursachen in Betracht gezogen:

Die Abflachung entsteht durch Rauschen. Das heisst, dass das Eingangssignal dort vom Rauschsignal überdeckt wird.

- Da der Komparator im unteren Bereich der Kurve bei der niedrigsten Spannung arbeitet ändert sich sein Verhalten.

- Es ist ein ballistischer Effekt. Das heisst, dass der Komparator eine gewisse Ladungsmenge braucht um überhaupt anzusprechen. Diese Ladung muss der Shaper innerhalb einer kurzen Zeit liefern.

Abbildung 49: Verstärkerkennlinien bei verschiedenen Regelspannungen. Die Spannung des Vorverstärkers und des Shapers wurden auf dem gleichen Wert VPS:=VRGPR=VRGSH gehalten.

Die Entscheidung für den ballistischen Effekt haben Simulationen des in Abb. 47 gezeigten Schaltungsteils gebracht. Abb. 50 zeigt die Situation genauer. Der Shaper lässt sich als Spannungsquelle mit einem Innenwiderstand beschreiben, der in einem Bereich um  $10k\Omega$  liegt. Der Komparator besitzt eine Eingangskapazität die während des Kippvorgangs durch den Miller-Effekt besonders gross wirkt und einen Wert um 1pF annimmt. Damit ein HIT-Signal erzeugt wird, muss die Schaltschwelle des zweiten Inverters bestehend aus

Abbildung 50: Zusammenwirken des Shapers und des Komparators

M16 und M23 erreicht werden. Sie liegt bei der halben Betriebsspannung (1V). Das Zeitintegral über den Impulsstrom am Shaper-Ausgang muss so gross sein, dass damit die Eingangskapazität des Komparators um 1V aufgeladen werden kann.

Betrachtet man z. B. ein Eingangssignal von  $V_{SH}=100\mathrm{mV}$  das während  $\Delta t=50\mathrm{ns}$  am Komparator anliegt, dann ergibt sich eine Spannungsänderung von

$$\Delta V_{COMP} = \frac{Q}{C_{COMP}} = \frac{U_{SH}\Delta t}{R_{SH}C_{COMP}} = 0.5V$$

(16)

Das wäre zu wenig um ein HIT-Signal zu produzieren.

#### 7.5.3 Frequenzverhalten

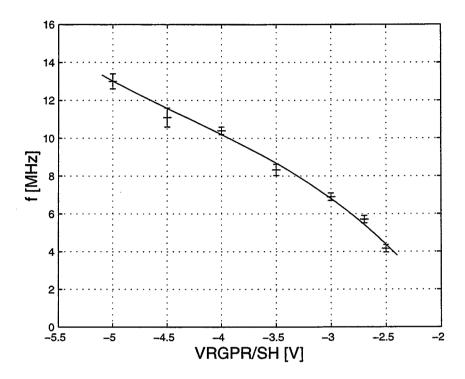

Das System aus Vorverstärker und Shaper besitzt ein bestimmtes Frequenzverhalten. Die maximale Verstärkung liegt bei einer Frequenz von einigen MHz. Diese Mittenfrequenz  $f_0$  ist von der Verstärkungseinstellung abhängig. Speist man in die Messschaltung in Abb. 47 anstatt der Signalflanke ein Sinussignal mit variabler Frequenz ein, lässt sich damit  $f_0$  ermitteln. Dazu wird die Komparatorschwelle bei ständig variierender Frequenz erhöht, bis der Komparator nur noch bei einer Frequenz anspricht. Damit ist  $f_0$  gefunden. Abb. 51 zeigt die Messresultate für verschiedene Verstärkungseinstellungen.

### 7.5.4 Wahl der Eichung für die Crosstalk-Messung

Aus den gewonnenen Erkenntnissen lässt sich die beste Wahl für die Verstärkungseinstellung für die Crosstalk-Messung bestimmen. Wegen der beschriebenen Krümmung in den Verstärkerkennlinien muss eine möglichst grosse Verstärkung gewählt werden. Die Verstärkung ist aber nach oben beschränkt. Ausserdem sinkt  $f_0$  schnell mit zunehmender Verstärkung. Die Wahl fiel auf die Einstellung

$$VRGPR = VRGSH = -2.7V.$$

Die Verstärkung beträgt bei dieser Einstellung  $22\mu\text{V/e}$  und  $f_0$  beträgt ca. 5.5MHz. Dieser Wert von  $f_0$  liegt eher an der unteren Grenze für realistische Bedingungen. Wählt man aber eine kleinere Verstärkung ist der Crosstalk nicht mehr zu sehen.

Abbildung 51:  $f_0$  in Abhängigkeit von der Verstärkung. Die Verstärkung nimmt von rechts nach links zu.

Abb. 52 zeigt die Verstärkerkennlinie für kleine Signale. Sie dient als Eichkurve für die Bestimmung der äquivalenten Eingangssignale bei der Crosstalk-Messung.

Abbildung 52: Eichkurve für die Crosstalk-Messung

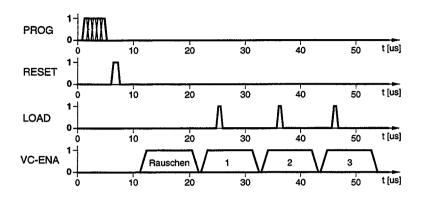

### 7.6 Crosstalk Messung

Abbildung 53: Zeitdiagramm für die Crosstalk-Messung

Für die Messung des Übersprechverhaltens habe ich den in Abb. 53 gezeigten Signalverlauf benutzt. Zuerst läuft der Programmiervorgang der Pixel nach Abschnitt 7.2 ab. Damit wird ein ausgewählter Pixel aktiviert. Das Calibrate-Signal wird durch anschliessendes Löschen des Schieberegisters von allen Pixeln ferngehalten. Danach löscht ein RESET-Signal die Hit-Flip-Flops in den Pixeln. Nach einer kurzen Pause wird dreimal hintereinander ein Suchsignal losgeschickt.

Um eine zeitliche Auflösung des Störverhaltens zu erreichen, wird durch das digitale Steuersignal VC\_ENA die Komparatorspannung VC- gesenkt und angehoben. Damit lässt sich die Komparatorschwelle zeitlich steuern. Dazu musste auf dem Elektronikboard eine kleine Zusatzschaltung eingebaut werden. Ist VC\_ENA aktiv, ist der Komparator "scharf". Bei passivem VC\_ENA wird VC- um 60mV gesenkt. Damit ist die Schwelle so hoch, dass der Komparator nicht mehr auf Störungen anspricht. Der ganze Zeitablauf wird periodisch wiederholt.

Es wurden vier Zeitfenster gewählt. Mit dem ersten wird nur der Rauschpegel gemessen. Die drei anderen sind während den drei Suchsignalen aktiv. Diese vier Fenster konnten einzeln gesetzt werden.

Abb. 54 zeigt oben VC- mit gesetztem Fenster 2. Unten befindet sich das Signal EN-CDOUT. Bei den Signalflanken läuft das Suchsignal durch die Doppelkolonne. Wenn kein Pixel einen Treffer registriert hat, fällt ENCDOUT sofort wieder in den High-Zustand zurück. Das ist in Abb. 54 nach der ersten Auslese der Fall, weil der Pixel dort nicht "scharf" ist. Hat jedoch der aktive Pixel durch eine Störung einen Treffer registriert, bleibt das Suchsignal dort stehen. ENCDOUT bleibt dann auf dem Low Pegel bis zum Start des nächsten Suchsignals. Das trifft zu etwa 50% bei der zweiten Auslese zu. Man beobachtet eine Überlagerung beider Fälle. Das bedeutet, dass der Pixel in 50% der Fälle vom Abfragesignal gestört wird. Die meisten Störungen werden aber erst bei der nächsten Auslese registriert, weil sie im zweiten Hit-Flip-Flop zwischengespeichert sind.

Für die Ermittlung der Störamplitude wurde durch messen von VC – VA der Wert von  $V_{OUT}$  bestimmt. Es wurde jeweils eine Messung mit dem Störsignal und eine nur mit

Abbildung 54: VC- (oben, 50mV/div) und /ENCDOUT (unten)

dem Rauschen durchgeführt. Der Wert für das Übersprechen  $V_{CN}$  berechnet sich aus der Differenz der beiden Messungen

$$V_{CN} = V_{OUT}^{ct} - V_{OUT}^{noise} \tag{17}$$

Es ergaben sich folgende Werte nach absteigenden Störungen geordnet:

- Störungen während der Programmierung

Dass sind die grössten Störungen. Sie bringen den Shaper zum Vollausschlag. Das

liegt natürlich auch daran, dass die Signale auf dem Elektronikboart nicht gefiltert

wurden. Die Störungen während der Programmierung sind aber nicht relevant, das

sie nicht während den Messungen auftreten.

- Störungen während der Auslese innerhalb derselben Doppelkolonne Hier lassen sich die Störungen in zwei Gruppen aufteilen:

- Eine Störung von Auslese 2 wird bei der Auslese 3 registriert (siehe Abb. 54).

Hier ergibt sich

$$V_{CN} = (2.0 \pm 0.5) \text{mV}$$

(CL = 68%)

Daraus erhält man aus der Eichkurve in Abb. 52 und aus (11) ein äquivalentes Eingangssignal von

$$630e^{-} \dots 820e^{-} \quad (CL = 95\%)$$

(18)

$$700e^{-} \dots 750e^{-}$$

(CL = 68%)

Dies ist das wichtigste Schlussergebnis der Crosstalk-Messung. Es stellt den grössten relevanten Beitrag dar.

Eine Störung von Auslese 2 wird bei der Auslese 2 registriert Hier ergibt sich ein Wert von

$$V_{CN} = (0.5 \pm 0.5) \text{mV}$$

(CL = 68%)

Für das äquivalente Eingangssignal erhält man eine obere Abschätzung von

$$< 620e^{-}$$

(CL = 95%)