## Controlling a large Data Acquisition System using an industrial SCADA system

Stefan Koestner (CERN) on behalf of the LHCb Online Group

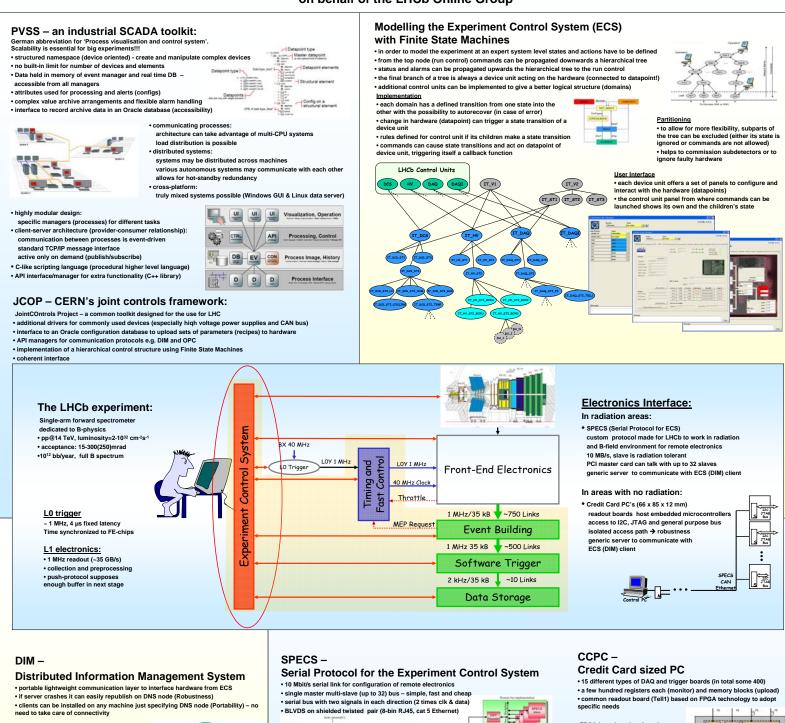

• DIM server running on CCPC or SPECS master PC publishes services to DIM Nam Server (DNS) from where the client (ECS) can subscribe to it. Data exchange peer to peer from server to client

Client sends commands (write/read) server updates services (data/status)

DNS

running DNS I

architecture comprises a number of managers which may run on independent may run on independent machines and communicate with the event manager via a PVSS internal protocol on top a DIM driver is implemented

which allows to communicate with hardware over ethernet

DE N RE N pc.psi DC 3 provides 16 long distance JTAG chains (4 signals each) provides 15 long distance I2C busses with selectable frequency

local i2C bus and 16 bit parallel bus (8 bit address range) DCC + POWER RECULATOR 32 configurable I/O lines

<u>SPECS slave</u> desig

SPECS multi-master board - 4 different busses standard 32-bit 33 MHz PCI board inserted on the same PC where SPECS server is running

1 ("daude,s "-dau ["dau ["dau ["dau ]"dau

I2C like protocol without acknowledge

slave can send interrupt and master repeats

clock only active during transfer (10 MHz) • variable number of words (<256) with 10 bits

SPECS mezzanine board houses the SPECS slave

DCU chip with 6 ADC channels (12 bit) and 1 temp senso

FPGA-based readout board • ADC conversion or optical conv. synchronisation, reordering, pedestal subtraction, common mode sub., zero suppression (PP) • MEP packing, IP framing (SL) Gigabit Ethernet Link

access to board via<u>gluecard</u> over a PLXPCI9030 bridge: •Parallel bus (8/16/32), 3 fast JTAG chains (2 MHz) to load firmware, 4 I2C lines and 9 GPIO lines

Separated ECS interface (CCPC) 4" - SM520PCX from Digitallogic atible microco i486 compatible (AMD ELAN 520) Linux Kernel at 133 MHz

ding from local bus 20 MB/s · filesystem shared over server

d as portable VERILOG code implemented in ACTEL APA150 FPGA (tested up to 40 krad) • SEU and SEL immune due to triple voting and one-hot state used