#### Universitatea POLITEHNICA București

Facultatea de Electronică, Telecomunicații și Tehnologia Informației

#### Teză de doctorat

# Aplicații de timp real ale rețelelor Ethernet în experimentul ATLAS

# Ethernet Networks for Real-Time Use in the ATLAS Experiment

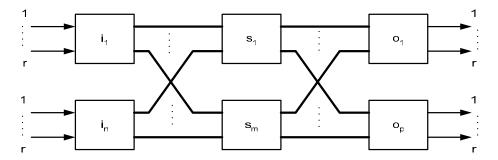

Doctorand: Conducător științific: ing. Cătălin Meiroșu prof. dr. ing. Vasile Buzuloiu

#### Acknowledgments

First, I would like to thank my three supervisors for the opportunity to pursue the work that lead to this thesis. Professor Vasile Buzuloiu sent me to CERN and suggested I might want to consider a PhD. He then supported and encouraged me through sometimes difficult moments. The late Bob Dobinson initiated and energetically steered most of the work presented here. His enthusiasm was contagious; his desire to always push the limits further was a permanent lightpath for me. Brian Martin's sharp critical sense and outspoken manners helped me focus on the right direction. He also carried the bulk of the proof-reading work and guided me to constantly improve the manuscript.

The work presented here was funded in part by two EU projects: SWIFT (ESPRIT EP28742) and ESTA (IST-33281-2001).

I am grateful to the members of the ATLAS Trigger DAQ community at CERN and abroad for their support and useful interactions during the time interval covered by this thesis, with special mentions for Micheal LeVine, Krzysztof Korcyl and Richard Hughes-Jones. I would like to thank the TDAQ management team for the continuous support.

I appreciate the contributions of my colleagues, current and former members of Bob's group throughout the years (in no particular order): Stefan Haas, Frank Saka, Emil Knezo, Stefan Stancu, Matei Ciobotaru, Mihail Ivanovici, Razvan Beuran, David Reeve, Alexis Lestra, Piotr Golonka, Miron Brezuleanu and Jamie Lokier.

The long-distance experiments described in this work would have been impossible without the cooperation of many people. Wade Hong, Andreas Hirstius, professor Kei Hiraki and professor Cees de Laat were instrumental in setting up and running the experiments. The international circuits were gracefully offered by the following national research network operators: SURFnet, CANARIE, WIDE, PNW. The switching equipment was loaned by Force10 Networks and Foundry Networks. Ixia provided test equipment and special support.

Last, but not least, I would like to thank my family (with a particular "thank you, sister") for their uninterrupted support and understanding. And to my friends, for putting up with my terrible working hours and still continuing to support me.

#### **Abstract**

Ethernet became today's de-facto standard technology for local area networks. Defined by the IEEE 802.3 and 802.1 working groups, the Ethernet standards cover technologies deployed at the first two layers of the OSI protocol stack. The architecture of modern Ethernet networks is based on switches. The switches are devices usually built using a store-and-forward concept. At the highest level, they can be seen as a collection of queues and mathematically modelled by means of queuing theory. However, the traffic profiles on modern Ethernet networks are rather different from those assumed in classical queuing theory. The standard recommendations for evaluating the performance of network devices define the values that should be measured but do not specify a way of reconciling these values with the internal architecture of the switches. The introduction of the 10 Gigabit Ethernet standard provided a direct gateway from the LAN to the WAN by the means of the WAN PHY. Certain aspects related to the actual use of WAN PHY technology were vaguely defined by the standard.

The ATLAS experiment at CERN is scheduled to start operation at CERN in 2007. The communication infrastructure of the Trigger and Data Acquisition System will be built using Ethernet networks. The real-time operational needs impose a requirement for predictable performance on the network part. In view of the diversity of the architectures of Ethernet devices, testing and modelling is required in order to make sure the full system will operate predictably. This thesis focuses on the testing part of the problem and addresses issues in determining the performance for both LAN and WAN connections. The problem of reconciling results from measurements to architectural details of the switches will also be tackled.

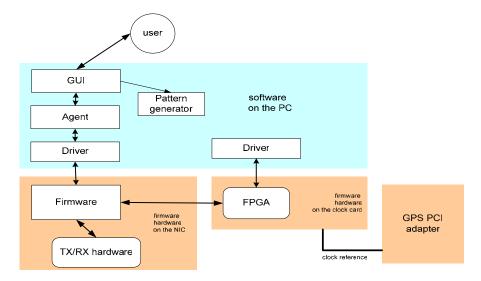

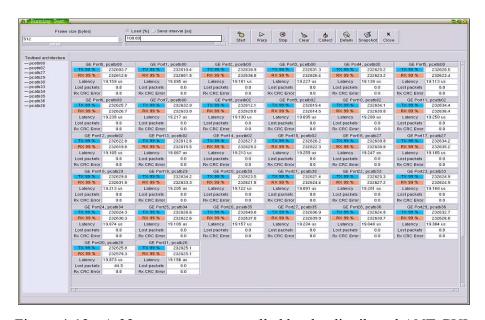

We developed a scalable traffic generator system based on commercial-off-the-shelf Gigabit Ethernet network interface cards. The generator was able to transmit traffic at the nominal Gigabit Ethernet line rate for all frame sizes specified in the Ethernet standard. The calculation of latency was performed with accuracy in the range of +/- 200 ns. We indicate how certain features of switch architectures may be identified through accurate throughput and latency values measured for specific traffic distributions. At this stage, we present a detailed analysis of Ethernet broadcast support in modern switches.

We use a similar hands-on approach to address the problem of extending Ethernet networks over long distances. Based on the 1 Gbit/s traffic generator used in the LAN, we develop a methodology to characterise point-to-point connections over long distance networks. At higher speeds, a combination of commercial traffic generators and high-end servers is employed to determine the performance of the connection. We demonstrate that the new 10 Gigabit Ethernet technology can interoperate with the installed base of SONET/SDH equipment through a series of experiments on point-to-point circuits deployed over long-distance network infrastructure in a multi-operator domain. In this process, we provide a holistic view of the end-to-end performance of 10 Gigabit Ethernet WAN PHY connections through a sequence of measurements starting at the physical transmission layer and continuing up to the transport layer of the OSI protocol stack.

### **Contents**

| 4.2.3. The Graphical User Interface                           | 54  |

|---------------------------------------------------------------|-----|

| 4.3. Results from the initial ANT                             |     |

| 4.4. The distributed version of the ANT                       | 59  |

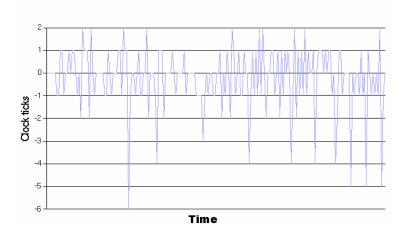

| 4.4.1. Clock synchronisation for the distributed ANT          | 61  |

| 4.4.2. The performance of the IP-enabled firmware             | 62  |

| 4.4.3. The IPv6 traffic generator                             | 64  |

| 4.5. Conclusion                                               | 64  |

| 5. Results from switch characterisation                       | 65  |

| 5.1. Methodology                                              | 65  |

| 5.1.1. Unicast traffic                                        |     |

| 5.1.2. Broadcast traffic                                      | 68  |

| 5.2. Results from measurements using Ethernet unicast traffic | 69  |

| 5.2.1. Intra-line card constant bitrate traffic               |     |

| 5.2.2. Inter-line card constant bitrate traffic               | 74  |

| 5.2.2.1. A simple inter-line card traffic pattern             | 74  |

| 5.2.2.2. A "pathological" traffic pattern                     | 78  |

| 5.2.3. Fully-meshed random traffic                            | 82  |

| 5.2.4. Results on a multi-stage architecture                  |     |

| 5.2.5. Summary                                                |     |

| 5.3. Broadcast traffic                                        |     |

| 5.3.1. Intra-line card broadcast traffic                      |     |

| 5.3.1.1. One broadcast source                                 |     |

| 5.3.1.2. Four broadcast sources                               |     |

| 5.3.2. Inter-line card broadcast traffic                      |     |

| 5.3.2.1. Four traffic sources                                 |     |

| 5.3.2.2. Eight traffic sources                                |     |

| 5.3.2.3. Maximum broadcast configuration – 32 sources         |     |

| 5.3.3. Summary                                                |     |

| 5.4. Conclusion                                               |     |

| 6. 10 GE WAN PHY Long-Haul Experiments                        | 103 |

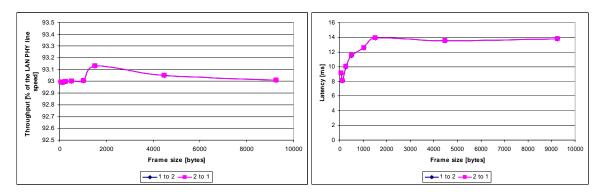

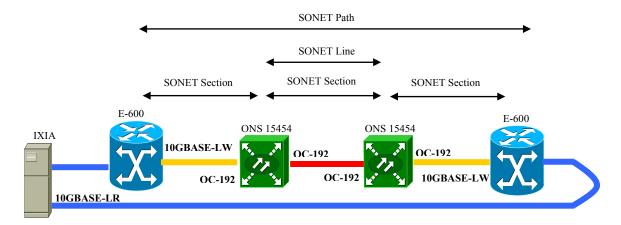

| 6.1. Proof of concept in the laboratory                       |     |

| 6.2. Experiments on real networks                             |     |

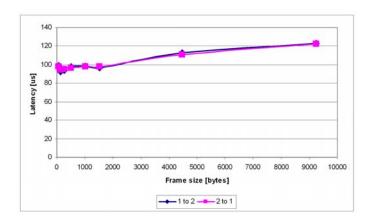

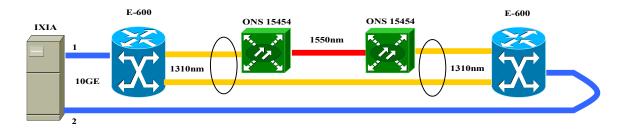

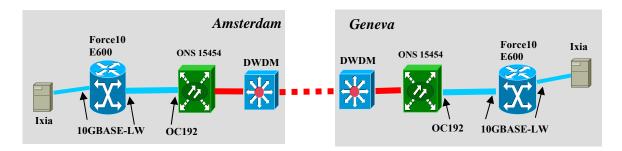

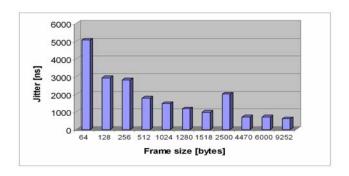

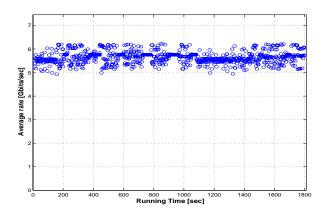

| 6.2.1. Geneva – Amsterdam                                     |     |

| 6.2.2. Geneva-Ottawa                                          |     |

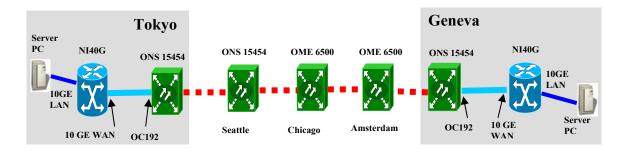

| 6.2.3. Geneva-Tokyo                                           |     |

| 6.2.3.1. Single-stream TCP tests                              |     |

| 6.2.3.2. Combined TCP and UDP tests                           |     |

| 6.3. Conclusion                                               |     |

| 7. Conclusions                                                | 119 |

| 7.1. Outline                                                  |     |

| 7.2. Recommendations for the ATLAS TDAQ system                |     |

| 7.3. Original contributions                                   |     |

| 7.4. Future work                                              | 126 |

| 8 References                                                  | 129 |

## 1. The Use of Ethernet in the Trigger and Data Acquisition System of the ATLAS Experiment

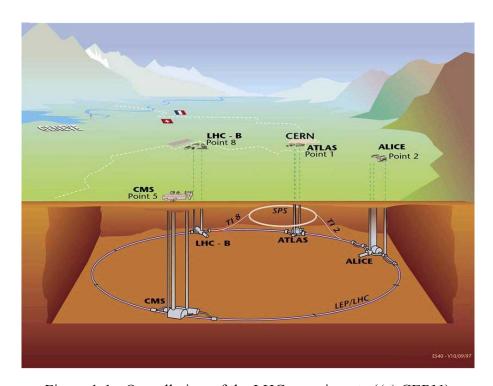

An ancient tradition in the field of physics calls for obtaining an experimental proof for any theoretical exploits. Experiments are also a way of always raising questions that sometime provide answers that in turn spawn new theories. The Large Hadron Collider (LHC), to start operation in 2007 at CERN in Geneva, will be the biggest experimental physics machine built to date. The LHC is a particle accelerator based on a ring with a circumference of 27 km (Figure 1-1).

Figure 1-1 - Overall view of the LHC experiments {(c) CERN}

Five experiments will take place at the LHC: ATLAS (A Thoroidal LHC Apparatus), CMS (The Compact Muon Solenoid), ALICE (A Large Ion Collider Experiment), LHCb, TOTEM (Total Cross Section, Elastic Scattering and Diffraction Dissociation at the LHC). Two beams of protons, travelling in opposite directions, are accelerated to high energies on the LHC ring. At particular locations along the ring, the beams are bent using magnets and brought to head-on collision inside particle detectors. Each one of the first four experiments is developing its own particle detector, optimized for the particular physics that constitute the mission of the experiment.

The ATLAS experiment was setup to explore the physics of proton-proton collisions at energies around 14 TeV [tdr-03]. The major goals are the discovery of a family of particles (known as the Higgs bosons, named after the physicist that first predicted its

existence) that would explain the breaking of the electroweak symmetry and to search for new physics beyond the Standard Model.

The beams at the LHC are not continuous – instead, they are formed by bunches of particles, succeeding each other at a distance of about 7 m (or 25 nanoseconds). The bunch-to-bunch collision (also known as bunch crossing) rate is hence 40 MHz. Every bunch crossing is expected to generate 23 inelastic particle collisions, producing a luminosity equal to  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> in the detector [tdr-03].

#### 1.1. The ATLAS detector

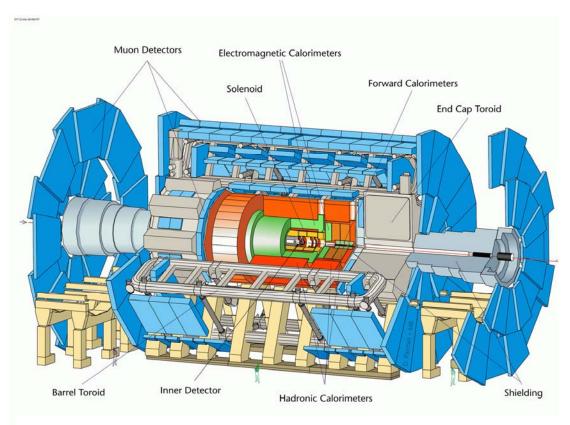

The ATLAS detector (Figure 1-2) is composed of three major detection systems: the Inner Detector, the Calorimeters and the Muon Spectrometer.

Figure 1-2 - Architectural view of the ATLAS detector {© CERN}

The Inner Detector measures the paths of electrically charged particles [inn-98]. It is composed of three parts: Pixels, Silicon Tracker (SCT) and Transition Radiation Tracker (TRT). The Pixel sub-detector is built using semiconductor devices that provide a position accuracy of 0.01 mm. The SCT is built from silicon microstrip detectors. The TRT is a tracking detector built using gas-filled straw tubes. Charged particles traversing the tube would induce electrical pulses that are recorded by the detector.

The calorimeter measures the energy of charged or neutral particles. A traversing particle interacts with the calorimeter, leaving a trace known as "shower". The shower is observed by the sensing elements of the detector. The Liquid Argon (LAr) calorimeter [lar-96] is composed out of four separate calorimeters: the barrel electromagnetic, the endcap electromagnetic, the endcap hadron, and the forward calorimeter. The sensing element is argon in liquid state – the showers in argon liberate electrons that are later recorded. The barrel calorimeter and two extended barrel hadronic calorimeters form the Tile calorimeter [tile-96]. The sensing elements of the Tile calorimeter are scintillating optical fibres – the showers reaching a fibre would produce photons that are later recorded.

The Muon Spectrometer [muon-97] detects muons, heavy particles that cannot be stopped by the calorimeters. It is composed of gas-filled tubes placed in a high magnetic field that bends the trajectory of the muons.

The total data collected by detectors at each bunch crossing is estimated to be around 1.5 MB [tdr-03]. This data is referred to as an "event" throughout this document. As events take place at a rate of 40 MHz, the overall quantity of data produced amounts to some 60 TB/s. However, only part of this data is interesting from the physics point of view. Therefore, the task of the ATLAS Trigger system is to select only the most interesting data, finally reducing the rate to O(100) Hz to be sent to permanent storage. The Data Acquisition system channels the data from the detector, through the trigger system, all the way to the input of the permanent storage. Even if it is expected that the ATLAS experiment will operate at lower luminosities in the first years [tdr-03], the Trigger and Data Acquisition system (TDAQ) will channel about the same quantity of data to the permanent storage [compm-05].

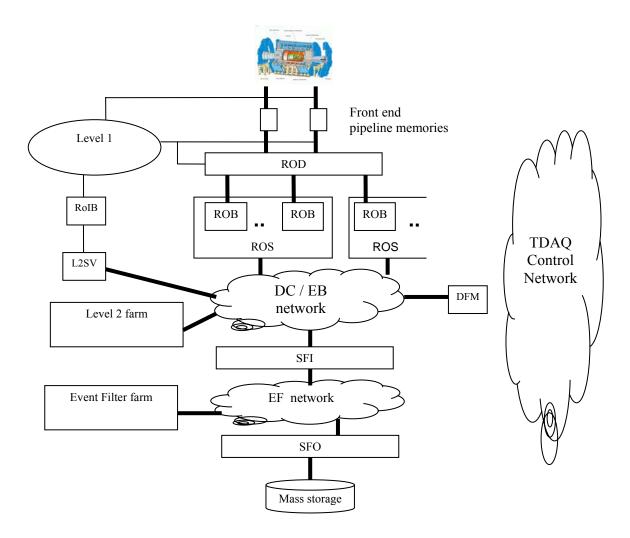

#### 1.2. The overall architecture of the TDAQ

The generic architecture of the TDAQ system is presented in Figure 1-3. The data acquired by the detectors is temporarily stored in pipelined memories directly connected to the respective detectors. The operation of the pipeline is synchronous to the event rate in the detector. The Level 1 filtering system will analyse fragments of the data, in real time, and select the most interesting events while reducing the data rate to 100 kHz. The TDAQ system is made of two main logical components: the DataFlow and the High-Level Trigger (HLT) system.

Figure 1-3 - Overall architecture of the ATLAS TDAQ system

The DataFlow has the task of receiving data accepted by Level 1, serving part of it to the HLT and transporting the selected data to the mass storage. The HLT is responsible for reducing the data rate (post-Level 1) by a factor of O(1000) and for classifying the events sent to mass storage. Both the DataFlow and HLT systems will have an infrastructure based on large Ethernet networks while the computing power will be provided by server-grade PCs.

The operation of the entire TDAQ system is made under the supervision of the ATLAS Online software. The Online software is responsible for all operational and control aspects during data taking or special calibration and test runs. A separate network (the TDAQ Control network) will carry the traffic generated by the Online software.

The data selected by Level 1 is passed from the Read Out Drivers (RODs) to the Read Out Buffers (ROBs), via 1600 optical fibres using S-LINK technology [slink]. Multiple ROBs are housed in the same chassis, known as a Read Out System (ROS). The Read

Out System is directly connected to the Data Collection (DC) and Event Building (EB) network, together with the Level 2 (LVL2) processing farm (about 600 computers), the LVL2 supervisors (L2SV - about 10 computers), the Data Flow Manager (DFM), and the Sub-Farm Inputs (SFIs - about 50 computers). The flow of data in the DC and EB networks will be described in more detail later.

The Event Filter (EF) farm will regroup a number of about 1600 computers. The Sub-Farm Outputs (SFOs - about 10 computers) will assure that the selected events are successfully sent to the mass storage facility. The Event Filter network (EF) interconnects the SFIs, the Event Filter farm and the SFOs. The flow of data in the EF network will be described in more detail later.

#### 1.2.1. The DataFlow system

The boundary between the detector readout and the data acquisition system was established at the ROBs. The Level 1 filter defines a Region of Interest (RoI) in the selected events and the set of event fragments that belong to this region is passed to the L2SV through the Region of Interest Builder (RoIB).

For each event selected by Level 1, requested fragments, part of the RoI, are sent on request by the ROBs to a computer in the Level 2 processing farm. The supervisor informs the DFM, who will start of the event building process by assigning an SFI to collect all the fragments of an accepted event. The fragments of the rejected events are deleted from the ROBs as result of a command issued the DFM.

The SFI serves the complete events to computers in the EF. The events accepted by the EF are transmitted to the SFO, while the events rejected by the EF are deleted by the SFI. The SFO is the last component of the ATLAS Online analysis system. The events sent to permanent storage are later retrieved, processed and analysed worldwide by the members of the ATLAS collaboration. This step is referred to as "Offline analysis" and is detailed in the ATLAS computing model document [compm-05].

The ATLAS Online analysis system operates in synch with the detector. Different parts of the system must operate with real-time constraints. The amount of time available for data transfer and analysis increases as the events approach the SFO. The ATLAS Offline analysis system has no real-time operation requirements. Its challenge will be to distribute the massive amount of data accumulated (about 26 TB/day) to the ATLAS collaboration institutes for detailed analysis.

#### 1.2.2. The High Level Trigger system

The HLT system has two components: the LVL2 and the EF. Due to the high data rate to be handled at LVL2 (100 kHz of events x 1.5 MB/event = 150 GB/s), a trade-off position was adopted whereby this stage will base its decision on a relatively simple analysis

performed on a small part of the available data. The EF will run a throughout analysis, on the entire data of one event.

The RoIB is informed by Level 1 which areas of the detector are expected to have observed interesting results. These areas are included in a list of RoI associated to each event. The RoIB sends the list to the L2SV. The L2SV allocates one node in the processing farm to analyse the data, according to the RoI list. The LVL2 processor may process several events at the same time. The analysis is carried in sequential steps, processing one RoI from the list at a time. The processor may decide to reject an event at any step of the processing. The time available for processing at LVL2 is about 10ms [tdr-03]. The decision taken as result of the processing is sent back to the L2SV.

The EF receives complete events, built by the SFI. The data rate at the entrance of the EF is about O(100) lower than in the LVL2, hence more time can be allocated to analysis while still using a reasonable amount of computers. The assumption is that a processor will spend about 1 second processing each event [tdr-03]. The EF will apply sophisticated reconstruction and triggering algorithms, adapted from the software framework for offline analysis.

#### 1.3. The TDAQ interconnection infrastructure

The input data is channelled into the TDAQ system through 1600 optical fibres using the SLink transmission protocol, a standard throughout the ATLAS experiment. The interconnections inside the TDAQ system, including the TDAQ control network, will be realized over networks built on Ethernet technology.

With respect to the choice of Ethernet technology, the TDAQ TDR contains the following statement [tdr-03]: "Experience has shown that custom electronics is more difficult and expensive to maintain in the long term than comparable commercial products. The use of commercial computing and network equipment, and the adoption of commercial protocol standards such as Ethernet, wherever appropriate and possible, is a requirement which will help us to maintain the system for the full lifetime of the experiment. The adoption of widely-supported commercial standards and equipment at the outset will also enable us to benefit from future improvements in technology by rendering equipment replacement and upgrade relatively transparent. An additional benefit of such an approach is the highly-competitive commercial market which offers high performance at low cost."

Table 2-1 summarizes the bandwidth requirements for the data path of the TDAQ system.

| Function         | Input requirements                                            | Output requirements                                                                                   |

|------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Detector readout | ~1600 event fragments of size<br>typically 1 kbyte at 100 kHz | Few per cent of input event<br>fragments to LVL2 at 100 kHz;<br>~1600 event fragments at ~3 kHz to EB |

| LVL2             | Few per cent of event fragments at<br>100 kHz                 | 100 kHz decision rate (~3 kHz accept<br>rate)                                                         |

| EB               | $\sim$ 1600 event fragments at $\sim$ 3 kHz                   | ~3 kHz and ~4.5 Gbyte/s                                                                               |

| EF               | ${\sim}3\mathrm{kHz}$ and ${\sim}4.5\mathrm{Gbyte/s}$         | $\sim\!\!200$ Hz and $\sim\!\!300$ Mbyte/s                                                            |

Table 1-1- Required performance for 100 kHz Level 1 accept rate [tdr-03]

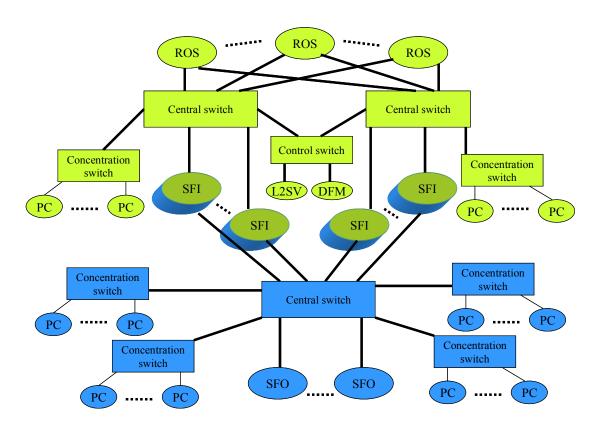

It is clear that Ethernet technology, at the stage it is today (see chapter 2 for an introduction) can fulfil the raw bandwidth requirements. The architectures envisaged for the DC/EB and EF networks are presented in Figure 1-4. A detailed view on the architectural choices is presented in [sta-05].

Figure 1-4 - The generic architecture of the DC, EB and EF networks

The requirements, in terms of latency and bandwidth guarantees, are very different between then DC/EB and EF networks. The DC/EB network, due to the fact that the

transfer protocol is based on the UDP/IP protocol (that means there are no automatic retransmissions of lost messages), requires a configuration that minimizes the packet loss and the transit time. The traffic in the DC/EB network is inherently bursty, due to the request-response nature of the communication between the LVL2 processors and ROSes and SFIs and ROSes. The traffic in the EF network is based on TCP/IP, hence benefits from automatic retransmission of the lost messages at the expense of additional traffic on the network. Considerations related to the overall cost of the system discard the use of a massively over provisioned network as a solution to minimise the packet loss.

#### 1.4. The option for remote processing

The TDAQ TDR specifies that the full luminosity of will only be reached after a couple of years from the start of the experiment. The full size deployment of the TDAQ system is expected to follow the increase of luminosity [tdr-03]. In addition to a potentially reduced-scale TDAQ system at the start of the experiments, the true requirements for the detector calibration and data monitoring traffic are largely unknown even today. The numbers included in this respect in the TDR are only indicative and were taken into account as such when dimensioning the different TDAQ data networks.

A certain amount of computing power could be made available at institutes collaborating in the ATLAS experiment. If the applications running over the TDAQ network would efficiently support data transmission over long-distances, this computing power could be made available in particular for calibration and monitoring tasks. The applications running over the DC/EB networks would not allow such an option due to the transit time constraints over the LVL2 filter. However, the processing time allocated to applications running over the EF network would allow for such deployment model. A significant part of the calibration data is expected to be handled at the EF, so this would be the natural place where remote computing capacities may intervene in real time. The options for remote processing in real time are detailed in [mei-05a]

#### 1.5. The need for evaluation and testing

The configuration of the TDAQ data networks has been optimized for the particular traffic pattern they are expected to carry. This is very different from the traffic in a generic network, mainly due to the high frequency request-response nature of the data processing in the TDAQ. Due to the complexity of the network and the operational constraints, it was necessary to develop a model of the entire network, together with the devices attached to it. Korcyl et al. developed a parametric switch model described in [kor-00]. The data for the parameterisation had to be obtained from real switches in order to make the predictions of the model relevant to the TDAQ system.

The Ethernet standards only define the functionality that has to be offered by the compliant devices, but not the ways to implement it. Often, even if the point to point connection supports the transfer rate of the full-duplex connection, the switching fabric

might only support part of the aggregated capacity. These concerns will be discussed in further detail in Chapter 3. More important, Ethernet is by definition a best-effort transfer protocol. It offers no guarantees with respect to the amount of bandwidth that can be used by one application on shared connections. The eight classes of services are only defined by the standard, leaving each manufacturer to choose a specific solution for how to handle prioritised traffic.

There was a clear need to qualify the devices that will be part of the network with respect to the requirements of the TDAQ prior to the purchase. This need was already expressed by Dobson [dob-99] and Saka [sak-01]. It was also important to evaluate whether these requirements are realistic in terms of what the market can actually provide. The performance reports made available by some of the manufacturers or independent test laboratories only detail a part of the capabilities of the device, usually a subset of the tests prescribed by RFC 2544 [rfc-2544]. In addition, the members of the TDAQ team know better than anyone else the particular traffic pattern that has to be supported by the network. Therefore, in the best tradition of the experimental physicists, the TDAQ decided to run the evaluation of network devices at their own premises, using equipment that was developed in house.

Developing the own TDAQ equipment for traffic generation was a logical step, in view of the costs of commercial equipment and combined expertise of the group members. More details on the advantages of this approach will be given in Chapter 4. In addition to the development of the test equipment, the design of an entire evaluation framework for local and wide area networks was required in order to provide a system-wide view and eventually integrate the results on a model covering the operation of the entire TDAQ data path.

The problems raised by the long-distance connections were somehow different. At first, a demonstration that a certain technology would actually work at all in a novel scenario was required. Then, transfers over long-distance networks that were relevant to the TDAQ environment concerned a set of point-to-point connections, deployed in a star technology centred at CERN. Multiple technologies may be used for building these connections, depending on the particular services offered by the carrier and the financial abilities of the company or research institute using the connection. Could Ethernet, the technology of choice for building the local TDAQ system, be used for the long-distance data transfers? What problems would appear in this scenario?

#### 1.6. Conclusion

The ATLAS experiment at CERN is building a Trigger and Data Acquisition system based on commodity-of-the-shelf components. Real-time operation constraints apply to parts of the TDAQ. The amount of data has to be reduced from about 150 GB/s at the entry of the system to about 300 MB/s to be sent to the permanent storage. Ethernet networks will be used to interconnect the different components of the system. Several thousands of connections will thus have to be integrated in the system. Chapter 2 will introduce Ethernet, the technology of choice for the TDAQ networks.

#### 2. The State of Networking: Ethernet Everywhere

Computer networks were invented in the 1960s as a way of accessing, from a low cost terminal, expensive mainframes located at distance. As data began to accumulate, the network naturally provided access to remote storage. The invention and evolution of the Internet transformed our information world into a web of interconnected computer networks. The networking paradigm remained practically unchanged throughout the last 40 years: a network allows a computer to access external resources and eventually share its own capabilities.

A Local Area Network (LAN) enables data exchanges between computers located in the same building. It requires a technology that provides high transmission speed while allowing for low installation and management overheads. Today, Ethernet is the de-facto standard for LAN connectivity. Ethernet owes its success to the cost effectiveness and continuous evolution while maintaining compatibility with the previous versions. This chapter will describe the evolution of Ethernet from 10 Mbps in the 1980s to 10 Gbit/s today. Even more than the increase in raw speed, it is the evolution in what the technology provides at the logical level that makes Ethernet ready for being used in one of the most demanding production environments: the Trigger and Data Acquisition System of the ATLAS experiment at CERN.

The old telephony system provided the basis of communications between computers from within a city to transcontinental scale. Referred as Metropolitan Area Networks (MAN) at city-scale or Wide Area Networks (WAN) at country to intercontinental scales, these networks were developed on top of an infrastructure designed for carrying phone calls. Reliability and service guarantees are traditionally the main issues to be addressed in the MAN and WAN. The technology that currently dominates the WAN is known as the Synchronous Optical Network (SONET) in America and the Synchronous Digital Hierarchy (SDH) in Europe and Japan. This chapter includes a brief introduction to SONET/SDH and explains how the 10 Gigabit Ethernet standard defines a novel way for interconnecting the LAN and the WAN.

#### 2.1. The evolution of Ethernet: 1974 - 2004

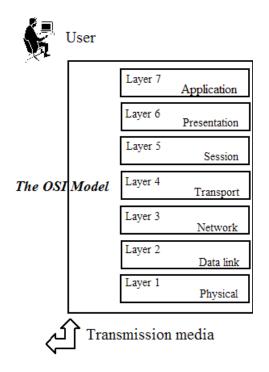

The International Standards Organisation defined a model for interconnecting computing systems, known as the Open System Interconnect (OSI) model [osi-94]. The OSI model divides the space between the user interface and the transmission medium into seven vertical layers. The data is passed between layers top-down and bottom-up in such way that a layer communicates directly only with the layer above. The OSI model is presented in Figure 2-1.

Figure 2-1 - The seven layers of the OSI model

The physical layer interfaces directly the computer to the transmission medium. It converts the bit stream received from the upper layer into signals adapted to an efficient transmission over the physical medium. The data link layer provides a managed virtual communication channel. It defines the way the transmission medium is accessed by the connected devices, detects and possibly corrects errors introduced by the lower layer and handles the control messages and protocol conversions.

#### 2.1.1. The foundation of Ethernet

Ethernet is a technology that spans the first two layers of the OSI model: the physical layer and the data link layer. The part situated at the data link layer remained quasi-unchanged during the entire evolution of Ethernet.

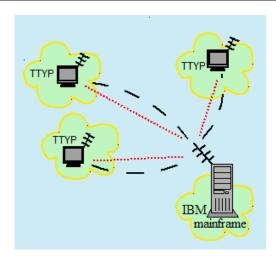

The history of Ethernet started in the Hawaii islands. At the beginning of the 1970s, Norman Abramson from the University of Hawaii developed the Aloha protocol [abr-70] to allow an IBM mainframe situated in a central location to communicate with terminals located on different islands (Figure 2-2). The wireless network allowed a source to transmit at any time on a shared communication channel.

Figure 2-2 - The Aloha network

The data rate was 9600 bauds and fixed-size frames were transmitted as a serial stream of bits. The mainframe would send an acknowledgment packet over a separate channel to the source of a successfully received packet. The terminal would time out if it did not receive an acknowledgement from the mainframe in a fixed time interval. Upon timeout, the terminal waited a random time and then tried to retransmit the packet. When two terminals would transmit at the same time, the data arriving at the mainframe would be corrupted due to physical interferences on the transmission channel. This event was referred to as a "collision" and resulted in both packets being lost. The two terminals would not receive acknowledgements from the mainframe in case a collision happened. A timeout mechanism triggered the retransmission of the unacknowledged packets. The Aloha protocol was quite inefficient [tan-96], due to the collisions and timeout mechanism: only 18% of the available bandwidth could be used.

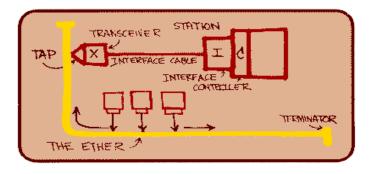

Robert Metcalfe from the Xerox research laboratory in Palo Alto developed an improved version of the Aloha network (Figure 2-3) to interconnect the minicomputers in its laboratory [met-76]. Metcalfe named his protocol "Ethernet": ether was the ubiquitous transmission medium for light, hypothesized at the end of the 19th century.

Figure 2-3 - The concept of Ethernet – an original drawing by Bob Metcalfe [met-76]

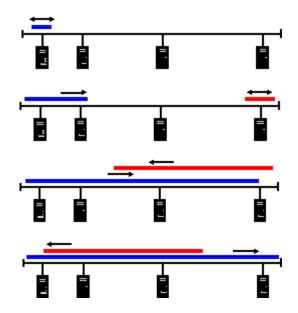

Ethernet introduced a new transmission medium: a thick yellow coaxial copper. Yet, the approach was similar to AlohaNet: the coaxial cable was a shared medium. The control channel that propagated the messages from the mainframe to the terminals in AlohaNet does not exist in Ethernet. To improve the use of the bandwidth available on the transmission medium, Metcalfe invented the Carrier Sense Multiple Access with Collision Detection (CSMA-CD) protocol [tan-96]. The CSMA/CD protocol had to take into account the variable size of the Ethernet frames. The operation of CSMA/CD is presented in Figure 2-4.

Figure 2-4 – Operation of the CSMA-CD protocol

The CSMA/CD protocol specifies that a node has to listen on the shared medium before, during and after transmitting a frame. It can only transmit if the transmission medium is available. However, due to the finite propagation time on the transmission medium, two nodes can consider the medium to be available and start transmitting at about the same time. This results in a collision. The time interval when a collision may happen is referred to as a collision window. The nodes will detect the collision and stop transmitting immediately, thus making the channel available for the other nodes. As in Aloha, the node that detected a collision while transmitting had to wait a random time interval before retransmitting the frame.

The maximum collision window extends over the double of the propagation time between the two ends of the network. The time to transmit the smallest frame has to be the same as the collision window in order for the collision detection mechanism to work. It is hence obvious that a small collision window combined with large frames transmitted when the medium has been seized would translate into maximum efficiency for the use of the transmission medium. However, for practical reasons, the minimum and maximum frame sizes are defined in the Ethernet standard, practically determining the span of the

network and the theoretical efficiency of the transmission. An in-depth study of the Ethernet efficiency through measurements on real networks can be found in [bog-88].

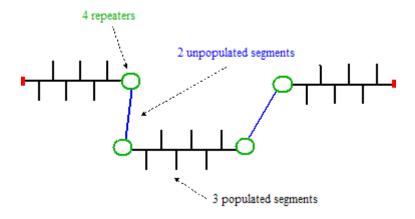

The first Ethernet standard was adopted by IEEE in 1985 [eth-85], five years after an industry alliance composed of Digital, Intel and Xerox issued an open specification for the protocol and transmission method [spu-00]. The minimum frame size was 64 bytes while the maximum frame length was set to 1518 bytes. The transmission speed was 10 Mbps. The official denomination was 10BASE5 (10 Mbps data rate, base band transmission, network segments having a maximum length of 500 meters). The medium was used for bidirectional transmission on the same channel, hence creating a half duplex network. It is well known that signals are attenuated and degraded by interferences while propagating on the transmission medium. Devices called repeaters were introduced in order to clean and amplify the signal, thus increasing the span of the network. Figure 2-5 presents the result of the rules that directed the design of the first Ethernet networks.

Figure 2-5 - Illustration of the 5-4-3-2-1 Ethernet rule

The design of the first Ethernet networks was governed by five simple principles, known as the "5-4-3-2-1":

- 5 segments, each segment spanning maximum 500 meters

- 4 repeaters to interconnect the segments

- 3 segments populated with nodes for a maximum of 100 nodes per segment

- 2 segments cannot be populated with nodes

- all the above form 1 collision domain or logical segment

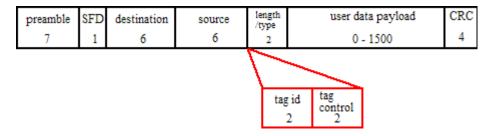

The first IEEE Ethernet standard [eth-85] defined the structure of the frame as presented in Figure 2-6.

| preamble | SFD | destination | source | length<br>/type | user data payload | CRC |

|----------|-----|-------------|--------|-----------------|-------------------|-----|

| 7        | 1   | 6           | 6      | 2               | 0 - 1500          | 4   |

Figure 2-6 - The structure of the 802.3-1985 Ethernet frame

The special pattern of the preamble bits allowed the receiver to lock onto the incoming serial bit stream. The Start of Frame Delimiter (SFD) signalled the imminent arrival of the frame. The source address was a number that uniquely identified a device connected to the Ethernet network. The IEEE allocated a particular address range to each manufacturer of Ethernet devices [oui]. The destination address may be the address of another Ethernet device or a special address that designated multicast or broadcast traffic (see below). The *length / type* field could be used to indicate the amount of data in the payload (if the value is less than 1500). When its value was bigger than 1500, this field identified the frame as either an Ethernet control frame or gave information on the higher layer protocol to be used when interpreting the payload. The payload contained the data passed by the higher layers in the OSI stack. This field may contain between 46 and 1500 bytes of data. When data was less than 46 bytes, zeroes were added to the data until the 46 bytes limit was reached. The length of the smallest transmitted frame was always 64 bytes, regardless of the amount of user data in the payload. The frame check sequence field contained a cyclic redundancy check (CRC) code that allowed the receiver to determine whether the content of the incoming frame was altered while in transit. The End of Frame Delimiter, in fact an idle period of 96 bit times, signals the end of the transmission and allows the cable to settle in a neutral electrical state.

Since all the members of the network are listening on the cable at the same time, Ethernet is effectively a protocol based on broadcast communications. To take advantage of the native support for broadcast in Ethernet, special addresses were allocated for broadcast traffic [eth-85]. A frame sent to the generic 0xFFFFFFFF address will be received and processed by all the devices connected to the network. A range of addresses (having the first bit equal to 1) were reserved for multicast, a special type of broadcast traffic where only some of the devices on the network are interested in and will process the received frames.

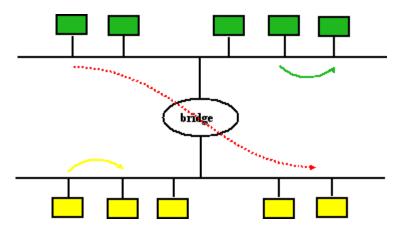

The number of connected devices increased as personal computers became more affordable for companies. The limitations imposed by an efficient CSMA-CD operation on the span of the network and number of connected devices turned out to be too important. The traffic over the network also increased with the number of devices. A phenomenon known as "network congestion" appeared when the throughput measured on the network was much lower than the theoretical numbers, due to the large number of devices to the network. The CSMA/CD protocol tried to control congestion through the exponentially random time a traffic source would have to wait before trying to retransmit in case of collision. However, higher layer transfer protocols (like TCP [rfc-793]) included their own congestion control mechanisms, further limiting the achieved transfer rate on Ethernet segments with an important number of nodes. One approach for reducing the number of nodes in a segment was the introduction of active network devices called bridges. The bridge interconnected two collision domains, thus effectively doubling the span of the network (Figure 2-7).

Figure 2-7 - Bridged Ethernet network

The bridges were first defined by IEEE in 1990 with the IEEE 802.1D standard [bri-90]. Traffic local to a collision domain was not passed over the bridge. At that time, it was generally accepted that the traffic in a bridged network followed the Pareto principle, with an average of only 20% of the traffic crossing the bridge [spu-00]. In a carefully designed network, most of the traffic was local to the collision domain, therefore the effective bandwidth available on the two networks connected through a bridge improved when compared with a big single collision domain.

#### 2.1.2. The evolution of Ethernet – faster and further

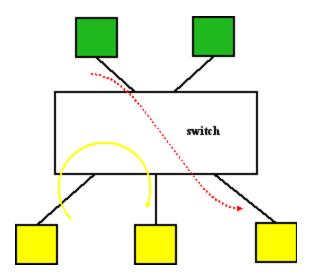

In the same year with the bridging standard, the IEEE introduced the 802.3i standard [utp-90] to define Ethernet transmission over the Unshielded Twisted Pair cable (UTP). The UTP cable could be used for full-duplex transmission. The topology of the network segment changed from a shared bus to a star. The device positioned at the centre of the network was either a hub or a switch.

The hub was a special type of multi-port repeater that had a single network node connected to each one of its ports. It just replaced the shared coaxial cable but brought no additional functionality. From the logical point of view, the entire network was still a shared bus. The communication on a segment was still made in half-duplex mode, hence limited to 10 Mbps shared between all connected devices.

The switch (Figure 2-8) was a multi-port bridge that interconnected any port to any other port momentarily and rapidly changed these temporary configurations. The presence of a switch enabled full-duplex connections, hence practically doubled the bandwidth at each node and greatly increased the total bandwidth available on the network.

Figure 2-8 - Switched Ethernet network

Modern Ethernet networks are built using switches. The internal bandwidth of the switch does not necessarily equal the sum of the bandwidth required to provide full duplex connections to all the ports in any traffic configuration. In this case, the switch is said to be "oversubscribed". Oversubscription is a common practice between equipment manufacturers for offering cost effective solutions to users that do not need all the theoretically available bandwidth at all times. Chapter 3 of the thesis will describe in detail the architecture of modern switches

Transmission of Ethernet over optical fibre was introduced in 1993 by the IEEE 802.3j standard [fib-93]. An upgrade in speed followed in 1995, increasing the available bandwidth to 100 Mbps [fast-95]. The transmission speed was further increased in 1998 to 1 Gbit/s by the IEEE 802.3z specification (known as Gigabit Ethernet) [gig-98].

The Gigabit Ethernet standard was the first Ethernet standard that did not target workstations as the primary user. The backbones of the data centres and small campus networks were addressed instead. At the time of adoption, optical fibre was the only transmission medium specified by the standard. Standard UTP copper cable was added later in 1999 by the adoption of the 802.3ad standard. The optical components defined by the 802.3z standard allowed for a maximum of 5 km distance between the two endpoints of a point-to-point connection. However, non-standard components allowed for up to 10 km and, in 2003, for up to 100 km distances. The CSMA/CD algorithm remained part of the standard in order to provide backward-compatibility support for devices operating in half duplex mode. However, it was very seldom used in practice as the vast majority of the deployed networks only used the full-duplex operation mode. Starting with the Gigabit Ethernet standard, Ethernet practically became a technology that only uses full-duplex point-to-point connections and a switch-centred star topology for the network.

During the first decade of Ethernet's life, other technologies arguably provided better services to the local area networks. Token Ring, for example, was collision-free and

provided more bandwidth than the original Ethernet. The Asynchronous Transmit Mode (ATM) provided guarantees on the amount of bandwidth that could be shared between different types of traffic. However, prices for components built for these technologies were too high compared to their Ethernet counterparts. The simplicity of installation, management and troubleshooting were additional advantages of the Ethernet technology.

The 10 Gigabit Ethernet standard (10 GE), adopted in 2002, built on this legacy but aimed to also bring Ethernet into the WAN area. A detailed description of the novelties introduced by this standard is presented after an introduction to wide area networking technology.

#### 2.1.3. The evolution of Ethernet – more functionality

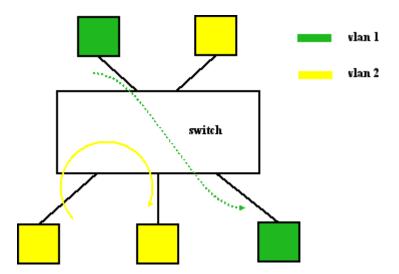

In parallel with increasing the speed and span of the network, Ethernet had to improve the manageability, survivability and functionality of the network in response to market demand. This subsection will only refer to the features that may be relevant in the context of the ATLAS experiment at CERN: virtual LANs, quality of service, flow control and spanning tree.

The switches and full-duplex connections allowed for increased network throughput compared to hubs and half-duplex connections. However, since the network was no longer a shared medium, broadcast and multicast traffic became a non-trivial issue. The switch had to forward a received broadcast packet to all the active ports and since many ports may send broadcast at the same time, large networks could be easily flooded by broadcast traffic. The broadcast floods could be limited by partitioning the switch in several logical entities that handled the traffic independently. A generalization of this feature is called Virtual LAN (VLAN) and was defined in the IEEE 802.1Q standard [etq-98]. Each VLAN contains its own broadcast domain and frames originating in one VLAN are not passed to any other VLAN (Figure 2-9).

Figure 2-9 - Ethernet network with VLANs

To enable this feature, a special field was added after the type/length field on the Ethernet header (Figure 2-10). The value of the type field is set to 0x8100 when the frame carries a VLAN identifier.

Figure 2-10 - VLAN additions to the Ethernet frame structure

The 14 bits reserved to the VLAN tag identifier limited the number of VLANs that could be defined in a network to 4094. When the standard was adopted, this number was considered large enough even for the requirements of the biggest corporation. In addition to the VLAN identifier, the 802.1Q standard provided support for marking eight different classes of traffic through three bits in the VLAN tag (Figure 2-10). Different applications require different service levels from the network and Ethernet was equipped with the basic features for allowing differentiated services. However, IEEE only defined the bits while allowing the manufacturers to specify how many classes of traffic are supported by a particular device. The policies to handle this traffic were not specified by the standard.

Flow control was introduced in the IEEE 802.1z standard for handling momentarily congestion on point to point full duplex links. A slow receiver could request a transmitter to pause transmission by transmitting a special Ethernet frame (Figure 2-11) that will be processed and consumed at the MAC level.

| nreamhle     | le CED            | destination | source | type  | opcode | time     | padding | CPC |

|--------------|-------------------|-------------|--------|-------|--------|----------|---------|-----|

| preamble SFD | 01 80 C2 00 00 01 |             | 88 08  | 00 01 | xx xx  | 42 bytes | CKC     |     |

Figure 2-11 - The structure of an Ethernet flow control frame

Two types of frames were defined: XOFF (stop transmit for a defined time interval) and XON (start transmit). An overloaded receiver may specify a time interval the transmitter should wait before sending the next frame. The time to wait was defined in terms of intervals equal to the time to send the minimum size frame. Also, if the processing of the backlog queue took less than anticipated, the receiving device may ask the source of traffic to resume transmission immediately by sending a XON packet.

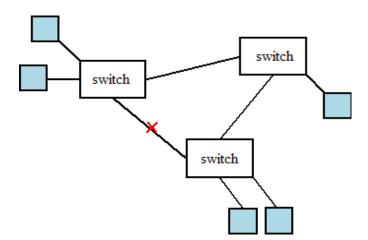

A switched Ethernet network is not allowed to contain loops. This is due to the mechanism that enables the bridge to learn what devices are attached to the network. Also, the broadcast mechanism requires a loop-free network. Since topologies became

more and more complicated, the IEEE introduced the spanning tree [bri-90] as a method of automatically detecting and removing loops from the network.

Figure 2-12 - Physical loop logically removed by the spanning tree

The loops are removed from the network by logically excluding the redundant connections from the packet forwarding path. Figure 2-12 presents a network where a loop was logically removed by the spanning tree.

However, in case of changes in the network topology (like failure of one of the forwarding connections), the standard spanning tree algorithm was too slow to converge to an alternate topology. Since traffic was blocked while the spanning tree tried to determine a loop-free configuration, this may translate in minutes of network interruption for large complicated networks. IEEE's response to this problem was the adoption of the 802.1w standard (Rapid Spanning Tree) that enabled faster convergence.

Running only one instance of the spanning tree on devices that are part of different VLANs may hamper connectivity by removing links that would be part of a loop, but belong to different VLANs. The IEEE 802.1s standard defined multiple instances of the spanning tree running on the same bridge and in combination with the 802.1r standard enabled running one instance of the spanning tree per VLAN.

#### 2.2. Introduction to long-haul networking technology

Throughout the last 30 years, the telecommunication networks were optimized for carrying voice traffic. The digitized phone signal had a bitrate of 64 Kbps (8-bit samples taken at a frequency of 8 KHz) and it was known as Digital Signal – level 0 (DS-0). Multiple DS-0s were aggregated by multiplexers into higher order signals. The DS-1 signal, for example, contained 24 DS-0 channels. However, the hierarchy of digital signals was not standardised for rates higher than DS-3 (28 DS-1 signals) [gor-02]. In addition, the network was plesiochronous: the network devices used their own internal clocks for probing the incoming bits. The differences between free-running clocks

translated into bit sampling errors, hence a reduced quality of the voice signal recovered at the other end of the connection. With the start of data communications during 1970s, the telephone operators could not afford the level of bit error rates provided by a plesiochronous network. In addition, the widespread of telecommunications required worldwide-agreed standards for interconnecting equipment from different manufacturers.

Introduced in the 1980's, the SONET/SDH protocols are the foundation of today's long haul networks. Bellcore (now Telcordia) proposed the SONET standard to the American National Standards Institute (ANSI) in 1985. In 1988, the Consultative Committee for International Telegraph and Telephone (CCITT – now ITU-T, the International Telecommunications Union) adopted SDH, a standard that includes SONET but supports different start payloads adapted to the European and Japanese telephone systems. The SONET/SDH protocols operate at layer one of the OSI stack. They allow mixing voice and data traffic while offering specific guarantees for each type of traffic.

The philosophy of the SONET/SDH protocols can be summarized as follows:

- Time-division multiplexed system with synchronous operation

- The network is organised hierarchically, starting with slower connections at the edge followed by increasing speeds, in fixed increments, on the links towards the core

- Management and maintenance functionalities are included in the communication protocol

- The network supports rapid self-healing capabilities (less than 50 milliseconds) in case of an outage on a connection in a ring topology

The SONET/SDH protocol was developed to support the legacy plesiochronous network hierarchy. The equipment always transmits 8000 frames per second. However, the size of the frame increased with the capacity of the channel. The current state-of-the art transmission speed is 9.95 Gbaud/s (OC-192/SDH-64). Table 1-1 shows the SONET/SDH transport hierarchy (DS – Digital Signal, STS – Synchronous Transport Signal, OC – Optical Carrier, STM – Synchronous Transport Module).

| Bit rate [Mbps] | PDH America | PDH Europe | SONET      | SDH       |

|-----------------|-------------|------------|------------|-----------|

| 9952            |             |            | STS/OC-192 | STM-64    |

| 2488            |             |            | STS/OC-48  | STM-16    |

| 622             |             |            | STS/OC-12  | STM-4     |

| 155             |             |            | STS/OC-3   | STM-1     |

| 140             |             | E4         |            |           |

| 51              |             |            | STS/OC-1   |           |

| 45              | DS-3/T3     |            | STS-1 SPE  | STS-1 SPE |

| 34              |             | E3         |            |           |

| 8               |             | E2         |            |           |

| 6               | DS-2/T2     |            |            |           |

| 2               |             | E1         |            |           |

| 1.5             | DS-1/T1     |            |            |           |

| 0.064           | DS-0/T0     | E0         |            |           |

Table 2-2 - The SONET/SDH hierarchy

The transmission medium for SONET/SDH is the optical fibre for long-distance communications or electrical wires for very short distances, mainly inside a rack of equipment. Due to the attenuation on the fibre, repeaters have to be installed at fixed distances on a long-distance connection. The repeaters are optical amplifiers that amplify the incoming light with no knowledge on the communication protocol. They are hence signal-agnostic. For the fibre commonly deployed (category C as defined by the ITU-T G.652 standard), the distance between two consecutive repeaters is about 40km. The repeaters are commonly referred as Erbium Doped-Fibre Amplifiers (EDFAs) from the technology employed in their construction. The EDFAs have a usable bandwidth of 30nm, centred on the 1545 nm wavelength. Within this narrow interval, they can amplify multiple optical channels.

Especially at high transmission speeds, optical signal dispersion in the optical fibre is the parameter that limits the distance that can be achieved before the signal must be regenerated. The operations to be applied to the signal are reshaping, reamplification and retiming (3R regeneration). The retiming operation requires an optical-electro-optical (OEO) conversion has to be performed. Due to the electrical stage involved, the 3R regeneration stage is no longer signal-agnostic: it requires knowledge about the bitrate and generic content of the signal to be reconstructed. The 3R regenerators deployed today in the long-distance network infrastructure assume SONET/SDH framing for the incoming signal. The distance between two regenerators is in general around 600 km.

The transmission capacity of an optical fibre can be increased through a wavelength division multiplex (WDM) technique that combines multiple communication channels using different frequencies over a single fibre. Up to 128 channels have been demonstrated, at a speed of 10 Gbit/s per channel, using a dense WDM technique [luc-02]. The WDM systems are signal agnostic, but whenever 3R regeneration is needed an OEO conversion has to be employed. Therefore SONET/SDH framing is required today for any signal that traverses a WDM connection. Practically, all current long-distance networks are built using SONET/SDH running over DWDM.

#### 2.3. The 10 Gigabit Ethernet standard

The 10 GE standard (IEEE 802.3ae-2002, [10ge-02]) defined the first Ethernet that did not support half duplex communications via CSMA/CD. By supporting only full-duplex connectivity, the 10 GE freed Ethernet of the CSMA/CD legacy. Henceforth, the distance of a point-to-point connection will only be limited by the optical components used for transmitting and propagating the signal.

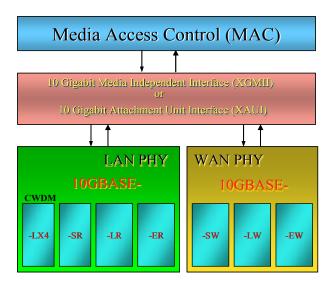

Several physical layers were defined in the 10 GE standard. The only transmission medium supported by the original version of the 802.3ae standard, issued in June 2002, was the optical fibre. The adoption of a standard for transmitting 10 GE over UTP copper cable is currently scheduled for 2006.

The standard defined a maximum reach of 40 km for a point-to-point connection, using 1550 nm lasers over single mode carrier-grade optical fibre. Two categories of physical layer devices (referred as transceivers later in this work) were supported by 10 GE: LAN PHY and WAN PHY (Figure 2-13).

Figure 2-13- Transceiver options in the 10 GE standard

LAN PHY was developed as a linear evolution in the purest Ethernet tradition: faster and further, keeping the Ethernet framing of the signal. WAN PHY was defined by IEEE for SONET/SDH compatible signalling rate and framing in order to enable the attachment of Ethernet to the existing base of long-distance network infrastructure.

### 2.3.1. The 10 GE LAN PHY – connectivity for LAN and MAN

The LAN PHY specified a transmission rate of 10.3125 Gbaud/s. The outgoing signal is encoded using a 64B/66B code, hence the actual transmission rate from the user's point of view is exactly 10 Gbit/s. The original commitment of the standard, transmit 10 times more data than the previous Ethernet version, had thus been fulfilled. The minimum and maximum frame sizes of the original Ethernet have been maintained, assuring the compatibility with older versions of the standard. The structure of the frame remained unchanged as well.

Four different optical devices were defined by the standard (Figure 2-13):

- the 10 GBASE-LX4, for operation over singlemode fibre using four parallel wavelengths simultaneously in order to reduce the signalling rate

- the 10 GBASE-SR, for operation over multimode fibre and a reach of up to 850 meters

- the 10 GBASE-LR, for operation over singlemode fibre and a reach of up to 10 km

• the 10 GBASE-SR, for operation over singlemode fibre and a reach of up to 40 km

The first generation of optical devices employed by the manufacturers were modules inherited from SONET/SDH. The second generation introduced modular hot-pluggable optical devices that complied to the XENPAK [xenpak] multi-source agreement between component manufacturers. The XENPAK device implemented the Physical Medium Attachment (PMA) and Physical Medium Dependent (PMD) layers of the 10 GE specification, thus being more than pure optical equipment. The XENPAK modules were relatively large and the heat produced posed problems to certain chassis designs or network environments. Subsequent generations, the XPAK and X2 modules, featured the same optical characteristics in a reduced package while also reducing the heat dissipation. The XFP modules [xfp] only contained the PMD layer, thus further reducing the footprint, power consumption and heat dissipation.

An innovative use of the 10 GE LAN PHY was demonstrated by the ESTA EU project [esta]. In two subsequent experiments, the span of a point-to-point 10 GE connection over dark fibre was pushed from 40 km (as defined by the standard) to 250 km and later to 525 km [pet-04]. This demonstration proved that a network built with 10 GE technology can span a country of the size of Denmark, almost reaching the limit where optical signals have to be regenerated.

Above a certain number of amplifiers and a certain distance on the optical fibre, the optical signal needs to be fully regenerated before being transmitted towards its destination. In order to follow the traditional 10x increase in data speed, the signalling rate of LAN PHY is 10.31 GBaud due to the 64B/66B coding technique used for the signal. The data rate and framing made LAN PHY incompatible with the installed wide area network infrastructure, hence the requirement to use a different device for transmitting Ethernet frames at long distances. WAN PHY was introduced by IEEE as a direct gateway from the LAN into the SONET/SDH-dominated WAN.

#### 2.3.2. The 10 GE WAN PHY – Ethernet over longdistance networks

WAN PHY was defined to be compatible with SONET/SDH in terms of signalling rate and encapsulation method. By inserting a WAN Interface Sublayer (WIS) before the PMD sublayer, the Ethernet frames are directly encapsulated onto SONET/SDH frames. WAN PHY therefore enabled the direct transport of native Ethernet frames over existing long-distance networks. However, the 10 GE standard does not guarantee strict interoperability of WAN PHY with SONET/SDH equipment due to mismatched optical and clock stability characteristics. Certain bits of the SONET/SDH management overhead were unused in the WAN PHY frame or were used with default values imposed by the standard. The SONET/SDH ring topology and 50ms restoration time were explicitly excluded from the WAN PHY specification.

The optical jitter characteristics of WAN PHY lasers were relaxed in comparison to the SONET/SDH standard. The main reason for the relaxed jitter specifications was to provide a less expensive solution by using lower price optoelectronic devices. Although the WAN PHY standard permits timing and optics that diverge from the SONET/SDH requirements in practice there were no available components to take advantage of the opportunity. All WAN PHY implementations evaluated in this work used SONET compatible laser sources. The newly introduced XFP device format defined the same optical components to be used for SONET/SDH, 10 GE and Fibre Channel [xfp].

The clock used as a reference for WAN PHY transmissions was allowed to be less accurate (20 parts per million – ppm instead of 4.6 ppm or a variation of +/- 20 microseconds per second instead of +/- 4.6 microseconds per second of the standard SONET clock). The 20 ppm value is the required timing accuracy of a SONET/SDH connection operating in a special maintenance mode. A SONET/SDH connection operating in production mode is required to have a timing signal accuracy of 4.6 ppm or better.

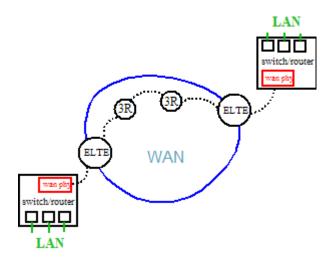

Instead of a direct interoperability guarantee, IEEE defined an additional piece of equipment (the Ethernet Line Terminating Equipment – ELTE) for connecting WAN PHY to SONET/SDH networks (Figure 2-14).

Figure 2-14 - Native Ethernet connection to the WAN through ELTE

The main tasks of the ELTE were to compensate for differences in clock accuracy and eventually add bits in the frame management overhead. However, no manufacturer had, to date, built an ELTE. The direct attachment of WAN PHY to the existing long-distance infrastructure was the only solution available for directly connecting 10 GE equipment to long-distance networks, at the time our experiments were performed.

The WAN PHY was defined to be compatible with SONET/SDH in terms of data rate and encapsulation method. The transmission rate was set to 9.95 GBaud/s, using a 64B/66B encoding. The payload capacity is only 9.58 Gbaud/s, using the Synchronous

Transport Signal (STS)-192c / Virtual Container (VC)-4-64c frame format. This translates into a usable data rate of 9.28 Gbit/s. The theoretical Ethernet data throughput of the WAN PHY was thus only 92.94% of the throughput achieved by the LAN PHY. An automatic rate control mode was defined by the IEEE 802.3ae standard to adjust the transmission rate between the two types of PHY.

There is a lot of LAN expertise and equipment readily available at research institutes and universities, but few people here have experience with SONET. The WAN PHY simplifies the implementation of the distributed LAN concept, allowing for native transmission of 10 GE frames worldwide.

#### 2.4. Conclusion

"Ethernet" is a generic denomination for the standard technology used in today's local area networks. The current version of the Ethernet standard has greatly evolved from the original starting point. Transmitting at 10 Gbit/s and empowered by advanced features like Virtual LANs, Class of Service and Rapid Spanning Tree, Ethernet is a technology that can be used everywhere a customer is looking for cost effective solutions. The Ethernet standards define the transmission methods and specify the content of the frames. However, these standards do not include specifications related to the internal architecture of devices built for switching Ethernet frames. Chapter 3 introduces the most popular architectures of Ethernet switches.

# 3. LAN and WAN building blocks: functionality and architectural overview

Modern Ethernet networks are built using full-duplex links and a star architecture, with the switch at the centre of the network. The switch has two basic functions: the spatial transfer of frames from the input port to the destination port and the resolution of contention (that is providing temporary storage and perhaps a scheduling algorithm to decide the order in which multiple frames destined to the same output port will leave the switch). The switch thus acts as a statistical multiplexer, whereby unscheduled arrival frames are transferred to their destination in a predictable and controlled manner.

This chapter will start with a theoretical approach to congestion through queuing theory. Then, the most common architectures used in switches will be reviewed. Traffic profiles on Ethernet networks will be briefly examined, in order to better understand the problem that switches have to address. The chapter will finish by presenting a generic Ethernet switch architecture, characteristic for the implementations present on the market in the interval 2001-2004.

# 3.1. Introduction to queuing theory

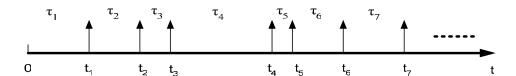

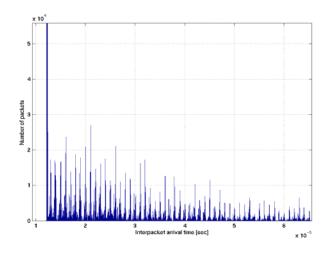

Poisson processes are sequences of events randomly spaced in time. Poisson distributions are used for describing a diverse set of processes, ranging from natural phenomenon (the amount of photon emission by radioactive materials) to social behaviour (the arrival of clients at the cashier's desk in a supermarket). The arrival of jobs to the service queue of a batch processing system, characteristic for the computing technology of mid-1960s, could also be described by Poisson formulas. Figure 3-1 shows a time representation of a Poisson process.

Figure 3-1 – Temporal representation of a Poisson process

A Poisson process is characterised by a parameter noted  $\lambda$  that is defined as the long-time average number of events per unit time. The probability of n events to happen within a time interval of length t is given by the formula:  $P_n(t) = \frac{(\lambda t)^n}{n!} e^{-\lambda t}$ .

It can be shown that the number of events in disjoint time intervals are independent. The  $\tau_1, \tau_2, \dots$  intervals, defined as the length of the time between consecutive events, are

random variables called the "interarrival times" of the Poisson process. It can also be shown that the interarrival times are independent and characterized by the probability:  $P(\tau_2 > t) = e^{-\lambda t}$ . Exponentially distributed random variables are said to be *memoryless*: for any t and t, t and t and t and t are t and t and t and t and t and t are t are t and t are t and t are t are t and t are t are t and t are t and t are t are t are t and t are t are t and t are t are t and t are t are t are t and t are t and t are t are t are t are t and t are t are t are t are t and t are t are t and t are t are t and t are t are t are t are t and t are t and t are t are t are t and t are t are t and t are t are t and t are t and t are t and t are t are

The Poisson processes have the following two properties, of particular relevance to queuing systems:

- 1. The merging of two independent Poisson processes, of rate  $\lambda_1$  and  $\lambda_2$ , results in another Poisson process, dependent on  $\lambda_1 + \lambda_2$ .

- 2. The splitting of a Poisson process of rate  $\lambda$  results in two Poisson processes, characterised by  $p\lambda$  and  $(1-p)\lambda$ , where p is a uniformly-distributed random probability.

Therefore, the Poisson character of the traffic is maintained throughout a network of queues, regardless on the number of queuing stages and independent on the flow through the system.

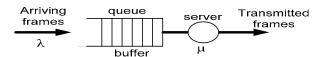

Kleinrock modelled the arrival of packets to a network queue using Poisson distributions in his seminal PhD thesis, published in 1964 [kle-61]. The assumption that incoming traffic is Poisson-distributed is widely used in modern switching theory. Figure 3-2 shows a generic queue model.

Figure 3-2 - Generic queue model

Frames arrive in the queue at a rate  $\lambda$  and after a processing stage they leave the queue at a rate  $\mu$ . Classic queuing theory uses the Kendall notation A/S/s/k to describe a queue:

- A represents the type of arrival process (examples: M memoryless = Poisson, G Geometric, D Deterministic)

- S represents the time required for the processing of each frame (example: M exponential, D deterministic, G generic or arbitrary)

- s is the number of servers that take frames from the queue

- *k* stands for the capacity of the queue. For simplicity, the capacity is usually considered infinite and the k parameter is omitted.

The two types of queues most widely used for modelling switching systems are M/D/1 and M/M/1. The M/D/1 is a queue consumed by one server, has Poisson arrivals with rate  $\lambda$  and a deterministic service time. The M/M/1 queue is also consumed by one server, has Poisson-distributed arrival times with rate  $\lambda$ , but the service time is Poisson-distributed with rate  $\mu$ .

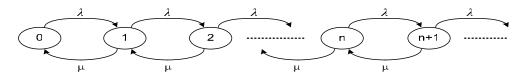

The behaviour of frames in an M/M/1 queue can be modelled as a continuous Markov process chain, due to the fact that the length of the queue increases and decreases depending on the frame arrival and service times. Hence a Markov analysis can be performed on the queue in order to find the distribution of waiting times and the average queue size. Figure 3-3 presents an M/M/1 queue modelled as a Markov chain.

Figure 3-3 - M/M/1 queue represented as a Markov chain

The interarrival rate  $\lambda$  and the service rate  $\mu$  are the labels associated to the transitions between the Markov states. Defining  $\rho = \frac{\lambda}{\mu}$  to represent the queue occupancy rate, the

average queue size can be calculated using the formula:  $E(Q) = \frac{\rho}{1-\rho}$ . It follows that  $\rho$

has to be less than 1 in order for the queue to be stable, e.g. not grow to infinity. Intuitively, it makes sense to require that the arrival rate be lower than the service rate – otherwise, the system is just oversubscribed and the queue grows continuously. The steady state probability of finding n frames in the queue is given by the equation:  $p_n = (1-\rho)\rho^n$ . The average delay experienced by a frame in the queue is determined using Little's formula:  $E(T) = \frac{E(Q)}{\lambda}$ , where T is the time spent by a frame in the queue,

including the waiting and service times. In the case of the M/M/1 queue,  $E(T) = \frac{1}{\mu - \lambda}$ .

Due to the constant service time, the M/D/1 queue can no longer be studied as a continuous Markov chain. However, Little's result still holds and together with the Pollaczek-Khinchin formula (that states that the expected waiting time is proportional with the second order moment of the service time and a factor of  $\frac{\lambda}{2(1-\rho)}$ ) allows for determining the average delay. The average number of frames in the queue is determined by the following formula:  $E(Q) = \frac{\rho}{1-\rho} \left(1-\frac{\rho}{2}\right)$ . The average delay is determined by  $E(T) = \frac{\lambda}{2\mu(\mu-\lambda)}$ .

As the offered load ( $\lambda$ ) approaches the service rate ( $\mu$ ), it becomes clear that the average delay experienced by a frame in an M/D/1 queue is about half of what would be the result

As the offered load ( $\lambda$ ) approaches the service rate ( $\mu$ ), it becomes clear that the average delay experienced by a frame in an M/D/1 queue is about half of what would be the result of an M/M/1 queue. The deterministic service time may be associated with fixed frame sizes, which made the M/D/1 queuing model popular for modelling ATM switches and

cell-based switching fabrics. However, assuming the length of Ethernet frames in the incoming traffic is Poisson distributed, an M/M/1 queue would better reflect the average occupancy and service time.

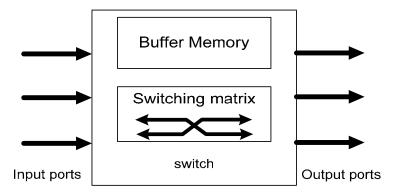

## 3.2. Switch fabric architectures

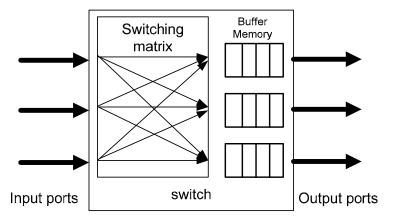

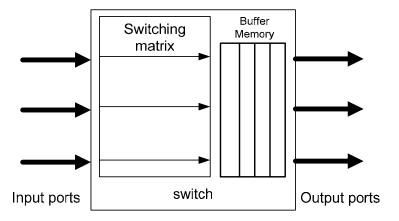

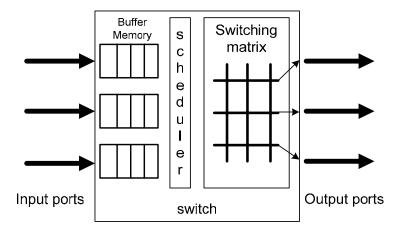

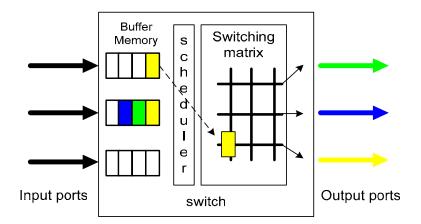

Independent on the actual distribution of the frame arrival times, Ethernet switches have to solve the fundamental problem of congestion. There is only one way to solve this problem, without discarding frames immediately: providing a buffer memory, where frames may be stored temporarily until the congested resource is free. The generic architecture of a switch is presented in Figure 3-4.

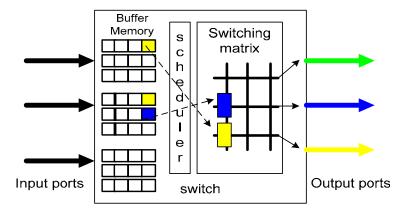

Figure 3-4 - Generic switch architecture

The combination of switching matrix and buffer memory will be referred as the "switching fabric" throughout this document. The two components of the fabric determine the performance of the switch. This section will present the most popular switching fabric architectures.

The following assumptions were considered for each of the subsequent analysis of a switch. The system operates synchronously and the time is partitioned in constant intervals, equal to the time required to transmit one frame. The length of the incoming frames is considered constant. To further mark the distinction, only the term "cell", referring to a fixed-size logical data transfer entity, will be used throughout this section. The time is considered to be partitioned in fixed size intervals, equal to the time interval needed to transmit one cell from the input port to the output port of the switch. The switch may transmit at most one cell from an input port to an output port during a time slot. One may consider that Ethernet frames arriving to such switch are split into cells of fixed size and it is the cells that are taken into account by the scheduler. The arrivals on the *N* input ports of the switch are governed by identical and independent (i.i.d) Bernoulli processes. Such a process is the discrete-time equivalent of the Poisson distribution presented in section 3.1. The probability that one cell will arrive at a particular input

during a time slot is p. Each cell is addressed to any given input with a uniform probability of 1/N, and successive cells are independent.

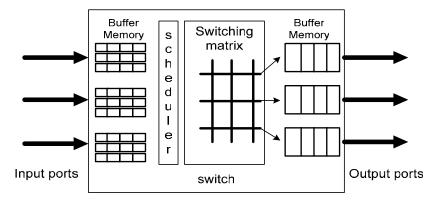

## 3.2.1. Output buffered switches and shared memory

The output buffered switch architecture allows for storing frames only at the output ports of the switch. Figure 3-5 presents the generic architecture of an output buffered switch.

Figure 3-5 - Generic architecture of an output buffered switch

The switching matrix is in fact a crosspoint fabric, connecting every input port to the memory associated to each output port. Therefore, each input port may use its own private connection to immediately transfer cells to the output port's memory. The flow of cells from an input port towards a particular output port is thus unaffected by the flows between the other ports. The transfer of cells from the input port to the output port's memory is performed in a FIFO manner.

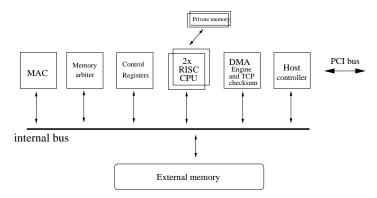

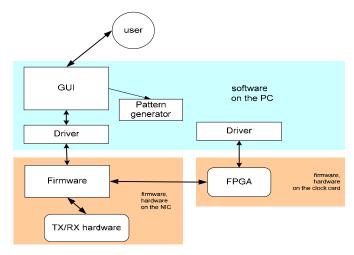

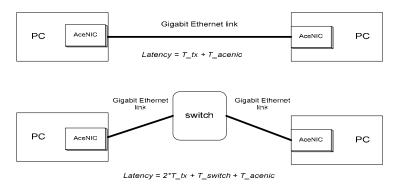

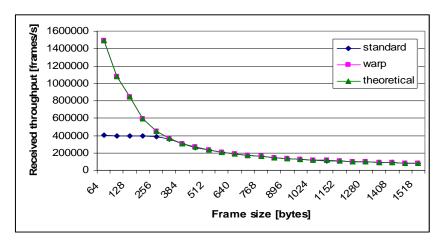

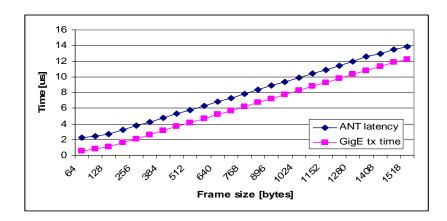

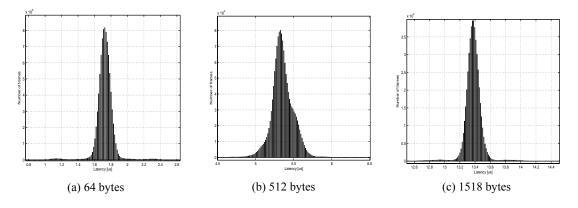

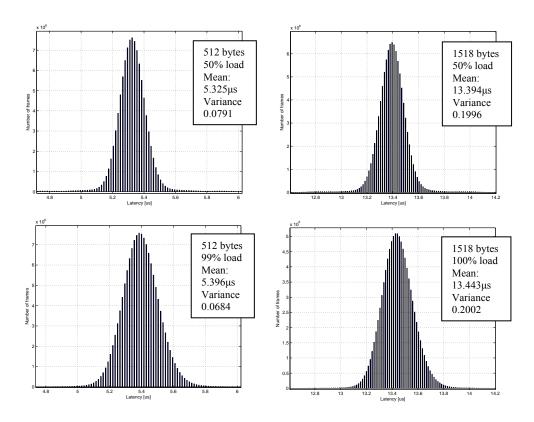

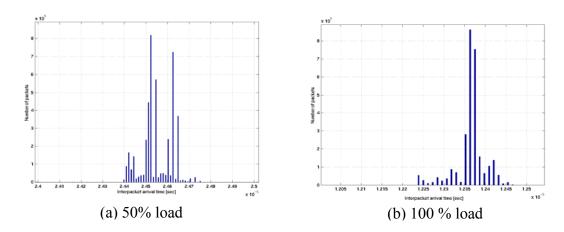

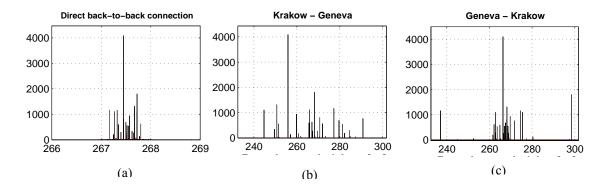

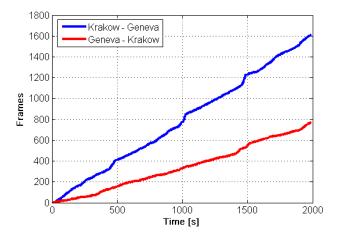

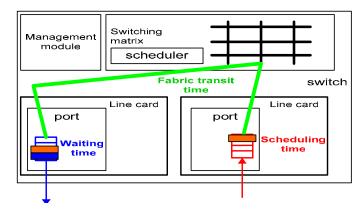

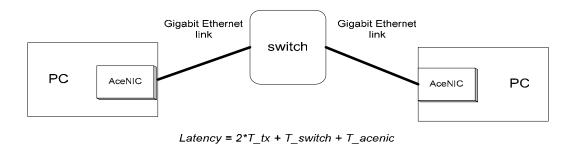

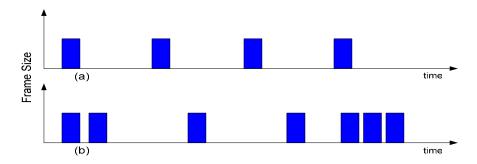

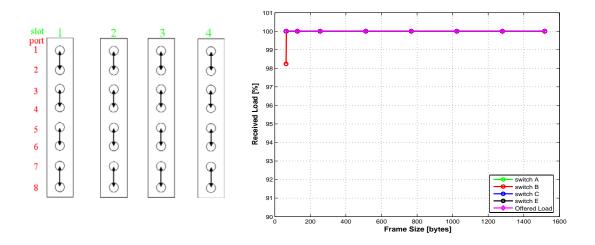

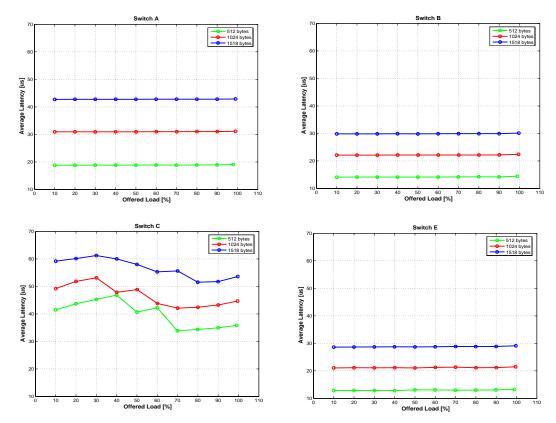

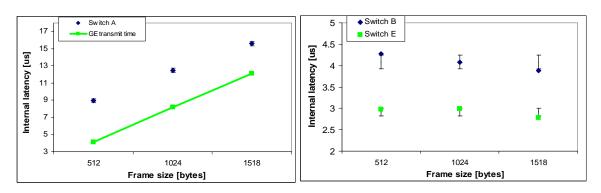

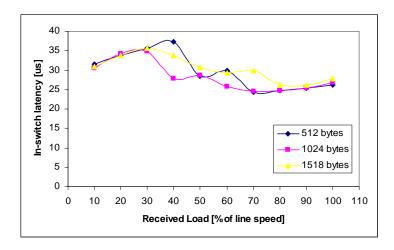

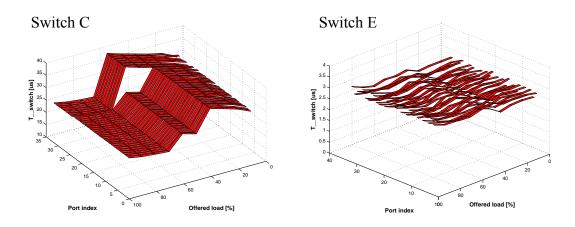

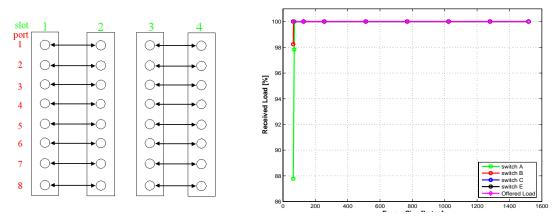

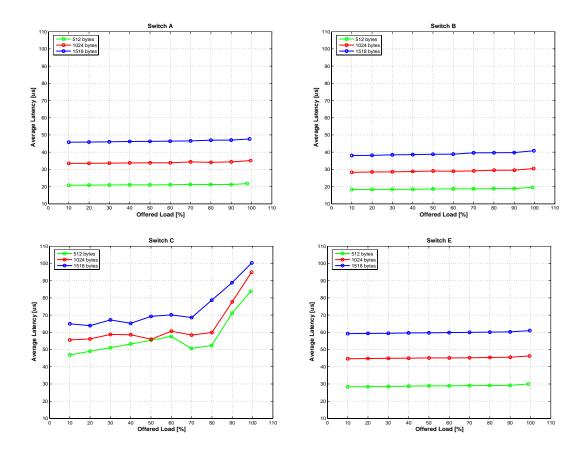

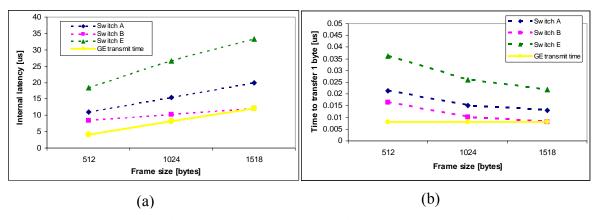

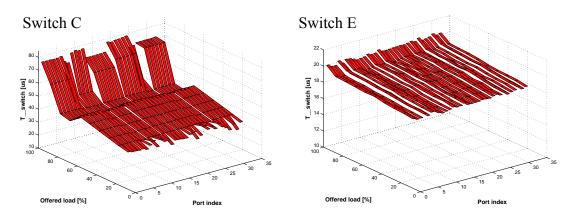

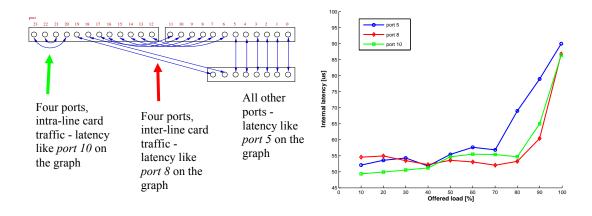

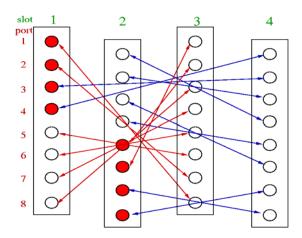

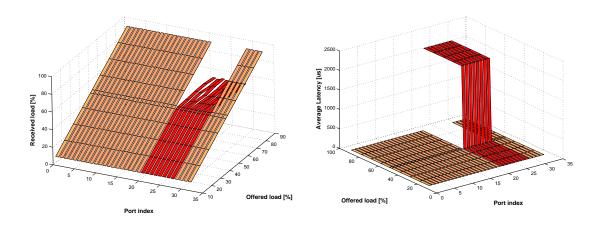

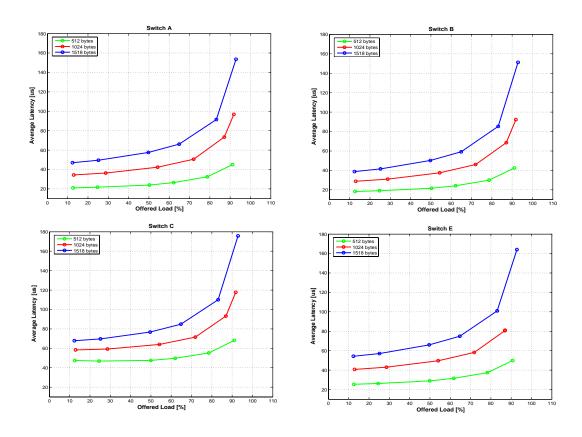

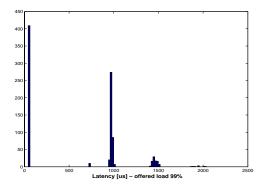

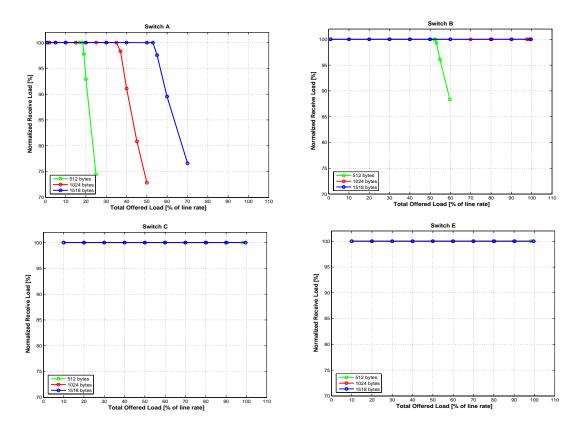

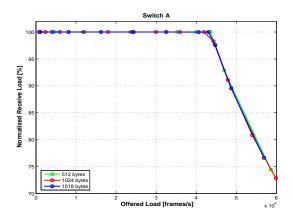

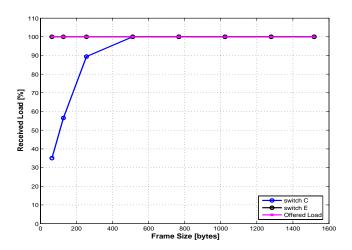

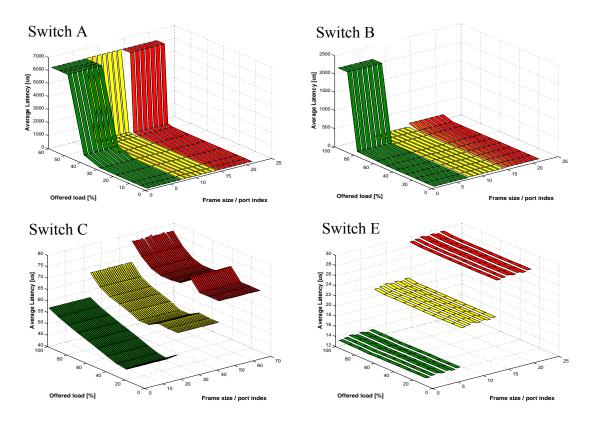

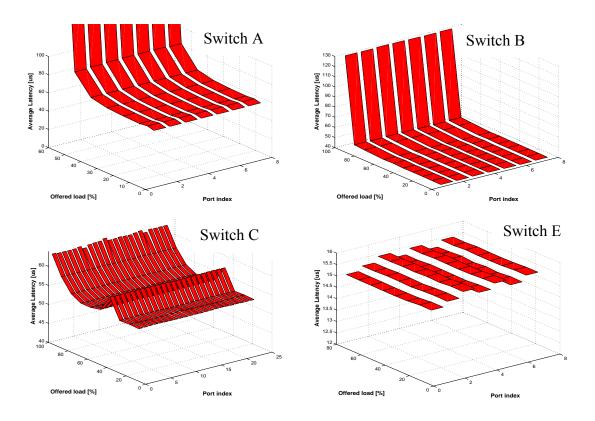

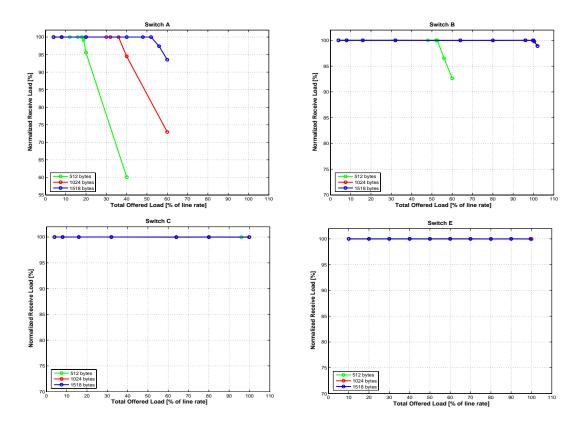

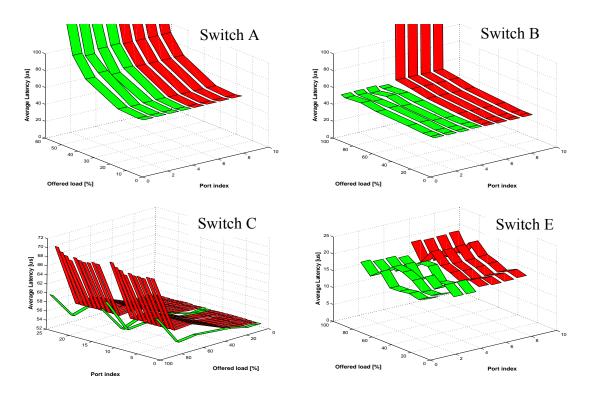

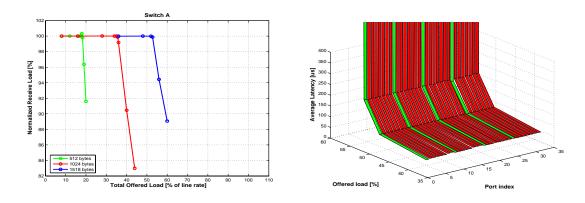

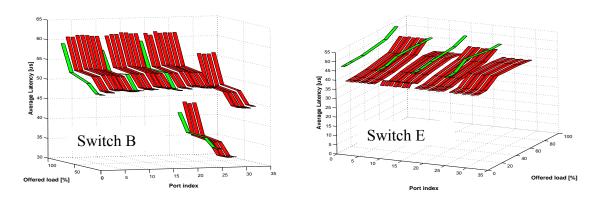

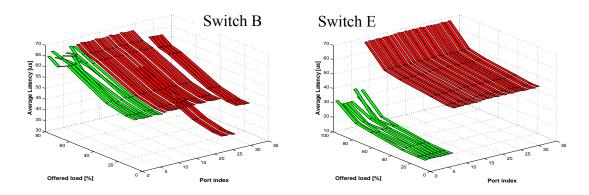

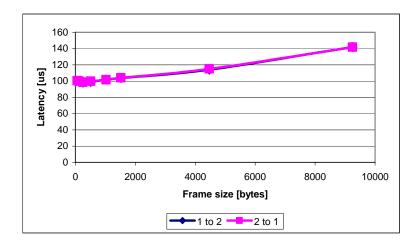

Karol et al. demonstrate [kar-87] that such an output buffered switch can be considered a linear combination of N parallel switches, each serving one output port. Queuing is only due to the probability of simultaneous arrivals of multiple cells addressed to the same output port, e.g. queuing appears because of an inherent property of the traffic. Follows immediately that an output buffered switch architecture will always provide the smallest average delay. Furthermore, Karol demonstrates that the steady-state probabilities for the average queue occupancy converge to those of an M/D/1 queue for each of the output ports. Therefore, an output buffered switch can achieve 100% throughput using infinite buffers that employ a FIFO strategy.