# FTuner: A Fast Dynamic Shape Tensors Program Auto-Tuner for Deep Learning Compilers

1<sup>st</sup> Pengyu Mu

School of Computer Science and Engineering Beihang University Beijing, China muphy@buaa.edu.cn

3rd Rui Wang

School of Computer Science and Engineering Beihang University Beijing, China

Abstract—Many artificial intelligence models process input data of different lengths and resolutions, making the shape of the tensors dynamic. The performance of these models depends on the shape of the tensors, which makes it difficult to optimize the tensors before the model runs. There are two common solutions to this problem. The first is to add useless data to the input to match a pre-optimized tensor library. The second is to use small basic tensors to create a tensor that is closest in size to the input data and then tune it to minimize padding. However, this second solution can be time-consuming.

This paper proposes a new technique for deep learning compilers called FTuner. Instead of using a large design space or training a cost model, we use an abstract computational unit called the uKernel to patch together small, various-sized tensors to match the shape of the input tensor. We determine the shape of the uKernel using an analytic hardware information model. Experiments show that the FTuner can achieve comparable operators and end-to-end performance to vendor libraries and achieves 3% speedup on existing auto-tuner with the modeltraining compiler while reducing tuning time by two orders of magnitude.

Index Terms—dynamic shape tensor, deep learning compilation, tensor program, auto-tuning

# I. INTRODUCTION

Large AI models [1]–[3], have complex structures, numerous parameters, and remarkable intelligence advantages. Therefore, improving the efficiency of these models on hardware has become crucial. However, achieving the theoretical performance of hardware can only be possible when deep learning models are finely tuned for this hardware. It is common practice to develop libraries for deep learning operators on different hardware manually, such as cuBLAS [4], cuDNN [5], CUTLASS [6], and oneAPI [7]. However, developing and maintaining these libraries can be costly and time-consuming due to the frequent iteration of the model and hardware.

Deep learning compilers [8]–[11], can generate highperformance programs for deep learning models on hardware. Some compilers, such as Ansor [12], even incorporate autotuners to optimize tensor programs automatically for optimal 2<sup>th</sup> Linquan Wei School of Computer Science and Engineering Beihang University Beijing, China

4<sup>nd</sup> Yi Liu School of Computer Science and Engineering Beihang University Beijing, China

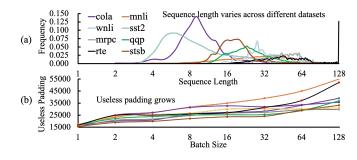

Fig. 1. Tensor shape diversity and padding cost. (a) The shape of input tensors varies across different datasets from the standard NLP benchmark GLUE [15]. (b) As the batch size increases, the amount of useless padding of the batch matrix multiplication grows.

Fig. 2. Illustration of Padding for Dynamic Shapes. Padding the dynamic shape to match the optimized kernel in the manual library.

performance. However, the input shape of large models cannot be known during the compilation phase. Therefore, if the shape of tensors is known only at runtime instead of compile time, it cannot guarantee effective execution for tensors in all possible shapes. For instance, in speech recognition models like WaveNet [13], the input speech duration can vary, and in natural language processing like BERT [14], the input sequence length ranges from a single word to hundreds. These scenarios involve what is known as dynamic shape tensors.

The problem of dynamic shape is quite common. In Fig. 1 (a), we can see the variety of shapes in terms of sequence length in an NLP benchmark called GLUE [15]. Currently, the compiler can only choose the smallest basic-shape tensor from

the available library and match it with additional padding data, as shown in Fig. 2. However, using padding data may lead to a significant reduction in performance. Large-scale AI models typically use a large batch size, and Fig. 1 (b) illustrates how padding to the batch matrix multiplication (Matmul) will gradually expand as the batch size increases.

Recent studies on auto-tuning dynamic shape tensors, such as DietCode [16] and HAOTuner [17], aim to reduce padding by creating small task units that can compose dynamic shape tensors. Compilers usually employ cost models to select high-performance units for dynamic shape tensors. However, training these models is time-consuming since these units are randomly generated and numerous in quantity. Roller [18], on the other hand, does not require any cost model but predicts tensor performance through strict hardware alignment. However, this method is only effective when the shape is known before the running. When dealing with dynamic shapes, Roller still generates a significant amount of padding, making it challenging to outperform the cost model training compilers.

To address this issue, we propose FTuner, a tensor tuning technique that enables the fast generation of high-performance kernel code for dynamic tensors. We introduce a novel abstract computing unit called uKernel and constrain its generation through hardware features and multiple metrics. Based on the metrics retained in uKernel, synthesis index analysis can help rapidly find high-performance uKernel-based programs. During the runtime of tensor programs, FTuner combines different uKernels to reduce padding in dynamic shape tensor programs. We have evaluated FTuner on both standard deep learning benchmarks and emerging new workloads against vendor libraries and state-of-the-art compilers, using a wide range of input shapes. Experiment results show that FTuner performs comparably to manual libraries on nearly half of the shapes and can be portable to different architectures.

In summary, this paper makes the following contributions:

- We propose an abstract computing unit called uKernel to create dynamic tensor programs. The size of the uKernel can be adjusted according to different memory hierarchies and computing resources instead of a time-consuming cost model.

- We implement a compiler framework FTuner based on uKernel. The compiler generates high-performance uKernels for dynamic shape tensors during the compilation phase. During runtime, FTuner combines different uKernels to create programs with small padding.

- The evaluation has shown that the techniques used by FTuner outperform state-of-the-art compilers on dynamic tensors. Furthermore, compared to compilers with model-training, FTuner reduces compilation time by two orders of magnitude, while achieves speedup by 3% on typical operators.

This paper is organized as follows. §II provides the background and motivation of this paper. §III gives an overview of FTuner. §IV introduces the compilation phase of FTuner. §V introduces the runtime of FTuner. We evaluate FTuner in §VI and conclude this paper in §VIII.

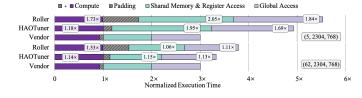

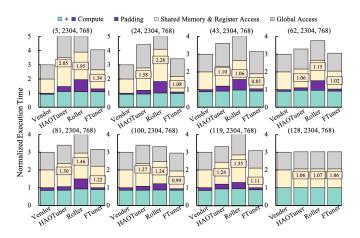

Fig. 3. The execution time breakdown of tensors optimized by different compilers. We used the NCU [19] to estimate the computation and memory access times for two shapes of the Dense operator on V100, normalized by Vendor. Roller [18] has a higher proportion of padding. Since the padding time of the Vendor cannot be measured, we estimate the padding time roughly by calculating the difference in computation time between the current kernel and the strictly aligned kernel.

# II. MOTIVATION

# A. The Gap Between Current Auto-tuner and Dynamic Shape Tensors Requirement

The current auto-tuners for compilers, such as Ansor [12], theoretically can explore the entire solution space and find the best schedule for tensor programs across all possible shapes. However, it's important to consider the significant time and computational power costs associated with this approach. These compilers utilize a cost model that employs machine learning, such as XGBoost [20], Chameleon [21], AdaTune [22], and heuristic search techniques like simulated annealing [23] and evolutionary algorithms [24] to find high-performance programs from a large solution space. Ansor, for instance, takes about 19.3 hours on V100 GPU to optimize only 8 shapes of input tensors for all the operators of the end-to-end model of BERT. Instead of creating optimal tensor programs with cost models, Roller [18] achieves highly predictable performance of tensor programs through strict hardware alignment. However, its method for handling dynamic shapes is not optimal.

DietCode [16] has an abstract computing unit that acts as a link between the tensor program and the hardware resource. By dividing the dynamic shape tensor input's kernel into multiple units and scheduling them onto the CUDA cores of the GPU, the program can be tuned by manipulating the units. To address performance instability issues across different devices in DietCode, HAOTuner [17] uses transfer algorithms to reduce the training time of the cost model slightly. However, it still takes 3 hours to optimize the entire BERT network and 35 minutes to optimize a single Dense operator. HAOTuner has a similar technique to DietCode and performs better performance than DietCode.

# B. Observation and Insights

Although HAOTuner [16] can perform relatively well on dynamic shape tensors, it takes too long to complete the tuning process. Roller [18] can significantly reduce the tuning time, but its support for dynamic shapes is unsatisfactory. To investigate this issue, we analyzed the computation and memory access time of Roller. We found that the performance degradation is mainly due to padding, as shown in

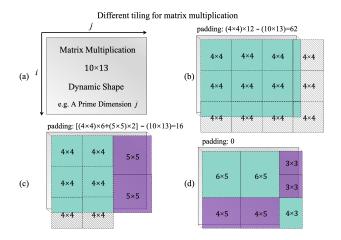

Fig. 4. Different tiling for matrix multiplication. (a) represents a matrix multiplication output dimension with a prime size axis, (b) is composed of a single kernel, (c) is the method adopted in this paper, which achieves zero-padding along the j-axis using two kernels, and (d) represents an ideal combined state that is difficult to achieve.

Fig. 3. Padding introduces additional boundary checks in nested loops, which slows down the computation process. Existing techniques have limitations in accurately profiling the computation time at a fine-grained level since computation and memory access time overlap. We tried multiple approaches, including tracking the number of instructions executed, but all exhibited significant errors. To estimate the timing of each component, we utilized the clock cycle statistics from NVIDIA NCU Tool [19]. On average, the Roller exhibits  $1.62 \times$  longer computation time than the Vendor. Therefore, if we can obtain abstract computing units like Roller, we can significantly reduce the tuning time. To enhance the performance of this approach, we need to minimize the program padding.

We found that using different basic tensor computation units to combine dynamic shape tensors can reduce padding. As shown in Fig. 4, (a) is a Matmul operator with a dynamic shape. HAOTuner uses only one unit to compose this tensor, as shown in (b). (c) can almost eliminate padding and enable using units with higher compute-to-memory ratios, but the challenge lies in accurately selecting these units. (d) represents an ideal state that we have not yet achieved. It motivates us to design a novel abstract computing unit and FTuner to select it and reduce padding.

# III. FTUNER DESIGN OVERVIEW

The main idea of FTuner is to use a small unit tensor, which we name ukernel, as the building block to create target variable input tensors. An analytical model uses the unit tensor. The same input tensor can be composed of uKernels of different sizes. The distinction between uKernels lies in the number of iterations in each layer of loops, which corresponds to different numbers of thread blocks. To minimize the useless padding, FTuner matches input tensors with multiple-sized ukernels. The uKernel is a predefined operator template, which is implemented as a TVM [8] schedule with its built-in scheduling primitives. FTuner can find a set of high-performance uKernels

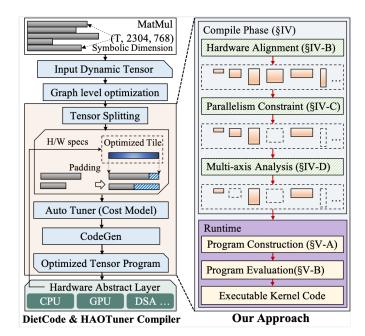

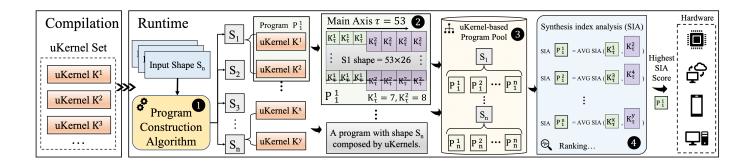

Fig. 5. The overall architecture of FTuner. Taking the Matmul operator as an example, we assume that the input shape is denoted by the symbol T along the i-axis, while the j and k axes remain fixed. We replaced the portion from tensor splitting to generating optimized tensor programs in DietCode [16].

| class ukernel {          |                               |

|--------------------------|-------------------------------|

| RegisterTile             | <pre>reg_tile;</pre>          |

| ShareMemoryTile          | <pre>smem_tile;</pre>         |

| vector <int></int>       | <pre>padding_threshold;</pre> |

| vector <double></double> | usage_eff;                    |

| vector <double></double> | compute_eff;                  |

| };                       |                               |

Fig. 6. The data structure of uKernel. It is an abstract computing unit representing a fraction of the tensor program. To facilitate the evaluation of uKernel's performance, we define the tile size at two memory hierarchies and three performance metrics.

ahead of running time. We compare the overall architecture of FTuner with Dietcode [16] and HAOTuner [17] in Fig. 5. HAOTuner has a similar technique to DietCode and performs better performance than DietCode. We adopted the same tuning process as DietCode while replacing the portion from tensor splitting to generating optimized tensor programs.

Given an operator's tensor program (including computational rules and specific input shape), a uKernel represents a code segment constituting that tensor program. It determines the scope of tensor computations under the current computational rules. To enhance the performance of uKernels, we establish performance parameters for each one. Fig. 6 shows the data structure of ukernels, including the tile sizes at different memory hierarchies, the proportion of effective computations, resource utilization, and the compute-to-memory ratio. Tab. I lists the keywords used in the data structure. The uKernel resides in the streaming multiprocessors (SMs) of the GPUs. Each SM consists of several thread blocks of different sizes, and uKernel is abstracted as a thread block.

TABLE I Keyword in uKernel.

| Keyword           | Definition                                             |

|-------------------|--------------------------------------------------------|

| reg_tile          | The tile size of uKernel in the register level.        |

| smem_tile         | The tile size of uKernel in the shared memory level.   |

| padding_threshold | The proportion of the part without padding in uKernel. |

| usage_eff         | The resource utilization of uKernel.                   |

| compute_eff       | The compute-to-memory ratio of uKernels.               |

We implemented FTuner based on TVM [8]. The frontend input of FTuner is an ONNX graph [25], which utilizes subgraph fusion from Ansor [12] and operator fusion from Relay [26]. The fused operators could be presented as multiple nested iterations, and FTuner can optimize each simultaneously. FTuner exports tensor expressions [10] and generates a uKernel set through its filter algorithm for the operator extracted from the optimized graph.

During the compilation stage, FTuner initiates a group of ukernel candidates for all the possible shapes of input tensors and creates an operator template where the type of ukernels is parameterized. At the runtime stage, FTuner constructs multiple candidates of the tensor programs for the input tensors and chooses the optimal one to execute. We introduce the compilation phase and running stage in Section 4 and Section 5, respectively.

#### IV. COMPILATION STAGE OF FTUNER

During the compilation phase, FTuner aims to generate a high-performance uKernel set. We use input dynamic shape tensor as workload, which includes every possible shape. We introduce the uKernel definition and then initialize the uKernel set through three parts: hardware alignment, parallelism constraints, and multi-axis analysis.

$$SIA \ Score = c_0 CMR + c_1 Pad + c_2 Occ \qquad (1)$$

We systematically derive each term of Equation 1 for uKernels step by step. Equation 1 serves as an analytical model used at the runtime stage to evaluate the performance of programs. Here, CMR, Pad, and Occ denote compute\_eff, padding\_threshold, and usage\_eff within the uKernels, respectively. These three factors are calculated using Equations 7, 2, and 3, respectively.

#### A. Hardware Alignment of uKernel

To align with hardware, FTuner tiles the computation from two memory hierarchies. For a more intuitive illustration, as shown in the left of Fig. 7, the naive loop for Matmul  $C_i, j = \sum_k A_i, kB_k, j$  as an example. In thread block, the loop structure in ① represents the tiling of shared memory along the i and j axes. ② represents the tiling along the k-axis. The tiling of the shared memory is completed only when the kaxis is finished. ③ illustrates the register tiles, where each tile along the k-axis comprises multiple registers.

FTuner provides the RegTileRule() (alg. 1 line 2) to tile reg\_tile based on factors of the axis length. Calculate all factors of the dynamic axis input. These factors serve as an array of the tiling for the register. For example, when the sequence length is a prime number (53), we store the factors of adjacent numbers (52, 54) in the array. SmemTileRule() (alg. 1 line 3) for shared memory tiling. First, determine the major axis of the loop, typically row-major or col-major. smem tile is first tiled along with the major axis, and the remaining axes grow linearly based on reg tile. For example, the k-axis is aligned with a multiple of 8, whereas for the i and j axes, we compute the factors that can evenly divide them. For float32, we select multiples of 8 on NVIDIA GPUs. For different datatypes, depending on the width of memory transactions, different alignment multiples can be used. Finally, the scaleup is repeated to expand the smem\_tile. This rule obtains an increasing smem\_tile while traversing all reg\_tiles.

Comparing ④ and ⑤, the same register tile results in different shared memory tiles (also represent thread-level tiles). Since the thread allocation determines the size of shared memory requested by the uKernel, the thread-level tile indicates the alignment of the uKernel with shared memory. ⑥ and ⑦ show that different register tiles can also result in the same shared memory tile. We aim to explore all possible tiling options to avoid missing high-performance uKernels. This phase on V100 can generate approximately 2 million uKernels for 128 input shapes.

TABLE II IMPORTANT NOTATIONS IN §IV-B.

| Definition                                            |  |  |

|-------------------------------------------------------|--|--|

| The workload represents the operator with shape.      |  |  |

| The value of padding_threshold K.pad is $\epsilon$ .  |  |  |

| The bytes to compose the workload using K.            |  |  |

| The bytes need to be padded.                          |  |  |

| The value of usage_eff K.occ is $\lambda$ .           |  |  |

| The number of uKernels required in the workload.      |  |  |

| The total number of SMs.                              |  |  |

| Thread blocks allocated to one SMs.                   |  |  |

| The default active thread block per SM.               |  |  |

| Active thread blocks per SM required by the workload. |  |  |

| The registers in the thread block.                    |  |  |

| The registers required for the remaining variables.   |  |  |

| The available number of registers per SM.             |  |  |

|                                                       |  |  |

#### B. Parallelism Constraint of uKernel

**Trade-off with padding & occupancy.** Resource occupancy is a crucial index for parallelism, but the key focus of this subsection is how to select a uKernel with less padding but higher resource occupancy. Our filter algorithm (alg. 1) explores the padding and resource occupancy for each uKernel to provide an equal opportunity. Note that, three functions in alg. 1 are executed sequentially, each returning a uKernel set defined as K.Align, K.Cross, and K.Filter, respectively. We employ the CrossPick algorithm (line 7) to select uKernels (K) with higher parallelism. Tab. II lists the notations used in §IV-B.

Fig. 7. Representing the actual tiling of uKernel at different levels using code. (1-3) shows uKernel tiling across the different levels. This example applies to operators represented by nested loops. The axes space(i,j) and reduce(k) can also represent the loop of the convolution. Such as space(n,k,p,q) and reduce(c,r,s). (1-3) provides four different loop states of uKernel. i.2 and j.2 represent the register tiles, i.1 and j.1 indicate the shared memory tiles, and also represent thread tiles. i.0 and j.0 represent block-level tiles.

$$K.pad = \frac{wkl.base(K)}{wkl.pad(K) + wkl.base(K)}$$

(2)

$$K.occ = \frac{wkl/K}{ceil\_by(wkl/K, NumCores)}$$

(3)

$$K.RegsInBlock \leq \frac{REGS\_PER\_SM}{block.bound}$$

where K.RegsInBlock =(reg\_tile\_{i,j} + RestRegs) × smem\_tile\_{i,j} (4)

The padding\_threshold is calculated by (2). A larger value of K.pad indicates less padding. The usage\_eff is calculated by (3). As each uKernel is assigned to one SM, wkl/K is also related to the number of occupied SMs. K.occ denotes the hardware occupancy ratio of a wkl composed using K.

We set the K.pad to the minimum  $\epsilon_{min}$  and the K.occ to the maximum  $\lambda_{max}$ . We gradually increase  $\epsilon$  and decrease  $\lambda$  by a certain proportion. Although we utilized the same stride size across different GPUs, it is a customizable value. We observed that the  $\epsilon$  (K.pad) and  $\lambda$  (K.occ) of uKernels are generally inversely proportional. Furthermore, there exists a certain proportionality between these factors, which is hardware-dependent. For V100, we set the stride  $\Delta \epsilon : \Delta \lambda$ to 10:1. For instance,  $\epsilon_{min} = 50\%$  increases by 1% and  $\lambda_{max} = 95\%$  decreases by 0.1% at each iteration. The filtering process terminates when either  $\epsilon_{max} = 95\%$  or  $\lambda_{min} = 90\%$ . The "Next()" signifies moving to the next uKernel, while the function "Forward()" indicates the next stride.  $\epsilon_{min,max}$ ,  $\lambda_{min,max}$  and stride size are hyperparameters.

**Parallelism bounds.** Increasing the use of registers in uKernel can improve hardware utilization, but register spillage can lead to severe performance degradation. FTuner sets parallelism bounds to control the number of thread blocks in one SM, as shown in SetBound (line 19). We retain default parameters  $\zeta$  obtained from heuristic search, whose value is 2 on V100. We set the block.bound to the minimum of  $Dev.\zeta$  and K.wkl.block (line 20). This is because, for

| Al   | gorithm 1: Filter Algorithm.                                         |

|------|----------------------------------------------------------------------|

| Iı   | nput: Dynamic Shape Workload                                         |

|      | Putput: uKernel Candidates                                           |

| 1 F  | unc HardwareAlign( <i>shape:wkl.DynShape</i> ,                       |

|      | Dev:device):                                                         |

| 2    | reg_tile = RegTileKernel(Shape);                                     |

| 3    | smem_tile = SmemTileKernel(Shape);                                   |

| 4    | padding_threshold $\in [\epsilon_{min}, \epsilon_{max}];$            |

| 5    | usage_eff $\in [\lambda_{min}, \lambda_{max}];$                      |

| 6    | Return K.Align;                                                      |

|      | unc CrossPick ( <i>K:uKernel, mem:K.MemCapacity</i> ,                |

|      | wkl:Workload):                                                       |

| 8    | foreach K in K.Align do                                              |

| 9    | if mem.IsOverflow() then                                             |

| 10   | Next(K);                                                             |

| 11   | foreach $\epsilon_i, \lambda_j$ do                                   |

| 12   | if $\epsilon_i > \epsilon_{max}$ or $\lambda_j < \lambda_{min}$ then |

| 13   | Next(K);                                                             |

| 14   | if $K.pad \geq \epsilon_i$ and $K.occ \geq \lambda_j$ then           |

| 15   | wkl.Add(K);                                                          |

| 16   | Forward $(\epsilon_i, \lambda_j)$ ;                                  |

| 17   | Next(K);                                                             |

| 18   | Return K.Cross;                                                      |

| 19 F | unc SetBound ( <i>K:uKernel, wkl:Workload, Dev:device</i> ):         |

| 20   | block.bound = $\min(K.wkl.block, Dev.\zeta)$ ;                       |

| 21   | foreach K in K.Cross do                                              |

| 22   | if K.IsInBound() then                                                |

| 23   | wkl.Add(K);                                                          |

| 24   | Return K.Filter;                                                     |

|      |                                                                      |

large workloads, choosing  $Dev.\zeta$  can avoid activating too many blocks, which may lead to register spillage. For small workloads, select K.wkl.block allows for an even distribution of blocks across each SM.  $Dev.\zeta$  denotes the default active thread block per SM in Device. K.wkl.block denotes the active blocks per SM required by the workload using uKernel K.

Next, we examine whether uKernels satisfy the constraints of parallel boundaries. The inequality for registers usage boundary judgment in K.IsInBound() (line 22) is shown in (4). RestRegs represent the registers required for the remaining variables generated during thread computation.

TABLE III Important Notations in §IV-C.

| Notations       | Definition                                             |  |  |

|-----------------|--------------------------------------------------------|--|--|

| $\Phi_{wkl}$    | The size of workload on space axis.                    |  |  |

| $\phi_K$        | The tile size of uKernel on the shared memory.         |  |  |

| Active Blocks   | The total blocks activated across all computing units. |  |  |

| $\psi$          | The threshold of compute-to-memory ratio.              |  |  |

| wkl.FLOPs       | The floating-point operations of workload.             |  |  |

| FLOPS           | The floating-point operations speed of the hardware.   |  |  |

| $K_{mem}$       | Memory access latency of uKernel.                      |  |  |

| $data_R$        | Amount of data read from global memory.                |  |  |

| $data_W$        | Amount of data written to global memory.               |  |  |

| $data_{transW}$ | Amount of data written to shared memory.               |  |  |

| $data_{transR}$ | Amount of data read from shared memory.                |  |  |

| $bw_G$          | Bandwidth of global memory.                            |  |  |

| $bw_S$          | Bandwidth of shared memory.                            |  |  |

#### C. Multi-axis Analysis of uKernel

After the parallelism constraint of uKernel, FTuner needs to confirm two things: 1) whether using this uKernel can saturate the computing resources for the workload, and 2) whether the uKernel is computationally intensive. FTuner selects uKernels that simultaneously satisfy these two conditions. Then, we assess two conditions from space and reduce axes.

**Space axis analysis.** The utilization of computing resources by the workload is determined based on the number of computing units and the number of thread blocks activated in each computing unit. FTuner set (5) to determine whether the uKernel satisfies the saturation condition.

$$\frac{\Phi_{wkl}}{\phi_K} \ge Active \ Blocks \tag{5}$$

$$\left[\frac{wkl.FLOPs}{FLOPS}:K_{mem}\right] \ge \psi \tag{6}$$

$$K_{mem} = max(\frac{data_R}{bw_G} + \frac{data_W}{bw_G}, \frac{data_{transW}}{bw_S} + \frac{data_{transR}}{bw_S})$$

(7)

$\frac{\Phi_{wkl}}{\phi_K}$  represents the number of uKernels composing the workload as shown in Tab. III, and if it satisfies (5), it indicates computational saturation. The Active Blocks are equal to the product of ACTIVE\_BLOCK\_PER\_SM and NumCores. Note that, the V100 has 80 SMs, and when the number of blocks is 81, it leads to poor performance. §IV-B has excluded the "slightly larger than Active Blocks" uKernel through K.occ (3), as we set ACTIVE\_BLOCK\_PER\_SM as 2, indicating that each SM is active with 2 blocks simultaneously. This setting is close to the maximum parallelism, so we don't consider the case with fewer blocks.

**Reduce axis analysis.** FTuner determines whether uKernel is compute-intensive using (6). The part before the inequality represents the compute-to-memory ratio of the uKernel, denoted by compute\_eff. If compute\_eff surpasses the threshold  $\psi$ , it suggests that the uKernel is computation-intensive. The memory access latency of uKernel K.mem is computed by (7).

#### Algorithm 2: Combination Algorithm. Input: uKernel Set after §IV-C Output: uKernel-based Tensor Program **1** Func CombinSearch $(K_{\tau}: K.dim.\tau, H: wkl.dim.\tau)$ : 2 foreach K in uKernel set do if $H \leq 0$ then 3 Next(K) ; 4 if $K_{\tau} \in divisor(H)$ then 5 CombinSet.Add( $K_{\tau}$ ); 6 Next(K); 7 Add uKernel to the combination set. 8 eİse 9 10 CombinSearch( $K_{\tau}, H - = K_{\tau}$ ); 11 Return CombinSet; 12 foreach K in K.Filter do if $K_{\tau} \in divisor(H)$ then 13 $uProg.Add(K_{\tau})$ ; 14 The program is generated by only one uKernel. 15 else 16 CombinSearch(); 17 uProg.Add(CombinSet); 18 19 Return uProg;

#### V. RUNTIME STAGE OF FTUNER

After section IV, we obtained a high-performance uKernels set. Due to the differences in hardware and input shape, the number of uKernels varies from twenty to hundreds.

# A. Program Construction

In this subsection, FTuner aims to find a combination of uKernels to generate programs with minimal padding. For instance, when one axis of shape is a prime number, it is challenging to achieve divisibility with just one size of uKernel. Non-divisibility leads to many boundary checks during memory access, reducing program performance.

To provide more combination options, we select the axis with max size as the main axis  $\tau$  as shown in Tab. IV. Alg. 2 aims to find a uKernel combination that perfectly covers the  $\tau$ -axis. For a problem size H(), there exist two uKernels, denoted as  $K^1$  and  $K^2$ , that can perfectly divide H, resulting in  $H = (Num_1 \times K_{\tau}^1, Num_2 \times K_{\tau}^2)$ . For example, as shown in Fig. 8 **2**, if H=53,  $K_{\tau}^1 = 7$ ,  $K_{\tau}^2 = 8$ , and  $H = (3 \times K_{\tau}^1, 4 \times K_{\tau}^2)$ .  $P_1^1$  is one of the uKernel-based programs found by algorithm **0** for input shape  $S_1$ . As shown in Alg. 14, we do not exclude using tensor programs generated by a single uKernel. We retain uKernels that are divisible by the main axis size H and store their programs in a pool (uProg can see in Fig. 8 **3**).

In the CombinSearch(), we iterate through all uKernels. First, we check if  $K_{\tau}$  is a factor of H (line 5). For example, since  $K_{\tau} = 7$  is not a factor of H=53, we continue searching for the next uKernel that can form 53. In this case, H is reduced by  $K_{\tau}$  in the next search round, making H=46 as shown in line 10. This process continues until we find the perfect division, i.e., H=(7,8), stored in the CombinSet, as shown in line 18. The combination algorithm ensures that programs generated by FTuner require no padding in at least one axis.

Fig. 8. The FTuner at runtime. Combination algorithm  $\mathbf{0}$  generates multiple uKernel-based programs  $P_n$  for each input shape  $S_n$ . In  $\mathbf{0}$ ,  $P_1^1$  is composed of uKernel  $K_{\tau}^1$  and  $K_{\tau}^2$ , which can perfectly divide the main axis of shape  $S_1$ . Each shape has many uKernel-based programs in the program pool  $\mathbf{0}$ . We rank these programs by SIA score in  $\mathbf{0}$ .

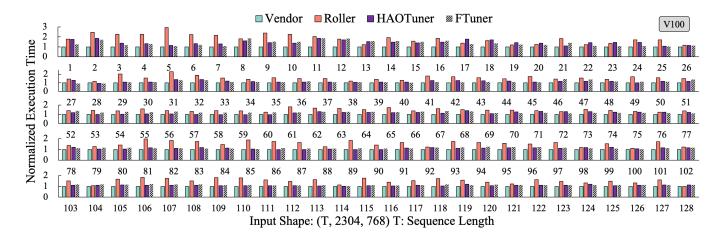

Fig. 9. The execution time of the Dense operator on the V100. The computed definition of Dense is  $C_{i,j} = \sum_k A_{i,k} B_{k,j}$ . The Vendor normalized the values of 128 shapes. FTuner can rival Vendor on 44% of the shapes. FTuner is up to 68% better than Roller when T=5, 23% on average. FTuner outperforms the HAOTuner in 59% of the shapes. FTuner is up to 30% better than HAOTuner when T=27, 0.6% on average.

TABLE IV Important Notations in §V.

| Notations                    | Definition                                                       |  |  |

|------------------------------|------------------------------------------------------------------|--|--|

| $\tau$ , H                   | The maximum axis $\tau$ with size H.                             |  |  |

| $K_{\tau}^{1}, K_{\tau}^{2}$ | The size of uKernel $K^1$ and $K^2$ along the main axis $\tau$ . |  |  |

| divisor(H)                   | The factors set of H.                                            |  |  |

| $P_n^1$                      | The 1st uKernel-based program for input shape $S_n$ .            |  |  |

| CMR, Pad, Occ                | comput_eff, padding_threshold, usage_eff in ukernel.             |  |  |

| $c_s, s = 0, 1, 2$           | The penalty coefficient for the three metrics.                   |  |  |

#### B. Program Evaluation

FTuner will evaluate programs in the uProg using a synthesis index analysis (SIA) to select the best-performing uKernelbased program for workloads of different input shapes. We calculate the SIA score using a weighted sum of three metrics (as shown in (1)): compute-to-memory ratio, padding, and resource utilization. According to the SIA score rank, all uKernel-based programs in the uProg are When calculating the SIA score for a program composed of two uKernels, and we take their average (as shown in Fig. 8 0).

We set coefficients c0=c1=c2=1. Users have the flexibility

to customize these coefficients. Since all the above-mentioned information is cached in the data structure of each uKernel, real-time queries can be performed when calculating the SIA scores. Then, FTuner selects the Top10 tensor programs based on their SIA scores for different input shapes of the workload and compares them with the measurement-on-device results of all programs. §VI-C validates the accuracy of the SIA. Note that FTuner does not require measurement-on-device at runtime. Additionally, during the runtime, the program construction and evaluation time is significantly smaller compared to the inference time (by about three orders of magnitude). Therefore, we include the runtime overhead in the inference time.

Users can modify each coefficient based on the type of operator and model, hardware features, and input tensor shape. For example, users can use NVIDIA's nvprof to determine operators' computation and memory access patterns. If the operator is compute-intensive, the coefficient of CMR can be increased. If the computing resources (obtained by nvidia-smi) of the hardware device are limited, such as embedded devices, the coefficient of Occ can be increased. In summary, even if users do not have guidance, selecting default coefficients can still result in high-performance tensor programs.

# VI. EVALUATION

We compare FTuner with three baselines: 1) Vendor, an operator library (cuBLAS [4] for GPU). cuDNN [5] mainly optimizes convolution operators, and certainly, CUTLASS [6] demonstrates superior performance. Nonetheless, given the extensive number of experiments, we compared it with cuBLAS for convenience rather than manually implementing CUTLASS for each shape. To maintain consistency with the baseline, we did not use Tensor Cores. Tensorization is another work that is orthogonal to FTuner. 2) Roller [18], the most representative fast compiler. 3) HAOTuner [17], the state-of-the-art compiler for dynamic shape, with all evaluated search rounds set to 1000 trials. HAOTuner has a similar technique to DietCode and performs better performance than DietCode.

**Experimental setup.** We evaluated FTuner on five NVIDIA GPUs with different architectures: NVIDIA Tesla K80 (Kepler) and V100 (Volta), GeForce GTX 3090 and A100 (Ampere), and 4090 (Ada Lovelace). All of them used a 32-core Intel Xeon E5-2620 v4 @2.10GHz CPU. We mainly chose K80 and V100 to compare them with a very related work Roller [18]. We used CUDA 11.1 for K80; other devices used CUDA 11.4 and TVM (v0.8) as the software environment configuration.

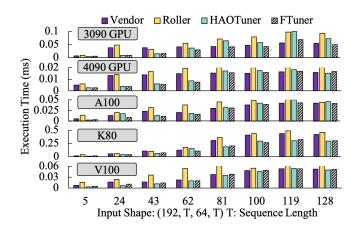

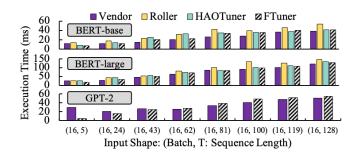

Workload. We evaluated two models, BERT [14] and GPT-2 [27], and two operators of attention [28]. FTuner tune operators that are performance bottlenecks, Dense and BatchMatmul, account for over 90% of the invocations in these two models. For simple element-wise operators like ReLU and element-wise add, FTuner directly handles them using inline functions in PyTorch [29]. The computed definitions of Dense and BatchMatmul are from ONNX [25]. We take the input length range of 1-128 for BERT as the experimental shapes for both single operators and end-to-end models (including GPT-2). We evaluate FTuner from four aspects: 1) Inference time for a single operator and end-to-end models, using Execution Time as the metric. 2) Compilation time. 3) Synthesis index analysis accuracy. 4) Padding and memory access analysis. To comprehensively evaluate the results of FTuner and to maintain consistency with HAOTuner, we evaluate BatchMatmul performance and the total optimization time of the compiler for 8 different shapes.

**Evaluation index.** We present the evaluation results in four ways: 1) For inference time for both operator and end-to-end models, We averaged the values from over one hundred runs in milliseconds (msec). 2) For compilation time, we report the time in seconds (sec). 3) For synthesis index analysis accuracy, we report the performance in GFLOPS. 4) For the padding and memory access analysis, we averaged the padding time in computation from over one hundred runs in milliseconds (msec). The final results are calculated as the average across all devices. Except for the GFLOPS metric, lower is better.

We also experimented with models that include convolution operators. However, due to their relatively fixed shape, these operators were not included in the comparison between HAO-Tuner [17] and DietCode [16]. Therefore, we did not include results for convolutions in this paper.

#### A. Dynamic Shape Tensor Program Performance

**Dense operator.** Fig. 9 shows the execution time of the Dense operator for 128 shapes on the V100. T represents the sequence length, which corresponds to the dynamic axis. Dense has one dynamic axis, while BatchMatmul has two. FTuner supports up to four dynamic axes. FTuner achieves comparable performance (within 10%) on 44% shapes. FTuner is up to 64% better than Roller [18], 23% on average. Only 4% of the shapes are lower than Roller because Roller can achieve strict alignment with hardware in these shapes. FTuner outperforms the HAOTuner [17] in 59% of the shapes.

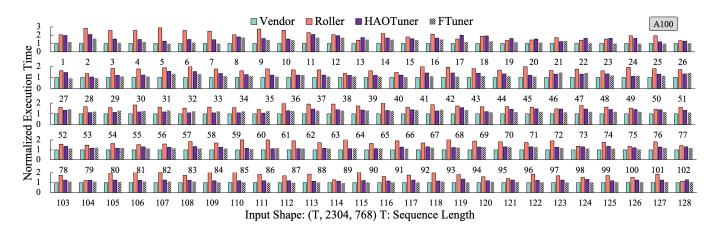

FTuner performs worse than HAOTuner in two intervals. Shapes 8-16 and 52-64 launch fewer blocks, resulting in lower SM utilization and a longer execution time. Users can customize the penalty coefficients in SIA based on scenarios to improve performance on high-frequency shapes. This issue does not exist on the K80 since a single operator cannot fully utilize the entire SM on an ample resources device (V100). We achieved relatively good results on the A100 as shown in Fig. 11. FTuner can achieve up to 66% speedup over Roller when T=5 and can achieve 33% speedup on average. FTuner outperforms the HAOTuner on 98% of the shapes and can get up to 42% speedup over HAOTuner when T=17, 12% on average.

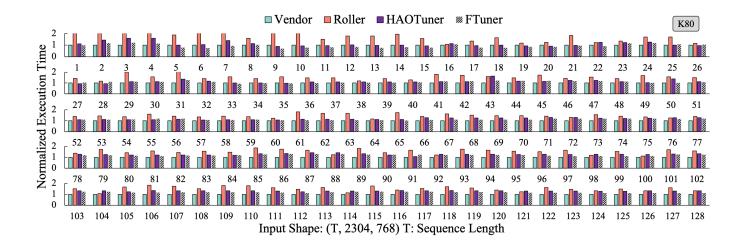

Fig. 10 presents the evaluation of the K80 GPU. Compared with the Vendor, FTuner can achieve comparable performance (within 10%) on 50% of the shapes, outperforming with 33% of them. FTuner outperforms Roller in performance across all shapes. FTuner is up to 70% better than Roller, 28% on average. FTuner outperforms HAOTuner on 88% of the shapes. Due to page limitations, this manuscript does not include the results on the 3090 and 4900 GPUs. Overall, FTuner performs an average of 28% better than Roller in the execution time of the Dense operator. Compared to HAOTuner, the performance fluctuates within 11%.

BatchMatmul operator. To maintain consistency with HAOTuner [17], we sampled 8 shapes starting from 5 with a step of 19. As shown in Fig. 12, FTuner can bring a 21% performance improvement compared to Vendor. FTuner is up to 80% better than Roller [18], 43% on average. FTuner is up to 51% better than HAOTuner, 5% on average. BatchMatmul has one extra axis in the input shape compared to Dense, with three dimensions along the space axis. Therefore, for HAOTuner, more dimensions expand the search space, making it hard for limited trials to find the best result. As the shape increases, the vendor can use larger loop tiles than FTuner and HAOTuner. When the shape is small, manually optimized tiles are difficult to cover. Conversely, as the shape increases, the vendor's performance becomes better. Due to the current version of cuBLAS being incompatible with the early Kepler architecture, the performance of the Vendor on K80 is noticeably inferior to others.

Fig. 10. The execution time of the Dense operator on the K80. The computed definition of Dense is  $C_{i,j} = \sum_k A_{i,k} B_{k,j}$ . The Vendor normalized the values of 128 shapes. FTuner can rival Vendor on 50% of the shapes. FTuner is up to 70% better than Roller when T=9, 28% on average. FTuner outperforms the HAOTuner in 98% of the shapes. FTuner is up to 33% better than HAOTuner when T=7, 8.2% on average.

Fig. 11. The execution time of the Dense operator on the K80. The computed definition of Dense is  $C_{i,j} = \sum_k A_{i,k} B_{k,j}$ . The Vendor normalized the values of 128 shapes. FTuner can rival Vendor on 40% of the shapes. FTuner is up to 66% better than Roller when T=5, 33% on average. FTuner outperforms the HAOTuner in 88% of the shapes. FTuner is up to 42% better than HAOTuner when T=17, 12% on average.

**End-to-end model.** We evaluated the execution time of three different end-to-end networks on the V100. As shown in Fig. 13, on BERT [14], FTuner achieves performance comparable to Vendor (within 8% on average). FTuner is up to 34% better than HAOTuner [17], 11% on average. FTuner is up to 44% better than Roller, 23% on average. Since HAOTuner's auto-scheduling does not support the Dense+biasadd (a fused operator), it would interrupt tuning. Similarly, Roller does not support GPT-2, so we could not measure them. Due to exceeding the maximum protobul size limit (2GB) during its graph loading phase, we could not verify the performance of BERT on TensorRT [30].

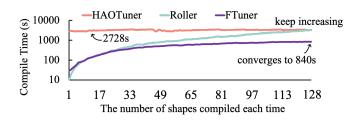

#### B. Compilation Time

We compare the compilation time of FTuner with HAO-Tuner [17] and Roller [18]. To comprehensively evaluate the

TABLE V COMPILATION TIME OF SINGLE OPERATORS AND END-TO-END MODELS FOR 8 INPUT SHAPES ON V100 GPU.

|             | Ansor    | HAOTuner | Roller | FTuner |

|-------------|----------|----------|--------|--------|

| Dense       | 6872s    | 1104s    | 163s   | 149s   |

| BatchMatmul | 13549s   | 2117s    | 272s   | 193s   |

| BERT-base   | 69518s   | 10862s   | 2528s  | 474s   |

| BERT-large  | 103878s  | 16231s   | 3792s  | 645s   |

| GPT-2       | Time-out | _        | _      | 1614s  |

results of FTuner and to maintain consistency with HAOTuner, we evaluate the total optimization time of the compiler for 8 different shapes. As shown in Fig. 14, the compilation time of the Dense across 1 to 128 shapes. For one shape, the compilation time of FTuner is about 37.84s, Roller is 17.26s,

Fig. 12. The execution time of the BatchMatmul. The computed definition of BatchMatmul is  $C_{b,i,j} = \sum_k A_{b,i,k} B_{b,k,j}$ . FTuner average is 21% better than the Vendor, 43% better than Roller, and 5% better than HAOTuner.

Fig. 13. The execution time of the end-to-end models on V100 for 8 shapes. On BERT, FTuner differs from the Vendor's average by within 8%. FTuner performs an average of 23% better than Roller and 11% better than HAOTuner. On GPT-2, FTuner is up to  $5.6 \times$  better than Vendor when T=5, on average can achieve comparable performance. We could not measure HAOTuner and Roller on GPT-2.

Fig. 14. The compilation time. The number of shapes compiled each time increased from 1 to 128, using the Dense operator on V100. FTuner converges to 840s, Roller keeps increasing, and HAOTuner remains high.

Fig. 15. Evaluation of synthesis index analysis (SIA). Using the Dense operator on V100. **SIA can choose programs close to optimal performance at the upper right corner.** The dots represent programs generated by FTuner in uProg. The triangles and squares represent the Top1 and Top10 programs based on SIA scores, respectively.

and HAOTuner is 2728.86s. As the shapes increase, FTuner's compilation time gradually converges to 840s, while Roller continues to expand, and HAOTuner remains unchanged.

As shown in Tab. V, FTuner reduces two orders of magnitude for end-to-end models compared to Ansor [12] and HAOTuner [17]. Compared to Roller [18], FTuner reduces compilation time by one order of magnitude. In BERT-base, Ansor [12] takes about 19.3 hours because Ansor requires recompilation whenever the input shape changes. HAOTuner [17] still needs 3 hours. The Roller is relatively faster and also takes 1.8 hours. FTuner completes the compilation process in only 474s, 645s for BERT-large, and 1614s for GPT-2. In the real world, the shapes of input tensors are arbitrary and far exceed 8. Therefore, the more shapes there are, the more obvious the advantage of FTuner in compilation time.

#### C. Program Evaluation versus Measurement

To verify the accuracy of synthesis index analysis, we conducted measurement-on-device on all programs generated by FTuner. As shown in Fig. 15, we used the SIA score as the horizontal axis and actual program throughput on the vertical axis. The dots represent programs in the program pool. The Top10 SIA are shown as squares, and the triangle represents the Top1. As the throughput increases, the SIA score generally shows an upward trend. However, there are

Fig. 16. The proportion of padding in computation. Dense operator on V100 with 8 shapes. The vendor normalizes padding and access time. We can reduce the proportion of padding in computations to within 15%. Compared to Roller, we have reduced it by up to  $7.12\times$ , with an average reduction of  $4.31\times$ .

inaccuracies in evaluations when the shape is small. Because SIA may not accurately select the highest performance and this evaluation method is simplistic, it cannot fully replace on-device measurement. However, this approach excels in the vast search space of dynamic shapes, allowing us to control performance evaluation errors within 10%.

#### D. Padding and Memory Access Analysis

In this subsection, we analyze the proportion of padding in the computation time. As shown in Fig. 16, we break down the computation time into effective computation (blue blocks) and ineffective computation, which is represented by the padding portion (mesh blocks). Compared to Roller [18], FTuner can reduce padding by an average of  $4.31 \times$ . For shared memory access time, FTuner only exceeds Vendor by 8%. Compared to HAOTuner [17] and Roller [18], it reduces by 25% and 39%, respectively. As for global memory access time, FTuner exceeds Vendor by 14%. Compared to HAOTuner and Roller, it reduces by 11% and 13%, respectively.

We also evaluated the SM utilization using the NVIDIA NCU Tool, as shown in Tab. VI. FTuner is up to 15% better than Vendor, 4% on average. FTuner is up to  $1.2\times$  better than HAOTuner, 35% on average. FTuner is up to 37% better than Roller, 15% on average. This significant improvement in SM utilization is attributed to the multi-axis analysis of input tensors conducted in §IV-C.

#### VII. RELATED WORK

**Deep learning compilers.** Well-featured and widely used deep learning compilers, such as XLA [31], TC [9], TVM [8], MLIR [11], Ansor [12], Alpa [32], and Roller [18], FlexTensor [33], Heron [34], Meta-schedule [35], AMOS [36], Hidet [37], EINNET [38], can achieve excellent tuning results for tensor programs. However, when it comes to dynamic shape, the tuning process may not be implemented efficiently due to

TABLE VI THE SM UTILIZATION ON DENSE OPERATOR.

| Input Shapes     | Vendor | HAOTuner | Roller | FTuner |

|------------------|--------|----------|--------|--------|

| (5, 2304, 768)   | 63.91  | 31.4     | 75.84  | 69.36  |

| (24, 2304, 768)  | 78.21  | 51.87    | 65.78  | 74.69  |

| (43, 2304, 768)  | 89.39  | 71.15    | 60.12  | 82.28  |

| (62, 2304, 768)  | 86.66  | 66.4     | 77.27  | 75.14  |

| (81, 2304, 768)  | 72.71  | 67.05    | 67.51  | 81.49  |

| (100, 2304, 768) | 70.61  | 67.89    | 81.25  | 83.13  |

| (119, 2304, 768) | 73.37  | 65.17    | 58.48  | 79.23  |

| (128, 2304, 768) | 72.74  | 67.03    | 69.42  | 83.3   |

design limitations. BlazerML [39] and [40] Using multiple kernels on the CPU for Conv2D.

Compilers for dynamic shape workloads. Selective tuning [41] groups workloads into clusters based on similarity ratios and applies exact schedules to different shapes. Nimble [42] generates a schedule for the largest shape and applies it to all shapes by loop tiling. DLight [43] is a site package under development for dynamic shapes in the TVM community. DISC [44] builds a compiler based on MLIR [11] but increases the memory footprint by introducing an offline compilation warmup. CoRa [45] introduces a new set of scheduling primitives for dynamic shapes and uses uninterpreted functions [46] to symbolically represent variable loop bounds and scheduling operations. DISC [44] and CoRa [45] do not support autotuning. MikPoly [47] constructs optimized programs for any shape on the fly by dividing the generation of micro-kernels into online and offline stages, but it still requires training in a cost model. Therefore, FTuner and MikPoly differ significantly in tuning time, and because MikPoly does not have opensource code, we cannot compare them.

Learning-based cost model. TenSet [48], Moses [49], TLP [50] propose MLP-based pre-trained cost models for tensor compilers, but they require a public multi-platform dataset. In addition to supervised learning approaches, there are re-inforcement learning approaches for compiler optimizations, such as Chameleon [21] and Neurovectorizer [51]. TensorIR [52] is an intermediate representation that supports dynamic shapes. However, extensive measurement-on-device is required to obtain training data for the cost model.

#### VIII. CONCLUSION

This paper introduces a fast dynamic shape auto-tuning compiler FTuner, which improves performance and reduces tuning time. FTuner utilizes an abstract computing unit called uKernel to compose dynamic shape tensors. It improves program performance by minimizing padding and provides a synthesis index analysis without a training cost model. FTuner outperforms other deep learning compilers in performance and tuning time. FTuner is portable, so we have adapted it to the Ascend architecture. When deploying to different hardware architectures, only the hardware description script needs to be provided, including memory bandwidth at different hierarchies, hardware core frequency, and number of hardware cores. In the future, we plan to refine CodeGen to support a broader backend. Additionally, as FTuner currently relies on numerous hyperparameters, we will explore an adaptive approach.

#### REFERENCES

- [1] Aditya Ramesh, Mikhail Pavlov, Gabriel Goh, Scott Gray, Chelsea Voss, Alec Radford, Mark Chen, and Ilya Sutskever. Zero-shot text-to-image generation. In Marina Meila and Tong Zhang, editors, Proceedings of the 38th International Conference on Machine Learning, ICML 2021, 18-24 July 2021, Virtual Event, volume 139 of Proceedings of Machine Learning Research, pages 8821–8831. PMLR, 2021.

- [2] Long Ouyang, Jeffrey Wu, Xu Jiang, Diogo Almeida, Carroll L. Wainwright, Pamela Mishkin, Chong Zhang, Sandhini Agarwal, Katarina Slama, Alex Ray, John Schulman, Jacob Hilton, Fraser Kelton, Luke Miller, Maddie Simens, Amanda Askell, Peter Welinder, Paul F. Christiano, Jan Leike, and Ryan Lowe. Training language models to follow instructions with human feedback. In *NeurIPS*, 2022.

- [3] Xueyan Zou, Jianwei Yang, Hao Zhang, Feng Li, Linjie Li, Jianfeng Gao, and Yong Jae Lee. Segment everything everywhere all at once. *CoRR*, abs/2304.06718, 2023.

- [4] NVIDIA. cublas: Cuda basic linear algebra subroutine library. https://developer.nvidia.com/cublas, 2021.

- [5] Sharan Chetlur, Cliff Woolley, Philippe Vandermersch, Jonathan Cohen, John Tran, Bryan Catanzaro, and Evan Shelhamer. cudnn: Efficient primitives for deep learning. https://developer.nvidia.com/cudnn, 2014.

- [6] NVIDIA. Cutlass: Cuda templates for linear algebra subroutines. https://github.com/NVIDIA/cutlass, 2022.

- [7] Intel. oneapi deep neural network library (onednn). https://github.com/oneapi-src/oneDNN, 2021.

- [8] Tianqi Chen, Thierry Moreau, Ziheng Jiang, Lianmin Zheng, Eddie Q. Yan, Haichen Shen, Meghan Cowan, Leyuan Wang, Yuwei Hu, Luis Ceze, Carlos Guestrin, and Arvind Krishnamurthy. TVM: an automated end-to-end optimizing compiler for deep learning. In Andrea C. Arpaci-Dusseau and Geoff Voelker, editors, 13th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2018, Carlsbad, CA, USA, October 8-10, 2018, pages 578–594. USENIX Association, 2018.

- [9] Nicolas Vasilache, Oleksandr Zinenko, Theodoros Theodoridis, Priya Goyal, Zachary DeVito, William S. Moses, Sven Verdoolaege, Andrew Adams, and Albert Cohen. The next 700 accelerated layers: From mathematical expressions of network computation graphs to accelerated GPU kernels, automatically. ACM Trans. Archit. Code Optim., 16(4):38:1– 38:26, 2020.

- [10] Andrew Adams, Karima Ma, Luke Anderson, Riyadh Baghdadi, Tzu-Mao Li, Michaël Gharbi, Benoit Steiner, Steven Johnson, Kayvon Fatahalian, Frédo Durand, and Jonathan Ragan-Kelley. Learning to optimize halide with tree search and random programs. *ACM Trans. Graph.*, 38(4):121:1–121:12, 2019.

- [11] Chris Lattner, Mehdi Amini, Uday Bondhugula, Albert Cohen, Andy Davis, Jacques A. Pienaar, River Riddle, Tatiana Shpeisman, Nicolas Vasilache, and Oleksandr Zinenko. MLIR: scaling compiler infrastructure for domain specific computation. In Jae W. Lee, Mary Lou Soffa, and Ayal Zaks, editors, IEEE/ACM International Symposium on Code Generation and Optimization, CGO 2021, Seoul, South Korea, February 27 - March 3, 2021, pages 2–14. IEEE, 2021.

- [12] Lianmin Zheng, Chengfan Jia, Minmin Sun, Zhao Wu, Cody Hao Yu, Ameer Haj-Ali, Yida Wang, Jun Yang, Danyang Zhuo, Koushik Sen, Joseph E. Gonzalez, and Ion Stoica. Ansor: Generating highperformance tensor programs for deep learning. In 14th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2020, Virtual Event, November 4-6, 2020, pages 863–879. USENIX Association, 2020.

- [13] Aäron van den Oord, Sander Dieleman, Heiga Zen, Karen Simonyan, Oriol Vinyals, Alex Graves, Nal Kalchbrenner, Andrew W. Senior, and Koray Kavukcuoglu. Wavenet: A generative model for raw audio. In *The 9th ISCA Speech Synthesis Workshop, Sunnyvale, CA, USA, 13-15 September 2016*, page 125. ISCA, 2016.

- [14] Jacob Devlin, Ming-Wei Chang, Kenton Lee, and Kristina Toutanova. BERT: pre-training of deep bidirectional transformers for language understanding. In Jill Burstein, Christy Doran, and Thamar Solorio, editors, Proceedings of the 2019 Conference of the North American Chapter

of the Association for Computational Linguistics: Human Language Technologies, NAACL-HLT 2019, Minneapolis, MN, USA, June 2-7, 2019, Volume 1 (Long and Short Papers), pages 4171–4186. Association for Computational Linguistics, 2019.

- [15] Alex Wang, Amanpreet Singh, Julian Michael, Felix Hill, Omer Levy, and Samuel R. Bowman. GLUE: A multi-task benchmark and analysis platform for natural language understanding. In 7th International Conference on Learning Representations, ICLR 2019, New Orleans, LA, USA, May 6-9, 2019. OpenReview.net, 2019.

- [16] Bojian Zheng, Ziheng Jiang, Cody Hao Yu, Haichen Shen, Joshua Fromm, Yizhi Liu, Yida Wang, Luis Ceze, Tianqi Chen, and Gennady Pekhimenko. Dietcode: Automatic optimization for dynamic tensor programs. In Diana Marculescu, Yuejie Chi, and Carole-Jean Wu, editors, Proceedings of Machine Learning and Systems 2022, MLSys 2022, Santa Clara, CA, USA, August 29 September 1, 2022. mlsys.org, 2022.

- [17] Pengyu Mu, Yi Liu, Rui Wang, Guoxiang Liu, Zhonghao Sun, Hailong Yang, Zhongzhi Luan, and Depei Qian. Haotuner: A hardware adaptive operator auto-tuner for dynamic shape tensor compilers. *IEEE Transactions on Computers*, 72(11):3178–3190, 2023.

- [18] Hongyu Zhu, Ruofan Wu, Yijia Diao, Shanbin Ke, Haoyu Li, Chen Zhang, Jilong Xue, Lingxiao Ma, Yuqing Xia, Wei Cui, Fan Yang, Mao Yang, Lidong Zhou, Asaf Cidon, and Gennady Pekhimenko. ROLLER: Fast and efficient tensor compilation for deep learning. In 16th USENIX Symposium on Operating Systems Design and Implementation (OSDI 22), pages 233–248, Carlsbad, CA, July 2022. USENIX Association.

- [19] NVIDIA. Nsight compute cli. https://docs.nvidia.com/nsightcompute/NsightComputeCli/, 2023.

- [20] Tianqi Chen and Carlos Guestrin. Xgboost: A scalable tree boosting system. In Balaji Krishnapuram, Mohak Shah, Alexander J. Smola, Charu C. Aggarwal, Dou Shen, and Rajeev Rastogi, editors, Proceedings of the 22nd ACM SIGKDD International Conference on Knowledge Discovery and Data Mining, San Francisco, CA, USA, August 13-17, 2016, pages 785–794. ACM, 2016.

- [21] Byung Hoon Ahn, Prannoy Pilligundla, Amir Yazdanbakhsh, and Hadi Esmaeilzadeh. Chameleon: Adaptive code optimization for expedited deep neural network compilation. In 8th International Conference on Learning Representations, ICLR 2020, Addis Ababa, Ethiopia, April 26-30, 2020. OpenReview.net, 2020.

- [22] Menghao Li, Minjia Zhang, Chi Wang, and Mingqin Li. Adatune: Adaptive tensor program compilation made efficient. In Hugo Larochelle, Marc'Aurelio Ranzato, Raia Hadsell, Maria-Florina Balcan, and Hsuan-Tien Lin, editors, Advances in Neural Information Processing Systems 33: Annual Conference on Neural Information Processing Systems 2020, NeurIPS 2020, December 6-12, 2020, virtual, 2020.

- [23] S. Kirkpatrick, C. D. Gelatt, and M. P. Vecchi. Optimization by simulated annealing. In *none*, volume 220, pages 671–680, 1983.

- [24] Pradnya A. Vikhar. Evolutionary algorithms: A critical review and its future prospects. In 2016 International Conference on Global Trends in Signal Processing, Information Computing and Communication (ICGT-SPICC), pages 261–265, 2016.

- [25] Ke Zhang Junjie Bai, Fang Lu. Onnx: open neural network exchange. https://onnx.ai/, 2019.

- [26] Jared Roesch, Steven Lyubomirsky, Marisa Kirisame, Josh Pollock, Logan Weber, Ziheng Jiang, Tianqi Chen, Thierry Moreau, and Zachary Tatlock. Relay: A high-level IR for deep learning. *CoRR*, abs/1904.08368, 2019.

- [27] Alec Radford, Jeffrey Wu, Rewon Child, David Luan, Dario Amodei, Ilya Sutskever, et al. Language models are unsupervised multitask learners. *OpenAI blog*, 1(8):9, 2019.

- [28] Ashish Vaswani, Noam Shazeer, Niki Parmar, Jakob Uszkoreit, Llion Jones, Aidan N. Gomez, Lukasz Kaiser, and Illia Polosukhin. Attention is all you need. In Isabelle Guyon, Ulrike von Luxburg, Samy Bengio, Hanna M. Wallach, Rob Fergus, S. V. N. Vishwanathan, and Roman Garnett, editors, Advances in Neural Information Processing Systems 30: Annual Conference on Neural Information Processing Systems 2017, December 4-9, 2017, Long Beach, CA, USA, pages 5998–6008, 2017.

- [29] PyTorch Team. The nested tensor package prototype. https://github.com/pytorch/nestedtensor, 2022.

- [30] NVIDIA. Tensorrt: Inference accelerator for deep learning. https://developer.nvidia.com/tensorrt, 2021.

- [31] Chris Leary and Todd Wang. Xla: Tensorflow, compiled. tensorflow dev summit (2017). https://www.tensorflow.org/xla, 2017.

- [32] Lianmin Zheng, Zhuohan Li, Hao Zhang, Yonghao Zhuang, Zhifeng Chen, Yanping Huang, Yida Wang, Yuanzhong Xu, Danyang Zhuo, Eric P. Xing, Joseph E. Gonzalez, and Ion Stoica. Alpa: Automating inter- and intra-operator parallelism for distributed deep learning. In Marcos K. Aguilera and Hakim Weatherspoon, editors, 16th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2022, Carlsbad, CA, USA, July 11-13, 2022, pages 559–578. USENIX Association, 2022.

- [33] Size Zheng, Yun Liang, Shuo Wang, Renze Chen, and Kaiwen Sheng. Flextensor: An automatic schedule exploration and optimization framework for tensor computation on heterogeneous system. In James R. Larus, Luis Ceze, and Karin Strauss, editors, ASPLOS '20: Architectural Support for Programming Languages and Operating Systems, Lausanne, Switzerland, March 16-20, 2020, pages 859–873. ACM, 2020.

- [34] Jun Bi, Qi Guo, Xiaqing Li, Yongwei Zhao, Yuanbo Wen, Yuxuan Guo, Enshuai Zhou, Xing Hu, Zidong Du, Ling Li, Huaping Chen, and Tianshi Chen. Heron: Automatically constrained high-performance library generation for deep learning accelerators. In Tor M. Aamodt, Natalie D. Enright Jerger, and Michael M. Swift, editors, Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3, ASPLOS 2023, Vancouver, BC, Canada, March 25-29, 2023, pages 314–328. ACM, 2023.

- [35] Junru Shao, Xiyou Zhou, Siyuan Feng, Bohan Hou, Ruihang Lai, Hongyi Jin, Wuwei Lin, Masahiro Masuda, Cody Hao Yu, and Tianqi Chen. Tensor program optimization with probabilistic programs. In Sanmi Koyejo, S. Mohamed, A. Agarwal, Danielle Belgrave, K. Cho, and A. Oh, editors, Advances in Neural Information Processing Systems 35: Annual Conference on Neural Information Processing Systems 2022, NeurIPS 2022, New Orleans, LA, USA, November 28 - December 9, 2022, 2022.

- [36] Size Zheng, Renze Chen, Anjiang Wei, Yicheng Jin, Qin Han, Liqiang Lu, Bingyang Wu, Xiuhong Li, Shengen Yan, and Yun Liang. AMOS: enabling automatic mapping for tensor computations on spatial accelerators with hardware abstraction. In Valentina Salapura, Mohamed Zahran, Fred Chong, and Lingjia Tang, editors, ISCA '22: The 49th Annual International Symposium on Computer Architecture, New York, New York, USA, June 18 - 22, 2022, pages 874–887. ACM, 2022.

- [37] Yaoyao Ding, Cody Hao Yu, Bojian Zheng, Yizhi Liu, Yida Wang, and Gennady Pekhimenko. Hidet: Task-mapping programming paradigm for deep learning tensor programs. In Tor M. Aamodt, Natalie D. Enright Jerger, and Michael M. Swift, editors, Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, ASPLOS 2023, Vancouver, BC, Canada, March 25-29, 2023, pages 370–384. ACM, 2023.

- [38] Liyan Zheng, Haojie Wang, Jidong Zhai, Muyan Hu, Zixuan Ma, Tuowei Wang, Shuhong Huang, Xupeng Miao, Shizhi Tang, Kezhao Huang, and Zhihao Jia. EINNET: optimizing tensor programs with derivation-based transformations. In Roxana Geambasu and Ed Nightingale, editors, 17th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2023, Boston, MA, USA, July 10-12, 2023, pages 739–755. USENIX Association, 2023.

- [39] Tencent. Blazerml. https://github.com/Tencent/BlazerML-tvm, 2023.

- [40] Nicolas Tollenaere, Guillaume Iooss, Stéphane Pouget, Hugo Brunie, Christophe Guillon, Albert Cohen, P. Sadayappan, and Fabrice Rastello. Autotuning convolutions is easier than you think. ACM Trans. Archit. Code Optim., 20(2):20:1–20:24, 2023.

- [41] Cody Yu. Slective tuning. https://github.com/apache/tvm/pull/4187, 2019.

- [42] Haichen Shen, Jared Roesch, Zhi Chen, Wei Chen, Yong Wu, Mu Li, Vin Sharma, Zachary Tatlock, and Yida Wang. Nimble: Efficiently compiling dynamic neural networks for model inference. In Alex Smola, Alex Dimakis, and Ion Stoica, editors, *Proceedings of Machine Learning and Systems 2021*, MLSys 2021, virtual, April 5-9, 2021. mlsys.org, 2021.

- [43] TVM. Dlight. https://discuss.tvm.apache.org/t/dlight-enabling-fast-andefficient-kernel-generation-by-hardware-information/16273, 2024.

- [44] Kai Zhu, Wenyi Zhao, Zhen Zheng, Tianyou Guo, Pengzhan Zhao, Junjie Bai, Jun Yang, Xiaoyong Liu, Lansong Diao, and Wei Lin. DISC: A dynamic shape compiler for machine learning workloads. In Eiko Yoneki and Paul Patras, editors, EuroMLSys@EuroSys 2021, Proceedings of the 1st Workshop on Machine Learning and Systemsg Virtual Event, Edinburgh, Scotland, UK, 26 April, 2021, pages 89–95. ACM, 2021.

- [45] Pratik Fegade, Tianqi Chen, Phillip B. Gibbons, and Todd C. Mowry. The cora tensor compiler: Compilation for ragged tensors with minimal

padding. In Diana Marculescu, Yuejie Chi, and Carole-Jean Wu, editors, Proceedings of Machine Learning and Systems 2022, MLSys 2022, Santa Clara, CA, USA, August 29 - September 1, 2022. mlsys.org, 2022.

- [46] Michelle Mills Strout, Mary W. Hall, and Catherine Olschanowsky. The sparse polyhedral framework: Composing compiler-generated inspectorexecutor code. *Proc. IEEE*, 106(11):1921–1934, 2018.

- [47] Feng Yu, Guangli Li, Jiacheng Zhao, Huimin Cui, Xiaobing Feng, and Jingling Xue. Optimizing dynamic-shape neural networks on accelerators via on-the-fly micro-kernel polymerization. In Rajiv Gupta, Nael B. Abu-Ghazaleh, Madan Musuvathi, and Dan Tsafrir, editors, Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, ASPLOS 2024, La Jolla, CA, USA, 27 April 2024- 1 May 2024, pages 797–812. ACM, 2024.

- [48] Lianmin Zheng, Ruochen Liu, Junru Shao, Tianqi Chen, Joseph Gonzalez, Ion Stoica, and Ameer Haj-Ali. Tenset: A large-scale program performance dataset for learned tensor compilers. In Joaquin Vanschoren and Sai-Kit Yeung, editors, Proceedings of the Neural Information Processing Systems Track on Datasets and Benchmarks 1, NeurIPS Datasets and Benchmarks 2021, December 2021, virtual, 2021.

- [49] Zhihe Zhao, Xian Shuai, Yang Bai, Neiwen Ling, Nan Guan, Zhenyu Yan, and Guoliang Xing. Moses: Efficient exploitation of crossdevice transferable features for tensor program optimization. *CoRR*, abs/2201.05752, 2022.

- [50] Yi Zhai, Yu Zhang, Shuo Liu, Xiaomeng Chu, Jie Peng, Jianmin Ji, and Yanyong Zhang. TLP: A deep learning-based cost model for tensor program tuning. In Tor M. Aamodt, Natalie D. Enright Jerger, and Michael M. Swift, editors, Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, ASPLOS 2023, Vancouver, BC, Canada, March 25-29, 2023, pages 833–845. ACM, 2023.

- [51] Ameer Haj-Ali, Nesreen K. Ahmed, Theodore L. Willke, Yakun Sophia Shao, Krste Asanovic, and Ion Stoica. Neurovectorizer: end-to-end vectorization with deep reinforcement learning. In CGO '20: 18th ACM/IEEE International Symposium on Code Generation and Optimization, San Diego, CA, USA, February, 2020, pages 242–255. ACM, 2020.

- [52] Siyuan Feng, Bohan Hou, Hongyi Jin, Wuwei Lin, Junru Shao, Ruihang Lai, Zihao Ye, Lianmin Zheng, Cody Hao Yu, Yong Yu, and Tianqi Chen. Tensorir: An abstraction for automatic tensorized program optimization. In Tor M. Aamodt, Natalie D. Enright Jerger, and Michael M. Swift, editors, Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, ASPLOS 2023, Vancouver, BC, Canada, March 25-29, 2023, pages 804–817. ACM, 2023.