# Accelerator-as-a-Service in Public Clouds: An Intra-Host Traffic Management View for Performance Isolation in the Wild

Jiechen Zhao<sup>♥</sup>, Ran Shu<sup>♣</sup>, Katie Lim<sup>♠</sup>, Zewen Fan<sup>◊</sup>,

Thomas Anderson♠, Mingyu Gao◊, Natalie Enright Jerger♥

\* University of Toronto, \* Microsoft Research, \* University of Washington, \* Tsinghua University

# ABSTRACT

I/O devices in public clouds have integrated increasing numbers of hardware accelerators, e.g., AWS Nitro, Azure FPGA and Nvidia BlueField. However, such specialized compute (1) is not explicitly accessible to cloud users with performance guarantee, (2) cannot be leveraged simultaneously by both providers and users, unlike general-purpose compute (e.g., CPUs). Through ten observations, we present that the fundamental difficulty of democratizing accelerators is insufficient performance isolation support. The key obstacles to enforcing accelerator isolation are (1) too many unknown traffic patterns in public clouds and (2) too many possible contention sources in the datapath. In this work, instead of scheduling such complex traffic on-the-fly and augmenting isolation support on each system component, we propose to model traffic as network flows and proactively re-shape the traffic to avoid unpredictable contention. We discuss the implications of our findings on the design of future I/O management stacks and device interfaces.

# **1** INTRODUCTION

To serve the growing demand for online software services [22], CPU efficiency is increasingly crucial due to stagnating performance [25]. Cloud providers have found that some common tasks, such as encryption, compression, and hashing, can consume up to 82% CPU cycles [30–32, 58]. To save CPU cycles and improve overall application throughput, clouds have started to leverage *hardware acceleration* [20, 26, 32, 38, 59, 61] to offload those auxiliary tasks. Fortunately, a diversity of bespoke silicon units already exist in PCIe-attached I/O devices for providers to use [3, 6, 7, 13, 14, 27].

Meanwhile, *users* of public clouds also suffer from a similar low-efficiency problem. For example, users need their own cryptography operations for confidentiality [8], which slows down up to  $4,000 \times$  if CPUs rather than accelerators execute the homomorphic encryption algorithm [55]. However, existing cloud accelerators accessible to *users* do not support performance guarantees [5]. In addition, some accelerators can be needed by both *users* and *providers*. Unfortunately, they currently cannot be leveraged simultaneously by the two parties, unlike general-purpose compute (e.g., CPUs). **Design goals.** In this paper, we aim to provide accelerators on diverse devices *as a service* to the users in the public cloud, allowing users to specify requirements in the same way they can specify how many CPU cores to rent. Our proposal addresses ① how accelerators can be used under a *diversity* of scenarios (network, storage, security, etc.) on various I/O paths and ② how providers and multiple users can *simultaneously* use each accelerator (when available) with *end-to-end performance isolation*.

**Relevant techniques.** Although no current proposals support both design goals, there are some techniques that support multi-tenancy I/Os for bandwidth allocation, and some techniques for leveraging I/O accelerators on NICs or storage devices. Unfortunately, some multi-tenancy proposals for I/O bandwidth need detailed tenant request information [35, 36, 46, 63], which is not available in the public cloud. Some fail to satisfy diverse scenarios because they tightly couple accelerators within only network or storage I/O paths and consider only simple traffic patterns [23, 24, 29, 39, 42, 44, 52]. Others allow accelerator sharing but fail to offer service-level agreements (SLAs) [29, 42, 44]. Finally, no proposals take the characteristics of accelerators themselves into account.

**Understanding isolation breakage.** Table 1 shows the end-to-end accelerator throughput ratios on three devices. In each test, two co-located tenants with the same priority invoke an accelerator under various traffic patterns. Instead of equal allocation (i.e., ratio=1), we find performance variability widely exists on different accelerators.

The fundamental challenges for performance isolation are twofold. First, traffic patterns are too diverse to manage. Even though an individual tenant is unlikely to be problematic, unpredictable contention still can happen depending on what traffic it is co-located with<sup>1</sup>. Worse, such mixed patterns are unknown a priori in the public cloud. Second, multiple possible contention sources on I/O datapath<sup>2</sup> can become the bottleneck and lead to isolation breakage. Accelerator

<sup>&</sup>lt;sup>1</sup>Unless specified, the "traffic pattern" in this paper refers to the mixed pattern of all tenants rather than that of an individual tenant's traffic. <sup>2</sup>System components on those paths include: ① host CPU, ② host network

<sup>(</sup>e.g., root complex, PCIe interconnects), 3 accelerator-side interface (e.g., buffers, queues, schedulers), and 4 heterogeneous accelerators themselves.

Table 1: Case studies: unpredictable acceleratorthroughput allocation ratios.

| Device                 | Acc. Type   | Thr. Ratio        |

|------------------------|-------------|-------------------|

| Intel QuickAssist ASIC | Compression | $0.5-5.1 \times$  |

| Nvidia BlueField-2     | RegEx       | $0.31-6.5 \times$ |

| Xilinx Alveo U250 FPGA | Hashing     | $0.25-8.4 \times$ |

I/O operations can also contend with other legacy I/O operations such as those from network and storage. Removing all possible contention sources may be possible but would be complex.

In Sec. 3, we break down potential contention sources in diverse I/O paths and then analyze them under various multitenant traffic patterns. Based on our observations, the root causes of the results in Table 1 are ① the limited low-level isolation mechanisms of components on those paths (e.g., tenants' traffic not isolated across PCIe lanes but allocated by credits), and ② not taking computational heterogeneity and non-linearity<sup>3</sup> of accelerators into account.

Our proposal: traffic shaping. Instead of improving percomponent isolation mechanisms by re-designing CPU boards and devices, we treat accelerator-related I/O as traffic flows and perform accurate traffic shaping. This idea is inspired by the effectiveness of per-NIC traffic shaping in datacenter networks for isolation enforcement and traffic management [18, 19, 37, 51]. We consider the untrusted accelerator I/O flows transferring within a server through insufficiently isolated infrastructure as similar to the datacenter network setting. Therefore, our traffic shaping approach is well-suited to addressing multi-tenancy isolation problems within a heterogeneous server architecture. We propose a system-level accelerator management stack that offers a decoupled management interface for accelerators. We discuss the feasibility of where and how to perform traffic shaping (Sec. 4), as well as other open problems (Sec. 5).

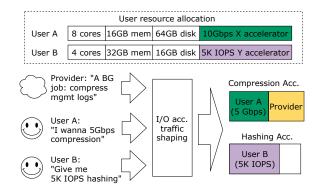

Acceleration service enabled by our proposal. Fig. 1 shows how this feature works. Users can directly request the type and throughput of accelerators, just like the existing ability to request the number of cores. For a given accelerator, we allow multiple users and the provider to take full advantage of it, without worrying about performance isolation breakage (e.g., compression accelerator in Fig. 1). Because our traffic shaping approach takes flow characteristics into account (e.g., message sizes and rates), we enable users to request either based on Gbps or IOPS (similar as the storage

Figure 1: New services empowered by our proposal.

performance business model in today's clouds [9]). Thus, users in multiple scenarios can safely invoke this service.

Note that our paper targets the infrastructure-as-a-service (IaaS) model for accelerators. We assume the cloud provider is trusted. All accelerators are offered and managed by the provider. Tenant users cannot program the accelerators. VM users are untrusted in terms of how much accelerator traffic they invoke.

### 2 BACKGROUND

**Benefits of I/O accelerators in public clouds.** Existing cloud infrastructures are embracing supports for accelerators, such as AWS Nitro [7], Azure FPGA [26] and Alibaba Cloud CIPU [4]. This trend is driven by the higher overall throughput and improved system efficiency benefited from accelerators. For instance, it is possible to offload 3-15% of CPU cycles by using (de)compression accelerators [32]. Other work has shown that an IPSec accelerator offering 32Gbps throughput [42] dramatically outperforms CPUs, which can only deliver 10Gbps while consuming as many as 8 Xeon cores. In addition, a homomorphic encryption accelerator allows a user to exchange data with an untrusted server 4,000× faster than a CPU [55].

In the future, we expect accelerators to be even more prevalent. Their growing importance can be seen from the increasing numbers and types of accelerators from the first to the third generation Nvidia BlueField DPUs [3]. Similarly, the Pensando Elba chip devotes significant die area for specialized processing engines and components [34].

**CPU-accelerator protocol.** The most commonly used protocol between the host and high-performance devices (e.g., NICs, SSDs, and accelerators) is based on the ring buffer abstraction, a *producer-consumer protocol* [10, 11, 38, 47]. The device and host software communicate by exchanging descriptors. On the device side, multiple hardware I/O queue

<sup>&</sup>lt;sup>3</sup>Non-linearity means accelerators I/O operations are not "channels" like read/write I/O or send/receive I/O that exhibit linearity, e.g., equal egress/ingress bandwidth requirements, and larger bandwidth can be linearly allocated for larger messages [24, 29, 42, 44, 46].

Accelerator-as-a-Service in Public Clouds: An Intra-Host Traffic Management View for Performance Isolation in the Wild

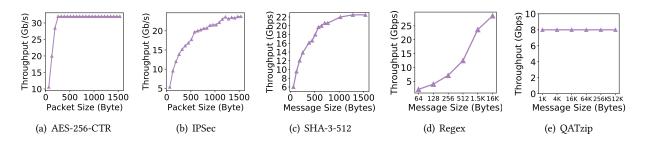

Figure 2: Accelerator profiling: compute throughput across message sizes.

pairs (QPs) are used to maximize bandwidth utilization. Each QP (submission queues (SQs) and completion queues (CQs)) is associated with a set of doorbell registers addressable via host-side load/store instructions and mapped to the physical memory address space. The host side pre-allocates DMA buffers and descriptor ring buffers for each hardware queue.

This process involves: ① The host sends a notification to ring the doorbell register of a particular hardware queue. Then ② the device uses DMA to read pre-prepared descriptors from the corresponding SQ ring buffer, ③ reads data for the accelerator from the appropriate DMA buffer, and finally, ④ updates the CQ ring buffer pointer using a DMA write.

# 3 EMBRACING ACCELERATORS: ISOLATION PROBLEMS IN THE WILD

This section understands the performance isolation problem for accelerators. After describing the methodologies (Sec. 3.1), this paper studies the components involved on accelerator paths and analyze the results regarding computation (Sec. 3.2) and communications (Sec. 3.3). Further breakdown analysis are given in Sec. 3.4.

## 3.1 Methodology

Since available commercial devices lack of sufficient visibility for multi-tenancy study, we set up hybrid testbeds. We separately study the characteristics of components along I/O paths, including accelerators (Sec. 3.2), and the host network (e.g., root complex, PCIe interconnects) and device-side interface (e.g., hardware QPs, on-device buffers) (Sec. 3.3-3.4).

**Accelerators.** We build a sub-system on an Intel Arria 10 FPGA. A traffic generator feeds messages into a 256KB data buffer unless the buffer is full. The accelerator pulls the next request from the data buffer before the current computation finishes. The pulling is in FIFO order. These results are analyzed in Sec. 3.2.

**Commercial devices.** Besides accelerators' computational characteristics, we also need to study the contention impacts of certain traffic patterns on the device interface and the host

networks. We choose one commodity NIC for characterizations due to the following reasons. First, host-NIC systems have already established mature software and hardware support for optimized host-device communications. Second, this testbed exhbits representative datapaths for accelerator invocations. This is because leveraging the NIC corroborates with prior work which reuses the NIC interface for accelerator invocations [23, 24, 29, 35, 42].

Specifically, the host has dual 16-core Intel Xeon E5 2698v3 CPU sockets and 256GB RAM, running Ubuntu 18.04 with Linux kernel version 4.17.12 installed. We attach one Mellanox ConnectX-6 card to this server and use its one 100Gbps port. To prevent the contention impacts from host resource contention (e.g., shared caches, memory controllers, and memory channels) from affecting our contention study, we run each tenant on a separate NUMA node.

Each tenant sends arbitrary sizes of intra-host RDMA reads or RDMA writes, which invoke host-device round trips based on the ring buffer protocol described in Sec. 2. Writes and reads of RDMA represent individual traffic in this round trip, i.e., device-to-host heavy and host-to-device heavy respectively. We set the same priority for both tenants. Each test runs for 10 minutes, and observations are in Sec. 3.3.

**Host-FPGA prototype.** Given the difficulties of changing low-level details within commercial devices, we create a host-FPGA prototype to further break down our analysis in Sec. 3.4. By customizing the driver on the host and the FPGA as the I/O device, we build an end-to-end system with better observability on each component from tenant processes running on the host to an accelerator. Moreover, we can mitigate some factors in the prototype to give further insights for device vendors (as accelerator designers) and cloud providers (as accelerator managers).<sup>4</sup> We use an Intel Arria 10 FPGA connected to the CPU host above via a PCIe root complex with a PCIe Gen 3.0 x8 interface. Each test runs 1 million commands and results are presented in Sec. 3.4.

<sup>&</sup>lt;sup>4</sup>We expect that there will be a hybrid model where providers may customize their devices, and meanwhile they buy third-party devices from vendors.

#### 3.2 Computational Characteristics

We emphasize two **features that have been overlooked** by previous studies on multi-tenant accelerators.

**Observation 1: Message size matters.** Fig. 2 shows the unique (non-linear) relations between each accelerator's compute throughput and its input data sizes. We point out that accelerators usually cannot deliver throughput linear to the data granularity they are fed, unlike network link bandwidth allocation.<sup>5</sup> Instead, such a trend is ad-hoc for each accelerator type.

**Observation 2: Egress/ingress bandwidth ratio varies.** We highlight that the bandwidth requirements of an accelerator invocation can differ in terms of ingress and egress paths. Based on our observations, there are several possible value ranges for the ratio  $\frac{egressbw}{ingressbw}$  (denoted as  $R = \frac{Eb}{Ib}$ ).

- *R*=1. For example, the output ciphertext of AES-256-CTR is always the same length as the input plaintext.

- *R*>1, e.g., decompression falls into this category.

- *R*<1, e.g., compression falls into this category.

- *Eb* is fixed. For example, SHA-3-512 has a fixed output message size of 64B, no matter how large the input is.

These categories lead to different potential contention cases. For examples, SHA-3-512 is much more likely to interfere with its ingress path (i.e., DMA reads) rather than on its egress path (i.e., DMA writes), which always has small messages as outputs; allocating *X* Gbps PCIe bandwidth might not be sufficient to feed data into a compression accelerator where a user requires *X*Gbps.

**Observation 3: Implementation matters.** Even for the same type of accelerator, different algorithms (e.g., lossy vs. lossless compression) will change the impact of the above curves. Additionally, different hardware implementations (e.g., ASIC vs. FPGA prototypes) will also impact the curves. The observation indicates that the providers should be aware of the characteristics of the accelerators in use. There should also be a rethinking about users' observability: users need to have a nicely designed management interface to know details about the accelerator they pay for.

#### 3.3 Commercial Device Characteristics

We observe that the host network and the device interface collaboratively affect end-to-end isolation.

**Observation 4: Different QP numbers impact bandwidth allocation.** We sweep the QP number from 1 to 16 for each tenant. Based on our explorations on two tenants both sending 4KB RDMA writes, we find the throughput ratio between two tenants ( $T_q$ ) is equal to the ratio of QP numbers. For example, 2QP vs. 1QP, and 8QP vs. 4QP exhibit the same bandwidth allocation result, i.e., ~52Gbps vs. ~26Gbps. Other cases are similarly linear but data is omitted. A straightforward estimation is that the round robin arbitration commonly used by commercial devices [14, 40, 45] leads to this QP-related linear throughput allocation. This observation suggests the provider must be aware of per-tenant QP allocation and be able to re-allocate QP numbers.<sup>6</sup>

**Observation 5: Different message size mixtures contend differently.** In this test, both tenants have one QP allocated on the NIC and both send RDMA writes. Tenant A sends 4KB messages all the time, while Tenant B varies its message sizes from 256B to 8KB. We find the throughput ratio  $T_m$  varies from 0.83× to 10.5×, exhibiting throughput allocation ratios that are non-linear to message size ratios. This may be due to (1) NIC interface contention (e.g., on buffers or caches), and (2) fair queuing policy giving more PCIe bandwidth to larger messages.

**Observation 6: Direction of traffic heaviness matters.** The heaviness of data transfers has directions, i.e., host to accelerator (HtA), or accelerator to host (AtH). We study the contention effects of two scenarios: (1) RDMA writes colocate with RDMA writes (i.e., homogeneous heaviness), and (2) RDMA writes colocate with RDMA reads (i.e., heterogeneous heaviness). All experiments use 2 QPs and the same message sizes (from 256B to 8KB) for both tenants. For homogeneous heaviness, the bandwidth is evenly allocated. However, for heterogeneous heaviness, AtH traffic steals 1.08-3.39× bandwidth from HtA channels. Thus, the accelerator management stack should be aware of the direction of heavy traffic.

#### 3.4 Breakdown Analysis

Within our host-FPGA prototype, we list the following features to better understand the phenomena in Sec. 3.3.

- **Ring buffer protocol breakdown**. We manually implement PCIe read and PCIe write commands, supported by an FPGA driver and a register interface on the FPGA. This allows us to break down the complex communication in the ring buffer protocol that requires multiple round trips in the host network. The breakdown helps contention source analysis in detail.

- Awareness on arbitrary on message sizes and PCIe MTU size. To tune accelerator message sizes injected into the host network, we build a DMA engine on the FPGA that can split accelerator messages into arbitrary sizes of

<sup>&</sup>lt;sup>5</sup>This assumption is naturally true for send/receive I/Os and read/write I/Os, though not explicitly clarified by prior multi-tenancy I/O work.

<sup>&</sup>lt;sup>6</sup>Previous multi-tenant RDMA NICs do not consider QP impacts and their reallocation [36, 63].

Accelerator-as-a-Service in Public Clouds: An Intra-Host Traffic Management View for Performance Isolation in the Wild

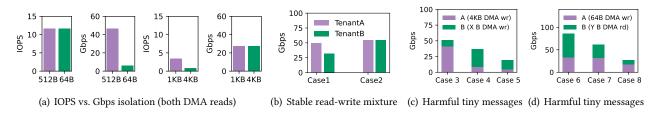

Figure 3: Host-FPGA characterization results.

Table 2: Host-FPGA contention (both tenants send

DMA reads). We vary MaxReadReqSize as the PCIe MTU

size variations.

|         |       | Tenant 1 message size M1 (Bytes) |               |

|---------|-------|----------------------------------|---------------|

|         |       | M1 <= MTU                        | M1 > MTU      |

| Tenant2 | M2 <= | IOPS fair                        | unpredictable |

| message | MTU   | Gbps unfair                      | contention    |

| size M2 | M2 >  | unpredictable                    | IOPS unfair   |

| (Bytes) | MTU   | contention                       | Gbps fair     |

PCIe reads and writes. The engine is also aware of PCIe "MTU" size<sup>7</sup> when splitting accelerator DMA messages.

- Arbitrary QP management. We manually implement hardware QPs and study contention effects on different arbitration or fair queuing policies across tenants.

- End-to-end invocations for each tenant. We run two tenants on the host that interact with the driver. Reported throughput is end-to-end, from tenant processes instead of only from FPGA hardware counters [42].

We first run two tenants with the same priority both invoking DMA reads. We vary each tenant's DMA read sizes from 16B to 4096B. We simply use robin robin on the FPGA to arbitrate traffic, similar to many other devices [14]. Fig. 3(a) shows representative data points; we omit the others due to space limits.

**Observation 7: Distinguishing throughput metrics matter.** Intuitively, throughput allocation across two tenants with the same priority can be considered as binary: fair or unfair. However, Fig. 3(a) demonstrates that the two tenants can be IOPS fair but data rate unfair (512B + 64B case), or data rate fair but IOPS unfair (1KB + 4KB case). Therefore, throughput fairness should be ternary (including neither metric is fair). Extending from fairness to arbitrary SLAs of each tenant, providers must distinguish IOPS SLA and data rate SLA to guarantee the required weighted fair share.

**Observation 8: Scheduling of mixed traffic on PCIe interconnects matters.** IOPS fairness occurs when both tenants send DMA reads whose sizes are smaller than PCIe's *MaxReadReqSize*. Data rate (Gbps) is fair when both send messages larger than *MaxReadReqSize* of PCIe. Otherwise, unpredictable contention will occur as summarized in Table 2. We perform the same experiment for two tenants running DMA writes. Results are similar to Table 2. The only difference is that the boundary is not *MaxReadReqSize* of PCIe but *MaxPayloadSize* of PCIe. Therefore, being aware of DMA read and write sizes or even re-sizing DMA messages to be either all larger or all smaller than PCIe MTU sizes is important. By doing so, providers can better guarantee predictable performance for either IOPS or data rate SLAs.

**Observation 9: Colocating opposite directions improve** DMA performance predictability. Given the contention Observation 5, one may consider avoiding colocating DMA writes with DMA reads. To explore if the DMA read-write mixture is the reason for contention, we run two cases. Case 1 is where tenant A sends 4KB DMA reads, and tenant B sends DMA writes, varying its size from 256B to 4KB. Case 2 is where tenant A sends 64B DMA reads, and tenant B sends 256B-4KB DMA reads. Fig. 3(b) shows that in both cases, tenant B's DMA read performance has a near-zero variance, while tenant A's DMA write performance only varies within 10%. The root cause of this predictability benefit is that DMA reads and writes naturally take advantage of the full-duplex feature of PCIe interconnects. Moreover, re-scheduling the timing of DMA reads and writes, and colocating DMA readintensive and DMA write-intensive traffic patterns together, can improve performance predictability.

**Observation 10: Preventing small DMA messages from taking over the PCIe interconnects is vital.** Fig. 3(c) and Fig. 3(d) show that the overall PCIe throughput can significantly drop due to small DMA messages. Cases 3-5 co-locate 4KB DMA writes with *X* B DMA writes, where *X* is 64B, 32B, and 16B. In Fig. 3(c), Case 3 delivers 51Gbps overall throughput, 94% of the ideal throughput for DMA writes in our prototype. However, Cases 4 and 5 suffer from 28% and 85% throughput drops because 32B or 16B DMA writes start to take over PCIe credits within the root complex. In Fig. 3(d), *Y* is 256B, 128B, and 32B, and similar throughput

<sup>&</sup>lt;sup>7</sup>We refer *MaxReadReqSize* and *MaxPayloadSize* to be PCIe "MTU" similar to Ethernet MTU.

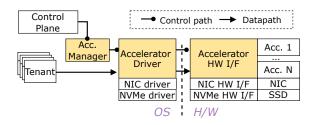

Figure 4: A system w/ accelerator management stack.

drops are observable. Disallowing users to inject such traffic is vital to prevent SLA violations for victim tenants. Such small message traffic can be flattened by batching, padding, or rate limiting.

# 4 ACCELERATOR TRAFFIC SHAPING

Based on observations in Sec. 3, we advocate one promising approach, i.e., proactively shaping the traffic on-the-fly and highlight the following design options.

**Should we support separate accelerator QPs?** Existing NICs invoke their accelerators by coupling them with the NIC's QPs [10, 12, 23, 24, 42]. However, once the accelerator is allocated, this static provisioning lacks sufficient support to reallocate its compute capacity, and experiences on-NIC contention induced by network traffic. As shown in Fig. 4, we propose a separate set of accelerator QPs from the host perspective. With accelerator QPs, accelerators have a traffic management interface that brings information through customized descriptors. Designers can optimize the accelerator driver for performance [49, 60] and enable other commands such as initialization, configuration, (re)allocation, monitoring, and traffic shaping. For example, the provider can control how many QPs are (re)allocated to each flow for performance or contention management (as observed in Sec. 3).

Where should the accelerator traffic shaping functionality reside? There are several options for the location of the traffic shaping: software hypervisor on the host, user domain (in VMs or containers), or the accelerator interface on the device. First, hypervisors do not always have permission to know detailed traffic information such as message sizes. Worse, in-hypervisor shaping loses manageability in some systems where hypervisors are bypassed [1, 26, 38]. Second, users know their own traffic patterns, but they do not know the accelerators' characteristics and patterns of other tenants.

Our work advocates traffic shaping in the accelerator interface. This design option stands out due to the following reasons. First, the accelerator interface has local accessibility to the accelerators. Thus, it has on-the-fly traffic observability to accelerators' status, such as queuing effects and Jiechen Zhao $^{\bullet}$ , Ran Shu $^{\bullet}$ , Katie Lim $^{\bullet}$ , Zewen Fan $^{\diamond}$ , Thomas Anderson $^{\bullet}$ , Mingyu Gao $^{\diamond}$ , Natalie Enright Jerger $^{\bullet}$

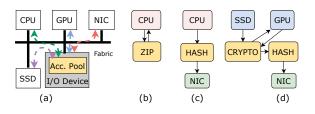

Figure 5: End-to-end scenarios. (a) A typical heterogeneous server with wild I/O contention, (b) function call mode, (c) inline mode, and (d) a complex use case.

egress/ingress bandwidth requirements. Second, the interface sits in the middle of diverse accelerator I/O paths, providing good interposition. Third, the interface is customizable by providers, e.g., the descriptors for host-accelerator protocol. **What traffic metrics to shape?** The traffic shaping unit for each tenant manages the following parameters: message sizes, burst size of messages, the number of QPs to send/receive, and the minimum rate<sup>8</sup> (i.e., the SLA), the maximum rate (i.e., how much maximal performance is provisioned). Note that because of the non-linearity characteristics of accelerators (Sec. 3.2), the traffic shaping parameters should be re-calculated case-by-case to match users' requirements under a particular traffic pattern.

# 5 OPEN PROBLEMS

Managing I/O contention in the wild. A typical server can be like Fig. 5(a). In such a system, wild I/O contention can occur beyond just accelerator I/O flows. For example, an Azure FPGA or an Nvidia BlueField may incorporate both accelerator and network I/O traffic to the host, potentially contending on host networks (similar to Sec. 3.3-Sec. 3.4). Fortunately, our observations generally help improve multitenancy for arbitrary I/Os. To shape all PCIe traffic, future work can exploit a hybrid traffic shaping approach. In a PCIe network, the per-device interface and the PCIe switch can synergistically police outgoing traffic. This is similar to hybrid traffic shaping in datacenter networks coordinating in-switch and per end-host traffic shaping [28, 51, 54]. When observing traffic patterns on-the-fly, harmful traffic patterns can be used as prior knowledge. Researchers can explore various shaping algorithms such as batching, splitting, padding, delaying, interleaving, and rate limiting for performance predictability.

Assisting congestion control designs. Intra-host congestion control has become an important topic recently for network applications [17, 43]. Several of these works emphasize IOMMU and memory bandwidth related congestion [16, 17].

<sup>&</sup>lt;sup>8</sup>The rate of an accelerator traffic stream can be Gbps or IOPS.

Our observations give another dimension of information to reduce congestion if re-shaping the traffic right. Our experiments disable IOMMU and isolate NUMA nodes (Sec. 3.1), orthogonal to findings in prior works [16, 17]. Future work may have further findings when combining our settings with those prior works. In addition, our approach will have broader manageability beyond network application, e.g., understanding congestion better when computational I/Os and legacy I/Os co-exist, under a certain PCIe topology.

**End-to-end accelerator integration.** There remains discussion of how end-to-end I/O paths can integrate accelerators as Fig. 5(b)(c) show. Accelerator QPs should exchange accelerator descriptors with other device QPs that exhibit different protocols and descriptor formats. One option is to leverage the OS to perform protocol conversion. One example is NVMe-over-Fabric protocol [2]. The other option learns from Internet routers to construct an overlay among diverse QPs across different devices. One example of such an IP layer like overlay [57] eliminates host involvements if designed on a PCIe switch or on the device.

Accelerator chaining. Various aspects of the server's traffic need to chain different types of services together [21, 33, 62]. For instance, in Fig. 5(d), after data is read from SSDs, a decryption accelerator is used before the data is fed into the GPU, whose output result is first encrypted and then SHA'ed before sending data into the network. Our approach is extensible to accelerator chaining by only shaping ingress and egress patterns of a chain. Further challenges emerge such as how to manage on-chain traffic and resources, and how to invoke network-attached accelerators if a single device cannot satisfy the entire accelerator chain.

**Managing I/O contention for GPUs.** In a time multiplexing mode, e.g., serving model inferences one user after another, the GPU is equivalent to a temporally multiplexed I/O accelerator. In that case, our design is feasible to shape GPU traffic with a PCIe network. Some of the big open problems when applying our design to this setting will be ① how to perform traffic shaping when GPUs are used under spatial multiplexing, ② how to incorporate the understanding of GPU internal contention into the traffic patterns to re-shape, and ③ how to incorporate our findings when managing PCIe congestion for multi-GPU servers.

**Fitting future fabrics.** New fabrics like CXL . io rely on PCIe interconnects, therefore the observations in Sec. 3 can also guide contention management for CXL devices. However, CXL devices [48, 56] may further bring in new traffic characteristics that either can be leveraged or should be avoided. In the future, researchers can exploit them based on methodologies in Sec. 3, and design appropriate shaping algorithms.

**Security issues of accelerator sharing.** We can quantify a set of attacks, such as performance attacks due to small messages (Observation 9). Further study of the security implications of accelerator sharing is needed. For example, newlyintroduced side channels can be a new vulnerability if users leverage cryptography accelerators to accelerate security operations; the sharing degree between providers and users remains another question to explore.

Accelerator cost and cloud-scale management. Generally, sharing reduces accelerator cost, e.g., TCO or embodied carbon emissions [50, 53]. Research on holistic cost models will help business profits and sustainability. For example, using densely populated accelerator servers [15, 41, 59] or attaching homogeneous accelerator devices per server [7, 26] is an open question. In addition, this paper only studies the case of two-tenant co-location. With more tenants, there should be new capacity planning and admission control supports at cloud-scale, balancing costs and serviceability.

#### REFERENCES

- 2008. White paper of PCI-SIG Single Root I/O Virtualization. https://www.intel.com/content/dam/doc/white-paper/pci-sigsingle-root-io-virtualization-support-in-virtualization-technologyfor-connectivity-paper.pdf. Accessed: 2024-7-11.

- [2] 2016. NVMe Over Fabric. https://www.nvmexpress.org/wp-content/ uploads/NVMe\_Over\_Fabrics.pdf. Accessed: 2024-7-11.

- [3] 2021. Nvidia BlueField-3 DPU Programmable Data Center Infrastructure On-a-Chip. https://www.nvidia.com/content/dam/enzz/Solutions/Data-Center/documents/datasheet-nvidia-bluefield-3dpu.pdf. Accessed: 2024-7-11.

- [4] 2022. Alibaba CIPU. https://www.breakinglatest.news/business/ alibaba-clouds-first-cipu-processor-is-reverse-self-developed-foros/. Accessed: 2022-12-30.

- [5] 2024. Amazon EC2 F1 Instances. https://aws.amazon.com/ec2/ instance-types/f1/. Accessed: 2024-7-11.

- [6] 2024. AMD Xilinx Alveo SN1000 SmartNIC. https://www.xilinx.com/ applications/data-center/network-acceleration/alveo-sn1000.html. Accessed: 2022-12-30.

- [7] 2024. AWS Nitro System. https://aws.amazon.com/ec2/nitro/. Accessed: 2024-7-11.

- [8] 2024. Azure confidential VMs. https://learn.microfsoft.com/en-us/ azure/confidential-computing/confidential-vm-overview. Accessed: 2024-7-11.

- [9] 2024. Azure managed disk types. https://learn.microsoft.com/enus/azure/virtual-machines/disks-types. Accessed: 2024-7-11.

- [10] 2024. Compression Device Library in DPDK. https://doc.dpdk.org/ guides/prog\_guide/compressdev.html. Accessed: 2024-7-11.

- [11] 2024. Cryptography Device Library in DPDK. https://doc.dpdk.org/ guides-18.08/prog\_guide/cryptodev\_lib.html. Accessed: 2024-7-11.

- [12] 2024. DPDK driver for Intel QuickAssist compression accelerator. https://doc.dpdk.org/guides/compressdevs/qat\_comp.html. Accessed: 2024-7-11.

- [13] 2024. Intel Infrastructure Processing Unit (Intel IPU) and Smart-NICs. https://www.intel.com/content/www/us/en/products/details/ network-io/ipu.html. Accessed: 2024-7-11.

- [14] 2024. Intel QuickAssist technology. https://www.intel. com/content/www/us/en/content-details/784036/accelerate-

Jiechen Zhao<sup>♥</sup>, Ran Shu<sup>♠</sup>, Katie Lim<sup>♠</sup>, Zewen Fan<sup>◊</sup>, Thomas Anderson<sup>♠</sup>, Mingyu Gao<sup>◊</sup>, Natalie Enright Jerger<sup>♥</sup>

cryptographic-operations-and-data-compression-workloads-withintel-qat.html?DocID=784036. Accessed: 2024-7-11.

- [15] 2024. TPU v4 configurations of Google CLoud. https://cloud.google. com/tpu/docs/v4. Accessed: 2024-7-11.

- [16] Saksham Agarwal, Rachit Agarwal, Behnam Montazeri, Masoud Moshref, Khaled Elmeleegy, Luigi Rizzo, Marc Asher de Kruijf, Gautam Kumar, Sylvia Ratnasamy, David Culler, and Amin Vahdat. 2022. Understanding host interconnect congestion. In Proceedings of the 21st ACM Workshop on Hot Topics in Networks (HotNets). 198–204.

- [17] Saksham Agarwal, Arvind Krishnamurthy, and Rachit Agarwal. 2023. Host Congestion Control. In *Proceedings of the ACM SIGCOMM Conference*. 275–287.

- [18] Sebastian Angel, Hitesh Ballani, Thomas Karagiannis, Greg O'Shea, and Eno Thereska. 2014. End-to-end performance isolation through virtual datacenters. In Proceedings of the 11th USENIX Symposium on Operating Systems Design and Implementation (OSDI). 233–248.

- [19] Hitesh Ballani, Paolo Costa, Thomas Karagiannis, and Ant Rowstron. 2011. Towards predictable datacenter networks. In *Proceedings of the* ACM SIGCOMM Conference. 242–253.

- [20] Jeff Barr. 2021. AWS AQUA (Advanced Query Accelerator) FPGA accelerator. https://aws.amazon.com/blogs/aws/new-aqua-advancedquery-accelerator-for-amazon-redshift/. Accessed: 2024-7-11.

- [21] Willem De Bruijn, Herbert Bos, and Henri Bal. 2011. Applicationtailored I/O with Streamline. ACM Transactions on Computer Systems (TOCS) 29, 2 (2011), 1–33.

- [22] Jeffrey Dean and Luiz André Barroso. 2013. The tail at scale. Commun. ACM 56, 2 (2013), 74–80.

- [23] Haggai Eran, Maxim Fudim, Gabi Malka, Gal Shalom, Noam Cohen, Amit Hermony, Dotan Levi, Liran Liss, and Mark Silberstein. 2022. FlexDriver: a network driver for your accelerator. In Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS). 1115–1129.

- [24] Haggai Eran, Lior Zeno, Maroun Tork, Gabi Malka, and Mark Silberstein. 2019. NICA: An infrastructure for inline acceleration of network applications. In *Proceedings of the 2019 USENIX Annual Technical Conference (ATC)*. 345–362.

- [25] Hadi Esmaeilzadeh, Emily Blem, Renee St Amant, Karthikeyan Sankaralingam, and Doug Burger. 2011. Dark silicon and the end of multicore scaling. In *Proceedings of the 38th ACM/IEEE International Symposium* on Computer Architecture (ISCA). 365–376.

- [26] Daniel Firestone, Andrew Putnam, Sambhrama Mundkur, Derek Chiou, Alireza Dabagh, Mike Andrewartha, Hari Angepat, Vivek Bhanu, Adrian Caulfield, Eric Chung, Harish Kumar Chandrappa, Somesh Chaturmohta, Matt Humphrey, Jack Lavier, Norman Lam, Fengfen Liu, Kalin Ovtcharov, Jitu Padhye, Gautham Popuri, Shachar Raindel, Tejas Sapre, Mark Shaw, Gabriel Silva, Madhan Sivakumar, Nisheeth Srivastava, Anshuman Verma, Qasim Zuhair, Deepak Bansal, Doug Burger, Kushagra Vaid, David A. Maltz, and Albert Greenberg. 2018. Azure accelerated networking: SmartNICs in the public cloud. In Proceedings of the 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 51–66.

- [27] Michael Galles and Francis Matus. 2021. Pensando distributed services architecture. *IEEE Micro* 41, 2 (2021), 43–49.

- [28] Monia Ghobadi, Yuchung Cheng, Ankur Jain, and Matt Mathis. 2012. Trickle: Rate limiting YouTube video streaming. In *Proceedins of the* 2012 USENIX Annual Technical Conference (ATC). 191–196.

- [29] Stewart Grant, Anil Yelam, Maxwell Bland, and Alex C. Snoeren. 2020. SmartNIC performance isolation with FairNIC: Programmable networking for the cloud. In *Proceedings of the ACM SIGCOMM Conference*. 681–693.

- [30] Svilen Kanev, Juan Pablo Darago, Kim Hazelwood, Parthasarathy Ranganathan, Tipp Moseley, Gu-Yeon Wei, and David Brooks. 2015. Profiling a warehouse-scale computer. In *Proceedings of the 42nd ACM/IEEE International Symposium on Computer Architecture (ISCA)*. 158–169.

- [31] Sagar Karandikar, Chris Leary, Chris Kennelly, Jerry Zhao, Dinesh Parimi, Borivoje Nikolic, Krste Asanovic, and Parthasarathy Ranganathan. 2021. A Hardware Accelerator for Protocol Buffers. In Proceedings of the 54th ACM/IEEE International Symposium on Microarchitecture (MICRO). 462–478.

- [32] Sagar Karandikar, Aniruddha N. Udipi, Junsun Choi, Joonho Whangbo, Jerry Zhao, Svilen Kanev, Edwin Lim, Jyrki Alakuijala, Vrishab Madduri, Yakun Sophia Shao, Borivoje Nikolic, Krste Asanovic, and Parthasarathy Ranganathan. 2023. CDPU: Co-designing Compression and Decompression Processing Units for Hyperscale Systems. In Proceedings of the 50th ACM/IEEE International Symposium on Computer Architecture (ISCA). 1–17.

- [33] Georgios P. Katsikas, Tom Barbette, Dejan Kostic, Rebecca Steinert, and Gerald Q. Maguire Jr. 2018. Metron: NFV service chains at the true speed of the underlying hardware. In Proceedings of the 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 171–186.

- [34] Patrick Kennedy. 2020. Pensando floor plan. https: //www.servethehome.com/pensando-distributed-servicesarchitecture-smartnic/. Accessed: 2024-7-11.

- [35] Mikhail Khalilov, Marcin Chrapek, Siyuan Shen, Alessandro Vezzu, Thomas Benz, Salvatore Di Girolamo, Timo Schneider, Daniele Di Sensi, Luca Benini, and Torsten Hoefler. 2024. OSMOSIS: Enabling Multi-Tenancy in Datacenter SmartNICs. arXiv preprint arXiv:2309.03628 (2024).

- [36] Xinhao Kong, Jingrong Chen, Wei Bai, Yechen Xu, Mahmoud Elhaddad, Shachar Raindel, Jitendra Padhye, Alvin R. Lebeck, and Danyang Zhuo. 2023. Understanding RDMA microarchitecture resources for performance isolation. In Proceedings of the 20th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 31–48.

- [37] Praveen Kumar, Nandita Dukkipati, Nathan Lewis, Yi Cui, Yaogong Wang, Chonggang Li, Valas Valancius, Jake Adriaens, Steve Gribble, Nate Foster, and Amin Vahdat. 2019. PicNIC: predictable virtualized NIC. In Proceedings of the ACM SIGCOMM Conference. 351–366.

- [38] Dongup Kwon, Junehyuk Boo, Dongryeong Kim, and Jangwoo Kim. 2020. FVM: FPGA-assisted Virtual Device Emulation for Fast, Scalable, and Flexible Storage Virtualization. In Proceedings of the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI). 955–971.

- [39] Dongup Kwon, Dongryeong Kim, Junehyuk Boo, Wonsik Lee, and Jangwoo Kim. 2021. A Fast and Flexible Hardware-based Virtualization Mechanism for Computational Storage Devices. In *Proceedings of the* 2021 USENIX Annual Technical Conference (ATC). 729–743.

- [40] Chen Li, Yifan Sun, Lingling Jin, Lingjie Xu, Zheng Cao, Pengfei Fan, David Kaeli, Sheng Ma, Yang Guo, and Jun Yang. 2019. Priority-based PCIe scheduling for multi-tenant multi-GPU systems. *IEEE Computer Architecture Letters* 18, 2 (2019), 157–160.

- [41] Katie Lim, Matthew Giordano, Theano Stavrinos, Baris Kasikci, and Tom Anderson. 2024. Beehive: A Flexible Network Stack for Direct-Attached Accelerators. arXiv preprint arXiv:2403.14770 (2024).

- [42] Jiaxin Lin, Kiran Patel, Brent E. Stephens, Anirudh Sivaraman, and Aditya Akella. 2020. PANIC: A High-Performance Programmable NIC for Multi-tenant Networks. In Proceedings of the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI). 243–259.

- [43] Kefei Liu, Zhuo Jiang, Jiao Zhang, Haoran Wei, Xiaolong Zhong, Lizhuang Tan, Tian Pan, and Tao Huang. 2023. Hostping: Diagnosing intra-host network bottlenecks in RDMA servers. In *Proceedings of*

Accelerator-as-a-Service in Public Clouds:

An Intra-Host Traffic Management View for Performance Isolation in the Wild

the 20th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 15–29.

- [44] Ming Liu, Tianyi Cui, Henry Schuh, Arvind Krishnamurthy, Simon Peter, and Karan Gupta. 2019. Offloading distributed applications onto smartNICs using iPipe. In *Proceedings of the ACM SIGCOMM Conference*. 318–333.

- [45] Maxime Martinasso, Grzegorz Kwasniewski, Sadaf R. Alam, Thomas C. Schulthess, and Torsten Hoefler. 2016. A PCIe congestion-aware performance model for densely populated accelerator servers. In Proceedings of the ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis (SC). IEEE, 739–749.

- [46] Jaehong Min, Ming Liu, Tapan Chugh, Chenxingyu Zhao, Andrew Wei, In Hwan Doh, and Arvind Krishnamurthy. 2021. Gimbal: enabling multi-tenant storage disaggregation on SmartNIC JBOFs. In *Proceedings of the ACM SIGCOMM Conference*. 106–122.

- [47] Rolf Neugebauer, Gianni Antichi, José Fernando Zazo, Yury Audzevich, Sergio López-Buedo, and Andrew W. Moore. 2018. Understanding PCIe performance for end host networking. In *Proceedings of the ACM* SIGCOMM Conference. 327–341.

- [48] Stanko Novakovic, Alexandros Daglis, Edouard Bugnion, Babak Falsafi, and Boris Grot. 2014. Scale-out NUMA. Proceedings of the 19th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS) (2014), 3–18.

- [49] Solal Pirelli and George Candea. 2020. A Simpler and Faster NIC Driver Model for Network Functions. In Proceedings of the 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI). 225–241.

- [50] Aster Plotnik, Karthik Ganesan, Natalie Enright Jerger, and Mark C. Jeffrey. 2024. Intergenerational Embodied Carbon. In Proceedings of the 1st Workshop on Hot Topics in Ethical Computer Systems (HotEthics).

- [51] Sivasankar Radhakrishnan, Yilong Geng, Vimalkumar Jeyakumar, Abdul Kabbani, George Porter, and Amin Vahdat. 2014. SENIC: Scalable NIC for End-Host Rate Limiting. In Proceedings of the 11th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 475–488.

- [52] Zhenyuan Ruan, Tong He, and Jason Cong. 2019. INSIDER: Designing In-Storage Computing System for Emerging High-Performance Drive. In Proceedings of the 2019 USENIX Annual Technical Conference (ATC). 379–394.

- [53] Hugo Sadok, Aurojit Panda, and Justine Sherry. 2023. Of apples and oranges: Fair comparisons in heterogenous systems evaluation. In Proceedings of the 22nd ACM Workshop on Hot Topics in Networks (HotNets). 1–8.

- [54] Ahmed Saeed, Nandita Dukkipati, Vytautas Valancius, Vinh The Lam, Carlo Contavalli, and Amin Vahdat. 2017. Carousel: Scalable traffic shaping at end hosts. In *Proceedings of the Conference of the ACM* SIGCOMM Conference. 404–417.

- [55] Nikola Samardzic, Axel Feldmann, Aleksandar Krastev, Nathan Manohar, Nicholas Genise, Srinivas Devadas, Karim Eldefrawy, Chris Peikert, and Daniel Sanchez. 2022. Craterlake: a hardware accelerator for efficient unbounded computation on encrypted data. In *Proceedings* of the 49th ACM/IEEE International Symposium on Computer Architecture (ISCA). 173–187.

- [56] Henry N Schuh, Arvind Krishnamurthy, David Culler, Henry M. Levy, Luigi Rizzo, Samira Khan, and Brent E. Stephens. 2024. CC-NIC: a Cache-Coherent Interface to the NIC. In Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS). 52–68.

- [57] Ran Shu, Peng Cheng, Guo Chen, Zhiyuan Guo, Lei Qu, Yongqiang Xiong, Derek Chiou, and Thomas Moscibroda. 2019. Direct Universal Access: Making Data Center Resources Available to FPGA. In Proceedings of the 16th USENIX Symposium on Networked Systems Design and

Implementation (NSDI). 127-140.

- [58] Akshitha Sriraman and Abhishek Dhanotia. 2020. Accelerometer: Understanding acceleration opportunities for data center overheads at hyperscale. In Proceedings of the 25th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS). 733–750.

- [59] Michael Bedford Taylor, Luis Vega, Moein Khazraee, Ikuo Magaki, Scott Davidson, and Dustin Richmond. 2020. Asic clouds: Specializing the datacenter for planet-scale applications. *Commun. ACM* 63, 7 (2020), 103–109.

- [60] Xiuxiu Wang, Yipei Niu, Fangming Liu, and Zichen Xu. 2020. When FPGA meets cloud: A first look at performance. *IEEE Transactions on Cloud Computing* 10, 2 (2020), 1344–1357.

- [61] Adam Wolnikowski, Stephen Ibanez, Jonathan Stone, Changhoon Kim, Rajit Manohar, and Robert Soulé. 2021. Zerializer: Towards zero-copy serialization. In Proceedings of the 18th Workshop on Hot Topics in Operating Systems (HotOS). 206–212.

- [62] Kai Zhang, Bingsheng He, Jiayu Hu, Zeke Wang, Bei Hua, Jiayi Meng, and Lishan Yang. 2018. G-NET: Effective GPU Sharing in NFV Systems. In Proceedings of the 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 187–200.

- [63] Yiwen Zhang, Yue Tan, Brent Stephens, and Mosharaf Chowdhury. 2022. Justitia: Software Multi-Tenancy in Hardware Kernel-Bypass Networks. In Proceedings of the 19th USENIX Symposium on Networked Systems Design and Implementation (NSDI). 1307–1326.