## Nano-Ironing van der Waals Heterostructures Towards Electrically Controlled Quantum Dots

Teymour Talha-Dean,<sup>1,2,\*</sup> Yaoju Tarn,<sup>1,\*</sup> Subhrajit Mukherjee,<sup>1</sup> John Wellington John,<sup>1</sup> Ding

Huang,<sup>1</sup> Ivan A. Verzhbitskiy,<sup>1</sup> Dasari Venkatakrishnarao,<sup>1</sup> Sarthak Das,<sup>1</sup> Rainer Lee,<sup>1</sup> Abhishek

Mishra,<sup>1</sup> Shuhua Wang,<sup>3</sup> Yee Sin Ang,<sup>3</sup> Kuan Eng Johnson Goh,<sup>1,4,5,†</sup> and Chit Siong Lau<sup>1,‡</sup>

<sup>1</sup>Institute of Materials Research and Engineering (IMRE), Agency for Science,

Technology and Research (A\*STAR), 2 Fusionopolis Way,

Innovis #08-03, Singapore 138634, Republic of Singapore

<sup>2</sup>Department of Physics and Astronomy, Queen Mary University of London, London, E1 4NS, United Kingdom

<sup>3</sup>Science, Mathematics and Technology, Singapore University of Technology and Design, 8 Somapah Road, 487372, Singapore

<sup>4</sup>Department of Physics, National University of Singapore, 2 Science Drive 3, 117551, Singapore

<sup>5</sup>Division of Physics and Applied Physics, School of Physical and Mathematical Sciences,

Nanyang Technological University, 50 Nanyang Avenue 639798, Singapore

Assembling two-dimensional van der Waals layered materials into heterostructures is an exciting development that sparked the discovery of rich correlated electronic phenomena and offers possibilities for designer device applications. However, resist residue from fabrication processes is a major limitation. Resulting disordered interfaces degrade device performance and mask underlying transport physics. Conventional cleaning processes are inefficient and can cause material and device damage. Here, we show that thermal scanning probe based cleaning can effectively eliminate resist residue to recover pristine material surfaces. Our technique is compatible at both the material- and device-level, and we demonstrate the significant improvement in the electrical performance of 2D WS<sub>2</sub> transistors. We also demonstrate the cleaning of van der Waals heterostructures to achieve interfaces with low disorder. This enables the electrical formation and control of quantum dots that can be tuned from macroscopic current flow to the single-electron tunnelling regime. Such material processing advances are crucial for constructing high-quality vdW heterostructures that are important platforms for fundamental studies and building blocks for quantum and nano-electronics applications.

#### I. INTRODUCTION

The successful isolation of graphene with mechanical exfoliation was a profound moment.[1] It led to an explosive growth in the field of two-dimensional (2D) materials. A large and growing '2D library' is now available, with thousands of 2D insulating, semiconducting, and metallic materials offering an extensive array of properties. Subsequent development of the dry transfer technique enabled the stacking of individual 2D layers into van der Waals (vdW) heterostructures.[2-4] Akin to the assembly of simple Lego blocks into complex structures, vdW heterostructures often display properties distinct from each individual layer. This offers exciting avenues for designer devices with tailored functionalities. Beyond applications, vdW heterostructures are ideal platforms for fundamental studies. Strong electronic correlations across layers can lead to emergent physics and quantum effects including unconventional superconductivity, [5] ferromagnetism, [6] ferroelectricity, [7] and quantized anomalous Hall effect. [8]

Central to these ideas is the need for pristine vdW surfaces/interfaces, but a key problem is resist residue from

lithography. Such residue can form films or clusters  $\sim 1$ -10 nm thick, which is significant considering the atomic thinness of 2D materials (< 1 nm). Several techniques exist for cleaning the resist residue. Standard solvent cleaning is typically insufficient and can introduce unwanted chemical doping.[9] It is usually supplemented by other techniques such as thermal annealing, [10] current annealing, [11] and nano-probe tip based mechanical cleaning[12–15]. The effectiveness of resist removal scales with temperature for thermal annealing, but the device thermal budget is an important consideration as contacts, substrates, and dielectrics may not be compatible with high temperatures. [16] Current annealing allows local channel heating but can lead to material damage and device breakdown unless complex feedback systems [17] are introduced. Mechanical cleaning with nano-probe tips can restore atomically clean surfaces but may require large local forces, especially for larger sized residue. These large forces lead to unintended defects and cause ruptures and film tears.[13–15]

To address the need for a damage-free method of resist removal for atomically clean and flat vdW material surfaces, we develop a technique we call 'nano-ironing'. The nano-ironing concept combines the advantages of annealing with mechanical tip based cleaning by using a heated nano probe tip. We show that nano-ironing is substantially more effective at removing resist residue compared to conventional mechanical nano probe tip based cleaning ('nano-brooming') at similar force levels. By restor-

<sup>\*</sup> These two authors contributed equally

<sup>†</sup> kejgoh@yahoo.com

<sup>&</sup>lt;sup>‡</sup> aaron\_lau@imre.a-star.edu.sg

ing surface cleanliness, WS<sub>2</sub> field effect transistors (FET) display significant improvements in carrier mobility and drain current, and reduction in unwanted charge doping. Finally, we use nano-ironing to prepare vdW heterostructures with low disorder. We show quantum transport measurements where we demonstrate electrical confinement and control of carriers to observe a transition from macroscopic current flow towards single-electron transport.

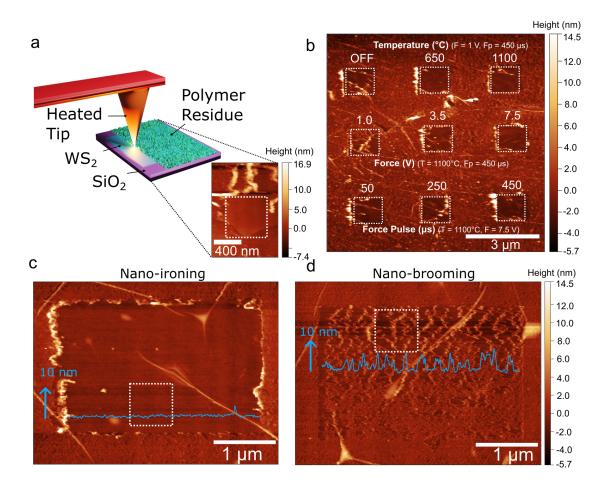

## II. NANO-IRONING: THERMAL SCANNING PROBE-BASED CLEANING

Our nano-ironing technique is based on a commercial thermal scanning probe lithography (t-SPL) system housed in an inert glovebox with typical  $O_2$  and  $H_2O$  levels below 5 ppm.[18, 19] Such inert environment mitigates possible oxidation of 2D material films during nano-ironing. The t-SPL's heated nanoprobe tip comes into contact with a vdW material surface and rasters to thermo-mechanically clean polymeric resist (Figure 1a). Precise alignment and controlled cleaning are possible with tunability of tip temperature, applied force, and duration of contact. (Figure 1b). We find that increasing the temperature can improve resist removal efficiency, while higher forces are useful for particularly stubborn or larger sized particulates. A higher force pulse, i.e., the duration of heated contact, prolongs heat transfer for better cleaning.

The key advantage of nano-ironing over nanobrooming lies in the extra degree of freedom allotted by temperature control. This achieves a substantially cleaner surface at comparable forces (Figure 1c, d) with almost an order of magnitude improvement in rootmean-square (RMS) roughness. We recover a surface with RMS roughness of  $300\pm40$  pm ( $1.20\pm0.3$  nm) after nano-ironing (nano-brooming). Importantly, nanoironing does not lead to any observable chemical and mechanical damage as shown via photoluminescence and Raman spectroscopy measurements (Supporting Information Figure S3). Detailed discussion on force and contact temperature estimations, and choice of t-SPL parameters for optimal cleanliness is available in the Supporting Information.

## III. ELECTRICAL CHARACTERIZATION

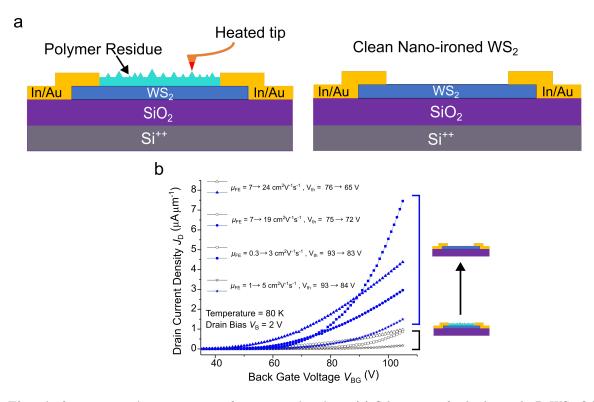

Polymeric resist residue can degrade carrier transport in 2D FETs through unwanted charge doping and increased roughness and impurity scattering. [20, 21] A useful way to estimate the effects of scattering mechanisms on carrier mobility  $\mu_{\rm FE}$  in 2D FETs is Matthiesen's rule  $\frac{1}{\mu} = \sum_{i} \frac{1}{\mu_{\rm i}}$ , where  $\mu_{\rm i}$  is the contribution from the *i*th scattering mechanism. The main scattering mechanisms are impurities, interface roughness, and phonons.[22, 23] At room temperature,  $\mu$  is typically limited by electronphonon scattering which can mask potential improvements from nano-ironing. Therefore, we investigate the low temperature performance of 2D WS<sub>2</sub> FETs before and after nano-ironing. We show that nano-ironing can indeed lead to increased current densities, increased carrier mobilities, and reduced unwanted charge-doping.

Our device consists of a chemical vapour deposition (CVD) grown monolayer WS<sub>2</sub> semiconducting channel with indium-gold (In/Au) alloy contacts on a heavily doped SiO<sub>2</sub>/Si substrate (Figure 2a). The SiO<sub>2</sub>/Si substrate also functions as a back gate electrode. Transfer curves of a 2D WS<sub>2</sub> FET measured at 80 K before (black, unfilled) and after (blue, filled) nano-ironing show increases in drain current density  $J_{\rm D}$  and field effect mobility  $\mu_{\rm FE}$  of ~2 to 10- fold across four devices. This highlights the improvements from reduced impurity and roughness scattering (Figure 2b). We also observe negative shifts in threshold voltage  $V_{\rm th}$  of ~3 to 11 V post nano-ironing, consistent with the expected reduction in *p*-type charge doping after eliminating resist residue.[20]

### IV. QUANTUM DOT CONTROL

Having demonstrated material- and device-level improvements from nano-ironing, we next highlight its potential for enabling quantum transport studies in vdW heterostructures. A key requirement for quantum transport is to create a homogeneous two-dimensional electron gas (2DEG).[24–27] This homogeneity needs atomically clean interfaces free from residual induced disorder to preserve high carrier mobility and enable experimental control over the local electrostatic potential and carrier density distribution. Such independent electrical control is necessary for precise confinement and tuning of the 2DEG, important for quantum information processing applications.[22, 27–31] For example in qubits, where state preparation, readout, and manipulation are performed with local electrostatic control.

Quantum transport is therefore typically only observed in high quality heterostructures assembled before any lithographic process to minimize trapped resist residue between interfaces. [32–38] However, this approach limits the choice of contact materials and introduces greater fabrication complexity. [33–35, 37–39] Complete reliance on such manually assembled contacts is intrinsically unscalable for technological applications. Another approach is to establish contacts post-heterostructure assembly with selective etching of the different vdW layers. [39, 40] This requires a high degree of precision and can lead to unwanted damage to the channel surface. A direct, damage- and residue-free contact lithography process that can preserve vdW heterostructure interface cleanliness is desired to increase experimental flexibility, material choices, and yield.

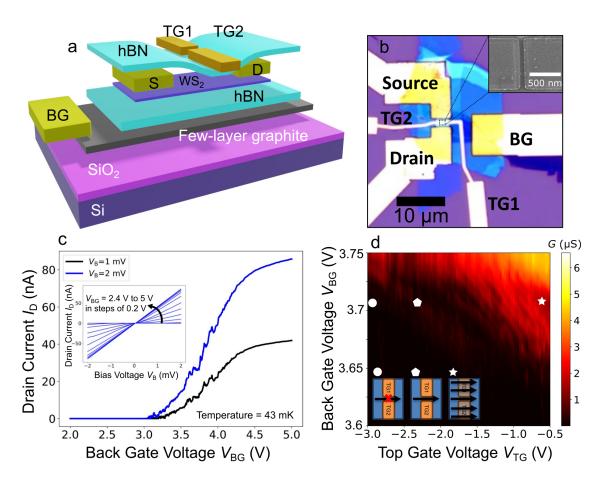

Here we demonstrate such a vdW heterostructure with atomically clean interfaces from nano-ironing (Figure

FIG. 1. Nano-ironing: heated nano-probe tip based cleaning of 2D material surfaces (a) Schematic of the nanoironing process. The inset shows an atomic-force microscopy (AFM) image after nano-ironing analogous to the cartoon schematic. The white box represents the atomically smooth nano-ironed flake area. Surrounding regions are covered with polymeric resist residue. (b) Demonstration of tuning parameters that can influence the degree of resist removal. Writer temperature T varies from room temperature to  $1100^{\circ}$ C, corresponding to an estimated range of tip contact temperatures of 30 to  $250^{\circ}$ C.[18] Applied forces, F, are expressed in voltage applied to the piezo tip. From these voltages, we can estimate the forces in newtons (Supporting Information). Force pulse,  $F_p$  is the duration for which the heated tip is in contact with each pixel on the surface. (c,d) Comparison of nano-ironed (with heat) and nano-broomed (without heat) areas at comparable F and  $F_P$  showing a substantially cleaner surface after nano-ironing. The AFM images in c and d share the same height scale bar. Respective line cuts are overlayed in blue, with the height scale indicated by the blue arrow. Root-mean-square (RMS) roughness values are calculated from the areas enclosed by the dashed squares, with  $300\pm40$  pm and  $1.20\pm0.3$  nm for nano-ironing and nano-brooming respectively.

3a). Our device consists of a hBN/WS<sub>2</sub>/hBN stack with a graphitic back gate electrode to tune the overall 2DEG carrier density. Local electrostatic control is induced through two split top gates (labelled TG1 and TG2) with a separation of  $\sim 70$  nm (Figure 3b). Before the top hBN dielectric is transferred over the WS<sub>2</sub> channel, In/Au contacts are lithographically defined which leaves behind resist residue. Nano-ironing removes this resist residue before top hBN encapsulation resulting in a clean interface for cryogenic quantum transport measurements.

We first assess the electrical transport characteristics of our vdW heterostructure at cryogenic temperatures. The transfer and output curves of the device measured at a temperature of 43 mK are shown in Figure 3c where we observe typical *n*-type semiconducting behaviour. The high-quality of our In/Au contacts with negligibly low Schottky barrier heights are confirmed from the linear output characteristics.[41, 42] Correspondingly, we measure a low device resistance  $R \sim 25 \text{ k}\Omega$ , indicating that contacts are sufficiently transparent with contact resistances  $R_{\rm C} < R/2=12.5 \text{ k}\Omega$ .

Next, we evaluate the electrical tunability of our device. We measure the device conductance G with standard low frequency lock-in measurements as a function of the back gate voltage  $V_{\rm BG}$  and a common top gate voltage  $V_{\rm TG}$  applied to both split top gates TG1 and TG2 (Figure 3d). The white symbols in Figure 3d indicate the transport regimes described below and in the inset schematics. We find that G can be effectively modulated by both  $V_{\rm BG}$  and  $V_{\rm TG}$ . A more positive  $V_{\rm BG}$  increases

FIG. 2. Electrical transport improvements from nano-ironing. (a) Schematics of a back-gated 2D WS<sub>2</sub> field effect transistor subjected to the nano-ironing process. (b) Transfer curves measured at 80 K for 4 separate devices before (black, unfilled) and after (blue, filled) nano-ironing. Carrier field-effect mobilities  $\mu_{\rm FE}$  and threshold voltages  $V_{\rm th}$  determined from the linear regimes show significant changes from nano-ironing. We observe between ~2 to 10-fold improvements in  $\mu_{\rm FE}$  and negative shifts of ~3 to 11 V in  $V_{\rm th}$ .

the overall carrier density and G. At small negative  $V_{\rm TG}$ , the electrostatic modulation is insufficient to deplete the local carrier densities underneath the gates resulting in current flow (star). With increasingly negative  $V_{\rm TG}$ , the local carrier densities are sufficiently depleted until current flow is largely restricted along the constriction between the split gates (pentagon), before complete pinchoff (circle).

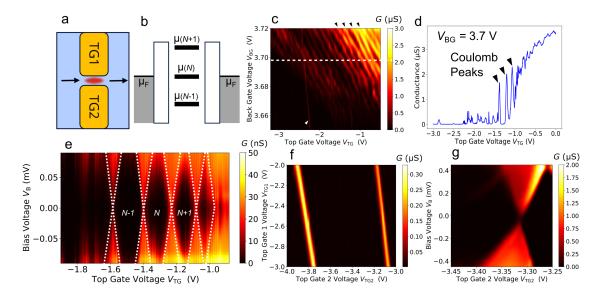

Having shown dual gate control, we next demonstrate the electrical formation of quantum dots. Negative voltages on the nanoscale split top gates can create electrostatic potential wells that confine islands of charged carriers, i.e., quantum dots (Figure 4a). Such quantum confinement is only possible in 2DEGs with a low degree of disorder. Otherwise, the disorder can dominate transport through the creation of highly untunable accidental quantum dots.[32, 43–45] Quantum dot formation results in a transition from macroscopic current flow to the single-electron transport regime, where electron-electron interactions lead to Coulomb blockade. [28] In this regime, transport across the device is Coulomb blocked unless an electrochemical potential level of the quantum dot is in resonance with the Fermi levels of the electrodes (Figure 4b), which then manifest as Coulomb conductance peaks.

Tunability of an electrically defined quantum dot by both  $V_{\rm BG}$  and  $V_{\rm TG}$  indicates their formation in the narrow constriction between the split top gates. Indeed, we observe such resonances in the form of several diagonal lines (indicated by the black arrows) in Figure 4c. Other resonances can also be observed (white arrow). As mentioned, these are likely due to accidental disorderinduced quantum dots located directly under a top gate rather than in the narrow constriction, and so appears as a nearly vertical line largely tunable only by  $V_{\rm TG}$ . The transition from macroscopic current flow to Coulomb blockade can be visualised from Figure 4d which shows 1D G sweeps. Strong Coulomb conductance peaks are observed as expected (black arrows).

The clearest indication of Coulomb blockade is obtained from transport spectroscopy of stability diagrams where G is measured while changing the bias voltage  $V_{\rm B}$ and  $V_{\rm TG}$  (Figure 4e). With increasingly negative  $V_{\rm TG}$ , we observe the appearance of consecutively larger diamondshaped regions of suppressed conductance. This is due to Coulomb blockade where no electrochemical potential levels of the quantum dot lie within the applied bias window and the total charge N on the quantum dot is stable. The heights of these Coulomb diamonds along the  $V_{\rm B}$  axis give the charging energy  $E_{\rm C}$  of the quantum dot.  $E_{\rm C}$  is the energy required to add/remove an electron from the island arising from electron-electron Coulombic repulsion and is inversely proportional to the quantum dot radius r.[22, 28] The increase in Coulomb diamond heights with increasingly negative  $V_{\rm TG}$  is thus consistent

FIG. 3. Nano-ironing two-dimensional van der Waals heterostructure. (a) Schematic illustration of our device consisting of a few-layer graphite back gate (BG), hBN/WS<sub>2</sub>/hBN heterostructure with source-drain contacts (S/D), and split top gate electrodes (TG1/TG2). (b) Optical image of the device with labelled electrodes. Scale bar 10  $\mu$ m. The inset shows a scanning electron micrograph of the split top gates separated by a gap of ~70 nm. The few-layer graphene back gate (BG) modulates the overall carrier density in the WS<sub>2</sub> channel and is separated by a 10 nm thick hBN dielectric. Another 16 nm thick top hBN dielectric layer electrically insulates the WS<sub>2</sub> channel from the split top gates used for local modulation of the electrostatic potential in the WS<sub>2</sub> channel. Transport measurements of our van der Waals heterostructure at a temperature of 43 mK. (c) Transfer curves showing typical *n*-type transistor characteristics. The inset shows the output curves where linear ohmic behaviour highlights the high quality In/Au contacts with low Schottky barrier heights. (d) Device conductance *G* as a function of the back gate voltage V<sub>BG</sub> and a common top gate voltage V<sub>TG</sub> applied to both split top gates. Schematic illustrations of the transport regimes indicated by the white circle, pentagon, and star symbols are shown in the lower left. Increasingly negative V<sub>TG</sub> depletes the local carrier density restricting the current flow to a narrow constriction between the split gates before eventual pinch-off.

with a decrease in the quantum dot size from stronger electrostatic confinement.

We further confirm gate tunability of the quantum dots with independent top gate sweeps of gates TG1 and TG2. We again observe diagonal Coulomb peak resonances in Figure 4f which shows G as a function of  $V_{\rm TG1}$  and  $V_{\rm TG2}$ . The resonance slope values are ~5, indicating that the dot is more strongly coupled to TG2 than TG1. Using only TG2, we can also observe a Coulomb peak transition in the bias stability diagram (Figure 4g). However, we note that the single gate tunability range is limited as it also results in a more asymmetric confinement potential. Future devices implementing additional independent gates for improved control over tunnel couplings should open up wider possibilities for 2D material-based quantum devices.

Beyond transport in nano- and quantum electronics, nano-ironing can be useful in many other applications. For example, reducing subthreshold swings is important for fast, low-power transistors but gate capacitances can be limited by resist residue.[46, 47] Nano-ironing can lead to fast transistors with subthreshold swings approaching the thermionic limit of 60 mV/dec.[48] In opto-electronics, resist residual removal improves photon absorption (emission) for photo-detectors (photoemitters).[49, 50] Excitonic resonances in 2D TMDs are

FIG. 4. Electrical formation and control of quantum dots. (a) Schematic illustration of gate-induced quantum dot formation along the channel and (b) single-electron transport. The bias voltage defines the Fermi levels  $\mu_{\rm F}$  of the left and right electrodes. A gate voltage controls the quantized electrochemical potential  $\mu_N$  of the quantum dot transitions from an occupation state of N electrons to N+1. Resonant single electron transport occurs when  $\mu_N$  is aligned with  $\mu_{\rm F}$  of the electrodes. Such resonances are observed in (c) which shows the device conductance G as a function of the back gate voltage  $V_{\rm BG}$  and a common top gate voltage  $V_{\rm TG}$  applied to both split top gates. Several diagonal parallel resonances (black arrows) due to quantum dot formation along the constriction are observed. A vertical resonance with a different slope is also present (white arrow) suggestive of disorder induced accidental quantum dots localised under the top gate. (d) Device conductance G as a function of top gate voltage  $V_{\rm TG}$  at a fixed back gate voltage  $V_{\rm BG}=3.7$  V (white horizontal dashed line in c) showing Coulomb peaks (black arrows) from resonant transport across the quantum dot. (e) Charge stability diagram showing diamond shaped regions of suppressed conductance indicative of Coulomb blockade at  $V_{\rm BG}=3.7$  V. The diamond sizes increase with more negative  $V_{\rm TG}$  due to a reduction in quantum dot size with stronger electrostatic confinement. (f) Device conductance G as a function of  $V_{\rm TG1}$  and  $V_{\rm TG2}$  with  $V_{\rm BG}=3.6$  V showing that the dot can be modulated by both split top gates. (g) Higher resolution stability diagram showing a Coulomb peak transition tuned by a single top gate 2 voltage  $V_{\rm TG2}$  with  $V_{\rm BG} = 3.6$  V and  $V_{\rm TG1} = -1.5$  V.

sensitive to the dielectric environment which can be dominated by resist residue.[51] Nano-ironing can improve exciton lifetimes and yields including inter-layer excitonic species in vdW heterostructures. In bio-sensing applications, device sensitivity and specificity can benefit from increased useful surface areas for detection or functionalization.[47, 52] Valleytronic and spintronic devices can expect improved valley/spin lifetimes and diffusion lengths from reduced roughness and impurity scattering with cleaner vdW surfaces.[26, 53, 54] Proximity induced effects such as anomalous Hall effect[55] and Zeeman Spin Hall effect[56] are also strongly dependent on interface cleanliness and can benefit from nano-ironing.

In summary, we show that a heated nano-probe tip efficiently removes residual resist (nano-ironing). This reduces surface roughness and recovers an atomically flat vdW material surface. Nano-ironed monolayer WS<sub>2</sub> transistors display improved electrical performance with reduced unwanted charge doping, higher carrier mobilities, and higher drain currents. Nano-ironing is useful for building vdW heterostructures with ultra-clean interfaces to create homogeneous 2DEGs for cryogenic quantum transport studies. We demonstrate electrical confinement and control of quantum dots in nano-ironed vdW heterostructures, enabling the transition from macroscopic current flow to single-electron transport regime. Such vdW heterostructure based quantum dots are useful platforms to unveil fundamental transport physics and important building blocks for quantum information processing applications. Nano-ironing thus paves the way towards new fabrication approaches and device architectures for vdW heterostructures.

### V. MATERIALS AND METHODS

# A. Thermal scanning probe for lithography and nano-ironing

The t-SPL system used for both contact patterning and nano-ironing was a Nanofrazor Scholar from Heidelberg Instruments kept in an inert glovebox. For t-SPL patterning procedure we spincoat a bi-layer resist stack consisting of 30/110 nm of polyphthalaldehyde (PPA) / poly (methyl methacrylate-co-methacrylic acid) (PMMA-MA) at 4000 rpm for 40 seconds. Samples are baked at 140 °C for 90 seconds after spinning the PMMA- MA layer, and at 110 °C for 120 seconds after spinning the PPA layer. After patterning, we etched the exposed PMMA-MA using 20 °C ethanol for 15 seconds. For t-SPL nano-ironing, a heater temperature of 1100 °C, a write force of 7.5 V, and a force pulse of 450 microseconds per pixel is used.

### B. Device fabrication

Device fabrication were conducted in an inert glovebox unless otherwise stated. CVD grown monolayer WS<sub>2</sub> was transferred onto the Si/SiO<sub>2</sub> device substrate via a PPC assisted transfer method.[57] The transfer method involves preparation steps which must be done outside of the glovebox. However, the final transfer of the CVD WS<sub>2</sub> onto Si/SiO<sub>2</sub> is performed inside the glovebox. 5/35nm In/Au contacts were defined via: (i) thermal scanning probe lithography (t-SPL) (ii) thermal evaporation (iii) lift-off. 2/50 nm Cr/Au lines and pads were then defined via: (i) Electron beam lithography (EBL) (ii) thermal evaporation (iii) lift-off. Electron beam lithography was carried out outside of the glove-box. Samples were passivated with resist while being transported between systems.

For the heterostructure device, we exfoliated graphite, hBN, and WS<sub>2</sub> flakes and stacked them with standard polymer-assisted dry transfer methods on an automated transfer stage setup.[58] After patterning the source, drain, and back-gate contacts with t-SPL, (channel length of 1.5  $\mu$ m with a width of ~4  $\mu$ m), we deposited 5/35 nm of In/Au alloy via thermal evaporator. After lift-off, we conducted nano-ironing on the channel to clean the interface, then used the same stacking system to encapsulate the channel with a top layer of hBN. We patterned the split gates (separated by ~70 nm with a width of ~800 nm) through EBL followed by Cr/Au (3/22 nm) metal deposition. Subsequent lines and pads were also defined by EBL, followed by 5/55 nm of Cr/Au deposition.

Further details of nanofabrication recipes and pro-

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Electric field effect in atomically thin carbon films, Science **306**, 666 (2004).

- [2] S. J. Haigh, A. Gholinia, R. Jalil, S. Romani, L. Britnell, D. C. Elias, K. S. Novoselov, L. A. Ponomarenko, A. K. Geim, and R. Gorbachev, Cross-sectional imaging of individual layers and buried interfaces of graphene-based heterostructures and superlattices, Nature Materials 11, 764 (2012).

- [3] A. K. Geim and I. V. Grigorieva, Van der Waals heterostructures, Nature 499, 419 (2013).

- [4] F. Pizzocchero, L. Gammelgaard, B. S. Jessen, J. M. Caridad, L. Wang, J. Hone, P. Bøggild, and T. J. Booth,

cesses can be found in the Supporting Information.

### C. FET transport measurements

FET transport measurements were conducted in a vacuum cryoprobe station cooled down to 80 K at a base pressure of  $\sim 10^{-6}$  Torr. All electrical measurements were carried out with a Keithley 2450 source meter.

### D. Quantum transport measurements

Quantum transport measurements were conducted in a BlueFors XLD dilution refrigerator at a base temperature of 43 mK using a Nanonis Tramea measurement system. E. Optical measurements

Room temperature PL and Raman spectroscopy were done through Invia Raman Renishaw system. The point spectra were obtained using a 532 nm laser with  $\times 100$  objective (NA = 0.85) and 2400  $l/\rm mm$  grating. The excitation power was kept below 50  $\mu\rm W$  to avoid any unintentional degradation due to laser-induced heating. The mapping was performed by scanning the sample in 7  $\times$  7  $\mu\rm m$  area through the same laser excitation.

### ACKNOWLEDGMENTS

This research was supported by the Agency for Science, Technology, and Research (A\*STAR) under its MTC YIRG grant No. M21K3c0124. We acknowledge the funding support from the Agency for Science, Technology and Research (#21709, C230917006, C230917007). K.E.J.G. acknowledges support from a Singapore National Research Foundation Grant (CRP21-2018-0001). D.H. acknowledges funding support from A\*STAR Project C222812022 and MTC YIRG M22K3c0105.

The hot pick-up technique for batch assembly of van der Waals heterostructures, Nature Communications 7, 11894 (2016).

- [5] Y. Cao, V. Fatemi, S. Fang, K. Watanabe, T. Taniguchi, E. Kaxiras, and P. Jarillo-Herrero, Unconventional superconductivity in magic-angle graphene superlattices, Nature 556, 43 (2018).

- [6] A. L. Sharpe, E. J. Fox, A. W. Barnard, J. Finney, K. Watanabe, T. Taniguchi, M. A. Kastner, and D. Goldhaber-Gordon, Emergent ferromagnetism near three-quarters filling in twisted bilayer graphene, Science **365**, 605 (2019).

- [7] Z. Zheng, Q. Ma, Z. Bi, S. de La Barrera, M.-H. Liu, N. Mao, Y. Zhang, N. Kiper, K. Watanabe, T. Taniguchi,

*et al.*, Unconventional ferroelectricity in moiré heterostructures, Nature **588**, 71 (2020).

- [8] M. Serlin, C. L. Tschirhart, H. Polshyn, Y. Zhang, J. Zhu, K. Watanabe, T. Taniguchi, L. Balents, and A. F. Young, Intrinsic quantized anomalous hall effect in a moiré heterostructure, Science 367, 900 (2020).

- [9] Y. Dan, Y. Lu, N. J. Kybert, Z. Luo, and A. T. C. Johnson, Intrinsic response of graphene vapor sensors, Nano Letters 9, 1472 (2009).

- [10] Z. Cheng, Q. Zhou, C. Wang, Q. Li, C. Wang, and Y. Fang, Toward intrinsic graphene surfaces: A systematic study on thermal annealing and wet-chemical treatment of sio2-supported graphene devices, Nano Letters 11, 767 (2011).

- [11] K. Bolotin, K. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P. Kim, and H. Stormer, Ultrahigh electron mobility in suspended graphene, Solid State Communications 146, 351 (2008).

- [12] N. Lindvall, A. Kalabukhov, and A. Yurgens, Cleaning graphene using atomic force microscope, Journal of Applied Physics 111, 64904 (2012).

- [13] M. R. Rosenberger, H. J. Chuang, K. M. McCreary, A. T. Hanbicki, S. V. Sivaram, and B. T. Jonker, Nano-"Squeegee" for the Creation of Clean 2D Material Interfaces, ACS Applied Materials and Interfaces 10, 10379 (2018).

- [14] Y. Kim, P. Herlinger, T. Taniguchi, K. Watanabe, and J. H. Smet, Reliable Postprocessing Improvement of van der Waals Heterostructures, ACS Nano 13, 14182 (2019).

- [15] S. K. Palai, M. Dyksik, N. Sokolowski, M. Ciorga, E. Sánchez Viso, Y. Xie, A. Schubert, T. Taniguchi, K. Watanabe, D. K. Maude, A. Surrente, M. Baranowski, A. Castellanos-Gomez, C. Munuera, and P. Plochocka, Approaching the Intrinsic Properties of Moiré Structures Using Atomic Force Microscopy Ironing., Nano Letters 23, 4749 (2023).

- [16] Y. Liu, X. Duan, H.-J. Shin, S. Park, Y. Huang, and X. Duan, Promises and prospects of two-dimensional transistors, Nature 591, 43 (2021).

- [17] C. S. Lau, J. A. Mol, J. H. Warner, and G. A. D. Briggs, Nanoscale control of graphene electrodes, Phys. Chem. Chem. Phys. 16, 20398 (2014).

- [18] X. Zheng, A. Calò, E. Albisetti, X. X. Liu, A. S. M. Alharbi, G. Arefe, X. X. Liu, M. Spieser, W. J. Yoo, T. Taniguchi, K. Watanabe, C. Aruta, A. Ciarrocchi, A. Kis, B. S. Lee, M. Lipson, J. Hone, D. Shahrjerdi, and E. Riedo, Patterning metal contacts on monolayer MoS<sub>2</sub> with vanishing Schottky barriers using thermal nanolithography, Nature Electronics **2**, 17 (2019).

- [19] E. Albisetti, A. Calò, A. Zanut, X. Zheng, G. M. de Peppo, and E. Riedo, Thermal scanning probe lithography, Nature Reviews Methods Primers 2, 32 (2022).

- [20] A. Pirkle, J. Chan, A. Venugopal, D. Hinojos, C. W. Magnuson, S. McDonnell, L. Colombo, E. M. Vogel, R. S. Ruoff, and R. M. Wallace, The effect of chemical residues on the physical and electrical properties of chemical vapor deposited graphene transferred to SiO<sub>2</sub>, Applied Physics Letters **99**, 122108 (2011).

- [21] J. W. Suk, W. H. Lee, J. Lee, H. Chou, R. D. Piner, Y. Hao, D. Akinwande, and R. S. Ruoff, Enhancement of the electrical properties of graphene grown by chemical vapor deposition via controlling the effects of polymer residue, Nano Letters 13, 1462 (2013).

- [22] C. S. Lau, J. Y. Chee, L. Cao, Z. Ooi, S. W. Tong, M. Bosman, F. Bussolotti, T. Deng, G. Wu, S.-W. Yang, T. Wang, S. L. Teo, C. P. Y. Wong, J. W. Chai, L. Chen, Z. M. Zhang, K. Ang, Y. S. Ang, and K. E. J. Goh, Gate-Defined Quantum Confinement in CVD 2D WS<sub>2</sub>, Advanced Materials **34**, 2103907 (2022).

- [23] D. Kieczka, T. Durrant, K. Milton, K. E. J. Goh, M. Bosman, and A. Shluger, Defects in WS 2 monolayer calculated with a nonlocal functional: any difference from GGA?, Electronic Structure 5, 024001 (2023).

- [24] Y. Zhang, V. W. Brar, C. Girit, A. Zettl, and M. F. Crommie, Origin of spatial charge inhomogeneity in graphene, Nature Physics 5, 722 (2009).

- [25] J. Martin, N. Akerman, G. Ulbricht, T. Lohmann, J. H. Smet, K. von Klitzing, and A. Yacoby, Observation of electron-hole puddles in graphene using a scanning single-electron transistor, Nature Physics 4, 144 (2008).

- [26] K. E. J. Goh, F. Bussolotti, C. S. Lau, D. Kotekar-Patil, Z. E. Ooi, and J. Y. Chee, Toward Valley-Coupled Spin Qubits, Advanced Quantum Technologies 3, 1900123 (2020).

- [27] X. Liu and M. C. Hersam, 2D materials for quantum information science, Nature Reviews Materials 4, 669 (2019).

- [28] R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, Spins in few-electron quantum dots, Reviews of Modern Physics 79, 1217 (2007).

- [29] A. R. Montblanch, M. Barbone, I. Aharonovich, M. Atatüre, and A. C. Ferrari, Layered materials as a platform for quantum technologies, Nature Nanotechnology 18, 555 (2023).

- [30] N. P. de Leon, K. M. Itoh, D. Kim, K. K. Mehta, T. E. Northup, H. Paik, B. S. Palmer, N. Samarth, S. Sangtawesin, and D. W. Steuerman, Materials challenges and opportunities for quantum computing hardware, Science **372**, eabb2823 (2021).

- [31] C. S. Lau, J. Y. Chee, D. Thian, H. Kawai, J. Deng, S. L. Wong, Z. E. Ooi, Y.-F. Lim, and K. E. J. Goh, Carrier control in 2D transition metal dichalcogenides with Al<sub>2</sub>O<sub>3</sub> dielectric, Scientific Reports 9, 8769 (2019).

- [32] Z.-Z. Z. Zhang, X.-X. X. Song, G. Luo, G.-W. W. Deng, V. Mosallanejad, T. Taniguchi, K. Watanabe, H.-O. O. Li, G. Cao, G.-C. C. G.-P. P. Guo, F. Nori, and G.-C. C. G.-P. P. Guo, Electrotunable artificial molecules based on van der Waals heterostructures, Science Advances 3, 1 (2017).

- [33] M. Hamer, E. Tóvári, M. Zhu, M. D. Thompson, A. Mayorov, J. Prance, Y. Lee, R. P. Haley, Z. R. Kudrynskyi, A. Patanè, D. Terry, Z. D. Kovalyuk, K. Ensslin, A. V. Kretinin, A. Geim, and R. Gorbachev, Gate-Defined Quantum Confinement in InSe-Based van der Waals Heterostructures, Nano Letters 18, 3950 (2018).

- [34] K. Wang, K. De Greve, L. A. Jauregui, A. Sushko, A. High, Y. Zhou, G. Scuri, T. Taniguchi, K. Watanabe, M. D. Lukin, H. Park, and P. Kim, Electrical control of charged carriers and excitons in atomically thin materials, Nature Nanotechnology 13, 128 (2018).

- [35] R. Pisoni, Z. Lei, P. Back, M. Eich, H. Overweg, Y. Lee, K. Watanabe, T. Taniguchi, T. Ihn, and K. Ensslin, Gate-Tunable Quantum Dot in a High Quality Single Layer MoS<sub>2</sub> Van der Waals Heterostructure, Applied Physics Letters **123101**, 2016 (2018).

- [36] M. Eich, R. Pisoni, H. Overweg, A. Kurzmann, Y. Lee, P. Rickhaus, T. Ihn, K. Ensslin, F. Herman, M. Sigrist,

K. Watanabe, and T. Taniguchi, Spin and Valley States in Gate-Defined Bilayer Graphene Quantum Dots, Physical Review X 8, 1 (2018).

- [37] S. Davari, J. Stacy, A. M. Mercado, J. D. Tull, R. Basnet, K. Pandey, K. Watanabe, T. Taniguchi, J. Hu, and H. O. Churchill, Gate-Defined Accumulation-Mode Quantum Dots in Monolayer and Bilayer WSe<sub>2</sub>, Physical Review Applied **13**, 1 (2020).

- [38] J. Boddison-Chouinard, A. Bogan, N. Fong, K. Watanabe, T. Taniguchi, S. Studenikin, A. Sachrajda, M. Korkusinski, A. Altintas, M. Bieniek, P. Hawrylak, A. Luican-Mayer, and L. Gaudreau, Gate-controlled quantum dots in monolayer WSe<sub>2</sub>, Applied Physics Letters **119**, 133104 (2021).

- [39] L. Wang, I. Meric, P. Y. Huang, Q. Gao, Y. Gao, H. Tran, T. Taniguchi, K. Watanabe, L. M. Campos, D. A. Muller, J. Guo, P. Kim, J. Hone, K. L. Shepard, and C. R. Dean, One-dimensional electrical contact to a two-dimensional material, Science **342**, 614 (2013).

- [40] S. Xu, Z. Wu, H. Lu, Y. Han, G. Long, X. Chen, T. Han, W. Ye, Y. Wu, J. Lin, J. Shen, Y. Cai, Y. He, F. Zhang, R. Lortz, C. Cheng, and N. Wang, Universal low-temperature Ohmic contacts for quantum transport in transition metal dichalcogenides, 2D Materials 3, 021007 (2016).

- [41] C. S. Lau, J. Y. Chee, Y. S. Ang, S. W. Tong, L. Cao, Z.-E. Ooi, T. Wang, L. K. Ang, Y. Wang, M. Chhowalla, and K. E. J. Goh, Quantum Transport in Two-Dimensional WS<sub>2</sub> with High-Efficiency Carrier Injection through Indium Alloy Contacts, ACS Nano 14, 13700 (2020).

- [42] X. Zheng, A. Calò, E. Albisetti, X. Liu, A. S. M. Alharbi, G. Arefe, X. Liu, M. Spieser, W. J. Yoo, T. Taniguchi, K. Watanabe, C. Aruta, A. Ciarrocchi, A. Kis, B. S. Lee, M. Lipson, J. Hone, D. Shahrjerdi, and E. Riedo, Patterning metal contacts on monolayer MoS<sub>2</sub> with vanishing Schottky barriers using thermal nanolithography, Nature Electronics 2, 17 (2019).

- [43] X. L. Liu, D. Hug, and L. M. K. Vandersypen, Gatedefined graphene double quantum dot and excited state spectroscopy, Nano Letters 10, 1623 (2010).

- [44] K. Lee, G. Kulkarni, and Z. Zhong, Coulomb blockade in monolayer MoS<sub>2</sub> single electron transistor, Nanoscale 8, 7755 (2016).

- [45] M. Brotons-Gisbert, A. Branny, S. Kumar, R. Picard, R. Proux, M. Gray, K. S. Burch, K. Watanabe, T. Taniguchi, and B. D. Gerardot, Coulomb blockade in an atomically thin quantum dot coupled to a tunable Fermi reservoir, Nature Nanotechnology 14, 442 (2019).

- [46] Y. Zhang, D. Venkatakrishnarao, M. Bosman, W. Fu, S. Das, F. Bussolotti, R. Lee, S. L. Teo, D. Huang, I. Verzhbitskiy, Z. Jiang, Z. Jiang, J. Chai, S. W. Tong, Z.-E. Ooi, C. P. Y. Wong, Y. S. Ang, K. E. J. Goh, and C. S. Lau, Liquid-Metal-Printed Ultrathin Oxides for Atomically Smooth 2D Material Heterostructures, ACS Nano 17, 7929 (2023).

- [47] C. S. Lau, S. Das, I. A. Verzhbitskiy, D. Huang, Y. Zhang, T. Talha-Dean, W. Fu, D. Venkatakrishnarao, and K. E. Johnson Goh, Dielectrics for two-dimensional transitionmetal dichalcogenide applications, ACS Nano 17, 9870 (2023).

- [48] S. Das, A. Sebastian, E. Pop, C. J. McClellan, A. D. Franklin, T. Grasser, T. Knobloch, Y. Illarionov, A. V. Penumatcha, J. Appenzeller, Z. Chen, W. Zhu, I. Asselberghs, L. J. Li, U. E. Avci, N. Bhat, T. D. Anthopoulos, and R. Singh, Transistors based on two-dimensional materials for future integrated circuits, Nature Electronics 4, 786 (2021).

- [49] H. Tan, Y. Fan, Y. Rong, B. Porter, C. Lau, Y. Zhou, Z. He, S. Wang, H. Bhaskaran, and J. Warner, Doping Graphene Transistors Using Vertical Stacked Monolayer WS<sub>2</sub> Heterostructures Grown by Chemical Vapor Deposition, ACS Applied Materials and Interfaces 8, 10.1021/acsami.5b08295 (2016).

- [50] H. Tan, W. Xu, Y. Sheng, C. S. Lau, Y. Fan, Q. Chen, M. Tweedie, X. Wang, Y. Zhou, and J. H. Warner, Lateral Graphene-Contacted Vertically Stacked WS 2 /MoS 2 Hybrid Photodetectors with Large Gain, Advanced Materials **29**, 1702917 (2017).

- [51] A. Raja, A. Chaves, J. Yu, G. Arefe, H. M. Hill, A. F. Rigosi, T. C. Berkelbach, P. Nagler, C. Schüller, T. Korn, *et al.*, Coulomb engineering of the bandgap and excitons in two-dimensional materials, Nature Communications 8, 1 (2017).

- [52] D. Sarkar, W. Liu, X. Xie, A. C. Anselmo, S. Mitragotri, and K. Banerjee, MoS<sub>2</sub> field-effect transistor for next-generation label-free biosensors, ACS Nano 8, 3992 (2014).

- [53] A. Avsar, H. Ochoa, F. Guinea, B. Zyilmaz, B. J. Van Wees, and I. J. Vera-Marun, Colloquium: Spintronics in graphene and other two-dimensional materials, Reviews of Modern Physics **92**, 021003 (2020).

- [54] J. R. Schaibley, H. Yu, G. Clark, P. Rivera, J. S. Ross, K. L. Seyler, W. Yao, and X. Xu, Valleytronics in 2D materials, Nature Reviews Materials 1, 1 (2016).

- [55] Z. Wang, C. Tang, R. Sachs, Y. Barlas, and J. Shi, Proximity-induced ferromagnetism in graphene revealed by the anomalous hall effect, Phys. Rev. Lett. 114, 016603 (2015).

- [56] P. Wei, S. Lee, F. Lemaitre, L. Pinel, D. Cutaia, W. Cha, F. Katmis, Y. Zhu, D. Heiman, J. Hone, J. S. Moodera, and C. T. Chen, Strong interfacial exchange field in the graphene/eus heterostructure, Nature Materials 15, 711 (2016).

- [57] A. Mondal, C. Biswas, S. Park, W. Cha, S.-H. Kang, M. Yoon, S. H. Choi, K. K. Kim, and Y. H. Lee, Low Ohmic contact resistance and high on/off ratio in transition metal dichalcogenides field-effect transistors via residue-free transfer, Nature Nanotechnology (2023).

- [58] S. Mukherjee, D. Dutta, A. Ghosh, and E. Koren, Graphene-in<sub>2</sub>se<sub>3</sub> van der waals heterojunction neuristor for optical in-memory bimodal operation, ACS Nano 17, 22287 (2023).