# SMT-Based Model Checking of Industrial Simulink Models

Daisuke Ishii<sup>1</sup>, Takashi Tomita<sup>1</sup>, Toshiaki Aoki<sup>1</sup>, The Quyen Ngo<sup>2</sup>, Thi Bich Ngoc Do<sup>3</sup>, and Hideaki Takai<sup>4</sup>

**Abstract.** The development of embedded systems requires formal analvsis of models such as those described with MATLAB/Simulink. However, the increasing complexity of industrial models makes analysis difficult. This paper proposes a model checking method for Simulink models using SMT solvers. The proposed method aims at (1) automated, efficient and comprehensible verification of complex models, (2) numerically accurate analysis of models, and (3) demonstrating the analysis of Simulink models using an SMT solver (we use Z3). It first encodes a target model into a predicate logic formula in the domain of mathematical arithmetic and bit vectors. We explore how to encode various Simulink blocks exactly. Then, the method verifies a given invariance property using the k-induction-based algorithm that extracts a subsystem involving the target block and unrolls the execution paths incrementally. In the experiment, we applied the proposed method and other tools to a set of models and properties. Our method successfully verified most of the properties including those unverified with other tools.

Keywords: SMT solvers  $\cdot$  Model checking  $\cdot$  MATLAB/Simulink

## 1 Introduction

Complex embedded systems are developed using a model-based approach, in which a *model* of a system is developed virtually before the actual implementation [18]; typical development targets are vehicles and robots. *MATLAB/Simulink* (Sect. 2) is a tool for developing cyber-physical system (CPS) models. It provides a graphical language and a numerical simulation engine.

As ISO-26262 recommends, formal analysis of models is important to assure the quality of products in the model-based development. A MATLAB toolbox Simulink Design Verifier (SLDV) (Sect. 6) provides a set of blocks to represent properties and dedicated model checking functions. Notably, checking invariance properties plays a crucial role in test generation. However, as industrial models become complex, several issues arise in the formal analysis:

- Scalability issue due to the increase in the time taken by checking properties.

<sup>&</sup>lt;sup>1</sup> Japan Advanced Institute of Science and Technology, Japan <sup>2</sup> VNU University of Science, Vietnam

<sup>&</sup>lt;sup>3</sup> Posts and Telecommunications Institute of Technology, Vietnam

<sup>4</sup> GAIO Technology Co., Japan

- Reliability issue due to the approximation applied during model checking by the tools such as SLDV.

- Explainability issue. The detail of the model checking process and the underlying "formal methods" of the tool are unknown.

SMT solvers [17] are a core technology of formal methods [3]. They handle decision problem instances in various domains e.g. reals, integers, and bit vectors. Recently, it has become possible to verify properties on floating-point (FP) numbers [7]. In terms of application, they have been applied to analysis of Simulink models (e.g. [22,12,5]). Yet state-of-the-art solvers are efficient, their scalability is limited in principle; in our preliminary experiments, the execution time blew up when analyzing industrial Simulink models directly.

The objective of this paper is to realize an invariance model checking method that is efficient, formal and comprehensible. We also aim at a feasibility study of analyzing industrial Simulink models using SMT solvers. The contributions of this paper are summarized as follows:

- SMT-based model checking method. We consider invariance properties and verify them with SMT-based model checking (Sect. 3). The method consists of an encoder from Simulink models to logic formulas (in SMT-LIB format) and a model checker. We present two encoding methods (Sect. 4): Approximate encoding based on mathematical numerals and exact encoding based on bit vectors. For model checking, we propose an algorithm that iteratively applies k-induction while expanding the paths unrolled and the local subsystem scope (Sect. 5).

- Experimental results with artificial and industrial Simulink models. Sect. 6 reports the results of the verification of nine models; we experimented using the proposed method, SLDV and CoCoSim for comparison. We explain that our method processed the models correctly and effectively; the advantages over the other tools and the validity of using our method in industrial settings are discussed.

#### 2 Simulink

Simulink<sup>5</sup> is a MATLAB toolbox for modeling synchronous and hybrid systems based on a graphical language. The targets are described as timed models, either with a continuous timeline or with a timeline discretized with a fixed sample time; in this work, we assume the latter. Simulink models are diagrams representing hierarchical directed graphs with edges, called *lines*, and nodes, called *blocks*, of various kinds.

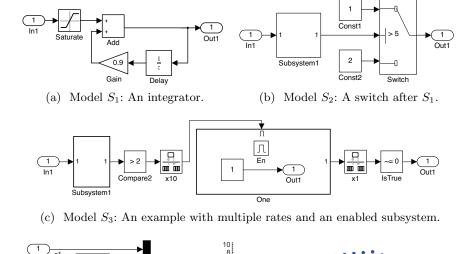

Example Simulink models are shown in Fig. 1. Model  $S_1$  describes an integration with a feedback loop, in which the input value is added with the output value of the previous step with gain 0.9; here, blocks of type Add, Constant, Gain and Unit Delay are utilized; also, block Saturate is used to limit the input range to [-1,1]. Each block is configured with its *parameters* such as gain

<sup>&</sup>lt;sup>5</sup> https://www.mathworks.com/products/simulink.html.

Fig. 1. Example Simulink models.

(e) Example of executing  $S_1$ .

(d) Model  $S_4$ : Bus signal.

factor, saturation threshold, and data type of the signal to be processed. Model  $S_2$  embeds  $S_1$  as a *subsystem* to model in a hierarchical way.  $S_2$  describes a branch using a Switch block that outputs a constant signal with a value of 1 or 2, depending on whether the input is greater than 5 or not. Model  $S_3$  is a more complex example with rate transition and a subsystem with an Enable port. Initially, the subsystem One is deactivated (outputs 0); it will be activated when Compare2 outputs true, but the activation occurs at a 10-fold period. Model  $S_4$  exemplifies matrix and bus signals. It outputs a signal that combines two named elements, a scalar signal e1 and a matrix signal e2.

Primary function of Simulink is numerical simulation, i.e. to obtain output signals of models. In this paper, we regard a signal as a bounded sequence of output values; j-th value is output at time  $j \times st$  ( $j \ge 0$  and st is a configured sample time). Example input and output signals are shown in Fig. 1e.

Simulink models have a tree structure consisting of subsystems. Accordingly, each block in models can be located by a path i.e. a sequence of subsystem names ending with a block name. We will use this structure to analyze models locally.

Formalization of Simulink models. A discrete-time Simulink model can be regarded as a transition system.  $^6$

<sup>&</sup>lt;sup>6</sup> This formalization may not be applicable to some discrete-time Simulink models, e.g. signal delays for variable lengths. Support for such models is a future work.

**Definition 1.** Assume sets  $V_i$ ,  $V_o$  and  $V_s$  of input, output, and state variables. For a set of variables  $V = \{v_1, \ldots, v_n\}$ , we denote their domain  $D_1 \times \cdots \times D_n$  by D(V). A transition system  $(\mathcal{I}, \mathcal{T})$  consists of an initial condition  $\mathcal{I} \subseteq D(V_s)$  and a transition relation  $\mathcal{T} \subseteq D(V_s) \times D(V_s) \times D(V_i) \times D(V_o)$ .

The model  $S_1$  is interpreted as  $(\mathcal{I}_1, \mathcal{T}_1)$ , where:

$$\mathcal{I}_1(s) :\Leftrightarrow s = 0, \quad \mathcal{T}_1(s, s', i, o) :\Leftrightarrow o = \max\{-1, \min\{i, 1\}\} + 0.9s \land s' = o.$$

Input/output variable i/o represents the value of an input/output signal at a step. The state variable s/s' is necessary for Delay to represent signal values before/after the transition. In the same way,  $S_2$  is interpreted as  $(\mathcal{I}_2, \mathcal{T}_2)$ :

$$\mathcal{I}_{2}(s) : \Leftrightarrow \mathcal{I}_{1}(s),$$

$$\mathcal{T}_{2}(s, s', i, o) : \Leftrightarrow \exists i', \exists o', \ \mathcal{T}_{1}(s, s', i', o') \land i = i' \land o = \begin{cases} 1 & \text{if } o' > 5, \\ 2 & \text{else.} \end{cases}$$

Predicates are defined based on  $(\mathcal{I}_1, \mathcal{T}_1)$ . Note how variables are handled when subsystemizing; state variables of  $S_1$  are inherited to  $S_2$ ; placeholders for the input and output of  $S_1$  are prepared locally in the rhs.

We assume that variables are typed as an instance of  $\mathit{Ty}_{C}$ , defined inductively as follows:

$$Ty_C ::= Ty_N \mid dTy_N \mid (d_1 \times \cdots \times d_m) Ty_N \mid Bus$$

$Ty_N ::= boolean \mid uintn \mid intn \mid double \mid single \mid half$

where  $d_{\square} \in \mathbb{N}$ ,  $m \geq 2$ , and  $n \in \{8, 16, 32, 64\}$ . Each term of  $Ty_C$  represents scalars, d-ary vectors, (possibly higher-dimension) matrices, and buses. Buses are concatenated values that combine named members of certain types; see Sect. 4.2 for how buses are analyzed.  $Ty_N$  consists of Boolean type, unsigned/signed integer types and three types for FP numbers. Basically, Simulink models are statically typed based on their descriptions and dialog settings. For instance, the variables i, o and s of  $S_1$  can be typed as scalar numerical type t, e.g. uint8 and double. Also, they can be typed as dt, where  $d \in \mathbb{N}$ , by configuring each block for element-wise processing of vector values.

Signals obtained by numerical simulation are formalized by execution paths.

**Definition 2.** Given  $(\mathcal{I}, \mathcal{T})$ , execution paths (or executions) of length k are

$$S_{-1} \xrightarrow{i_0/o_0} S_0 \xrightarrow{i_1/o_1} S_1 \cdots S_{k-2} \xrightarrow{i_{k-1}/o_{k-1}} S_{k-1},$$

where  $s_{\square} \in D(\mathcal{V}_s)$ ,  $i_{\square} \in D(\mathcal{V}_i)$ ,  $o_{\square} \in D(\mathcal{V}_o)$ ,  $\mathcal{I}(s_{-1})$ , and  $\mathcal{T}(s_{j-1}, s_j, i_j, o_j)$  holds for  $j \in [0, k-1]$ . Input, output and state signals are the traces  $i_0 \cdots i_{k-1}$ ,  $o_0 \cdots o_{k-1}$ , and  $s_{-1} \cdots s_{k-1}$  of an execution path.

The input and output signal values at the initial time are represented by  $i_0$  and  $o_0$ . Signals can be depicted as in Fig 1e.

<sup>&</sup>lt;sup>7</sup> Other than these types, there are types for fixed-point numbers, strings, enumeration values, and user-defined ValueType objects; support of these types is a future work.

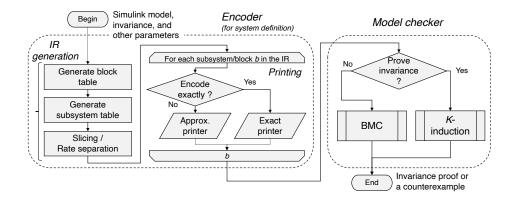

Fig. 2. Process of SMT-based model checking.

## 3 SMT-Based Model Checking

SMT (satisfiability modulo theories) solvers are automated provers for the satisfiability of logic formulas that involve predicates in various theories e.g. integer, real and FP arithmetic. In this paper, we apply a representative implementation  $Z3^8$  to the analysis of Simulink models.

We assume an invariance property of a Simulink model and verify that it holds for the model or violated in an execution. Typically, such properties can represent a test objective; a counterexample corresponds to a test case and a valid invariance indicates a dead logic.

**Definition 3.** Given a model  $(\mathcal{I}, \mathcal{T})$ , an invariance is described by a formula  $\Box \phi$ , where  $\phi \subseteq D(\mathcal{V}_i) \times D(\mathcal{V}_s)$  is a predicate on the input and state variables. Assume an execution path involving input signal  $i_0 \cdots i_{k-1}$  and state signals  $s_{-1} \cdots s_{k-1}$ . Then, it is a counterexample if  $\neg \phi(s_{j-1}, i_j)$  holds for a  $j \in [0, k-1]$ . Invariance  $\Box \phi$  holds for a model iff there is no counterexample.

For example, control condition of the Switch block in  $S_2$  is described by an invariance  $\Box(o'>5)$ , where o' represents  $\max\{-1,\min\{i,1\}\}+0.9s$ .  $S_2$  does not satisfy  $\Box(o'>5)$  as shown in Fig. 1e. The objectives in Simulink coverage testing are regarded as invariance properties defined for some block types.<sup>9</sup>

In this paper, we propose a process illustrated in Fig. 2 for checking an invariance  $\Box \phi$  of a Simulink model  $(\mathcal{I}, \mathcal{T})$ . It mainly consists of two parts:

1. Encode a target Simulink model and a property into the input format of SMT solvers (Sect. 4). It generates a definition of the transition system  $(\mathcal{I}, \mathcal{T})$  represented by the model. The predicate  $\phi$  is instrumented in the definition. The process consists of generation of intermediate representation

<sup>8</sup> https://github.com/Z3Prover/z3.

https://www.mathworks.com/help/slcoverage/ug/model-objects-that-receive -coverage.html.

- (IR) of the model and printing of the IR. The process involves several steps to handle industrial models. Notably, there are a printing step that can generates exact machine representation of numerals (Sect. 4.1), and steps for slicing and separation of different rate portions of a model (Sect. 4.2).

- 2. Model checking of the invariance  $\Box \phi$  (Sect. 5). Verification is basically done by encoding a bounded execution path of the model and by feeding it to an SMT solver. We use two methods: A bounded model checking (BMC) method for falsification and a k-induction method to prove the invariance. We propose an iterative process regarding the parameter k (Alg. 1) and a strategy to efficiently expand the target subsystem.

The basic techniques employed by the proposed method are known ones; the results of encoding are similar to those obtained by a combination of the CoCoSim [5] and Kind2 [10] tools; BMC and k-induction are basic SMT-based methods. In this work, we extend the techniques; for example, we support the encoding of industrial models and we examine a subsystem-wise model checking for efficiency; see also discussions in Sect. 7.

When a subsystem S' of a model S is given a property  $\Box \phi$ , it can be verified locally for S' or globally for S. Our subsystem-wise method starts from a local verification and gradually attempts the verification for the parent systems until the invariance is proved. Let  $\mathcal{V}_{\Box}$  and  $\mathcal{V}'_{\Box}$  be the sets of variables for S and S'. To verify globally, we consider a translation  $\phi \uparrow S$  of the predicate  $\phi$  in S, which is straightforward since  $\mathcal{V}'_s \subseteq \mathcal{V}_s$  and the Simulink model S should describe a relation in  $D(\mathcal{V}_i) \times D(\mathcal{V}_s) \times D(\mathcal{V}'_i)$  (note that  $\phi \subseteq D(\mathcal{V}'_i) \times D(\mathcal{V}'_s)$ ). There is the following relationship between the two:

**Proposition 1.** If  $\Box \phi$  holds for S',  $\Box (\phi \uparrow S)$  holds for S.

*Proof.* The contraposition obviously holds because a counterexample of  $\Box \phi$  can be extracted from that of  $\Box (\phi \uparrow S)$ .

## 4 SMT-LIB Encoding of Simulink Models

SMT-LIB [2] is an input format for SMT solvers, which has a LISP-like prefix grammar. Here, we describe the encoding method with an example. Fig. 3 lists an encoded SMT-LIB description of the model  $S_2$  (and  $S_1$  as a subsystem). At Lines 6–11, predicates  $\mathcal{I}_1$  and  $\mathcal{T}_1$  of  $S_1$  are defined as Bool-valued functions init1 and trans1. Lines 13–18 define  $(\mathcal{I}_2, \mathcal{T}_2)$  in the same way. The encoding process is either approximate or exact (Sect. 4.1); the example is an approximate encoding. Assuming that variables s, s', i and o of  $S_1$  are typed as FP numbers, they are encoded with variables s00, s01, i1 and i2 of sort Real, which represents mathematical rational numbers. In the same way, variable i3 of i4 is sorted as unbounded integers. Lines 20–23 instrument the invariance i4 (o<sub>-</sub> > 5). Two global variables curr\_step and flag\_kind and the argument i5 of transition predicates are introduced for the verification (Sect. 5). Lines 25–32 describe a length-2 execution path where values at each step are parameterized by fresh

```

;; Variable representing the current step.

(declare-const curr_step Int)

;; Whether to verify the induction step.

(declare-const flag_kind Bool)

;; Specification of subsystem S1.

(define-fun init1 ((s@O Real)) Bool (= s@O 0))

(define-fun trans1

((c Int) (s@0 Real) (s@1 Real) (i Real) (o Real)) Bool

(let ((lv (saturate 1 (- 1) i)))

10

(and (= o (+ lv (* 0.9 s@0))) (= s@1 o))))

11

12

;; Specification of the parent system S2.

(define-fun init2 ((s@O Real)) Bool (init1 s@O))

14

(define-fun trans2

15

((c Int) (s@0 Real) (s@1 Real) (i Real) (o Int)) Bool

16

(exists ((i_ Real) (o_ Real))

17

(and (trans1 c s@0 s@1 i_ o_) (= i_ i) (= o (ite (> o_ 5) 1 2))

18

;; Objective instrumentation.

(=> (= c curr_step) (not (> o_ 5)))

21

;; Assumption for the induction step.

22

(=> flag_kind (=> (< c curr_step) (> o_ 5))) )))

23

24

;; Encoding of the execution path.

25

(declare-const s@i Real) (assert (init2 s@i))

26

27

(declare-const s@O Real) (declare-const i@O Real)

28

(declare-const o@O Int) (assert (trans2 0 s@i s@O i@O o@O))

29

30

(declare-const s01 Real) (declare-const i01 Real)

31

(declare-const o@1 Int) (assert (trans2 1 s@0 s@1 i@1 o@1))

32

;; Check the reachability at step 1.

34

(check-sat-assuming (and (= curr_step 1) (not flag_kind)))

```

**Fig. 3.** Simulink models  $S_1$  and  $S_2$  encoded in SMT-LIB.

variables. The predicate init2 is asserted for the initial step -1 and trans2 is asserted for the later steps. State variables are shared between two steps. Finally, at Line 35, command (check-sat-assuming c) will invoke a solving process; it will assume the argument constraint c temporarily. With setting a step number to curr\_step and disabling flag\_kind, the violation of the invariance at step 1, i.e. reachability to the state such that  $\neg(o_- > 5)$ , should be checked. This example will result in unsat; unrolling the execution path up to step 6 will result in sat.

#### 4.1 Exact Encoding of Machine-Representable Numbers

For reliable analysis, we propose to encode FP numbers and integers using the vocabulary provided by the SMT-LIB theories FloatingPoint and BitVector. This encoding method exactly describes rounded values, overflow cases, etc. Solving exact formulas tends to be expensive; thus, we use this method along with the approximate method. FloatingPoint provides the sorts (e.g. Float64 for double-precision FP numbers), arithmetic operators (e.g. fp.add for addition), and utility functions (e.g.  $(fp.to_sbv\ n)$ ) that converts an FP number to a signed bit vectors of length n). For machine integers, we prepare necessary vocabularies based on BitVector as in [1]; we use the sort  $(BitVec\ n)$  to represent n-bit integers and define the functions for arithmetic operations, e.g. int64.add (they are defined in the beginning of the encoder outputs).

For example, the first equation in Line 11 of Fig. 3 is encoded as:

Variables o, lv and s@O are of sort Float64. RNE represents a rounding mode.

#### 4.2 Encoding of Complex Simulink Models

This section describes techniques for more complex models.

A subsystem  $(\mathcal{I}, \mathcal{T})$  can be executed conditionally by adding an activation port, e.g. EnablePort in Fig. 1c. When deactivated, the subsystem outputs the initial value or the previous value. We encode such subsystems by introducing wrappers for  $\mathcal{I}$  and  $\mathcal{T}$ . For example,  $\mathcal{T}$  of the subsystem One in Fig. 1c is encoded into the following wrapper predicate:

```

(define-fun trans ( (ien Bool) (so@0 t) (so@1 t) (o t) ) Bool

(ite ien

;; Activate the body transition predicate.

(and (trans_body o) (= so@1 o) )

;; Else, output the prev value and keep the state unchanged.

(and (= o so@0) (= so@1 so@0)) ))

```

It assumes that the body content (to output constant 1) trans\_body is predefined. Output variable o of sort t is inherited from trans\_body. Variables ien, so@0 and so@1 are introduced to represent a signal input to the EnablePort and state variables to keep track of a previous output value when deactivated.  $\mathcal{I}$  is also wrapped and the initial output value is configured.

Activation using TriggerPort is encoded with a wrapper and a behavioral description of the trigger signal such as Rising (we pre-define pattern functions as in [24]). We also use wrapper predicates to encode multi-rate models (e.g.  $S_3$  in Fig. 1c). For a subsystem configured to be executed with a slower rate, we encode with a wrapper equipped with a local counter variable, which computes the activation period and activates the body predicate accordingly. Multiple rates may be present in a subsystem; in such a case, we run a preprocess to divide the subsystem into separate dummy subsystems for each rate (Sect. 4.3).

Encoding of vector signals is simply done by preparing scalar variables for each element of vector values. For bus signals, we utilize their schema externally specified by a bus object data type. <sup>10</sup> Based on the specification, we introduce an SMT-LIB sort that represents bus signal values. For the model  $S_4$  in Fig. 1d, the sort and accessors for the elements are declared as follows:

```

(declare-sort BO 0)

(declare-fun BO_e1 (BO) Int) ;; Accessor for member e1.

(declare-fun BO_e2_1_1 (BO) Real) ;; Accessor for member e2.

;; BO_e2_1_2, BO_e2_2_1, and BO_e2_2_2 are also declared.

```

Given a value bo of sort B0, (B0\_e2\_1\_1 bo) represents the element at (1,1) of the matrix-typed member e2. Using the sort B0,  $\mathcal{T}_4$  is defined as follows:

## 4.3 Implementation of the Encoder

We have implemented the encoder as a MATLAB script (about 9000 LOCs). The script implements the IR generation process and printers as shown in Fig. 2.

In IR generation, we first prepare a block table (BT), an array of struct (record) data where each element represents a block (or a subsystem). Most content of a Simulink model can be accessed via command get (or get\_param) in a script. So, BT collects necessary information, e.g. block-line graph structure and type signature of each inport/outport. Second, we generate another struct array, subsystem table (ST), that represents the tree structure of subsystems. Each element corresponds to a transition system and contains lists of variables and a list of child subsystems. Third, we modify BT and ST to support multirate models and to slice the target portion of the content. Slicing is done by a backward reachability analysis on BT, starting from the objective block of the invariance property. For each multi-rate ST element, we classify the blocks ratewise, and then introduce dummy subsystems with dummy inports and outports.

Approximate and exact printers basically translate the content of a ST into an SMT-LIB description. Each ST element is printed as definitions of corresponding  $\mathcal{I}$  and  $\mathcal{T}$ . The body of each definition mainly contains assignments to the variables and their rhs are printed by traversing BT.

Our implementation supports encoding of 37 block types (but not all parameter settings). Unsupported block instances are stubbed with local unconstrained variables in a predicate definition.

#### 5 Model Checking Methods

As described in Sect. 3, we consider two methods for verifying an invariance  $\Box \phi$  of a Simulink model  $(\mathcal{I}, \mathcal{T})$ , i.e. BMC and k-induction. In the following, we

<sup>&</sup>lt;sup>10</sup> We consider only *nonvirtual* buses.

#### **Algorithm 1:** A *k*-induction procedure.

```

Input: Simulink model (\mathcal{I}, \mathcal{T}), Invariance \Box \phi, k \in \mathbb{N}_{\geq 2}, Encode exactly? b

Output: true, false or maybe

1 EncodeSystemAndAssert_b(\mathcal{I}, \mathcal{T}, \phi);

2 for j \in [0, k-1] do

3 | EncodeTransAndAssert_b(\mathcal{T}, j);

4 | if j > 0 \wedge \mathrm{CSA}(\mathbf{c} = j \wedge \mathbf{f} = \top) = \mathrm{unsat} then return true; end

5 | if \mathrm{CSA}(\mathrm{EncodeInit}_b(\mathcal{I}) \wedge \mathbf{c} = j \wedge \mathbf{f} = \bot) = \mathrm{sat} then

6 | If (\mathcal{I}, \mathcal{T}) is top-level then return false; else return maybe; end

7 | end

8 end

9 return maybe;

```

abbreviate (check-sat-assuming c) to CSA(c), curr\_step in Fig. 3 to c and flag\_kind to f, respectively.

Given  $k \geq 1$ , the BMC method searches for a counterexample of length-k or less. It performs the following steps for each  $j \in [0, k-1]$ . (0) Assume that  $(\mathcal{I}, \mathcal{T})$  instrumented with  $\phi$  has been encoded. (1) Encode the length-(j+1) execution paths. (2) Feed the encoded result to an SMT solver and then solve the command  $\mathsf{CSA}(\mathsf{c} = j \land \mathsf{f} = \bot)$ . The process is done efficiently by incrementing from j = 1, encoding only  $\mathcal{T}$  for the j-th step in (1).

The k-induction method [23] consists of the proofs of the following facts:

- Base case: " $\phi$  is invariant for execution paths of length k-1 or less."

- Induction step: "Assume execution paths of length k that are not initialized. Let  $j \in [0, k-2]$ , and if  $\phi$  holds for every j-th step of a path, then  $\phi$  holds at the last (k-1)-th step of the path."

Alg. 1 is an incremental procedure for proving the two facts. We assume an SMT solver process running in the background. The algorithm generates SMT-LIB expressions in several stages and feeds them to the solver at each stage. The definition of the model is generated at **Line 1** and predicate  $\mathcal{T}$  reaching step j is generated at **Line 3**. Then, it verifies the base case (**Line 5**) and induction step (**Line 4**; checked one iteration after). Based on the locality (Prop. 1),  $(\mathcal{I}, \mathcal{T})$  can be a subsystem, but it is needed to be the top-level system to falsify the invariance (**Line 6**).

**Implementation.** BMC and k-induction methods have been implemented as MATLAB scripts (about 2500 LOCs). In addition to the encoding process, they generate SMT-LIB expressions for execution paths during a verification process. For SMT solving, they communicate with an external server that wraps Z3 via a TCP socket.

The k-induction script conducts verification subsystem-wise, starting from the objective subsystem of the invariance property. The script repeatedly invoke Alg. 1, controlling the following two factors (initially d := 1 and k := 1):

- 1. Number d of subsystem hierarchies. We start applying Alg. 1 on the subsystem (d = 1) that is targeted by the property. When the result is inconclusive, we increase the value of d, i.e. to invoke Alg. 1 in the upper hierarchy.

- 2. Bound k on the path lengths. Once the whole hierarchy has been analyzed, we increase the value k exponentially (and repeat for each subsystem again). Alg. 1 is modified to skip the verification for an initial range of [1, k-1] that has been processed in the previous round.

# 6 Experimental Evaluation

This section describes an empirical evaluation of the proposed method (abbreviated as "PM" in the following). We have verified artificial and industrial Simulink models using our implementation and exiting tools (SLDV and Co-CoSim). Here, the purpose was to answer: **RQ1**: Does PM correctly handle the collected Simulink models? **RQ2**: How is the scalability of PM? **RQ3**: Is the performance of PM better than other tools?

Experiments were conducted on 64-bit Ubuntu 20.04 virtual machines (with 4 cores and 8GB RAM), running on a 2.2GHz Intel Xeon E5-2650v4 processor (12 cores) with 128GB RAM. We used MATLAB R2022a. Execution time was limited to 1 hour.

#### Evaluated tools. We used the following three tools.

- (i) PM implemented (cf. Sect. 4.3 and 5) as an add-on to a proprietary tool PROMPT.<sup>11</sup> In the experiment, we applied the BMC method to obtain counterexamples of false properties, and the k-induction method to prove true properties. BMC was performed against the entire system, while k-induction (Alg. 1) was performed subsystem-wise. Each verification was performed in two ways using either approximate or exact encoder; we respectively refer to them by "PM/A" and "PM/E."

- (ii) SLDV, <sup>12</sup> a tool for analyzing Simulink models based on formal methods. Also, it seems to apply approximations in the analysis. Among various functions of SLDV, we used the "property proving (PP)" function in this experiment. If a Proof Objective block representing an invariance property is added to a Simulink model, it performs verification of whether it holds or be falsified by a counterexample. We enabled the option "FindViolation" for false properties and "Prove" for true properties.

- (iii) CoCoSim (version 1.2), a front-end tool for applying formal tools to Simulink. Its "prove properties" function allows invariance verification using Kind2 (version 1.2), a model checker for Lustre programs. Process of the function consists of translation from Simulink to Lustre and invocation of Kind2.

<sup>11</sup> https://www.en.gaio.co.jp/products/prompt-2/.

<sup>12</sup> https://www.mathworks.com/products/simulink-design-verifier.html.

Target Simulink models. We have prepared 5 artificial and 4 industrial examples to ensure that the different types of models could be handled correctly and effectively. We refer to the models as (1)–(9); also, we refer to a model with a parameter p as  $(i)_p$ . Model  $(1)_{th}$  represents  $S_2$  in Sect. 2 with switching threshold th. Models  $(2)_{th}$  and  $(3)_{th}$  describe second and fourth-order digital filters with threshold th on the output signals. Model  $(4)_{th}$  describes 32 nested counters that are reset at threshold th. Model (5) is the multi-rate model  $S_3$  with additional logic blocks. Models (6)–(8) are taken from the Lockheed Martin challenge [11,19]. We used the first, fourth and sixth problems. Model (9) describes a realistic controller using various types of blocks and externally-controlled subsystems. The size of each model is shown in Table 1.

#### 6.1 Results

For each model, we considered 2 or 4 invariance properties such that half of them are false and the rest are true; false and true instances are denoted by  $(i)_{Pj}$  and  $(i)_{Qj}$ , respectively  $(j \in \{1,2\})$ . The properties prepared can be regarded as test objectives for a block or subsystem, such as conditions on input/output signals and activation conditions. We verified them using the tools. The execution time of PM and SLDV is shown in Fig. 4. The right side of Table 1 shows the parameters of PM used for each property; the number of sliced blocks that belong to the analyzed subsystems, the maximum bound k used in the model checking, and the number d of analyzed subsystem hierarchies. Results of the SMT-LIB encoding of the models (other than (9)) are available at https://www.dropbox.com/s/ohwo5sq0vcak566/2022\_icfem\_smt2.zip.

#### 6.2 Discussions

**RQ1** (correctness). All the conclusive results of PM were confirmed correct. For false properties, we manually simulated the obtained counterexamples using Simulink and confirmed that they were indeed so. For true properties, we confirmed that the results of PM were the same as other tools. Errors on  $(9)_{P2}$  occurred due to unsupported blocks by the encoder. Some block types, e.g. lookup tables and nonlinear arithmetic functions, are difficult to encode and/or to analyze. Our tool either causes an error when falsifying, or abstract them with stub variables in the encoding for an invariance proof.

**RQ2** (scalability). Using a parameterized model, we can observe the exponential increase of execution time. Right figure shows the time needed to falsify the instances  $(1)_{th,P1}$  with several th's. The scalability of PM/A was enough (better than SLDV on more than half of the instances) to handle most of the prepared models. PM/E scaled an order of magnitude

Time (s)

<sup>1000</sup> PM/E SLDV

100 PM/A

10 20 30 40 k

<sup>&</sup>lt;sup>13</sup> https://github.com/dsksh/sl-examples.

**Table 1.** Statistics on the models and the solving process. The abbreviations "s's" and "b's" represent "subsystems" and "sliced blocks," respectively. Third to sixth sections correspond to false and true properties.

|                                         |                                           | P1                               |       | P2                  |         |          | Q1                |                     |                  | Q2                |                     |             |  |

|-----------------------------------------|-------------------------------------------|----------------------------------|-------|---------------------|---------|----------|-------------------|---------------------|------------------|-------------------|---------------------|-------------|--|

| Model                                   | # blocks                                  | # s's  <del>7</del>              | ⊭ b's | $k _{\overline{i}}$ | # b's   | k        | # b's             | k                   | d                | # b's             | k                   | d           |  |

| $\mathbf{(1)}_{th}$                     | 12                                        | 1                                | 11    | 7                   | _       | 1        | 11                | 1                   | 1                | _                 | _                   |             |  |

| $(2)_{th}$                              | 16                                        | 1                                | 14    | 2                   | 14      | 7        | 14                | 10                  | 2                | 14                | 29                  | 2           |  |

| $\mathbf{(3)}_{th}^{n}$                 | 24                                        | 1                                | 22    | 15                  | _       |          | 22                | $\geq 34$           | 2                | _                 | _                   |             |  |

| ${\bf (4)}_{th}$                        | 290                                       | 32                               | 289   | 12                  | _       |          | 289               | 1                   | 1                | _                 | _                   |             |  |

| <b>(5)</b>                              | 33                                        | 8                                | 26    | 21                  | _       |          | 25                | 1                   | 1                | _                 | _                   |             |  |

| (6)                                     | 479                                       | 39                               | 321   | 2                   | 327     | 1        | 259               | 1                   | 1                | 321               | 1                   | 2           |  |

| <b>(7)</b>                              | 291                                       | 18                               | 116   | 1                   | 103     | 1        | 58                | 1                   | 2                | 9                 | 1                   | 3           |  |

| (8)                                     | 712                                       | 188                              | 27    | 1                   | 327     | 1        | 27                | 1                   | 3                | 327               | 1                   | 3           |  |

| (9)                                     | 574                                       | 30                               | 19    | 1                   | 407     | $\geq 1$ | 12                | 1                   | 1                | 407               | 1                   | 3           |  |

| 0 -<br>0 -<br>(1) <sub>0.5,P1</sub> (2) | *.1,P1(2)*.4,P                            | 2(3) <sub>0.1,P</sub>            |       |                     |         |          | (7) <sub>P1</sub> | (7) <sub>P2</sub> ( | 8) <sub>P1</sub> | (8) <sub>P2</sub> | (9)** <sub>P1</sub> | ()<br>Error |  |

| 0                                       | 0                                         |                                  | (     | (α) Ι               | aisiiic | autor    | 1.                |                     |                  |                   |                     |             |  |

| A/TO                                    | 0<br>1<br>0<br>1<br>0<br>1<br>0           | 000                              |       |                     |         |          |                   |                     | 10               | Error             |                     | ŀ           |  |

| 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - |                                           |                                  |       |                     |         |          |                   |                     |                  |                   |                     |             |  |

| (1) <sub>1,Q1</sub> (2                  | (2) <sub>2,Q1</sub> (2) <sub>1,28,0</sub> | <sub>22</sub> (3) <sub>2,Q</sub> |       |                     |         |          |                   |                     | 8) <sub>Q1</sub> | (8) <sub>Q2</sub> | (9) <sub>Q1</sub>   | (9          |  |

|                                         |                                           |                                  | (b) I | nvari               | ance v  | erific   | cation.           |                     |                  |                   |                     |             |  |

**Fig. 4.** Execution time in seconds. Results marked with "TO" are timeouts. "A" means "solved under approximation (white portion shows time required)." Superscript \* (resp. \*\*) indicates that PM/A (resp. PM/A and PM/E) outperforms SLDV.

worse, limiting the number of instances it could handle. As shown in Table 1 and Fig. 4, the execution time increases basically with the number of encoded blocks, "# b's"  $\times k$ . <sup>14</sup> To improve the applicability, slicing and subsystem-wise process of PM is significant. Table 1 shows that the numbers of encoded blocks were reduced, contributing to the number of instances verified in time.

**RQ3** (tool comparison). PM/A outperformed the other tools for 17 out of 28 instances. PM/E was able to handle 15 instances including industrial ones, although its performance was worse than PM/A (it ran out of time for the others). Notably, we verified 3 instances that could not be handled by other tools

<sup>&</sup>lt;sup>14</sup> It is likely to depend on other factors, e.g. the form of encoded formulas and the number of solutions; a detailed analysis is omitted from this paper.

$((8)_{P2},$  exact verification of  $(1)_{1,Q1}$  and approximate verification of  $(2)_{1.28,Q2}$ ). Regarding the encoding method, PM/E should be used to prove a property reliably. When falsifying properties, counterexamples obtained by PM/A can be certified by a simulation using Simulink.

SLDV resulted in timeouts for 4 true instances. On  $(1)_{1,Q1}$  and  $(2)_{2,Q1}$ , it first indicated "valid under approximation" and then ran out of time to prove the validity accurately. It is not clear whether the "approximation" method is similar to PM. Errors on  $(8)_{P2/Q2}$  and  $(9)_{P2}$  were "due to nonlinearities."

CoCoSim handled only model  $(1)_{th}$ . 5 models were resulted in errors during conversion to Lustre (due to unsupported blocks). Verification of 3 models failed in the model checking process of Kind2.

## 7 Related Work

Model checking techniques using SAT/SMT solvers have been applied to various domains [3]. Bourbouh et al. [5] have developed the CoCoSim tool for Simulink models using an SMT-based model checker, Kind2 [10]. The basic process in this paper is similar but we provide an exact encoding method and more support for industrial models. Filipovikj et al. [12] have proposed a bounded model checking method for a subset of Simulink models. A related technology is model checking for the synchronous language Lustre [14,8]. Versions of the Kind tool [13,16,10] and Zustre [15] have been developed. They have implemented techniques such as IC3 [6], parallel solving, and Horn clause encoding; they can be implemented in our method in the future. Kind2 supports accurate encoding with machine integers; our method handles FP numbers in addition.

SMT-based methods require formalization of the target Simulink models. Some of the existing work has formalized via translation to Lustre [8,24,5]. The basic concepts of Simulink are naturally mapped to the Lustre counterparts. A node definition describes the relation between input and output values of a Simulink subsystem at each step, and the method in this paper encodes in basically the same way. Additionally, translation methods for multi-rate (or multi-periodic) models and conditionally executed subsystems have examined [24,5]. Our method handles multi-rates in the same way but differs in that we directly encode to SMT-LIB descriptions, whereas the above methods use the when construct of Lustre. Zhou et al. [25] have proposed a translation method into input-output finite automata. They also formalized conditioning on subsystems and multi-rate models. The result of the transformation is a flat automaton with no subsystem structure. Bouissou et al. [4] have formalized the simulator for continuous-time models implemented in Simulink, which involves numerical integration and zero crossing detection.

There are SMT-based test generation methods that translate Simulink models to constraints and perform a symbolic analysis [22,9], which is performed to obtain a test case as a solution that satisfies constraints. They do not consider to verify invariance properties explicitly. The SmartTestGen tool [20,21] combines four approaches of test generation; one of them considers invariance checking to

guide the coverage strategy. From their evaluation, the effectiveness of the tool for our example models is not clear.

## 8 Conclusions

We have presented an SMT-based model checking method for the invariance verification of Simulink models. Experimental result shows that it is useful in industrial setting; we had the competing results with the state-of-the-art tool, SLDV; our tool handled models that could not be properly analyzed by other tools. The verification process is comprehensible by the intermediate encoded representation and the parameters such as k and d. The resulting invariance proofs are reliable based on exact encoding with bit vectors.

There are several future issues such as improvement of the model checking algorithm and the SMT-LIB encoding method for faster verification, and experiments on the analysis of larger and more complex models.

#### References

- Baranowski, M., He, S., Lechner, M., Nguyen, T.S., Rakamarić, Z.: An SMT Theory of Fixed-Point Arithmetic. In: IJCAR. pp. 13–31. LNCS 12166 (2020). https://doi.org/10.1007/978-3-030-51074-9\_2

- Barrett, C., Fontaine, P., Tinelli, C.: The SMT-LIB Standard (Version 2.6) (2021), https://smtlib.cs.uiowa.edu/

- 3. Biere, A., Kröning, D.: SAT-Based Model Checking. In: Handbook of Model Checking, chap. 10, pp. 277-303. Springer (2018), https://link.springer.com/chapter/10.1007/978-3-319-10575-8\_10

- Bouissou, O., Chapoutot, A.: An operational semantics for Simulink's simulation engine. ACM SIGPLAN Notices 47(5), 129–138 (2012). https://doi.org/10.1145/2345141.2248437

- 5. Bourbouh, H., Garoche, P.l., Loquen, T., Noulard, E., Pagetti, C.: CoCoSim, a code generation framework for control/command applications. In: ERTS. pp. 1–11 (2020)

- Bradley, A.R.: SAT-Based Model Checking Without Unrolling. In: VMCAI. pp. 70–87. LNCS 6538 (2011)

- 7. Brain, M., Schanda, F., Sun, Y.: Building Better Bit-Blasting for Floating-Point Problems. In: TACAS. pp. 79–98. *LNCS* 11427, Springer International Publishing (2019). https://doi.org/10.1007/978-3-030-17462-0\_5

- Caspi, P., Curic, A., Maignan, A., Sofronis, C., Tripakis, S., Niebert, P.: From simulink to SCADE/Lustre to TTA: A layered approach for distributed embedded applications. ACM SIGPLAN Notices 38(7), 153–162 (2003). https://doi.org/ 10.1145/780731.780754

- 9. Chakrabarti, S., Ramesh, S.: SymTest: A framework for symbolic testing of embedded software. In: ISEC. pp. 48–58 (2016). https://doi.org/10.1145/2856636. 2856642

- Champion, A., Mebsout, A., Sticksel, C., Tinelli, C.: The KIND 2 Model Checker. In: CAV. pp. 510-517. LNCS 9780 (2016). https://doi.org/10.1007/ 978-3-319-41540-6\_29, https://kind2-mc.github.io/kind2/

- 11. Elliott, C.: Cyber-Physical V&V Challenges for the Evaluation of State of the Art Model Checkers. In: Safe and Secure Systems and Software Symposium (S5) (2016)

- Filipovikj, P., Rodriguez-Navas, G., Seceleanu, C.: Bounded invariance checking of simulink models. In: Proceedings of the ACM Symposium on Applied Computing. pp. 2168–2177 (2019). https://doi.org/10.1145/3297280.3297493

- 13. Hagen, G., Tinelli, C.: Scaling up the formal verification of Lustre programs with SMT-based techniques. In: FMCAD. pp. 1-9. IEEE (2008). https://doi.org/10.1109/FMCAD.2008.ECP.19

- Halbwachs, N., Lagnier, F., Raymond, P.: Synchronous Observers and the Verification of Reactive Systems. In: Algebraic Methodology and Software Technology (AMAST). pp. 83–96 (1993)

- 15. Kahsai, T., Gurfinkel, A.: Zustre (2018), https://github.com/coco-team/zustre

- 16. Kahsai, T., Tinelli, C.: PKind: A parallel k-induction based model checker. In: International Workshop on Parallel and Distributed Methods in verification (PDMC). vol. 72, pp. 55–62 (2011). https://doi.org/10.4204/eptcs.72.6

- 17. Kroening, D., Strichman, O.: Decision Procedures. Springer, 2nd edn. (2016)

- 18. Lee, E.A., Seshia, S.A.: Introduction to Embedded Systems. A Cyber-Physical Systems Approach. MIT Press, 2nd edn. (2017), http://leeseshia.org

- 19. Mavridou, A., Bourbouh, H., Giannakopoulou, D., Pressburger, T., Hejase, M., Garoche, P.L., Schumann, J.: The Ten Lockheed Martin Cyber-Physical Challenges: Formalized, Analyzed, and Explained. In: IEEE International Conference on Requirements Engineering. pp. 300–310 (2020). https://doi.org/10.1109/RE48521.2020.00040

- Peranandam, P., Raviram, S., Satpathy, M., Yeolekar, A., Gadkari, A., Ramesh, S.: An integrated test generation tool for enhanced coverage of Simulink/Stateflow models. In: DATE. pp. 308–311. IEEE (2012). https://doi.org/10.1109/date. 2012.6176485

- Raviram, S., Peranandam, P., Satpathy, M., Ramesh, S.: SmartTestGen+ : A Test Suite Booster for Enhanced Structural Coverage. In: ICTAC. pp. 164–167. LNCS 7521 (2012)

- 22. Ren, H., Bhatt, D., Hvozdovic, J.: Improving an Industrial Test Generation Tool Using SMT Solver. In: NFM. pp. 100–106. LNCS 9690 (2016). https://doi.org/10.1007/978-3-319-40648-0

- 23. Sheeran, M., Singh, S., Stålmarck, G.: Checking safety properties using induction and a SAT-solver. In: FMCAD. pp. 127–144. *LNCS* 1954 (2000), http://link.springer.com/chapter/10.1007/3-540-40922-X\_8

- 24. Tripakis, S., Sofronis, C., Caspi, P., Curic, A.: Translating Discrete-Time Simulink to Lustre. ACM Transactions on Embedded Computing Systems 4(4), 779–818 (2005). https://doi.org/10.1145/1113830.1113834

- 25. Zhou, C., Kumar, R.: Semantic translation of simulink diagrams to input/output extended finite automata. Discrete Event Dynamic Systems: Theory and Applications 22(2), 223–247 (2012). https://doi.org/10.1007/s10626-010-0096-1