## Formal Verification Methodologies for Nonlinear Analog Circuits

Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich Informatik und Mathematik der Johann Wolfgang Goethe-Universität in Frankfurt am Main

> von Sebastian Steinhorst aus Mainz

Frankfurt (2011) (D 30)

#### Acknowledgments

This thesis is the result of five years of my research in the Electronic Design Methodology Group at the Institute of Computer Science of the Goethe-University of Frankfurt am Main. It would not have been possible without the support of many people.

First of all, I would like to express my deepest gratitude to my doctoral advisor, Lars Hedrich, for his encouragement, guidance and support from the beginnings of my research until the finalization of this thesis. His keen mind and overwhelming interest in my work have been an invaluable help.

I am especially indebted to Helmut Gräb for fruitful discussions, his continuous interest in this thesis and for acting as a referee.

Moreover, I owe a big thank you to my examiners Georg Schnitger and Uwe Brinkschulte for their interesting questions and valuable remarks.

I am grateful to Angelika Schifignano for all of her assistance, being the nicest and most caring secretary I could imagine.

I would like to thank Oliver Mitea, with whom I shared the office for 4 years, for the great time we had together as colleagues and most of all for becoming a friend. Furthermore, I would like to thank my colleagues Mingyu Ma, Markus Meissner, Julius von Rosen and Felix Salfelder for the great working atmosphere in our group. Thank you also to Ronja Düffel, Andreas Hofmann, Conrad Rau, David Sabel and Manfred Schmidt-Schauß for the good times we had.

Finally, I would like to thank my wonderful wife Christina Steinhorst, my parents Doris and Gerhard Steinhorst, my parents-in-law Melitta and Fred Bayer and grandma Ottilia Gutermann for their patience, continuous support and for allowing me to concentrate on my research work by managing my private affairs.

#### **Abstract**

The objective of this thesis is to develop new methodologies for formal verification of nonlinear analog circuits. Therefore, new approaches to discrete modeling of analog circuits, specification of analog circuit properties and formal verification algorithms are introduced.

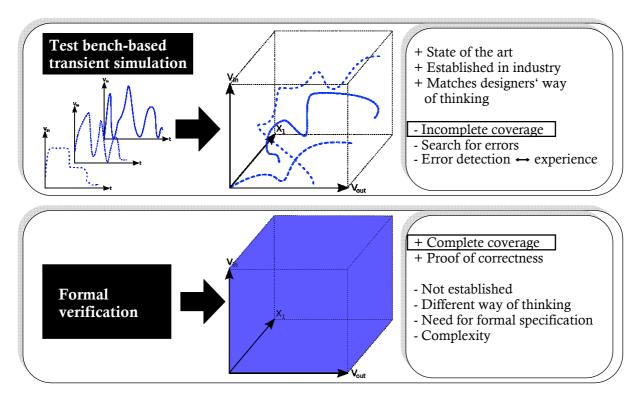

While the design flow for digital circuits is mostly automated and formalized, the analog design flow still contains several manual steps. This particularly applies to the area of verification, which is the process of systematically assuring specification conformance of all design steps. There are two global classes of verification approaches, represented by conventional non-formal verification and formal verification. Non-formal test bench-based simulation is the state of the art in the area of analog verification in industrial design flows. Due to the experimental character of this approach, critical specification-violating corner-case behavior can remain unreached by the simulation runs and therewith undiscovered by the designer.

Formal approaches to verification of analog circuits are not yet introduced into industrial design flows and still subject to research. Formal verification proves specification conformance for all possible input conditions and all possible internal states of a circuit. Automatically proving that a model of the circuit satisfies a declarative machine-readable property specification is referred to as model checking. Equivalence checking proves the equivalence of two circuit implementations.

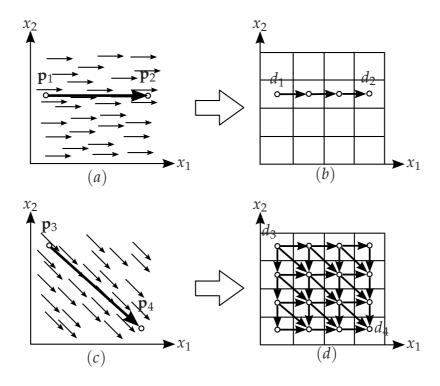

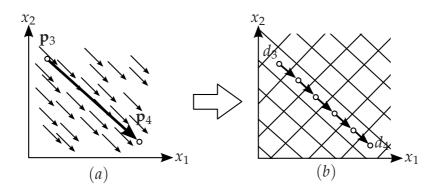

Starting from the state of the art in modeling analog circuits for simulation-based verification, discrete modeling of analog circuits for state space-based formal verification methodologies is motivated in this thesis. The up to now most capable approach to discrete modeling partitions the state space into paraxial hyperboxes of homogeneous behavior of the state space dynamics. Due to the paraxial slicing, the non-paraxial vector field dynamics representing the state space dynamics cannot be sufficiently captured. Hence, the hyperbox-approach is not rotation invariant with respect to the structure of the state space dynamics which results in a massive over-approximation of the successor relation of the discrete transition model. In order to improve the discrete modeling of analog circuits, a new trajectory-directed partitioning algorithm was developed in the scope of this thesis. This new approach determines the partitioning of the state space parallel or orthogonal to the trajectories of the state space dynamics.

Therewith, a high accuracy of the successor relation is achieved in combination with a lower number of states necessary for a discrete model of equal accuracy compared to the hyperbox-approach. The mapping of the partitioning to a discrete analog transition structure (DATS) enables the application of formal verification algorithms.

Formal property specification for the initial approaches to model checking of analog circuits was strongly related to temporal logic specification approaches in the digital domain. However, specification of analog properties such as slew rate and oscillation is fundamentally different from digital properties such as fairness and liveness. Additionally, already in the digital domain, specification by using temporal logics such as the Computation Tree Logic (CTL) was considered not to be designer-friendly. Hence, specifying analog properties with CTL cannot be considered as suitable for analog designers that, in general, do not have a background in computer science. By analyzing digital specification concepts and the existing approaches to analog property specification, the requirements for a new specification language for analog properties have been discussed in this thesis. On the one hand, it shall meet the requirements for formal specification of verification approaches applied to DATS models. On the other hand, the language syntax shall be oriented on natural language phrases. By synthesis of these requirements, the analog specification language (ASL) was developed in the scope of this thesis. ASL includes a natural language encapsulation of temporal logic operations, advanced operations for determination of transition paths and oscillations, as well as arithmetic calculations on state space variable values. Hence, a combination of high expressiveness with a designer-oriented syntax was achieved. An extended variable concept, parameterized macros and an assertion-layer allow to develop reusable specifications for complex analog properties. The verification algorithms for model checking, that were developed in combination with ASL for application to DATS models generated with the new trajectory-directed approach, offer a significant enhancement compared to the state of the art.

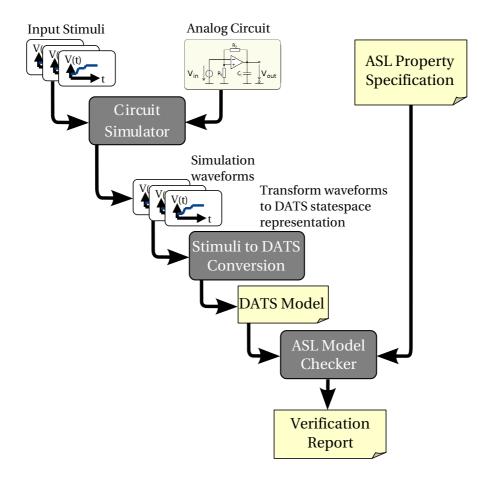

In order to prepare a transition of signal-based to state space-based verification methodologies, an approach to transfer transient simulation results from non-formal test bench simulation flows into a partial state space representation in form of a DATS has been developed in the scope of this thesis. As has been demonstrated by examples, the same ASL specification that was developed for formal model checking on complete discrete models could be evaluated without modifications on transient simulation waveforms.

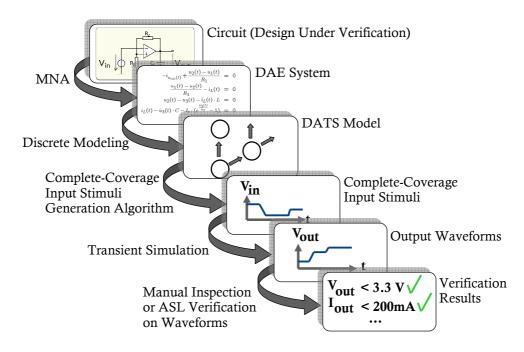

An approach to counterexample generation for the formal ASL model checking methodology offers to generate transition sequences from a defined starting state to a specification-violating state for inspection in transient simulation environments. Based on this counterexample generation, a new formal verification methodology using complete state space-covering input stimuli was developed. On a DATS model of the analog circuit, an input stimulus is determined such that all reachable states and tran-

sitions of the modeled circuit are visited at least once from a defined starting state. The generated sequence of tuples of value and time for the input variables represent piecewise linear input stimuli for each input of the circuit. By conducting a transient simulation with these complete state space-covering input stimuli, the circuit adopts every state and transition that were visited during stimulus generation. An alternative formal verification methodology is given by retransferring the transient simulation responses to a DATS model and by applying the ASL verification algorithms in combination with an ASL property specification.

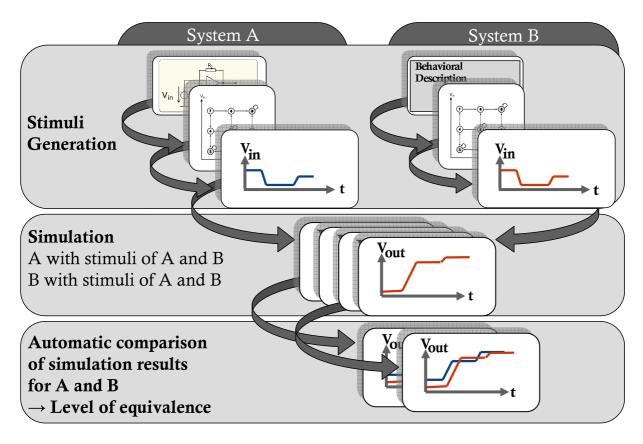

Moreover, the complete state space-covering input stimuli can be applied to develop a formal equivalence checking methodology. The new approach introduced in the scope of this thesis replaces the user-defined input stimuli from conventional nonformal equivalence checking approaches with complete-coverage stimuli. Therewith, the equivalence of two implementations can be proven for every inner state of both systems by comparing the transient simulation responses to the complete-coverage stimuli of both circuits.

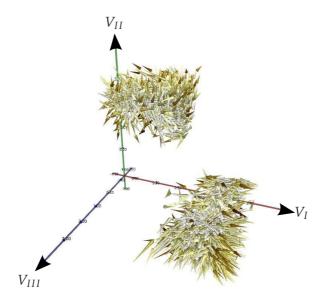

In order to visually inspect the results of the newly introduced verification methodologies, an approach to dynamic state space visualization using multi-parallel particle simulation was developed. Due to the particles being randomly distributed over the complete state space and moving corresponding to the state space dynamics, another perspective to the system's behavior is provided that covers the state space and hence offers formal results.

The prototypic implementations of the formal verification methodologies developed in the scope of this thesis have been applied to several example circuits. The acquired results for the new approaches to discrete modeling, specification and verification algorithms all demonstrate the capability of the new verification methodologies to be applied to complex circuit blocks and their properties.

### Zusammenfassung (German Abstract)

Gegenstand dieser Dissertation ist die Entwicklung neuer Methodiken zur formalen Verifikation nichtlinearer analoger elektronischer Schaltungen. Dazu werden im Rahmen dieser Arbeit entstandene neue Ansätze in den Bereichen verifikationsgerechte diskrete Modellierung analoger Schaltungen, Spezifikation analoger Schaltungseigenschaften und formale Verifikationsalgorithmen vorgestellt.

Während der Entwurfsprozess digitaler Schaltungen weitgehend automatisiert und formalisiert ist, sind zum Entwurf analoger Schaltungen noch viele manuelle Schritte notwendig. Insbesondere im Bereich der Sicherstellung, dass ein Entwurf die in einem Lastenheft spezifizierten Eigenschaften zu jeder Zeit erfüllt, stehen wesentlich weniger Verfahren zur Verfügung als im Bereich digitaler Schaltungen.

Die systematische Sicherstellung der Spezifikationseinhaltung von Entwurfsschritten wird als Verifikation bezeichnet. Aufbauend auf Analysewerkzeugen, wie der Simulation von Schaltungsverhalten im Zeitbereich unter Berücksichtigung sich verändernder Eingangsgrößen, wird für die Verifikation eine Systematik der durchzuführenden Analysen benötigt. Es gibt zwei Klassen von Verifikationsverfahren, welche durch die Bereiche der konventionellen, nicht-formalen Verifikation und der formalen Verifikation gebildet werden.

Der Stand der Technik im Bereich der Analogverifikation in industriellen Entwurfsprozessen ist die Testbench-basierte Simulation. Dieser nicht-formale Ansatz charakterisiert das Schaltungsverhalten anhand von Simulationsläufen mit einer begrenzten Zahl von benutzerdefinierten Eingangssignalen. Abhängig von der Erfahrung des Schaltungsentwicklers decken diese Signale einen Teil der zukünftigen realen Eingangssignale der Schaltung nach ihrer Fertigung ab. Durch den experimentellen Charakter der Verifikation können kritische nicht-spezifikationsgerechte Verhaltenseigenschaften der Schaltung durch die Simulationen unerreicht und so durch den Schaltungsentwickler unentdeckt bleiben. Das Ausbleiben des Entdeckens weiterer Fehler wird im Bereich der nicht-formalen Verifikation als Erfüllen der Spezifikation betrachtet. Wie bereits erläutert, ist dies aber nicht hinreichend für den Nachweis, dass die Schaltung unter allen zukünftigen Umständen die Spezifikation erfüllt. Diese Problematik wird in dieser Arbeit anhand eines einführenden motivierenden Beispiels dargestellt, bei dem eine Oszillatorschaltung erst nach ihrer Fertigung kritisches Verhal-

ten offenbart hat und so nicht einsetzbar war. Während die Simulationsläufe im Entwurfsprozess die Schaltung als voll funktionsfähig darstellten, zeigte sich später, dass bestimmte Startbedingungen, sogenannte "Initial Conditions" diese Schaltung reproduzierbar daran hindern können, in eine Oszillation zu laufen. Die im Rahmen dieser Arbeit entwickelten formalen Verifikationsmethodiken können derartige Fehler identifizieren.

Formale Verifikationsverfahren für analoge Schaltungen sind noch Gegenstand der Forschung. Formale Verifikation beweist, dass für alle möglichen Eingangssignale und für alle möglichen internen Zustände einer Schaltung die Spezifikation eingehalten wird. Formale Verfahren, die ein Modell einer Schaltung automatisiert auf die Einhaltung einer deklarativen maschinenlesbaren Eigenschaftsspezifikation überprüfen, werden als "Model Checking" bezeichnet. Vergleicht man formal die Äquivalenz zweier Implementierungen, stellt dieser Prozess das Verfahren des "Equivalence Checking" dar.

Ausgehend vom Stand der Technik der Modellierung analoger Schaltungen für die simulationsbasierte Verifikation wird im Rahmen dieser Arbeit die diskrete Modellierung analoger Schaltungen für zustandsraumbasierte formale Verifikationsverfahren betrachtet. Der leistungsfähigste bestehende Ansatz zur diskreten zustandsraumbasierten Modellierung teilt den Zustandsraum in achsenparallele Hyperboxen homogenen Verhaltens der Zustandsraumdynamik auf. Hierbei besteht eine Problematik bei der Abbildung nicht-achsenparalleler Vektorfelddynamik, die die Zustandsraumdynamik repräsentiert. Da der bestehende Ansatz nicht rotationsinvariant im Bezug auf die Vektorfeldstruktur ist, findet eine massive Überabschätzung der Nachfolgerrelation des diskreten Transitionsmodells statt. Um dieser Problematik entgegenzutreten wurde im Rahmen dieser Arbeit ein neuer Ansatz zur diskreten Modellierung entwickelt, der die Aufteilungsstruktur anhand der Trajektorien der Vektorfelddynamik bestimmt. So wird eine hohe Genauigkeit der Nachfolgerrelation ermöglicht, woraus eine niedrigere Zahl an Zuständen für ein diskretes Modell gleicher Genauigkeit im Vergleich mit dem Hyperbox-Ansatz folgt.

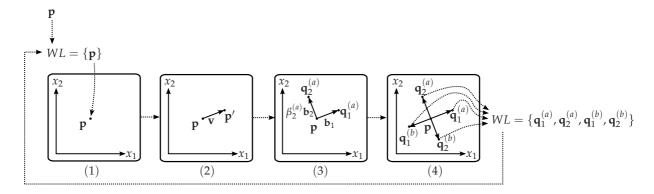

Der neue Ansatz zur Trajektorien-gesteuerten Partitionierung basiert auf der Bestimmung eines initialen transienten Simulationsschritts von einem Startpunkt im Zustandsraum. Um den Transitionsvektor wird unter Einsatz des Gram-Schmidt-Orthogonalisierungsverfahrens ein Orthogonalsystem erzeugt, dessen Addition und Trajektorienflussrichtung-korrigierte Subtraktion mit dem initialen Startpunkt neue Startpunkte für transiente Schritte mit nachfolgender Orthogonalsystem-Erzeugung bildet. Eine Skalierung der Vektoren stellt die Homogenität eingeschlossener Zustandsraumpartitionen sicher. Mit diesem neuen Diskretisierungsverfahren werden die Eckpunkte geometrischer Objekte bestimmt, die den Zustandsraum bis zu nutzerdefinierten Ausdehnungsgrenzen partitionieren. Während die Topologie des Graphen der Ecken und Kanten der Partitionsobjekte isomorph zum entsprechend kon-

struierten Graph eines Hyperwürfels ist, gibt es sonst keine Regularität zur einfachen Beschreibung der Partitionen durch Objekte, wie z.B. Polytope. Eine vorgeschlagene Approximation der Grenzflächen der Partitionsobjekte durch eine gewichtete Kombination von Hyperebenen erlaubt dennoch die Bestimmung von Punkt-Einschlüssen in den Partitionsobjekten. Die Abbildung der Partitionierung auf eine diskrete analoge Transitionsstruktur (DATS) erfolgte auf einer dualen Darstellung der Partitionsobjekte, sodass die von transienten Simulationsschritten repräsentierten Kanten der Partitionen als Zentren von Zustandsraumgebieten betrachtet werden können. Dies erlaubt eine effiziente Bestimmung des diskreten Modells mit hoher Genauigkeit der Transitionsrelation, die so direkt durch transiente Simulationsschritte bestimmt wird.

Da automatisierte Verifikationsmethodiken im analogen Bereich noch nicht etabliert sind, ist in der Praxis die Formalisierung der Spezifikation ebenfalls noch nicht weit fortgeschritten. Als nächster Entwicklungsschritt ist eine verbreitete Anwendung von Verfahren zur Assertion-basierten Simulation im Analogbereich zu erwarten. Eigenschaftsspezifikationen für dieses Verfahren, bei dem Simulationsergebnisse automatisiert mit einer maschinenlesbaren Spezifikation verglichen werden, stellen einen ersten Schritt zur Formalisierung analoger Eigenschaftsspezifikation dar. Die hierbei eingesetzte signalbasierte Eigenschaftsformulierung ist allerdings nicht für die zustandsraumbasierte Verifikation einsetzbar.

Die formale Spezifikation von Eigenschaften in ersten Ansätzen zum Model Checking analoger Schaltungen hat sich stark an den bestehenden Verfahren aus dem Bereich digitaler Hardware orientiert. Eine Erweiterung der Temporallogik "Computation Tree Logic" (CTL) um einen analogen Operator und die Spezifikation von Zeitbeschränkungen erlaubten nur eine sehr begrenzte Formulierung analoger Systemeigenschaften. Analoge Eigenschaften wie z.B. Flankensteilheit und Oszillation sind grundlegend anders zu spezifizieren als digitale Eigenschaften wie "Fairness" und "Lebendigkeit". Zudem ist die temporallogische Spezifikation bereits im digitalen Bereich als nicht anwenderfreundlich betrachtet worden. Analoge Eigenschaften mit CTL zu spezifizieren ist somit für die nicht aus dem Bereich der Informatik stammenden Analogentwickler nicht zielführend.

Ausgehend von einer Analyse digitaler Spezifikationskonzepte und der bestehenden Ansätze für analoge Eigenschaften wurden Anforderungen an eine neue Spezifikationssprache für analoge Eigenschaften abgeleitet. Sie soll den formalen Spezifikationsansprüchen für Verifikationsverfahren auf diskreten analogen Transitionsstrukturen genügen und dabei eine Sprachsyntax besitzen, die an natürlichsprachliche Formulierungen angelehnt ist. Die aus diesen Anforderungen im Rahmen dieser Arbeit entwickelte analoge Spezifikationssprache "Analog Specification Language" (ASL) basiert auf einer natürlichsprachlichen Kapselung temporallogischer Operationen, die mit erweiterten Algorithmen zur Transitionspfadbestimmung, Durchführung von Berechnungen auf Zustandsparametern und Oszillationsbestimmung eine hohe Aus-

drucksstärke analoger Eigenschaften mit einer anwenderfreundlichen Syntax kombinieren konnte. Ein erweitertes Variablenkonzept, Kapselung in parametrisierte Makros und eine Assertionen-Ebene erlauben es, wiederverwendbare Spezifikationen für komplexe Eigenschaften zu erzeugen. Die zusammen mit ASL entwickelten Model Checking-Verifikationsalgorithmen zur Auswertung von ASL-Spezifikationen auf einem mit dem Trajektorien-gesteuerten Diskretisierungsverfahren erzeugten DATS-Modell bilden eine wesentliche Erweiterung zum Stand der Technik. Die neuen Spezifikationsmöglichkeiten konnten anhand von neuen Spezifikationsmethodiken für Überschwingen, erweiterte Oszillationseigenschaften wie Eingangsspannungssensitivität von spannungsgesteuerten Oszillatoren und Startverhalten von autonomen Schaltungen demonstriert werden.

Um einen Übergang der Verifikation von signalbasierten zu zustandsraumbasierten Methodiken zu ermöglichen, wurde im Rahmen dieser Arbeit ein Ansatz entwickelt, der die Übertragung von transienten Simulationsergebnissen aus nicht-formalen Testbench-Simulationsumgebungen in eine partielle DATS-Zustandsraumdarstellung erlaubt. Damit kann, wie anhand von Beispielen gezeigt werden konnte, die gleiche ASL-Spezifikation für Eigenschaften eines vollständigen diskreten Modells ohne Modifikation auch auf Simulationsergebnissen ausgewertet werden.

Ein für das formale ASL-basierte Model Checking entwickelter Ansatz zur Erzeugung von Gegebenbeispielen für als spezifikationsverletzend identifizierte Zustandsraumgebiete erlaubt es, Transitionsfolgen von einem definierten Startzustand zu einem spezifikationsverletzenden Zustand zu ermitteln. Diese Transitionsfolgen entsprechen auf einer DATS stückweise-linearen analogen Signalverläufen, die das in den ungewünschten Zustand führende Schaltungsverhalten in Signalform repräsentieren. Neben der Möglichkeit der direkten Beurteilung aller Zustandsraumparameter auf Signalebene bietet dieser Ansatz die Möglichkeit, den Gegenbeispiel-Signalverlauf auch für die Eingangsvariablen der Schaltung zu exportieren. Diese stückweise-linearen Eingangsstimuli können in einer herkömmlichen Testbench-Umgebung verwendet werden, um das spezifikationsverletzende Verhalten in einer gewohnten Verifikationsumgebung per Simulation mit diesen Eingangsstimuli zu reproduzieren.

Auf Basis des Gegenbeispiel-Verfahrens wurde eine neue formale Verifikationsmethodik mittels vollständig den Zustandsraum einer Schaltung abdeckenden Eingangsstimuli entwickelt. Die zugrundeliegende Motivation war es, formale Verfahren in die bislang nicht-formalen Testbench-basierten Simulationsumgebungen zu integrieren. Dazu wird auf einem diskreten Modell der analogen Schaltung ein Eingangsstimulus so ermittelt, dass von einem Startzustand aus alle im Modell vorhandenen Zustände und Transitionen mindestens einmal besucht werden. Die dabei entstehende Folge von Wert-Zeit-Paaren für die Eingangssignale stellen wiederum stückweise-lineare Eingangsstimuli für jeden Eingang der Schaltung dar. Führt man eine transiente Simulation der Schaltung mit diesen vollständig den Zustandsraum abdeckenden Stimuli

durch, wird die Schaltung während der Simulation alle Zustände und Transitionen annehmen, die bei der Traversierung des diskreten Modells aufgezeichnet wurden. Somit kann eine Simulation in einer konventionellen Testbench-Umgebung durchgeführt werden, die im Gegensatz zu anwenderdefinierten Stimuli jeden möglichen erreichbaren Zustand der Schaltung annimmt. Mit der Gültigkeit der Simulationsergebnisse für jeden Zustand der Schaltung ist somit ein effizientes Verfahren zur vollständig den Zustandsraum abdeckenden und somit formalen Simulation gegeben. Überträgt man die mit diesem Verfahren ermittelten Simulationsergebnisse wieder in ein DATS-Modell und führt darauf ASL-Verifikationsalgorithmen aus, ist eine formale Assertion-basierte Verifikation möglich, die eine alternative Verifikationsmethodik zum Model Checking darstellt.

Die vollständig den Zustandsraum abdeckenden Eingangsstimuli bieten noch eine weitere Anwendungsmöglichkeit im Bereich des Aquivalenzvergleichs. Nur wenige existierende Ansätze im Bereich der Forschung bieten die Möglichkeit, für nichtlineare analoge Schaltungen die vollständige Verhaltensäquivalenz bezüglich einer definierten Fehlergrenze zu beweisen. Aufgrund komplexer Algorithmen ist der Anwendungsbereich limitiert auf den Vergleich von Implementierungen, die keine wesentlichen Unterschiede in ihrem Abstraktionsgrad besitzen. Im industriellen Einsatz wird Aquivalenzvergleich nicht-formal durch den Vergleich von Simulationsergebnissen durchgeführt, die mittels anwenderdefinierten Eingangsstimuli berechnet wurden. Die im Rahmen dieser Arbeit entwickelte Methodik zum formalen Äquivalenzvergleich auf Basis der vollständig den Zustandsraum abdeckenden Eingangsstimuli ersetzt die anwenderdefinierten Eingangsstimuli durch die vollständig den Zustandsraum abdeckenden. So kann die Aquivalenz für jeden möglichen Zustand der zu vergleichenden Implementierungen anhand eines automatisierten Vergleichs der Simulationsergebnisse beider Implementierungen gezeigt werden. Eine vollständige Verifikationsaussage kann getroffen werden, wenn Stimuli für jede der zu vergleichenden Implementierungen generiert werden und die Simulation jeder Implementierung mit allen Stimuli der eigenen und der anderen Implementierung erfolgt. Der Abstraktionsgrad zwischen den Implementierungen ist hierbei irrelevant.

Um die Ergebnisse der neu eingeführten formalen Verifikationsmethodiken visuell zu untersuchen, wurde ein Verfahren entwickelt, das den Zustandsraum und seine Dynamik mittels eines Partikel-Simulationsansatzes visualisiert. Da die Partikel über den gesamten Zustandsraum randomisiert verteilt werden und sich dann gemäß der Vektorfelddynamik fortbewegen, kann auch hier ein Einblick in das Systemverhalten gewonnen werden, der eine weitestgehend vollständige und somit formale Repräsentation des Zustandsraums bietet.

Die prototypische Implementierung der im Rahmen dieser Arbeit entwickelten formalen Verifikationsmethodiken wurde auf zahlreiche Beispielschaltungen angewendet. Ein modifizierter Ringoszillator wurde mittels ASL-Model Checking und Parti-

kelsimulation auf Startbedingungen untersucht, die eine Oszillation verhindern. Das Überschwingen eines aktiven Sallen-Key Tiefpassfilters wurde mittels ASL-Model Checking mit Gegenbeispielgenerierung untersucht. Eine transiente Simulation dieser Schaltung mit einem vollständig den Zustandsraum abdeckenden Eingangsstimulus wurde wiederum mit der ASL-Spezifikation verifiziert. Ein Vergleich der neuen diskreten Modellierung mittels des Trajektorien-gesteuerten Ansatzes mit dem Hyperbox-Diskretisierungsverfahren konnte eine wesentliche Steigerung der Modellierungsgenauigkeit des neuen Verfahrens dokumentieren. Für eine Charge-Pump-Schaltung wurde das Startverhalten per Model Checking verifiziert und die ASL-Spezifikation zudem auf die Ergebnisse einer konventionellen transienten Simulation angewendet. Das Model Checking der Eingangsspannungssensitivität eines spannungsgesteuerten Oszillators konnte sowohl die Fähigkeit des neuen Diskretisierungsverfahrens wie auch der Spezifikations- und Verifikationsmethodik zeigen, erfolgreich auf komplexen Zustandsraumstrukturen zu operieren. Schließlich wurde das neue Stimuli-basierte Aquivalenzvergleichsverfahren anhand einer Bandpass-Schaltung, eines Delta-Sigma-Modulators zweiter Ordnung und weiterer Schaltungen demonstriert und mit einem bestehenden Verfahren verglichen.

Trotz der in der Arbeit diskutierten bestehenden Herausforderungen, die bis zu einem industriellen Einsatz der neu vorgestellten Methodiken noch bearbeitet werden müssen, konnten mehrere neue Methodiken zur Formalisierung analoger Verifikation motiviert und erfolgreich prototypisch umgesetzt werden.

## Contents

| Abstract Zusammenfassung (German Abstract) List of Tables List of Figures List of Algorithms | iii<br>vii |

|----------------------------------------------------------------------------------------------|------------|

| List of Tables List of Figures                                                               |            |

| List of Figures                                                                              |            |

|                                                                                              | xviii      |

| List of Algorithms                                                                           | xxii       |

|                                                                                              | xxiii      |

| List of Symbols and Abbreviations                                                            | xxv        |

| 1 Introduction                                                                               | 1          |

| 1.1 Analog Circuit Design Flow                                                               | 2          |

| 1.2 Analog Circuit Analysis and Verification                                                 | 4          |

| 1.3 Formal Verification                                                                      | 4          |

| 1.4 Motivating Example                                                                       | 5          |

| 1.5 Contributions                                                                            | 7          |

| 1.6 Publications                                                                             | 9          |

| 1.7 Overview                                                                                 | 9          |

| 2 System Representation for Verification                                                     | 11         |

| 2.1 System Description                                                                       | 11         |

| 2.2 Digital Systems                                                                          | 14         |

| 2.3 Analog Systems                                                                           | 16         |

| 2.3.1 Device Models                                                                          | 17         |

| 2.3.2 Network Analysis using the Modified Nodal Approach                                     | 18         |

| 2.3.3 Numerical Simulation                                                                   | 19         |

| 2.3.4 DAE Index                                                                              | 21         |

|   |      | 2.3.5               | Analog Behavioral Modeling and Hardware Description Lan-       |    |

|---|------|---------------------|----------------------------------------------------------------|----|

|   |      |                     | guages                                                         | 21 |

|   |      | 2.3.6               | State Space Representation                                     | 24 |

|   | 2.4  | Discre              | ete Modeling of Analog Systems                                 | 24 |

|   |      | 2.4.1               | Discrete Analog Transition Structure                           | 25 |

|   |      | 2.4.2               | The Discretization Problem for Analog Circuits                 | 27 |

|   |      | 2.4.3               | Hyperbox Discretization                                        | 31 |

|   |      | 2.4.4               | Trajectory-Directed Discretization                             | 32 |

|   |      |                     | 2.4.4.1 Calculating the State Space Partitioning               | 33 |

|   |      |                     | 2.4.4.2 Geometric Structure of the State Space Partitions      | 38 |

|   |      |                     | 2.4.4.3 Transition Relation of the Hypercells                  | 43 |

|   |      |                     | 2.4.4.4 Mapping the Trajectory-Directed Partitioning to a DATS | 44 |

|   |      |                     | 2.4.4.5 Duality of the Trajectory-Directed Partitioning        | 45 |

|   |      |                     | 2.4.4.6 Handling Input Variables                               | 47 |

|   |      |                     | 2.4.4.7 Runtime Complexity                                     | 48 |

|   |      |                     | 2.4.4.8 Modeling Error Analysis                                | 50 |

| 3 | Prop | erty S <sub>l</sub> | pecification for Verification                                  | 55 |

|   | 3.1  | Basic l             | Definitions                                                    | 55 |

|   | 3.2  | Opera               | ational and Declarative Specification                          | 56 |

|   | 3.3  | Proper              | erty Specification for Discontinuous Systems                   | 57 |

|   |      | 3.3.1               | Linear Temporal Logic (LTL)                                    | 58 |

|   |      | 3.3.2               | Computation Tree Logic (CTL)                                   | 59 |

|   |      | 3.3.3               | Property Specification Language (PSL)                          | 61 |

|   | 3.4  | Existin             | ng Approaches to Specification of Analog System Properties     | 62 |

|   |      | 3.4.1               | Specification of Assertions within Analog Hardware Description |    |

|   |      |                     | Languages                                                      | 63 |

|   |      | 3.4.2               | PSL for Analog Signal Property Specification                   | 64 |

|   |      | 3.4.3               | CTL Specification of Analog Properties in the State Space      | 64 |

|   | 3.5  | Analo               | og Specification Language (ASL)                                | 65 |

|   |      | 3.5.1               | Language Concept                                               | 67 |

|   |      | 3.5.2               | EBNF Grammar of ASL                                            | 67 |

|   |      | 3.5.3               | Semantics of ASL Operations                                    | 69 |

| 4 | Veri | fication            | n of Systems                                                   | 75 |

|   | 4.1  | Non-F               | Formal Verification                                            | 76 |

|   |      | 4.1.1               | Simulation-Based Verification                                  | 76 |

|   |      | 4.1.2               | Assertion-Based Verification                                   | 76 |

|   | 4.2  | Verific             | cation Coverage                                                | 77 |

|   |      | 4.2.1               | Structural Coverage                                            | 79 |

|   |      | 4.2.2               | Functional Coverage                                            | 80 |

|   | 4.3        | Forma   | al Verification                                                                                                  | 80  |

|---|------------|---------|------------------------------------------------------------------------------------------------------------------|-----|

|   |            | 4.3.1   | Model Checking                                                                                                   | 81  |

|   |            | 4.3.2   | Equivalence Checking                                                                                             | 82  |

|   | 4.4        | Existin | ng Approaches to Non-Formal Analog Circuit Verification                                                          | 83  |

|   |            | 4.4.1   | Assertion-Based Approaches to Analog Verification                                                                | 83  |

|   |            | 4.4.2   | Analog Verification Coverage                                                                                     | 84  |

|   |            | 4.4.3   | Formalizing the Analog Verification Flow                                                                         | 85  |

|   | 4.5        | Existi  | ng Formal Approaches to Analog Verification                                                                      | 86  |

|   |            | 4.5.1   | Reachability Analysis and Verification of Analog Circuits                                                        | 86  |

|   |            | 4.5.2   | Analog Model Checking                                                                                            | 87  |

|   |            | 4.5.3   | Analog Equivalence Checking                                                                                      | 88  |

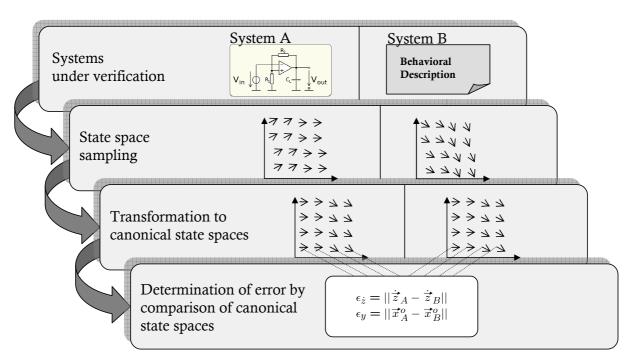

|   |            |         | 4.5.3.1 The VERA Equivalence Checking Algorithm                                                                  | 90  |

| 5 | Ana        | log For | rmal Verification Methodologies                                                                                  | 93  |

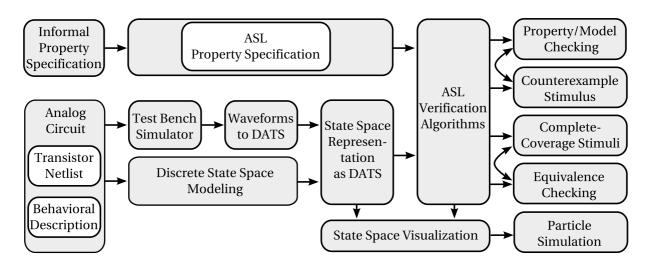

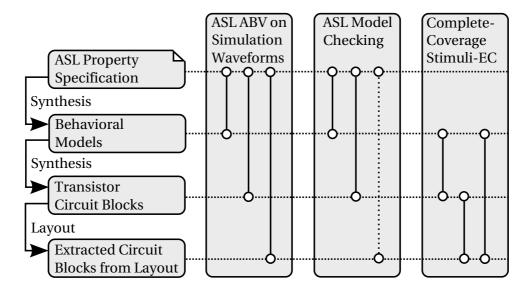

| 3 | 5.1        | _       | Verification Methodologies for the Analog Design Flow                                                            | 93  |

|   | 5.1        | 5.1.1   | Verification Methodology Perspective                                                                             | 94  |

|   |            | 5.1.2   | · · ·                                                                                                            | 95  |

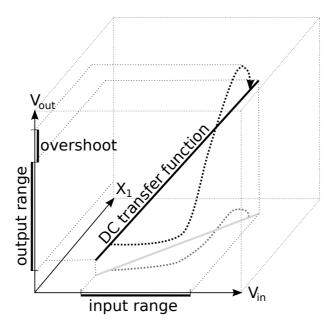

|   | 5.2        |         | Design Flow Perspective                                                                                          | 96  |

|   | 5.2        | 5.2.1   | Specification of Circuit Overshoot                                                                               | 96  |

|   |            | 5.2.1   | Specification of Oscillation and Voltage Controlled Oscillator                                                   | 90  |

|   |            | 3.2.2   | 1                                                                                                                | 98  |

|   |            | 5.2.3   | Gain $K_{VCO}$                                                                                                   |     |

|   | 5.3        |         | Specification of the Startup Time of Autonomous Circuits Property Verification on Transient Simulation Waveforms |     |

|   | 5.4        |         | terexample Generation for Model Checking                                                                         |     |

|   | 3.4        | 5.4.1   |                                                                                                                  |     |

|   | E          |         | 1                                                                                                                |     |

|   | 5.5        | _       | Polete-Coverage Input Stimuli Generation                                                                         |     |

|   | E (        |         | Verification Methodology                                                                                         |     |

|   | 5.6        | -       | ralence Checking using Complete-Coverage Input Stimuli                                                           |     |

|   |            | 5.6.1   | Error Measures for Waveform Comparison                                                                           |     |

|   | <b>-</b> - | 5.6.2   | Automation in the ASL Verification Flow                                                                          |     |

|   | 5.7        | Muiti-  | -Parallel State Space Particle Simulation                                                                        | 114 |

| 6 | -          |         | ital Results                                                                                                     | 117 |

|   | 6.1        |         | ementation                                                                                                       | 117 |

|   | 6.2        |         | cation of Initial Conditions of a Ring Oscillator                                                                |     |

|   | 6.3        | Verific | cation of Active Lowpass Filter Overshoot                                                                        |     |

|   |            | 6.3.1   | Model Checking                                                                                                   | 122 |

|   |            | 6.3.2   | Counterexample                                                                                                   | 123 |

|   |            | 6.3.3   | Complete-Coverage Input Stimulus                                                                                 | 124 |

|   |            | 6.3.4   | Comparison to Hyperbox Discretization                                                                            | 125 |

|   |            | 635     | ASI. Verification on Simulation Waveforms                                                                        | 126 |

|    | 6.4   | Verific | ration of CMOS Charge Pump Startup Time        | 128 |

|----|-------|---------|------------------------------------------------|-----|

|    |       | 6.4.1   | Model Checking                                 | 128 |

|    |       | 6.4.2   | ASL Verification on Simulation Waveforms       | 131 |

|    | 6.5   | Model   | Checking of VCO Gain $K_{VCO}$                 | 132 |

|    | 6.6   | Equiva  | alence Checking with Complete-Coverage Stimuli | 134 |

|    |       | 6.6.1   | Biquad Bandpass Filter                         | 135 |

|    |       | 6.6.2   | Second-Order Delta-Sigma Modulator             | 136 |

|    |       | 6.6.3   | Further Circuit Examples                       | 138 |

|    | 6.7   | Assess  | sment                                          | 140 |

| 7  | Con   | clusion | ıs                                             | 143 |

|    | 7.1   | Summ    | nary                                           | 143 |

|    | 7.2   | Challe  | enges and Future Work                          | 145 |

| A  | App   | endix   |                                                | 147 |

|    | A.1   | VCO S   | State Space Slices                             | 147 |

| Bi | bliog | raphy   |                                                | 149 |

## List of Tables

| 2.1 | State transition table for the two-bit down counter                                                           | 15  |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of the trajectory-directed discretization and the hyperbox                                         |     |

|     | discretization approaches                                                                                     | 53  |

| 3.1 | Explanation of LTL syntax                                                                                     | 59  |

| 3.2 | Explanation of CTL syntax                                                                                     | 60  |

| 3.3 | Explanation of CTL-AT syntax                                                                                  | 65  |

| 6.1 | Verification results for the modified ring oscillator with results obtained                                   |     |

|     | from ASL model checking (MC) and transient analysis (TRA)                                                     | 119 |

| 6.2 | Runtimes of the trajectory-directed discretization algorithm for the                                          |     |

|     | Sallen-Key lowpass filter                                                                                     | 121 |

| 6.3 | Verification results calculated by the ASL model checking algorithms on                                       |     |

|     | the DATS for the Sallen-Key lowpass filter                                                                    | 123 |

| 6.4 | Verification results calculated by the ASL model checking (MC) al-                                            |     |

|     | gorithms on the DATS for the Sallen-Key lowpass filter compared to                                            |     |

|     | the ASL evaluation on the transient simulation results (Sim) using a                                          | 100 |

|     | complete-coverage input stimulus                                                                              | 128 |

| 6.5 | Runtimes of the trajectory-directed discretization algorithm for the                                          |     |

|     | CMOS charge pump                                                                                              | 129 |

| 6.6 | Comparison between ASL property evaluation on a DATS generated by                                             |     |

|     | the trajectory-directed discretization (TDD) method and on simulation                                         | 100 |

|     | waveforms obtained from transient analysis (TRA)                                                              | 132 |

| 6.7 | Comparison of the results between ASL model checking and transient                                            | 101 |

|     | analysis for the oscillation period of the VCO at different input voltages.                                   | 134 |

| 6.8 | Comparison of the results between ASL model checking and transient analysis for the gain $K_{VCO}$ of the VCO | 134 |

| 6.9 | Comparison of the results between equivalence checking by complete                                            |     |

|     | state space-covering input stimuli (stimEC) and the transformed state                                         |     |

|     | space comparison approach (VERA)                                                                              | 141 |

|     |                                                                                                               |     |

| 6.10 | Runtimes of the stimEC equivalence checking approach compared to the |     |

|------|----------------------------------------------------------------------|-----|

|      | approximated simulation runtimes of circuit comparison by systematic |     |

|      | simulation.                                                          | 142 |

## List of Figures

| 1.1                    | Y-chart for hierarchical analog design with exemplary synthesis steps                                                                          | 3      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.2                    | The synthesis steps in the design flow transfer a specification to an implementation. Every implementation step needs to be analyzed for spec- |        |

| 1.0                    | ification conformance by verification methods                                                                                                  | 5      |

| 1.3                    | Modified ring oscillator with an even number of inverter stages and                                                                            | (      |

| 1.4                    | cross-coupling                                                                                                                                 | 6<br>7 |

| 1. <del>4</del><br>1.5 | State space trajectories of initial conditions leading into the non-                                                                           | 1      |

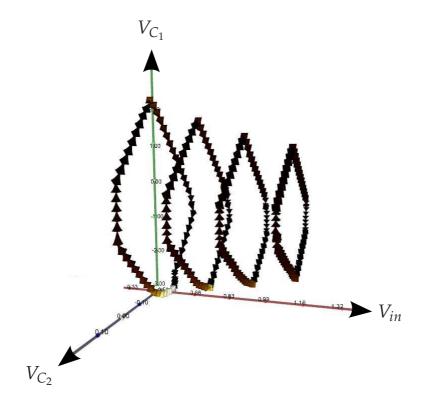

| 2.0                    | oscillating steady states for transistor ratio $\alpha/\beta=1.95.\ldots$                                                                      | 8      |

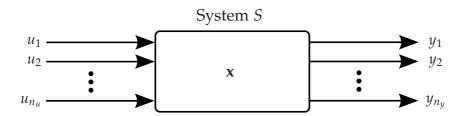

| 2.1                    | General illustration of a system                                                                                                               | 12     |

| 2.2                    | Circuit schematic for the two-bit down counter (a) and the correspond-                                                                         |        |

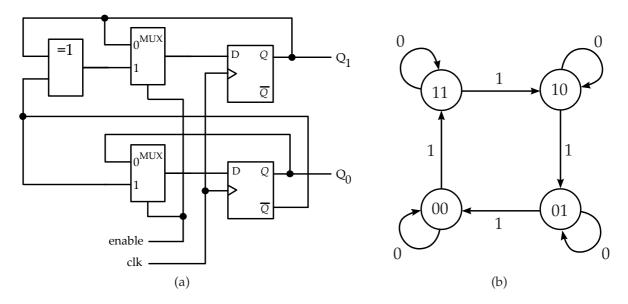

|                        | ing state transition graph (b)                                                                                                                 | 16     |

| 2.3                    | Simple nonlinear analog circuit example with input voltage $V_{in}$ , resistor                                                                 |        |

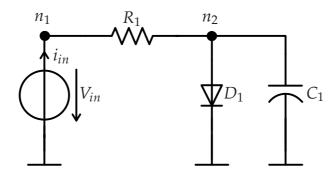

|                        | $R_1$ , diode $D_1$ and capacitor $C_1$                                                                                                        | 19     |

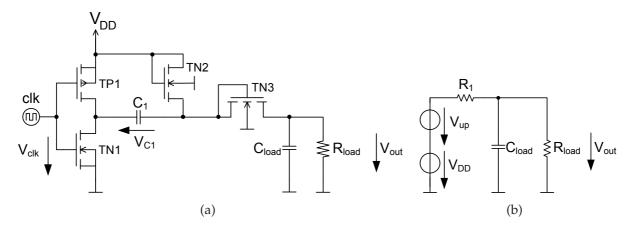

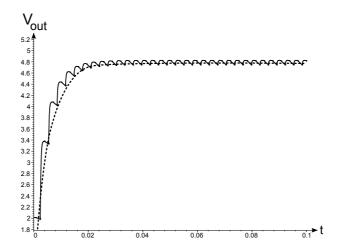

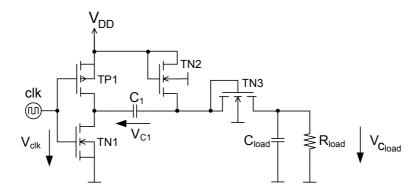

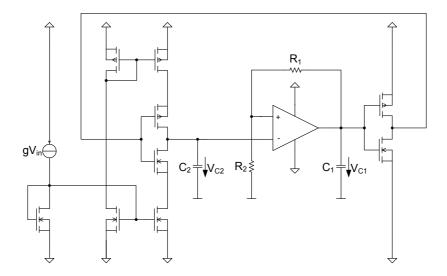

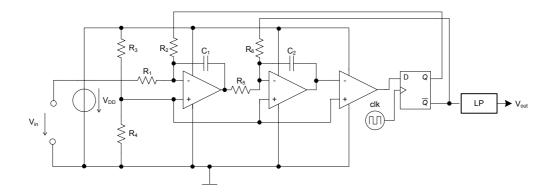

| 2.4                    | Schematic of the CMOS implementation of the charge pump circuit (a)                                                                            |        |

|                        | and simplified macro model (b)                                                                                                                 | 22     |

| 2.5                    | Transient startup response of the transistor netlist charge pump (solid                                                                        |        |

|                        | line) and the simplified model (dashed line)                                                                                                   | 23     |

| 2.6                    | Schematic illustration of a graph structure representing a DATS                                                                                | 27     |

| 2.7                    | Illustration of a vector field with paraxial flow                                                                                              | 33     |

| 2.8                    | Illustration of a non-paraxial vector field flow with a trajectory-directed                                                                    |        |

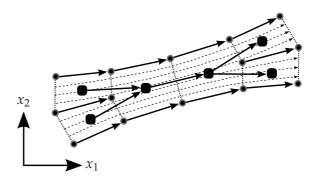

|                        | state space partitioning.                                                                                                                      | 34     |

| 2.9                    | Schematic visualization of the process of determining the trajectory-                                                                          |        |

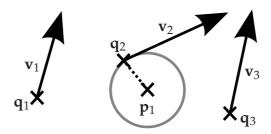

|                        | orthogonal point sets $\mathbf{q}^{(a)}$ and $\mathbf{q}^{(b)}$ in a two-dimensional space                                                     | 37     |

| 2.10                   | Illustration of the orthogonal sets constructed around the transition vec-                                                                     |        |

|                        | tors in a three-dimensional state space                                                                                                        | 38     |

| 2.11                   | Illustration of a hypercell object in a three-dimensional space                                                                                | 40     |

| 2.12                   | Basis vector sets for each vertex of a hypercell facet for determination of                                                                    |        |

|                        | the position of point $p$ with respect to the facet                                                                                            | 41     |

| 2.13                   | Curved surface in a three-dimensional space representing a facet of a cell.                                                                    | 42     |

| 2.14                                                      | Schematic illustration of contracting and expanding vector field flow, with the corresponding partitioning and the successor relation for the hypercells                                                                                                                              | 44                                |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

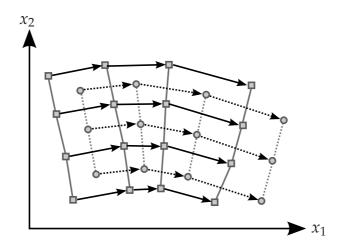

| 2.15                                                      | Illustration of a two-dimensional vector field with calculated transition endpoints as boxes and the quadrilateral enclosed regions of the state space                                                                                                                                | 46                                |

| 2.16                                                      | Schematic illustration of a DATS with a possible input change-induced transition path (a). The corresponding input signal (b) and output signal (c) is assumed for this path.                                                                                                         | 48                                |

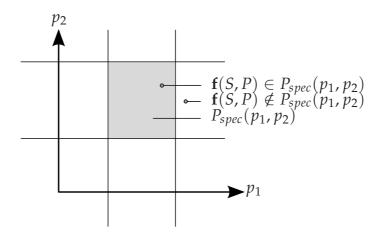

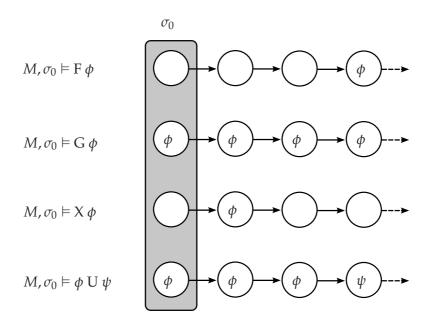

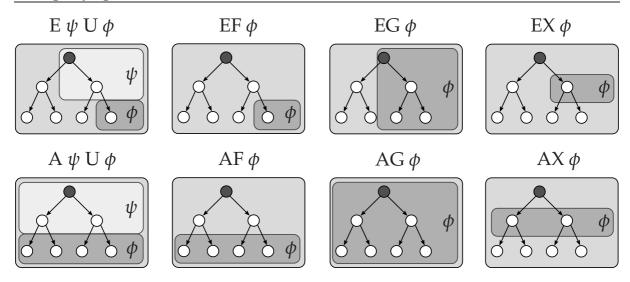

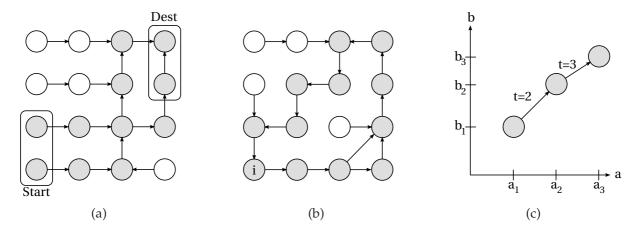

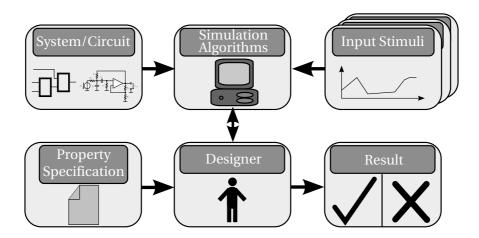

| 3.1<br>3.2<br>3.3<br>3.4                                  | Property space with specification and performances                                                                                                                                                                                                                                    | 56<br>59<br>60<br>73              |

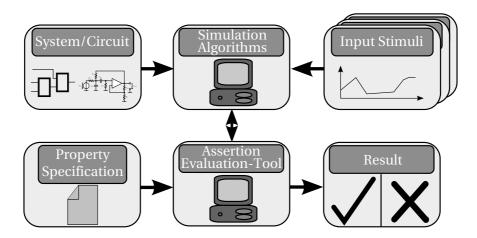

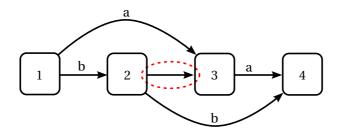

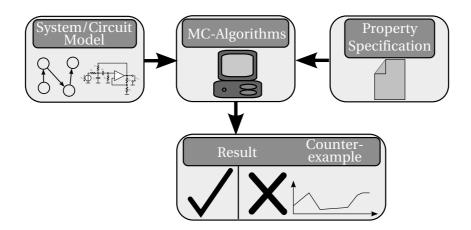

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                           | Simulation-based verification flow.  Assertion-based verification flow.  Illustration of structural coverage.  Model checking flow.  Comparison of verification coverage in the state space by test benchbased transient simulation and formal verification.                          | 77<br>78<br>80<br>81              |

| 4.6                                                       | Structure of the VERA equivalence checking methodology                                                                                                                                                                                                                                | 91                                |

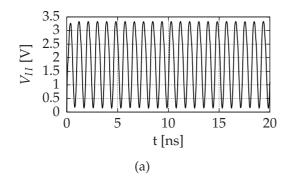

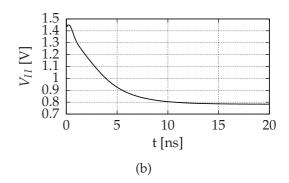

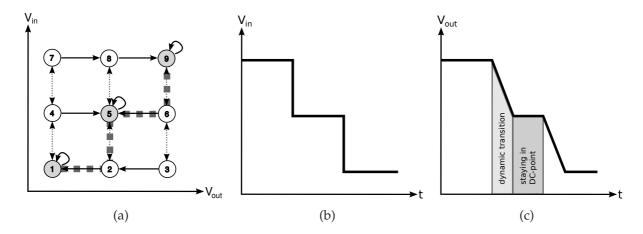

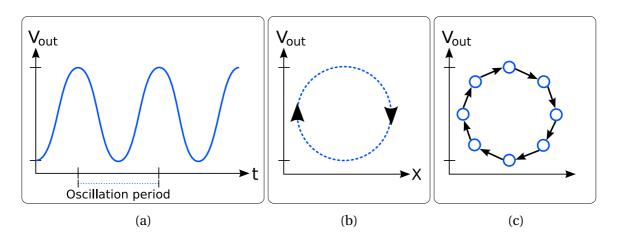

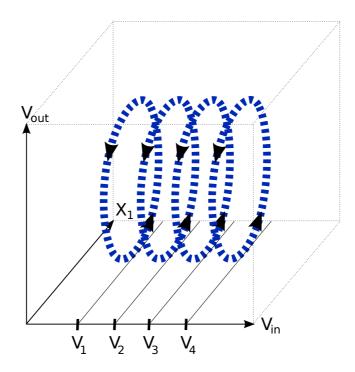

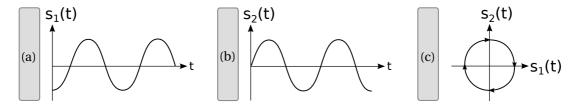

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Analog verification framework for different verification methodologies. New verification methodologies in the analog design flow Overshoot of the output voltage caused by a trajectory in the state space. Oscillation in the time domain (a), in the continuous state space (b) and | 94<br>96<br>97                    |

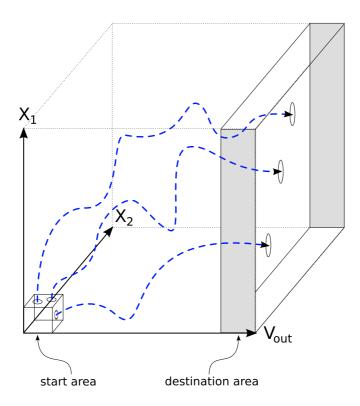

| 5.5                                                       | in the DATS (c)                                                                                                                                                                                                                                                                       | 98<br>99                          |

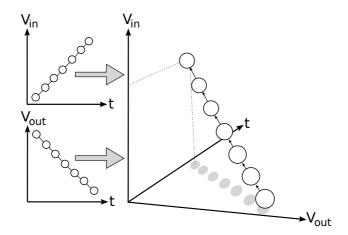

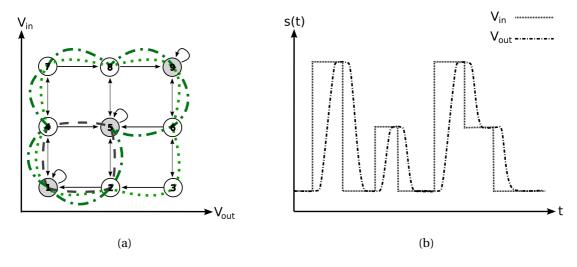

| 5.6<br>5.7<br>5.8                                         | Schematic illustration of startup transition paths                                                                                                                                                                                                                                    | 101                               |

| 5.9                                                       | representation of periodic signals $s_1(t)$ and $s_2(t)$ (c) ASL assertion-based verification flow for transient simulation results                                                                                                                                                   | 103                               |

| 5.10                                                      | transferred to a state space representation                                                                                                                                                                                                                                           | <ul><li>104</li><li>109</li></ul> |

|                                                           | Complete-coverage input stimuli generation and verification flow Equivalence checking flow using complete state space-covering input                                                                                                                                                  | 110                               |

|                                                           | stimuli                                                                                                                                                                                                                                                                               | 113                               |

| 5.13             | discrete vector field $V_D$                                                                                                                                                                                                                | 115 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

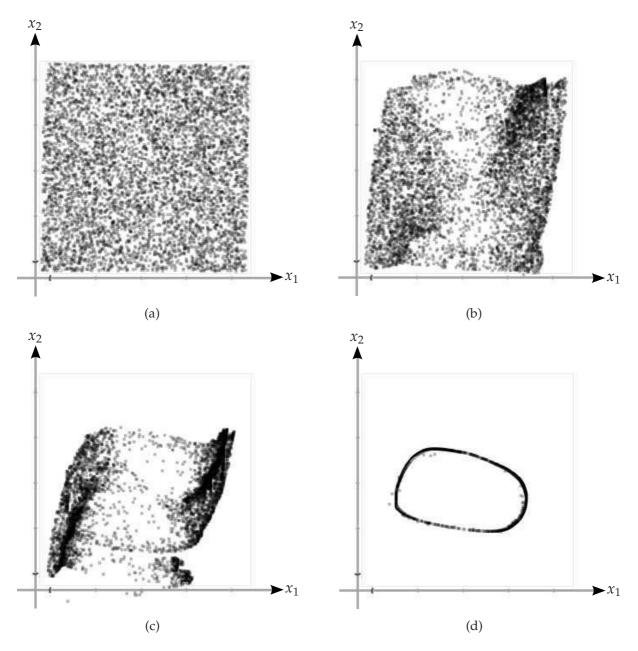

| 5.14             | Particle simulation for the two-dimensional state space of an oscillator circuit with increasing time from (a) to (d)                                                                                                                      | 116 |

|                  | circuit with increasing time from (a) to (a).                                                                                                                                                                                              | 110 |

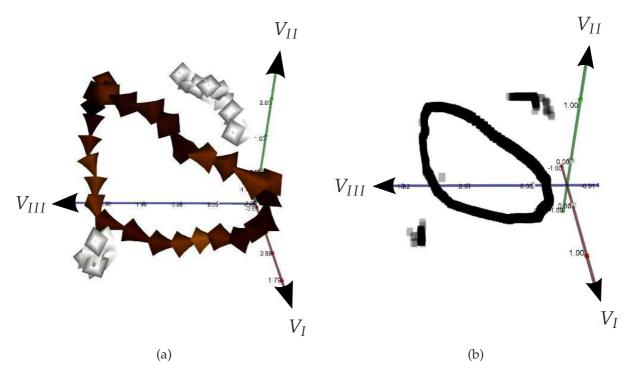

| 6.1              | Transition vectors between states of the detected oscillation set and non-periodic steady states of the modified ring oscillator detected by model checking for $\alpha/\beta$ -ratio 1.95 (a). Particle simulation visualizing the oscil- |     |

|                  | lation trajectory and the non-periodic steady states (b)                                                                                                                                                                                   |     |

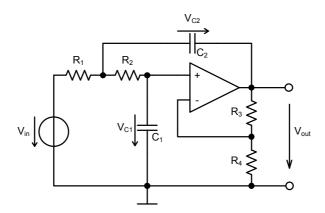

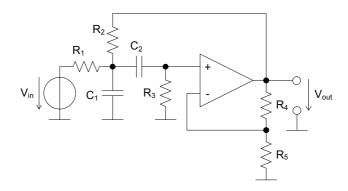

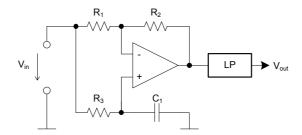

| 6.2              | Circuit schematic of Sallen-Key biquad lowpass filter                                                                                                                                                                                      |     |

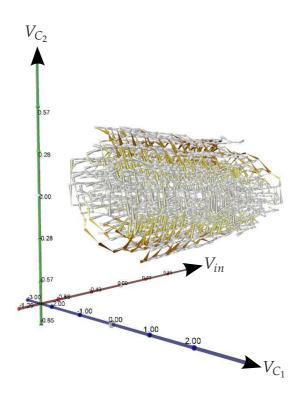

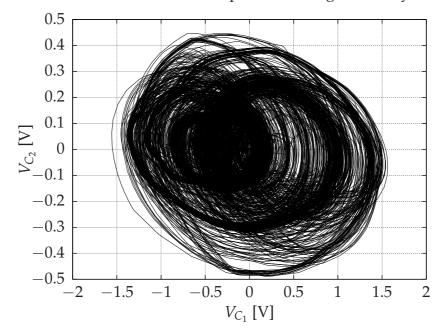

| 6.3              | Reachable state space of the Sallen-Key biquad lowpass filter                                                                                                                                                                              | 122 |

| 6.4              | Transient response to the counterexample input stimulus of the Sallen-                                                                                                                                                                     |     |

|                  | Key biquad lowpass filter                                                                                                                                                                                                                  | 124 |

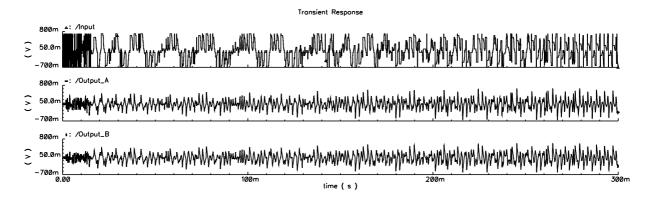

| 6.5              | Complete generated input stimulus and transient output response of the                                                                                                                                                                     |     |

|                  | Sallen-Key biquad lowpass filter                                                                                                                                                                                                           | 124 |

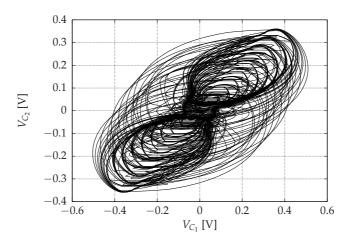

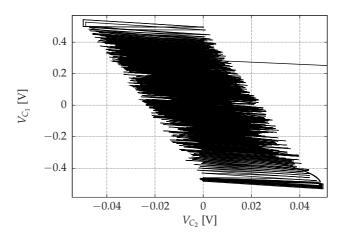

| 6.6              | Transient response to the generated input stimulus of the Sallen-Key bi-                                                                                                                                                                   |     |

|                  | quad lowpass filter plotted over $V_{C_1}$ and $V_{C_2}$                                                                                                                                                                                   | 125 |

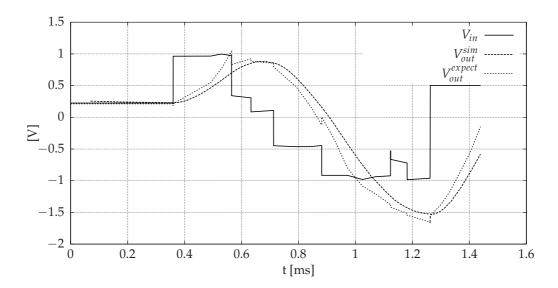

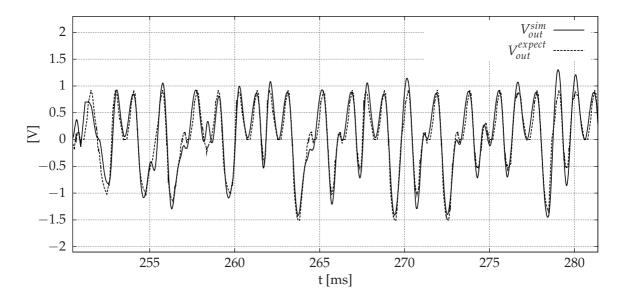

| 6.7              | Excerpt of the transient response to the complete-coverage input stimu-                                                                                                                                                                    |     |

|                  | lus of the Sallen-Key biquad lowpass filter with the expected response                                                                                                                                                                     |     |

|                  | generated by the trajectory-directed discretization approach                                                                                                                                                                               | 126 |

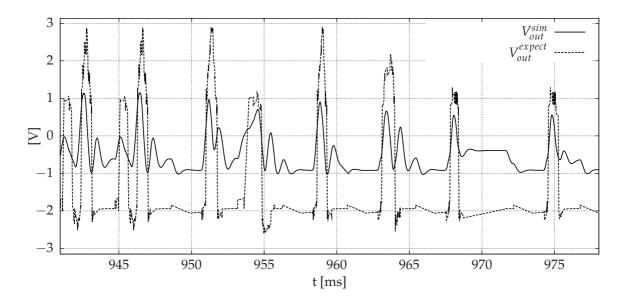

| 6.8              | Transient response to the complete-coverage input stimulus of the                                                                                                                                                                          |     |

|                  | Sallen-Key biquad lowpass filter with the expected response generated                                                                                                                                                                      |     |

|                  | by the hyperbox discretization approach                                                                                                                                                                                                    |     |

| 6.9              | Circuit schematic of the CMOS charge pump                                                                                                                                                                                                  |     |

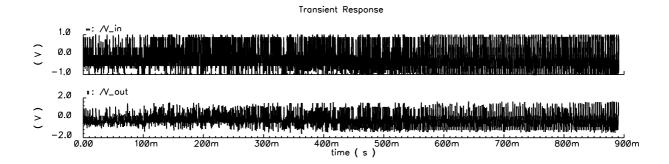

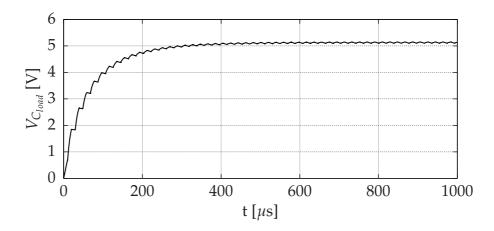

|                  | Transient output waveform of the CMOS charge pump circuit                                                                                                                                                                                  | 129 |

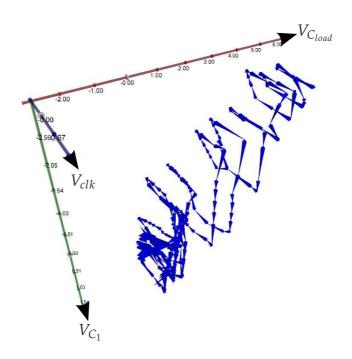

| 6.11             | Startup trajectory projected to $V_{C_1}$ , $V_{C_{load}}$ and $V_{clk}$ , identified by evaluat-                                                                                                                                          |     |

|                  | ing the ASL property specification on the DATS of the charge pump                                                                                                                                                                          | 130 |

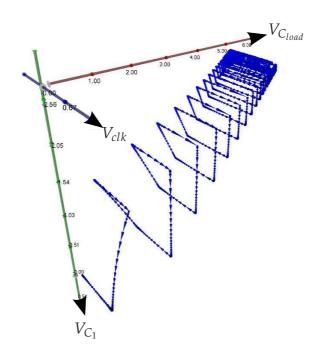

| 6.12             | Transient simulation waveforms of the charge pump for $V_{C_1}$ , $V_{C_{load}}$ and                                                                                                                                                       |     |

|                  | $V_{clk}$ transferred into a DATS representation for application of ASL veri-                                                                                                                                                              | 404 |

|                  | fication algorithms.                                                                                                                                                                                                                       |     |

|                  | Circuit schematic of the voltage controlled oscillator                                                                                                                                                                                     | 132 |

| 6.14             | Oscillation areas of the voltage controlled oscillator at different control                                                                                                                                                                | 400 |

|                  | voltages                                                                                                                                                                                                                                   | 133 |

|                  | Circuit schematic of the biquad bandpass filter circuit netlist                                                                                                                                                                            | 136 |

| 6.16             | Complete generated input stimulus and transient output response of the                                                                                                                                                                     |     |

|                  | biquad bandpass filter transistor netlist (Output_A) and VHDL-AMS be-                                                                                                                                                                      | 105 |

| ( 1 <del>-</del> | havioral model (Output_B).                                                                                                                                                                                                                 | 13/ |

| 6.17             | Transient response to the generated input stimulus of the biquad band-<br>pass filter plotted over $V_{C_1}$ and $V_{C_2}$                                                                                                                 | 137 |

| 6.18             | Circuit schematic of the second-order delta-sigma modulator                                                                                                                                                                                |     |

| 6.19 | Simple behavioral model for the second-order delta-sigma modulator      |     |

|------|-------------------------------------------------------------------------|-----|

|      | using an allpass filter for signal delay modeling                       | 138 |

| 6.20 | Transient response to the generated input stimulus of the delta-sigma   |     |

|      | modulator transistor netlist plotted over $V_{C_1}$ and $V_{C_2}$       | 139 |

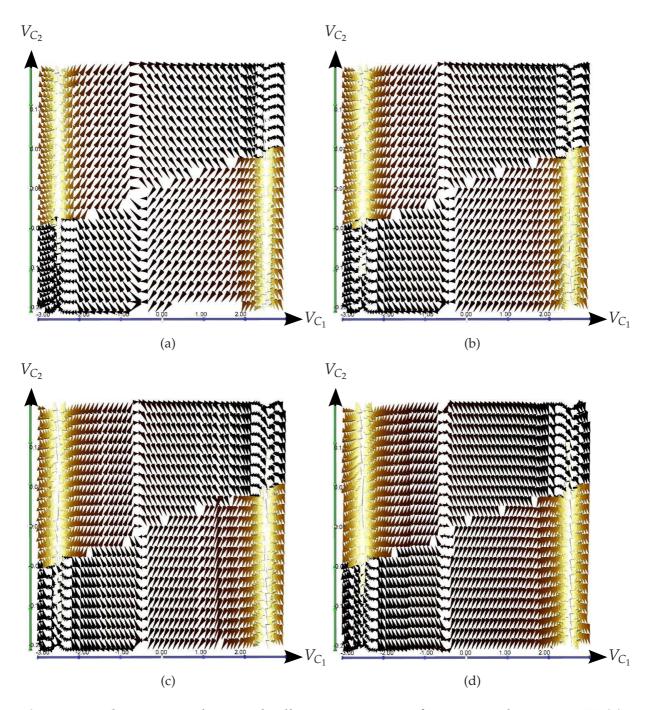

| A.1  | State space slices with all state transitions for input voltages 0.66 V |     |

|      | (a), 0.83 V (b), 1.00 V (c) and 1.17 V (d) showing the adaption of the  |     |

|      | trajectory-directed discretization to the changed transition structure  | 148 |

## List of Algorithms

| 1 | Trajectory-Directed Partitioning Algorithm           | 39  |

|---|------------------------------------------------------|-----|

| 2 | ASL Transition Algorithm.                            | 71  |

| 3 | ASL Oscillation Algorithm                            | 71  |

| 4 | ASL Delta_compare Algorithm                          | 72  |

| 5 | Counterexample Generation Algorithm                  | 105 |

| 6 | Complete-Coverage Input Stimuli Generation Algorithm | 108 |

| 7 | Particle Simulation Algorithm                        | 115 |

## List of Symbols and Abbreviations

| Notation            | n                                                                             |

|---------------------|-------------------------------------------------------------------------------|

| х                   | Scalar value $x \in \mathbb{R}$                                               |

| x                   | Vector $\mathbf{x} = (x_1, x_2,, x_n)^T \in \mathbb{R}^n$                     |

| A                   | Matrix $\mathbf{A} \in \mathbb{R}^{n \times n}$                               |

| x                   | Absolute value of <i>x</i>                                                    |

| [x]                 | Interval $[x] = [\underline{x}, \overline{x}]$                                |

| $\ \mathbf{x}\ $    | Vector norm of x                                                              |

| ×                   | Temporal derivative of $\mathbf{x}(t)$                                        |

| f()                 | Function returning a scalar                                                   |

| $\mathbf{f}()$      | Function returning a vector                                                   |

|                     |                                                                               |

| Symbols             | 5                                                                             |

| a                   | Vertices constraining a partition of the trajectory-directed discretization   |

| $\alpha, \beta$     | Scalar factors                                                                |

| В                   | Orthogonal basis                                                              |

| $\mathcal{C}$       | Runtime complexity                                                            |

| deg                 | Out-degree                                                                    |

| $\Delta_{rs}$       | Length difference ratio between two vectors $\mathbf{v}_r$ and $\mathbf{v}_s$ |

| $\epsilon$          | Error function                                                                |

| $\epsilon_{\Delta}$ | Mean direction error                                                          |

| $\epsilon_{	heta}$  | Mean length error                                                             |

| $\epsilon_{suc}$    | Mean successor relation error                                                 |

| J                   | Jacobian matrix                                                               |

| k                   | Number of state space partitions (Section 2.4)                                |

Approximated number of sample points of the trajectory-directed dis-K cretization in one dimension L Labeling function  $L_A$ Labeling function of the DATS for the atomic propositions  $L_T$ Labeling function of the DATS for the atomic transition propositions  $L_V$ Labeling function of the DATS for the extended state space variable values  $L_X$ Labeling function of the DATS for the DAE system's inner variable values M Model Number of dimensions of the extended state space  $\mathbf{z}^{(e)}$  $n_d$ Number of input variables in **u**  $n_u$ Number of output variables in **y**  $n_{\nu}$ Number of linear independent state space variables in **z**  $n_z$ 0 Asymptotic upper complexity bound P Property space  $P_{spec}$ Specification Ordered sequence of states  $\pi = \sigma_1, \sigma_2, ..., \sigma_n$  representing a directed state  $\pi$ path П Set of paths  $\Pi = \{\pi_1, \pi_2, ..., \pi_n\}$ Formula in a specification logic φ, ψ Points in  $\mathcal{Z}$ p,q R Transition relation  $\mathcal{R}$ Partition of  $\mathcal{Z}$  $\mathbb{R}$ Set of all real numbers User-defined scalar value r S System  $\Sigma$ Unordered set  $\Sigma = \{\sigma_1, \sigma_2, ..., \sigma_n\}$  of states TTemporal labeling function for the edges of a DATS  $\theta_{rs}$ Angle between two vectors  $\mathbf{v}_r$  and  $\mathbf{v}_s$ Vector  $\mathbf{u} = (u_1, u_2, ..., u_{n_u})^T$  of input variables u Continuous vector field in  $\mathbb{R}^{n_d}$  $\mathcal{V}$ Direction vector

**v** Vector  $\mathbf{x} = (x_1, x_2, ..., x_{n_x})^T$  of inner variables of a system

y Vector  $\mathbf{y} = (y_1, y_2, ..., y_{n_y})^T$  of output variables

**z** Vector  $\mathbf{z} = (z_1, z_2, ..., z_{n_z})^T$  of linear independent state space variables

$\mathbf{z}^{(e)}$  Vector  $\mathbf{z}^{(e)}$  of extended state space variables  $(\mathbf{z}^T, \mathbf{u}^T)^T$

$\mathcal{Z}$  Infinite point set in  $\mathbb{R}^{n_d}$

$\mathbb{Z}$  Set of all integer numbers

#### Abbreviations

ABV Assertion-Based Verification

AC Alternating Current

AMS Analog/Mixed-Signal

AP Atomic Proposition

ASL Analog Specification Language

ATPG Automatic Test Pattern Generation

AVF Analog Verification Framework

BCE Branch Constitutive Equation

BDD Binary Decision Diagram

BE Backward Euler

BMD Binary Moment Diagram

CCIS Complete-Coverage Input Stimuli

CMOS Complementary Metal Oxide Semiconductor

CTL Computation Tree Logic

DAE Differential Algebraic Equation

DATS Discrete Analog Transition Structure

DC Direct Current

DUV Design Under Verification

EBNF Extended Backus-Naur-Form

EC Equivalence Checking

EDA Electronic Design Automation

FE Forward Euler

HDL Hardware Description Language

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

LIC Line Integral Convolution

LTE Local Truncation Error

LTL Linear Temporal Logic

MC Model Checking

MNA Modified Nodal Analysis

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NP Nondeterministic Polynomial Time

NR Newton-Raphson

ODE Ordinary Differential Equation

OVL Open Verification Library

PL List of accepted partitioning points

PSL Property Specification Language

RF Radio Frequency

RTCTL Real Time Computation Tree Logic

SAT Satisfiability Problem of Boolean Formulas

SERE Sequential Extended Regular Expression

SMV Symbolic Model Verifier

SPICE Simulation Program with Integrated Circuit Emphasis

STL Signal Temporal Logic

SVA System Verilog Assertions

TDD Trajectory-Directed Discretization

TR Transient

TRA Transient Analysis

VCO Voltage Controlled Oscillator

VHDL Very High Speed Integrated Circuit Hardware Description Language

WL Waiting List

# Introduction

The impact of electronic devices on our everyday life is inevitable. With the dependency on electronics increasing continuously, the consequences of errors in such electronic systems are increasing just as well. There are several levels of severity from just being disconnected during a phone call to possible airplane crashes due to errors in the electronic components. Even for non-safety-critical cases, errors in electronic systems have an economic dimension, where the cost of missed design flaws is determining whether a company can stay competitive or not.

Due to the increasing system complexity and decreasing time to market, design verification has become a more and more crucial part of the electronic circuit design flow. While formal verification methods are established in the digital domain, industrial analog circuit design flows are lacking formal or at least formalized verification methodologies. Analog circuit verification still depends on the designer's experience and expertise to manually define appropriate test benches for simulation-based design flows and to select the right input signals in order to detect possible design errors.

In contrast to the common perception of digital circuits dominating today's electronic devices, the importance of analog circuits and especially of analog circuit design is increasing. This is due to the fact that most electronic circuits are nowadays mixed-signal systems, using analog interfaces to the external environment in combination with a digital core. Moreover, with decreasing feature sizes, not only the relative percentage of the not equally-scaling analog part of mixed-signal designs increases, but also the analog behavior of digital circuit components becomes more and more critical.

Finally, important parts of digital systems such as clock generators have always been designed on the analog level.

Hence, driven by the perennial demand for higher design efficiency, new methodologies offering more automation of the analog verification process are of vital importance.

While approaches to assertion-based simulation are emerging, which are mainly automating previously manual efforts, they are not targeting the fundamental problem of analog circuit verification: verification coverage. Today's established common verification methodology is analyzing the circuit's behavior by simulation using test benches. Specification conformance is checked by performing several transient simulations with input signals which are considered to be representative for the future operating conditions of the circuit. Although this approach to discover design errors has been working for decades, redesigns have occurred frequently due to missing some critical behavior of the circuit during simulation.

There has been significant progress in several areas of electronic design automation (EDA) for analog circuits. Some complex tasks such as sizing, placement and design centering have been addressed by EDA-vendors, now being available as automated tools which are fully integrated into the design flow. These tools are exploiting algorithmic concepts which by far outperform manual approaches. By contrast, the area of analog design verification is not yet systematically covered by existing tools.

Therefore, the goal of this thesis is to advance the field of formal verification methodologies for analog circuits in order to contribute to the development and future productive application of analog formal verification methodologies.

#### 1.1 Analog Circuit Design Flow

The objective of the design flow for analog circuits is to transfer a functional specification of the design into a physical implementation satisfying the specification. Between the initial specification and the final implementation, several design steps are required in order to hierarchically partition the complex tasks into solvable portions.

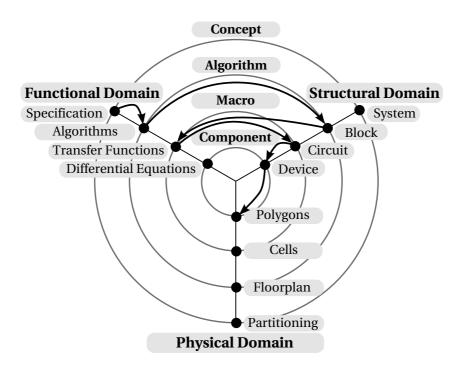

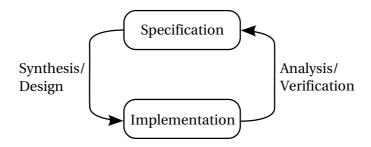

For a classification of the design abstraction levels and the design domains, the application of the Y-chart to the analog design task offers a structured approach to this hierarchy [GDWL92, HBKK94]. The Y-chart consists of three views which build the functional domain, the structural domain and the physical domain. Different levels of abstraction range from the top-level concept layer to the low-level component layer. Descending from higher abstraction levels to lower levels by increasing the overall complexity of the design is regarded as synthesis. Comparing the conformance of lower levels of abstraction with higher levels or different domains is regarded as analysis. Figure 1.1 shows the Y-chart for the analog design flow with a possible top-down

**Figure 1.1:** Y-chart for hierarchical analog design with exemplary synthesis steps.

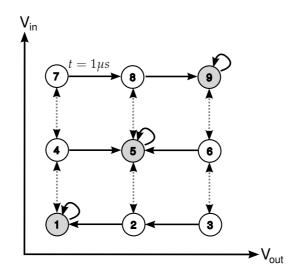

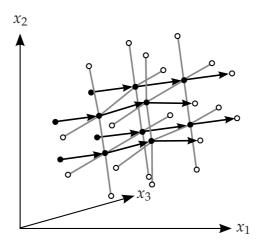

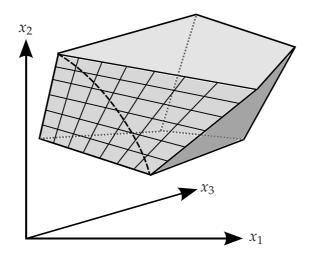

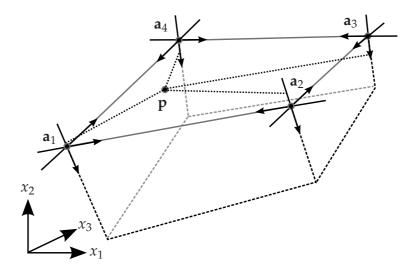

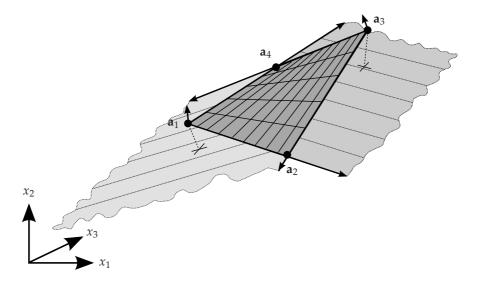

design flow from the functional specification to the physical implementation, which will be explained in the following.